アクティブマトリックス型表示装置の駆動方法

【課題】電源投入時、あるいは信号投入時に良好な画質を維持するようにする。

【解決手段】電源が安定した後、出画素選択ゲートドライバ部200が全画素回路101をスキャンし、最後の点灯オンオフドライバ部300から、点灯オンオフゲート信号(BG1―BGn)を出力する。このとき点灯オンオフシフトレジスタ301のスタートパルスSTV2は、点灯オンオフゲート信号出力制御回路302の出力イネーブル信号OEV2が出力された後に、スタートするようにし、走査信号としての点灯オンオフゲート信号(BG1―BGn)が不用意に画素回路に供給されないようにした。

【解決手段】電源が安定した後、出画素選択ゲートドライバ部200が全画素回路101をスキャンし、最後の点灯オンオフドライバ部300から、点灯オンオフゲート信号(BG1―BGn)を出力する。このとき点灯オンオフシフトレジスタ301のスタートパルスSTV2は、点灯オンオフゲート信号出力制御回路302の出力イネーブル信号OEV2が出力された後に、スタートするようにし、走査信号としての点灯オンオフゲート信号(BG1―BGn)が不用意に画素回路に供給されないようにした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば有機エレクトロ・ルミネセンス素子(以下有機EL素子と言う)を用いた表示装置であり、特に電源投入時、全画面信号投入時に画面上で横輝度線などが生じるのを防止するもので、駆動開始時の画質品位維持を得るアクティブマトリックス型表示装置の駆動方法に関する。

【背景技術】

【0002】

有機EL表示素子を用いたアクティブマトリックス型表示装置が開発されている。この装置では、有機EL表示素子を駆動する駆動トランジスタの特性が各画素間でほぼ同一であることが要求される。しかしながら、通常、トランジスタをガラス基板などの絶縁体上に形成するため、トランジスタ特性のばらつきを生じ易い。

【0003】

この問題に対しては、閾値キャンセル型回路、カレントコピー型回路が提案されている(特許文献1及び2を参照のこと)。これら回路によると、駆動電流に駆動トランジスタの閾値が与える影響を排除することができる。したがって、画素間で駆動トランジスタの閾値がばらついていたとしても、そのようなばらつきが有機EL素子に供給する駆動電流に与える影響を最小とすることができる。

【特許文献1】米国特許第6,229,506B1号明細書

【特許文献2】米国特許第6,373,454B1号明細書

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記の閾値キャンセル型回路、カレントコピー型回路による効果は、表示装置が動作状態にあるときのものである。しかし本発明者は、特に電源投入時、全画面が例えば黒に変化するような信号投入時の画質品位に着目している。即ち、表示装置の各部に対する電源電圧を印加するシーケンスは、ドライブ回路及び画素回路の電源電圧が安定した後、画素回路の走査信号と画素選択パルスが順次出力されることが好ましい。しかしながら、このような起動を行ったとしても、部分的に横輝線が現われる等、画質品位上好ましくないことがわかった。

【0005】

そこでこの発明は、電源投入時、あるいは信号投入時に良好な画質を維持することができるアクティブマトリックス型表示装置の駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

この発明の一例では、基板上にマトリックス状に配列された複数の画素回路と、前記複数の画素回路の容量に対して信号を書き込むために、画素回路の行毎にシフトした選択を行ない、信号書き込み期間を設定する画素選択ゲート信号を選択した行のラインに与える画素選択ゲートドライバと、前記複数の画素回路の表示素子の発光期間を設定するために、前記画素回路の行毎にシフトした選択を行ない、点灯オンオフゲート信号を選択した行のラインに与える点灯オンオフドライバとを有し、前記点灯オンオフドライバは、スタートパルスでシフト動作を開始する点灯オンオフシフトレジスタと、出力イネーブル信号が与えられることにより前記点灯オンオフシフトレジスタの出力を導出する点灯オンオフゲート信号出力制御回路と、この点灯オンオフゲート信号出力制御回路の出力のレベルを調整して前記行のラインに与えるレベルシフタとからなり、前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされた後に、前記点灯オンオフシフトレジスタをスタートさせることを特徴とする。

【発明の効果】

【0007】

電源投入時、あるいは信号投入時の表示品位が確保できる。

【発明を実施するための最良の形態】

【0008】

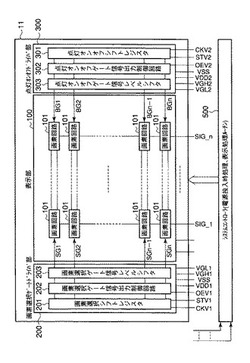

以下この発明の一実施形態として有機EL表示装置を例に取り、図面を参照して説明する。図1は、この発明が適用された表示装置の概略図である。ガラス基板11の中央には、表示部100が構築されている。この表示部100には、画素回路101がマトリックス状に配列されている。画素回路101の具体的構成例については後述する。

【0009】

表示部100には、列として配線された信号線SIG_1〜SIG_Nに映像信号を供給する信号線駆動回路が接続されているがここでは省略している。また表示部100には、行として配列された複数の走査線を駆動する走査線駆動回路が接続される。走査線駆動回路は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300として示されている。図では、画素選択ゲートドライバ部200と点灯オンオフドライバ部300とが、表示部100の左右に配置されているがいずれか一方に両者が配置されていても良い。

【0010】

画素選択ゲートドライバ部200は、画素選択シフトレジスタ201を含む。この画素選択シフトレジスタ201は、水平周期に同期して水平方向へ配列されている画素群を、1行ずつ垂直方向へ順次走査するために、走査線駆動信号を出力する。走査線駆動信号は、画素選択ゲート信号出力制御回路202に入力される。画素選択ゲート信号出力制御回路202は、走査線駆動信号の出力又は非出力を制御する回路であり、システム電源投入時に出力タイミングを得るために利用される。

【0011】

この画素選択ゲート信号出力制御回路202から出力された走査線駆動信号は、画素選択ゲート信号レベルシフタ203を介して、画素回路に画素選択ゲート信号SG1-SGnとして出力される。この画素選択ゲート信号SG1-SGnは、画素回路に対して、画素信号を書き込むためのタイミング信号として利用される。

【0012】

一方、点灯オンオフドライバ部300は、点灯オンオフシフトレジスタ301を含む。この点灯オンオフシフトレジスタ301は、水平周期に同期して水平方向へ配列されている画素群を、1行ずつ垂直方向へ順次走査するために、走査線駆動信号を出力する。走査線駆動信号は、点灯オンオフゲート信号出力制御回路302に入力される。点灯オンオフゲート信号出力制御回路302は、走査線駆動信号の出力又は非出力を制御する回路であり、システム電源投入時に出力タイミングを得るために利用される。

【0013】

この点灯オンオフゲート信号出力制御回路302から出力された走査線駆動信号は、点灯オンオフゲート信号レベルシフタ303を介して、画素回路に点灯オンオフゲート信号BG1-BGnとして出力される。この点灯オンオフゲート信号BG1-BGnは、画素回路に対して、表示素子の点灯期間を設定するタイミング信号として利用される。

【0014】

表示装置の全体は、システムコントローラ500により統括されて制御される。システムコントローラ500は、ガラス基板11上に構築されてもよいし、外部に設けられてもよい。このシステムコントローラ500内には、各種の処理プログラムが含まれており、電源投入時の立ち上げ処理を行うルーチン、さらには通常動作時の信号処理ルーチンなどが実現される。本発明の要部となるタイミングパルスを得るのもこのシステムコントローラ500で生成される。さらにまた、システムコントローラ500には、外部から映像信号データ、同期パルス、クロックなどが供給されている。

【0015】

図2には、上記の画素選択ゲートドライバ部200と点灯オンオフドライバ部300とをさらに具体化して示している。

【0016】

画素選択シフトレジスタ201は、少なくとも表示部の水平ライン数分が縦列接続された保持回路SRA1、SRA2、SRA3、…を有し、水平周期に同期したクロックCKV1により駆動される。VDD1,VSSは高電位側の電源電圧と低電位側の電源電圧であり、保持回路SRA1、SRA2、SRA3、…に供給されている。またSTV1は、画素選択シフトレジスタ201のスタートパルスとして用いられる。このパルスは、垂直周期に同期して供給されている。保持回路SRA1、SRA2、SRA3、…は、スタートパルスSTV1をクロックCKV1に同期して順次次段に転送する。

【0017】

画素選択ゲート信号出力制御回路202は、少なくとも表示部の水平ライン数分のナンド回路NA1、NA2、NA3、…からなる。このナンド回路NA1、NA2、NA3、…の各一方の入力端には、対応する保持回路SRA1、SRA2、SRA3、…の出力がそれぞれ供給され、他方の入力端には共通に、出力イネーブル信号OEV1が供給される。この出力イネーブル信号OEV1がローレベルになった時、保持回路SRA1、SRA2、SRA3、…の出力が、それぞれ対応するナンド回路NA1、NA2、NA3、…を介して出力される。ナンド回路NA1、NA2、NA3、…の出力は、それぞれ対応するレベルシフタLSA1、LSA2、LSA3、…に入力され、表示部100に適合したレベルに変換された後、表示部100に供給される。VGH1、VGL1は、レベルシフタの出力電位を決めるための電圧であり、高電位側の電源電圧と低電位側の電源電圧である。

【0018】

点灯オンオフシフトレジスタ301は、少なくとも表示部の水平ライン数分が縦列接続された保持回路SRB1、SRB2、SRB3、…を有し、水平周期に同期したクロックCKV2により駆動される。VDD2,VSSは高電位側の電源電圧と低電位側の電源電圧であり、保持回路SRB1、SRB2、SRB3、…に供給されている。またSTV2は、点灯オンオフシフトレジスタ301のスタートパルスとして用いられる。このパルスは、垂直周期に同期して供給されている。保持回路SRB1、SRB2、SRB3、…は、スタートパルスSTV2をクロックCKV2に同期して順次次段に転送する。

【0019】

点灯オンオフゲート信号出力制御回路302は、少なくとも表示部の水平ライン数分のナンド回路NB1、NB2、NB3、…からなる。このナンド回路NB1、NB2、NB3、…の各一方の入力端には、対応する保持回路SRB1、SRB2、SRB3、…の出力がそれぞれ供給され、他方の入力端には共通に、出力イネーブル信号OEV2が供給される。この出力イネーブル信号OEV2がローレベルになった時、保持回路SRB1、SRB2、SRB3、…の出力が、それぞれ対応するナンド回路NB1、NB2、NB3、…を介して出力される。ナンド回路NB1、NB2、NB3、…の出力は、それぞれ対応するレベルシフタLSB1、LSB2、LSB3、…に入力され、表示部100に適合したレベルに変換された後、表示部100に供給される。VGH2、VGL2は、レベルシフタの出力電位を決めるための電圧であり、高電位側の電源電圧と低電位側の電源電圧である。

【0020】

図3(A)と図3(B)には、画素回路の例を示している。いずれの画素回路が用いられてもよい。図3(A)の回路から説明する。第1電圧(ここではアノード電圧)PVDDが与えられた第1の電源ラインには、駆動トランジスタTRのソースが接続されている。駆動トランジスタTRのゲートとソース間には、容量C1が接続されている。駆動トランジスタTRのドレインは、スイッチSW1を介して信号線SIGに接続されている。駆動トランジスタTRのゲートとドレイン間には、スイッチSW2が接続されている。駆動トランジスタTR、スイッチSW1,SW2は薄膜トランジスタで構成されている。スイッチSW1,SW2のゲートは、画素選択を行う走査線に接続されており、ここには、対応する画素選択ゲート信号SG1-SGnが供給される。

【0021】

駆動トランジスタTRのドレインは、薄膜トランジスタで構成されるスイッチSW3のソースに接続される。このスイッチSW3のドレインは、有機EL素子である表示素子OELD1の一方の電極(ここではアノード)に接続されている。スイッチSW3のゲートは、点灯オンオフゲート信号BG1-BGnのいずれか1つが与えられている走査線に接続されている。

【0022】

画素選択ゲート信号によりスイッチSW1、SW2がオンしたときに、信号線に流れる信号電流に応じて、容量C1に駆動トランジスタTRのソース−ドレイン間電流に対応する信号電圧が供給される。スイッチSW1、SW2がオフすると、この信号電圧が容量C1に保持され、次いでスイッチSW3がオンすると、容量C1に蓄積されている信号電圧に見合う電流が駆動トランジスタTR、スイッチSW3を介して、表示素子OELD1に流れる。発光量は、表示素子OELD1に流れる電流にほぼ比例する。スイッチSW3は、点灯オンオフゲート信号により制御されている。

【0023】

図3(B)の回路は、スイッチSW1のソースが信号線に接続され、ドレインが直接トランジスタTRのゲートに接続されている。スイッチSW1がオンしたときに、容量C1に信号電圧が供給される。スイッチSW1がオフすると信号電圧が容量C1に保持され、次いでスイッチSW3がオンすると、容量C1に蓄積されている信号電圧に見合う電流が駆動トランジスタTR、スイッチSW3を介して、表示素子OELD1に流れる。発光量は、表示素子OELD1に流れる電流にほぼ比例する。

【0024】

図4(A−F)には、上記の装置の電源投入時の動作を示している。図4(A)は、電源電圧VSSを基準にして、装置内で用いられる各種の電源電圧を示している。VGH1、VGH2、PVDD、VDD1、VDD2、VGL1、VGL2、PVSSは、図示していないが電源回路で作成されている。図4(B)、図4(C)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300で用いられる出力イネーブル信号OEV1とOEV2の出力の変化を示している。また、図4(D)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるクロックCKV1、CKV2の出力の変化を示している。図4(E)、図4(F)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるスタートパルスSTV1、STV2の出力の様子を示している。

【0025】

時点t1で電源がオンされると、出力イネーブル信号OEV1とOEV2はローレベルに固定される。クロックCKV1、CKV2、スタートパルスSTV1、STV2は、通常動作状態になる。次に、各種電源電圧が安定した時点t2から一定時間が経過すると、時点t3で出力イネーブル信号OEV1が通常動作状態に移行する。そして1垂直期間(1V)後に出力イネーブル信号OEV2が通常動作状態に移行する。

【0026】

つまり、電源投入時には、まず表示部100の全体の全画素回路に対して信号電圧(例えば黒レベルあるいは表示信号)が書き込まれた後に、はじめて、点灯オンとなり、全画面の表示が得られるようになっている。

【0027】

図5(A−Z)には、上記のように電源が投入されたときの装置各部の信号変化の様子を示している。図示している期間は、垂直ブランキング期間(VBLK)の時間的に前後する付近である。図5(A)には、垂直同期信号を示している。図5(B)には、対応する水平ライン(LINE1〜LINEN+4)を示している。図5(C)、図5(D)は、第2と第1の出力イネーブル信号OEV2とOEV1を示している。出力イネーブル信号OEV1が通常動作を開始して1垂直期間経過した後、出力イネーブル信号OEV2がスタートしている。

【0028】

第1の出力イネーブル信号OEV1により、図5(H)〜(K)の画素選択ゲート信号SG1〜SG4、図5(L)〜(P)の画素選択ゲート信号SGn〜SGn+4が出力される。

【0029】

第2の出力イネーブル信号OEV2がスタートした時点t4から、図5(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図5(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4、が順次得られる。図5(Z)のVGH2は、点灯オンオフドライバ部300のレベルシフタにおける高電位側の電源電圧である。

【0030】

ここで発明者は、点灯オンオフゲート信号出力制御回路302からシフトレジスタの出力を許可するために出力イネーブル信号OEV2がハイレベルに移行したときに、問題があることに着目した。即ち、今、図5(Q)−(Y)に示すように、点灯オンオフ信号がハイレベルであるとする。ここで垂直同期期間の終わり(時点t4)に、出力イネーブル信号OEV2がローレベルからハイレベルに切り換わるものとする(図5(C))。また、シフトレジスタ301によるシフト動作が、図5(Y)、(Q)−(T)のように進行するものとする。すると今、時点t4で、出力イネーブル信号OEV2がローレベルからハイレベルに切り換わると、点灯オンオフゲート信号BG4−BGn+3がハイレベルから一斉にローレベルとなる(図の縦長の楕円の点線で囲む部分)。これは、既に、点灯オンオフシフトレジスタ301が動作しており、殆どのシフトレジスタ出力(点灯オンオフゲート信号BG4−BGn+3に対応)がローレベル(点灯オン制御状態)に切り換わる必要があるからでる。一方では、このとき、ハイレベルを維持すべき点灯をオフすべきオンオフゲート信号が存在する(図5(Y)、(Q)−(T)の点灯オンオフ信号)。これは信号書き込みが行われる期間に相当するからである。

【0031】

しかし、これらの点灯オンオフ信号(図5(Y)、(Q)−(T))は一時的に低下する現象が見られる。この要因は、点灯オンオフゲート信号BG4−BGn+3がハイレベルから一斉にローレベルとなり、基板の電圧VGH2が一時的に低下したことに起因する。このように点灯オンオフ信号(図5(Y)、(Q)−(T))が一時的に低下すると、この点灯オンオフ信号が供給されるスイッチSW3が瞬間的に電流が流れ、表示素子が瞬間的に点灯するという問題がある。

【0032】

そこで発明者は、さらに駆動方法を考慮し、以下の対策を施すものである。即ち、図6(A−F)に示すように、装置の各部のスタートシーケンスにおいて、特に点灯オンオフシフトレジスタ301のスタートパルスSTV2を点灯オンオフゲート信号出力制御回路302の出力イネーブル信号OEV2がスタートした時点よりも遅くするのである。図6(A−F)には、その様子を示すタイミングチャートを示している。

【0033】

図6の(A)は、電源電圧VSSを基準にして、装置内で用いられる各種の電源電圧を示している。VGH1、VGH2、PVDD、VDD1、VDD2、VGL1、VGL2、PVSSは、図示していないが電源回路で作成されている。図6(B)、図6(C)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300で用いられる出力イネーブル信号OEV1とOEV2の出力の変化を示している。また、図6(D)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるシフトクロックCKV1、CKV2の出力の変化を示している。図6(E)、図6(F)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるスタートパルスSTV1、STV2の出力の様子を示している。

【0034】

時点t1で電源がオンされると、出力イネーブル信号OEV1とOEV2はローレベルに固定される。シフトクロックCKV1、CKV2、スタートパルスSTV1は、通常動作状態になる。次に、各種電源電圧が安定した時点t2から一定時間が経過すると、時点t3で出力イネーブル信号OEV1が通常動作状態に移行する。そして1垂直期間(1V)後に出力イネーブル信号OEV2が通常動作状態に移行する(時点t4)。そして、次に、時点t5で点灯オンオフシフトレジスタ301のスタートパルスSTV2がスタートする。

【0035】

つまり、電源投入時には、まず表示部100の全画素回路に対して信号電圧が書き込まれた後に、はじめて、点灯オンとなり、全画面の表示が得られるようになっている。

【0036】

図7(A−Z)には、上記のような動作シーケンスを持つ装置各部の信号変化の様子を示している。図示している期間は、垂直ブランキング期間(VBLK)の時間的に前後する付近である。同一の図7(A)には、垂直同期信号を示している。図7(B)には、水平ライン(LINE1〜LINEN+4)を示している。図7(C)、図7(D)は、第1と第2の出力イネーブル信号OEV2とOEV1を示している。出力イネーブル信号OEV1が通常動作を開始して1垂直期間経過した後、出力イネーブル信号OEV2がスタートしている。

【0037】

第1の出力イネーブル信号OEV1により、図7(H)〜(K)の画素選択ゲート信号SG1〜SG4、図7(L)〜(P)の画素選択ゲート信号SGn〜SGn+4が出力される。

【0038】

第2の出力イネーブル信号OEV2がスタートした時点t4から、一定時間が経過した後の時点t5以降に、図7(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図7(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4、が順次得られる。これは、図7の(G)に示すように、例え出力イネーブル信号OEV2がスタートしたとしても、シフトレジスタ301の出力がローレベルに固定されており、時点t5で初めてシフト動作が開始されるからである。図7(Z)のVGH2は、点灯オンオフドライバ部300のレベルシフタにおける高電位側の電源電圧である。

【0039】

このような動作シーケンスにすると、点灯オンオフドライバ部300のレベルシフタにおける高電位側の電源電圧の変動もない。また図5で示した点灯オンオフゲート信号のような電位変動がない。この結果、画素点灯オンオフを決めるスイッチSW3が一時的に不要な導通状態となることが防止され、画質の品位を維持することが可能となる。

【0040】

この発明は、上記の実施の形態に限定されるものではない。図8(A−F)にはこの発明の他の実施の形態の動作を示すタイミングチャートを示している。図6に示したタイミングチャートと同じ部分には、同じ符号を付している。図6に示したタイミングチャートと異なる部分を説明する。この実施の形態においても、基本的には、点灯オンオフシフトレジスタ301のスタートパルスSTV2の通常動作スタート時点t6を点灯オンオフゲート信号出力制御回路302の出力イネーブル信号OEV2がスタートした時点t5よりも遅くするのである。この考え方は、図6の実施形態と変わりはない。しかし、図6の実施の形態と異なる部分は、点灯オンオフドライバ部300の例えば1垂直期間のウォーミングアップ期間(時点t3−t4)を設けこの間はシフトレレジスタ301のスタートパルスを正常動作させるのである。次の再開時の不安定動作が防止される。しかしこのウオーミングアップ期間(1垂直期間)は、ゲート信号出力制御回路302の出力イネーブル信号OEV2がローレベルに固定されているので、点灯オンオフゲート信号が出力することはない。点灯オンオフゲート信号が出力するのは時点t6以降ということになる。

【0041】

この発明は、上記の実施の形態に限定されるものではない。図9(A―Z)にはこの発明の他の実施の形態の動作を示すタイミングチャートを示している。図9(A―Z)において図7(A−Z)と異なる部分は、図9(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図9(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4のデューティーが異なる点である。ここでは、点灯オンオフゲート信号のデューティーを例えば1垂直期間の1/4のデューティーにする。例えば、1垂直期間の内、4番目の水平期間に対応する期間を間引きするのである。この様子を示したのが、図9(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図9(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4である。このためには、シフトレジスタ301に与えるスタートパルスSTV2を4水平周期毎に与えるとよい。

【0042】

このようなシーケンスで起動した場合の動作は以下のようになる。即ち、スタートパルスSTV2が、図4で説明したように電源投入と同時にスタートしたとする。そして、図4のように時点t4で出力イネーブルゲート信号OEV2がハイレベルになったとする。すると、当然、点灯オンオフゲート信号の出力ラインのうち多くはハイレベルを維持すべきライン(点灯オフを維持するため)と、反転すべきライン(点灯スタートのため)とが存在する。図4に示した例であると、点灯スタートするライン(点灯オンオフゲート信号が出力されるライン)が多いために、基板電圧までの変動し、これが、点灯オフすべきラインまでに影響あたえた。しかし本実施の形態によると、この影響は、図4、図5の例に比べて、1/4以下に低減する。

【0043】

本実施の形態では、点灯オンオフゲート信号のデューティーを1垂直期間の1/4のデューティーにしているからである。このことにより、時点t4で多くのライン(点灯オンオフゲート信号が出力されるライン)が一斉にローレベルに低下するのであるが、その本数は、図4、図5の例に比べて、1/4以下に低減している。よって、基板に対して電位変動を与える影響が低減し、これにともない、レベルシフタ303の出力レベルも変動を受け難くなるからである。上記の実施の形態では、点灯オンオフゲート信号のデューティーを1垂直期間の1/4のデューティーとしたが、これに限定されるものではない。1垂直期間の数分の1のデューティーであればよい。

【0044】

上記のように点灯オンオフゲート信号のデューティーを変化させる技術は、発光期間を制御して、輝度を調整する場合にも利用可能である。したがって、輝度調整機能と、電源投入時の画質劣化防止機能とを兼用させることが可能である。

【0045】

なお、この発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてもよい。

【図面の簡単な説明】

【0046】

【図1】本発明が適用されたアクティブマトリックス型表示装置の概略を示す図。

【図2】本発明に係る装置の画素選択ゲートドライバ部200と点灯オンオフドライバ部300の具体的構成例を示す図。

【図3】図1の画素回路の具体的構成例を示す図。

【図4】図1、図2の装置の電源投入時の全体の動作例を説明するために示したタイミングチャート。

【図5】図4のタイミングで動作したとき、図1、図2の装置のさらに各部の回路の動作例を説明するために示したタイミングチャート。

【図6】図1、図2の装置の電源投入時の全体の他の動作例を説明するために示したタイミングチャート。

【図7】図6のタイミングで動作したとき、図1、図2の装置のさらに各部の回路の動作例を説明するために示したタイミングチャート。

【図8】図1、図2の装置の電源投入時の全体のさらにまた他の動作例を説明するために示したタイミングチャート。

【図9】図1、図2の装置の電源投入時のまた他の動作例を説明するために示したタイミングチャート。

【符号の説明】

【0047】

100…表示部、200…が素選択ゲートドライバ部200、300…点灯オンオフドライバ部、201…画素選択シフトレジスタ、202…画素選択ゲート信号出力制御回路、203…画素選択ゲート信号レベルシフタ、301…点灯オンオフシフトレジスタ、302…点灯オンオフゲート信号出力制御回路、303…点灯オンオフゲート信号レベルシフタ。

【技術分野】

【0001】

本発明は、例えば有機エレクトロ・ルミネセンス素子(以下有機EL素子と言う)を用いた表示装置であり、特に電源投入時、全画面信号投入時に画面上で横輝度線などが生じるのを防止するもので、駆動開始時の画質品位維持を得るアクティブマトリックス型表示装置の駆動方法に関する。

【背景技術】

【0002】

有機EL表示素子を用いたアクティブマトリックス型表示装置が開発されている。この装置では、有機EL表示素子を駆動する駆動トランジスタの特性が各画素間でほぼ同一であることが要求される。しかしながら、通常、トランジスタをガラス基板などの絶縁体上に形成するため、トランジスタ特性のばらつきを生じ易い。

【0003】

この問題に対しては、閾値キャンセル型回路、カレントコピー型回路が提案されている(特許文献1及び2を参照のこと)。これら回路によると、駆動電流に駆動トランジスタの閾値が与える影響を排除することができる。したがって、画素間で駆動トランジスタの閾値がばらついていたとしても、そのようなばらつきが有機EL素子に供給する駆動電流に与える影響を最小とすることができる。

【特許文献1】米国特許第6,229,506B1号明細書

【特許文献2】米国特許第6,373,454B1号明細書

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記の閾値キャンセル型回路、カレントコピー型回路による効果は、表示装置が動作状態にあるときのものである。しかし本発明者は、特に電源投入時、全画面が例えば黒に変化するような信号投入時の画質品位に着目している。即ち、表示装置の各部に対する電源電圧を印加するシーケンスは、ドライブ回路及び画素回路の電源電圧が安定した後、画素回路の走査信号と画素選択パルスが順次出力されることが好ましい。しかしながら、このような起動を行ったとしても、部分的に横輝線が現われる等、画質品位上好ましくないことがわかった。

【0005】

そこでこの発明は、電源投入時、あるいは信号投入時に良好な画質を維持することができるアクティブマトリックス型表示装置の駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

この発明の一例では、基板上にマトリックス状に配列された複数の画素回路と、前記複数の画素回路の容量に対して信号を書き込むために、画素回路の行毎にシフトした選択を行ない、信号書き込み期間を設定する画素選択ゲート信号を選択した行のラインに与える画素選択ゲートドライバと、前記複数の画素回路の表示素子の発光期間を設定するために、前記画素回路の行毎にシフトした選択を行ない、点灯オンオフゲート信号を選択した行のラインに与える点灯オンオフドライバとを有し、前記点灯オンオフドライバは、スタートパルスでシフト動作を開始する点灯オンオフシフトレジスタと、出力イネーブル信号が与えられることにより前記点灯オンオフシフトレジスタの出力を導出する点灯オンオフゲート信号出力制御回路と、この点灯オンオフゲート信号出力制御回路の出力のレベルを調整して前記行のラインに与えるレベルシフタとからなり、前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされた後に、前記点灯オンオフシフトレジスタをスタートさせることを特徴とする。

【発明の効果】

【0007】

電源投入時、あるいは信号投入時の表示品位が確保できる。

【発明を実施するための最良の形態】

【0008】

以下この発明の一実施形態として有機EL表示装置を例に取り、図面を参照して説明する。図1は、この発明が適用された表示装置の概略図である。ガラス基板11の中央には、表示部100が構築されている。この表示部100には、画素回路101がマトリックス状に配列されている。画素回路101の具体的構成例については後述する。

【0009】

表示部100には、列として配線された信号線SIG_1〜SIG_Nに映像信号を供給する信号線駆動回路が接続されているがここでは省略している。また表示部100には、行として配列された複数の走査線を駆動する走査線駆動回路が接続される。走査線駆動回路は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300として示されている。図では、画素選択ゲートドライバ部200と点灯オンオフドライバ部300とが、表示部100の左右に配置されているがいずれか一方に両者が配置されていても良い。

【0010】

画素選択ゲートドライバ部200は、画素選択シフトレジスタ201を含む。この画素選択シフトレジスタ201は、水平周期に同期して水平方向へ配列されている画素群を、1行ずつ垂直方向へ順次走査するために、走査線駆動信号を出力する。走査線駆動信号は、画素選択ゲート信号出力制御回路202に入力される。画素選択ゲート信号出力制御回路202は、走査線駆動信号の出力又は非出力を制御する回路であり、システム電源投入時に出力タイミングを得るために利用される。

【0011】

この画素選択ゲート信号出力制御回路202から出力された走査線駆動信号は、画素選択ゲート信号レベルシフタ203を介して、画素回路に画素選択ゲート信号SG1-SGnとして出力される。この画素選択ゲート信号SG1-SGnは、画素回路に対して、画素信号を書き込むためのタイミング信号として利用される。

【0012】

一方、点灯オンオフドライバ部300は、点灯オンオフシフトレジスタ301を含む。この点灯オンオフシフトレジスタ301は、水平周期に同期して水平方向へ配列されている画素群を、1行ずつ垂直方向へ順次走査するために、走査線駆動信号を出力する。走査線駆動信号は、点灯オンオフゲート信号出力制御回路302に入力される。点灯オンオフゲート信号出力制御回路302は、走査線駆動信号の出力又は非出力を制御する回路であり、システム電源投入時に出力タイミングを得るために利用される。

【0013】

この点灯オンオフゲート信号出力制御回路302から出力された走査線駆動信号は、点灯オンオフゲート信号レベルシフタ303を介して、画素回路に点灯オンオフゲート信号BG1-BGnとして出力される。この点灯オンオフゲート信号BG1-BGnは、画素回路に対して、表示素子の点灯期間を設定するタイミング信号として利用される。

【0014】

表示装置の全体は、システムコントローラ500により統括されて制御される。システムコントローラ500は、ガラス基板11上に構築されてもよいし、外部に設けられてもよい。このシステムコントローラ500内には、各種の処理プログラムが含まれており、電源投入時の立ち上げ処理を行うルーチン、さらには通常動作時の信号処理ルーチンなどが実現される。本発明の要部となるタイミングパルスを得るのもこのシステムコントローラ500で生成される。さらにまた、システムコントローラ500には、外部から映像信号データ、同期パルス、クロックなどが供給されている。

【0015】

図2には、上記の画素選択ゲートドライバ部200と点灯オンオフドライバ部300とをさらに具体化して示している。

【0016】

画素選択シフトレジスタ201は、少なくとも表示部の水平ライン数分が縦列接続された保持回路SRA1、SRA2、SRA3、…を有し、水平周期に同期したクロックCKV1により駆動される。VDD1,VSSは高電位側の電源電圧と低電位側の電源電圧であり、保持回路SRA1、SRA2、SRA3、…に供給されている。またSTV1は、画素選択シフトレジスタ201のスタートパルスとして用いられる。このパルスは、垂直周期に同期して供給されている。保持回路SRA1、SRA2、SRA3、…は、スタートパルスSTV1をクロックCKV1に同期して順次次段に転送する。

【0017】

画素選択ゲート信号出力制御回路202は、少なくとも表示部の水平ライン数分のナンド回路NA1、NA2、NA3、…からなる。このナンド回路NA1、NA2、NA3、…の各一方の入力端には、対応する保持回路SRA1、SRA2、SRA3、…の出力がそれぞれ供給され、他方の入力端には共通に、出力イネーブル信号OEV1が供給される。この出力イネーブル信号OEV1がローレベルになった時、保持回路SRA1、SRA2、SRA3、…の出力が、それぞれ対応するナンド回路NA1、NA2、NA3、…を介して出力される。ナンド回路NA1、NA2、NA3、…の出力は、それぞれ対応するレベルシフタLSA1、LSA2、LSA3、…に入力され、表示部100に適合したレベルに変換された後、表示部100に供給される。VGH1、VGL1は、レベルシフタの出力電位を決めるための電圧であり、高電位側の電源電圧と低電位側の電源電圧である。

【0018】

点灯オンオフシフトレジスタ301は、少なくとも表示部の水平ライン数分が縦列接続された保持回路SRB1、SRB2、SRB3、…を有し、水平周期に同期したクロックCKV2により駆動される。VDD2,VSSは高電位側の電源電圧と低電位側の電源電圧であり、保持回路SRB1、SRB2、SRB3、…に供給されている。またSTV2は、点灯オンオフシフトレジスタ301のスタートパルスとして用いられる。このパルスは、垂直周期に同期して供給されている。保持回路SRB1、SRB2、SRB3、…は、スタートパルスSTV2をクロックCKV2に同期して順次次段に転送する。

【0019】

点灯オンオフゲート信号出力制御回路302は、少なくとも表示部の水平ライン数分のナンド回路NB1、NB2、NB3、…からなる。このナンド回路NB1、NB2、NB3、…の各一方の入力端には、対応する保持回路SRB1、SRB2、SRB3、…の出力がそれぞれ供給され、他方の入力端には共通に、出力イネーブル信号OEV2が供給される。この出力イネーブル信号OEV2がローレベルになった時、保持回路SRB1、SRB2、SRB3、…の出力が、それぞれ対応するナンド回路NB1、NB2、NB3、…を介して出力される。ナンド回路NB1、NB2、NB3、…の出力は、それぞれ対応するレベルシフタLSB1、LSB2、LSB3、…に入力され、表示部100に適合したレベルに変換された後、表示部100に供給される。VGH2、VGL2は、レベルシフタの出力電位を決めるための電圧であり、高電位側の電源電圧と低電位側の電源電圧である。

【0020】

図3(A)と図3(B)には、画素回路の例を示している。いずれの画素回路が用いられてもよい。図3(A)の回路から説明する。第1電圧(ここではアノード電圧)PVDDが与えられた第1の電源ラインには、駆動トランジスタTRのソースが接続されている。駆動トランジスタTRのゲートとソース間には、容量C1が接続されている。駆動トランジスタTRのドレインは、スイッチSW1を介して信号線SIGに接続されている。駆動トランジスタTRのゲートとドレイン間には、スイッチSW2が接続されている。駆動トランジスタTR、スイッチSW1,SW2は薄膜トランジスタで構成されている。スイッチSW1,SW2のゲートは、画素選択を行う走査線に接続されており、ここには、対応する画素選択ゲート信号SG1-SGnが供給される。

【0021】

駆動トランジスタTRのドレインは、薄膜トランジスタで構成されるスイッチSW3のソースに接続される。このスイッチSW3のドレインは、有機EL素子である表示素子OELD1の一方の電極(ここではアノード)に接続されている。スイッチSW3のゲートは、点灯オンオフゲート信号BG1-BGnのいずれか1つが与えられている走査線に接続されている。

【0022】

画素選択ゲート信号によりスイッチSW1、SW2がオンしたときに、信号線に流れる信号電流に応じて、容量C1に駆動トランジスタTRのソース−ドレイン間電流に対応する信号電圧が供給される。スイッチSW1、SW2がオフすると、この信号電圧が容量C1に保持され、次いでスイッチSW3がオンすると、容量C1に蓄積されている信号電圧に見合う電流が駆動トランジスタTR、スイッチSW3を介して、表示素子OELD1に流れる。発光量は、表示素子OELD1に流れる電流にほぼ比例する。スイッチSW3は、点灯オンオフゲート信号により制御されている。

【0023】

図3(B)の回路は、スイッチSW1のソースが信号線に接続され、ドレインが直接トランジスタTRのゲートに接続されている。スイッチSW1がオンしたときに、容量C1に信号電圧が供給される。スイッチSW1がオフすると信号電圧が容量C1に保持され、次いでスイッチSW3がオンすると、容量C1に蓄積されている信号電圧に見合う電流が駆動トランジスタTR、スイッチSW3を介して、表示素子OELD1に流れる。発光量は、表示素子OELD1に流れる電流にほぼ比例する。

【0024】

図4(A−F)には、上記の装置の電源投入時の動作を示している。図4(A)は、電源電圧VSSを基準にして、装置内で用いられる各種の電源電圧を示している。VGH1、VGH2、PVDD、VDD1、VDD2、VGL1、VGL2、PVSSは、図示していないが電源回路で作成されている。図4(B)、図4(C)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300で用いられる出力イネーブル信号OEV1とOEV2の出力の変化を示している。また、図4(D)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるクロックCKV1、CKV2の出力の変化を示している。図4(E)、図4(F)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるスタートパルスSTV1、STV2の出力の様子を示している。

【0025】

時点t1で電源がオンされると、出力イネーブル信号OEV1とOEV2はローレベルに固定される。クロックCKV1、CKV2、スタートパルスSTV1、STV2は、通常動作状態になる。次に、各種電源電圧が安定した時点t2から一定時間が経過すると、時点t3で出力イネーブル信号OEV1が通常動作状態に移行する。そして1垂直期間(1V)後に出力イネーブル信号OEV2が通常動作状態に移行する。

【0026】

つまり、電源投入時には、まず表示部100の全体の全画素回路に対して信号電圧(例えば黒レベルあるいは表示信号)が書き込まれた後に、はじめて、点灯オンとなり、全画面の表示が得られるようになっている。

【0027】

図5(A−Z)には、上記のように電源が投入されたときの装置各部の信号変化の様子を示している。図示している期間は、垂直ブランキング期間(VBLK)の時間的に前後する付近である。図5(A)には、垂直同期信号を示している。図5(B)には、対応する水平ライン(LINE1〜LINEN+4)を示している。図5(C)、図5(D)は、第2と第1の出力イネーブル信号OEV2とOEV1を示している。出力イネーブル信号OEV1が通常動作を開始して1垂直期間経過した後、出力イネーブル信号OEV2がスタートしている。

【0028】

第1の出力イネーブル信号OEV1により、図5(H)〜(K)の画素選択ゲート信号SG1〜SG4、図5(L)〜(P)の画素選択ゲート信号SGn〜SGn+4が出力される。

【0029】

第2の出力イネーブル信号OEV2がスタートした時点t4から、図5(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図5(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4、が順次得られる。図5(Z)のVGH2は、点灯オンオフドライバ部300のレベルシフタにおける高電位側の電源電圧である。

【0030】

ここで発明者は、点灯オンオフゲート信号出力制御回路302からシフトレジスタの出力を許可するために出力イネーブル信号OEV2がハイレベルに移行したときに、問題があることに着目した。即ち、今、図5(Q)−(Y)に示すように、点灯オンオフ信号がハイレベルであるとする。ここで垂直同期期間の終わり(時点t4)に、出力イネーブル信号OEV2がローレベルからハイレベルに切り換わるものとする(図5(C))。また、シフトレジスタ301によるシフト動作が、図5(Y)、(Q)−(T)のように進行するものとする。すると今、時点t4で、出力イネーブル信号OEV2がローレベルからハイレベルに切り換わると、点灯オンオフゲート信号BG4−BGn+3がハイレベルから一斉にローレベルとなる(図の縦長の楕円の点線で囲む部分)。これは、既に、点灯オンオフシフトレジスタ301が動作しており、殆どのシフトレジスタ出力(点灯オンオフゲート信号BG4−BGn+3に対応)がローレベル(点灯オン制御状態)に切り換わる必要があるからでる。一方では、このとき、ハイレベルを維持すべき点灯をオフすべきオンオフゲート信号が存在する(図5(Y)、(Q)−(T)の点灯オンオフ信号)。これは信号書き込みが行われる期間に相当するからである。

【0031】

しかし、これらの点灯オンオフ信号(図5(Y)、(Q)−(T))は一時的に低下する現象が見られる。この要因は、点灯オンオフゲート信号BG4−BGn+3がハイレベルから一斉にローレベルとなり、基板の電圧VGH2が一時的に低下したことに起因する。このように点灯オンオフ信号(図5(Y)、(Q)−(T))が一時的に低下すると、この点灯オンオフ信号が供給されるスイッチSW3が瞬間的に電流が流れ、表示素子が瞬間的に点灯するという問題がある。

【0032】

そこで発明者は、さらに駆動方法を考慮し、以下の対策を施すものである。即ち、図6(A−F)に示すように、装置の各部のスタートシーケンスにおいて、特に点灯オンオフシフトレジスタ301のスタートパルスSTV2を点灯オンオフゲート信号出力制御回路302の出力イネーブル信号OEV2がスタートした時点よりも遅くするのである。図6(A−F)には、その様子を示すタイミングチャートを示している。

【0033】

図6の(A)は、電源電圧VSSを基準にして、装置内で用いられる各種の電源電圧を示している。VGH1、VGH2、PVDD、VDD1、VDD2、VGL1、VGL2、PVSSは、図示していないが電源回路で作成されている。図6(B)、図6(C)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300で用いられる出力イネーブル信号OEV1とOEV2の出力の変化を示している。また、図6(D)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるシフトクロックCKV1、CKV2の出力の変化を示している。図6(E)、図6(F)は、画素選択ゲートドライバ部200と点灯オンオフドライバ部300のシフトレジスタで用いられるスタートパルスSTV1、STV2の出力の様子を示している。

【0034】

時点t1で電源がオンされると、出力イネーブル信号OEV1とOEV2はローレベルに固定される。シフトクロックCKV1、CKV2、スタートパルスSTV1は、通常動作状態になる。次に、各種電源電圧が安定した時点t2から一定時間が経過すると、時点t3で出力イネーブル信号OEV1が通常動作状態に移行する。そして1垂直期間(1V)後に出力イネーブル信号OEV2が通常動作状態に移行する(時点t4)。そして、次に、時点t5で点灯オンオフシフトレジスタ301のスタートパルスSTV2がスタートする。

【0035】

つまり、電源投入時には、まず表示部100の全画素回路に対して信号電圧が書き込まれた後に、はじめて、点灯オンとなり、全画面の表示が得られるようになっている。

【0036】

図7(A−Z)には、上記のような動作シーケンスを持つ装置各部の信号変化の様子を示している。図示している期間は、垂直ブランキング期間(VBLK)の時間的に前後する付近である。同一の図7(A)には、垂直同期信号を示している。図7(B)には、水平ライン(LINE1〜LINEN+4)を示している。図7(C)、図7(D)は、第1と第2の出力イネーブル信号OEV2とOEV1を示している。出力イネーブル信号OEV1が通常動作を開始して1垂直期間経過した後、出力イネーブル信号OEV2がスタートしている。

【0037】

第1の出力イネーブル信号OEV1により、図7(H)〜(K)の画素選択ゲート信号SG1〜SG4、図7(L)〜(P)の画素選択ゲート信号SGn〜SGn+4が出力される。

【0038】

第2の出力イネーブル信号OEV2がスタートした時点t4から、一定時間が経過した後の時点t5以降に、図7(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図7(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4、が順次得られる。これは、図7の(G)に示すように、例え出力イネーブル信号OEV2がスタートしたとしても、シフトレジスタ301の出力がローレベルに固定されており、時点t5で初めてシフト動作が開始されるからである。図7(Z)のVGH2は、点灯オンオフドライバ部300のレベルシフタにおける高電位側の電源電圧である。

【0039】

このような動作シーケンスにすると、点灯オンオフドライバ部300のレベルシフタにおける高電位側の電源電圧の変動もない。また図5で示した点灯オンオフゲート信号のような電位変動がない。この結果、画素点灯オンオフを決めるスイッチSW3が一時的に不要な導通状態となることが防止され、画質の品位を維持することが可能となる。

【0040】

この発明は、上記の実施の形態に限定されるものではない。図8(A−F)にはこの発明の他の実施の形態の動作を示すタイミングチャートを示している。図6に示したタイミングチャートと同じ部分には、同じ符号を付している。図6に示したタイミングチャートと異なる部分を説明する。この実施の形態においても、基本的には、点灯オンオフシフトレジスタ301のスタートパルスSTV2の通常動作スタート時点t6を点灯オンオフゲート信号出力制御回路302の出力イネーブル信号OEV2がスタートした時点t5よりも遅くするのである。この考え方は、図6の実施形態と変わりはない。しかし、図6の実施の形態と異なる部分は、点灯オンオフドライバ部300の例えば1垂直期間のウォーミングアップ期間(時点t3−t4)を設けこの間はシフトレレジスタ301のスタートパルスを正常動作させるのである。次の再開時の不安定動作が防止される。しかしこのウオーミングアップ期間(1垂直期間)は、ゲート信号出力制御回路302の出力イネーブル信号OEV2がローレベルに固定されているので、点灯オンオフゲート信号が出力することはない。点灯オンオフゲート信号が出力するのは時点t6以降ということになる。

【0041】

この発明は、上記の実施の形態に限定されるものではない。図9(A―Z)にはこの発明の他の実施の形態の動作を示すタイミングチャートを示している。図9(A―Z)において図7(A−Z)と異なる部分は、図9(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図9(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4のデューティーが異なる点である。ここでは、点灯オンオフゲート信号のデューティーを例えば1垂直期間の1/4のデューティーにする。例えば、1垂直期間の内、4番目の水平期間に対応する期間を間引きするのである。この様子を示したのが、図9(Q)〜(T)の点灯オンオフゲート信号BG1〜BG4、図9(U)〜(Y)の点灯オンオフゲート信号BGn〜BGn+4である。このためには、シフトレジスタ301に与えるスタートパルスSTV2を4水平周期毎に与えるとよい。

【0042】

このようなシーケンスで起動した場合の動作は以下のようになる。即ち、スタートパルスSTV2が、図4で説明したように電源投入と同時にスタートしたとする。そして、図4のように時点t4で出力イネーブルゲート信号OEV2がハイレベルになったとする。すると、当然、点灯オンオフゲート信号の出力ラインのうち多くはハイレベルを維持すべきライン(点灯オフを維持するため)と、反転すべきライン(点灯スタートのため)とが存在する。図4に示した例であると、点灯スタートするライン(点灯オンオフゲート信号が出力されるライン)が多いために、基板電圧までの変動し、これが、点灯オフすべきラインまでに影響あたえた。しかし本実施の形態によると、この影響は、図4、図5の例に比べて、1/4以下に低減する。

【0043】

本実施の形態では、点灯オンオフゲート信号のデューティーを1垂直期間の1/4のデューティーにしているからである。このことにより、時点t4で多くのライン(点灯オンオフゲート信号が出力されるライン)が一斉にローレベルに低下するのであるが、その本数は、図4、図5の例に比べて、1/4以下に低減している。よって、基板に対して電位変動を与える影響が低減し、これにともない、レベルシフタ303の出力レベルも変動を受け難くなるからである。上記の実施の形態では、点灯オンオフゲート信号のデューティーを1垂直期間の1/4のデューティーとしたが、これに限定されるものではない。1垂直期間の数分の1のデューティーであればよい。

【0044】

上記のように点灯オンオフゲート信号のデューティーを変化させる技術は、発光期間を制御して、輝度を調整する場合にも利用可能である。したがって、輝度調整機能と、電源投入時の画質劣化防止機能とを兼用させることが可能である。

【0045】

なお、この発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてもよい。

【図面の簡単な説明】

【0046】

【図1】本発明が適用されたアクティブマトリックス型表示装置の概略を示す図。

【図2】本発明に係る装置の画素選択ゲートドライバ部200と点灯オンオフドライバ部300の具体的構成例を示す図。

【図3】図1の画素回路の具体的構成例を示す図。

【図4】図1、図2の装置の電源投入時の全体の動作例を説明するために示したタイミングチャート。

【図5】図4のタイミングで動作したとき、図1、図2の装置のさらに各部の回路の動作例を説明するために示したタイミングチャート。

【図6】図1、図2の装置の電源投入時の全体の他の動作例を説明するために示したタイミングチャート。

【図7】図6のタイミングで動作したとき、図1、図2の装置のさらに各部の回路の動作例を説明するために示したタイミングチャート。

【図8】図1、図2の装置の電源投入時の全体のさらにまた他の動作例を説明するために示したタイミングチャート。

【図9】図1、図2の装置の電源投入時のまた他の動作例を説明するために示したタイミングチャート。

【符号の説明】

【0047】

100…表示部、200…が素選択ゲートドライバ部200、300…点灯オンオフドライバ部、201…画素選択シフトレジスタ、202…画素選択ゲート信号出力制御回路、203…画素選択ゲート信号レベルシフタ、301…点灯オンオフシフトレジスタ、302…点灯オンオフゲート信号出力制御回路、303…点灯オンオフゲート信号レベルシフタ。

【特許請求の範囲】

【請求項1】

基板上にマトリックス状に配列された複数の画素回路と、前記複数の画素回路の容量に対して信号を書き込むために、画素回路の行毎にシフトした選択を行ない、信号書き込み期間を設定する画素選択ゲート信号を選択した行のラインに与える画素選択ゲートドライバと、前記複数の画素回路の表示素子の発光期間を設定するために、前記画素回路の行毎にシフトした選択を行ない、点灯オンオフゲート信号を選択した行のラインに与える点灯オンオフドライバとを有し、

前記点灯オンオフドライバは、スタートパルスでシフト動作を開始する点灯オンオフシフトレジスタと、出力イネーブル信号が与えられることにより前記点灯オンオフシフトレジスタの出力を導出する点灯オンオフゲート信号出力制御回路と、この点灯オンオフゲート信号出力制御回路の出力のレベルを調整して前記行のラインに与えるレベルシフタとからなり、

前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされた後に、前記点灯オンオフシフトレジスタをスタートさせることを特徴とするアクティブマトリックス型表示装置の駆動方法。

【請求項2】

前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされたときよりも1垂直期間前には、前記画素選択ゲートドライバの画素選択ゲート信号の出力イネーブル信号(OEV1)がスタートしていることを特徴とする請求項1記載のアクティブマトリックス型表示装置の駆動方法。

【請求項3】

前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号が一定レベルに固定されている間に、前記点灯オンオフシフトレジスタが1垂直期間はウオーミングアップ動作するように前記点灯オンオフシフトレジスタをスタートさせ次に停止させるとともに、

この後、前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされた後に、前記点灯オンオフシフトレジスタをスタートさせることを特徴とする請求項1記載のアクティブマトリックス型表示装置の駆動方法。

【請求項4】

前記点灯オンオフシフトレジスタが1垂直期間ウオーミングアップ動作を開始したときは、前記画素選択ゲートドライバの画素選択ゲート信号の出力イネーブル信号(OEV1)がスタートし、

前記点灯オンオフシフトレジスタが1垂直期間ウオーミングアップ動作して停止した後、1垂直期間経過して、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされていることを特徴とする請求項3記載のアクティブマトリックス型表示装置の駆動方法。

【請求項5】

前記複数の画素回路と、前記画素選択ゲートドライバと、点灯オンオフドライバの各電源電圧が安定した後に、前記画素選択ゲートドライバの画素選択ゲート信号の出力イネーブル信号(OEV1)がスタートすることを特徴とする請求項2又は4のいずれかに記載のアクティブマトリックス型表示装置の駆動方法。

【請求項6】

基板上にマトリックス状に配列された複数の画素回路と、前記複数の画素回路の容量に対して信号を書き込むために、画素回路の行毎にシフトした選択を行ない、信号書き込み期間を設定する画素選択ゲート信号を選択した行のラインに与える画素選択ゲートドライバと、前記複数の画素回路の表示素子の発光期間を設定するために、前記画素回路の行毎にシフトした選択を行ない、点灯オンオフゲート信号を選択した行のラインに与える点灯オンオフドライバとを有し、

前記点灯オンオフドライバは、スタートパルスでシフト動作を開始する点灯オンオフシフトレジスタと、出力イネーブル信号が与えられることにより前記点灯オンオフシフトレジスタの出力を導出する点灯オンオフゲート信号出力制御回路と、この点灯オンオフゲート信号出力制御回路の出力のレベルを調整して前記行のラインに与えるレベルシフタとからなり、

前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号が少なくともスタートするときは、

前記点灯オンオフシフトレジスタの前記スタートパルスは、各行のラインに与える点灯オンオフゲート信号のデューティーが1垂直期間の数分の1となるように設定されていることを特徴とするアクティブマトリックス型表示装置の駆動方法。

【請求項7】

前記各行のラインに与える点灯オンオフゲート信号のデューティーが1垂直期間の数分の1となるように設定する方法が、表示装置の通常動作時の輝度調整に採用されることを特徴とする請求項6記載のアクティブマトリックス型表示装置の駆動方法。

【請求項1】

基板上にマトリックス状に配列された複数の画素回路と、前記複数の画素回路の容量に対して信号を書き込むために、画素回路の行毎にシフトした選択を行ない、信号書き込み期間を設定する画素選択ゲート信号を選択した行のラインに与える画素選択ゲートドライバと、前記複数の画素回路の表示素子の発光期間を設定するために、前記画素回路の行毎にシフトした選択を行ない、点灯オンオフゲート信号を選択した行のラインに与える点灯オンオフドライバとを有し、

前記点灯オンオフドライバは、スタートパルスでシフト動作を開始する点灯オンオフシフトレジスタと、出力イネーブル信号が与えられることにより前記点灯オンオフシフトレジスタの出力を導出する点灯オンオフゲート信号出力制御回路と、この点灯オンオフゲート信号出力制御回路の出力のレベルを調整して前記行のラインに与えるレベルシフタとからなり、

前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされた後に、前記点灯オンオフシフトレジスタをスタートさせることを特徴とするアクティブマトリックス型表示装置の駆動方法。

【請求項2】

前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされたときよりも1垂直期間前には、前記画素選択ゲートドライバの画素選択ゲート信号の出力イネーブル信号(OEV1)がスタートしていることを特徴とする請求項1記載のアクティブマトリックス型表示装置の駆動方法。

【請求項3】

前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号が一定レベルに固定されている間に、前記点灯オンオフシフトレジスタが1垂直期間はウオーミングアップ動作するように前記点灯オンオフシフトレジスタをスタートさせ次に停止させるとともに、

この後、前記点灯オンオフシフトレジスタの前記スタートパルスは、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされた後に、前記点灯オンオフシフトレジスタをスタートさせることを特徴とする請求項1記載のアクティブマトリックス型表示装置の駆動方法。

【請求項4】

前記点灯オンオフシフトレジスタが1垂直期間ウオーミングアップ動作を開始したときは、前記画素選択ゲートドライバの画素選択ゲート信号の出力イネーブル信号(OEV1)がスタートし、

前記点灯オンオフシフトレジスタが1垂直期間ウオーミングアップ動作して停止した後、1垂直期間経過して、前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号がスタートされていることを特徴とする請求項3記載のアクティブマトリックス型表示装置の駆動方法。

【請求項5】

前記複数の画素回路と、前記画素選択ゲートドライバと、点灯オンオフドライバの各電源電圧が安定した後に、前記画素選択ゲートドライバの画素選択ゲート信号の出力イネーブル信号(OEV1)がスタートすることを特徴とする請求項2又は4のいずれかに記載のアクティブマトリックス型表示装置の駆動方法。

【請求項6】

基板上にマトリックス状に配列された複数の画素回路と、前記複数の画素回路の容量に対して信号を書き込むために、画素回路の行毎にシフトした選択を行ない、信号書き込み期間を設定する画素選択ゲート信号を選択した行のラインに与える画素選択ゲートドライバと、前記複数の画素回路の表示素子の発光期間を設定するために、前記画素回路の行毎にシフトした選択を行ない、点灯オンオフゲート信号を選択した行のラインに与える点灯オンオフドライバとを有し、

前記点灯オンオフドライバは、スタートパルスでシフト動作を開始する点灯オンオフシフトレジスタと、出力イネーブル信号が与えられることにより前記点灯オンオフシフトレジスタの出力を導出する点灯オンオフゲート信号出力制御回路と、この点灯オンオフゲート信号出力制御回路の出力のレベルを調整して前記行のラインに与えるレベルシフタとからなり、

前記点灯オンオフゲート信号出力制御回路の出力イネーブル信号が少なくともスタートするときは、

前記点灯オンオフシフトレジスタの前記スタートパルスは、各行のラインに与える点灯オンオフゲート信号のデューティーが1垂直期間の数分の1となるように設定されていることを特徴とするアクティブマトリックス型表示装置の駆動方法。

【請求項7】

前記各行のラインに与える点灯オンオフゲート信号のデューティーが1垂直期間の数分の1となるように設定する方法が、表示装置の通常動作時の輝度調整に採用されることを特徴とする請求項6記載のアクティブマトリックス型表示装置の駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2007−114476(P2007−114476A)

【公開日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願番号】特願2005−305689(P2005−305689)

【出願日】平成17年10月20日(2005.10.20)

【出願人】(302020207)東芝松下ディスプレイテクノロジー株式会社 (2,170)

【Fターム(参考)】

【公開日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願日】平成17年10月20日(2005.10.20)

【出願人】(302020207)東芝松下ディスプレイテクノロジー株式会社 (2,170)

【Fターム(参考)】

[ Back to top ]