アクティブ・マトリクス型表示装置

【課題】液晶表示装置または有機EL表示装置の画素TFTとしてアモルファスシリコンよりも電界効果移動度が大きい、アモルファスの金属酸化物系半導体或いは有機半導体を用いた場合の過剰充電効果の増大に起因する、フリッカーレベルの増大や画面輝度の均一性低下による表示品位の低下を抑制する。

【解決手段】フリッカーや焼き付等の視認性が高い中間調表示における突き抜け電圧と、過剰充電効果の指標となる対向電極電位の面内格差との関係式を新たに導出し、これに基いて新たに導出した対向電極電位の面内格差を許容限界値以下に低減するための条件を満たすように設計する。

【解決手段】フリッカーや焼き付等の視認性が高い中間調表示における突き抜け電圧と、過剰充電効果の指標となる対向電極電位の面内格差との関係式を新たに導出し、これに基いて新たに導出した対向電極電位の面内格差を許容限界値以下に低減するための条件を満たすように設計する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、各画素にスイッチング素子としてのトランジスタを配置したアクティブ・マトリクス型表示装置において表示品位の低下を低減する技術に関し、特に、トランジスタの電界効果移動度の増大によって助長される走査信号線の時定数に起因した過剰充電効果による表示品位の低下を低減する技術に関する。

【背景技術】

【0002】

現在、アモルファスシリコン薄膜を用いた薄膜トランジスタ(以下、TFTという)が液晶表示装置等のスイッチング素子として利用され、テレビ受像機やパーソナルコンピューターのモニター等において実用化されている。しかしながらその電界効果移動度は結晶シリコンや100cm2/Vs未満のポリシリコンと比べて非常に小さく、およそ0.5〜1cm2/Vsであるため、液晶表示装置が大型高精細化や高速応答化するにつれて必要な電流量を確保するためにTFTのサイズを大きくして対応する必要がある。

【0003】

その結果としてTFTの寄生容量が増大し、寄生容量の影響を低減するために必要な補助容量が増大する。補助容量は補助容量線と画素電極との交差容量として形成されるが、補助容量線は時定数を低減するために遮光性の金属配線が好ましいため、結果的に補助容量の増大は補助容量線の面積の増加をもたらして開口率の低下を招く。即ち、大型高精細化や高速応答化に伴って開口率が確保できなくなり、アモルファスシリコンを画素のスイッチング素子として用いるには限界がある。

【0004】

その一方で、近年、金属酸化物系半導体薄膜を用いた半導体素子が注目されている。この薄膜は成膜方法やプロセス条件によって異なるが、Soluble系のもので3cm2/Vs以上、スッパッタリング法によって成膜したもので10cm2/Vs以上の電界効果移動度を示し、今後の研究によって更なる高移動度化が期待される。また、低温での成膜や可視光に対して透明な膜を形成できること等の特徴を有しており、プラスチック基板やフィルムなどの透明性基板上にフレキシブルで透明なTFTを形成することが可能である(特許文献1)

【0005】

また、TFTの活性層に用いる酸化物半導体膜として、In、Ga及びZnを含む酸化物から構成される半絶縁性の透明なアモルファス薄膜が知られており、これをチャネル層に用いるとともに、電気伝導度の大きなInGaZnO3(ZnO)4の層にAu膜を積層したものをソース・ドレイン電極として用いたトップゲート型TFTの構造が開示されており、さらに、アモルファスInGaZnO4のTFTはアモルファスシリコン薄膜トランジスタに比べて格段に大きな電界効果移動度を有することが開示されている(特許文献2)。

【0006】

そして、このような優れた特性を備えるTFTを、液晶表示装置だけではなく、他の表示装置にも利用できるようにすべく、現在活発な研究開発が行われている。更には、高価な真空装置を製造設備として必要としない有機TFTの開発も盛んに行われており、近年では電界効果移動度が1cm2/Vsを超えるものが報告され、表示装置への適用を目指した研究開発が精力的に行われている。特許文献3は、走査方向の前段の走査線と絶縁膜を介して一部重畳して配置される画素電極の間で補助容量を形成したCsオンゲート・タイプのアレイ基板において、電荷の再分配と走査線の時定数により生ずるフリッカーを低減する技術を開示する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−150900号公報

【特許文献2】特開2006−165529号公報

【特許文献3】特開2003−177725号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

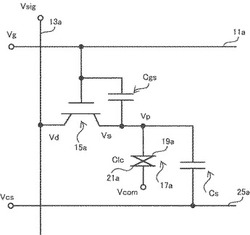

図1は液晶表示装置10のアレイ基板の一部に対応する概略の等価回路図であり、走査信号線11a、11b・・・11nと表示信号線13a、13b・・・13mで囲まれた複数の画素領域がマトリクス状に配置されている。走査信号線と表示信号線はそれぞれ抵抗を有しており、互いの交差領域には容量が形成される。このため、各配線の端部に設けた給電電極に印加した信号電位(Vg、Vsig)は抵抗と容量で決まる時定数によって遅延して歪ながら伝搬する。ここで、時定数は1-1/e≒0.632、即ち配線の給電電極に印加される電位の変化量に対して、その63.2%の電位変化に要する時間である。

【0009】

図2は図1に示した画素領域の概略の等価回路図であり、TFT15aのゲート電極は走査信号線11aに、ドレイン電極は表示信号線13aに、ソース電極は画素電極19aに、それぞれ接続されている。画素電極19aは走査信号線11aと略並行に配置された補助容量線25aと絶縁膜を介して交差しており、交差部が補助容量Csとなる。補助容量線25aも抵抗を有しており、表示信号線13aとの交差部において容量を形成している。

【0010】

ここで、補助容量線25aは抵抗を低減するために遮光性金属で形成する必要があるため、その存在が開口率を低下させる。開口率の低減を抑制するために補助容量の構成には様々な工夫がなされており、たとえば画素電極19aと電気的に接続した電極と補助容量線25aの交差領域に補助容量を形成したり、或いは補助容量線25aを配置せずに画素電極19aの延在部と上段または下段画素の走査信号線との交差領域に補助容量を形成したりすることができる。

【0011】

また、TFT15aのゲート電極とソース電極の間にはゲート・ソース間の寄生容量Cgsが形成されている。このような配線や画素を同一の絶縁性基板上に配置して構成した第一の基板と、絶縁性の基板よりなる第二の基板との間に液晶層17aを挟持することで液晶表示装置10が構成される。画素電極19aと液晶層17aを挟んで液晶容量Clcを構成する対向電極21aは第一の基板上、或いは第二の基板上に配置される。

【0012】

図3は図2の等価回路において、画素電極電位Vpが対向電極電位Vcomより高い正極性書き込みにより負荷容量Cloadを充電する際のゲート電位Vgl、Vgh、表示信号線電位Vsig、画素電極電位Vp及び対向電極電位Vcomを示すタイミングチャートである。図3(A)は走査信号線11aの給電電極に近い画素(Left)、図3(B)は走査信号線11aの給電電極から遠い画素(Right)についてのものである。

【0013】

図3において走査信号線11aの給電電極に、走査信号線11aの選択期間のみTFT15aをON状態にするゲート電位Vghを、非選択期間にはTFT15aをOFF状態にするゲート電位Vglをそれぞれ印加するパルス状の走査信号線電位Vgを給電する。走査信号線11aの給電電極に印加する走査信号線電位VgをOFF状態のゲート電位VglからON状態のゲート電位Vghに切り替えると、時定数τgの影響で給電電極から離れるほど走査信号線11aの電位がOFF状態のゲート電位VglからON状態のゲート電位Vghへ変位するのに時間を要するため、TFT15aがOFF状態からON状態へ遷移するのに要する時間が長くなり、選択期間内で負荷容量Cloadを充電する時間が短くなる。

【0014】

ここで、負荷容量Cloadは次式で与えられる。

Cload=Clc+Cs+Cgs+Cother

ここにCotherは画素電極19aとその周囲の各配線との間に形成されるカップリング容量の総和である。このため液晶表示装置10を設計する上では、給電電極から最も遠い画素の充電が選択期間内に完了するようにTFTのサイズを設定する必要がある。図3(A)、(B)のいずれにおいても選択期間が終了する前に充電が完了すると、画素電極19aの電位Vp、即ちソース電極電位Vsは、表示信号線13aの電位つまりドレイン電極電位Vdとほぼ等しくなって、TFT15aから負荷容量Cloadへ向かう電流が流れないので画素電極電位Vpの変化は停止する。この結果、選択期間終了時点では同一の走査信号線に接続された各画素の画素電極電位Vpは略等しくなる。

【0015】

選択期間が終了すると走査信号線11aの給電電極に印加される走査信号線電位VgはON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglに切り替わり、接続された各TFT15aはON状態からOFF状態に向けて導通状態が遷移を始める。ON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglへの電位変化も同様に時定数τgの影響を受けるため、給電電極から離れるにしたがって時間を要する。即ち、走査信号線11aに印加する走査信号が矩形パルスであった場合、給電電極近傍に配置されたTFT15aは走査信号が瞬時にON状態の電位VghからOFF状態の電位Vglに低下してTFT15aはOFF状態となり、この走査信号線電位Vgの電位変化量ΔVgは寄生容量Cgsを介して画素電極電位Vpを低下させる。

【0016】

このときの画素電極電位Vpの低下量ΔVpはΔVg=Vgh−Vglとしたときに次式で表される。

ΔVp=(Cgs/Cload)ΔVg ・・・(1)

画素電極電位低下量ΔVpは寄生容量Cgsを介したカップリング効果による画素電極電位Vpの低下量、或いはゲート電極電位がON状態の電位VghからOFF状態の電位Vglに変化する際に負荷容量Cloadに蓄えられた電荷の総量を保持しながら寄生容量Cgsの印加電圧の極性変化に伴う電荷再分配によって生じた画素電極電位Vpの低下量とみることもできる。ここで述べた、画素電極電位Vpが選択期間終了時の電位からOFF状態のTFT15aに対応する電位へ低下する現象を突き抜けと呼び、そのときの画素電極電位Vpの低下量ΔVpを突き抜け電圧ΔVpと呼ぶ。

【0017】

選択期間の終了時点ではVd≒Vsであったためソース・ドレイン間電圧VdsはVds≒0となって表示信号線13aから画素電極19aに向かって電流は流れなかったが、この画素電極電位Vpの低下によってVds=ΔVpとなり、ゲート・ソース間電圧Vgsに応じた電流が表示信号線13aから画素電極19aに向かって流れることになる。走査信号線11aの給電電極近傍では瞬時にゲート電極電位がON状態の電位VghからOFF状態の電位Vglに低下してTFT15aがOFF状態となるため、Vds=ΔVpとなってもTFT15aにはゲート電極電位がOFF状態のゲート電位Vglのときにドレイン・ソース間に流れる電流Ioff程度の微小な電流しか流れず、これによる画素電極電位Vpの変化は無視できる。

【0018】

しかし、TFT15aが走査信号線11aの給電電極から離れるにつれてON状態の電位VghからOFF状態の電位Vglへの電位低下に時間を要するためTFT15aは瞬時にOFF状態にならず、TFT15aがOFF状態になる前の期間にソース・ドレイン間電圧Vdsに応じた電流が表示信号線13aから画素電極19aに向かって流れる。即ち選択期間が終了した後にも負荷容量Cloadへの充電が継続され、突き抜け電圧ΔVpが低減する。突き抜けによる画素電極電位Vpの低下と、充電による画素電極電位Vpの上昇という二つの現象が合わさった結果、実効的な突き抜け電圧である実効突き抜け電圧ΔVpが低下することになる。

【0019】

例えば画面全体を正極性の同一電位に充電する場合、TFT15aがOFF状態になったときの画素電極電位Vpは、走査信号線11aの給電電極から離れるにつれて実効的な突き抜け電圧ΔVpが減少するために画素電極電位Vpが上昇する。この結果、対向電極電位Vcomと画素電極電位Vpの差である液晶層印加電圧は、走査信号線11aの給電電極から離れるほど増大する。負極性の書き込みの場合、画素電極電位Vp即ちソース電極電位Vsが正極性書き込みの場合よりも低いためゲート・ソース間電圧Vgsが大きくなり、選択期間終了後に継続される負荷容量への充電量も大きくなる。

【0020】

このため負極性書き込みにおける実効突き抜け電圧は正極性書き込みの場合よりも小さくなる。今、正極性書き込みにおける表示信号線電位と実効突き抜け電圧をそれぞれVsig+とΔVp+、負極性書き込みにおける表示信号線電位と実効突き抜け電圧をそれぞれVsig-とΔVp-、TFT15aがOFF状態における正極性と負極性それぞれの画素電極電位をVp+とVp-とおくと、Vp+とVp-はそれぞれ次式で表される。

Vp+=(Vsig+)−(ΔVp+)

Vp-=(Vsig-)−(ΔVp-)

【0021】

また、実効的に液晶層に印加される電圧は、正極性と負極性における液晶層印加電圧の平均値に略一致すると見なすことができる。そこで、正極性と負極性の平均の液晶層印加電圧をVavgとおくとVavgは次式で表される。

Vavg=[{(Vp+)−Vcom}+{Vcom−(Vp-)}]/2

={(Vsig+)−(Vsig-)}/2+{(ΔVp-)−(ΔVp+)}/2

これより、走査信号線の給電電極に近い画素では選択期間終了後に負荷容量への充電が継続されないためΔVp-=ΔVp+であり、平均の液晶層印加電圧Vavg={(Vsig+)−(Vsig-)}/2となる。走査信号線の給電電極から遠い画素では、過剰充電効果によってΔVp-<ΔVp+となるため、平均の液晶層印加電圧は走査信号線の給電電極に近い画素よりも低下する。従って、TFT15aが走査信号線11aの給電電極から離れるほど、液晶層17aに印加される平均の電圧、即ち実効印加電圧は所定の印加電圧よりも減少することになる。

【0022】

選択期間終了後にTFT15aがOFF状態となるまでの期間を過剰充電期間、過剰充電期間にTFT15aから画素電極へ流れ込む電流を過剰充電電流、過剰充電電流による負荷容量Cloadへの充電を過剰充電、過剰充電によって生じる現象を総じて過剰充電効果と呼ぶことにする。

【0023】

上述のように液晶表示装置では過剰充電効果によって画素電極電位Vpが所定の電位からシフトすることになり、そのシフト量は走査信号線11aの給電電極から離れるほど増大する。この結果、様々な表示不良や表示品位の低下をもたらす。例えば画面全体が同一階調を表示する場合、本来なら画面全体の液晶層印加電圧は等しくなっているが、過剰充電効果によって走査信号線の給電電極側から終端側へ向かって液晶層印加電圧が減少するため、輝度傾斜と呼ばれるなだらかな輝度分布が生じる。しかし、過剰充電を許容範囲内に抑制することができる場合、輝度傾斜は許容範囲内に低減されて使用上の問題にはならない。

【0024】

過剰充電効果として生じる現象には輝度傾斜以外に様々なものがある。その中で特に視認性が高く顕著に現れる現象として、最適対向電極電位Vcom,optの面内分布に起因するフリッカーが挙げられる。以下で、図面を参照しながら、過剰充電効果によって生じる最適対向電極電位Vcom,optの面内分布に起因するフリッカーの発生メカニズムについて説明する。

【0025】

液晶表示装置において、TFT15aの負荷容量Cloadの一部を成す液晶容量Clcは、画素電極19aと対向電極21a及びこれらの電極に挟まれた液晶層17aより構成されており、両電極間の電界によって液晶層内の液晶分子の配向を制御することによって液晶層17aを透過する光の強度を制御する。対向電極21aと画素電極19aとの間に生じる電界によって液晶分子の配向を制御するため、画素毎に両電極の電位を独立に制御せずに、どちらか一方の電極電位が他の画素と同一になるように外部から給電し、他方の電極電位のみを画素毎に独立に制御することが可能である。

【0026】

この場合、画素構造が単純化するため開口率や歩留まりの点で有利となる。このため、一般的な液晶表示装置においては対向電極を他の画素と一体化した構造にして電位を外部から給電している。具体的に述べると対向電極は、TNモードやVAモードの液晶表示装置では対向基板全体に配置した巨大なベタ電極構造とし、IPSモードでは走査信号線方向に配列した各画素と一体化した構造とすることが一般に行われている。また、一部のIPSモードでは、同一基板上に画素電極と対向電極をそれぞれ画素毎に独立して制御する構造も提案されている。この構造は液晶層印加電圧の面内均一性を向上できる点で有利ではあるが、画素構造が煩雑となるため開口率や歩留まりの低下を招き易い。

【0027】

以上のように対向電極電位Vcomが同一の走査信号線に接続された複数のTFTに渡って同一の場合において、画素電極電位Vpが表示画面内で不均一になると、液晶層17aの印加電圧も不均一となる。この結果、不均一な液晶層印加電圧の分布に応じて輝度分布も不均一になり、表示品位を低下させる。従って、画素電極電位Vpの面内均一性を向上させることは重要である。

【0028】

液晶分子は直流電圧によって電気分解するため交流電圧によって駆動する必要があり、液晶層に印加する電圧の極性を常に反転させる駆動を行う。このため、例えば画面全体が同一階調の表示を行う場合、TFT15aがOFF状態のときの正極性画素電極電位をVp+とし、負極性画素電極電位をVp-とすると、対向電極21aの電位を正極性画素電極電位Vp+と負極性画素電極電位Vp-の平均値に設定したときに両極性の液晶層印加電圧が等しくなる。

【0029】

この時の対向電極電位Vcomを最適対向電極電位Vcom,optと呼び、次式で表す。

Vcom,opt={(Vp+)+(Vp-)}/2

対向電極電位Vcomが最適対向電極電位Vcom,optからシフトした場合、正極性と負極性の液晶層印加電圧が異なるため各極性での液晶分子の配向も異なる。即ち、液晶分子の配向が時間的に変動するため、透過光強度が時間的に一定とはならずに振動し、この透過光強度の振動がフリッカーとして視認されることになる。或いはまた、両極性の印加電圧が異なる状態が継続した場合、両極性の印加電圧の差が、実効的に直流電圧が印加されたものとして作用し、液晶層中の不純物イオンが画素電極表面などにトラップされる現象を誘発する。トラップされた不純物イオンが多くなると、トラップされた不純物イオンが形成する電界に対して液晶分子が応答するようになり、焼き付きとして視認されることになる。

【0030】

図4(A)は、走査信号線方向に並んだ異なるn点とf点におけるそれぞれの最適対向電極電位Vcom,opt(n)、Vcom,opt(f)から対向電極電位Vcomのシフトに対するフリッカー率の関係を模式的に示したものである。ここでフリッカー率とは、測定ポイントにおける全透過光強度に占める30Hzの光強度の割合である。30Hzの光は人間がフリッカーとして最も感知し易い周波数である。図4(B)は、走査信号線の給電電極側から反対側までの画素の位置において画素電極電位Vpと対向電極電位Vcomが過剰充電効果によって変化する様子を模式的に示した図である。

【0031】

図4(A)においてn点に対応する実線は走査信号線の給電電極に近い領域を示し、f点に対応する破線は給電電極から遠い領域を示している。それぞれのポイントにおけるフリッカー率はそれぞれのポイントにおける対向電極電位Vcomに対して最小値を有し、そこから対向電極電位Vcomが増えても減ってフリッカー率は増大する。フリッカー率が最小となるときの対向電極電位Vcomが当該ポイントにおける最適対向電極電位Vcom,optであり、最適対向電極電位Vcom,optが印加されているポイントにおいてそれぞれ、対向電極電位Vcomと画素電極電位Vpの差である正極性と負極性の液晶層印加電圧は等しくなっている。

【0032】

前述のように過剰充電効果によって正極性と負極性の液晶層印加電圧において、共に実効突き抜け電圧が低下するため、図4(B)に示すように正極性と負極性の画素電極電位Vpは共に走査信号線の給電電極から離れるにつれて上昇し、最適対向電極電位Vcom,optも走査信号線の給電電極から離れるほど上昇する。このため対向電極電位Vcomを一定の値にしたときに、図4(A)に示すようにあるポイントの対向電極電位Vcomは最適対向電極電位Vcom,optとなっても、他のポイントでは最適対向電極電位Vcom,optからシフトしているためフリッカー率が大きくなる。

【0033】

従って、画面全体としてのフリッカーを低減するためには図4(B)に示すようにn点とf点の両ポイントにおける最適対向電極電位Vcom,opt(n)、Vcom,opt(f)の中間に存在するc点に対向電極電位Vcomを設定することになるが、この場合の対向電極電位Vcomはn点とf点のどちらのポイントにとっても最適対向電極電位Vcom,optではないためフリッカーを完全に解消することはできない。このため、解消しきれずに生じるフリッカーのレベルを許容限界以内に抑制する必要がある。

【0034】

フリッカーは正極性と負極性における液晶の配向の相違に起因しているため、最適対向電極電位Vcom,optからのズレに対するフリッカー率は粘性や誘電率異方性などの液晶の物性や、液晶層の電界強度に影響する液晶層の厚さなどの応答速度に関するパラメータに依存することになる。しかし実際には各パネルメーカの液晶表示装置は高速応答化や低電圧駆動化などといった目指す特性が同じであるため、結果的に表示モードや駆動方法などの基本的な仕様が同じなら液晶材料の相違に対してこれらのパラメータの差は小さくなっている。

【0035】

即ち、最適対向電極電位Vcom,optからのズレに対するフリッカー率の変化の割合は、表示モードや駆動方法が同じなら液晶種別によらず略一定となる。このため、上述の解消しきれないフリッカーの視認性と以下に述べる最適対向電極電位Vcom,optの面内格差である最適対向電極電位差δVcom,optは強い相関性を有することになる。図4(B)に示すように、対向電極電位Vcomの最適対向電極電位Vcom,optからのズレは、n点とf点で最も大きくなり、画素の位置が中央に近付くに伴って小さくなる。従って、走査信号線の給電電極に最も近い画素と最も遠い画素における最適対向電極電位Vcom,optの差に相当する最適対向電極電位差δVcom,optを過剰充電効果の指標とすることができる。

【0036】

そこで、最適対向電極電位差δVcom,optを次式で定義する。

δVcom,opt=Vcom,opt(far)-Vcom,opt(near)

ここで、Vcom,opt(near)は走査信号線の給電電極に最も近い画素における最適対向電極電位を表し、Vcom,opt(far)は最も遠い画素における最適対向電極電位を表す。

【0037】

上述のように過剰充電効果は、液晶層印加電圧の面内不均一性に起因した表示品位の低下を招く。このため、過剰充電効果を抑制する必要があり、様々な方法が提案されている。その一つとして、図3に示すように表示信号線電位Vsigの変化時刻を走査信号線電位VgがON状態のゲート電位VghからOFF状態のゲート電位Vglに切り替わる時刻より遅らせる方法があり、多くの液晶表示装置において実用化されている。例えば特許文献3では、走査信号線の電位が変化する時刻と表示信号線の電位が変化する時刻の設定法についての実施例が示されている。

【0038】

即ち、当該走査信号線11aに接続されたTFT15aがOFF状態になる前に表示信号線13aの電位が次段走査信号線11bに接続された負荷容量の充電に向けて変化した場合、過剰充電期間におけるTFTのドレイン電極電位Vdが当該画素に対する電位から次段画素に対する電位に変化することになる。この結果、当該画素の画素電極電位が所定の値から大きくシフトすることになる。これを抑制するため、当該走査信号線に接続されたTFTが完全にOFF状態になるのを待って表示信号線の電位を変化させる必要がある。この待ち時間として、概ね走査信号線の時定数程度に設定することが一般に行われている。

【0039】

この手法は過剰充電期間におけるTFT動作点の設定によって、過剰充電効果を抑制するものである。過剰充電は過剰充電電流の流れ易さ、即ち半導体層の電界効果移動度に依存するため、電界効果移動度が小さいアモルファスシリコンに対しては上記手法のみ適用しても過剰充電の低減効果は十分であったと考えられ、電界効果移動度が増大した場合には上記手法のみでは十分な過剰充電の低減効果を得られないことが懸念される。しかし、過剰充電効果と電界効果移動度との関係についての詳しい研究結果の報告はこれまでになされていないのが実情である。

【0040】

そこで、本発明の発明者が長年に渡って液晶表示装置の開発に際して使用し、改良を続けてきたシミュレータを用いて、最適対向電極電位差δVcom,optを過剰充電効果の指標とするシミュレーションを行った。得られた結果において、過剰充電効果と電界効果移動度との関係を図5に示す。図5は、半導体層としてアモルファスシリコンを用いた26インチのFull-HD、フレーム周波数120Hz、TNモードの液晶表示装置について、電界効果移動度が0〜50cm2/Vsの範囲で求めたものである。

【0041】

一般的に最適対向電極電位差δVcom,optの許容限界は0.2V程度であるのに対して、図5では電界効果移動度の増大に対して最適対向電極電位差δVcom,optが0.2Vを大きく超えている。即ち、電界効果移動度の増大に対して最適対向電極電位差δVcom,optを低減するためには、設計や製造プロセスにおける対策の導入が不可欠であることを示唆している。

【0042】

ところで、液晶表示装置は誘電率異方性を有する液晶分子の配向状態を電界によって制御するものであるため、液晶層17aへの印加電圧に対して液晶容量Clcが異なり、突き抜け電圧ΔVpも液晶層印加電圧によって異なる。また、フリッカーや焼き付きなどの視認性も同様に液晶層印加電圧によって異なる。液晶層印加電圧の変化に対する輝度変化は、最大輝度の50%の輝度となる50%液晶層印加電圧V50付近で最も大きくなるため、過剰充電によって生じる液晶層印加電圧の面内不均一性に起因した過剰充電効果の諸現象の視認性もこの付近の液晶層印加電圧において高まる。

【0043】

このため、過剰充電効果の解析を50%液晶層印加電圧V50で行い、50%液晶層印加電圧V50における突き抜け電圧ΔVpを特に50%突き抜け電圧ΔVp,v50と表すことにする。なお本発明においては、過剰充電効果の解析を最大輝度の50%の輝度となる液晶層印加電圧に限定する必要はなく、過剰充電効果の視認性の影響によっては他の割合の液晶層印加電圧を選択することもできる。

【0044】

フリッカーの視認性が高い表示状態は、画面全体が同一の中間調表示の場合であるため、突き抜け電圧ΔVpとしては50%突き抜け電圧ΔVp,v50だけを考えることができる。しかし、焼き付きは上述のように正極性と負極性の液晶層印加電圧の差に起因し、この電圧差は実効突き抜け電圧の面内不均一性によって生じるため、過剰充電効果が微弱で無視できる場合であっても異なる階調領域が混在する表示状態では、突き抜け電圧ΔVpが階調に応じて異なることに起因して液晶層の実効印加電圧に直流電圧成分が生じる。

【0045】

このため、階調による相違、即ち液晶層印加電圧の相違に対する直流電圧成分の相違を抑制する条件として、式(1)の負荷容量Cloadが最小となる場合の最大突き抜け電圧ΔVp,maxと、最大突き抜け電圧ΔVp,maxと負荷容量Cloadが最大となる場合の最小突き抜け電圧ΔVp,minとの差である最大突き抜け電圧差d(ΔVp)max=ΔVp,max-ΔVp,minを基準値以下に設定する方法が従来より用いられている。

【0046】

また、液晶容量Clcも印加電圧に応じて異なり、液晶容量Clcの最大値と最小値をそれぞれClc,max、Clc,minとし、50%液晶層印加電圧V50に対する液晶容量Clcを50%液晶容量Clc,v50とすると、それぞれに対して負荷容量Cloadも最大負荷容量Cload,max、最小負荷容量Cload,min、50%負荷容量Cload,v50とおくことができる。

【0047】

ここで、最適対向電極電位差δVcom,optの解析において正極性画素電位Vp+と負極性画素電位Vp-の算出時刻を、選択期間終了時刻から選択期間の3倍の時間が経過した時刻とした。これは、後に述べる突き抜け補償駆動の場合においてもTFTが完全にOFF状態に至った直後の時刻であり、この時刻で画素電位を算出することによってTFTのOFF状態におけるリーク電流の影響を無視することができ、その結果として過剰充電効果の解析を明確に行えるからである。

【0048】

アモルファスシリコン(a-Si)に対する従来の画素設計の方法を以下で図面を参照しながら説明する。本従来例におけるデバイスモデルの概要は次の通りである。画素精細度Full-HD(走査信号線数1080本)、画素サイズ100μm×300μm、走査信号線選択期間7.55μs、ゲート絶縁膜の比誘電率と膜厚はそれぞれ7.4、3000Å、液晶動作モードはTN、最大液晶容量Clc,maxは0.365pF、最小液晶容量Clc,minは0.177pF、50%液晶容量Clc,v50は0.271pFとする。

【0049】

また、TFT形状は図6に示すアモルファスシリコンに対して一般的に用いられているU字型とし、チャネル長Lは最小加工寸法を想定して4μmとした。以上のデバイスモデル設定項目は、本明細書で述べる全ての従来の方法、及び後に述べる本発明の実施例に対して共通事項である。その他個別の設定項目及びパラメータについては、その都度示す。

【0050】

液晶表示装置の画素設計は、TFTの負荷容量Cloadに対するTFTサイズを決めること、及び画素電極の周囲に配置された走査信号線及び表示信号線と画素電極との間に形成される寄生容量を介したカップリングを抑制すること、という2つの要素から成り立つ。第3の要素として、TFTのリーク電流や液晶層中の不純物イオンに対する負荷容量Cloadの電荷保持能力設定条件に基く負荷容量設定というものがあるが、これは本発明の過剰充電とは独立したものであるため、ここでは説明を行わない。

【0051】

表示信号線と画素電極19aとのカップリングは、補助容量電極を両者の間に配置することで生じるシールド効果によって十分に低減することが可能である。但し、表示信号線と画素電極との間のカップリングを低減するために必要な補助容量の大きさはおよそ0.1pF程度以上であることが多い。

【0052】

これに対して、画素電極19aと走査信号線との間のカップリング、特に当該走査信号線11aとの間のカップリングによる画素電極電位Vpの変動は、主に画素電極19aが接続されているTFT15aのソース電極とゲート電極との交差領域に形成される寄生容量Cgsを介したものであり、上述の突き抜け電圧ΔVpとなる。即ち、カップリング容量の主体がTFTの寄生容量Cgsであるため、シールド効果を利用したカップリングの低減を行うことができず、結果として全てのカップリングの中で支配的なものとなる。

【0053】

突き抜け電圧ΔVpを低減する方法は、式(1)より寄生容量Cgsを低減するか負荷容量Cloadを増大するか、或いは走査信号線電位変化量ΔVgを低減するかの何れかである。TFT15aのチャネル幅Wとチャネル長L、及びON状態のゲート電極電位Vghは負荷容量Cloadを充電するための電流量を確保することで決まり、W/LとON状態のゲート電極電位Vghは互いに相反的な関係にある。

【0054】

しかし、ON状態のゲート電極電位Vghは走査信号線のドライバーICの出力バラツキなどの影響を強く受けるため、ON状態のゲート電極電位Vghによって電流量を微調整することは好ましくなく、必要なON状態のゲート電極電位Vghの値に対してある程度のマージンを上乗せした値に設定する必要がある。このため、一般的にはON状態のゲート電極電位Vghによって電流値をラフに決定した後、チャネル幅Wによって微調整する。W/Lを大きくするためにチャネル長Lは極力小さく設定することが望ましく、一般的にはプロセス上の最小加工寸法に設定するため、設計上は固定値となる。OFF状態のゲート電極電位VglはTFT15aの閾値電圧VthやTFT15aのリーク電流の影響を低減することで決まるプロセス・パラメータであり、設計上は固定値と見なされる。

【0055】

また、負荷容量Cloadを構成する液晶容量Clcは画素サイズによって略決定するため、負荷容量Cloadの支配的なパラメータは補助容量Csとなる。従って、突き抜け電圧ΔVpの値を決める重要なパラメータはチャネル幅Wの関数である寄生容量Cgsと、補助容量Csの関数である負荷容量Cloadとなる。このため、チャネル幅Wと負荷容量Cloadは突き抜け電圧ΔVpに関する制約条件を満たしながら、かつ互いに値を修正しながら収束を図るように決定される。

【0056】

[非補償駆動]

従来の画素設計の方法として、TFT15aの島状半導体にアモルファスシリコンを用いた場合について以下で図面を参照しながら説明する。この場合の個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=1.5V、ON状態のゲート電極電位Vgh=20V、OFF状態のゲート電極電位Vgl=-6V、電界効果移動度μeff=0.5cm2/Vsである。

【0057】

図6はアモルファスシリコンのTFTとして広く用いられているTFT形状で、合せズレによる寄生容量Cgsの変動率が小さいという特徴を有する。この場合、チャネル幅Wは、島状半導体57上のソース電極51のエッヂの長さとして定義することができる。また、チャネル形状がU字型をしているためチャネル幅Wには最小値Wmin-uが存在する。これは、U字の直線部が短くなって円弧部のみになった場合に合せズレによる寄生容量Cgsの変動率が急増するためである。U字型の電極をドレイン電極53、内側の直線的な電極をソース電極51とすると、チャネル長L=4μm、ソース電極幅=4μmの場合のチャネル幅Wの最小値Wmin-uは14.3μmである。

【0058】

図6においてゲート電極55の端と島状半導体57の端の距離は3σ相当の合せズレによって互いに近づいた場合に一致するように設定し、半導体層はゲート電極層に対してアライメントするため島状半導体57とゲート電極55は直接合せの関係にあるので、ゲート電極55の端と島状半導体57の端の距離は3σ相当の直接合せ精度δdとしている。同様に島状半導体57の端とドレイン電極53の先端間距離は3σ相当の合せズレによって互いに近づいた場合に一致するように設定し、半導体層とソース・ドレイン電極層は共にゲート電極層に対してアライメントするため島状半導体57とドレイン電極53は互いに間接合せの関係にあるので、島状半導体57の端とドレイン電極53の端との距離は3σ相当の間接合せ精度δiとしている。

【0059】

本明細書では、従来例の説明及び本発明の実施例において3σ相当の直接合せ精度δdと間接合せ精度δiをそれぞれ3μmと4μmに共通事項として設定している。この値は後に述べるように液晶事業創成期におけるプロセス精度の値である。しかし、合せ精度が向上した今日でも、ゲート電極端と半導体層端間距離及び半導体層端とドレイン電極の先端間距離において合わせズレに対するマージンを大きく確保すべきであるため、それぞれの距離を液晶事業の創成期と同じく3μmと4μmに設定することが多く、その場合には4σや5σ相当の合わせズレに対するマージンを有することになる。

【0060】

図6において点線59で囲んだ領域に形成される寄生容量Cgs領域は、島状半導体57上のソース電極51とドレイン電極53で挟まれたチャネル領域の中央からソース電極51寄りの領域と、ソース電極51とゲート電極55の交差領域との和として定義することができる。また、合せズレによる寄生容量Cgsの変動は、島状半導体57上の領域の変動はないものとみなし、ソース電極51とゲート電極55の交差面積のみ変動するとみなすことができる。

【0061】

これにより、寄生容量Cgsはチャネル幅W、チャネル長L、TFT形状と合せ精度、および単位面積容量で決まる。ソース電極51の幅Wsはプロセス上の最小加工寸法とすることができるため、寄生容量Cgsの設計パラメータはチャネル幅Wのみであり、他はプロセス・パラメータであるため設計上は固定値となる。

【0062】

以上の説明をまとめると、液晶表示装置の設計において、チャネル幅Wに対して充電可能な最大負荷容量Cload,maxの存在領域と、チャネル幅Wに対する突き抜け電圧ΔVpを基準値以下に低減するために最低限必要な最大負荷容量Cload,maxの存在領域との共通集合領域が画素の候補領域となる。この候補領域の中で補助容量Csが最小となるときに開口率が最大となり、最適な画素となる。

【0063】

特に従来のアモルファスシリコンの場合には、突き抜け電圧ΔVpとして負荷容量Cloadが最小となる場合の最大突き抜け電圧ΔVp,maxと、最大突き抜け電圧ΔVp,maxと負荷容量Cloadが最大となる場合の最小突き抜け電圧ΔVp,minとの差である最大突き抜け電圧差d(ΔVp)maxを基準値以下に低減することが従来より制約条件とされてきた。この様子を図7に示す。ここでは、突き抜け電圧ΔVpに対する制約条件として、従来より用いられている最大突き抜け電圧ΔVp,maxと最大突き抜け電圧差d(ΔVp)maxを取り上げ、それぞれの上限値を1.7V、0.35Vとしている。

【0064】

図7において、W-Cloadのグラフはチャネル幅Wに対して充電可能な最大の容量、即ちW-Cload特性を表し、チャネル幅Wに対する最大負荷容量Cload,maxはこのW-Cloadのグラフより下側に設定されることになる。W-ΔVp,maxのグラフは、チャネル幅Wに対して最大突き抜け電圧ΔVp,maxが上限値となる場合の最大負荷容量Cload,maxを表しており、最大突き抜け電圧ΔVp,maxを上限値以下にするためには、式(1)より最大負荷容量Cload,maxをこのグラフよりも上側に設定する必要がある。W-d(ΔVp)maxのグラフは、チャネル幅Wに対して最大突き抜け電圧差d(ΔVp)maxが上限値となる場合の最大負荷容量Cload,maxを表しており、最大突き抜け電圧差d(ΔVp)maxを上限値以下にするためには、最大負荷容量Cload,maxをこのグラフよりも上側に設定する必要がある。

【0065】

即ち、それぞれを基準値以下に低減するため最大負荷容量Cload,maxは、W-Cloadのグラフよりも下側で、かつW-d(ΔVp)maxのグラフとW-ΔVp,maxのグラフのいずれよりも上側に設定することになる。図7の場合、最大突き抜け電圧差W-d(ΔVp)maxのグラフがW-ΔVp,maxのグラフよりも上方に位置するため、W-Cloadのグラフより下側の領域で且つW-d(ΔVp)maxのグラフより上側の領域が画素の候補領域となる。他に条件が無い場合、この画素候補領域の中で開口率が最大、即ち遮光性の電極よりなる補助容量が最小となる点が最適な画素となる。従って、W-CloadのグラフとW-d(ΔVp)maxのグラフは共にWに対して単調増加していることから、両グラフの交点Xが最適な画素となる。

【0066】

図8は図7におけるW-CloadのグラフとW-d(ΔVp)maxのグラフとの交点Xの状態について、50%突き抜け電圧ΔVp,v50が設計値通りに出来上がった設計値である設計50%突き抜け電圧ΔVp,v50typ、及び寄生容量Cgsが合せズレなどによって変動した場合に50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typに対して±0.5V変動した場合の最適対向電極電位差δVcom,optをシミュレーションした結果である。

【0067】

図7においてW-d(ΔVp)maxのグラフとW-Cloadのグラフとの交点Xの状態はW=37.3μm、Cload,max=0.802pFであり、換算するとΔVp,v50=1.29Vとなる。最適対向電極電位差δVcom,optの上限値をξ+=0.2V、下限値をξ-=−0.2Vとすると、図8においてξ+とξ-となる50%突き抜け電圧ΔVp,v50はそれぞれ1.13Vと1.71Vである。これより、許容される50%突き抜け電圧ΔVp,v50の設計値からの変動量は、ΔVp,v50が増大する場合と減少する場合それぞれδ(ΔVp,v50)+=1.71−1.29=0.42V、δ(ΔVp,v50)-=1.29−1.13=0.16Vとなる。

【0068】

50%突き抜け電圧ΔVp,v50の変動方向に偏りがないならδ(ΔVp,v50)+とδ(ΔVp,v50)-の内小さい方が律速するので、この場合δ(ΔVp,v50)-=0.16Vに対して画素を決定することになる。突き抜け電圧ΔVpの変動が全て寄生容量Cgsの変動によるものであった場合、その変動の許容限界δCgsは式(1)より4.49fFに相当する。この寄生容量Cgsの変動が合せズレのみによるものであった場合、その合せズレ量の許容限界は単位面積容量を用いて算出すると5.14μmに相当することになる。

【0069】

ここで、寄生容量Cgsの変動面積はソース電極51の幅Wsで直接合せズレ量δdと間接合わせズレ量δiとの合成長さ分の変動に相当し、これらの合せズレの発生頻度が正規分布する場合、この合成合わせズレ量δdiはSQRT(δd^2+δi^2)と表される。ここにSQRT()は括弧内の平方根を表し、A^2はAのべき乗を表す。液晶事業の創世記の合せ精度は3σでδd=3μm、δi=4μmであり、この場合のδdiは5μmであった。近年の合せ精度は向上しており3σでδd=2μm、δi=3μmとすると、δdiが5.14μmとなるズレは4.3σに相当する。

【0070】

即ち、液晶事業創世記のプロセス精度であっても寄生容量Cgsのフォトレジストの合わせズレ量が5.14μmを超えるのは3σ以上の場合であり、今日のプロセス精度では4.3σに相当するため、歩留まりへの影響は小さく無視することができる。従って、電界効果移動度が0.5cm2/Vsのa-Siの場合、最適対向電極電位差δVcom,optを考慮しないで設計しても今日のプロセス精度が提供する合わせズレ量で製造すれば自動的に最適対向電極電位差δVcom,optが許容限度内に収まることになる。

【0071】

これに対して電界効果移動度が10cm2/Vsである透明アモルファス酸化物半導体(TAOS)について従来の設計方法を用いた場合を以下で図面を参照しながら説明する。ここでの個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=0V、ON状態のゲート電極電位Vgh=15V、OFF状態のゲート電極電位Vgl=-2V、電界効果移動度μeff=10cm2/Vsとしている。

【0072】

図9はTAOSにおけるチャネル幅Wと充電可能な最大容量の関係(W-Cload特性)と、チャネル幅Wと最大突き抜け電圧ΔVp,maxとの関係(W-ΔVp,max特性)及び最大突き抜け電圧差d(ΔVp)maxとの関係(W-d(ΔVp)max特性)をシミュレーションして求めた結果を示している。図9において、アモルファスシリコンの場合と同一の最大突き抜け電圧ΔVp,maxと最大突き抜け電圧差d(ΔVp)maxに関する制約条件を与えたときに、ΔVp,max≦1.7V及びd(ΔVp)max≦0.35Vを満たす場合の最大負荷容量Cload,maxに対しては、W-Cloadのグラフよりチャネル幅WをU字型TFTの最小値Wmin-uに設定しても書込みが可能である。他に制約条件が与えられていない場合、最適な画素の候補はW-ΔVp,maxのグラフよりも上にあるW-d(ΔVp)maxのグラフ上で且つチャネル幅Wの最小値Wmin-uの点に存在する。この状態の画素はW=14.3μm、Cload,max=0.477pFであり、換算するとΔVp,v50=0.67Vとなる。

【0073】

図10は図9より求めた最適な画素候補について、50%突き抜け電圧ΔVp,v50が設計値通りに出来上がった設計値である設計50%突き抜け電圧ΔVp,v50typ、及び寄生容量Cgsが合せズレなどによって変動した場合に50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typに対して±0.5V変動した場合の最適対向電極電位差δVcom,optをシミュレーションした結果である。

【0074】

図10において、ξ+=0.2V、ξ-=−0.2Vとすると、50%突き抜け電圧ΔVp,v50が許容変動限界となるのは50%突き抜け電圧ΔVp,v50が減少した場合で、δ(ΔVp,v50)-=0.0236Vである。これに対する寄生容量Cgsの許容変動量の限界値は0.531fFに相当する。この寄生容量Cgsの変動が全てフォトレジストの合わせズレによるものであった場合のズレ量許容値は0.608μmに相当する。

【0075】

このズレ量の許容限界は、今日の合せ精度で3σ相当の直接合せズレ量δdと間接合わせズレ量δiがそれぞれ2μmと3μmの場合であっても僅か0.506σにしか相当せず、量産ラインにおいて合わせ精度を0.506σ以下に管理することは現実的には不可能である。従って、電界効果移動度が10cm2/VsであるTAOSにおいて、最適対向電極電位差δVcom,optを許容限界値以下に抑えた液晶表示装置の設計を行うためには、最大突き抜け電圧ΔVp,maxと最大突き抜け電圧差d(ΔVp)maxを基準値以下に抑制するという条件以外に新たな制約条件を導入する必要がある。

【0076】

尚、以上の説明では最適対向電極電位差δVcom,optの許容限界値をξ+=0.2V、ξ-=-0.2Vとしたが、この値は実用されている値の一例である。実際には最適対向電極電位差δVcom,optの許容限界値は製品仕様で決まる値であり、製品毎に異なるものである。しかし、電界効果移動度が大きくなってきた場合には、最適対向電極電位差δVcom,optの許容限界値が例示した値より大きくなっても、現在のプロセス精度で製造可能なズレ量の範囲で最適対向電極電位差δVcom,optを許容値に納めた液晶表示装置を設計することが困難なことには変わりがない。

【0077】

[補償駆動]

既に述べたように、過剰充電電流は突き抜け電圧ΔVpがTFTのソース・ドレイン間電圧Vdsとして作用することで流れるため、過剰充電効果は突き抜け電圧ΔVpに強く依存する。このため、過剰充電効果を低減するためには突き抜け電圧ΔVpの低減を図ることが有効である。その手段の一つとして、突き抜け補償駆動が挙げられる。本来の突き抜け補償駆動は、駆動によって突き抜け電圧ΔVpを低減することによって補助容量Csを低減し、開口率を増大させるものである。

【0078】

突き抜け補償駆動には多様な方法が提案され実用化されているが、基本的には補助容量Csを介したカップリングを利用して突き抜けによる画素電極電位Vpの低下を補償するもので、実効的な突き抜け電圧ΔVpを十分に低減するという点では全て同じである。即ち、寄生容量Cgsを介した走査信号線電位Vgの変化による画素電極電位Vpの変動量と、補助容量Csを介した補助容量電極の電位変化による画素電極電位Vpの変動量が等しい場合に画素電極電位Vpの変動が相殺される、というのが突き抜け補償駆動の原理である。

【0079】

そこで、突き抜け補償条件として次式が成り立つ。

(Cgs/Cload)ΔVg=(Cs/Cload)ΔVcs・・・(2)

ここで、ΔVcsは補助容量電極の電位変化量である。この関係式は、補助容量Csが画素電極の延在部と前段画素の走査信号線との交差領域に形成されるCs on Gate構造であった場合でも成り立つ。この場合、走査信号線電位VgはTFTがON状態のゲート電極電位Vghから、OFF状態のゲート電極電位Vglに低下する前にVglより低い第3の電位Vgcに低下する。即ち、当該走査信号線の電位がON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglに切り替わる時、前段走査信号線の電位はVgcからVglへと切り替わる。このとき、ΔVcs=Vgl-Vgcとなる。

【0080】

突き抜け補償駆動に対する従来の例としてアモルファスシリコンにCs on Gateを用いた場合について、以下で図面を参照しながら説明する。この場合の個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=1.5V、ON状態のゲート電極電位Vgh=20V、OFF状態のゲート電極電位Vgl=-6V、電界効果移動度μeff=0.5cm2/Vsである。チャネル幅Wはアモルファスシリコンに突き抜け非補償駆動を適用した場合と同一の37.3μmとする。

【0081】

突き抜け補償駆動はTFTがON状態の期間における負荷容量Cloadへの充電には影響が小さいため、ここでは無視しても差し支えない。従って、この場合のW-Cload特性とW-ΔVp,max特性及びW-d(ΔVp)max特性は図7と同一である。

【0082】

図11は、アモルファスシリコンに対してCs on Gateによる突き抜け補償駆動をした場合の従来の方法における50%突き抜け電圧ΔVp,v50と最適対向電極電位差δVcom,optの関係をシミュレーションで求めた結果である。Lは、50%突き抜け電圧ΔVp,v50の設計値である設計50%突き抜け電圧ΔVp,v50typに対する最適対向電極電位差δVcom,optである設計最適対向電極電位差δVcom,typの関係を示すグラフ、M(0V)〜M(2V)は、0V〜2Vの各設計50%突き抜け電圧ΔVp,v50typにおいて50%突き抜け電圧ΔVp,v50の変動に対する最適対向電極電位差δVcom,optの変動の関係を示すグラフである。

【0083】

設計50%突き抜け電圧ΔVp,v50typの増加に対してグラフLで示した設計最適対向電極電位差δVcom,typが緩やかに増大して約2Vで横軸と交わる。このとき50%突き抜け電圧ΔVp,v50が増大する場合と減少する場合のそれぞれの許容変動量δ(ΔVp,v50)+とδ(ΔVp,v50)-は等しく、許容変動量が最大となる。具体的には、ΔVp,v50typ=2.12Vでδ(ΔVp,v50)+=δ(ΔVp,v50)-=0.150Vとなり、この状態においてΔVp,v50の変動が全てCgsの変動によるものであった場合の許容Cgs変動量δCgsは2.49fFとなる。このCgs変動が全て合わせズレによるものであった場合の許容合わせズレ量は、3σ相当の直接合せ精度δdと間接の合わせ精度δiがそれぞれ2μmと3μmの場合で2.37σに相当する。この場合の最大負荷容量Cload,maxは0.526pFであり、突き抜け非補償駆動の場合と比べて補助容量Csが0.276pF低減でき、この分だけ開口率が増大する。

【0084】

ここでは詳しく述べないが、実際の設計に際して突き抜け補償駆動の場合、突き抜け電圧の設計は制約条件を課さずに行われ、式(1)に基づいて設計50%突き抜け電圧ΔVp,v50typを求めるとおよそ2V〜2.5Vになっていることが多い。製造工程において合わせ精度を2.37σ或いはそれ以下で管理することは不可能ではないが困難を伴うため、実際には製造設備の改造による合わせ精度の向上などによって対応している。即ち、このような労力を費やしてでも、突き抜け補償駆動による突き抜け電圧の制約条件緩和によってもたらされる補助容量低減による開口率の増大が必要とされている。一度このような対応が実施された製造工程においては、従来のアモルファスシリコンにおける突き抜け補償駆動の場合、突き抜け電圧に関する制約条件を考慮しなくても、結果的に最適対向電極電位差δVcom,optが許容範囲内に収まることになる。

【0085】

また、突き抜け補償駆動を行っているにも関わらず突き抜けが影響する過剰充電が生じている理由は、式(2)の突き抜け補償条件が、突き抜け補償過程が終了した時点での電位を一致させるものであるのに対して、実際には走査信号線電位と補償駆動による画素電極電位との間における電位の時間変化率が一致しないために生じた電位差によって過剰充電電流が流れることに起因する。

【0086】

即ち、走査信号線と補助容量線の時定数の設定法が全く異なり、特に容量の設定に関しては一般に両者の絶縁膜構成が異なるため単位面積容量が異なり、また走査信号線の場合は時定数の値のみが重要であるのに対して補助容量線では時定数に加えてカップリング低減などの機能を有するために容量の値を厳密な計算に基づいて決定される。こうしたことから、一般に走査信号線と補助容量線の時定数は大きく異なるため、特に走査信号線の選択期間終了直後の過剰充電期間初期においては、走査信号線の電位変化による画素電極電位変化量と補助容量線の電位変化による画素電極電位変化量が互いに相殺されない。このために生じた画素電極電位の変化量がソース・ドレイン間電圧Vdsとなって過剰充電電流が流れるからである。

【0087】

或いはCs on Gate構造の場合には、画素電極が当該走査信号線から受ける電位変化の過程は2段階に分かれており、第一段階は選択期間終了直後に走査信号線の電位がON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglより低い第3の電位Vgcに切り替わる変化であり、第二段階は第3の電位VgcからOFF状態のゲート電極電位Vglへ切り替わる変化である。これに対して前段走査信号線から受ける電位変化の過程は、第3の電位VgcからOFF状態のゲート電極電位Vglへ切り替わる変化の一回だけである。このため、当該走査信号線から受ける画素電極電位変化量と前段走査信号線から受ける画素電極電位変化量が互いに相殺されない期間が存在し、この期間に過剰充電電流が流れるためである。

【0088】

以上を要約すれば、電界効果移動度が0.5cm2/Vs程度の従来のアモルファスシリコンに対する液晶表示装置の設計においては、過剰充電効果の影響が小さいため過剰充電効果に起因するフリッカーの指標となる最適対向電極電位差δVcom,optに関する制約条件を与えなくても、自然に最適対向電極電位差δVcom,optが許容範囲内に収まっていた。しかし、電界効果移動度が大きくなると過剰充電効果も増大するため、電界効果移動度が10cm2/VsのTAOSの場合には最適対向電極電位差δVcom,optを許容範囲内に低減するには、設計に際して新たな制約条件の導入が必要である。

【0089】

本発明は以上の点に鑑みてなされたものであり、本発明の目的は、表示品位の高いアクティブ・マトリクス型表示装置を提供することにある。さらに本発明の目的は、電界効果移動度が1cm2/Vsから70cm2/Vsの範囲にあるトランジスタを有するアクティブ・マトリクス型表示装置の表示品位を高めることにある。さらに本発明の目的は、そのようなアクティブ・マトリクス型表示装置を製造する方法を提供することにある。

【課題を解決するための手段】

【0090】

本発明は、電界効果移動度の増大に伴って増大する過剰充電効果に起因したフリッカーまたは画面輝度の均一性低下の指標に走査信号線方向における対向電極電位Vcomの面内格差である対向電極電位差δVcomを採用して、フリッカーまたは画面輝度の均一性低下を許容範囲内に収めるための新たな設計上の制約条件を提供し、高品位のアクティブ・マトリクス型表示装置を実現する。

【0091】

本発明は、電界効果移動度が1cm2/Vsを超えると影響が顕著になる過剰充電効果に起因した表示品位の低下を抑制するための手法を提供するものである。過剰充電効果による表示品位として影響を受けるのは輝度傾斜、焼き付き等の最適対向電極電位Vcom,optの面内分布に関するものである。特に、視認性の高いフリッカーに着目し、最適対向電極電位Vcom,optの走査線方向の面内格差である最適対向電極電位差δVcom,optを指標としてフリッカーまたは画面輝度の均一性低下を抑制する新たな設計条件を提供する。さらに本発明は、半導体層の電界効果移動度が1cm2/Vs以上のときにも、ON状態のゲート電極電位Vgh、OFF状態のゲート電極電位Vgl、負荷容量Cload、およびゲート・ソース間容量Cgsなどのプロセスの制御パラメータの値を決定して、最適対向電極電位差δVcom,optを許容変動範囲に収めることを可能にする式を提供する。

【0092】

具体的には、最適対向電極電位差δVcom,optが最大輝度に対してn%の輝度となる中間調におけるn%突き抜け電圧ΔVp,vnの一次関数として表せること、及び製造プロセスの影響によって寄生容量Cgsなどが変動することによるn%突き抜け電圧ΔVp,vnの変動に対する最適対向電極電位差δVcom,optの変動をn%突き抜け電圧ΔVp,vnの関数として定式化する。更には、プロセスレベルに対して最適対向電極電位差δVcom,optの許容限界値ξを超えないためにn%突き抜け電圧ΔVp,vnの設計値が満たすべき条件を、先に定式化した式を元に導出するものである。

【0093】

図24は走査信号線時定数τg=2.5μs、閾値電圧Vth=0V、ON状態のゲート電極電位Vgh=15V、OFF状態のゲート電極電位Vgl=-6V、設計50%突き抜け電圧ΔVp,v50typ=1.5Vの場合について、定式化した式及びシミュレーションによって設計最適対向電極電位差δVcom,typを電界効果移動度μeffが0〜100cm2/Vsの範囲で求めた結果を比較して示した図である。シミュレーション結果では電界効果移動度μeffの増大に対して設計最適対向電極電位差δVcomtypは単調増加しているが、定式化した式による算出値は電界効果移動度μeff>50cm2/Vsの領域において設計最適対向電極電位差δVcom,typが減少している。過剰充電は過剰充電電流に起因した現象であり、電流の流れ易さである電界効果移動度が大きいほど過剰充電電流も大きくなるため、定式化した式より算出した値の減少は適用限界を超えていることを示唆している。

【0094】

また、電界効果移動度μeffがおよそ2cm2/Vs以下でグラフの傾きが非常に大きな領域において、シミュレーション結果がなだらかなカーブを描いておらず歪みが生じており、シミュレーションにとってクリティカルな領域となっている。この原因は電界効果移動度μeffの変化に対して設計最適対向電極電位差δVcom,typが敏感に変化するため、数値解析における収束性が低下したことに起因していると考えられる。これに対して定式化した式による算出値はなだらかなカーブを描いているが、これは定式化した式の導出に際してシミュレーション結果に対して内挿式を用いてFittingしているため、シミュレーションの収束性に起因したグラフ形状の歪みが平均化されたことによるものであり、電界効果移動度μeffがおよそ2cm2/Vs以下の領域おいては定式化した式による算出値の方がシミュレーション結果よりも信憑性が高いと考えられる。

【0095】

図25は定式化した式より算出した値からシミュレーション値を引いた値Δを示した図である。定式化した式より算出した値とシミュレーション値とが略一致と見なすための両者の差の許容限界を20mVと仮定すると、図25より電界効果移動度μeffがおよそ1.5〜70cm2/Vsの領域において許容限界以下となっている。ここで、誤差20mVというのは、表示信号線の時定数による画面の上端と下端の輝度差を液晶層印加電圧の差に換算した場合の許容限界として用いられることがある値であり、図25は隣接画素の印加電圧差を比較するものではなくシミュレーション値と定式化した式より算出した値との比較であるため、優位差無しとする限界値として20mVを用いた。

【0096】

また、電界効果移動度μeffがおよそ2cm2/Vs以下の領域に対するシミュレーションにおける収束性の低下を考慮すると、実際には略一致と見なせる領域の下限は1.5cm2/Vsよりも低く、少なくとも1cm2/Vs付近までは略一致と見なせるものと考えられる。

【0097】

以上より、定式化した式が適用できる範囲は電界効果移動度がおよそ1cm2/Vs〜70cm2/Vsの範囲であり、好ましくは1.5cm2/Vs〜50cm2/Vsの範囲である。また、nの範囲としておよそ15〜70、即ち15%から70%の輝度となる中間調表示において適用することができる。更には、nを50にすると一般的に電圧変化に対する透過率変化の割合が最大になるため、最適対向電極電位差δVcom,optを50%突き抜け電圧ΔVp,v50の一次関数として表すことが望ましい。

【0098】

また、フリッカーには、表示画面の広範囲の輝度があたかも点滅するかのように変化するものだけでなく、半径が数mm程度の微小な領域の輝度が軽微に振動するものが表示画面の広範囲にわたってランダムに分布するものもある。隣り合う微小フリッカー領域の輝度差は、微小領域である上に輝度が安定しないため実測は困難であるが、主観評価では256階調の1〜3階調分程度、或いはそれ以上に相当する。この場合、いわゆるフリッカーとして認識されない場合が多いが、微小な輝度ムラ状態が表示画面の広範囲に分布するため、表示パターンの輪郭がボヤけ、全体的にモヤモヤしたような画質を招く。このモードのフリッカーを、局所モードのフリッカーと呼ぶことがある。

【0099】

この原因は、ゲート絶縁膜の軽微な膜厚分布に起因した最適対向電極電位Vcom,optの面内不均一性によるものと推測している。即ち、ゲート絶縁膜などの絶縁性薄膜の膜厚精度は一般に設定値に対して±10%以下として管理されている。しかし、膜厚を測定するのは画素領域の周囲に配置された膜厚測定パターンであるため、実際に画素領域の膜厚分布を測定している訳ではない。このため、実際には管理値より小さい数%程度の膜厚の異なる領域がランダムに画面全体に分布しているものと考えられ、局所モードのフリッカーは、この軽微な膜厚の相違が軽微な突き抜け電圧の分布を生じ、その結果として過剰充電効果の程度差が視認される現象と考えられる。

【0100】

隣り合う2つの局所モードフリッカー領域を考えた場合、互いの距離が近く非常に狭い領域であるため、それぞれの領域における合せズレ量や配線幅、液晶層の厚みなどのプロセス精度に起因する変動項目は、ゲート絶縁膜の膜厚以外全て同一とみなすことができる。即ち、両領域間の相違はゲート膜厚差に起因するTFTのゲート・ソース間寄生容量Cgsのみであると考えられる。

【0101】

この場合、両領域間の突き抜け電圧の差に対する最適対向電極電位Vcom,optの差は本発明の式(4)で表される直線Mの傾きηに略一致する。これは、ηがゲート・ソース間寄生容量Cgsの変動などに起因した50%突き抜け電圧ΔVp,v50の変動に対する最適対向電極電位差δVcom,optの変動の割合であり、合せズレによるゲート・ソース間寄生容量の変動に際したチャネル長Wの変動による過剰充電電流の変動の影響はゲート・ソース間寄生容量Cgsの変動による影響と比べて十分に小さいためである。従って、ηの絶対値が小さいほど隣り合う局所モードのフリッカーレベルの差が軽減され、表示品位の向上を図ることができる。また、非常に狭い範囲内の現象であるために両領域間でゲート・ソース間寄生容量Cgsのみ異なると見なせることから、対向電極電位を画素毎に独立して制御する場合に対しても局所モードのフリッカーをηによって評価することができる。

【0102】

図12は、50%突き抜け電圧ΔVp,v50の設計値である設計50%突き抜け電圧ΔVp,v50typと設計最適対向電極電位差δVcom,typとの関係を示す直線L、及び50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから変動した場合の最適対向電極電位差δVcom,optの変動関係を示す直線M、及び最適対向電極電位差δVcom,optの許容範囲の上限値ξ+と下限値ξ-との関係を示す概念図である。

【0103】

本発明の発明者は、直線Lが次の式(3)で表されることを見出した。

L:δVcom,typ=(α・ΔVp,v50typ+β)γ・・・(3)

ここで、直線Lの傾きが正、即ちα・γ>0であることに注意を要する。これは、突き抜け電圧ΔVpがソース・ドレイン間電圧Vdsとして作用して過剰充電電流が流れることによって過剰充電が行われることに起因している。また、α、β、γは後で説明する計算式によって求まる係数である。

【0104】

本発明の発明者は、直線Mが次の式(4)で表されることを見出した。

M:δVcom,opt=η(ΔVp,v50−ΔVp,v50typ)+δVcom,typ・・・(4)

ここで、直線Mの傾きηは、η<0であることに注意を要する。これは、50%突き抜け電圧ΔVp,v50が変動によって増大した場合、画素電極電位Vpの低下量が増大するために最適対向電極電位Vcom,optが低下することに起因している。

【0105】

次に、最適対向電極電位差δVcom,optの許容上限値と下限値をそれぞれξ+とξ-とし、ξ+及びξ-に対する50%突き抜け電圧ΔVp,v50をそれぞれΔVp,v50-とΔVp,v50+とする。最適対向電極電位差δVcom,optの上限値がξ+以下になるためには、ΔVp,v50-における最適対向電極電位差δVcom,optがξ+以下であればよいので、

η((ΔVp,v50-)−ΔVp,v50typ)+(α・ΔVp,v50typ+β)γ≦ξ+

より、

ΔVp,v50typ−(ΔVp,v50-)≦{(α・ΔVp,v50typ+β)γ−(ξ+)}/η

が得られる。

【0106】

同様に、最適対向電極電位差δVcom,optの下限値がξ-以上になるためには、ΔVp,v50+における最適対向電極電位差δVcom,optがξ-以上であればよいので、

η((ΔVp,v50+)−ΔVp,v50typ)+(α・ΔVp,v50typ+β)γ≧ξ-

より、

(ΔVp,v50+)−ΔVp,v50typ≦{(ξ-)−(α・ΔVp,v50typ+β)γ}/η

が得られる。

【0107】

これより、ΔVp,v50がΔVp,v50typから減少する方向の許容変動量δ(ΔVp,v50)-と、ΔVp,v50がΔVp,v50typから増大する方向の許容変動量δ(ΔVp,v50)+をそれぞれ

δ(ΔVp,v50)-=ΔVp,v50typ-(ΔVp,v50-)>0

δ(ΔVp,v50)+=(ΔVp,v50+)-ΔVp,v50typ>0

とすると、次の式(5)と式(6)が得られる。

δ(ΔVp,v50)-≦{(α・ΔVp,v50typ+β)γ−(ξ+)}/η・・・(5)

δ(ΔVp,v50)+≦{(ξ-)−(α・ΔVp,v50typ+β)γ}/η・・・(6)

従って、式(5)と式(6)を満たすように設計すると、過剰充電効果によるフリッカーを許容限度内に抑制することができる。

【0108】

ここで、最大輝度の50%となる液晶層印加電圧に着目した理由は、透過率-液晶層印加電圧の関係において、電圧変化に対する透過率変化の割合が最大となる領域のためである。即ち、液晶層印加電圧の変化に対する透過率が敏感に変化するため、過剰充電による液晶層印加電圧の面内不均一性に起因したフリッカーや焼き付などが視認され易いからである。しかし、近年の液晶表示装置の画面輝度の増大に伴って輝度50%でも十分に明るいため人間の目にとって視認性が低下し、輝度50%よりも暗い画面で視認性が高かまる場合がある。そこで、画面輝度を最大輝度のn%としたときに、本発明の式(3)と式(4)が成り立つnの範囲を求めた例を以下で図面参照しながら説明する。

【0109】

図22は画面輝度が最大輝度のn%となる液晶層印加電圧Vnに対するδVcom,optについて、シミュレーション結果と式(3)より得られたδVcom,opt-Vn特性を比較して示すグラフである。個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=0V、ON状態のゲート電極電位Vgh=15V、OFF状態のゲート電極電位Vgl=-2V、電界効果移動度μeff=10cm2/Vsとした。更に、表示モードを液晶層に電圧を印加しない状態で透過率100%即ち最大輝度となるノーマリーホワイトとし、輝度100%となるときの液晶の比誘電率ε100を液晶の比誘電率-印加電圧特性における最小値として3.00、ε100に対する液晶層印加電圧V100を液晶の閾値電圧とし、液晶層印加電圧最大値V0を6.5Vとし、V0のときの輝度を0%としてこのときの液晶の比誘電率ε0を6.18とした。

【0110】

透過率-液晶層印加電圧特性と液晶の比誘電率-液晶層印加電圧特性とが互いに強い相関関係にあることから、輝度n%となるときの液晶の比誘電率εnをε0とε100を元に線形補間によって求め、液晶の比誘電率-液晶層印加電圧特性よりεnに対する液晶層印加電圧Vnを求めた。また、式(3)においてΔVp,v50typを、輝度n%となる液晶層印加電圧Vnにおける突き抜け電圧の設計値ΔVp,vntypに置き換えてδVcom,optを算出し、シミュレーションにおいても同様に行った。

【0111】

図22において、50%液晶層印加電圧V50では式(3)によって求めた値とシミュレーション結果の値は一致せず約6mVの差がある。これは本発明式の有する精度を表しているが、一般的なδVcom,optの許容限界値である200mVに対して約3%のズレであり、実用上問題のないレベルであるとして略一致と見なすことができる。式(3)とシミュレーションのそれぞれより求めたδVcom,optの差として10mVまで誤差として許容すると、およそ15%液晶層印加電圧V15〜70%液晶層印加電圧V70の範囲で、即ち輝度15%〜70%の範囲で略一致と見なすことができ、この範囲において本発明の式(3)は成り立つことになる。また、この範囲を超えた領域において、式(3)の値はシミュレーション値からかけ離れている訳ではないので、精度を要求しないラフな検討に際しては0%液晶層印加電圧V0〜100%液晶層印加電圧V100の全範囲において式(3)を用いることが可能であることが分かる。

【0112】

図23は図22と同一条件にて行ったシミュレーション結果と本発明の式(4)より求めたη-Vn特性を比較して示すグラフである。式(4)において50%突き抜け電圧ΔVp,v50及び設計50%突き抜け電圧ΔVp,v50typをそれぞれn%突き抜け電圧ΔVp,vn及び設計n%突き抜け電圧ΔVp,vntypに置き換えてηを算出し、シミュレーションにおいても同様に行った。図23において、液晶層印加電圧が10%液晶層印加電圧V10〜100%液晶層印加電圧V100の領域で、即ち輝度が10%〜100%の範囲において誤差±1%の範囲内でシミュレーション結果と本発明の式(4)が一致しており、この範囲において式(4)が成り立つ。以上を踏まえて、具体的な発明内容を以下に示す。

【0113】

本発明のアクティブ・マトリクス型の液晶表示装置は、電界効果移動度が1cm2/Vs以上で且つ70cm2/Vs以下であって、最適対向電極電位差δVcom,optの許容上限値と下限値をそれぞれξ+とξ-とし、ξ+とξ-に対するn%突き抜け電圧ΔVp,vnをそれぞれΔVp,vn-とΔVp,vn+とし、設計n%突き抜け電圧をΔVp,vntypとし、n%突き抜け電圧ΔVp,vnが設計n%突き抜け電圧ΔVp,vntypから増大した場合と減少した場合の許容変動限界量をそれぞれ、δ(ΔVp,vn)+=(ΔVp,vn+)−ΔVp,vntypとδ(ΔVp,vn)-=ΔVp,vntyp-(ΔVp,vn-)とし、最適対向電極電位差δVcom,optの設計値である設計最適対向電極電位差δVcom,typを式(3)とし、

δVcom,typ=(α・ΔVp,vntyp+β)γ・・・(3)

n%突き抜け電圧ΔVp,vnの変動量に対する最適対向電極電位差δVcom,optの変動量の割合をηとし、α、β、γをそれぞれ後で説明する計算式より求まる係数としたとき、δ(ΔVp,vn)+とδ(ΔVp,vn)-がそれぞれ式(5)、式(6)を満たすように設定することを特徴とする。

δ(ΔVp,vn)+≦{(ξ-)−(α・ΔVp,vntyp+β)γ}/η・・・(5)

δ(ΔVp,vn)-≦{(α・ΔVp,vntyp+β)γ−(ξ+)}/η・・・(6)

【0114】

さらに本発明はnを15〜70の範囲とすることができる。さらに、好ましくはnを50とすることができる。nを50とし、ξ+とξ-に対する50%突き抜け電圧ΔVp,v50をそれぞれΔVp,v50-とΔVp,v50+とし、50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから増大した場合と減少した場合の許容変動限界量をそれぞれ、

δ(ΔVp,v50)+=(ΔVp,v50+)−ΔVp,v50typとδ(ΔVp,v50)-=ΔVp,v50typ-(ΔVp,v50-)とし、

最適対向電極電位差δVcom,optの設計値である設計最適対向電極電位差δVcom,typを式(3A)とし、

δVcom,typ=(α・ΔVp,v50typ+β)γ・・・(3A)

50%突き抜け電圧ΔVp,v50の変動量に対する最適対向電極電位差δVcom,optの変動量の割合をηとし、α、β、γをそれぞれ後で説明する計算式より求まる係数としたとき、δ(ΔVp,v50)+とδ(ΔVp,v50)-がそれぞれ式(5A)、式(6A)を満たすように設定することを特徴とする。

δ(ΔVp,v50)+≦{(ξ-)−(α・ΔVp,v50typ+β)γ}/η・・・(5A)

δ(ΔVp,v50)-≦{(α・ΔVp,v50typ+β)γ−(ξ+)}/η・・・(6A)

【0115】

表示装置が突き抜け非補償駆動の場合はα、β、γ、ηを次式で与えることができる。

α=A・exp(-1/(B・μeff))+0.2

A={0.58exp(-1/Vgh)-0.591}Vth+{7.924exp(-1/Vgh)-7.23}

B=Ba{exp(Bb(Vgh-14))-1}+Bc

Ba=15exp(-0.455Vth)

Bb=0.00667Vth+0.01

Bc=1.2exp(-0.35Vth)-0.47

β=C・exp(-1/(D・μeff))-0.19

C=-0.002Vth+0.337exp(-1/Vgh)-0.148

D={0.06exp(-Vgh+14)+0.00042}exp(Vth)-0.0051Vgh+0.362

γ={E・exp(-F/τg)+G・τg}νc

E={-0.00032μeff+0.01(exp(-1.17/Vth)+1)}Vgh+0.008μeff+0.722exp(-0.101Vth)

F={2.71exp(-0.0272μeff)+0.597exp(-1.37/Vth)}/Vgh+(0.0667Vth+0.3)exp(-0.268μeff)

G={-0.0479μeff+1.4exp(-1.35/Vth)+1.75}/Vgh+0.0012μeff+0.0701exp(-0.301Vth)-0.1

νc=0.620exp(0.0353Vgh)(-Vgl)^(-0.0203Vgh+0.275)

η=η0・γ0

η0=P・exp(-1/ΔVp,vntyp)+Q

P={0.115exp(-0.164Vgh)・exp(Vth)−0.00610Vgh+0.460}μeff^(-0.559)

Q=exp(-1/(μeff+Qa))+Qb

Qa=0.128Vgh−0.005exp(0.2Vth+4.70)+0.350

Qb=(0.0008Vth+0.0183)Vgh−0.0554Vth−1.88

γ0=νe・κ(τg)/κ(τg=2.5)

κ(τg)=exp(-R/τg)+S・τg+T

R=Ra1・exp(Ra2・μeff)・exp(-1/(Vgh-10))+0.5exp(-Rc2/μeff)+Rc3

Ra1=0.214exp(-1.37/Vth)+0.351

Ra2=0.153exp(-1.37/Vth)-0.216

Rc2=1.29exp(0.388Vth)

Rc3=0.544exp(0.0147Vth)-1

S={0.000376loge(μeff)-0.0000667Vth-0.00123}Vgh+Sb

Sb=(0.00237Vth+0.0345)exp(Sb2・μeff)

Sb2=0.00258exp(0.388Vth)-0.05

T=Ta1・Vgh・μeff^Ta2+Tb1・loge(μeff)+Tb2

Ta1=0.007exp(-1.60/Vth)+0.0258

Ta2=0.0223exp(0.265Vth)-0.1

Tb1=-0.0001Vth+0.0597

Tb2=0.847exp(-0.0966Vth)-3.00

νe=(-0.0242Vgh+1.17)(-Vgl)^( 0.0006Vgh^1.96)

ここで、Vth、Vgh、Vgl及びΔVp,vntypの単位は[V]、μeffの単位は[cm2/Vs]、τgの単位は[μs]である。またκ(τg)は、κがτgの関数であることを表し、「^」はべき乗記号を表す。更には、logeは自然対数を表す。

【0116】

突き抜け補償駆動の場合のα、β、ηは、次式で与えることができる。

α=A・μeff+B

A=0.00001[{4exp(-0.462Vth)-15}Vgh+20.2exp(0.0361Vth)]

B=0.0001{(4.33Vth+25.2)Vgh-203Vth+852}

β=C・loge(μeff)+D

C=0.0001(16.2Vgh-0.6Vth-108)

D=-(0.0118Vth+0.105)loge(Vgh)+0.0374Vth+0.0625

η=η0・γ0

η0=P・exp(ΔVp,vntyp)+Q

P=-Pa1・Vgh^(Pa2)・μeff^(Pb1・Vgh+Pb2)

Pa1=4exp(1.12Vth)+109

Pa2=-5exp(-1/(0.0916Vth))-2.57

Pb1=0.00007Vth+0.0096

Pb2=-0.0146Vth-0.204

Q=-{(0.0001Vth-0.0123)Vgh+0.0238Vth+1.08}μeff^Qb

Qb=(4.46Vth+43.0)Vgh^(-0.0289Vth-2.16)+0.0118Vth-0.185

γ0=νe・κ(τg)/ κ(τg=2.5)

κ(τg)=exp(-R/τg)+S・τg+T

R=Ra1・exp(Ra2・μeff)・exp(-1/(Vgh-10))+0.5exp(-Rc2/μeff)+Rc3

Ra1=0.214exp(-1.37/Vth)+0.351

Ra2=0.153exp(-1.37/Vth)-0.216

Rc2=1.29exp(0.388Vth)

Rc3=0.544exp(0.0147Vth)-1

S={0.000376loge(μeff)-0.0000667Vth-0.00123}Vgh+Sb

Sb=(0.00237Vth+0.0345)exp(Sb2・μeff)

Sb2=0.00258exp(0.388Vth)-0.05

T=Ta1・Vgh・μeff^Ta2+Tb1・loge(μeff)+Tb2

Ta1=0.007exp(-1.6/Vth)+0.0258

Ta2=0.0223exp(0.265Vth)-0.1

Tb1=-0.0001Vth+0.0597

Tb2=0.847exp(-0.0966Vth)-3.00

νe=(-0.0242Vgh+1.17)(-Vgl)^(0.0006Vgh^1.96)

ここで、VthとVgh、Vgl及びΔVp,vntypの単位は[V]、μeffの単位は[cm2/Vs]、τgの単位は[μs]である。またκ(τg)は、κがτgの関数であることを表し、「^」はべき乗記号を表す。更には、logeは自然対数を表す。

【0117】

アクティブ・マトリクス型の表示装置は液晶表示装置又は有機EL表示装置とすることができる。また、ηの絶対値は2以下にすることができる。半導体層には、アモルファスの金属酸化物又は有機物を採用することができる。有機EL表示装置の場合、一画素に2個のTFTと1個の容量よりなる2T1C型、或いは複数個のTFTと複数個の容量よりなる回路を有するが2T1C型と等価である場合の有機EL表示装置の画素は、液晶表示装置の画素と電気回路的に等価であり、上記制約条件の式(5)及び式(6)を満たすように構成することができる。本発明は、上記の設計手法を表示装置の製造方法に適用することができる。

【発明の効果】

【0118】

本発明により、表示品位の高いアクティブ・マトリクス型表示装置を提供することができた。さらに本発明により、電界効果移動度が1cm2/Vsから70cm2/Vsの範囲にあるトランジスタを有するアクティブ・マトリクス型表示装置の表示品位を高めることができた。さらに本発明により、そのようなアクティブ・マトリクス型表示装置を製造する方法を提供することができた。

【図面の簡単な説明】

【0119】

【図1】液晶表示装置の構成を示す概略等価回路図である。

【図2】液晶表示装置の画素構成を示す概略等価回路図である。

【図3】過剰充電効果の原理を示す駆動電位波形と画素電位のタイミングチャートである。

【図4】フリッカー率と最適対向電極電位Vcom,optの関係を示す概念図である。

【図5】電界効果移動度の増大に対する最適対向電極電位差δVcom,optの推移を示すシミュレーション結果である。

【図6】従来の液晶表示装置に用いられているアモルファスシリコンTFTとそのゲート・ソース間の寄生容量Cgsの領域を示す図である。

【図7】アモルファスシリコンに対する従来例における、チャネル幅Wに対する充電可能な負荷容量の関係及びチャネル幅Wに対する突き抜け電圧ΔVpを基準値以下に低減するために必要な負荷容量の関係を示すシミュレーション結果である。

【図8】アモルファスシリコンに対する従来例における、50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから変動した場合の最適対向電極電位差δVcom,optの変動を示すシミュレーション結果である。

【図9】TAOSに対する従来例における、チャネル幅Wに対する充電可能な負荷容量の関係及びチャネル幅Wに対する突き抜け電圧ΔVpを基準値以下に低減するために必要な負荷容量の関係を示すシミュレーション結果である。

【図10】TAOSに対する従来例における、50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから変動した場合の最適対向電極電位差δVcom,optの変動を示すシミュレーション結果である。

【図11】アモルファスシリコンに対してCs on Gateによる突き抜け補償駆動を行った場合の従来例における、設計50%突き抜け電圧ΔVp,v50typと設計最適対向電極電位差δVcom,typとの関係、及び50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから変動した場合の最適対向電極電位差δVcom,optの変動関係を示すシミュレーション結果である。

【図12】過剰充電効果を抑制する本発明の関係式を説明するために用いる、設計50%突き抜け電圧ΔVp,v50typと設計最適対向電極電位差δVcom,typとの関係、及び50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから変動した場合の最適対向電極電位差δVcom,optの変動関係及び最適対向電極電位差δVcom,optの許容限界値を示す概念図である。

【図13】TAOSに対して本発明の関係式に基く制約条件を適用した場合の一実施例における、設計50%突き抜け電圧ΔVp,v50typと設計最適対向電極電位差δVcom,typとの関係、及び50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから変動した場合の最適対向電極電位差δVcom,optの変動関係を示す図である。

【図14】TAOSに対して本発明の関係式に基く制約条件を適用した場合の一実施例における、50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから減少する方向にシフトした場合の許容変動量δ(ΔVp,v50)-と設計50%突き抜け電圧ΔVp,v50typとの関係を示す図である。

【図15】TAOSに対して本発明の関係式に基く制約条件を適用した場合の一実施例における、許容合わせズレ量δdiと設計50%突き抜け電圧ΔVp,v50typとの関係を示す図である。

【図16】TAOSに対してCs on Gateによる突き抜け補償駆動を行った場合に本発明の関係式に基く制約条件を適用した一実施例における、設計50%突き抜け電圧ΔVp,v50typと設計最適対向電極電位差δVcom,typとの関係、及び50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから変動した場合の最適対向電極電位差δVcom,optの変動関係を示す図である。

【図17】TAOSに対してCs on Gateによる突き抜け補償駆動を行った場合に本発明の関係式に基く制約条件を適用した一実施例における、50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから減少する方向と増加する方向にシフトした場合のそれぞれの許容変動量δ(ΔVp,v50)-及びδ(ΔVp,v50)+と設計50%突き抜け電圧ΔVp,v50typとの関係を示す図である。

【図18】TAOSに対してCs on Gateによる突き抜け補償駆動を行った場合に本発明の関係式に基く制約条件を適用した一実施例における、50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから減少する方向と増加する方向にシフトした場合に対するそれぞれの許容合わせズレ量δdi-及びδdi+と設計50%突き抜け電圧ΔVp,v50typとの関係を示す図である。

【図19】アモルファスシリコンとTAOSについてそれぞれ突き抜け補償駆動と非突き抜け補償駆動の場合について、本発明における式(4)で表される直線の傾きηと50%突き抜け電圧ΔVp,50の設計値との関係を示す図である。

【図20】基本的な有機EL表示装置の画素の概略等価回路図である。

【図21】基本的な有機EL表示装置の画素が液晶表示装置の画素と等価であることを示すための、有機EL表示装置の概略等価回路図である。

【図22】最適対向電極電位差と階調表示電圧との関係について、本発明の関係式とシミュレーションによって求めた結果を比較した図である。

【図23】各階調表示電圧における突き抜け電圧の変化量に対する最適対向電極電位差の変化量の割合を、本発明の関係式とシミュレーションによって求めた結果を比較した図である。

【図24】最適対向電極電位差と電界効果移動度との関係について、本発明の関係式とシミュレーションによって求めた結果を比較した図である。

【図25】最適対向電極電位差と電界効果移動度との関係について、本発明の関係式とシミュレーションによって求めた最適対向電極電位差の差を、各電界効果移動度に対して示した図である。

【発明を実施するための形態】

【0120】

[非補償駆動]

電界効果移動度が10cm2/VsであるTAOSで構成されたTFTに対して本発明の関係式に基づいた設計手法を適用した場合の一実施例を以下で図面を参照しながら説明する。本実施例における個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=0V、ON状態のゲート電極電位Vgh=15V、OFF状態のゲート電極電位Vgl=-2V、半導体層の電界効果移動度μeff=10cm2/Vsである。即ちこれらのパラメータは図9、図10を参照して説明したとおり、従来の設計手法では、最適対向電極電位差δVcom,optを許容限界値以下に抑えることが困難であったものであるが、本発明の手法を適用することでこれらのパラメータを採用しても液晶表示装置の設計が可能になることを以下に示す。このため、W-Cload特性とW-ΔVp,max特性及びW-d(ΔVp)max特性のグラフは図9と同一になる。

【0121】

図13は本発明の関係式を用いて求めた50%突き抜け電圧ΔVp,v50に対する最適対向電極電位差δVcom,optの関係を示すグラフである。Lは式(3)より求めたグラフで、TFTが設計通りに出来上がったときの寄生容量Cgsにおける設計50%突き抜け電圧ΔVp,v50typに対する設計最適対向電極電位差δVcom,typを表す。

【0122】

“M(0V)”〜“M(1.5V)”はそれぞれ式(4)より求めたグラフであり、設計50%突き抜け電圧ΔVp,v50typが0V〜1.5Vの場合に寄生容量Cgsが合せズレなどによって設計値から変動した場合を想定し、これによって50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから±0.5V変動した場合の最適対向電極電位差δVcom,optを表す。最適対向電極電位差δVcom,optの許容限界としてξ+=0.2V、ξ-=−0.2Vとすると、図13においてΔVp,v50>0.2Vの領域では、図12を参照すると明らかなようにδ(ΔVp,v50)-<δ(ΔVp,v50)+であり、増大する場合よりも減少する場合の方が許容される50%突き抜け電圧ΔVp,v50の変動量が小さく、設計を律速する。また、50%突き抜け電圧ΔVp,v50を低減すると補助容量Csが増大して開口率の低下を招くため、ΔVp,v50<0.2Vの領域については考えず、ΔVp,v50>0.2Vの領域のみを考えることにする。

【0123】

図12、図13を参照すると明らかなように、ΔVp,v50>0.2Vの領域では、最適対向電極電位差δVcom,optがξ+より小さくなるようなδ(ΔVp,v50)-を検討することになる。図9、図10を参照して説明したとおり、従来の設計手法で得られた画素候補はチャネル幅W=Wmin-u、最大負荷容量Cload,max=0.477pF、設計50%突き抜け電圧ΔVp,v50typ=0.67Vというものであったが、合わせ精度の管理値を実施不可能なほど小さく設定しなければならないものであったため最適な画素とはならなかった。本実施例では図13に基づいて、合わせ精度の管理値を実施可能な範囲に設定できる最適な画素を見出す手法について説明する。

【0124】

図14は、図13における設計50%突き抜け電圧ΔVp,v50typの各値に対する50%突き抜け電圧の許容変動量δ(ΔVp,v50)-を求めたグラフである。合わせ精度の管理値を実施可能な範囲に設定するためには突き抜け電圧の設計値からの変動量δ(ΔVp,v50)-を大きく設定する必要がある。即ち、図9、図10を参照して説明した従来例において設計50%突き抜け電圧ΔVp,v50typが0.67Vの場合は許容合わせズレ量が小さく0.506σ相当でしかなかったので、実施可能な許容合わせズレ量とするためには図14より、設計50%突き抜け電圧ΔVp,v50typを0.67Vよりも小さく設定することになる。このため、式(1)に示す突き抜け電圧の式より、チャネル幅W=Wmin-uに固定して50%負荷容量Cload,v50をパラメータとして設計50%突き抜け電圧ΔVp,v50typを表すことにする。チャネル幅WをWmin-uに固定するのは、チャネル幅WがWmin-uより大きい場合に負荷容量をより大きく設定するために遮光性電極よりなる補助容量が大きくなって開口率が低下するのを回避するためである。これにより、図14に示す設計50%突き抜け電圧ΔVp,v50typと突き抜け電圧の許容変動量δ(ΔVp,v50)-との関係は、50%負荷容量Cload,v50と突き抜け電圧の許容変動量δ(ΔVp,v50)-との関係に置き換えることができる。得られた50%負荷容量Cload,v50と突き抜け電圧の許容変動量δ(ΔVp,v50)-との関係は、再度式(1)を用いて、50%負荷容量Cload,v50とゲート・ソース間の寄生容量Cgsの許容変動量δCgsとの関係に置き換えることができる。得られたゲート・ソース間の寄生容量Cgsの許容変動量δCgsは、ゲート・ソース間の単位面積容量と図6を参照して説明したゲート・ソース間寄生容量Cgsの合わせズレによる変動面積から、許容合わせズレ量δdiに変換することができる。

【0125】

図15は、図14より得られた設計50%突き抜け電圧ΔVp,v50typと許容合わせズレ量δdiの関係を示したグラフである。図6に示した3σ相当の直接の合わせズレ量δdと間接の合せズレ量δiをそれぞれ2μmと3μmとすると、合成合せズレ量δdiは3.6μmである。図15より、許容合わせズレ量δdiが3.6μmとなるのは設計50%突き抜け電圧ΔVp,v50typが0.539Vのときであることが分かる。また、この状態に対する最大負荷容量Cload,maxを求めると0.570pFであって、図9よりチャネル幅WがWmin-uであっても十分に充電が可能な容量であり、且つW-ΔVp,max特性のグラフ及びW-d(ΔVp)max特性のグラフよりも上方に位置していることがわかる。即ち、設計50%突き抜け電圧ΔVp,v50typを0.539Vに設定する場合、3σ相当の合成合わせズレ量に対するマージンを有し、従来の突き抜け制約条件である最大突き抜け電圧ΔVp,max≦1.7Vと最大突き抜け電圧差d(ΔVp)max≦0.35Vを満たし、且つ設計最適対向電極電位差δVcom,typを許容限度以下に抑制するために必要な補助容量の値を最小に抑えた最適な画素となる。

【0126】

[補償駆動]

次に、電界効果移動度が10cm2/VsであるTAOSにCs on Gateによる突き抜け補償駆動を用いた場合に対して本発明の関係式に基づいた設計手法を適用した一実施例を、以下で図面を参照しながら説明する。本実施例における個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=0V、ON状態のゲート電極電位Vgh=15V、OFF状態のゲート電極電位Vgl=-2V、電界効果移動度μeff=10cm2/Vsである。即ち、突き抜け補償駆動を行わない場合の本発明の実施例で適用したものと同一である。また、突き抜け補償駆動はTFTがON状態の期間における負荷容量Cloadへの充電に対して影響は小さいため、ここでは無視しても差し支えない。従って、本実施例のW-Cload特性とW-ΔVp,max特性及びW-d(ΔVp)max特性は図9と同一である。

【0127】

図16は本発明の関係式を用いて求めた50%突き抜け電圧ΔVp,v50に対する最適対向電極電位差δVcom,optの関係を示すグラフである。Lは式(3)より求めたグラフで、設計値通りに出来上がったTFTの寄生容量Cgsにおける設計50%突き抜け電圧ΔVp,v50typに対する設計最適対向電極電位差δVcom,typを表す。“M(0V)”〜“M(3V)”はそれぞれ式(4)より求めたグラフであり、設計50%突き抜け電圧ΔVp,v50typが0V〜3Vの場合に寄生容量Cgsが合せズレなどによって設計値から変動した場合を想定し、これによって50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typから±0.5V変動した場合の最適対向電極電位差δVcom,optを表す。

【0128】

図16において、設計50%突き抜け電圧ΔVp,v50typに対する設計最適対向電極電位差δVcom,typを表す直線Lの傾きは、図14の突き抜け非補償駆動の場合と比べて小さくなっている。これは突き抜け補償駆動によって実効突き抜け電圧が低下した結果、過剰充電電流が低下したことによるものである。しかし、50%突き抜け電圧ΔVp,v50の変動に対する最適対向電極電位差δVcom,optの変動を示す直線Mの傾きが、突き抜け非補償駆動の場合と比べて大きくなっており、更には設計50%突き抜け電圧ΔVp,v50typの増加に対して直線Mの傾きの絶対値が増大している。これは、突き抜け補償条件に起因するもので、式(2)より突き抜け補償駆動において寄生容量Cgsと補助容量Csの比が一定でなければならないからである。

【0129】

今、直線Lは設計50%突き抜け電圧ΔVp,v50typが1.41Vにおいて横軸と交わり、このとき50%突き抜け電圧ΔVp,v50が増大する場合と減少する場合のそれぞれの50%突き抜け電圧許容変動量δ(ΔVp,v50)+とδ(ΔVp,v50)-は等しく、50%突き抜け電圧許容変動量が最大となる。しかし、50%突き抜け電圧の許容変動量が最大であっても、許容される合わせズレ量δdiが最大になる訳ではない。これは式(1)から分かるように、突き抜け電圧がゲート・ソース間の寄生容量Cgsと負荷容量Cloadとの比に比例することに起因している。アモルファスシリコンに突き抜け補償駆動を適用する場合は50%突き抜け電圧許容変動量が最大となる領域近傍で設計を行っていたが、これは電界効果移動度が小さいアモルファスシリコンに対して少しでも開口率を大きくするためであった。これに対して、本発明の目的は電界効果移動度が大きい半導体を用いた場合の画質を向上させることである。このため、本実施例では図16に基づいて画素の最適化を図る手法について以下で図面を参照しながら説明する。

【0130】

図11を参照して説明したアモルファスシリコンに突き抜け補償駆動を適用した従来例の場合と同様に、本実施例においても突き抜け補償駆動によって突き抜けに関する制約条件が緩和されるものとして、最大突き抜け電圧ΔVp,maxや最大突き抜け電圧差d(ΔVp)maxに対する上限値を設定しないものとする。即ち、画素の最適化を図る条件は、最適対向電極電位差δVcom,optが許容範囲内に抑制され、合わせ精度の管理値が実施可能な範囲に設定され、且つ開口率が最大となることである。

【0131】

図17は、図16における設計50%突き抜け電圧ΔVp,v50typの各値に対して50%突き抜け電圧が減少する方向と増加する方向の許容変動量δ(ΔVp,v50)-とδ(ΔVp,v50)+を求めたグラフである。図14、図15を用いて説明した突き抜け非補償駆動の場合と同様に、図17に示す50%突き抜け電圧の許容変動量δ(ΔVp,v50)-及びδ(ΔVp,v50)+と設計50%突き抜け電圧ΔVp,v50typとの関係から、許容合わせズレ量δdiと設計50%突き抜け電圧ΔVp,v50typとの関係を求めていく。

【0132】

即ち、チャネル幅WをW=Wmin-uに固定し、式(1)に示す突き抜け電圧の式より、50%負荷容量Cload,v50をパラメータとして設計50%突き抜け電圧ΔVp,v50typを表す。チャネル幅WをWmin-uに固定するのは、チャネル幅WがWmin-uより大きい場合に負荷容量をより大きく設定するために遮光性電極よりなる補助容量が大きくなって開口率が低下するのを回避するためである。これにより、図17に示す突き抜け電圧の許容変動量δ(ΔVp,v50)-及びδ(ΔVp,v50)+と設計50%突き抜け電圧ΔVp,v50typとの関係は、突き抜け電圧の許容変動量δ(ΔVp,v50)-及びδ(ΔVp,v50)+と50%負荷容量Cload,v50との関係に置き換えることができる。

【0133】

得られた50%突き抜け電圧の許容変動量δ(ΔVp,v50)-及びδ(ΔVp,v50)+と50%負荷容量Cload,v50との関係は、再度式(1)を用いて、ゲート・ソース間の寄生容量Cgsの許容変動量δCgsと50%負荷容量Cload,v50との関係に置き換える。得られたゲート・ソース間の寄生容量Cgsの許容変動量δCgsは、ゲート・ソース間の単位面積容量と図6を参照して説明したゲート・ソース間寄生容量Cgsの合わせズレによる変動面積から、許容合わせズレ量δdiに変換することができる。特に、50%突き抜け電圧が設計50%突き抜け電圧から減少する方向の50%突き抜け電圧の許容変動量δ(ΔVp,v50)-に対する許容合わせズレ量をδdi-とし、50%突き抜け電圧が設計50%突き抜け電圧から増加する方向の50%突き抜け電圧の許容変動量δ(ΔVp,v50)+に対する許容合わせズレ量をδdi+とする。

【0134】

図18は、図17より得られた50%突き抜け電圧が設計50%突き抜け電圧から減少する方向の50%突き抜け電圧の許容変動量δ(ΔVp,v50)-に対する許容合わせズレ量δdi-及び50%突き抜け電圧が設計50%突き抜け電圧から増加する方向の50%突き抜け電圧の許容変動量δ(ΔVp,v50)+に対する許容合わせズレ量δdi+と設計50%突き抜け電圧ΔVp,v50typとの関係を示したグラフである。図17において設計50%突き抜け電圧ΔVp,v50typ=2V付近でδ(ΔVp,v50)+が最大値を示すのに対して、図18においてδdi+が単調減少しているのは、チャネル幅WをWmin-uに固定して各設計50%突き抜け電圧ΔVp,v50に対して求めた50%負荷容量Cload,v50が設計50%突き抜け電圧ΔVp,v50typに対して示す単調減少の度合いが、δ(ΔVp,v50)+の増加の度合いよりも大きいためである。この結果、許容合わせズレ量δdi-とδdi+はいずれも設計50%突き抜け電圧ΔVp,v50typに対して単調減少を示す。

【0135】

図6に示した3σ相当の直接の合わせズレ量δdと間接の合せズレ量δiをそれぞれ2μmと3μmとすると、合成合せズレ量δdiは3.6μmである。図18より、許容合わせズレ量δdiが3.6mμm以上となる設計50%突き抜け電圧ΔVp,v50typの領域は、δdi-に対しては1.25V以下、δdi+に対しては0.425V以下である。即ち、δdi-とδdi+が共に3.6μm以上となるのはΔVp,v50typ≦0.425Vである。開口率を最大にするためには遮光性電極よりなる補助容量を必要最小限の大きさに設定する必要があり、合わせ精度の工程管理を3σで行うことが可能であれば許容合わせズレ量δdi-とδdi+の内律速する方の値を3σに設定することになる。

【0136】

本実施例において3σに相当するのは、設計50%突き抜け電圧ΔVp,v50=0.425Vの状態である。この場合の最大負荷容量Cload,maxは0.698pFであり、図9よりチャネル幅WがWmin-uであっても十分に充電可能な容量である。以上より、本実施例における最適な画素の状態は、チャネル幅W=Wmin-u、最大負荷容量Cload,maxは0.698pF、設計50%突き抜け電圧ΔVp,v50=0.425Vである。また、図11を参照して説明したアモルファスシリコンに突き抜け補償駆動を適用した場合の合わせ精度と同じ2.37σに対しては、許容合わせズレ量δdiは1.98μmとなり、許容合わせズレ量はδdi+が律速して設計50%突き抜け電圧ΔVp,v50typを1.53Vに設定することになる。

【0137】

ここで、本実施例で説明した突き抜け補償駆動を行う場合の最適画素に対する設計50%突き抜け電圧ΔVp,v50typの値が、図13〜図15を用いて説明したTAOSに突き抜け非補償駆動を適用した場合の最適画素に対する設計50%突き抜け電圧ΔVp,v50typの値よりも小さくなっている。即ち、両者のチャネル幅Wが同一であることから設計50%突き抜け電圧ΔVp,v50typの差は遮光性の電極よりなる補助容量Csの差を意味し、突き抜け非補償駆動を適用すると開口率が高くなる場合があることが本発明による新たな知見として得られた。これは、図13及び図16を参照して説明した本発明の式(4)より求めたMの傾き、つまり50%突き抜け電圧ΔVp,v50の変化に対する最適対向電極電位差δVcom,optの比ηの絶対値は突き抜け非補償駆動の場合よりも突き抜け補償駆動の場合の方が大きいことに起因している。

【0138】

[局所モードフリッカー]

次に、局所モードのフリッカー低減に対して本発明を用いる場合について以下で図面を参照しながら説明する。図19は、従来例及び本発明の実施例において述べたアモルファスシリコンとTAOSを画素TFTの半導体層として用いた液晶表示装置における、50%突き抜け電圧ΔVp,v50の変動に対する最適対向電極電位差δVcom,optの変化の割合を示す式(4)で表される直線Mの傾きηの設計50%突き抜け電圧ΔVp,v50typ依存性を示すグラフである。

【0139】

即ち、アモルファスシリコンについてはシミュレーションで求めた図8と図11における各直線Mの傾きを、TAOSについては本発明の関係式(4)より求めた図13と図16における直線Mの傾きをそれぞれプロットしたものである。そして、図19(A)は突き抜け非補償駆動の場合を示し、TAOSについては実施例で用いたパラメータVgh=15VとVgl=-2Vに加えて、Vgh=12VとVgl=-2V及びVgh=12VとVgl=-6Vの場合について破線グラフで示す。同様に図19(B)は突き抜け補償駆動の場合を示し、TAOSについては実施例で用いたパラメータVgh=15VとVgl=-2Vに加えて、Vgh=12VとVgl=-2V及びVgh=12VとVgl=-6Vの場合について破線グラフで示す。

【0140】

図19(A)に示す突き抜け非補償駆動の場合、Vghの増大及びVglの低下につれて、50%突き抜け電圧ΔVp,v50の変動に対する最適対向電極電位差δVcom,optの変化の割合を示すηの絶対値が増大しているがその増大量は小さく、アモルファスシリコンと同程度の0.6〜0.7に収まっている。アモルファスシリコンの非突き抜け補償駆動の場合、局所モードのフリッカーは非常に軽微で視認が困難なレベルであったことから、TAOSにおいても局所モードのフリッカーは非常に軽微なものになると考えられる。

【0141】

これに対して図19(B)に示す突き抜け補償駆動の場合はVghの増大及びVglの低下に対するηの絶対値の増大量が大きく、アモルファスシリコンの場合よりもηの絶対値が大きくなる場合がある。アモルファスシリコンに突き抜け補償駆動を適用した場合の局所モードフリッカーの実情は明確に視認できるレベルにあることから、ηの絶対値の許容限界は1.5〜2.0程度であると考えられ、好ましくは突き抜け非補償駆動レベルの0.7以下に抑制する必要がある。即ち、最適対向電極電位差を許容限界以内に抑制し、且つηの絶対値が2.0以下に抑制するように設計を行う必要がある。

【0142】

[有機EL]

次に、本発明を有機EL表示装置に適用する場合について説明する。図20は最も基本的な有機EL表示装置100の画素の概略等価回路図である。第一のTFT115のゲート電極は走査信号線111に、ドレイン電極は表示信号線113に、ソース電極は蓄積容量Cstと第二のTFT117のゲート電極にそれぞれ接続されている。第二のTFT117のドレイン電極は電源電圧Vcom1に、ソース電極は有機EL素子であるLED119にそれぞれ接続されている。即ち、TFTが2個と容量が1個からなる2T1C型と呼ばれるものである。

【0143】

走査信号線111の選択期間に第一のTFT115がON状態となって蓄積容量Cstへの充電が行われ、第一のTFT115のソース電極電位(以後、画素電極電位Vp1という。)がドレイン電極電位と等しくなったときに充電が完了する。このときの画素電極電位Vp1によって第二のTFT117がON状態となり、LED119には順バイアス電圧が印加されて電流が流れ、EL発光が生じる。走査信号線111の選択期間終了後にも蓄積容量Cstによって画素電極電位Vp1は保持されて第二のTFT117のON状態が維持され、LED119への電流注入が継続される。

【0144】

このとき、LED119へ一定電流値の注入が継続されるためには第二のTFT117のドレイン電極電位である電源電圧Vcom1は保持期間中一定である必要があるが、画素毎に電源電圧Vcom1の値を独立に制御することは画素構造の煩雑化による歩留まり低下などを招くため困難である。従って、電源電圧Vcom1は画面全体で一定として外部電源から給電し、画素毎に画素電極電位Vp1のみを制御することでLED119に流れる電流値の制御を行う。この結果、LED119に流れる電流は第二のTFT117のゲート電極電位で制御することになり、その電流値は画素電極電位Vp1の値に対して非常に敏感に変化する。即ち、画素電極電位Vp1の均一性と安定性を向上させることが重要である。

【0145】

画素電極電位Vp1が不均一になる原因は電流注入型の表示装置であるため、特に第二のTFT117が常にON状態となることから電圧ストレスによる閾値電圧Vthのシフトが指摘されている。この対策として、複数個のTFTと複数個の容量よりなる補償回路を各画素に配置する方法があり、様々な回路が提案されている。しかし、補償回路の導入は画素構造の煩雑化を招くため、光の取り出し方向の制限や歩留まりの低下を招くなどの不利な点がある。更には、液晶表示装置における突き抜け補償駆動の場合と同様に、容量結合型の補償であるため、各容量の値が合せズレなどのプロセス変動によって設計値からシフトした場合には期待通りの補償効果が得られず、輝度の面内均一性を逆に低下させる場合もある。

【0146】

更には、液晶表示装置の場合と同様に、過剰充電効果も画素電極電位Vp1の不均一性をもたらす。図21は、図20における第一のTFT115のゲート・ドレイン間の寄生容量の両電極がそれぞれ走査信号線111と表示信号線113の給電電極から電圧が印加されるため画素電極電位Vp1に影響しないことから省略し、第二のTFT117のチャネルとLED119を可変抵抗RtftとRelにそれぞれ置き換えたものである。図21と液晶表示装置10の画素の等価回路を示す図2と比べると、第一のTFT115のON電流による負荷容量の充電という観点で、2T1C型有機EL表示装置の画素と液晶表示装置の画素は等価であることが分かる。

【0147】

また、図21では図の煩雑化を避けるために省略しているが、走査信号線111と表示信号線113、及び可変抵抗Rtftの給電配線はそれぞれ抵抗を有しており、画素領域がマトリクス状をしているため各配線は互いに交差して容量を形成している。従って、各配線の給電電極に印加された信号電位の変化は、それぞれの時定数によって歪みながら伝播していく。このため、有機EL表示装置においても突き抜けによる過剰充電が生じ、過剰充電効果として画素電極電位Vp1の面内不均一性が生じることになる。

【0148】

以上をまとめると、液晶表示装置10の場合と同様に、或いはそれ以上に有機EL表示装置において第一のTFT115のソース電極と第二のTFT117のゲート電極が接続されたノードの画素電極電位Vp1を均一且つ所定の値に制御することが重要である。画素電極電位Vp1の不均一性の原因である電圧ストレスによる閾値電圧Vthのシフトを低減するために、補償回路を画素に組み込む手法が注目されて様々な回路が提案されている。

【0149】

しかし、補償回路の導入には、画素構造の煩雑化を伴うため歩留まり低下や光取り出し方向を限定するなどの不利な点があり、更にはプロセス変動によって補償回路の構成が補償条件を満たさずに画素電極電位Vp1の均一性の低下を招く場合もある。これに対して、過剰充電効果に対する対策は行われておらず、TAOSを画素TFTとして用いる場合には画素電極電位Vp1の不均一性が更に増大することが懸念される。

【0150】

こうした状況の下、本発明による設計手法は画素構造の煩雑化を伴うことなく過剰充電効果の抑制を図ることができるものであり、補償回路と併用することでより一掃の画素電極電位Vp1の均一性を向上させることができる。有機EL表示装置に対して本発明を適用する場合について以下で説明する。

【0151】

液晶表示装置の場合、画素電極電位Vpの対向電極電位Vcomに着目して輝度の均一性の向上を図った。有機EL表示装置の場合電源電圧Vcom1が与えられており、画素電極電位Vp1で第二のTFT117のON電流とLED119への注入電流を制御する。即ち、設定された電源電圧Vcom1に対して画素電極電位Vp1を適宜与えることによって可変抵抗RtftとRel及び第二のTFT117のソース電極電位Vqが決まる。第二のTFT117のON電流はゲート、ソース、ドレインの各電極電位の相対値で決まるので、電源電圧Vcom1の変動に着目するのも、画素電極電位Vp1の変動に着目するのも等価である。

【0152】

そこで、有機EL表示装置における画素電極電位Vp1を液晶表示装置10にて用いた画素電極電位Vpと置き換えて、液晶表示装置10について説明した対向電極電位Vcomに関する関係式の画素電極電位Vpを規定する。ここで、画素電極電位Vp1の不均一性による画質への影響は輝度ムラなどとして視認され、これは中間調において視認性が高まる。そこで、最大表示輝度の50%となる画素電極電位VpをVp,v50とし、Vp,v50において過剰充電の抑制を図る。

【0153】

有機EL表示装置の場合、負荷容量の印加電圧極性の反転を伴わないので、液晶表示装置のように局所的な対向電極電位Vcomの最適値というものは存在しない。このため、走査信号線111の給電電極に最も近い画素のVp,v50(near)と最も遠い画素のVp,v50(far)に対してδVpをδVp=Vp,v50(far)−Vp,v50(near)とし、δVpと50%突き抜け電圧ΔVp,v50の関係式を式(3)に倣って式(7)とおく。

δVp=(α・ΔVp,v50+β)γ・・・(7)

ここで、50%突き抜け電圧ΔVp,v50は次式で表される。

ΔVp,v50=(Cgs1,v50/Cload,v50)ΔVg

ΔVg=Vgh-Vgl

【0154】

Cgs1,v50とCload,v50はそれぞれ画面輝度が最大輝度の50%となる第二のTFT117のゲート電極電位V50における第一のTFT115のゲート・ソース間容量Cgs1と第一のTFT115に対する負荷容量であり、Cload,v50は次式で表される。

Cload,v50=Cgs1,v50+Cst+Cgs2,v50+Cgd2,v50+Cother

蓄積容量Cstは固定容量で一定であるが、ゲート・ソース間の寄生容量Cgsとゲート・ドレイン間の寄生容量Cgdは、MIS構造を有するTFTの寄生容量のため印加される電圧によって容量値が変化する。したがってV50に対する値をCgs2,v50、Cgd2,v50としているが、TFTがON状態であれば印加電圧に対する容量値の変化は小さく、一定値と見なすことができる。Cotherは画素電極電位Vpと同電位の全ての電極がその周りに配置された配線や電極などとの間に形成するカップリング容量の総和である。

【0155】

次に、設計50%突き抜け電圧ΔVp,v50typに対するδVpをδVp,typとすると、ΔVp,v50の変動に対するδVpの変動は式(4)に倣って式(8)で表される。

δVp=η(ΔVp,v50−ΔVp,v50typ)+δVp,typ・・・(8)

ηは50%突き抜け電圧ΔVp,v50の変動に対するδVpの変動の割合である。δVpの許容変動の上限値をξ+、下限値をξ-とし、50%突き抜け電圧ΔVp,v50が50%突き抜け電圧の設計値ΔVp,v50typから減少する方向の許容変動量δ(ΔVp,v50)-とΔVp,v50がΔVp,v50typから増大する方向の許容変動量δ(ΔVp,v50)+をそれぞれ

δ(ΔVp,v50)-=ΔVp,v50typ−(ΔVp,v50-)>0

δ(ΔVp,v50)+=(ΔVp,v50+)−ΔVp,v50typ>0

とすると、液晶表示装置の場合と同様に式(5)と式(6)を満たすように設計すれば過剰充電による画素電極電位Vp1の変動が許容範囲内に抑えられることになる。先に説明した式(5)と式(6)を改めて次に示す。

δ(ΔVp,v50)-≦{(α・ΔVp,v50typ+β)γ−(ξ+)}/η・・・(5)

δ(ΔVp,v50)+≦{(ξ-)−(α・ΔVp,v50typ+β)γ}/η・・・(6)

ここで、ξ+とξ-は輝度の面内均一性に関する製品仕様を満たすことから決まる値であり、製品毎に異なる。

【0156】

式(5)、(6)を使用することで、アクティブ・マトリクス型の表示装置が電界効果移動度が1cm2/Vs以上で且つ70cm2/Vs以下のトランジスタを備えていても、既存の製造プロセスにおけるフォトレジストの位置合わせ精度で製造することができるような設計をすることができる。具体的には、最初に設定したΔVp,v50typで式(5)、(6)を満たすか否かを検証し、満たさない場合にΔVp,v50typの制御パラメータであるON状態のゲート電極電位Vgh、OFF状態のゲート電極電位Vgl、寄生容量Cgs、および負荷容量Cloadのいずれかまたは複数の要素の組み合わせを変更しながら収束させる。その際に、OFF状態のゲート電極電位Vglはプロセス・パラメータであるため固定しておき、ON状態のゲート電極電位Vghは精密に変更できないため、寄生容量Cgsおよび負荷容量Cloadを変更することが望ましい。

【0157】

そして、これまで本発明について図面に示した特定の実施の形態をもって説明してきたが、本発明は図面に示した実施の形態に限定されるものではなく、本発明の効果を奏する限り、これまで知られたいかなる構成であっても採用することができることはいうまでもないことである。更には、式(3)、式(4)、式(7)、式(8)におけるα、β、γ、ηを与える式は本明細書にて示した形態に限定されるものではなく、本発明の効果を奏する限り、異なる他の形態であっても採用することができることはいうまでもないことである。

【符号の説明】

【0158】

11a〜11c 走査信号線

13a〜13c 表示信号線

15a 薄膜トランジスタ(TFT)

17a 液晶層

19a 画素電極

21a 対向電極

25a 補助容量線

Clc 液晶容量

Cs 補助容量

Cgs 寄生容量

Cload 負荷容量

Cload,max 最大負荷容量

Vp 画素電極電位

ΔVp 突き抜け電圧(画素電極電位低下量)

ΔVp,v50 50%突き抜け電圧

ΔVp,v50typ 設計50%突き抜け電圧

Vcom 対向電極電位、

Vcom1 電源電圧

Vcom,opt 最適対向電極電位

δVcom 対向電極電位差

δVcom,opt 最適対向電極電位差

δVcom,typ 設計対向電極電位差

Vcs 補助容量電極電位

Vg 走査信号線電位

ΔVg 走査信号線電位変化量

Vs ソース電極電位

Vd ドレイン電極電位

Vds ソース・ドレイン間電圧

Vgs ゲート・ソース間電圧

Vgh ON状態のゲート電極電位

Vgl OFF状態のゲート電極電位

Vsig 表示信号線電位

【技術分野】

【0001】

本発明は、各画素にスイッチング素子としてのトランジスタを配置したアクティブ・マトリクス型表示装置において表示品位の低下を低減する技術に関し、特に、トランジスタの電界効果移動度の増大によって助長される走査信号線の時定数に起因した過剰充電効果による表示品位の低下を低減する技術に関する。

【背景技術】

【0002】

現在、アモルファスシリコン薄膜を用いた薄膜トランジスタ(以下、TFTという)が液晶表示装置等のスイッチング素子として利用され、テレビ受像機やパーソナルコンピューターのモニター等において実用化されている。しかしながらその電界効果移動度は結晶シリコンや100cm2/Vs未満のポリシリコンと比べて非常に小さく、およそ0.5〜1cm2/Vsであるため、液晶表示装置が大型高精細化や高速応答化するにつれて必要な電流量を確保するためにTFTのサイズを大きくして対応する必要がある。

【0003】

その結果としてTFTの寄生容量が増大し、寄生容量の影響を低減するために必要な補助容量が増大する。補助容量は補助容量線と画素電極との交差容量として形成されるが、補助容量線は時定数を低減するために遮光性の金属配線が好ましいため、結果的に補助容量の増大は補助容量線の面積の増加をもたらして開口率の低下を招く。即ち、大型高精細化や高速応答化に伴って開口率が確保できなくなり、アモルファスシリコンを画素のスイッチング素子として用いるには限界がある。

【0004】

その一方で、近年、金属酸化物系半導体薄膜を用いた半導体素子が注目されている。この薄膜は成膜方法やプロセス条件によって異なるが、Soluble系のもので3cm2/Vs以上、スッパッタリング法によって成膜したもので10cm2/Vs以上の電界効果移動度を示し、今後の研究によって更なる高移動度化が期待される。また、低温での成膜や可視光に対して透明な膜を形成できること等の特徴を有しており、プラスチック基板やフィルムなどの透明性基板上にフレキシブルで透明なTFTを形成することが可能である(特許文献1)

【0005】

また、TFTの活性層に用いる酸化物半導体膜として、In、Ga及びZnを含む酸化物から構成される半絶縁性の透明なアモルファス薄膜が知られており、これをチャネル層に用いるとともに、電気伝導度の大きなInGaZnO3(ZnO)4の層にAu膜を積層したものをソース・ドレイン電極として用いたトップゲート型TFTの構造が開示されており、さらに、アモルファスInGaZnO4のTFTはアモルファスシリコン薄膜トランジスタに比べて格段に大きな電界効果移動度を有することが開示されている(特許文献2)。

【0006】

そして、このような優れた特性を備えるTFTを、液晶表示装置だけではなく、他の表示装置にも利用できるようにすべく、現在活発な研究開発が行われている。更には、高価な真空装置を製造設備として必要としない有機TFTの開発も盛んに行われており、近年では電界効果移動度が1cm2/Vsを超えるものが報告され、表示装置への適用を目指した研究開発が精力的に行われている。特許文献3は、走査方向の前段の走査線と絶縁膜を介して一部重畳して配置される画素電極の間で補助容量を形成したCsオンゲート・タイプのアレイ基板において、電荷の再分配と走査線の時定数により生ずるフリッカーを低減する技術を開示する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−150900号公報

【特許文献2】特開2006−165529号公報

【特許文献3】特開2003−177725号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

図1は液晶表示装置10のアレイ基板の一部に対応する概略の等価回路図であり、走査信号線11a、11b・・・11nと表示信号線13a、13b・・・13mで囲まれた複数の画素領域がマトリクス状に配置されている。走査信号線と表示信号線はそれぞれ抵抗を有しており、互いの交差領域には容量が形成される。このため、各配線の端部に設けた給電電極に印加した信号電位(Vg、Vsig)は抵抗と容量で決まる時定数によって遅延して歪ながら伝搬する。ここで、時定数は1-1/e≒0.632、即ち配線の給電電極に印加される電位の変化量に対して、その63.2%の電位変化に要する時間である。

【0009】

図2は図1に示した画素領域の概略の等価回路図であり、TFT15aのゲート電極は走査信号線11aに、ドレイン電極は表示信号線13aに、ソース電極は画素電極19aに、それぞれ接続されている。画素電極19aは走査信号線11aと略並行に配置された補助容量線25aと絶縁膜を介して交差しており、交差部が補助容量Csとなる。補助容量線25aも抵抗を有しており、表示信号線13aとの交差部において容量を形成している。

【0010】

ここで、補助容量線25aは抵抗を低減するために遮光性金属で形成する必要があるため、その存在が開口率を低下させる。開口率の低減を抑制するために補助容量の構成には様々な工夫がなされており、たとえば画素電極19aと電気的に接続した電極と補助容量線25aの交差領域に補助容量を形成したり、或いは補助容量線25aを配置せずに画素電極19aの延在部と上段または下段画素の走査信号線との交差領域に補助容量を形成したりすることができる。

【0011】

また、TFT15aのゲート電極とソース電極の間にはゲート・ソース間の寄生容量Cgsが形成されている。このような配線や画素を同一の絶縁性基板上に配置して構成した第一の基板と、絶縁性の基板よりなる第二の基板との間に液晶層17aを挟持することで液晶表示装置10が構成される。画素電極19aと液晶層17aを挟んで液晶容量Clcを構成する対向電極21aは第一の基板上、或いは第二の基板上に配置される。

【0012】

図3は図2の等価回路において、画素電極電位Vpが対向電極電位Vcomより高い正極性書き込みにより負荷容量Cloadを充電する際のゲート電位Vgl、Vgh、表示信号線電位Vsig、画素電極電位Vp及び対向電極電位Vcomを示すタイミングチャートである。図3(A)は走査信号線11aの給電電極に近い画素(Left)、図3(B)は走査信号線11aの給電電極から遠い画素(Right)についてのものである。

【0013】

図3において走査信号線11aの給電電極に、走査信号線11aの選択期間のみTFT15aをON状態にするゲート電位Vghを、非選択期間にはTFT15aをOFF状態にするゲート電位Vglをそれぞれ印加するパルス状の走査信号線電位Vgを給電する。走査信号線11aの給電電極に印加する走査信号線電位VgをOFF状態のゲート電位VglからON状態のゲート電位Vghに切り替えると、時定数τgの影響で給電電極から離れるほど走査信号線11aの電位がOFF状態のゲート電位VglからON状態のゲート電位Vghへ変位するのに時間を要するため、TFT15aがOFF状態からON状態へ遷移するのに要する時間が長くなり、選択期間内で負荷容量Cloadを充電する時間が短くなる。

【0014】

ここで、負荷容量Cloadは次式で与えられる。

Cload=Clc+Cs+Cgs+Cother

ここにCotherは画素電極19aとその周囲の各配線との間に形成されるカップリング容量の総和である。このため液晶表示装置10を設計する上では、給電電極から最も遠い画素の充電が選択期間内に完了するようにTFTのサイズを設定する必要がある。図3(A)、(B)のいずれにおいても選択期間が終了する前に充電が完了すると、画素電極19aの電位Vp、即ちソース電極電位Vsは、表示信号線13aの電位つまりドレイン電極電位Vdとほぼ等しくなって、TFT15aから負荷容量Cloadへ向かう電流が流れないので画素電極電位Vpの変化は停止する。この結果、選択期間終了時点では同一の走査信号線に接続された各画素の画素電極電位Vpは略等しくなる。

【0015】

選択期間が終了すると走査信号線11aの給電電極に印加される走査信号線電位VgはON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglに切り替わり、接続された各TFT15aはON状態からOFF状態に向けて導通状態が遷移を始める。ON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglへの電位変化も同様に時定数τgの影響を受けるため、給電電極から離れるにしたがって時間を要する。即ち、走査信号線11aに印加する走査信号が矩形パルスであった場合、給電電極近傍に配置されたTFT15aは走査信号が瞬時にON状態の電位VghからOFF状態の電位Vglに低下してTFT15aはOFF状態となり、この走査信号線電位Vgの電位変化量ΔVgは寄生容量Cgsを介して画素電極電位Vpを低下させる。

【0016】

このときの画素電極電位Vpの低下量ΔVpはΔVg=Vgh−Vglとしたときに次式で表される。

ΔVp=(Cgs/Cload)ΔVg ・・・(1)

画素電極電位低下量ΔVpは寄生容量Cgsを介したカップリング効果による画素電極電位Vpの低下量、或いはゲート電極電位がON状態の電位VghからOFF状態の電位Vglに変化する際に負荷容量Cloadに蓄えられた電荷の総量を保持しながら寄生容量Cgsの印加電圧の極性変化に伴う電荷再分配によって生じた画素電極電位Vpの低下量とみることもできる。ここで述べた、画素電極電位Vpが選択期間終了時の電位からOFF状態のTFT15aに対応する電位へ低下する現象を突き抜けと呼び、そのときの画素電極電位Vpの低下量ΔVpを突き抜け電圧ΔVpと呼ぶ。

【0017】

選択期間の終了時点ではVd≒Vsであったためソース・ドレイン間電圧VdsはVds≒0となって表示信号線13aから画素電極19aに向かって電流は流れなかったが、この画素電極電位Vpの低下によってVds=ΔVpとなり、ゲート・ソース間電圧Vgsに応じた電流が表示信号線13aから画素電極19aに向かって流れることになる。走査信号線11aの給電電極近傍では瞬時にゲート電極電位がON状態の電位VghからOFF状態の電位Vglに低下してTFT15aがOFF状態となるため、Vds=ΔVpとなってもTFT15aにはゲート電極電位がOFF状態のゲート電位Vglのときにドレイン・ソース間に流れる電流Ioff程度の微小な電流しか流れず、これによる画素電極電位Vpの変化は無視できる。

【0018】

しかし、TFT15aが走査信号線11aの給電電極から離れるにつれてON状態の電位VghからOFF状態の電位Vglへの電位低下に時間を要するためTFT15aは瞬時にOFF状態にならず、TFT15aがOFF状態になる前の期間にソース・ドレイン間電圧Vdsに応じた電流が表示信号線13aから画素電極19aに向かって流れる。即ち選択期間が終了した後にも負荷容量Cloadへの充電が継続され、突き抜け電圧ΔVpが低減する。突き抜けによる画素電極電位Vpの低下と、充電による画素電極電位Vpの上昇という二つの現象が合わさった結果、実効的な突き抜け電圧である実効突き抜け電圧ΔVpが低下することになる。

【0019】

例えば画面全体を正極性の同一電位に充電する場合、TFT15aがOFF状態になったときの画素電極電位Vpは、走査信号線11aの給電電極から離れるにつれて実効的な突き抜け電圧ΔVpが減少するために画素電極電位Vpが上昇する。この結果、対向電極電位Vcomと画素電極電位Vpの差である液晶層印加電圧は、走査信号線11aの給電電極から離れるほど増大する。負極性の書き込みの場合、画素電極電位Vp即ちソース電極電位Vsが正極性書き込みの場合よりも低いためゲート・ソース間電圧Vgsが大きくなり、選択期間終了後に継続される負荷容量への充電量も大きくなる。

【0020】

このため負極性書き込みにおける実効突き抜け電圧は正極性書き込みの場合よりも小さくなる。今、正極性書き込みにおける表示信号線電位と実効突き抜け電圧をそれぞれVsig+とΔVp+、負極性書き込みにおける表示信号線電位と実効突き抜け電圧をそれぞれVsig-とΔVp-、TFT15aがOFF状態における正極性と負極性それぞれの画素電極電位をVp+とVp-とおくと、Vp+とVp-はそれぞれ次式で表される。

Vp+=(Vsig+)−(ΔVp+)

Vp-=(Vsig-)−(ΔVp-)

【0021】

また、実効的に液晶層に印加される電圧は、正極性と負極性における液晶層印加電圧の平均値に略一致すると見なすことができる。そこで、正極性と負極性の平均の液晶層印加電圧をVavgとおくとVavgは次式で表される。

Vavg=[{(Vp+)−Vcom}+{Vcom−(Vp-)}]/2

={(Vsig+)−(Vsig-)}/2+{(ΔVp-)−(ΔVp+)}/2

これより、走査信号線の給電電極に近い画素では選択期間終了後に負荷容量への充電が継続されないためΔVp-=ΔVp+であり、平均の液晶層印加電圧Vavg={(Vsig+)−(Vsig-)}/2となる。走査信号線の給電電極から遠い画素では、過剰充電効果によってΔVp-<ΔVp+となるため、平均の液晶層印加電圧は走査信号線の給電電極に近い画素よりも低下する。従って、TFT15aが走査信号線11aの給電電極から離れるほど、液晶層17aに印加される平均の電圧、即ち実効印加電圧は所定の印加電圧よりも減少することになる。

【0022】

選択期間終了後にTFT15aがOFF状態となるまでの期間を過剰充電期間、過剰充電期間にTFT15aから画素電極へ流れ込む電流を過剰充電電流、過剰充電電流による負荷容量Cloadへの充電を過剰充電、過剰充電によって生じる現象を総じて過剰充電効果と呼ぶことにする。

【0023】

上述のように液晶表示装置では過剰充電効果によって画素電極電位Vpが所定の電位からシフトすることになり、そのシフト量は走査信号線11aの給電電極から離れるほど増大する。この結果、様々な表示不良や表示品位の低下をもたらす。例えば画面全体が同一階調を表示する場合、本来なら画面全体の液晶層印加電圧は等しくなっているが、過剰充電効果によって走査信号線の給電電極側から終端側へ向かって液晶層印加電圧が減少するため、輝度傾斜と呼ばれるなだらかな輝度分布が生じる。しかし、過剰充電を許容範囲内に抑制することができる場合、輝度傾斜は許容範囲内に低減されて使用上の問題にはならない。

【0024】

過剰充電効果として生じる現象には輝度傾斜以外に様々なものがある。その中で特に視認性が高く顕著に現れる現象として、最適対向電極電位Vcom,optの面内分布に起因するフリッカーが挙げられる。以下で、図面を参照しながら、過剰充電効果によって生じる最適対向電極電位Vcom,optの面内分布に起因するフリッカーの発生メカニズムについて説明する。

【0025】

液晶表示装置において、TFT15aの負荷容量Cloadの一部を成す液晶容量Clcは、画素電極19aと対向電極21a及びこれらの電極に挟まれた液晶層17aより構成されており、両電極間の電界によって液晶層内の液晶分子の配向を制御することによって液晶層17aを透過する光の強度を制御する。対向電極21aと画素電極19aとの間に生じる電界によって液晶分子の配向を制御するため、画素毎に両電極の電位を独立に制御せずに、どちらか一方の電極電位が他の画素と同一になるように外部から給電し、他方の電極電位のみを画素毎に独立に制御することが可能である。

【0026】

この場合、画素構造が単純化するため開口率や歩留まりの点で有利となる。このため、一般的な液晶表示装置においては対向電極を他の画素と一体化した構造にして電位を外部から給電している。具体的に述べると対向電極は、TNモードやVAモードの液晶表示装置では対向基板全体に配置した巨大なベタ電極構造とし、IPSモードでは走査信号線方向に配列した各画素と一体化した構造とすることが一般に行われている。また、一部のIPSモードでは、同一基板上に画素電極と対向電極をそれぞれ画素毎に独立して制御する構造も提案されている。この構造は液晶層印加電圧の面内均一性を向上できる点で有利ではあるが、画素構造が煩雑となるため開口率や歩留まりの低下を招き易い。

【0027】

以上のように対向電極電位Vcomが同一の走査信号線に接続された複数のTFTに渡って同一の場合において、画素電極電位Vpが表示画面内で不均一になると、液晶層17aの印加電圧も不均一となる。この結果、不均一な液晶層印加電圧の分布に応じて輝度分布も不均一になり、表示品位を低下させる。従って、画素電極電位Vpの面内均一性を向上させることは重要である。

【0028】

液晶分子は直流電圧によって電気分解するため交流電圧によって駆動する必要があり、液晶層に印加する電圧の極性を常に反転させる駆動を行う。このため、例えば画面全体が同一階調の表示を行う場合、TFT15aがOFF状態のときの正極性画素電極電位をVp+とし、負極性画素電極電位をVp-とすると、対向電極21aの電位を正極性画素電極電位Vp+と負極性画素電極電位Vp-の平均値に設定したときに両極性の液晶層印加電圧が等しくなる。

【0029】

この時の対向電極電位Vcomを最適対向電極電位Vcom,optと呼び、次式で表す。

Vcom,opt={(Vp+)+(Vp-)}/2

対向電極電位Vcomが最適対向電極電位Vcom,optからシフトした場合、正極性と負極性の液晶層印加電圧が異なるため各極性での液晶分子の配向も異なる。即ち、液晶分子の配向が時間的に変動するため、透過光強度が時間的に一定とはならずに振動し、この透過光強度の振動がフリッカーとして視認されることになる。或いはまた、両極性の印加電圧が異なる状態が継続した場合、両極性の印加電圧の差が、実効的に直流電圧が印加されたものとして作用し、液晶層中の不純物イオンが画素電極表面などにトラップされる現象を誘発する。トラップされた不純物イオンが多くなると、トラップされた不純物イオンが形成する電界に対して液晶分子が応答するようになり、焼き付きとして視認されることになる。

【0030】

図4(A)は、走査信号線方向に並んだ異なるn点とf点におけるそれぞれの最適対向電極電位Vcom,opt(n)、Vcom,opt(f)から対向電極電位Vcomのシフトに対するフリッカー率の関係を模式的に示したものである。ここでフリッカー率とは、測定ポイントにおける全透過光強度に占める30Hzの光強度の割合である。30Hzの光は人間がフリッカーとして最も感知し易い周波数である。図4(B)は、走査信号線の給電電極側から反対側までの画素の位置において画素電極電位Vpと対向電極電位Vcomが過剰充電効果によって変化する様子を模式的に示した図である。

【0031】

図4(A)においてn点に対応する実線は走査信号線の給電電極に近い領域を示し、f点に対応する破線は給電電極から遠い領域を示している。それぞれのポイントにおけるフリッカー率はそれぞれのポイントにおける対向電極電位Vcomに対して最小値を有し、そこから対向電極電位Vcomが増えても減ってフリッカー率は増大する。フリッカー率が最小となるときの対向電極電位Vcomが当該ポイントにおける最適対向電極電位Vcom,optであり、最適対向電極電位Vcom,optが印加されているポイントにおいてそれぞれ、対向電極電位Vcomと画素電極電位Vpの差である正極性と負極性の液晶層印加電圧は等しくなっている。

【0032】

前述のように過剰充電効果によって正極性と負極性の液晶層印加電圧において、共に実効突き抜け電圧が低下するため、図4(B)に示すように正極性と負極性の画素電極電位Vpは共に走査信号線の給電電極から離れるにつれて上昇し、最適対向電極電位Vcom,optも走査信号線の給電電極から離れるほど上昇する。このため対向電極電位Vcomを一定の値にしたときに、図4(A)に示すようにあるポイントの対向電極電位Vcomは最適対向電極電位Vcom,optとなっても、他のポイントでは最適対向電極電位Vcom,optからシフトしているためフリッカー率が大きくなる。

【0033】

従って、画面全体としてのフリッカーを低減するためには図4(B)に示すようにn点とf点の両ポイントにおける最適対向電極電位Vcom,opt(n)、Vcom,opt(f)の中間に存在するc点に対向電極電位Vcomを設定することになるが、この場合の対向電極電位Vcomはn点とf点のどちらのポイントにとっても最適対向電極電位Vcom,optではないためフリッカーを完全に解消することはできない。このため、解消しきれずに生じるフリッカーのレベルを許容限界以内に抑制する必要がある。

【0034】

フリッカーは正極性と負極性における液晶の配向の相違に起因しているため、最適対向電極電位Vcom,optからのズレに対するフリッカー率は粘性や誘電率異方性などの液晶の物性や、液晶層の電界強度に影響する液晶層の厚さなどの応答速度に関するパラメータに依存することになる。しかし実際には各パネルメーカの液晶表示装置は高速応答化や低電圧駆動化などといった目指す特性が同じであるため、結果的に表示モードや駆動方法などの基本的な仕様が同じなら液晶材料の相違に対してこれらのパラメータの差は小さくなっている。

【0035】

即ち、最適対向電極電位Vcom,optからのズレに対するフリッカー率の変化の割合は、表示モードや駆動方法が同じなら液晶種別によらず略一定となる。このため、上述の解消しきれないフリッカーの視認性と以下に述べる最適対向電極電位Vcom,optの面内格差である最適対向電極電位差δVcom,optは強い相関性を有することになる。図4(B)に示すように、対向電極電位Vcomの最適対向電極電位Vcom,optからのズレは、n点とf点で最も大きくなり、画素の位置が中央に近付くに伴って小さくなる。従って、走査信号線の給電電極に最も近い画素と最も遠い画素における最適対向電極電位Vcom,optの差に相当する最適対向電極電位差δVcom,optを過剰充電効果の指標とすることができる。

【0036】

そこで、最適対向電極電位差δVcom,optを次式で定義する。

δVcom,opt=Vcom,opt(far)-Vcom,opt(near)

ここで、Vcom,opt(near)は走査信号線の給電電極に最も近い画素における最適対向電極電位を表し、Vcom,opt(far)は最も遠い画素における最適対向電極電位を表す。

【0037】

上述のように過剰充電効果は、液晶層印加電圧の面内不均一性に起因した表示品位の低下を招く。このため、過剰充電効果を抑制する必要があり、様々な方法が提案されている。その一つとして、図3に示すように表示信号線電位Vsigの変化時刻を走査信号線電位VgがON状態のゲート電位VghからOFF状態のゲート電位Vglに切り替わる時刻より遅らせる方法があり、多くの液晶表示装置において実用化されている。例えば特許文献3では、走査信号線の電位が変化する時刻と表示信号線の電位が変化する時刻の設定法についての実施例が示されている。

【0038】

即ち、当該走査信号線11aに接続されたTFT15aがOFF状態になる前に表示信号線13aの電位が次段走査信号線11bに接続された負荷容量の充電に向けて変化した場合、過剰充電期間におけるTFTのドレイン電極電位Vdが当該画素に対する電位から次段画素に対する電位に変化することになる。この結果、当該画素の画素電極電位が所定の値から大きくシフトすることになる。これを抑制するため、当該走査信号線に接続されたTFTが完全にOFF状態になるのを待って表示信号線の電位を変化させる必要がある。この待ち時間として、概ね走査信号線の時定数程度に設定することが一般に行われている。

【0039】

この手法は過剰充電期間におけるTFT動作点の設定によって、過剰充電効果を抑制するものである。過剰充電は過剰充電電流の流れ易さ、即ち半導体層の電界効果移動度に依存するため、電界効果移動度が小さいアモルファスシリコンに対しては上記手法のみ適用しても過剰充電の低減効果は十分であったと考えられ、電界効果移動度が増大した場合には上記手法のみでは十分な過剰充電の低減効果を得られないことが懸念される。しかし、過剰充電効果と電界効果移動度との関係についての詳しい研究結果の報告はこれまでになされていないのが実情である。

【0040】

そこで、本発明の発明者が長年に渡って液晶表示装置の開発に際して使用し、改良を続けてきたシミュレータを用いて、最適対向電極電位差δVcom,optを過剰充電効果の指標とするシミュレーションを行った。得られた結果において、過剰充電効果と電界効果移動度との関係を図5に示す。図5は、半導体層としてアモルファスシリコンを用いた26インチのFull-HD、フレーム周波数120Hz、TNモードの液晶表示装置について、電界効果移動度が0〜50cm2/Vsの範囲で求めたものである。

【0041】

一般的に最適対向電極電位差δVcom,optの許容限界は0.2V程度であるのに対して、図5では電界効果移動度の増大に対して最適対向電極電位差δVcom,optが0.2Vを大きく超えている。即ち、電界効果移動度の増大に対して最適対向電極電位差δVcom,optを低減するためには、設計や製造プロセスにおける対策の導入が不可欠であることを示唆している。

【0042】

ところで、液晶表示装置は誘電率異方性を有する液晶分子の配向状態を電界によって制御するものであるため、液晶層17aへの印加電圧に対して液晶容量Clcが異なり、突き抜け電圧ΔVpも液晶層印加電圧によって異なる。また、フリッカーや焼き付きなどの視認性も同様に液晶層印加電圧によって異なる。液晶層印加電圧の変化に対する輝度変化は、最大輝度の50%の輝度となる50%液晶層印加電圧V50付近で最も大きくなるため、過剰充電によって生じる液晶層印加電圧の面内不均一性に起因した過剰充電効果の諸現象の視認性もこの付近の液晶層印加電圧において高まる。

【0043】

このため、過剰充電効果の解析を50%液晶層印加電圧V50で行い、50%液晶層印加電圧V50における突き抜け電圧ΔVpを特に50%突き抜け電圧ΔVp,v50と表すことにする。なお本発明においては、過剰充電効果の解析を最大輝度の50%の輝度となる液晶層印加電圧に限定する必要はなく、過剰充電効果の視認性の影響によっては他の割合の液晶層印加電圧を選択することもできる。

【0044】

フリッカーの視認性が高い表示状態は、画面全体が同一の中間調表示の場合であるため、突き抜け電圧ΔVpとしては50%突き抜け電圧ΔVp,v50だけを考えることができる。しかし、焼き付きは上述のように正極性と負極性の液晶層印加電圧の差に起因し、この電圧差は実効突き抜け電圧の面内不均一性によって生じるため、過剰充電効果が微弱で無視できる場合であっても異なる階調領域が混在する表示状態では、突き抜け電圧ΔVpが階調に応じて異なることに起因して液晶層の実効印加電圧に直流電圧成分が生じる。

【0045】

このため、階調による相違、即ち液晶層印加電圧の相違に対する直流電圧成分の相違を抑制する条件として、式(1)の負荷容量Cloadが最小となる場合の最大突き抜け電圧ΔVp,maxと、最大突き抜け電圧ΔVp,maxと負荷容量Cloadが最大となる場合の最小突き抜け電圧ΔVp,minとの差である最大突き抜け電圧差d(ΔVp)max=ΔVp,max-ΔVp,minを基準値以下に設定する方法が従来より用いられている。

【0046】

また、液晶容量Clcも印加電圧に応じて異なり、液晶容量Clcの最大値と最小値をそれぞれClc,max、Clc,minとし、50%液晶層印加電圧V50に対する液晶容量Clcを50%液晶容量Clc,v50とすると、それぞれに対して負荷容量Cloadも最大負荷容量Cload,max、最小負荷容量Cload,min、50%負荷容量Cload,v50とおくことができる。

【0047】

ここで、最適対向電極電位差δVcom,optの解析において正極性画素電位Vp+と負極性画素電位Vp-の算出時刻を、選択期間終了時刻から選択期間の3倍の時間が経過した時刻とした。これは、後に述べる突き抜け補償駆動の場合においてもTFTが完全にOFF状態に至った直後の時刻であり、この時刻で画素電位を算出することによってTFTのOFF状態におけるリーク電流の影響を無視することができ、その結果として過剰充電効果の解析を明確に行えるからである。

【0048】

アモルファスシリコン(a-Si)に対する従来の画素設計の方法を以下で図面を参照しながら説明する。本従来例におけるデバイスモデルの概要は次の通りである。画素精細度Full-HD(走査信号線数1080本)、画素サイズ100μm×300μm、走査信号線選択期間7.55μs、ゲート絶縁膜の比誘電率と膜厚はそれぞれ7.4、3000Å、液晶動作モードはTN、最大液晶容量Clc,maxは0.365pF、最小液晶容量Clc,minは0.177pF、50%液晶容量Clc,v50は0.271pFとする。

【0049】

また、TFT形状は図6に示すアモルファスシリコンに対して一般的に用いられているU字型とし、チャネル長Lは最小加工寸法を想定して4μmとした。以上のデバイスモデル設定項目は、本明細書で述べる全ての従来の方法、及び後に述べる本発明の実施例に対して共通事項である。その他個別の設定項目及びパラメータについては、その都度示す。

【0050】

液晶表示装置の画素設計は、TFTの負荷容量Cloadに対するTFTサイズを決めること、及び画素電極の周囲に配置された走査信号線及び表示信号線と画素電極との間に形成される寄生容量を介したカップリングを抑制すること、という2つの要素から成り立つ。第3の要素として、TFTのリーク電流や液晶層中の不純物イオンに対する負荷容量Cloadの電荷保持能力設定条件に基く負荷容量設定というものがあるが、これは本発明の過剰充電とは独立したものであるため、ここでは説明を行わない。

【0051】

表示信号線と画素電極19aとのカップリングは、補助容量電極を両者の間に配置することで生じるシールド効果によって十分に低減することが可能である。但し、表示信号線と画素電極との間のカップリングを低減するために必要な補助容量の大きさはおよそ0.1pF程度以上であることが多い。

【0052】

これに対して、画素電極19aと走査信号線との間のカップリング、特に当該走査信号線11aとの間のカップリングによる画素電極電位Vpの変動は、主に画素電極19aが接続されているTFT15aのソース電極とゲート電極との交差領域に形成される寄生容量Cgsを介したものであり、上述の突き抜け電圧ΔVpとなる。即ち、カップリング容量の主体がTFTの寄生容量Cgsであるため、シールド効果を利用したカップリングの低減を行うことができず、結果として全てのカップリングの中で支配的なものとなる。

【0053】

突き抜け電圧ΔVpを低減する方法は、式(1)より寄生容量Cgsを低減するか負荷容量Cloadを増大するか、或いは走査信号線電位変化量ΔVgを低減するかの何れかである。TFT15aのチャネル幅Wとチャネル長L、及びON状態のゲート電極電位Vghは負荷容量Cloadを充電するための電流量を確保することで決まり、W/LとON状態のゲート電極電位Vghは互いに相反的な関係にある。

【0054】

しかし、ON状態のゲート電極電位Vghは走査信号線のドライバーICの出力バラツキなどの影響を強く受けるため、ON状態のゲート電極電位Vghによって電流量を微調整することは好ましくなく、必要なON状態のゲート電極電位Vghの値に対してある程度のマージンを上乗せした値に設定する必要がある。このため、一般的にはON状態のゲート電極電位Vghによって電流値をラフに決定した後、チャネル幅Wによって微調整する。W/Lを大きくするためにチャネル長Lは極力小さく設定することが望ましく、一般的にはプロセス上の最小加工寸法に設定するため、設計上は固定値となる。OFF状態のゲート電極電位VglはTFT15aの閾値電圧VthやTFT15aのリーク電流の影響を低減することで決まるプロセス・パラメータであり、設計上は固定値と見なされる。

【0055】

また、負荷容量Cloadを構成する液晶容量Clcは画素サイズによって略決定するため、負荷容量Cloadの支配的なパラメータは補助容量Csとなる。従って、突き抜け電圧ΔVpの値を決める重要なパラメータはチャネル幅Wの関数である寄生容量Cgsと、補助容量Csの関数である負荷容量Cloadとなる。このため、チャネル幅Wと負荷容量Cloadは突き抜け電圧ΔVpに関する制約条件を満たしながら、かつ互いに値を修正しながら収束を図るように決定される。

【0056】

[非補償駆動]

従来の画素設計の方法として、TFT15aの島状半導体にアモルファスシリコンを用いた場合について以下で図面を参照しながら説明する。この場合の個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=1.5V、ON状態のゲート電極電位Vgh=20V、OFF状態のゲート電極電位Vgl=-6V、電界効果移動度μeff=0.5cm2/Vsである。

【0057】

図6はアモルファスシリコンのTFTとして広く用いられているTFT形状で、合せズレによる寄生容量Cgsの変動率が小さいという特徴を有する。この場合、チャネル幅Wは、島状半導体57上のソース電極51のエッヂの長さとして定義することができる。また、チャネル形状がU字型をしているためチャネル幅Wには最小値Wmin-uが存在する。これは、U字の直線部が短くなって円弧部のみになった場合に合せズレによる寄生容量Cgsの変動率が急増するためである。U字型の電極をドレイン電極53、内側の直線的な電極をソース電極51とすると、チャネル長L=4μm、ソース電極幅=4μmの場合のチャネル幅Wの最小値Wmin-uは14.3μmである。

【0058】

図6においてゲート電極55の端と島状半導体57の端の距離は3σ相当の合せズレによって互いに近づいた場合に一致するように設定し、半導体層はゲート電極層に対してアライメントするため島状半導体57とゲート電極55は直接合せの関係にあるので、ゲート電極55の端と島状半導体57の端の距離は3σ相当の直接合せ精度δdとしている。同様に島状半導体57の端とドレイン電極53の先端間距離は3σ相当の合せズレによって互いに近づいた場合に一致するように設定し、半導体層とソース・ドレイン電極層は共にゲート電極層に対してアライメントするため島状半導体57とドレイン電極53は互いに間接合せの関係にあるので、島状半導体57の端とドレイン電極53の端との距離は3σ相当の間接合せ精度δiとしている。

【0059】

本明細書では、従来例の説明及び本発明の実施例において3σ相当の直接合せ精度δdと間接合せ精度δiをそれぞれ3μmと4μmに共通事項として設定している。この値は後に述べるように液晶事業創成期におけるプロセス精度の値である。しかし、合せ精度が向上した今日でも、ゲート電極端と半導体層端間距離及び半導体層端とドレイン電極の先端間距離において合わせズレに対するマージンを大きく確保すべきであるため、それぞれの距離を液晶事業の創成期と同じく3μmと4μmに設定することが多く、その場合には4σや5σ相当の合わせズレに対するマージンを有することになる。

【0060】

図6において点線59で囲んだ領域に形成される寄生容量Cgs領域は、島状半導体57上のソース電極51とドレイン電極53で挟まれたチャネル領域の中央からソース電極51寄りの領域と、ソース電極51とゲート電極55の交差領域との和として定義することができる。また、合せズレによる寄生容量Cgsの変動は、島状半導体57上の領域の変動はないものとみなし、ソース電極51とゲート電極55の交差面積のみ変動するとみなすことができる。

【0061】

これにより、寄生容量Cgsはチャネル幅W、チャネル長L、TFT形状と合せ精度、および単位面積容量で決まる。ソース電極51の幅Wsはプロセス上の最小加工寸法とすることができるため、寄生容量Cgsの設計パラメータはチャネル幅Wのみであり、他はプロセス・パラメータであるため設計上は固定値となる。

【0062】

以上の説明をまとめると、液晶表示装置の設計において、チャネル幅Wに対して充電可能な最大負荷容量Cload,maxの存在領域と、チャネル幅Wに対する突き抜け電圧ΔVpを基準値以下に低減するために最低限必要な最大負荷容量Cload,maxの存在領域との共通集合領域が画素の候補領域となる。この候補領域の中で補助容量Csが最小となるときに開口率が最大となり、最適な画素となる。

【0063】

特に従来のアモルファスシリコンの場合には、突き抜け電圧ΔVpとして負荷容量Cloadが最小となる場合の最大突き抜け電圧ΔVp,maxと、最大突き抜け電圧ΔVp,maxと負荷容量Cloadが最大となる場合の最小突き抜け電圧ΔVp,minとの差である最大突き抜け電圧差d(ΔVp)maxを基準値以下に低減することが従来より制約条件とされてきた。この様子を図7に示す。ここでは、突き抜け電圧ΔVpに対する制約条件として、従来より用いられている最大突き抜け電圧ΔVp,maxと最大突き抜け電圧差d(ΔVp)maxを取り上げ、それぞれの上限値を1.7V、0.35Vとしている。

【0064】

図7において、W-Cloadのグラフはチャネル幅Wに対して充電可能な最大の容量、即ちW-Cload特性を表し、チャネル幅Wに対する最大負荷容量Cload,maxはこのW-Cloadのグラフより下側に設定されることになる。W-ΔVp,maxのグラフは、チャネル幅Wに対して最大突き抜け電圧ΔVp,maxが上限値となる場合の最大負荷容量Cload,maxを表しており、最大突き抜け電圧ΔVp,maxを上限値以下にするためには、式(1)より最大負荷容量Cload,maxをこのグラフよりも上側に設定する必要がある。W-d(ΔVp)maxのグラフは、チャネル幅Wに対して最大突き抜け電圧差d(ΔVp)maxが上限値となる場合の最大負荷容量Cload,maxを表しており、最大突き抜け電圧差d(ΔVp)maxを上限値以下にするためには、最大負荷容量Cload,maxをこのグラフよりも上側に設定する必要がある。

【0065】

即ち、それぞれを基準値以下に低減するため最大負荷容量Cload,maxは、W-Cloadのグラフよりも下側で、かつW-d(ΔVp)maxのグラフとW-ΔVp,maxのグラフのいずれよりも上側に設定することになる。図7の場合、最大突き抜け電圧差W-d(ΔVp)maxのグラフがW-ΔVp,maxのグラフよりも上方に位置するため、W-Cloadのグラフより下側の領域で且つW-d(ΔVp)maxのグラフより上側の領域が画素の候補領域となる。他に条件が無い場合、この画素候補領域の中で開口率が最大、即ち遮光性の電極よりなる補助容量が最小となる点が最適な画素となる。従って、W-CloadのグラフとW-d(ΔVp)maxのグラフは共にWに対して単調増加していることから、両グラフの交点Xが最適な画素となる。

【0066】

図8は図7におけるW-CloadのグラフとW-d(ΔVp)maxのグラフとの交点Xの状態について、50%突き抜け電圧ΔVp,v50が設計値通りに出来上がった設計値である設計50%突き抜け電圧ΔVp,v50typ、及び寄生容量Cgsが合せズレなどによって変動した場合に50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typに対して±0.5V変動した場合の最適対向電極電位差δVcom,optをシミュレーションした結果である。

【0067】

図7においてW-d(ΔVp)maxのグラフとW-Cloadのグラフとの交点Xの状態はW=37.3μm、Cload,max=0.802pFであり、換算するとΔVp,v50=1.29Vとなる。最適対向電極電位差δVcom,optの上限値をξ+=0.2V、下限値をξ-=−0.2Vとすると、図8においてξ+とξ-となる50%突き抜け電圧ΔVp,v50はそれぞれ1.13Vと1.71Vである。これより、許容される50%突き抜け電圧ΔVp,v50の設計値からの変動量は、ΔVp,v50が増大する場合と減少する場合それぞれδ(ΔVp,v50)+=1.71−1.29=0.42V、δ(ΔVp,v50)-=1.29−1.13=0.16Vとなる。

【0068】

50%突き抜け電圧ΔVp,v50の変動方向に偏りがないならδ(ΔVp,v50)+とδ(ΔVp,v50)-の内小さい方が律速するので、この場合δ(ΔVp,v50)-=0.16Vに対して画素を決定することになる。突き抜け電圧ΔVpの変動が全て寄生容量Cgsの変動によるものであった場合、その変動の許容限界δCgsは式(1)より4.49fFに相当する。この寄生容量Cgsの変動が合せズレのみによるものであった場合、その合せズレ量の許容限界は単位面積容量を用いて算出すると5.14μmに相当することになる。

【0069】

ここで、寄生容量Cgsの変動面積はソース電極51の幅Wsで直接合せズレ量δdと間接合わせズレ量δiとの合成長さ分の変動に相当し、これらの合せズレの発生頻度が正規分布する場合、この合成合わせズレ量δdiはSQRT(δd^2+δi^2)と表される。ここにSQRT()は括弧内の平方根を表し、A^2はAのべき乗を表す。液晶事業の創世記の合せ精度は3σでδd=3μm、δi=4μmであり、この場合のδdiは5μmであった。近年の合せ精度は向上しており3σでδd=2μm、δi=3μmとすると、δdiが5.14μmとなるズレは4.3σに相当する。

【0070】

即ち、液晶事業創世記のプロセス精度であっても寄生容量Cgsのフォトレジストの合わせズレ量が5.14μmを超えるのは3σ以上の場合であり、今日のプロセス精度では4.3σに相当するため、歩留まりへの影響は小さく無視することができる。従って、電界効果移動度が0.5cm2/Vsのa-Siの場合、最適対向電極電位差δVcom,optを考慮しないで設計しても今日のプロセス精度が提供する合わせズレ量で製造すれば自動的に最適対向電極電位差δVcom,optが許容限度内に収まることになる。

【0071】

これに対して電界効果移動度が10cm2/Vsである透明アモルファス酸化物半導体(TAOS)について従来の設計方法を用いた場合を以下で図面を参照しながら説明する。ここでの個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=0V、ON状態のゲート電極電位Vgh=15V、OFF状態のゲート電極電位Vgl=-2V、電界効果移動度μeff=10cm2/Vsとしている。

【0072】

図9はTAOSにおけるチャネル幅Wと充電可能な最大容量の関係(W-Cload特性)と、チャネル幅Wと最大突き抜け電圧ΔVp,maxとの関係(W-ΔVp,max特性)及び最大突き抜け電圧差d(ΔVp)maxとの関係(W-d(ΔVp)max特性)をシミュレーションして求めた結果を示している。図9において、アモルファスシリコンの場合と同一の最大突き抜け電圧ΔVp,maxと最大突き抜け電圧差d(ΔVp)maxに関する制約条件を与えたときに、ΔVp,max≦1.7V及びd(ΔVp)max≦0.35Vを満たす場合の最大負荷容量Cload,maxに対しては、W-Cloadのグラフよりチャネル幅WをU字型TFTの最小値Wmin-uに設定しても書込みが可能である。他に制約条件が与えられていない場合、最適な画素の候補はW-ΔVp,maxのグラフよりも上にあるW-d(ΔVp)maxのグラフ上で且つチャネル幅Wの最小値Wmin-uの点に存在する。この状態の画素はW=14.3μm、Cload,max=0.477pFであり、換算するとΔVp,v50=0.67Vとなる。

【0073】

図10は図9より求めた最適な画素候補について、50%突き抜け電圧ΔVp,v50が設計値通りに出来上がった設計値である設計50%突き抜け電圧ΔVp,v50typ、及び寄生容量Cgsが合せズレなどによって変動した場合に50%突き抜け電圧ΔVp,v50が設計50%突き抜け電圧ΔVp,v50typに対して±0.5V変動した場合の最適対向電極電位差δVcom,optをシミュレーションした結果である。

【0074】

図10において、ξ+=0.2V、ξ-=−0.2Vとすると、50%突き抜け電圧ΔVp,v50が許容変動限界となるのは50%突き抜け電圧ΔVp,v50が減少した場合で、δ(ΔVp,v50)-=0.0236Vである。これに対する寄生容量Cgsの許容変動量の限界値は0.531fFに相当する。この寄生容量Cgsの変動が全てフォトレジストの合わせズレによるものであった場合のズレ量許容値は0.608μmに相当する。

【0075】

このズレ量の許容限界は、今日の合せ精度で3σ相当の直接合せズレ量δdと間接合わせズレ量δiがそれぞれ2μmと3μmの場合であっても僅か0.506σにしか相当せず、量産ラインにおいて合わせ精度を0.506σ以下に管理することは現実的には不可能である。従って、電界効果移動度が10cm2/VsであるTAOSにおいて、最適対向電極電位差δVcom,optを許容限界値以下に抑えた液晶表示装置の設計を行うためには、最大突き抜け電圧ΔVp,maxと最大突き抜け電圧差d(ΔVp)maxを基準値以下に抑制するという条件以外に新たな制約条件を導入する必要がある。

【0076】

尚、以上の説明では最適対向電極電位差δVcom,optの許容限界値をξ+=0.2V、ξ-=-0.2Vとしたが、この値は実用されている値の一例である。実際には最適対向電極電位差δVcom,optの許容限界値は製品仕様で決まる値であり、製品毎に異なるものである。しかし、電界効果移動度が大きくなってきた場合には、最適対向電極電位差δVcom,optの許容限界値が例示した値より大きくなっても、現在のプロセス精度で製造可能なズレ量の範囲で最適対向電極電位差δVcom,optを許容値に納めた液晶表示装置を設計することが困難なことには変わりがない。

【0077】

[補償駆動]

既に述べたように、過剰充電電流は突き抜け電圧ΔVpがTFTのソース・ドレイン間電圧Vdsとして作用することで流れるため、過剰充電効果は突き抜け電圧ΔVpに強く依存する。このため、過剰充電効果を低減するためには突き抜け電圧ΔVpの低減を図ることが有効である。その手段の一つとして、突き抜け補償駆動が挙げられる。本来の突き抜け補償駆動は、駆動によって突き抜け電圧ΔVpを低減することによって補助容量Csを低減し、開口率を増大させるものである。

【0078】

突き抜け補償駆動には多様な方法が提案され実用化されているが、基本的には補助容量Csを介したカップリングを利用して突き抜けによる画素電極電位Vpの低下を補償するもので、実効的な突き抜け電圧ΔVpを十分に低減するという点では全て同じである。即ち、寄生容量Cgsを介した走査信号線電位Vgの変化による画素電極電位Vpの変動量と、補助容量Csを介した補助容量電極の電位変化による画素電極電位Vpの変動量が等しい場合に画素電極電位Vpの変動が相殺される、というのが突き抜け補償駆動の原理である。

【0079】

そこで、突き抜け補償条件として次式が成り立つ。

(Cgs/Cload)ΔVg=(Cs/Cload)ΔVcs・・・(2)

ここで、ΔVcsは補助容量電極の電位変化量である。この関係式は、補助容量Csが画素電極の延在部と前段画素の走査信号線との交差領域に形成されるCs on Gate構造であった場合でも成り立つ。この場合、走査信号線電位VgはTFTがON状態のゲート電極電位Vghから、OFF状態のゲート電極電位Vglに低下する前にVglより低い第3の電位Vgcに低下する。即ち、当該走査信号線の電位がON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglに切り替わる時、前段走査信号線の電位はVgcからVglへと切り替わる。このとき、ΔVcs=Vgl-Vgcとなる。

【0080】

突き抜け補償駆動に対する従来の例としてアモルファスシリコンにCs on Gateを用いた場合について、以下で図面を参照しながら説明する。この場合の個別パラメータは、走査信号線時定数τg=2.5μs、閾値電圧Vth=1.5V、ON状態のゲート電極電位Vgh=20V、OFF状態のゲート電極電位Vgl=-6V、電界効果移動度μeff=0.5cm2/Vsである。チャネル幅Wはアモルファスシリコンに突き抜け非補償駆動を適用した場合と同一の37.3μmとする。

【0081】

突き抜け補償駆動はTFTがON状態の期間における負荷容量Cloadへの充電には影響が小さいため、ここでは無視しても差し支えない。従って、この場合のW-Cload特性とW-ΔVp,max特性及びW-d(ΔVp)max特性は図7と同一である。

【0082】

図11は、アモルファスシリコンに対してCs on Gateによる突き抜け補償駆動をした場合の従来の方法における50%突き抜け電圧ΔVp,v50と最適対向電極電位差δVcom,optの関係をシミュレーションで求めた結果である。Lは、50%突き抜け電圧ΔVp,v50の設計値である設計50%突き抜け電圧ΔVp,v50typに対する最適対向電極電位差δVcom,optである設計最適対向電極電位差δVcom,typの関係を示すグラフ、M(0V)〜M(2V)は、0V〜2Vの各設計50%突き抜け電圧ΔVp,v50typにおいて50%突き抜け電圧ΔVp,v50の変動に対する最適対向電極電位差δVcom,optの変動の関係を示すグラフである。

【0083】

設計50%突き抜け電圧ΔVp,v50typの増加に対してグラフLで示した設計最適対向電極電位差δVcom,typが緩やかに増大して約2Vで横軸と交わる。このとき50%突き抜け電圧ΔVp,v50が増大する場合と減少する場合のそれぞれの許容変動量δ(ΔVp,v50)+とδ(ΔVp,v50)-は等しく、許容変動量が最大となる。具体的には、ΔVp,v50typ=2.12Vでδ(ΔVp,v50)+=δ(ΔVp,v50)-=0.150Vとなり、この状態においてΔVp,v50の変動が全てCgsの変動によるものであった場合の許容Cgs変動量δCgsは2.49fFとなる。このCgs変動が全て合わせズレによるものであった場合の許容合わせズレ量は、3σ相当の直接合せ精度δdと間接の合わせ精度δiがそれぞれ2μmと3μmの場合で2.37σに相当する。この場合の最大負荷容量Cload,maxは0.526pFであり、突き抜け非補償駆動の場合と比べて補助容量Csが0.276pF低減でき、この分だけ開口率が増大する。

【0084】

ここでは詳しく述べないが、実際の設計に際して突き抜け補償駆動の場合、突き抜け電圧の設計は制約条件を課さずに行われ、式(1)に基づいて設計50%突き抜け電圧ΔVp,v50typを求めるとおよそ2V〜2.5Vになっていることが多い。製造工程において合わせ精度を2.37σ或いはそれ以下で管理することは不可能ではないが困難を伴うため、実際には製造設備の改造による合わせ精度の向上などによって対応している。即ち、このような労力を費やしてでも、突き抜け補償駆動による突き抜け電圧の制約条件緩和によってもたらされる補助容量低減による開口率の増大が必要とされている。一度このような対応が実施された製造工程においては、従来のアモルファスシリコンにおける突き抜け補償駆動の場合、突き抜け電圧に関する制約条件を考慮しなくても、結果的に最適対向電極電位差δVcom,optが許容範囲内に収まることになる。

【0085】

また、突き抜け補償駆動を行っているにも関わらず突き抜けが影響する過剰充電が生じている理由は、式(2)の突き抜け補償条件が、突き抜け補償過程が終了した時点での電位を一致させるものであるのに対して、実際には走査信号線電位と補償駆動による画素電極電位との間における電位の時間変化率が一致しないために生じた電位差によって過剰充電電流が流れることに起因する。

【0086】

即ち、走査信号線と補助容量線の時定数の設定法が全く異なり、特に容量の設定に関しては一般に両者の絶縁膜構成が異なるため単位面積容量が異なり、また走査信号線の場合は時定数の値のみが重要であるのに対して補助容量線では時定数に加えてカップリング低減などの機能を有するために容量の値を厳密な計算に基づいて決定される。こうしたことから、一般に走査信号線と補助容量線の時定数は大きく異なるため、特に走査信号線の選択期間終了直後の過剰充電期間初期においては、走査信号線の電位変化による画素電極電位変化量と補助容量線の電位変化による画素電極電位変化量が互いに相殺されない。このために生じた画素電極電位の変化量がソース・ドレイン間電圧Vdsとなって過剰充電電流が流れるからである。

【0087】

或いはCs on Gate構造の場合には、画素電極が当該走査信号線から受ける電位変化の過程は2段階に分かれており、第一段階は選択期間終了直後に走査信号線の電位がON状態のゲート電極電位VghからOFF状態のゲート電極電位Vglより低い第3の電位Vgcに切り替わる変化であり、第二段階は第3の電位VgcからOFF状態のゲート電極電位Vglへ切り替わる変化である。これに対して前段走査信号線から受ける電位変化の過程は、第3の電位VgcからOFF状態のゲート電極電位Vglへ切り替わる変化の一回だけである。このため、当該走査信号線から受ける画素電極電位変化量と前段走査信号線から受ける画素電極電位変化量が互いに相殺されない期間が存在し、この期間に過剰充電電流が流れるためである。

【0088】

以上を要約すれば、電界効果移動度が0.5cm2/Vs程度の従来のアモルファスシリコンに対する液晶表示装置の設計においては、過剰充電効果の影響が小さいため過剰充電効果に起因するフリッカーの指標となる最適対向電極電位差δVcom,optに関する制約条件を与えなくても、自然に最適対向電極電位差δVcom,optが許容範囲内に収まっていた。しかし、電界効果移動度が大きくなると過剰充電効果も増大するため、電界効果移動度が10cm2/VsのTAOSの場合には最適対向電極電位差δVcom,optを許容範囲内に低減するには、設計に際して新たな制約条件の導入が必要である。

【0089】

本発明は以上の点に鑑みてなされたものであり、本発明の目的は、表示品位の高いアクティブ・マトリクス型表示装置を提供することにある。さらに本発明の目的は、電界効果移動度が1cm2/Vsから70cm2/Vsの範囲にあるトランジスタを有するアクティブ・マトリクス型表示装置の表示品位を高めることにある。さらに本発明の目的は、そのようなアクティブ・マトリクス型表示装置を製造する方法を提供することにある。

【課題を解決するための手段】

【0090】

本発明は、電界効果移動度の増大に伴って増大する過剰充電効果に起因したフリッカーまたは画面輝度の均一性低下の指標に走査信号線方向における対向電極電位Vcomの面内格差である対向電極電位差δVcomを採用して、フリッカーまたは画面輝度の均一性低下を許容範囲内に収めるための新たな設計上の制約条件を提供し、高品位のアクティブ・マトリクス型表示装置を実現する。

【0091】

本発明は、電界効果移動度が1cm2/Vsを超えると影響が顕著になる過剰充電効果に起因した表示品位の低下を抑制するための手法を提供するものである。過剰充電効果による表示品位として影響を受けるのは輝度傾斜、焼き付き等の最適対向電極電位Vcom,optの面内分布に関するものである。特に、視認性の高いフリッカーに着目し、最適対向電極電位Vcom,optの走査線方向の面内格差である最適対向電極電位差δVcom,optを指標としてフリッカーまたは画面輝度の均一性低下を抑制する新たな設計条件を提供する。さらに本発明は、半導体層の電界効果移動度が1cm2/Vs以上のときにも、ON状態のゲート電極電位Vgh、OFF状態のゲート電極電位Vgl、負荷容量Cload、およびゲート・ソース間容量Cgsなどのプロセスの制御パラメータの値を決定して、最適対向電極電位差δVcom,optを許容変動範囲に収めることを可能にする式を提供する。

【0092】

具体的には、最適対向電極電位差δVcom,optが最大輝度に対してn%の輝度となる中間調におけるn%突き抜け電圧ΔVp,vnの一次関数として表せること、及び製造プロセスの影響によって寄生容量Cgsなどが変動することによるn%突き抜け電圧ΔVp,vnの変動に対する最適対向電極電位差δVcom,optの変動をn%突き抜け電圧ΔVp,vnの関数として定式化する。更には、プロセスレベルに対して最適対向電極電位差δVcom,optの許容限界値ξを超えないためにn%突き抜け電圧ΔVp,vnの設計値が満たすべき条件を、先に定式化した式を元に導出するものである。

【0093】