アドレスデコーディング方法とこれを用いた半導体メモリ装置

【課題】半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【解決手段】読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部10と、ストローブクロックの第1レベルに応答してアドレスをラッチし、ストローブクロックの第2レベルに応答して、アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部20と、内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部30と、を備える。

【解決手段】読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部10と、ストローブクロックの第1レベルに応答してアドレスをラッチし、ストローブクロックの第2レベルに応答して、アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部20と、内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部30と、を備える。

【発明の詳細な説明】

【背景技術】

【0001】

半導体メモリ装置は、動作モードに応じてデータを格納し、これを出力するための装置である。例えば、中央処理装置(CPU)などでデータを要求すると、半導体メモリ装置は、データを要求する装置から入力されたアドレスに対応するデータを出力する読み出し動作を行ったり、そのアドレスに対応する位置にデータ要求装置から提供されるデータを格納する書き込み動作を行う。

【0002】

このような読み出し動作および書き込み動作はアドレス経路を通して行われる。このアドレス経路には、ロウアドレスによってワードラインを選択した後、メモリセルに格納されたデータをセンスアンプによって増幅させる経路であるロウアドレス経路と、カラムアドレスによって複数の出力イネーブル信号Yi<n>のうちの1つを選択する経路であるカラムアドレス経路と、がある。このうち、カラムアドレス経路に関する動作(以下、「カラム動作」という。)は、カラムデコーダで構成されたカラム回路によって制御されるが、カラム経路回路は、カラムアドレスをデコーディングして複数の出力イネーブル信号Yi<n>のうちの1つを選択的にイネーブルさせ、イネーブルされた出力イネーブル信号Yi<n>によって選択されたビットラインに載せられたデータを入出力ラインに伝送する動作を行う。

【0003】

また、カラム動作は、アドレスをストロービングするためのストローブクロックCSTRを用いて出力イネーブル信号Yi<n>を生成する。実際に、半導体メモリ装置は、データを読み出したり書き込むための複数の制御回路およびデータ伝送ラインを備えており、複数の制御回路およびデータ伝送ラインによるローディング(Loading)の変化、およびカラム動作におけるPVT特性(Process、Voltage、Temperature)の変化により、ストローブクロックCSTRの入力時点が変化することがある。

【0004】

従来技術のカラム動作において、アドレスをデコーディングして出力イネーブル信号をイネーブルさせる動作を説明するが、PVT特性の変化によってストローブクロックCSTRの入力時点が早い場合(FAST)と遅い場合(SLOW)とに分けて説明すると、次のとおりである。

【0005】

図1は、従来技術のカラム動作において、ストローブクロックに応じてアドレスをデコーディングして生成される出力イネーブル信号のタイミング図である。

【0006】

まず、ストローブクロックCSTRの入力時点が早い場合(FAST)、第1組み合わせのアドレスADD<1:5>に応じて生成される内部アドレスIADD1<1:4>,IADD2<1:8>をデコーディングして、ストローブクロックCSTRがイネーブルされる「A」期間に出力イネーブル信号Yi<n>がイネーブルされる。しかし、ストローブクロックCSTRの入力時点が内部アドレスIADD1<1:4>,IADD2<1:8>のセットアップ時間より早い(FAST)時点に入力されるため、出力イネーブル信号Yi<n>のパルス幅が小さく形成され、半導体メモリ装置の読み出し動作および書き込み動作にエラーが発生することがある。

【0007】

次に、ストローブクロックCSTRの入力時点が遅い場合(SLOW)、第1組み合わせのアドレスADD<1:5>に応じて生成される内部アドレスIADD1<1:4>,IADD2<1:8>をデコーディングして、ストローブクロックCSTRがイネーブルされる「B」期間に出力イネーブル信号Yi<n>がイネーブルされる。しかし、ストローブクロックCSTRの入力時点が遅延されて入力されるため、第2組み合わせのアドレスADD<1:5>に応じて生成された内部アドレスIADD1<1:4>,IADD2<1:8>の入力時点と、ストローブクロックCSTRのイネーブル期間とが重なる。これにより、第1組み合わせのアドレスADD<1:5>に応じてイネーブルされる出力イネーブル信号Yi<n>と、第2組み合わせのアドレスADD<1:5>に応じてイネーブルされる出力イネーブル信号Yi<n+1>とがイネーブルされることとなり、半導体メモリ装置の読み出し動作および書き込み動作にエラーが発生することがある。

【0008】

なお、上記背景技術に関する先行技術文献としては、例えば下記特許文献1及び特許文献2が挙げられる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許公開第2001/0008282 A1号公報

【特許文献2】韓国特許第100884604 B1号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は、ストローブクロックの入力時点を、アドレスのセットアップタイム後に遅延させ、ストローブクロックの立ち上がりエッジに同期する出力イネーブル信号を生成することにより、半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【課題を解決するための手段】

【0011】

そこで、本発明は、読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部と、前記ストローブクロックの第1レベルに応答してアドレスをラッチし、前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部と、前記内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部と、を備える半導体メモリ装置を提供する。

【0012】

また、本発明は、読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成する第1ステップと、前記ストローブクロックの第1レベルに応答してアドレスをラッチする第2ステップと、前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する第3ステップと、を含むアドレスデコーディング方法を提供する。

【図面の簡単な説明】

【0013】

【図1】従来技術のカラム動作において、ストローブクロックに応じてアドレスをデコーディングして生成される出力イネーブル信号のタイミング図である。

【図2】本発明の一実施形態に係る半導体メモリ装置の構成を示すブロック図である。

【図3】図2に示す半導体メモリ装置に備えられたストローブクロック生成部の回路図である。

【図4】図2に示す半導体メモリ装置に備えられた第1内部アドレス生成部の回路図である。

【図5】図2に示す半導体メモリ装置に備えられた第2内部アドレス生成部の回路図である。

【図6】図2に示す半導体メモリ装置に備えられた第2内部アドレス生成部の他の実施形態に係る回路図である。

【図7】本発明の一実施形態に係るカラム動作において、ストローブクロックに応じてアドレスをデコーディングして生成される出力イネーブル信号のタイミング図である。

【発明を実施するための形態】

【0014】

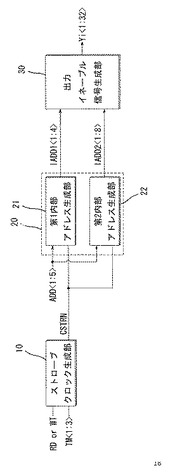

図2は、本発明の一実施形態に係る半導体メモリ装置の構成を示すブロック図である。

【0015】

図2に示すように、半導体メモリ装置は、読み出し信号RDまたは書き込み信号WTに応答して、選択的にイネーブルされる第1ないし第3テストモード信号TM<1:3>に応じて遅延量が調整されるストローブクロックCSTRNを生成するストローブクロック生成部10と、ストローブクロックCSTRNの第1レベルに応答してアドレスADD<1:5>をラッチし、ストローブクロックCSTRNの第2レベルに応答して、アドレスADD<1:5>をデコーディングして第1内部アドレスIADD1<1:4>および第2内部アドレスIADD2<1:8>を生成する内部アドレス生成部20と、第1内部アドレスIADD1<1:4>および第2内部アドレスIADD2<1:8>をデコーディングして選択的にイネーブルされる出力イネーブル信号Yi<1:32>を生成する出力イネーブル信号生成部30と、を備える。

【0016】

以下、ストローブクロック生成部10の構成を、図3を参照してより具体的に説明する。

【0017】

図3を参照すると、ストローブクロック生成部10は、読み出し信号RDまたは書き込み信号WTをバッファリングして第1ないし第3遅延信号Delay<1:3>を生成する遅延信号生成部11と、第1ないし第3テストモード信号TM<1:3>に応答して、第1ないし第3遅延信号Delay<1:3>のうちの少なくともいずれか1つをバッファリングしてストローブクロックCSTRNとして出力するストローブクロック出力部12と、から構成される。

【0018】

遅延信号生成部11は、読み出し信号RDまたは書き込み信号WTを所定期間遅延して第1遅延信号Delay<1>を生成する第1遅延信号生成部110と、第1遅延信号Delay<1>を所定期間遅延して第2遅延信号Delay<2>を生成する第2遅延信号生成部111と、第2遅延信号Delay<2>を所定期間遅延して第3遅延信号Delay<3>を生成する第3遅延信号生成部112と、から構成される。ここで、第3遅延信号Delay<3>の遅延量は第2遅延信号Delay<2>の遅延量より大きく、第2遅延信号Delay<2>の遅延量は第1遅延信号Delay<1>より大きい。また読み出し信号RDは、半導体メモリ装置が読み出し動作する場合にイネーブルされ、書き込み信号WTは、半導体メモリ装置が書き込み動作する場合にイネーブルされる信号である。

【0019】

ストローブクロック出力部12は、第1遅延信号Delay<1>と第1テストモード信号TM<1>とをNAND演算して出力するNANDゲートND10と、第2遅延信号Delay<2>と第2テストモード信号TM<2>とをNAND演算して出力するNANDゲートND11と、第3遅延信号Delay<3>と第3テストモード信号TM<3>とをNAND演算して出力するNANDゲートND12と、NANDゲートND10〜ND12の出力信号をNAND演算してストローブクロックCSTRNを生成するNANDゲートND13と、から構成される。ここでストローブクロックCSTRNの遅延量は、第1テストモード信号TM<1>がイネーブルされる場合には第1遅延信号Delay<1>の遅延量を有し、第2テストモード信号TM<2>がイネーブルされる場合には第2遅延信号Delay<2>の遅延量を有し、第3テストモード信号TM<3>がイネーブルされる場合には第3遅延信号Delay<3>の遅延量を有する。また、第1ないし第3テストモード信号TM<1:3>は、テストモードに入って選択的にイネーブルされるか、またはヒューズカッティングの可否によって選択的にイネーブルされる信号である。

【0020】

内部アドレス生成部20は、第1および第2アドレスADD<1:2>をデコーディングして第1内部アドレスIADD1<1:4>を生成する第1内部アドレス生成部21と、第3ないし第5アドレスADD<3:5>をデコーディングして第2内部アドレスIADD2<1:8>を生成する第2内部アドレス生成部22と、から構成される。

【0021】

以下、第1内部アドレス生成部21の構成を、図4を参照してより具体的に説明する。

【0022】

図4を参照すると、第1内部アドレス生成部21は、第1および第2アドレスADD<1:2>をデコーディングして第1デコーディング信号DEC1<1:4>を生成する第1入力デコーダ210と、ストローブクロックCSTRNに応答して、第1デコーディング信号DEC1<1:4>をバッファリングして第1ノードnd20に出力する第1バッファ部211と、ストローブクロックCSTRNに応答して第1ノードnd20の信号をラッチする第1ラッチ部212と、第1ラッチ部212の出力信号とストローブクロックCSTRNとをAND演算して第1内部アドレスIADD1<1:4>を生成する論理部213と、から構成される。第1バッファ部211は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第1デコーディング信号DEC1<1:4>を反転バッファリングして第1ノードnd20に出力する。第1ラッチ部212は、第1ノードnd20の信号を反転バッファリングして出力し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第1ノードnd20の信号をラッチする。

【0023】

以下、第2内部アドレス生成部22の構成を、図5を参照してより具体的に説明する。

【0024】

図5を参照すると、第2内部アドレス生成部22は、ストローブクロックCSTRNに応答して第3ないし第5アドレスADD<3:5>をバッファリングし、第2ノードnd21に出力する第2バッファ部220と、ストローブクロックCSTRNに応答して第2ノードnd21の信号をラッチし、反転バッファリングして反転アドレスBADD<1:3>を生成する第2ラッチ部221と、反転アドレスBADD<1:3>をデコーディングして第2内部アドレスIADD2<1:8>を生成する出力デコーダ222と、から構成される。第2バッファ部220は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第3ないし第5アドレスADD<3:5>を反転バッファリングして第2ノードnd21に出力する。第2ラッチ部221は、第2ノードnd21の信号を反転バッファリングして反転アドレスBADD<1:3>として出力し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第2ノードnd21の信号をラッチする。出力デコーダ222は、反転アドレスBADD<1:3>をデコーディングして第2内部アドレスIADD2<1:8>を生成する。

【0025】

このように構成された半導体メモリ装置の動作を、図7を参照して、ストローブクロックCSTRNの論理レベルに応じて第1ないし第5アドレスADD<1:5>をデコーディングして出力イネーブル信号Yi<1:32>を生成する動作を説明するが、第2テストモード信号TM<2>がイネーブルされる場合を例として説明すると、次のとおりである。

【0026】

まず、ストローブクロック生成部10は、テストモードまたはヒューズカッティングによってイネーブルされる第2テストモード信号TM<2>に応じて第1遅延信号Delay<1>より遅延量が大きく、第3遅延信号Delay<3>より遅延量が小さい第2遅延信号Delay<2>をバッファリングして、「X」期間にイネーブルされるストローブクロックCSTRNを生成する。

【0027】

次に、第1内部アドレス生成部21の第1入力デコーダ210は、第1および第2アドレスADD<1:2>をデコーディングして第1デコーディング信号DEC1<1:4>を生成し、第1バッファ部211は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1デコーディング信号DEC1<1:4>を反転バッファリングして第1ノードnd20に出力する。第1ラッチ部212は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1ノードnd20の信号をラッチし、第1ノードnd20の信号を反転バッファリングして出力する。論理部213は、第1ラッチ部212の出力信号とストローブクロックCSTRNとをAND演算して第1内部アドレスIADD1<1:4>を生成する。すなわち、第1内部アドレス生成部21は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1および第2アドレスADD<1:2>をデコーディングして生成された第1デコーディング信号DEC1<1:4>を受けてラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の「X」期間に第1デコーディング信号DEC1<1:4>をデコーディングして第1内部アドレスIADD1<1:4>を生成する。

【0028】

第2内部アドレス生成部22の第2バッファ部220は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第3ないし第5アドレスADD<3:5>を反転バッファリングして第2ノードnd21に出力する。第2ラッチ部221は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第2ノードnd21の信号をラッチし、第2ノードnd21の信号を反転バッファリングして反転アドレスBADD<1:3>として出力する。出力デコーダ222は、反転アドレスBADD<1:3>をデコーディングして第2内部アドレスIADD2<1:8>を生成する。すなわち第2内部アドレス生成部22は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第3ないし第5アドレスADD<3:5>を受けてラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の「X」期間に第3ないし第5アドレスADD<3:5>をバッファリングして生成された反転アドレスBADD<1:3>をデコーディングして、第2内部アドレスIADD2<1:8>を生成する。

【0029】

次に、出力イネーブル信号生成部30は、第1内部アドレスIADD1<1:4>および第2内部アドレスIADD2<1:8>をデコーディングして選択的にイネーブルされる出力イネーブル信号Yi<1:32>を生成する。

【0030】

このように構成された半導体メモリ装置は、ストローブクロックCSTRNの入力時点を、内部アドレスのセットアップタイムより大きい遅延量で遅延させて生成する。そして、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間にアドレスをラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の期間にラッチされたアドレスをデコーディングして出力イネーブルYi<1:32>を生成するため、半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる。

【0031】

図6は、図2に示す半導体メモリ装置に備えられた第2内部アドレス生成部の他の実施形態に係る回路図である。

【0032】

図6を参照すると、第2内部アドレス生成部22は、第3ないし第5アドレスADD<3:5>をデコーディングして第2デコーディング信号DEC2<1:8>を生成する第2入力デコーダ223と、ストローブクロックCSTRNに応答して、第2デコーディング信号DEC2<1:8>を反転バッファリングして第3ノードnd23に出力する第3バッファ部224と、ストローブクロックCSTRNに応答して、第3ノードnd23の信号をラッチする第3ラッチ部225と、第3ラッチ部225の出力信号をバッファリングして第2内部アドレスIADD2<1:8>として出力する遅延部226と、から構成される。第3バッファ部224は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第2デコーディング信号DEC2<1:8>を反転バッファリングして第3ノードnd23に出力する。第3ラッチ部225は、第3ノードnd23の信号を反転バッファリングして出力し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第3ノードnd23の信号をラッチする。

【0033】

このように、本発明の他の実施形態で構成された半導体メモリ装置の動作を、図7を参照して、ストローブクロックCSTRNの論理レベルに応じて第1ないし第5アドレスADD<1:5>をデコーディングして出力イネーブル信号Yi<1:32>を生成する動作を説明するが、第2テストモード信号TM<2>がイネーブルされる場合を例として説明すると、次のとおりである。

【0034】

まず、ストローブクロック生成部10は、テストモードまたはヒューズカッティングによってイネーブルされる第2テストモード信号TM<2>に応じて第1遅延信号Delay<1>より遅延量が大きく、第3遅延信号Delay<3>より遅延量が小さい第2遅延信号Delay<2>をバッファリングして、「X」期間にイネーブルされるストローブクロックCSTRNを生成する。

【0035】

次に、第1内部アドレス生成部21の第1入力デコーダ210は、第1および第2アドレスADD<1:2>をデコーディングして第1デコーディング信号DEC1<1:4>を生成し、第1バッファ部221は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1デコーディング信号DEC1<1:4>をバッファリングして第1ノードnd20に出力する。第1ラッチ部222は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1ノードnd20の信号をラッチする。論理部223は、第1ラッチ部222の出力信号とストローブクロックCSTRNとをAND演算して第1内部アドレスIADD1<1:4>を生成する。すなわち、第1内部アドレス生成部21は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1および第2アドレスADD<1:2>をデコーディングして生成された第1デコーディング信号DEC1<1:4>を受けてラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の「X」期間に第1デコーディング信号DEC1<1:4>をデコーディングして第1内部アドレスIADD1<1:4>を生成する。

【0036】

第2内部アドレス生成部22の第2入力デコーダ223は、第3ないし第5アドレスADD<3:5>をデコーディングして第2デコーディング信号DEC2<1:8>を生成し、第3バッファ部224は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第2デコーディング信号DEC2<1:8>を反転バッファリングして第3ノードnd23に出力する。第3ラッチ部225は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第3ノードnd23の信号をラッチし、反転バッファリングして出力する。遅延部226は、第3ラッチ部225の出力信号をバッファリングして第2内部アドレスIADD2<1:8>を生成する。すなわち、第2内部アドレス生成部22は、第3ないし第5アドレスADD<3:5>をデコーディングして第2デコーディング信号DEC2<1:8>を生成し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第2デコーディング信号DEC2<1:8>を受けてラッチし、これをバッファリングして第2内部アドレスIADD2<1:8>を生成する。

【0037】

次に、出力イネーブル信号生成部30は、第1および第2内部アドレスIADD1<1:4>,IADD2<1:8>をデコーディングして選択的にイネーブルされる出力イネーブル信号Yi<1:32>を生成する。

【0038】

以上、本実施形態の半導体メモリ装置は、ストローブクロックCSTRNの入力時点を、内部アドレスのセットアップタイムより大きい遅延量で遅延させて生成し、このとき、ストローブクロックCSTRNの論理レベルに応じて外部から入力される第1組み合わせの第1ないし第5アドレスADD<1:5>をラッチし、ストローブクロックCSTRNがイネーブルされた時点にラッチされた第1ないし第5アドレスADD<1:5>をデコーディングしてストローブクロックCSTRNの立ち上がりエッジに同期する第1ないし第32出力イネーブル信号Yi<1:32>を生成するため、正しい出力イネーブル信号を生成することができ、半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる。

【背景技術】

【0001】

半導体メモリ装置は、動作モードに応じてデータを格納し、これを出力するための装置である。例えば、中央処理装置(CPU)などでデータを要求すると、半導体メモリ装置は、データを要求する装置から入力されたアドレスに対応するデータを出力する読み出し動作を行ったり、そのアドレスに対応する位置にデータ要求装置から提供されるデータを格納する書き込み動作を行う。

【0002】

このような読み出し動作および書き込み動作はアドレス経路を通して行われる。このアドレス経路には、ロウアドレスによってワードラインを選択した後、メモリセルに格納されたデータをセンスアンプによって増幅させる経路であるロウアドレス経路と、カラムアドレスによって複数の出力イネーブル信号Yi<n>のうちの1つを選択する経路であるカラムアドレス経路と、がある。このうち、カラムアドレス経路に関する動作(以下、「カラム動作」という。)は、カラムデコーダで構成されたカラム回路によって制御されるが、カラム経路回路は、カラムアドレスをデコーディングして複数の出力イネーブル信号Yi<n>のうちの1つを選択的にイネーブルさせ、イネーブルされた出力イネーブル信号Yi<n>によって選択されたビットラインに載せられたデータを入出力ラインに伝送する動作を行う。

【0003】

また、カラム動作は、アドレスをストロービングするためのストローブクロックCSTRを用いて出力イネーブル信号Yi<n>を生成する。実際に、半導体メモリ装置は、データを読み出したり書き込むための複数の制御回路およびデータ伝送ラインを備えており、複数の制御回路およびデータ伝送ラインによるローディング(Loading)の変化、およびカラム動作におけるPVT特性(Process、Voltage、Temperature)の変化により、ストローブクロックCSTRの入力時点が変化することがある。

【0004】

従来技術のカラム動作において、アドレスをデコーディングして出力イネーブル信号をイネーブルさせる動作を説明するが、PVT特性の変化によってストローブクロックCSTRの入力時点が早い場合(FAST)と遅い場合(SLOW)とに分けて説明すると、次のとおりである。

【0005】

図1は、従来技術のカラム動作において、ストローブクロックに応じてアドレスをデコーディングして生成される出力イネーブル信号のタイミング図である。

【0006】

まず、ストローブクロックCSTRの入力時点が早い場合(FAST)、第1組み合わせのアドレスADD<1:5>に応じて生成される内部アドレスIADD1<1:4>,IADD2<1:8>をデコーディングして、ストローブクロックCSTRがイネーブルされる「A」期間に出力イネーブル信号Yi<n>がイネーブルされる。しかし、ストローブクロックCSTRの入力時点が内部アドレスIADD1<1:4>,IADD2<1:8>のセットアップ時間より早い(FAST)時点に入力されるため、出力イネーブル信号Yi<n>のパルス幅が小さく形成され、半導体メモリ装置の読み出し動作および書き込み動作にエラーが発生することがある。

【0007】

次に、ストローブクロックCSTRの入力時点が遅い場合(SLOW)、第1組み合わせのアドレスADD<1:5>に応じて生成される内部アドレスIADD1<1:4>,IADD2<1:8>をデコーディングして、ストローブクロックCSTRがイネーブルされる「B」期間に出力イネーブル信号Yi<n>がイネーブルされる。しかし、ストローブクロックCSTRの入力時点が遅延されて入力されるため、第2組み合わせのアドレスADD<1:5>に応じて生成された内部アドレスIADD1<1:4>,IADD2<1:8>の入力時点と、ストローブクロックCSTRのイネーブル期間とが重なる。これにより、第1組み合わせのアドレスADD<1:5>に応じてイネーブルされる出力イネーブル信号Yi<n>と、第2組み合わせのアドレスADD<1:5>に応じてイネーブルされる出力イネーブル信号Yi<n+1>とがイネーブルされることとなり、半導体メモリ装置の読み出し動作および書き込み動作にエラーが発生することがある。

【0008】

なお、上記背景技術に関する先行技術文献としては、例えば下記特許文献1及び特許文献2が挙げられる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許公開第2001/0008282 A1号公報

【特許文献2】韓国特許第100884604 B1号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は、ストローブクロックの入力時点を、アドレスのセットアップタイム後に遅延させ、ストローブクロックの立ち上がりエッジに同期する出力イネーブル信号を生成することにより、半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【課題を解決するための手段】

【0011】

そこで、本発明は、読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部と、前記ストローブクロックの第1レベルに応答してアドレスをラッチし、前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部と、前記内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部と、を備える半導体メモリ装置を提供する。

【0012】

また、本発明は、読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成する第1ステップと、前記ストローブクロックの第1レベルに応答してアドレスをラッチする第2ステップと、前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する第3ステップと、を含むアドレスデコーディング方法を提供する。

【図面の簡単な説明】

【0013】

【図1】従来技術のカラム動作において、ストローブクロックに応じてアドレスをデコーディングして生成される出力イネーブル信号のタイミング図である。

【図2】本発明の一実施形態に係る半導体メモリ装置の構成を示すブロック図である。

【図3】図2に示す半導体メモリ装置に備えられたストローブクロック生成部の回路図である。

【図4】図2に示す半導体メモリ装置に備えられた第1内部アドレス生成部の回路図である。

【図5】図2に示す半導体メモリ装置に備えられた第2内部アドレス生成部の回路図である。

【図6】図2に示す半導体メモリ装置に備えられた第2内部アドレス生成部の他の実施形態に係る回路図である。

【図7】本発明の一実施形態に係るカラム動作において、ストローブクロックに応じてアドレスをデコーディングして生成される出力イネーブル信号のタイミング図である。

【発明を実施するための形態】

【0014】

図2は、本発明の一実施形態に係る半導体メモリ装置の構成を示すブロック図である。

【0015】

図2に示すように、半導体メモリ装置は、読み出し信号RDまたは書き込み信号WTに応答して、選択的にイネーブルされる第1ないし第3テストモード信号TM<1:3>に応じて遅延量が調整されるストローブクロックCSTRNを生成するストローブクロック生成部10と、ストローブクロックCSTRNの第1レベルに応答してアドレスADD<1:5>をラッチし、ストローブクロックCSTRNの第2レベルに応答して、アドレスADD<1:5>をデコーディングして第1内部アドレスIADD1<1:4>および第2内部アドレスIADD2<1:8>を生成する内部アドレス生成部20と、第1内部アドレスIADD1<1:4>および第2内部アドレスIADD2<1:8>をデコーディングして選択的にイネーブルされる出力イネーブル信号Yi<1:32>を生成する出力イネーブル信号生成部30と、を備える。

【0016】

以下、ストローブクロック生成部10の構成を、図3を参照してより具体的に説明する。

【0017】

図3を参照すると、ストローブクロック生成部10は、読み出し信号RDまたは書き込み信号WTをバッファリングして第1ないし第3遅延信号Delay<1:3>を生成する遅延信号生成部11と、第1ないし第3テストモード信号TM<1:3>に応答して、第1ないし第3遅延信号Delay<1:3>のうちの少なくともいずれか1つをバッファリングしてストローブクロックCSTRNとして出力するストローブクロック出力部12と、から構成される。

【0018】

遅延信号生成部11は、読み出し信号RDまたは書き込み信号WTを所定期間遅延して第1遅延信号Delay<1>を生成する第1遅延信号生成部110と、第1遅延信号Delay<1>を所定期間遅延して第2遅延信号Delay<2>を生成する第2遅延信号生成部111と、第2遅延信号Delay<2>を所定期間遅延して第3遅延信号Delay<3>を生成する第3遅延信号生成部112と、から構成される。ここで、第3遅延信号Delay<3>の遅延量は第2遅延信号Delay<2>の遅延量より大きく、第2遅延信号Delay<2>の遅延量は第1遅延信号Delay<1>より大きい。また読み出し信号RDは、半導体メモリ装置が読み出し動作する場合にイネーブルされ、書き込み信号WTは、半導体メモリ装置が書き込み動作する場合にイネーブルされる信号である。

【0019】

ストローブクロック出力部12は、第1遅延信号Delay<1>と第1テストモード信号TM<1>とをNAND演算して出力するNANDゲートND10と、第2遅延信号Delay<2>と第2テストモード信号TM<2>とをNAND演算して出力するNANDゲートND11と、第3遅延信号Delay<3>と第3テストモード信号TM<3>とをNAND演算して出力するNANDゲートND12と、NANDゲートND10〜ND12の出力信号をNAND演算してストローブクロックCSTRNを生成するNANDゲートND13と、から構成される。ここでストローブクロックCSTRNの遅延量は、第1テストモード信号TM<1>がイネーブルされる場合には第1遅延信号Delay<1>の遅延量を有し、第2テストモード信号TM<2>がイネーブルされる場合には第2遅延信号Delay<2>の遅延量を有し、第3テストモード信号TM<3>がイネーブルされる場合には第3遅延信号Delay<3>の遅延量を有する。また、第1ないし第3テストモード信号TM<1:3>は、テストモードに入って選択的にイネーブルされるか、またはヒューズカッティングの可否によって選択的にイネーブルされる信号である。

【0020】

内部アドレス生成部20は、第1および第2アドレスADD<1:2>をデコーディングして第1内部アドレスIADD1<1:4>を生成する第1内部アドレス生成部21と、第3ないし第5アドレスADD<3:5>をデコーディングして第2内部アドレスIADD2<1:8>を生成する第2内部アドレス生成部22と、から構成される。

【0021】

以下、第1内部アドレス生成部21の構成を、図4を参照してより具体的に説明する。

【0022】

図4を参照すると、第1内部アドレス生成部21は、第1および第2アドレスADD<1:2>をデコーディングして第1デコーディング信号DEC1<1:4>を生成する第1入力デコーダ210と、ストローブクロックCSTRNに応答して、第1デコーディング信号DEC1<1:4>をバッファリングして第1ノードnd20に出力する第1バッファ部211と、ストローブクロックCSTRNに応答して第1ノードnd20の信号をラッチする第1ラッチ部212と、第1ラッチ部212の出力信号とストローブクロックCSTRNとをAND演算して第1内部アドレスIADD1<1:4>を生成する論理部213と、から構成される。第1バッファ部211は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第1デコーディング信号DEC1<1:4>を反転バッファリングして第1ノードnd20に出力する。第1ラッチ部212は、第1ノードnd20の信号を反転バッファリングして出力し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第1ノードnd20の信号をラッチする。

【0023】

以下、第2内部アドレス生成部22の構成を、図5を参照してより具体的に説明する。

【0024】

図5を参照すると、第2内部アドレス生成部22は、ストローブクロックCSTRNに応答して第3ないし第5アドレスADD<3:5>をバッファリングし、第2ノードnd21に出力する第2バッファ部220と、ストローブクロックCSTRNに応答して第2ノードnd21の信号をラッチし、反転バッファリングして反転アドレスBADD<1:3>を生成する第2ラッチ部221と、反転アドレスBADD<1:3>をデコーディングして第2内部アドレスIADD2<1:8>を生成する出力デコーダ222と、から構成される。第2バッファ部220は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第3ないし第5アドレスADD<3:5>を反転バッファリングして第2ノードnd21に出力する。第2ラッチ部221は、第2ノードnd21の信号を反転バッファリングして反転アドレスBADD<1:3>として出力し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第2ノードnd21の信号をラッチする。出力デコーダ222は、反転アドレスBADD<1:3>をデコーディングして第2内部アドレスIADD2<1:8>を生成する。

【0025】

このように構成された半導体メモリ装置の動作を、図7を参照して、ストローブクロックCSTRNの論理レベルに応じて第1ないし第5アドレスADD<1:5>をデコーディングして出力イネーブル信号Yi<1:32>を生成する動作を説明するが、第2テストモード信号TM<2>がイネーブルされる場合を例として説明すると、次のとおりである。

【0026】

まず、ストローブクロック生成部10は、テストモードまたはヒューズカッティングによってイネーブルされる第2テストモード信号TM<2>に応じて第1遅延信号Delay<1>より遅延量が大きく、第3遅延信号Delay<3>より遅延量が小さい第2遅延信号Delay<2>をバッファリングして、「X」期間にイネーブルされるストローブクロックCSTRNを生成する。

【0027】

次に、第1内部アドレス生成部21の第1入力デコーダ210は、第1および第2アドレスADD<1:2>をデコーディングして第1デコーディング信号DEC1<1:4>を生成し、第1バッファ部211は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1デコーディング信号DEC1<1:4>を反転バッファリングして第1ノードnd20に出力する。第1ラッチ部212は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1ノードnd20の信号をラッチし、第1ノードnd20の信号を反転バッファリングして出力する。論理部213は、第1ラッチ部212の出力信号とストローブクロックCSTRNとをAND演算して第1内部アドレスIADD1<1:4>を生成する。すなわち、第1内部アドレス生成部21は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1および第2アドレスADD<1:2>をデコーディングして生成された第1デコーディング信号DEC1<1:4>を受けてラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の「X」期間に第1デコーディング信号DEC1<1:4>をデコーディングして第1内部アドレスIADD1<1:4>を生成する。

【0028】

第2内部アドレス生成部22の第2バッファ部220は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第3ないし第5アドレスADD<3:5>を反転バッファリングして第2ノードnd21に出力する。第2ラッチ部221は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第2ノードnd21の信号をラッチし、第2ノードnd21の信号を反転バッファリングして反転アドレスBADD<1:3>として出力する。出力デコーダ222は、反転アドレスBADD<1:3>をデコーディングして第2内部アドレスIADD2<1:8>を生成する。すなわち第2内部アドレス生成部22は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第3ないし第5アドレスADD<3:5>を受けてラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の「X」期間に第3ないし第5アドレスADD<3:5>をバッファリングして生成された反転アドレスBADD<1:3>をデコーディングして、第2内部アドレスIADD2<1:8>を生成する。

【0029】

次に、出力イネーブル信号生成部30は、第1内部アドレスIADD1<1:4>および第2内部アドレスIADD2<1:8>をデコーディングして選択的にイネーブルされる出力イネーブル信号Yi<1:32>を生成する。

【0030】

このように構成された半導体メモリ装置は、ストローブクロックCSTRNの入力時点を、内部アドレスのセットアップタイムより大きい遅延量で遅延させて生成する。そして、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間にアドレスをラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の期間にラッチされたアドレスをデコーディングして出力イネーブルYi<1:32>を生成するため、半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる。

【0031】

図6は、図2に示す半導体メモリ装置に備えられた第2内部アドレス生成部の他の実施形態に係る回路図である。

【0032】

図6を参照すると、第2内部アドレス生成部22は、第3ないし第5アドレスADD<3:5>をデコーディングして第2デコーディング信号DEC2<1:8>を生成する第2入力デコーダ223と、ストローブクロックCSTRNに応答して、第2デコーディング信号DEC2<1:8>を反転バッファリングして第3ノードnd23に出力する第3バッファ部224と、ストローブクロックCSTRNに応答して、第3ノードnd23の信号をラッチする第3ラッチ部225と、第3ラッチ部225の出力信号をバッファリングして第2内部アドレスIADD2<1:8>として出力する遅延部226と、から構成される。第3バッファ部224は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第2デコーディング信号DEC2<1:8>を反転バッファリングして第3ノードnd23に出力する。第3ラッチ部225は、第3ノードnd23の信号を反転バッファリングして出力し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の期間に第3ノードnd23の信号をラッチする。

【0033】

このように、本発明の他の実施形態で構成された半導体メモリ装置の動作を、図7を参照して、ストローブクロックCSTRNの論理レベルに応じて第1ないし第5アドレスADD<1:5>をデコーディングして出力イネーブル信号Yi<1:32>を生成する動作を説明するが、第2テストモード信号TM<2>がイネーブルされる場合を例として説明すると、次のとおりである。

【0034】

まず、ストローブクロック生成部10は、テストモードまたはヒューズカッティングによってイネーブルされる第2テストモード信号TM<2>に応じて第1遅延信号Delay<1>より遅延量が大きく、第3遅延信号Delay<3>より遅延量が小さい第2遅延信号Delay<2>をバッファリングして、「X」期間にイネーブルされるストローブクロックCSTRNを生成する。

【0035】

次に、第1内部アドレス生成部21の第1入力デコーダ210は、第1および第2アドレスADD<1:2>をデコーディングして第1デコーディング信号DEC1<1:4>を生成し、第1バッファ部221は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1デコーディング信号DEC1<1:4>をバッファリングして第1ノードnd20に出力する。第1ラッチ部222は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1ノードnd20の信号をラッチする。論理部223は、第1ラッチ部222の出力信号とストローブクロックCSTRNとをAND演算して第1内部アドレスIADD1<1:4>を生成する。すなわち、第1内部アドレス生成部21は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第1および第2アドレスADD<1:2>をデコーディングして生成された第1デコーディング信号DEC1<1:4>を受けてラッチし、ストローブクロックCSTRNのレベルが論理ハイレベル(第2レベル)の「X」期間に第1デコーディング信号DEC1<1:4>をデコーディングして第1内部アドレスIADD1<1:4>を生成する。

【0036】

第2内部アドレス生成部22の第2入力デコーダ223は、第3ないし第5アドレスADD<3:5>をデコーディングして第2デコーディング信号DEC2<1:8>を生成し、第3バッファ部224は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第2デコーディング信号DEC2<1:8>を反転バッファリングして第3ノードnd23に出力する。第3ラッチ部225は、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第3ノードnd23の信号をラッチし、反転バッファリングして出力する。遅延部226は、第3ラッチ部225の出力信号をバッファリングして第2内部アドレスIADD2<1:8>を生成する。すなわち、第2内部アドレス生成部22は、第3ないし第5アドレスADD<3:5>をデコーディングして第2デコーディング信号DEC2<1:8>を生成し、ストローブクロックCSTRNのレベルが論理ローレベル(第1レベル)の「X」期間の前の期間に第2デコーディング信号DEC2<1:8>を受けてラッチし、これをバッファリングして第2内部アドレスIADD2<1:8>を生成する。

【0037】

次に、出力イネーブル信号生成部30は、第1および第2内部アドレスIADD1<1:4>,IADD2<1:8>をデコーディングして選択的にイネーブルされる出力イネーブル信号Yi<1:32>を生成する。

【0038】

以上、本実施形態の半導体メモリ装置は、ストローブクロックCSTRNの入力時点を、内部アドレスのセットアップタイムより大きい遅延量で遅延させて生成し、このとき、ストローブクロックCSTRNの論理レベルに応じて外部から入力される第1組み合わせの第1ないし第5アドレスADD<1:5>をラッチし、ストローブクロックCSTRNがイネーブルされた時点にラッチされた第1ないし第5アドレスADD<1:5>をデコーディングしてストローブクロックCSTRNの立ち上がりエッジに同期する第1ないし第32出力イネーブル信号Yi<1:32>を生成するため、正しい出力イネーブル信号を生成することができ、半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる。

【特許請求の範囲】

【請求項1】

読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部と、

前記ストローブクロックの第1レベルに応答してアドレスをラッチし、前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部と、

前記内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部と、

を備えることを特徴とする半導体メモリ装置。

【請求項2】

前記読み出し信号は、半導体メモリ装置が読み出し動作する場合にイネーブルされ、前記書き込み信号は、半導体メモリ装置が書き込み動作する場合にイネーブルされる信号であることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項3】

前記第1テストモード信号ないし第3テストモード信号は、テストモードに入って選択的にイネーブルされるか、またはヒューズカッティングの可否によって選択的にイネーブルされる信号であることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項4】

前記ストローブクロック生成部は、

前記読み出し信号または前記書き込み信号をバッファリングして第1遅延信号ないし第3遅延信号を生成する遅延信号生成部と、

前記第1テストモード信号ないし第3テストモード信号に応答して、前記第1遅延信号ないし第3遅延信号のうちの少なくともいずれか1つをバッファリングして前記ストローブクロックとして出力するストローブクロック出力部と、

を備えることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項5】

前記第3遅延信号の遅延量は前記第2遅延信号の遅延量より大きく、前記第2遅延信号の遅延量は前記第1遅延信号の遅延量より大きいことを特徴とする請求項4に記載の半導体メモリ装置。

【請求項6】

前記遅延信号生成部は、

前記読み出し信号または前記書き込み信号を所定期間遅延して前記第1遅延信号を生成する第1遅延信号生成部と、

前記第1遅延信号を所定期間遅延して前記第2遅延信号を生成する第2遅延信号生成部と、

前記第2遅延信号を所定期間遅延して前記第3遅延信号を生成する第3遅延信号生成部と、

を備えることを特徴とする請求項4に記載の含む半導体メモリ装置。

【請求項7】

前記内部アドレス生成部は、

第1アドレスおよび第2アドレスをデコーディングして第1内部アドレスを生成する第1内部アドレス生成部と、

第3アドレスないし第5アドレスをデコーディングして第2内部アドレスを生成する第2内部アドレス生成部と、

を備えることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項8】

前記第1内部アドレス生成部は、

前記第1アドレスおよび第2アドレスをデコーディングして第1デコーディング信号を生成する第1入力デコーダと、

前記ストローブクロックに応答して、前記第1デコーディング信号をバッファリングして第1ノードに出力する第1バッファ部と、

前記ストローブクロックに応答して、前記第1ノードの信号をラッチする第1ラッチ部と、

前記第1ラッチ部の出力信号と前記ストローブクロックとを論理演算して前記第1内部アドレスとして出力する論理部と、

を備えることを特徴とする請求項7に記載の半導体メモリ装置。

【請求項9】

前記第2内部アドレス生成部は、

前記ストローブクロックに応答して、前記第3アドレスないし第5アドレスをバッファリングして第2ノードに出力する第2バッファ部と、

前記ストローブクロックに応答して、前記第2ノードの信号をラッチして反転アドレスを生成する第2ラッチ部と、

前記反転アドレスをデコーディングして前記第2内部アドレスを生成する出力デコーダと、

を備えることを特徴とする請求項7に記載の半導体メモリ装置。

【請求項10】

前記第2内部アドレス生成部は、

前記第3アドレスないし第5アドレスをデコーディングして第2デコーディング信号を生成する第2入力デコーダと、

前記ストローブクロックに応答して、前記第2デコーディング信号をバッファリングして第3ノードに出力する第3バッファ部と、

前記ストローブクロックに応答して、前記第3ノードの信号をラッチする第3ラッチ部と、

前記第3ラッチ部の出力信号をバッファリングして前記第2内部アドレスとして出力する遅延部と、

を備えることを特徴とする請求項7に記載の半導体メモリ装置。

【請求項11】

読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成する第1ステップと、

前記ストローブクロックの第1レベルに応答して、アドレスをラッチする第2ステップと、

前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する第3ステップと、

を含むことを特徴とするアドレスデコーディング方法。

【請求項12】

第1ステップは、

前記読み出し信号または前記書き込み信号を所定期間遅延して第1遅延信号ないし第3遅延信号を生成する遅延信号生成ステップと、

前記第1テストモード信号ないし第3テストモード信号に応答して、前記第1遅延信号ないし第3遅延信号のうちの少なくともいずれか1つをバッファリングして前記ストローブクロックを生成するストローブクロック生成ステップと、

を含むことを特徴とする請求項11に記載のアドレスデコーディング方法。

【請求項13】

前記ストローブクロックは、前記第1テストモード信号ないし第3テストモード信号に応答して、前記第1遅延信号ないし第3遅延信号のうちの少なくともいずれか1つがバッファリングされて生成されることを特徴とする請求項12に記載のアドレスデコーディング方法。

【請求項14】

前記第3遅延信号の遅延量は前記第2遅延信号の遅延量より大きく、前記第2遅延信号の遅延量は前記第1遅延信号の遅延量より大きいことを特徴とする請求項12に記載のアドレスデコーディング方法。

【請求項15】

前記第3ステップは、

前記ストローブクロックの前記第2レベルに応答して、前記アドレスをデコーディングして内部アドレスを生成する内部アドレス生成ステップと、

前記内部アドレスをデコーディングして選択的にイネーブルされる前記出力イネーブル信号を生成する出力イネーブル信号生成ステップと、

を含むことを特徴とする請求項11に記載のアドレスデコーディング方法。

【請求項1】

読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部と、

前記ストローブクロックの第1レベルに応答してアドレスをラッチし、前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部と、

前記内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部と、

を備えることを特徴とする半導体メモリ装置。

【請求項2】

前記読み出し信号は、半導体メモリ装置が読み出し動作する場合にイネーブルされ、前記書き込み信号は、半導体メモリ装置が書き込み動作する場合にイネーブルされる信号であることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項3】

前記第1テストモード信号ないし第3テストモード信号は、テストモードに入って選択的にイネーブルされるか、またはヒューズカッティングの可否によって選択的にイネーブルされる信号であることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項4】

前記ストローブクロック生成部は、

前記読み出し信号または前記書き込み信号をバッファリングして第1遅延信号ないし第3遅延信号を生成する遅延信号生成部と、

前記第1テストモード信号ないし第3テストモード信号に応答して、前記第1遅延信号ないし第3遅延信号のうちの少なくともいずれか1つをバッファリングして前記ストローブクロックとして出力するストローブクロック出力部と、

を備えることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項5】

前記第3遅延信号の遅延量は前記第2遅延信号の遅延量より大きく、前記第2遅延信号の遅延量は前記第1遅延信号の遅延量より大きいことを特徴とする請求項4に記載の半導体メモリ装置。

【請求項6】

前記遅延信号生成部は、

前記読み出し信号または前記書き込み信号を所定期間遅延して前記第1遅延信号を生成する第1遅延信号生成部と、

前記第1遅延信号を所定期間遅延して前記第2遅延信号を生成する第2遅延信号生成部と、

前記第2遅延信号を所定期間遅延して前記第3遅延信号を生成する第3遅延信号生成部と、

を備えることを特徴とする請求項4に記載の含む半導体メモリ装置。

【請求項7】

前記内部アドレス生成部は、

第1アドレスおよび第2アドレスをデコーディングして第1内部アドレスを生成する第1内部アドレス生成部と、

第3アドレスないし第5アドレスをデコーディングして第2内部アドレスを生成する第2内部アドレス生成部と、

を備えることを特徴とする請求項1に記載の半導体メモリ装置。

【請求項8】

前記第1内部アドレス生成部は、

前記第1アドレスおよび第2アドレスをデコーディングして第1デコーディング信号を生成する第1入力デコーダと、

前記ストローブクロックに応答して、前記第1デコーディング信号をバッファリングして第1ノードに出力する第1バッファ部と、

前記ストローブクロックに応答して、前記第1ノードの信号をラッチする第1ラッチ部と、

前記第1ラッチ部の出力信号と前記ストローブクロックとを論理演算して前記第1内部アドレスとして出力する論理部と、

を備えることを特徴とする請求項7に記載の半導体メモリ装置。

【請求項9】

前記第2内部アドレス生成部は、

前記ストローブクロックに応答して、前記第3アドレスないし第5アドレスをバッファリングして第2ノードに出力する第2バッファ部と、

前記ストローブクロックに応答して、前記第2ノードの信号をラッチして反転アドレスを生成する第2ラッチ部と、

前記反転アドレスをデコーディングして前記第2内部アドレスを生成する出力デコーダと、

を備えることを特徴とする請求項7に記載の半導体メモリ装置。

【請求項10】

前記第2内部アドレス生成部は、

前記第3アドレスないし第5アドレスをデコーディングして第2デコーディング信号を生成する第2入力デコーダと、

前記ストローブクロックに応答して、前記第2デコーディング信号をバッファリングして第3ノードに出力する第3バッファ部と、

前記ストローブクロックに応答して、前記第3ノードの信号をラッチする第3ラッチ部と、

前記第3ラッチ部の出力信号をバッファリングして前記第2内部アドレスとして出力する遅延部と、

を備えることを特徴とする請求項7に記載の半導体メモリ装置。

【請求項11】

読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成する第1ステップと、

前記ストローブクロックの第1レベルに応答して、アドレスをラッチする第2ステップと、

前記ストローブクロックの第2レベルに応答して、前記アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する第3ステップと、

を含むことを特徴とするアドレスデコーディング方法。

【請求項12】

第1ステップは、

前記読み出し信号または前記書き込み信号を所定期間遅延して第1遅延信号ないし第3遅延信号を生成する遅延信号生成ステップと、

前記第1テストモード信号ないし第3テストモード信号に応答して、前記第1遅延信号ないし第3遅延信号のうちの少なくともいずれか1つをバッファリングして前記ストローブクロックを生成するストローブクロック生成ステップと、

を含むことを特徴とする請求項11に記載のアドレスデコーディング方法。

【請求項13】

前記ストローブクロックは、前記第1テストモード信号ないし第3テストモード信号に応答して、前記第1遅延信号ないし第3遅延信号のうちの少なくともいずれか1つがバッファリングされて生成されることを特徴とする請求項12に記載のアドレスデコーディング方法。

【請求項14】

前記第3遅延信号の遅延量は前記第2遅延信号の遅延量より大きく、前記第2遅延信号の遅延量は前記第1遅延信号の遅延量より大きいことを特徴とする請求項12に記載のアドレスデコーディング方法。

【請求項15】

前記第3ステップは、

前記ストローブクロックの前記第2レベルに応答して、前記アドレスをデコーディングして内部アドレスを生成する内部アドレス生成ステップと、

前記内部アドレスをデコーディングして選択的にイネーブルされる前記出力イネーブル信号を生成する出力イネーブル信号生成ステップと、

を含むことを特徴とする請求項11に記載のアドレスデコーディング方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−101737(P2013−101737A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2012−101455(P2012−101455)

【出願日】平成24年4月26日(2012.4.26)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成24年4月26日(2012.4.26)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]