アナログトランジスタ駆動信号により補償されるエレクトロルミネセント・ディスプレイ

ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置であって、駆動回路は、駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、駆動トランジスタの第2の供給電極に電気的に接続されるELデバイスとを有し、第1の供給電極、及び第2の供給電極を、異なった時間に流れる電流を測定して、駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変動を示す経年劣化信号を提供する測定回路と、線形コード値を提供する手段と、駆動トランジスタ、及びELデバイスの特性の変動を補償するために、経年劣化信号に応じて、線形コード値を変更する補償器と、駆動トランジスタのゲート電極を駆動するために、変更線形コード値に応じて、アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、を有する装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、エレクトロルミネセント・デバイスを介して電流を供給する駆動トランジスタに印加されるアナログ信号の制御に関する。

【背景技術】

【0002】

フラットパネル・ディスプレイは、演算、娯楽、及び通信のための情報ディスプレイとして、大いに興味を引く。有機発光ダイオード(OLED、organic light-emitting diode)技術などのエレクトロルミネセント(EL)・フラットパネル・ディスプレイ技術は、液晶ディスプレイ(LCD)、及びプラズマディスプレイパネル(PDP)などの他の技術に対して、色域、色彩、輝度、及び消費電力において利益をもたらす。しかしながら、ELディスプレイは、時間に伴う性能劣化に悩まされる。ディスプレイの寿命に亘って、高い画質を提供するためには、この劣化を補償しなければならない。

【0003】

一般的に、ELディスプレイは、同一のサブ画素のアレイを有する。サブ画素はそれぞれ、駆動トランジスタ(一般的には薄膜であり、TFTである)、及び実質的に光を発光する有機ダイオードであるELデバイスを有する。ELデバイスの光出力は、デバイスを流れる電流にほぼ比例するので、一般的に駆動トランジスタは、ゲート‐ソース電圧Vgsに応答する電圧制御電流源として構成される。LCDディスプレイで使用されるソースドライバと類似するソースドライバは、駆動トランジスタに制御電圧を提供する。ソースドライバは、所望のコード値ステップ74をアナログ電圧ステップ75に変換して、駆動トランジスタを制御する。ビット深度がより大きい線形ソースドライバが利用可能になりつつあるが、一般的には、コード値と、電圧との間の関係は、非線形である。非線形コード値と電圧との関係は、OLEDでは、LCDの特徴的なS形状(米国特許第4896947号などに示される)とは異なる形状を有するが、必要なソースドライバ電極は、2つの技術の間で非常に類似する。LCDソースドライバと、ELソースドライバとの間の類似性に加えて、LCDディスプレイと、ELディスプレイとは、一般的に同一の基板に製造される。すなわち、米国特許第5034340号において、Tanakaらが教示するように、アモルファスシリコン(a‐Si)である。アモルファスSiは、高価ではなく、かつ大型ディスプレイにおける処理が容易である。

【0004】

〔劣化のモード〕

しかしながら、アモルファスシリコンは、準安定である。すなわち、時間とともにa‐Si TFTのゲートに電圧バイアスが印加されて、しきい値電圧(Vth)がシフトすることによって、I−Vカーブがシフトする(Kagan & Andry, ed. Thin-film Transistors. New York: Marcel Dekker, 2003. Sec. 3.5, pp. 121-131)。一般的にVthは、順バイアスの下で時間とともに増加するため、平均的には、Vthシフトは、時間とともにディスプレイが薄暗くなる原因になるであろう。

【0005】

a‐Si TFTの不安定性に加えて、現在のELデバイス自体に不安定性を有する。例えばOLEDデバイスにおいて、電流がOLEDデバイスを流れるときに、OLEDデバイスの順電圧(Voled)が時間とともに増加し、効率(一般的にcd/Aで測定される)が低下する(Shinar, ed. Organic Light-Emitting Devices: a survey. New York: Springer-Verlag, 2004. Sec. 3.4, pp. 95-97)。定電流で駆動するときでも、効率の損失によって、時間とともにディスプレイが平均的に薄暗くなる。さらに、一般的なOLEDディスプレイの構成では、OLEDは、駆動トランジスタのソースに取り付けられる。この構成では、Voledが増加することにより、トランジスタのソース電圧が昇圧し、Vgsが低くなるので、OLEDデバイスを流れる電流(Ioled)が減少するために、時間とともに薄暗くなる原因になる。

【0006】

これら3つの効果(Vthシフト、OLED効率の損失、及びVoled上昇)によって、OLEDサブ画素はそれぞれ、OLEDデバイスを流れる電流に比例する割合で、時間とともに輝度を失うことになる。(Vthシフトが1次的な効果であり、Voledシフトが2次的な効果であり、OLED効率の損失が3次的な効果である)したがって、時間とともにディスプレイが薄暗くなり、より多くの電流によって駆動されることになるこれらのサブ画素は、より早く光が弱まるであろう。この示差的な経年劣化(differential aging)によって、好ましくない可視的な焼付けがディスプレイに生ずることになる。ますます多くの放送局がコンテンツ上の固定位置にロゴを連続的に重ね合わせるなどするために、示差的な経年劣化は、今日深刻化する問題である。一般的に、ロゴは、周囲のコンテンツよりも明るいので、ロゴ内の画素は、周囲のコンテンツよりも早く経年劣化し、そのロゴを含まないコンテンツを見るときに可視的なロゴの負電極画の複写が作られる。一般的にロゴは、高い空間周波数のコンテンツを含む(例えばAT&T(登録商標)の球体)ので、1つのサブ画素が、激しく経年劣化する一方、近接するサブ画素は、軽く劣化するだけである。したがって、好ましくない可視的な焼付けを除去するために、画素はそれぞれ、別々に経年劣化を補償しなければならない。

【0007】

〔先行技術〕

これら3つの効果の1つ、又は2つ以上を補償することが公知である。1次的効果であり、印加するバイアスで改善可能であるVthシフト(Mohan et al., "Stability issues in digital circuits in amorphous silicon technology," Electrical and Computer Engineering, 2001, Vol. 1, pp. 583-588)を考慮すると、補償スキーマは、一般的に4つのグループに分割される。画素内の補償、画素内の測定、パネル内の測定、及び逆バイアスである。

【0008】

画素内のVth補償スキーマでは、Vthシフトが生じるときにVthシフトを補償するために、それぞれのサブ画素に付加回路が加えられる。Leeらによる「新たなa−Sia:しきい値電圧の劣化を補償するH TFT画素設計("A New a-Si:H TFT Pixel Design Compensating Threshold Voltage Degradation of TFT and OLED", SID 2004 Digest, pp. 264-274)」は、所望のデータ電圧を印加する前に、サブ画素の記憶キャパシタにそれぞれのサブ画素のVthを記憶することによって、Vthを補償する7トランジスタ‐1キャパシタ(7T1C)サブ画素回路を教示する。このような方法では、Vthシフトは、補償されるが、Voled上昇、又はOLED効率の損失は、補償できない。これらの方法は、従来の2T1C電圧駆動サブ画素回路と比較して、サブ画素がより複雑になり、かつサブ画素回路の大きさを大きくする必要がある。サブ画素がより複雑になることによって、生産量が減少する。微細な形状が必要となるので、組立誤差に対して脆弱になるためである。具体的には、一般的な裏面発光構造において、サブ画素回路全体の大きさが大きくなることにより、消費電力が増加する。発光するそれぞれのサブ画素の割合、すなわち開口率が減少するためである。OLEDの発光は、固定電流における領域に比例するので、開口率が小さいOLEDデバイスは、大きな開口率を有するOLEDと同一の輝度を作り出すために、より大きな電流が必要である。さらに、小さな領域に大きな電流を流すことにより、OLEDデバイスの電流密度が大きくなるので、Voled上昇と、OLED効率の損失とが加速される。

【0009】

画素内測定Vth補償スキームは、それぞれのサブ画素に付加回路を加えて、Vthシフトを示す値を測定することを可能にする。次いでパネル外の回路は、測定結果を処理し、それぞれのサブ画素の駆動を調整して、Vthシフトを補償する。例えば、米国特許出願第2006/0273997(A1)号において、Nathanらは、所与の電圧条件の下での電流、又は所与の電流条件の電圧のいずれか一方として、TFT劣化データを測定することが可能な4トランジスタ画素回路を教示する。米国特許第7199602号において、Naraらは、検査インタコネクトをディスプレイに付加し、かつスイッチングトランジスタに検査インタコネクトを接続するスイッチングトランジスタを、ディスプレイのそれぞれの画素に付加することを教示する。米国特許第6518962号において、Kimuraらには、ディスプレイのそれぞれの画素に補正TFTを付加して、EL劣化を補償することを教示する。これらの方法は、画素内Vth補償スキームの不利な点を共有するが、一部は、Voeldシフト、又はOLED効率の損失をさらに補償できる。

【0010】

逆バイアスVth補償スキームは、逆電圧の一部の形式を使用して、Vthをある開始点に戻す。この方法は、Voled上昇、又はOLED効率の損失を補償できない。例えば、米国特許第7116058号において、Loらは、アクティブマトリクス画素回路の記憶キャパシタの基準電圧を調整して、それぞれのフレームの間の駆動トランジスタを逆バイアスすることを教示する。フレーム内部、又はフレーム間に逆バイアスを印加することによって、可視的なアーチファクトを防止するが、デューティサイクルが減少することによって、ピーク輝度が減少する。逆バイアス方法は、画素内補償方法よりも消費電力の増加を低減しながら、パネルの平均的なVthシフトを補償できるが、より複雑な外部電源供給が必要であり、画素回路、又は信号線を付加する必要がある可能性があり、他の画素よりも光の弱まりが大きい画素を個々に補償できない可能性がある。

【0011】

Voledシフト、及びOLED効率の損失を考慮すると、Arnoldらによる米国特許第6995519号は、OLEDデバイスの経年劣化を補償する方法の一例である。この方法は、デバイスの輝度の全体的な変化は、OLEDエミッタの変化により生じると仮定する。しかしながら、回路の駆動トランジスタをa−Siで形成されるとき、この仮定は有効ではない。使用に伴ってトランジスタのしきい値も変化するためである。このため、Arnoldの方法は、トランジスタが経年劣化効果を示す回路においては、サブ画素の経年劣化の完全な補償を提供することはないであろう。また、逆バイアスなどの方法を使用して、a‐Siトランジスタのしきい値電圧シフトを軽減するとき、OLED効率の損失の補償は、逆バイアス効果の適当な追跡/予測、若しくはOLED電圧の変化、又はトランジスタしきい値電圧の変化の直接的な測定なしには、信頼性が低くなる可能性がある。

【0012】

例えば米国特許第6489631号において、Youngらにより教示されるように、補償の他の方法では、それぞれの画素の光出力を直接測定する。この方法は、3つの経年劣化の全ての要因による変化を補償できるが、非常に高精度な外部光センサが必要であるか、又はそれぞれの画素に統合される光センサが必要になる。外部光センサは、デバイスの価格、及び複雑さを付加する一方、統合光センサは、サブ画素がより複雑になり、電子回路の大きさが大きくなるとともに、付随する性能が低下する。

【0013】

現在のVth補償スキームは、欠点を有しないものはなく、Voled上昇、又はOLED効率の損失を補償するものは、ほとんどない。それぞれのサブ画素のVthシフトを補償するものは、パネルの複雑さ、及び生産量の低下の代償として、行われる。したがって、これらの難点を克服して、ELパネルの劣化を補償し、ELディスプレイパネルの全体的な寿命に亘る好ましくない可視的な焼付けを防止するために、補償を改善することへのニーズが引き続き存在する。

【発明の概要】

【課題を解決するための手段】

【0014】

本発明に従って、ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置であって、駆動回路は、駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、駆動トランジスタの第2の供給電極に電気的に接続されるELデバイスとを有し、

a)第1の供給電極、及び第2の供給電極を、異なった時間に流れる電流を測定して、駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変動を示す経年劣化信号を提供する測定回路と、

b)線形コード値を提供する手段と、

c)駆動トランジスタ、及びELデバイスの特性の変動を補償するために、経年劣化信号に応じて、線形コード値を変更する補償器と、

d)駆動トランジスタのゲート電極を駆動するために、変更線形コード値に応じて、アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置を提供する。

【0015】

また、ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する方法であって、駆動回路は、駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、駆動トランジスタの第2の供給電極に電気的に接続されるELデバイスとを有し、

a)第1の供給電極、及び第2の供給電極を、異なった時間に流れる電流を測定して、駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変動を示す経年劣化信号を提供するステップと、

b)線形コード値を提供するステップと、

c)駆動トランジスタ、及びELデバイスの特性の変動を補償するために、経年劣化信号に応じて、線形コード値を変更するステップと、

d)駆動トランジスタのゲート電極を駆動するために、変更線形コード値に応じて、アナログ駆動トランジスタ制御信号を作り出すステップと、

を有する方法を提供する。

【0016】

さらに、ELパネルの複数のELサブ画素の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置であって、第1の電圧源と、第2の電圧源と、複数のELサブ画素とをELパネルに有し、駆動回路のELデバイスは、それぞれのELサブ画素のELデバイスに電流を印加し、駆動回路はそれぞれ、第1の電圧源に電気的に接続される第1の供給電極と、ELデバイスの第1の電極に電気的に接続される第2の供給電極とを有する駆動トランジスタを有し、ELデバイスはそれぞれ、第2の電圧源に電気的に接続される第2の電極を有し、改良点は、

a)第1の電圧源、及び第2の電圧源を、異なった時間に流れる電流を測定して、サブ画素の駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変動を示すそれぞれのサブ画素の経年劣化信号を提供する測定回路と、

b)それぞれのサブ画素の線形コード値を提供する手段と、

c)それぞれのサブ画素の駆動トランジスタ、及びELデバイスの特性の変動を補償するために、経年劣化信号に応じて、線形コード値を変更する補償器と、

d)駆動トランジスタのゲート電極を駆動するために、変更線形コード値に応じて、アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置を提供する。

【発明の効果】

【0017】

本発明は、アナログ駆動トランジスタ制御信号を提供する効果的な方法を提供する。補償を実行するために、1つの測定のみが必要である。いずれのアクティブマトリクスのバックプレーンに提供可能である。制御信号の補償は、補償を線形電圧領域にできるように、ルックアップテーブル(LUT)を使用して、非線形から線形に信号を変更することによって、単純化されている。本発明は、複雑な画素回路、又は外部の測定デバイスを必要とせずに、Vthシフト、Voledシフト、及びOLED効率の損失を補償する。本発明は、サブ画素の開口率を減少させない。本発明は、パネルの通常動作には影響を与えない。

【図面の簡単な説明】

【0018】

【図1】本発明を実施する制御システムのブロックを概略的に示す図である。

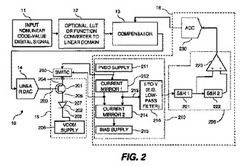

【図2】図1のブロックのより詳細な形の回路を概略的に示す図である。

【図3】典型的なOLEDパネルを概略的に示す図である。

【図4A】理想的な条件の下で図2の測定回路を動作させるタイミングを概略的に示す図である。

【図4B】サブ画素の自己発熱によるエラーを有する図2の測定回路を動作させるタイミングを概略的に示す図である。

【図5A】経年劣化していないサブ画素、及び経年劣化し、Vthシフトを示すサブ画素のI−V特性曲線を示す図である。

【図5B】経年劣化していないサブ画素、及び経年劣化し、Vthシフトと、Voledシフトとを示すサブ画素のI−V特性曲線を示す図である。

【図6A】図1の補償器の上位レベルのデータフローを概略的に示す図である。

【図6B】補償器の詳細なデータフローの(2つの部分の)第1の部分を概略的に示す図である。

【図6C】補償器の詳細なデータフローの(2つの部分の)第2の部分を概略的に示す図である。

【図7】領域変換ユニットと、補償器の効果を示すジョーンズダイアグラムである。

【図8】補償測定の頻度を時間とともに表すプロットを示す図である。

【図9】パーセント電流の関数としてパーセント効率を表すプロットを示す図である。

【図10】本発明に従う駆動回路の詳細な回路を示す図である。

【発明を実施するための形態】

【0019】

本発明の上述の目的、特徴、及び利点、並びに他の目的、特徴、及び利点は、以下の説明、及び図面を併せて理解するときに、より明確になるであろう。ここで、図面に共通する同一の特徴を示すために、可能な限り同一の符号が使用されている。

【0020】

本発明は、アクティブマトリクスELディスプレイパネルの駆動トランジスタ、及びELデバイスの劣化を補償する。1つの実施形態において、アクティブマトリクスOLEDパネルの全てのサブ画素のVthシフト、Voledシフト、及びOLED効率の損失を補償する。パネルは、1つ、又は2つ以上のサブ画素をそれぞれが備える複数の画素を有する。例えば、それぞれの画素は、赤色のサブ画素、緑色のサブ画素、及び青色のサブ画素を有してもよい。それぞれのサブ画素は、光を発光するELデバイスと、周囲の電子機器とを有する。サブ画素は、パネルの最も小さなアドレス可能な素子である。ELデバイスは、OLEDデバイスにできる。

【0021】

以下の議論において、まずシステム全体を考察する。次いで、サブ画素の電気的な詳細に進んだ後に、1つのサブ画素の測定、及び複数のサブ画素を測定するタイミングの電気的な詳細に進む。次に、補償器が、測定結果を使用する方法を対象とする。最後に、本システムが、消費者製品などにおいて工場から寿命末期まで、1つの実施形態において実施される方法が説明される。

【0022】

〔概説〕

図1において、本発明に係る全体的なシステム10のブロックを概略的に示す。非線形入力信号11は、ELパネル上に数あるELサブ画素の1つであるELサブ画素のELデバイスからの特定の光強度を指令する。本信号11は、ビデオデコーダ、画像処理経路、又は他の信号源から生成されてもよく、デジタル、又はアナログでよく、非線形コード化され、又は線形コード化されてもよい。例えば、非線形入力信号は、sRGBコード値ステップ(sRGB code value step)74、又はNTSC輝度電圧ステップ(MTSC luma voltage step)75にしてもよい。どのようなソース、及びフォーマットであっても、好適には、信号は、コンバータ12によってデジタルフォーマットに変換できるとともに、線形電圧などの線形領域に変換できる。これは、以下の「領域間共通処理、及びビット深度(Cross-domain processing, and bit depth)」において、さらに説明されることになるであろう。ルックアップテーブル、又はLCDソースに類似する機能は、この変換を実行できる。変換の結果は、指令駆動電圧(commanded drive voltage)を示すことができる線形コード値にすることになるであろう。

【0023】

補償器13は、ELサブ画素からの特定の指令光強度に対応できる線形コード値を取り込む。ELサブ画素の駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの変動は、ELサブ画素が、線形コード値に対応する指令光強度を概して作り出さなくなるであろうことをいう。補償器13は、変更線形コード値を出力することにより、ELサブ画素が、指令の強度を作り出すことになるであろう。補償器の動作は、以下の「実施」において、さらに説明されることになるであろう。

【0024】

補償器13からの変更線形コード値は、線形ソースドライバ14に移動する。線形ソースドライバ14は、デジタル‐アナログコンバータにできる。線形ソースドライバ14は、変更線形コード値に対応する電圧にできるアナログ駆動トランジスタ制御信号を作り出す。線形ソースドライバ14は、線形になるように設計されるソースドライバにでき、若しくは近似的に線形な出力を作り出すように設定されるガンマ電圧を有する従来のLCDソースドライバ、又はOLEDソースドライバにできる。後者の場合、線形性からのずれは、結果の質に影響を及ぼすことになるであろう。また、この線形ソースドライバ14は、同一出願人による国際公報2005/116971 A1において、Kawabeが教示するように、時分割(デジタル駆動)ソースドライバにしてもよい。この場合、ソースドライバからのアナログ電圧は、補償器の出力信号に依存する時間量の光出力を指令する所定のレベルに設定される。それに対して、従来の線形ソースドライバは、(一般に全体フレームの)固定された時間量の補償器の出力信号に依存するレベルのアナログ電圧を提供する。線形ソースドライバは、1つ、又は2つ以上のアナログ駆動トランジスタ制御信号を同時に出力できる。本発明に係る1つの実施形態において、ELパネルは、1つ、又は2つ以上のマイクロチップを備える線形ソースドライバを有し、マイクロチップはそれぞれ、ELパネルのELサブ画素の列の数に等しい数のアナログ駆動トランジスタ制御信号を同時に作り出すように、1つ、又は2つ以上のアナログ駆動トランジスタ制御信号を出力できる。

【0025】

線形ソースドライバ14が作り出すアナログ駆動トランジスタ制御信号は、EL駆動回路15に提供されるが、ELサブ画素に提供してもよい。この回路は、以下の「ディスプレイ素子の説明」において説明されることになるように、駆動トランジスタ、及びELデバイスを有する。アナログ電圧が駆動トランジスタのゲート電極に提供されるとき、駆動トランジスタ、及びELデバイスを電流が流れることによって、ELデバイスが光を発光する。一般に、ELデバイスを流れる電流と、出力デバイスの輝度との間には、線形の関係があり、駆動トランジスタに印加される電圧と、ELデバイスを流れる電流との間には、非線形の関係がある。したがって、ELデバイスがフレームの間に発光する光の合計量は、線形ソースデバイス14の電圧の非線形関数にできる。

【0026】

以下の「データ収集」においてさらに説明されることになるように、EL駆動回路を流れる電流は、特定の駆動条件の下で電流測定回路16によって測定される。ELサブ画素の測定電流は、指令駆動信号を調整するために必要な情報を補償器に提供する。これは、以下の「アルゴリズム」において、さらに説明されることになるであろう。

【0027】

以下の「動作シーケンス」において、さらに説明されることになるように、本システムは、ELパネルの動作寿命に亘りELパネルの駆動トランジスタ、及びELデバイスの変動を補償できる。

【0028】

〔ディスプレイ素子の説明〕

図10において、OLEDデバイスなどのELデバイスに電流を印加する駆動回路15を示す。駆動回路15は、アモルファスシリコン・トランジスタにしてもよい駆動トランジスタ201と、ELデバイス202と、正電極にできる第1の電圧源211(「PVDD」)と、負電極にできる第2の電極206(「Vcom」)とを有する。ELデバイス202は、第1の電極207と第2の電極208とを有する。駆動トランジスタは、ゲート電極203と、駆動トランジスタのドレインにできる第1の供給電極204と、駆動トランジスタのソースにできる第2の供給電極205とを有する。アナログ駆動トランジスタ制御信号は、随意的には選択トランジスタ36を介して、ゲート電極203に提供できる。アナログ駆動トランジスタ制御信号は、記憶キャパシタ1002に記憶できる。第1の供給電極204は、第1の電圧源211に電気的に接続される。第2の供給電極は、ELデバイス202の第1の電極207に電気的に接続される。ELデバイスの第2の電極208は、第2の電圧源206に電気的に接続される。駆動トランジスタ201、及びELデバイス202は、随意的な選択トランジスタ36と、記憶キャパシタ1002とともに、ELパネルに典型的に存在する駆動回路の一部であるELサブ画素を構成する。典型的には、電力供給は、ELパネルの外に配置される。電気的な接続は、スイッチ、母線、導電性トランジスタ、若しくは電流経路を提供する能力を有する他のデバイス、又は構造にできる。

【0029】

本発明に係る1つの実施形態において、第1の供給電極204は、PVDD母線1011を介して第1の電圧源211に電気的に接続され、第2の電極208は、薄板カソード1012を介して第2の電圧源206に電気的に接続され、アナログ駆動トランジスタ制御信号は、線形ソースドライバ14がゲート電極203に提供する。

【0030】

本発明は、アナログ駆動トランジスタ制御信号を駆動トランジスタのゲート電極に提供する。駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変化を補償する制御信号を提供するためには、その変動が既知でなければならない。変動は、駆動トランジスタの第1の供給電極、及び第2の供給電極を異なった時間に流れる電流を測定して、変動を表すアナログ信号を提供することによって、決定される。これは、以下に「アルゴリズム」において、詳細に説明されることになるであろう。経年劣化信号は、デジタル、又はアナログにできる。経年劣化信号は、電圧、又は電流で表すことができる。

【0031】

図2において、図1に示す非線形入力信号11、コンバータ12、補償器13、及び線形ソースドライバ14を含む全体的なシステムとの関連で駆動回路15を示す。上述のように、駆動トランジスタ201は、ゲート電極203、第1の供給電極204、及び第2の供給電極205を有する。ELデバイス202は、第1の電極207、及び第2の電極208を有する。システムは、電圧源211、及び206を有する。なお、第1の電圧源211は、以下のカレントミラーユニットの説明を明確にするために、駆動回路15の外に示される。

【0032】

一般的にFETである駆動トランジスタ201、及びELデバイス202の動作は、本質的に同一の電流が、第1の供給電極204と、第2の供給電極205と、EL電極207、及び208とを介して、第1の電圧源211から第2の電圧源206に流れるものである。したがって、電流は、このつながりのいずれかの点で測定できる。第1の電圧源211において、ELパネルの外で電流を測定して、ELサブ画素の複雑さを低減できる。1つの実施形態において、本発明は、カレントミラーユニット210と、相関2重サンプルユニット220と、アナログ‐デジタルコンバータ230とを使用する。これらは、以下に「データ補正」において、詳細に説明されることになるであろう。

【0033】

図2に示す駆動回路15は、Nチャネル駆動トランジスタ構造であり、かつ非反転EL構造である。この場合、ELデバイス202は、トランジスタ201のソース205に接続され、ゲート電極203の電圧を高くすると、光出力を大きくするように指令され、電圧源211は、第2の電圧源206よりも高電位であるので、電流は、211から206に流れる。しかしながら、本発明は、Pチャネル駆動トランジスタ、又はNチャネル駆動トランジスタ、及び非反転ELデバイス、反転ELデバイスのいずれの組み合わせに適用可能である。また本発明は、LTPS駆動トランジスタ、又はa−Si駆動トランジスタに適用可能である。

【0034】

〔データ補正〕

〔ハードウェア〕

さらに図2を参照すると、パネル上の特別な電子機器に拠ることなしに、それぞれのELサブ画素の電流を測定するために、本発明は、カレントミラーユニット210と、相関2重サンプル(CDS)ユニット220と、アナログ‐デジタルコンバータ(ADC)230とを有する測定回路16を採用する。

【0035】

カレントミラーユニット210は、電圧源211に取り付けられるが、供給211、供給206、又はELデバイス、並びに駆動トランジスタの第1の供給電極、及び第2の供給電極を通る電流経路の他のいずれかに取り付けることができる。これは、ELデバイスに光を発光させる駆動電流の経路である。第1のカレントミラー212は、スイッチ200を介してEL駆動回路15に駆動電流を供給し、出力213にミラー電流を作り出す。ミラー電流は、駆動電流と等しくできる。一般的に、ミラー電流は、駆動電流の関数にできる。例えば、ミラー電流は、複数の駆動電流にして、付加的な測定システム利得を提供できる。第2のカレントミラー214と、バイアス供給215は、バイアス電流を第1のカレントミラー212に印加して、測定結果が回路の寄生インピーダンスに影響されないように、第1のカレントミラーにおける電圧変動を低減する。また、この回路は、測定回路の電流引き込みにより、カレントミラーにおける電圧が変化することによって、測定されるELサブ画素を流れる電流の変化を低減する。有利には、これは、電流に依存する駆動トランジスタ、端末における電圧を変化させる可能性がある簡素な感知抵抗などの他の電流測定の選択肢よりも、信号対雑音比が改良される。最終的には、電流‐電圧(I‐V)コンバータ216は、さらなる処理のために、第1のカレントミラーのミラー電流を電圧信号に変換する。I‐Vコンバータ216は、トランスインピーダンス増幅器、又はローパスフィルタを有してもよい。単一のELサブ画素において、I‐Vコンバータの出力は、そのサブ画素の経年劣化信号にできる。以下に説明されるように、複数のサブ画素の測定では、測定回路は、経年劣化信号を作り出す電圧信号に応答する回路をさらに有してもよい。先に説明したように、駆動トランジスタ、及びELデバイスの特性が、駆動トランジスタ、及びELデバイスの動作によって時間とともに変化すると、Vth、及びVoledは、変化することになるであろう。この結果として、測定電流、すなわち経年劣化信号は、これらの変動に応じて変化することになるであろう。これは、以下に「アルゴリズム」において、さらに説明されることになるであろう。

【0036】

1つの実施形態において、第1の電圧源211は、+15VDCの電位を有し、第2の電力供給206は、−5VDCの電位を有し、バイアス供給215は、−16VDCの電位を有することができる。バイアス供給215の電位は、全ての測定電流のレベルにおいて、安定したバイアス電流を提供するように、第1の電圧源211の電位に基づいて選択できる。

【0037】

ELサブ画素が測定されないとき、カレントミラーは、継電器、又はFETにできるスイッチ200によって、パネルから電気的な接続を切断することができる。スイッチは、駆動トランジスタ201の第1の電極、及び第2の電極を流れる駆動電流の流れと測定回路との電気的な接続を選択的にできる。測定の間、スイッチ200は、第1の電圧源211を第1のカレントミラー212に電気的に接続して、測定を可能にする。通常動作の間、スイッチ200は、第1の電圧源211を第1のカレントミラーではなく、第1の供給電極に直接接続することによって、駆動電流の流れから測定回路を除去する。このため、測定回路は、パネルの通常動作には影響を与えることはない。また有利には、カレントミラー212、及び214のトランジスタなどの測定回路の構成素子は、動作電流でなく、測定電流のみのための大きさにできる。一般的に、通常動作は、測定よりも非常に大きな電流を引き出すので、これによって、測定回路の大きさ、及び価格の実質的な縮減が可能になる。

【0038】

〔サンプリング〕

カレントミラーユニット210は、1つのELサブ画素の回路の測定が可能である。複数のサブ画素の電流を測定するためには、1つの実施形態において、本発明は、標準的なOLEDソースドライバとともに使用可能なタイミングスキームを有する相関2重サンプリングを使用する。

【0039】

図3を参照すると、本発明において有用なELパネル30は、3つの主要な構成要素を有する。すなわち、列線32a、32b、及び32cを駆動するソースドライバ31と、行線34a、34b、及び34cを駆動するゲートドライブ33と、サブ画素マトリクス35とである。本発明に係る1つの実施形態では、ソースドライバ31は、線形ソースドライバ14にできる。なお、ソースドライバと、ゲートドライバとは、1つ、又は2つ以上のマイクロチップを有してもよい。なおまた、用語「行」、及び「列」は、ELパネルのいずれの特定の方向をも示唆しない。サブ画素のマトリクスは、概して同一であり、かつ概して行、及び列のアレイに配列される複数のELサブ画素を有する。ELサブ画素はそれぞれ、ELデバイス202を備える駆動回路15を有する。駆動回路はそれぞれ、ELデバイスに電流を印加し、選択トランジスタ36と、駆動トランジスタ201とを有する。スイッチとして動作する選択トランジスタ36は、行線、及び列線を駆動トランジスタ201に電気的に接続する。選択トランジスタのゲートは、適当な行線34に電気的に接続され、選択トランジスタのソース電極、及びドレイン電極は、1つが、適当な列線32に電気的に接続され、1つが、駆動トランジスタのゲート電極に接続される。ソースが、列線、又は駆動トランジスタのゲート電極のいずれに接続されても、選択信号の動作には影響しない。本発明の1つの実施形態において、サブ画素マトリクス35のELデバイス202はそれぞれ、OLEDデバイスにしてもよく、サブ画素マトリクス35の駆動トランジスタは、アモルファスシリコン・トランジスタにしてもよい。

【0040】

また、ELパネルは、第1の電圧源211と、第2の電圧源206とを有する。図10を参照すると、電流は、駆動トランジスタの第1の供給電極204と、第1の電圧源211とを電気的に接続するPVDD母線1011などによって、駆動トランジスタ201に供給できる。ELデバイス202の第2の電極208と、第2の電圧源206とを電気的に接続する薄板カソード1012は、電流経路を完成することができる。明確にするために、図3を再び参照すると、電圧源211、及び206が、図3に示される。ここで、供給にサブ画素を接続する様々なスキーマとともに本発明を採用するように、電圧源211、及び206は、それぞれのサブ画素に接続できる。それぞれの駆動トランジスタの第2の供給電極205は、対応するELデバイスの第1の電極207に電気的に接続できる。

【0041】

図2に示すように、ELパネルは、第1の電源供給211に電気的に接続される測定回路16を有してもよい。この回路は、第1の電圧源と、第2の電圧源とを流れる電流を測定する。これは、キルヒホッフの法則と同様である。

【0042】

本パネルの典型的な動作において、ソースドライバ31は、列線32に適当なアナログ駆動トランジスタ制御信号を駆動する。次いで、ゲートドライバ33は、第1の行線34aを活性化し、適当な制御信号が選択トランジスタ36を介して、適当な駆動トランジスタのゲート電極に通されて、これらのトランジスタに取り付けられたELデバイス202に電流を印加する。次いで、ゲートドライバは、第1の行線34aを非活性にして、選択トランジスタを通った値を、他の行の制御信号が破損することを防止する。ソースドライバは、列線の次の行の制御信号を駆動し、ゲートドライバは、次の行34bを活性化する。この処理は、全ての行で繰り返す。このように、パネル上の全てのサブ画素は、1度に1つの行に適当な制御信号を受信する。行時間(row time)は、1つの行線(34aなど)を活性化する時間と、次(34bなど)を活性化する時間との間の時間である。行時間は、一般的に全ての行で一定である。

【0043】

有利には、本発明に従って、この行ステップを使用して、1度に1つのサブ画素のみを活性化し、列を下方に動かす。図3を参照して、列32aのみを駆動し、全てのサブ画素をオフにして開始すると仮定する。列線32aは、High電圧などのアナログ駆動トランジスタ制御信号を有して、取り付けられるサブ画素に光を発光させることになるであろう。他の全ての列線32b..32cは、Low電圧などの制御信号を有して、取り付けられるサブ画素に光を発光させないであろう。全てのサブ画素がオフなので、パネルは、電流を引き込まない(しかし、以下の「ノイズのソース」を参照のこと)。上部の行から開始して、行は、時間軸の目盛によって示される点で活性化する。行が活性化すると、列32aに取り付けられるサブ画素が動作する。そして、パネルが引き出す総電流が上昇する。ここで図4aを参照すると、サブ画素が活性化し(行線34aなど)、測定回路16によって、その電流が測定される。具体的には、測定されるものは、上述のように第1の電圧源、及び第2の電圧源を介する電流を表す電流測定回路からの電圧信号である。明確にするために、電流を表す電圧信号の測定を「電流測定」と称する。時間2において、次のサブ画素が活性化し(列線34bなど)、電流42が測定される。電流42は、第1のサブ画素からの電流と、第2のサブ画素からの電流との和である。第2の測定42と、第1の測定41との間の差異は、第2のサブ画素により引き出される電流である。このように、処理は、それぞれのサブ画素の電流を測定して、第1の列を下って進む。次いで、第2の列を測定し、第3、第4とパネルの残りについて測定する。なお、測定(41、42など)はそれぞれ、サブ画素を活性化した後にできるだけ早く行われる。理想的な状況では、測定はそれぞれ、次のサブ画素が活性化される前のいずれかの時間に行うことができるが、以下で説明されるように、サブ画素が活性化された後に迅速に測定することによって、自己発熱効果によるエラーを除去する可能性がある。この方法によって、測定結果は、サブ画素のセトリング・タイム(settling time)で許容されることになるであろう範囲で、迅速に行うことが可能になる。

【0044】

相関2重サンプリングユニット220は、測定電流をサンプリングして、経年劣化信号を作り出す。ハードウェアにおいて、図2におけるカレントミラーユニット210からの対応電圧信号を、サンプル及び保持ユニット(sample-and-hold unit)221、及び222にラッチすることによって、電流は、測定される。電圧信号は、I‐Vコンバータ216によって作り出すことができる。差動増幅器223は、連続するサブ画素の測定結果の間の差異をとる。サンプル及び保持ユニット221の出力は、差動増幅器223のプラス端子に電気的に接続され、サンプル及び保持ユニット222の出力は、差動増幅器223のマイナス端子に電気的に接続される。例えば、電流41を測定するときは、測定は、サンプル及び保持ユニット221にラッチされる。次いで、電流42を測定する(ユニット221にラッチされる)前に、ユニット221の出力は、第2のサンプル及び保持ユニット222にラッチされる。次いで電流42を、測定する。これにより、電流41は、ユニット222に保持され、電流42は、ユニット221に保持される。したがって、ユニット221の値からユニット222の値を減ずる差動増幅器の出力は、(電圧信号で示す)電流42から(電圧信号で示す)電流41を減ずるもの、すなわち差異43である。43などのそれぞれの電流の差異は、対応するサブ画素の経年劣化信号にできる。例えば、電流の差異43は、行線34bと、列線32aとに取り付けされたサブ画素の経年劣化信号にできる。このように、行を下り、列を横切ることにより、それぞれのサブ画素の測定と、それぞれのサブ画素が提供する経年劣化信号を測定できる。

【0045】

〔ノイズ源〕

実際には、電流波形は、きれいなステップではなく、波形が安定するのを待ってからようやく測定できる。それぞれのサブ画素を複数測定して、互いに平均化できる。この測定は、次のサブ画素に進む前に連続的に行うことができる。また、これは、別々に測定でき、パネルのサブ画素はそれぞれ、それぞれの経路で測定される。電圧源206と、211との間の容量は、セトリング・タイムになる可能性がある。通常の動作で見られるように、この容量は、内在するキャパシタ、又は外部のキャパシタによって提供される。有利には、測定中に外部のキャパシタとの電気的な結合を切断するために使用することができるスイッチが提供される。これにより、セトリング・タイムを削減することになるであろう。

【0046】

全ての電力供給は、可能な限りノイズがないように保つべきである。いずれかの電力供給のノイズは、電流測定に影響を与えることになるであろう。例えば、行を非活性化するために使用する電源供給(多くの場合VGL、又はVoffと称され、一般的に−8VDC近辺である)のノイズは、選択トランジスタを介して駆動トランジスタに容量的に結合され、電流に影響を与えるので、電流測定のノイズが多くなる。パネルが、分割供給面(split supply plane)などの複数の電源供給領域を有する場合は、これらの領域は、並列に測定できる。この測定では、領域間のノイズを分離し、測定時間を削減できる。

【0047】

1つの主要なノイズ源は、ソースドライバ自体である可能性がある。ソースドライバがスイッチングするときはいつでも、過渡ノイズは、電力供給面、及び個々のサブ画素に結合して、測定ノイズを生じる可能性がある。このノイズを削減するために、ソースドライバからの制御信号は、列を下る間、一定に保つことができる。例えば、RGBストライプパネル上の赤色のサブ画素の列を測定するとき、その行のソースドライバに供給される赤色コード値は、全ての列で一定にできる。これによって、ソースドライバの過渡ノイズを除去できる。

【0048】

ソースドライバは、現在の列(32aなど)の活性化から次の列(32bなど)の活性化に変更しなければならないため、ソースドライバの過渡は、列の最初、及び列の最後において、回避することは不可能である。この結果、いずれかの列の第1のサブ画素、及び続く1つ、又は2つ以上のサブ画素の測定は、過渡によるノイズの影響を受ける。1つの実施形態では、ELパネルは、可視される行の上部、又は下部に、ユーザに可視されない追加の行を有してもよい。ソースドライバの過渡が追加の行においてのみ生じるように十分な追加の行を配置し、可視的なサブ画素の測定が影響を受けないようにすることができる。他の実施形態において、行の開始におけるソースドライバの過渡と、その列の第1の行の測定との間、及びその列の最後の行の測定と、行の最後におけるソースドライバの過渡との間に、遅延を挿入することができる。

【0049】

パネルは、全てのサブ画素がオフのときでさえも、いくらかの電流を引き出す可能性がある。この「暗電流」は、遮断時の駆動トランジスタのリークによるものである可能性がある。暗電流は、DCバイアスノイズを測定電流に付加する。図4において、点49で示すように、これは、第1のサブ画素を活性化する前に、全てのサブ画素をオフにして測定することによって、除去できる。この場合、サブ画素1により引き出される電流は、単に測定41ではなく、測定41から測定49を減じたものになるであろう。

【0050】

〔電流の安定性〕

これまでの説明では、サブ画素がオンし、安定すると、残りの列が終わるまで電流が維持されると仮定された。この仮定を崩す可能性がある2つの効果は、記憶容量リーク効果と、内部サブ画素効果(within-subpixel effects)である。

【0051】

公知の技術である記憶容量は、すべてのサブ画素の一部にでき、駆動トランジスタのゲートと、基準電圧との間を電気的に接続できる。サブ画素の選択トランジスタのリーク電流は、記憶容量の電荷を徐々に抜き取る。駆動トランジスタのゲート電圧が変化して、電流が引き出される。また、サブ画素に取り付けられる列線が時間とともに値が変化している場合、AC素子を有するので、選択トランジスタの寄生容量を介して、記憶容量に結合する可能性がある。記憶容量の値が変化して、電流がサブ画素によって引き出される。

【0052】

記憶容量の値が安定しても、内部サブ画素効果は、測定を破損する可能性がある。共通の内部サブ画素効果は、サブ画素が引き出す電流を時間とともに変化させる可能性があるサブ画素の自己発熱である。a−Si TFTのドリフト移動度は、温度の関数である。温度が上昇すると、移動度が大きくなる(Kagan & Andry, op. cit., sec. 2.2.2, pp. 42−43)。電流が、駆動トランジスタを介して流れるとき、駆動トランジスタ、及びELデバイスの電力損失により、サブ画素が加熱されるので、トランジスタの温度が上昇するとともに、移動度が大きくなる。また、加熱によりVoledが下がる。OLEDが駆動トランジスタのソース端子に取り付けられる場合は、これによって、駆動トランジスタのVgsが上昇する可能性がある。これらの効果によって、トランジスタを流れる電流量が増加する。通常動作の下では、パネルが表示する画像の平均的な容量に基づく平均の温度に安定するので、自己発熱は、重要な効果ではない可能性がある。しかしながら、サブ画素電流を測定するとき、自己発熱は、測定を破損する可能性がある。図4bを参照すると、測定41は、サブ画素1を活性化した後、可能な限り早く行われる。この場合、サブ画素1の自己発熱は、測定に影響を与えない。しかしながら、測定41と、測定42との間の時間において、サブ画素1は、自己発熱して、量421だけ電流が増加するであろう。したがって、サブ画素の電流を表す計算上の差異43は、誤っているであろう。量421によって、過度に大きくなっているであろう。量421は、行時間当たりのサブ画素の電流の上昇である。

【0053】

自己発熱効果、及び同様なノイズ特性を作り出す他の内部サブ画素効果を補正するために、自己発熱を、特性化し、それぞれのサブ画素の既知の自己発熱要素を取り除くことができる。一般的にそれぞれのサブ画素は、それぞれの行時間の間に同一量の電流が上昇する。このため、連続するそれぞれのサブ画素において、活性化する全てのサブ画素の自己発熱を、取り除くことができる。例えば、サブ画素3の電流424を得るために、測定423は、要素421の2倍である自己発熱要素422を減少できる。要素421は、サブ画素当たりの要素であり、既に活性化している2つのサブ画素を乗じる。自己発熱は、何十、又は百もの行時間において、1つのサブ画素をオンすることによって特性化され、オンになっている間に定期的に電流を測定できる。時間に対応する電流の平均的な傾きは、1つの行時間で乗じることによって、行時間421当たりのサブ画素の上昇を計算できる。

【0054】

自己発熱、及び電力損失によるエラーは、測定基準ゲート電圧を低く選択することにより、低減可能である(図5aの510)が、電圧を高くすることによって、信号対雑音比が改善される。測定基準ゲート電圧は、これらの要因の平衡を保つように、パネル配置ごとに選択できる。

【0055】

〔アルゴリズム〕

図5aを参照すると、I−V曲線501は、経年劣化前のサブ画素の測定特性である。I−V曲線502は、経年劣化後のサブ画素の測定特性である。曲線501、及び502は、異なる電流レベルにおける同一の電圧差503、504、505、及び506で示される、主として水平方向のシフトによって分離される。すなわち、経年劣化の1次的な効果は、一定量ゲート電圧軸上でI−V曲線がシフトすることである。MOSFETの飽和領域で維持されるとき、これは、式Id=K(Vgs−Vth)2である(Lurch, N.Fundamentals of electronics, 2e. New York: John Wiley & Sons, 1971, pg. 110)。駆動トランジスタが動作すると、Vthは増加する。Vthが増加すると、Vgsが、それに応じて増加して、Idを一定に維持しなければならない。したがって、Vthが増加するときに、Vgsを一定にすると、Idが低くなる。

【0056】

図5aの例では、測定基準ゲート電圧510において、経年劣化していないサブ画素は、点511で表される電流を作り出す。電流は、そのサブ画素の経年劣化信号である。しかしながら、経年劣化したサブ画素は、そのゲート電圧において、点512aで表される、より低い電流量を作り出す。点511、及び521aは、異なる時間において行われる同一サブ画素の測定結果にできる。例えば、点511は、製造時の測定結果にでき、点512aは、顧客がいくらか使用した後の測定結果にできる。点512aで表される電流は、経年劣化していないサブ画素が電圧513(点512b)で駆動されるときに作り出されるであろう。このため、電圧シフトΔVth514は、電圧510、及び513の間の差異の電圧として計算される。このように、電圧シフト514は、経年劣化していな曲線に経年劣化した曲線を戻すために必要なシフトである。この例では、ΔVth514は、2V弱である。次いで、Vthシフトを補償し、経年劣化していないサブ画素と同一の電流で経年劣化したサブ画素を駆動するために、電圧差514は、指令された全ての駆動電圧(線形コード電圧)に加える。また、さらなる処理のために、パーセント電流(percent current)は、電流512aを電流511で除して計算される。それ故に、経年劣化していないサブ画素は、100%電流を有することになるであろう。パーセント電流は、本発明に従ういくつかのアルゴリズムで使用される。外部環境によって生じる可能性がある負の電流読み出し511は、0に留めるか、又は無視することができる。なお、パーセント電流は、常に測定基準ゲート電圧510において計算される。

【0057】

一般的に、経年劣化したサブ画素の電流は、経年劣化していないサブ画素の電流よりも大きくなる可能性があり、又は小さくなる可能性がある。例えば、温度が高いと、より多くの電流が流れるために、高温度環境下のほとんど経年劣化していないサブ画素は、低温度環境下の経年劣化していないサブ画素よりも多くの電流を引き出す可能性がある。本発明に係る補償アルゴリズムは、いずれの場合も取り扱うことができる。すなわち、ΔVth514は、正にでき、又は負にできる(経年劣化していない画素においては、ゼロにできる)。同様に、パーセント電流は、100%よりも大きくでき、又は小さくできる(経年劣化していない画素においては、正確に100%にできる)。

【0058】

Vthシフトによる電圧差は、全ての電流で同一であるので、I−V曲線のいずれか単一の点を測定して、この差を決定できる。1つの実施形態では、有利には、測定は、高いゲート電圧で行われ、測定の信号対雑音比が増加するが、曲線の何れのゲート電圧を使用できる。

【0059】

Voledシフトは、経年劣化の2次的な効果である。ELデバイスが動作すると、Voledがシフトして、I−V曲線が、もはや経年劣化していない曲線の単なるシフトではなくなる。これは、Voledが電流に非線形に上昇するためである。これにより、低電流と異なるように高電流にVoledが影響を与えることになるであろう。この効果によって、I−V曲線がシフトするとともに、水平方向に広げられる。Voledシフトを補償するために、2つの測定を行い、曲線が広がった大きさを決定できる。又は負荷の下でのOLEDの典型的なVoledを特性化して、開ループの方法でVoledの寄与を推定することが可能である。双方は、容認可能な結果を作り出すことができる。片対数目盛のI−V曲線である図5bを参照すると、要素550は、Vthシフトによるものであり、要素552は、Voledシフトによるものである。Voledシフトは、測定装置を搭載したOLEDサブ画素を、期間が長い時間の標準的な入力信号によって駆動すること、及びVthと、Voledを定期的に測定することによって、特性化できる。2つの測定は、OLEDと、トランジスタとの間の測定装置を搭載したサブ画素にプローブ点を提供することによって、独立に行うことができる。この特性を使用して、パーセント電流は、Vthシフトのみでなく、適当なΔVth、及びVoledにマッピングできる。

【0060】

OLED効率の損失は、3次的な経年劣化効果である。OLEDが経年劣化すると、効率が低下し、同一の電流量では、同一の光量をもはや作り出すことができない。光学センサ、又は付加的な電子機器を要せずにこれを補償するために、Vthシフトの関数としてOLED効率の損失を特性化して、先のレベルの光出力に戻すために必要な追加電流量を推定することが可能である。OLED効率の損失は、測定装置を搭載したOLEDサブ画素を、期間が長い時間の標準的な入力信号によって駆動すること、及びVthと、Voledと、Ioledとを様々な駆動レベルで定期的に測定することによって、特性化できる。効率は、Ioled/Voledとして計算でき、この計算は、Vth、又はパーセント電流に相関してもよい。なお、Vthシフトは、簡単に元に戻されるが、OLED効率はそうではないので、この特性は、Vthが順方向であるときに、最も効率的な結果が得られる。Vthシフトが逆方向である場合、OLED効率の損失と、Vthシフトとの相関は、複雑になる。さらなる処理のために、上述のパーセント電流の計算に類似するパーセント効率は、経年劣化した効率を新しい効率で除することにより計算できる。

【0061】

図9を参照して、実験データへの90などの直線の当てはめ(linear fit)とともに、様々な駆動レベルにおけるパーセント効率の実験プロットを、パーセント電流の関数として示す。プロットが示すように、所与のいずれの駆動レベルにおいて、効率は、パーセント電流に線形の関連になる。この線形モデルにより、効果的な開ループ効率補償が可能になる。同様な結果が「ポリマー発光ダイオードにおける寿命、及び劣化効果("Lifetime and degradation effects in polymer light-emitting diodes," J. App. Phys. 85.4 (1999): 2441-2447)」において、具体的には2445ページの図12で示されるように、Parkerらにより報告される。またParkerらは、単一の機構が、効率の損失(輝度の減少)、及びVoled上昇(電圧増加)の双方に関与することを提案する。

【0062】

Vth、及びVoledを含む駆動トランジスタ、及びELデバイスの特性は、駆動トランジスタ、及びELデバイスの時間に伴う動作によって、時間とともに変化する。パーセント電流は、これらの変動を表す経年劣化信号として使用でき、これらの変動を補償することを可能にする。

【0063】

このアルゴリズムは、OLEDに関連して説明されているが、当業者には明らかなように、他のELデバイスもまた、これらの分析を適用して補償できる。

【0064】

〔実施〕

図6aを参照すると、線形コード値が指令駆動電圧であり、変更線形コード値が補償電圧である補償器の実施が示される。補償器は、1度に1つのサブ画素で動作する。すなわち、複数のサブ画素は、逐次処理できる。例えば、補償は、左から右へ、上から下への従来のスキャン指令において信号源から線形コード値を着信して、それぞれのサブ画素のために実行できる。補償は、補償回路の複数の複製を平行させることによって、又は補償器をパイプラインすることによって、複数の画素で同時に実行できる。これらの技術は、当業者には明らかであろう。

【0065】

補償器60への入力は、サブ画素位置601、及び指令駆動電圧を表すことができるサブ画素の線形コード値602である。補償器は、線形コード値を変更して、線形ソースドライバのための変更線形コード値を作り出す。これは、補償電圧アウト603などにしてもよい。補償器は、サブ画素の経年数を決定するブロック61、OLED効率を随意的に補償するブロック62、経年数に基づいて補償を決定するブロック63、及び補償するブロック64の主要な4つのブロックを有することができる。ブロック61、及び62は、OLED効率の補償に主に関連し、ブロック63、及び64は、電圧補償、特にVth/Voled補償に主に関連する。

【0066】

図6bは、ブロック61、及び62の拡大図である。サブ画素配置601を使用して、製造時に記憶された基準経年劣化信号の測定i0611と、最も新しく記憶された経年劣化信号の測定i1とを読み出す。経年劣化信号の測定は、先に「データ収集」において説明された測定回路が出力する経年劣化信号にしてもよい。測定結果は、それぞれ異なった時間における位置601のサブ画素の経年劣化信号の測定結果にしてもよい。この測定結果は、メモリ619に記憶できる。メモリ619は、フラッシュメモリなどの不揮発性RAM、及びEEPROMなどのROMにできる。i0測定は、NVRAM、又はROMに記憶できる。i1測定は、NVRAMに記憶できる。測定612は、単一の測定、いくつかの測定の平均、測定の指数加重移動平均、又は当業者に明らかであろう他の平滑方法の結果にしてもよい。

【0067】

パーセント電流613は、上述のように、i1/i0として計算でき、0(故障した画素)、1(変化なし)、1未満(電流損失)、1より大きい(電流利得)にできる。一般的に、最新の経年劣化信号の測定結果は、製造時の測定結果よりも小さいので、パーセント電流は、0と1との間になる。パーセント電流は、個々の測定i0、i1と同様に、電流の変動を示すので、メモリ619に直接記憶される場合は、パーセント電流自体を経年劣化信号にできる。

【0068】

パーセント電流613は、次の処理段63に送信されるとともに、モデル695に入力されて、パーセントOLED効率614を決定する。モデル695は、最新の測定時における所与の電流による発光量を、製造時の電流による発光量で除したものである効率614を出力する。電流を得ている画素において、効率の損失を計算することは難しいので、パーセント電流が1よりも大きい場合には、1の効率、すなわち損失がないことが生じる可能性がある。またモデル695は、破線矢印で示すように、線形コード値602の関数にしてもよい。この場合、OLED効率は、指令電流に依存する。線形コード値602をモデル695の入力として含むか否かは、パネル設計の寿命試験、及びモデリングによって決定できる。

【0069】

同時に、補償器は、指令電圧などの線形コード値を602において受信する。この線形コード値は、製造時に測定されたパネルの元のI−V曲線691を通って、所望の電流621を決定する。これを、動作628において、パーセント効率614で除して、所望の電流の光出力を、製造時の値に戻す。結果として生じるブースト電流(boosted voltage)は、曲線691の反転である曲線692を通って、どの指令電流が、効率の損失が存在する下で所望の光量を作り出すことになるかを決定する。曲線692からの値は、効率調整電流622として次の段に通される。

【0070】

効率補償が要求されない場合、随意的なバイパス経路626に示すように、入力電圧602は、変化せずに、効率調整電流622として次の段に送信される。この場合、パーセント電流613は、計算すべきであるが、パーセント効率614は、計算する必要はない。

【0071】

図6cは、図6aの拡大図であるブロック63、及び64である。ブロック63、及び64は、パーセント電流613、及び効率調整電流622を、前段から受信する。「補償を得る」ブロック63は、反転I−V曲線692を介して電流損失623をマッピングする段階と、測定基準ゲート電圧(510)から結果(513)を減じて、VthシフトΔVth631を獲得する段階とを有する。「補償する」ブロック64は、(式1)で与えられる補償電圧アウト603を計算する動作633を有する。

Vout=Vin+ΔVth(1+α(Vg,ref−Vin)) (式1)

ここで、Voutは、603であり、ΔVthは、631であり、αは、アルファ値632であり、Vg,refは、測定基準ゲート電圧510であり、Vinは、効率調整電圧622である。補償電圧アウトは、線形ソースドライバの変更線形コード値として表すことができ、駆動トランジスタ、及びELデバイスの特性の変動を補償できる。

【0072】

ストレートなVthシフトの場合、αはゼロになり、動作633は、効率調整電圧622に加算されるVthシフト量が減少することになるであろう。いずれか特定のサブ画素において、加算量は、新たな測定が行われるまで一定である。したがって、この場合、動作633において加算させる電圧は、測定が行われた後に、予め計算することができ、ブロック63、及び64を無くして、記憶値を検索して加算することが可能になる。これにより、かなりの量の論理回路を省くことができる。

【0073】

〔領域間共通処理、及びビット深度〕

従来の画像処理経路は、典型的には非線形コード値(NLCV)を作り出す。すなわち、輝度に非線形な関係を有するデジタル値を作り出す(Giorgianni & Madden. Digital Color Management: encoding solutions. Reading, Mass.: Addison-Wesley, 1998. Ch. 13, pp. 283- 295)。非線形出力を使用することは、典型的なソースドライバの入力領域に一致し、人間の目の精度範囲にコード値の精度範囲を一致させる。しかしながら、Vthシフトは、電圧領域の動作であるので、線形電圧空間で最も簡単に実行される。線形ソースドライバを使用するとともに、ソースドライバより先に領域変換を実行することで、非線形領域の画像処理経路を、線形領域の補償器に効果的に組み込むことができる。なお、この説明は、デジタル処理に関するものであるが、アナログ処理をアナログシステム、又はデジタル/アナログ混載システムにおいて、実行できる。なおまた、補償器は、電圧以外の線形空間において、動作できる。例えば、補償器は、線形電流空間において、動作できる。

【0074】

図7を参照すると、領域変換ユニット12、及び補償器13の効果を表すジョーンズダイアグラム(Jones-diagram)が示される。この図は、これらのユニットの数学的な効果を示し、実行方法を示すものではない。これらのユニットの実行は、アナログ、又はデジタルにできる。象限Iは、領域変換ユニット12の動作を表す。非線形コード値(NLCV、nonlinear code values)にできる軸701上の非線形入力信号は、変換711を介してマッピングして、軸702上に線形コード値(LCV、linear code values)を形成することによって、変換される。象限IIは、補償器12の動作を表す。軸702上のLCVは、721、及び722などの変換を介してマッピングされて、変更線形信号値(CLCV、changed linear code values)を軸703上に形成する。

【0075】

象限Iを参照すると、領域変換ユニット12は、NLCVなどの非線形入力信号を受信し、LCVに変換する。この変換は、輪郭黒色、及びクラッシュ黒色(contouring and crush blacks)などの好ましくない可視的なアーチファクトを回避するために、十分な解像度により実行すべきである。図7に示すように、デジタルシステムにおいて、NLCV軸701は、量子化できる。この場合、LCV軸702は、隣接する2つのNLCV間の変換711における最も小さい変化を表すのに十分な解像度を有するべきである。これは、NLCVステップ712として示され、LCVステップ713に対応する。LCVは、線形で規定されるので、LCV軸702全体の解像度は、ステップ713を示すために、十分にすべきである。その結果として、LCVは、画像情報の損失を回避するために、NLCVよりも細かい解像度で規定できる。解像度は、ナイキスト・サンプリング理論による類推によって、ステップ713の2倍の解像度にできる。

【0076】

変換711は、経年劣化していないサブ画素の理想的な変換である。変換711は、いずれのサブ画素の経年劣化、又は全体としての画素の経年劣化には関係がない。具体的には、変換711は、Vth、Voled、又はOLED効率のいずれか変化によって、修正されない。全ての色について1つの変換にでき、又はそれぞれの色について1つの変換にできる。有利には、領域変換ユニットは、変換711によって、画像処理経路を補償器から切り離すことによって、2つが情報を共有することなしに、ともに動作することが可能になる。これによって、双方の実施が簡素化される。

【0077】

象限IIを参照すると、補償器13は、画素当たりのバイアスにおいて、LCVを変更線形コード値(CLCV)に変更する。図7において、一般性を失わないストレートなVthシフトである補正である簡単な場合が示される。ストレートなVthシフトは、LCVからCLCVへのストレートな電圧シフトによって、補正できる。他の経年劣化効果は、「実施」において既に説明したように、取り扱うことができる。

【0078】

曲線721は、経年劣化していないサブ画素のための補償器の動作を表す。この場合、CLCVは、LCVと同一にすることができる。曲線722は、経年劣化したサブ画素のための補償器の動作を表す。この場合、CLCVは、問題となるサブ画素のVthシフトを表すオフセットをLCVに加えることができる。この結果として、一般的には、CLCVは、補償のためのヘッドルームを提供するために、LCVよりも大きな範囲が必要になるであろう。例えば、サブ画素が、新しいときに256個のLCVが必要であり、寿命に亘る最大シフトが128LCVである場合、CLCVは、経年劣化が激しいサブ画素の補償のクリッピングを回避するために、384=256+128までの値を表なければならない必要があるであろう。

【0079】

図7において、領域変換ユニット、及び補償器の効果の完全な例を示す。図7の破線矢印に従うと、3のNLCVが、領域変換ユニット12によって、象限Iに示されるように、変換711を介して9のLCVに変換される。経年劣化していないサブ画素では、補償器13は、象限IIに示すように、曲線721によって、9のCLCVとして通過することになるであろう。12CLCV程度のVthシフトを有する経年劣化したサブ画素において、9のLCVは、曲線722によって、9+12=21のCLCVに変換されることになるであろう。

【0080】

実際には、NLCVは、画像処理経路からのコード値にでき、8ビット以上有してもよい。フレームごとに、パネル上のそれぞれのサブ画素のためのNLCVにしてもよい。LCVは、電圧を表す線形値にして、ソースドライバによって、駆動できる。先に説明したように、LCVは、十分な解像度を有するために、NLCVよりも大きなビットを有してもよい。CLCVもまた、電圧を表す線形値にして、ソースドライバによって、駆動できる。先に説明したように、CLCVは、補償のためのヘッドルームを提供するために、LCVよりも大きなビットを有してもよい。本明細書で説明したように、入力NLCVから作り出して、それぞれのサブ画素のLCV、及びCLCVにすることができる。

【0081】

1つの実施形態において、コード値(NLCV)、すなわち画像処理経路からの非線形入力信号は、9ビット幅である。電圧を表すことができる線形コード値は、11ビット幅である。非線形入力信号から線形コード値への変換は、LUT、又は関数により実行できる。補償器は、所望の電圧を表す11ビットの線形コード値を含むことができ、12ビットの変更線形コード値を作り出して、線形ソースドライバ14に送信できる。次いで、線形ソースドライバは、変更線形コード値に応答して、取り付けられたELサブ画素の駆動トランジスタのゲート電極を駆動できる。比較器は、出力が入力よりも深いビット深度を有して、補償のためのヘッドルームを提供できる。すなわち、新しく広げた範囲において、最小線形コード値ステップ75に必要な同一の解像度を維持しながら、電圧範囲78を電圧範囲79に広げることができる。補償器の出力範囲は、曲線71の範囲内で広げることができるとともに、曲線71の範囲よりも大きく広げることができる。

【0082】

パネル設計はそれぞれ、最大Vthシフト73、Voled上昇、及び効率の損失がパネルの設計寿命を超えることになるように決定するように特性化でき、補償器、及びソースドライバは、補償するために十分な範囲を有することができる。この特性化は、標準的なトランジスタの飽和領域Ids式を用いて、必要な電流から必要なゲートバイアス及びトランジスタ寸法まで進めることができる。次いで、a−Siの時間に伴う劣化の従来の様々なモデルを用いて、時間に伴うVthシフトに進めることができる。

【0083】

〔動作のシーケンス〕

〔パネル設計特性〕

この項では、特定のOLEDパネル設計の大量生産との関係で説明される。大量生産を開始する前に、設計が特性化される。加速寿命試験を実行でき、I−V曲線は、様々なレベルに経年劣化された様々なサンプルパネルにおける様々な色の様々なサブ画素について測定される。測定に必要な数、及び形式、並びに経年劣化レベルの数、及び形式は、具体的なパネルの特性に依存する。これらの測定によって、値アルファ(α)を計算できるとともに、測定基準ゲート電圧を選択できる。アルファ(図6c、項目634)は、時間に伴うストレートなシフトからの偏差を表す値である。0のアルファ値は、Vthシフトのみなどの場合のように、全ての経年劣化が電圧軸に対してストレートなシフトであることを示す。測定基準ゲート電圧(図5a、310)は、補償のための経年劣化信号の測定が行われる電圧であり、電力低下を抑えながら良好なS/N比を提供するように選択できる。

【0084】

α値は、最適に計算できる。一例を表1に示す。ΔVthは、いくつかの経年劣化の条件下で、いくつかのゲート電圧で測定できる。次いで、ΔVth差異は、それぞれのΔVthと、測定基準ゲート電圧310におけるΔVthとの間で計算される。Vg差異は、それぞれのゲート電圧と、測定基準ゲート電圧310との間で計算される。次いで、測定基準ゲート電圧310における適当なΔVthを式のΔVthに使用し、適当に計算されたゲート電圧差異を(Vg,ref−Vin)として使用して、式1の内項ΔVth・α(Vg,ref−Vin)をそれぞれの測定について計算して、予測ΔVth差異を得ることができる。次いでα値を繰り返して選択するとともに、好適には数学的に最小化して、予測ΔVth差異と、計算されるΔVth際との間のエラーを低減できる。エラーは、最大差、又はRMS差として表すことができる。また、Vgの差の関数である最小二乗適合などの従来からの他の方法を使用できる。

【0085】

【表1】

【0086】

α、及び測定基準ゲート電圧に加えて、特性は、上述のように、Vthシフトの関数としてVoledシフトを決定し、Vthシフト、サブ画素当たりの自己発熱要素、最大Vthシフト、Voledシフト、及び効率の損失の関数として効率の損失を決定し、非線形‐線形変換、及び補償器に必要な解像度を決定する。必要な解像度は、名称を「RGBWディスプレイの較正(Calibrating RGBW Displays)」という同一出願人の同時係属のAlessiらによる2007年4月13日付の米国出願シリアル番号第11/734934号などのパネル較正手段と併せて特性化できる。この出願は参照することにより本明細書に包含される。また以下の「現場において」で説明されることになるように、特性化は、実施において特性化測定を行う条件を決定する。これら全ての決定は、当業者が行うことができる。

【0087】

〔大量生産〕

設計が特性化されると、量産を開始できる。製造時に、1つ、又は2つ以上のI−V曲線を、作成するパネルごとに測定する。これらのパネルの曲線は、複数のサブ画素の曲線の平均にできる。パネルの種々の色には、別個の曲線にでき、またパネルの種々の領域には、別個の曲線にできる。電流は、現実的なI−V曲線を作成するのに十分な駆動電圧において測定できる。I−V曲線における何らかのエラーは、結果に影響を与える可能性がある。また、測定時において、基準電流、すなわち測定基準ゲート電圧における電流は、パネル上の全てのサブ画素において測定できる。I−V曲線、及び基準電流は、パネルに記憶され、現場に送られる。

【0088】

〔現場において〕

現場に置かれると、パネル上のサブ画素は、駆動される程度に依存して種々の割合で経年劣化する。いくらかの時間の後、1つ、又は2つ以上の画素は、補償に必要とされるのに十分に大きくシフトしている。その時間を決定する方法を以下で考察する。

【0089】

補償するために、補償測定が行われ、適用される。補償測定は、測定基準ゲート電圧におけるそれぞれのサブ画素の電流である。測定は、先に「アルゴリズム」において説明したように適用される。測定は、サブ画素を駆動するときにいつでも適用できるように、次の測定が行われるまで記憶される。全体的なパネル、又はパネルのいずれかのサブセットは、補償測定が行われるときに、測定できる。いずれかのサブ画素を駆動するとき、そのサブ画素の最新の測定を補償に使用できる。またこれは、サブ画素の第1のサブセットを1つの時間で測定でき、第2のサブセットを他の時間に測定でき、最新のパスにおいて全てのサブ画素が測定されていない場合でさえも、パネルに亘る補償が可能であることを意味する。また1つのサブ画素よりも大きなブロックを測定し、同一の補償をブロックの全てのサブ画素に適用するが、この場合、ブロック境界のアーチファクトが導入されないように注意する。また、1つのサブ画素よりも大きなブロックを測定することによって、高い空間周波数パターンの可視的な焼付けへの脆弱性が導入される。このパターンは、ブロックの大きさよりも小さなパターンを有してもよい。この脆弱性は、それぞれのサブ画素に比較して複数のサブ画素のブロックを測定するために必要な時間の低減とのトレードオフになる可能性がある。

【0090】

補償測定を所望の頻度で頻繁に、又は頻繁でなく行うことができる。典型的な範囲は、8時間に1度から4週間に1度にできる。図8において、パネルが活性化する長さとの関係で、補償測定が行われている頻度の一例が示される。この曲線は、単なる例である。実際には、この曲線は、設計の加速寿命試験を通して、具体的なパネル設計について決定できる。測定頻度は、駆動トランジスタ、及びELデバイスの時間にともなう特性変化の割合に基づいて選択できる。パネルが新しいときは、双方は、より早くシフトするので、補償測定は、パネルが古いときよりも新しいときのほうが、より頻繁に行なってもよい。補償測定を行うときを決定する、いくつかの方法がある。例えば、所与のいくつかの駆動電圧において、全体的にパネルを活性化するときに引き出される合計の電流を測定し、同一の測定の先の結果と比較できる。他の例では温度、及び環境光などのパネルに影響を与える環境要因を測定でき、環境温度がいくつかのしきい値よりも大きく変化しているなどの場合に、補償測定を行う。また、パネルの画像領域内、又は画像領域外のいずれかのそれぞれのサブ画素の電流を測定できる。パネルの画像領域の外部の場合、サブ画素は、測定の目的で提供される基準サブ画素にできる。サブ画素は、望ましい環境条件の何かの一部にさらすことができる。例えば、サブ画素は、不透明な材料で覆うことで、環境温度には応答するが、環境光には応答しないようにできる。

【0091】

上述の実施形態は、駆動回路のトランジスタがnチャネルトランジスタであるように構成される。トランジスタがpチャネルトランジスタである実施形態、又は適当な周知の修正を回路に行ったnチャネルと、pチャネルとのいくつかの組み合わせである実施形態もまた、本発明に有用であることは、当業者には理解されるであろう。また、説明される実施形態では、非反転(共通カソード)構造のOLEDが示される。本発明は、反転(共通アノード)構造もまた適用できる。さらに、上述の実施形態は、駆動回路のトランジスタがa−Siトランジスタであるように構成される。上述の実施形態は、時間の関数で安定しないいずれのアクティブマトリクスバックプレーンに適用できる。例えば、有機半導体材料と、酸化亜鉛とで形成されるトランジスタは、時間の関数で変化することが公知である。したがって、同一のアプローチをこのトランジスタに適用できる。さらにまた、トランジスタの経年劣化とは独立にELデバイスの経年劣化を補償できるので、本発明は、LTPS TFTなど経年劣化しないトランジスタを有するアクティブマトリクスバックプレーンにも適用できる。また、本発明は、OLED以外のELデバイスにも適用できる。他のELデバイスの型の劣化モデルは、本明細書で説明される劣化モデルとは異なるが、本発明に係る測定技術、モデリング技術、及び補償技術をなお適用できる。

【符号の説明】

【0092】

10 全体的なシステム

11 非線形入力信号

12 電圧領域変換

13 補償器

14 線形ソースドライバ

15 OLED駆動回路

16 電流測定回路

30 OLEDパネル

31 ソースドライバ

32a 列線

32b 列線

32c 列線

33 ゲートドライバ

34a 行線

34b 行線

34c 行線

35 サブ画素マトリクス

36 選択トランジスタ

41 測定

42 測定

43 差異

49 測定

60 補償器

61 ブロック

62 ブロック

63 ブロック

64 ブロック

71 I−V曲線

73 電圧シフト

74 コード値ステップ

75 電圧ステップ

76 電圧ステップ

78 電圧ステップ

79 電圧ステップ

90 直線の当てはめ

200 スイッチ

201 駆動トランジスタ

202 OLEDデバイス

203 ゲート電極

204 第1の供給電極

205 第2の供給電極

206 電圧源

207 第1の電極

208 第2の電極

210 カレントミラーユニット

211 電圧源

212 第1のカレントミラー

213 第1のカレントミラー出力

214 第2のカレントミラー

215 バイアス供給

216 電流‐電圧コンバータ

220 相関2重サンプリングユニット

221 サンプリング、及び維持ユニット

222 サンプリング、及び維持ユニット

223 差動増幅器

230 アナログ‐デジタルコンバータ

421 自己発熱量

422 自己発熱量

423 測定

424 差異

501 経年劣化していないI−V曲線

502 経年劣化しているI−V曲線

503 電圧の差異

504 電圧の差異

505 電圧の差異

506 電圧の差異

510 測定基準ゲート電圧

511 電流

512a 電流

512b 電流

513 電圧

514 電圧シフト

550 電圧シフト

552 電圧シフト

601 サブ画素配置

602 指令電圧

603 補償電圧

611 電流

612 電流

613 パーセント電流

614 パーセント効率

619 メモリ

621 電流

622 電圧

626 ブロック

628 動作

631 電圧シフト

632 アルファ値

633 動作

691 I−V曲線

692 反転I−V曲線

695 モデル

701 軸

702 軸

703 軸

711 変換の最小変化

712 ステップ

713 ステップ

721 変換

722 変換

1002 記憶容量

1011 母線

1012 薄板カソード

【技術分野】

【0001】

本発明は、エレクトロルミネセント・デバイスを介して電流を供給する駆動トランジスタに印加されるアナログ信号の制御に関する。

【背景技術】

【0002】

フラットパネル・ディスプレイは、演算、娯楽、及び通信のための情報ディスプレイとして、大いに興味を引く。有機発光ダイオード(OLED、organic light-emitting diode)技術などのエレクトロルミネセント(EL)・フラットパネル・ディスプレイ技術は、液晶ディスプレイ(LCD)、及びプラズマディスプレイパネル(PDP)などの他の技術に対して、色域、色彩、輝度、及び消費電力において利益をもたらす。しかしながら、ELディスプレイは、時間に伴う性能劣化に悩まされる。ディスプレイの寿命に亘って、高い画質を提供するためには、この劣化を補償しなければならない。

【0003】

一般的に、ELディスプレイは、同一のサブ画素のアレイを有する。サブ画素はそれぞれ、駆動トランジスタ(一般的には薄膜であり、TFTである)、及び実質的に光を発光する有機ダイオードであるELデバイスを有する。ELデバイスの光出力は、デバイスを流れる電流にほぼ比例するので、一般的に駆動トランジスタは、ゲート‐ソース電圧Vgsに応答する電圧制御電流源として構成される。LCDディスプレイで使用されるソースドライバと類似するソースドライバは、駆動トランジスタに制御電圧を提供する。ソースドライバは、所望のコード値ステップ74をアナログ電圧ステップ75に変換して、駆動トランジスタを制御する。ビット深度がより大きい線形ソースドライバが利用可能になりつつあるが、一般的には、コード値と、電圧との間の関係は、非線形である。非線形コード値と電圧との関係は、OLEDでは、LCDの特徴的なS形状(米国特許第4896947号などに示される)とは異なる形状を有するが、必要なソースドライバ電極は、2つの技術の間で非常に類似する。LCDソースドライバと、ELソースドライバとの間の類似性に加えて、LCDディスプレイと、ELディスプレイとは、一般的に同一の基板に製造される。すなわち、米国特許第5034340号において、Tanakaらが教示するように、アモルファスシリコン(a‐Si)である。アモルファスSiは、高価ではなく、かつ大型ディスプレイにおける処理が容易である。

【0004】

〔劣化のモード〕

しかしながら、アモルファスシリコンは、準安定である。すなわち、時間とともにa‐Si TFTのゲートに電圧バイアスが印加されて、しきい値電圧(Vth)がシフトすることによって、I−Vカーブがシフトする(Kagan & Andry, ed. Thin-film Transistors. New York: Marcel Dekker, 2003. Sec. 3.5, pp. 121-131)。一般的にVthは、順バイアスの下で時間とともに増加するため、平均的には、Vthシフトは、時間とともにディスプレイが薄暗くなる原因になるであろう。

【0005】

a‐Si TFTの不安定性に加えて、現在のELデバイス自体に不安定性を有する。例えばOLEDデバイスにおいて、電流がOLEDデバイスを流れるときに、OLEDデバイスの順電圧(Voled)が時間とともに増加し、効率(一般的にcd/Aで測定される)が低下する(Shinar, ed. Organic Light-Emitting Devices: a survey. New York: Springer-Verlag, 2004. Sec. 3.4, pp. 95-97)。定電流で駆動するときでも、効率の損失によって、時間とともにディスプレイが平均的に薄暗くなる。さらに、一般的なOLEDディスプレイの構成では、OLEDは、駆動トランジスタのソースに取り付けられる。この構成では、Voledが増加することにより、トランジスタのソース電圧が昇圧し、Vgsが低くなるので、OLEDデバイスを流れる電流(Ioled)が減少するために、時間とともに薄暗くなる原因になる。

【0006】

これら3つの効果(Vthシフト、OLED効率の損失、及びVoled上昇)によって、OLEDサブ画素はそれぞれ、OLEDデバイスを流れる電流に比例する割合で、時間とともに輝度を失うことになる。(Vthシフトが1次的な効果であり、Voledシフトが2次的な効果であり、OLED効率の損失が3次的な効果である)したがって、時間とともにディスプレイが薄暗くなり、より多くの電流によって駆動されることになるこれらのサブ画素は、より早く光が弱まるであろう。この示差的な経年劣化(differential aging)によって、好ましくない可視的な焼付けがディスプレイに生ずることになる。ますます多くの放送局がコンテンツ上の固定位置にロゴを連続的に重ね合わせるなどするために、示差的な経年劣化は、今日深刻化する問題である。一般的に、ロゴは、周囲のコンテンツよりも明るいので、ロゴ内の画素は、周囲のコンテンツよりも早く経年劣化し、そのロゴを含まないコンテンツを見るときに可視的なロゴの負電極画の複写が作られる。一般的にロゴは、高い空間周波数のコンテンツを含む(例えばAT&T(登録商標)の球体)ので、1つのサブ画素が、激しく経年劣化する一方、近接するサブ画素は、軽く劣化するだけである。したがって、好ましくない可視的な焼付けを除去するために、画素はそれぞれ、別々に経年劣化を補償しなければならない。

【0007】

〔先行技術〕

これら3つの効果の1つ、又は2つ以上を補償することが公知である。1次的効果であり、印加するバイアスで改善可能であるVthシフト(Mohan et al., "Stability issues in digital circuits in amorphous silicon technology," Electrical and Computer Engineering, 2001, Vol. 1, pp. 583-588)を考慮すると、補償スキーマは、一般的に4つのグループに分割される。画素内の補償、画素内の測定、パネル内の測定、及び逆バイアスである。

【0008】

画素内のVth補償スキーマでは、Vthシフトが生じるときにVthシフトを補償するために、それぞれのサブ画素に付加回路が加えられる。Leeらによる「新たなa−Sia:しきい値電圧の劣化を補償するH TFT画素設計("A New a-Si:H TFT Pixel Design Compensating Threshold Voltage Degradation of TFT and OLED", SID 2004 Digest, pp. 264-274)」は、所望のデータ電圧を印加する前に、サブ画素の記憶キャパシタにそれぞれのサブ画素のVthを記憶することによって、Vthを補償する7トランジスタ‐1キャパシタ(7T1C)サブ画素回路を教示する。このような方法では、Vthシフトは、補償されるが、Voled上昇、又はOLED効率の損失は、補償できない。これらの方法は、従来の2T1C電圧駆動サブ画素回路と比較して、サブ画素がより複雑になり、かつサブ画素回路の大きさを大きくする必要がある。サブ画素がより複雑になることによって、生産量が減少する。微細な形状が必要となるので、組立誤差に対して脆弱になるためである。具体的には、一般的な裏面発光構造において、サブ画素回路全体の大きさが大きくなることにより、消費電力が増加する。発光するそれぞれのサブ画素の割合、すなわち開口率が減少するためである。OLEDの発光は、固定電流における領域に比例するので、開口率が小さいOLEDデバイスは、大きな開口率を有するOLEDと同一の輝度を作り出すために、より大きな電流が必要である。さらに、小さな領域に大きな電流を流すことにより、OLEDデバイスの電流密度が大きくなるので、Voled上昇と、OLED効率の損失とが加速される。

【0009】

画素内測定Vth補償スキームは、それぞれのサブ画素に付加回路を加えて、Vthシフトを示す値を測定することを可能にする。次いでパネル外の回路は、測定結果を処理し、それぞれのサブ画素の駆動を調整して、Vthシフトを補償する。例えば、米国特許出願第2006/0273997(A1)号において、Nathanらは、所与の電圧条件の下での電流、又は所与の電流条件の電圧のいずれか一方として、TFT劣化データを測定することが可能な4トランジスタ画素回路を教示する。米国特許第7199602号において、Naraらは、検査インタコネクトをディスプレイに付加し、かつスイッチングトランジスタに検査インタコネクトを接続するスイッチングトランジスタを、ディスプレイのそれぞれの画素に付加することを教示する。米国特許第6518962号において、Kimuraらには、ディスプレイのそれぞれの画素に補正TFTを付加して、EL劣化を補償することを教示する。これらの方法は、画素内Vth補償スキームの不利な点を共有するが、一部は、Voeldシフト、又はOLED効率の損失をさらに補償できる。

【0010】

逆バイアスVth補償スキームは、逆電圧の一部の形式を使用して、Vthをある開始点に戻す。この方法は、Voled上昇、又はOLED効率の損失を補償できない。例えば、米国特許第7116058号において、Loらは、アクティブマトリクス画素回路の記憶キャパシタの基準電圧を調整して、それぞれのフレームの間の駆動トランジスタを逆バイアスすることを教示する。フレーム内部、又はフレーム間に逆バイアスを印加することによって、可視的なアーチファクトを防止するが、デューティサイクルが減少することによって、ピーク輝度が減少する。逆バイアス方法は、画素内補償方法よりも消費電力の増加を低減しながら、パネルの平均的なVthシフトを補償できるが、より複雑な外部電源供給が必要であり、画素回路、又は信号線を付加する必要がある可能性があり、他の画素よりも光の弱まりが大きい画素を個々に補償できない可能性がある。

【0011】

Voledシフト、及びOLED効率の損失を考慮すると、Arnoldらによる米国特許第6995519号は、OLEDデバイスの経年劣化を補償する方法の一例である。この方法は、デバイスの輝度の全体的な変化は、OLEDエミッタの変化により生じると仮定する。しかしながら、回路の駆動トランジスタをa−Siで形成されるとき、この仮定は有効ではない。使用に伴ってトランジスタのしきい値も変化するためである。このため、Arnoldの方法は、トランジスタが経年劣化効果を示す回路においては、サブ画素の経年劣化の完全な補償を提供することはないであろう。また、逆バイアスなどの方法を使用して、a‐Siトランジスタのしきい値電圧シフトを軽減するとき、OLED効率の損失の補償は、逆バイアス効果の適当な追跡/予測、若しくはOLED電圧の変化、又はトランジスタしきい値電圧の変化の直接的な測定なしには、信頼性が低くなる可能性がある。

【0012】

例えば米国特許第6489631号において、Youngらにより教示されるように、補償の他の方法では、それぞれの画素の光出力を直接測定する。この方法は、3つの経年劣化の全ての要因による変化を補償できるが、非常に高精度な外部光センサが必要であるか、又はそれぞれの画素に統合される光センサが必要になる。外部光センサは、デバイスの価格、及び複雑さを付加する一方、統合光センサは、サブ画素がより複雑になり、電子回路の大きさが大きくなるとともに、付随する性能が低下する。

【0013】

現在のVth補償スキームは、欠点を有しないものはなく、Voled上昇、又はOLED効率の損失を補償するものは、ほとんどない。それぞれのサブ画素のVthシフトを補償するものは、パネルの複雑さ、及び生産量の低下の代償として、行われる。したがって、これらの難点を克服して、ELパネルの劣化を補償し、ELディスプレイパネルの全体的な寿命に亘る好ましくない可視的な焼付けを防止するために、補償を改善することへのニーズが引き続き存在する。

【発明の概要】

【課題を解決するための手段】

【0014】

本発明に従って、ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置であって、駆動回路は、駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、駆動トランジスタの第2の供給電極に電気的に接続されるELデバイスとを有し、

a)第1の供給電極、及び第2の供給電極を、異なった時間に流れる電流を測定して、駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変動を示す経年劣化信号を提供する測定回路と、

b)線形コード値を提供する手段と、

c)駆動トランジスタ、及びELデバイスの特性の変動を補償するために、経年劣化信号に応じて、線形コード値を変更する補償器と、

d)駆動トランジスタのゲート電極を駆動するために、変更線形コード値に応じて、アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置を提供する。

【0015】

また、ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する方法であって、駆動回路は、駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、駆動トランジスタの第2の供給電極に電気的に接続されるELデバイスとを有し、

a)第1の供給電極、及び第2の供給電極を、異なった時間に流れる電流を測定して、駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変動を示す経年劣化信号を提供するステップと、

b)線形コード値を提供するステップと、

c)駆動トランジスタ、及びELデバイスの特性の変動を補償するために、経年劣化信号に応じて、線形コード値を変更するステップと、

d)駆動トランジスタのゲート電極を駆動するために、変更線形コード値に応じて、アナログ駆動トランジスタ制御信号を作り出すステップと、

を有する方法を提供する。

【0016】

さらに、ELパネルの複数のELサブ画素の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置であって、第1の電圧源と、第2の電圧源と、複数のELサブ画素とをELパネルに有し、駆動回路のELデバイスは、それぞれのELサブ画素のELデバイスに電流を印加し、駆動回路はそれぞれ、第1の電圧源に電気的に接続される第1の供給電極と、ELデバイスの第1の電極に電気的に接続される第2の供給電極とを有する駆動トランジスタを有し、ELデバイスはそれぞれ、第2の電圧源に電気的に接続される第2の電極を有し、改良点は、

a)第1の電圧源、及び第2の電圧源を、異なった時間に流れる電流を測定して、サブ画素の駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変動を示すそれぞれのサブ画素の経年劣化信号を提供する測定回路と、

b)それぞれのサブ画素の線形コード値を提供する手段と、

c)それぞれのサブ画素の駆動トランジスタ、及びELデバイスの特性の変動を補償するために、経年劣化信号に応じて、線形コード値を変更する補償器と、

d)駆動トランジスタのゲート電極を駆動するために、変更線形コード値に応じて、アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置を提供する。

【発明の効果】

【0017】

本発明は、アナログ駆動トランジスタ制御信号を提供する効果的な方法を提供する。補償を実行するために、1つの測定のみが必要である。いずれのアクティブマトリクスのバックプレーンに提供可能である。制御信号の補償は、補償を線形電圧領域にできるように、ルックアップテーブル(LUT)を使用して、非線形から線形に信号を変更することによって、単純化されている。本発明は、複雑な画素回路、又は外部の測定デバイスを必要とせずに、Vthシフト、Voledシフト、及びOLED効率の損失を補償する。本発明は、サブ画素の開口率を減少させない。本発明は、パネルの通常動作には影響を与えない。

【図面の簡単な説明】

【0018】

【図1】本発明を実施する制御システムのブロックを概略的に示す図である。

【図2】図1のブロックのより詳細な形の回路を概略的に示す図である。

【図3】典型的なOLEDパネルを概略的に示す図である。

【図4A】理想的な条件の下で図2の測定回路を動作させるタイミングを概略的に示す図である。

【図4B】サブ画素の自己発熱によるエラーを有する図2の測定回路を動作させるタイミングを概略的に示す図である。

【図5A】経年劣化していないサブ画素、及び経年劣化し、Vthシフトを示すサブ画素のI−V特性曲線を示す図である。

【図5B】経年劣化していないサブ画素、及び経年劣化し、Vthシフトと、Voledシフトとを示すサブ画素のI−V特性曲線を示す図である。

【図6A】図1の補償器の上位レベルのデータフローを概略的に示す図である。

【図6B】補償器の詳細なデータフローの(2つの部分の)第1の部分を概略的に示す図である。

【図6C】補償器の詳細なデータフローの(2つの部分の)第2の部分を概略的に示す図である。

【図7】領域変換ユニットと、補償器の効果を示すジョーンズダイアグラムである。

【図8】補償測定の頻度を時間とともに表すプロットを示す図である。

【図9】パーセント電流の関数としてパーセント効率を表すプロットを示す図である。

【図10】本発明に従う駆動回路の詳細な回路を示す図である。

【発明を実施するための形態】

【0019】

本発明の上述の目的、特徴、及び利点、並びに他の目的、特徴、及び利点は、以下の説明、及び図面を併せて理解するときに、より明確になるであろう。ここで、図面に共通する同一の特徴を示すために、可能な限り同一の符号が使用されている。

【0020】

本発明は、アクティブマトリクスELディスプレイパネルの駆動トランジスタ、及びELデバイスの劣化を補償する。1つの実施形態において、アクティブマトリクスOLEDパネルの全てのサブ画素のVthシフト、Voledシフト、及びOLED効率の損失を補償する。パネルは、1つ、又は2つ以上のサブ画素をそれぞれが備える複数の画素を有する。例えば、それぞれの画素は、赤色のサブ画素、緑色のサブ画素、及び青色のサブ画素を有してもよい。それぞれのサブ画素は、光を発光するELデバイスと、周囲の電子機器とを有する。サブ画素は、パネルの最も小さなアドレス可能な素子である。ELデバイスは、OLEDデバイスにできる。

【0021】

以下の議論において、まずシステム全体を考察する。次いで、サブ画素の電気的な詳細に進んだ後に、1つのサブ画素の測定、及び複数のサブ画素を測定するタイミングの電気的な詳細に進む。次に、補償器が、測定結果を使用する方法を対象とする。最後に、本システムが、消費者製品などにおいて工場から寿命末期まで、1つの実施形態において実施される方法が説明される。

【0022】

〔概説〕

図1において、本発明に係る全体的なシステム10のブロックを概略的に示す。非線形入力信号11は、ELパネル上に数あるELサブ画素の1つであるELサブ画素のELデバイスからの特定の光強度を指令する。本信号11は、ビデオデコーダ、画像処理経路、又は他の信号源から生成されてもよく、デジタル、又はアナログでよく、非線形コード化され、又は線形コード化されてもよい。例えば、非線形入力信号は、sRGBコード値ステップ(sRGB code value step)74、又はNTSC輝度電圧ステップ(MTSC luma voltage step)75にしてもよい。どのようなソース、及びフォーマットであっても、好適には、信号は、コンバータ12によってデジタルフォーマットに変換できるとともに、線形電圧などの線形領域に変換できる。これは、以下の「領域間共通処理、及びビット深度(Cross-domain processing, and bit depth)」において、さらに説明されることになるであろう。ルックアップテーブル、又はLCDソースに類似する機能は、この変換を実行できる。変換の結果は、指令駆動電圧(commanded drive voltage)を示すことができる線形コード値にすることになるであろう。

【0023】

補償器13は、ELサブ画素からの特定の指令光強度に対応できる線形コード値を取り込む。ELサブ画素の駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの変動は、ELサブ画素が、線形コード値に対応する指令光強度を概して作り出さなくなるであろうことをいう。補償器13は、変更線形コード値を出力することにより、ELサブ画素が、指令の強度を作り出すことになるであろう。補償器の動作は、以下の「実施」において、さらに説明されることになるであろう。

【0024】

補償器13からの変更線形コード値は、線形ソースドライバ14に移動する。線形ソースドライバ14は、デジタル‐アナログコンバータにできる。線形ソースドライバ14は、変更線形コード値に対応する電圧にできるアナログ駆動トランジスタ制御信号を作り出す。線形ソースドライバ14は、線形になるように設計されるソースドライバにでき、若しくは近似的に線形な出力を作り出すように設定されるガンマ電圧を有する従来のLCDソースドライバ、又はOLEDソースドライバにできる。後者の場合、線形性からのずれは、結果の質に影響を及ぼすことになるであろう。また、この線形ソースドライバ14は、同一出願人による国際公報2005/116971 A1において、Kawabeが教示するように、時分割(デジタル駆動)ソースドライバにしてもよい。この場合、ソースドライバからのアナログ電圧は、補償器の出力信号に依存する時間量の光出力を指令する所定のレベルに設定される。それに対して、従来の線形ソースドライバは、(一般に全体フレームの)固定された時間量の補償器の出力信号に依存するレベルのアナログ電圧を提供する。線形ソースドライバは、1つ、又は2つ以上のアナログ駆動トランジスタ制御信号を同時に出力できる。本発明に係る1つの実施形態において、ELパネルは、1つ、又は2つ以上のマイクロチップを備える線形ソースドライバを有し、マイクロチップはそれぞれ、ELパネルのELサブ画素の列の数に等しい数のアナログ駆動トランジスタ制御信号を同時に作り出すように、1つ、又は2つ以上のアナログ駆動トランジスタ制御信号を出力できる。

【0025】

線形ソースドライバ14が作り出すアナログ駆動トランジスタ制御信号は、EL駆動回路15に提供されるが、ELサブ画素に提供してもよい。この回路は、以下の「ディスプレイ素子の説明」において説明されることになるように、駆動トランジスタ、及びELデバイスを有する。アナログ電圧が駆動トランジスタのゲート電極に提供されるとき、駆動トランジスタ、及びELデバイスを電流が流れることによって、ELデバイスが光を発光する。一般に、ELデバイスを流れる電流と、出力デバイスの輝度との間には、線形の関係があり、駆動トランジスタに印加される電圧と、ELデバイスを流れる電流との間には、非線形の関係がある。したがって、ELデバイスがフレームの間に発光する光の合計量は、線形ソースデバイス14の電圧の非線形関数にできる。

【0026】

以下の「データ収集」においてさらに説明されることになるように、EL駆動回路を流れる電流は、特定の駆動条件の下で電流測定回路16によって測定される。ELサブ画素の測定電流は、指令駆動信号を調整するために必要な情報を補償器に提供する。これは、以下の「アルゴリズム」において、さらに説明されることになるであろう。

【0027】

以下の「動作シーケンス」において、さらに説明されることになるように、本システムは、ELパネルの動作寿命に亘りELパネルの駆動トランジスタ、及びELデバイスの変動を補償できる。

【0028】

〔ディスプレイ素子の説明〕

図10において、OLEDデバイスなどのELデバイスに電流を印加する駆動回路15を示す。駆動回路15は、アモルファスシリコン・トランジスタにしてもよい駆動トランジスタ201と、ELデバイス202と、正電極にできる第1の電圧源211(「PVDD」)と、負電極にできる第2の電極206(「Vcom」)とを有する。ELデバイス202は、第1の電極207と第2の電極208とを有する。駆動トランジスタは、ゲート電極203と、駆動トランジスタのドレインにできる第1の供給電極204と、駆動トランジスタのソースにできる第2の供給電極205とを有する。アナログ駆動トランジスタ制御信号は、随意的には選択トランジスタ36を介して、ゲート電極203に提供できる。アナログ駆動トランジスタ制御信号は、記憶キャパシタ1002に記憶できる。第1の供給電極204は、第1の電圧源211に電気的に接続される。第2の供給電極は、ELデバイス202の第1の電極207に電気的に接続される。ELデバイスの第2の電極208は、第2の電圧源206に電気的に接続される。駆動トランジスタ201、及びELデバイス202は、随意的な選択トランジスタ36と、記憶キャパシタ1002とともに、ELパネルに典型的に存在する駆動回路の一部であるELサブ画素を構成する。典型的には、電力供給は、ELパネルの外に配置される。電気的な接続は、スイッチ、母線、導電性トランジスタ、若しくは電流経路を提供する能力を有する他のデバイス、又は構造にできる。

【0029】

本発明に係る1つの実施形態において、第1の供給電極204は、PVDD母線1011を介して第1の電圧源211に電気的に接続され、第2の電極208は、薄板カソード1012を介して第2の電圧源206に電気的に接続され、アナログ駆動トランジスタ制御信号は、線形ソースドライバ14がゲート電極203に提供する。

【0030】

本発明は、アナログ駆動トランジスタ制御信号を駆動トランジスタのゲート電極に提供する。駆動トランジスタ、及びELデバイスの動作によって時間とともに生じる駆動トランジスタ、及びELデバイスの特性の変化を補償する制御信号を提供するためには、その変動が既知でなければならない。変動は、駆動トランジスタの第1の供給電極、及び第2の供給電極を異なった時間に流れる電流を測定して、変動を表すアナログ信号を提供することによって、決定される。これは、以下に「アルゴリズム」において、詳細に説明されることになるであろう。経年劣化信号は、デジタル、又はアナログにできる。経年劣化信号は、電圧、又は電流で表すことができる。

【0031】

図2において、図1に示す非線形入力信号11、コンバータ12、補償器13、及び線形ソースドライバ14を含む全体的なシステムとの関連で駆動回路15を示す。上述のように、駆動トランジスタ201は、ゲート電極203、第1の供給電極204、及び第2の供給電極205を有する。ELデバイス202は、第1の電極207、及び第2の電極208を有する。システムは、電圧源211、及び206を有する。なお、第1の電圧源211は、以下のカレントミラーユニットの説明を明確にするために、駆動回路15の外に示される。

【0032】

一般的にFETである駆動トランジスタ201、及びELデバイス202の動作は、本質的に同一の電流が、第1の供給電極204と、第2の供給電極205と、EL電極207、及び208とを介して、第1の電圧源211から第2の電圧源206に流れるものである。したがって、電流は、このつながりのいずれかの点で測定できる。第1の電圧源211において、ELパネルの外で電流を測定して、ELサブ画素の複雑さを低減できる。1つの実施形態において、本発明は、カレントミラーユニット210と、相関2重サンプルユニット220と、アナログ‐デジタルコンバータ230とを使用する。これらは、以下に「データ補正」において、詳細に説明されることになるであろう。

【0033】

図2に示す駆動回路15は、Nチャネル駆動トランジスタ構造であり、かつ非反転EL構造である。この場合、ELデバイス202は、トランジスタ201のソース205に接続され、ゲート電極203の電圧を高くすると、光出力を大きくするように指令され、電圧源211は、第2の電圧源206よりも高電位であるので、電流は、211から206に流れる。しかしながら、本発明は、Pチャネル駆動トランジスタ、又はNチャネル駆動トランジスタ、及び非反転ELデバイス、反転ELデバイスのいずれの組み合わせに適用可能である。また本発明は、LTPS駆動トランジスタ、又はa−Si駆動トランジスタに適用可能である。

【0034】

〔データ補正〕

〔ハードウェア〕

さらに図2を参照すると、パネル上の特別な電子機器に拠ることなしに、それぞれのELサブ画素の電流を測定するために、本発明は、カレントミラーユニット210と、相関2重サンプル(CDS)ユニット220と、アナログ‐デジタルコンバータ(ADC)230とを有する測定回路16を採用する。

【0035】

カレントミラーユニット210は、電圧源211に取り付けられるが、供給211、供給206、又はELデバイス、並びに駆動トランジスタの第1の供給電極、及び第2の供給電極を通る電流経路の他のいずれかに取り付けることができる。これは、ELデバイスに光を発光させる駆動電流の経路である。第1のカレントミラー212は、スイッチ200を介してEL駆動回路15に駆動電流を供給し、出力213にミラー電流を作り出す。ミラー電流は、駆動電流と等しくできる。一般的に、ミラー電流は、駆動電流の関数にできる。例えば、ミラー電流は、複数の駆動電流にして、付加的な測定システム利得を提供できる。第2のカレントミラー214と、バイアス供給215は、バイアス電流を第1のカレントミラー212に印加して、測定結果が回路の寄生インピーダンスに影響されないように、第1のカレントミラーにおける電圧変動を低減する。また、この回路は、測定回路の電流引き込みにより、カレントミラーにおける電圧が変化することによって、測定されるELサブ画素を流れる電流の変化を低減する。有利には、これは、電流に依存する駆動トランジスタ、端末における電圧を変化させる可能性がある簡素な感知抵抗などの他の電流測定の選択肢よりも、信号対雑音比が改良される。最終的には、電流‐電圧(I‐V)コンバータ216は、さらなる処理のために、第1のカレントミラーのミラー電流を電圧信号に変換する。I‐Vコンバータ216は、トランスインピーダンス増幅器、又はローパスフィルタを有してもよい。単一のELサブ画素において、I‐Vコンバータの出力は、そのサブ画素の経年劣化信号にできる。以下に説明されるように、複数のサブ画素の測定では、測定回路は、経年劣化信号を作り出す電圧信号に応答する回路をさらに有してもよい。先に説明したように、駆動トランジスタ、及びELデバイスの特性が、駆動トランジスタ、及びELデバイスの動作によって時間とともに変化すると、Vth、及びVoledは、変化することになるであろう。この結果として、測定電流、すなわち経年劣化信号は、これらの変動に応じて変化することになるであろう。これは、以下に「アルゴリズム」において、さらに説明されることになるであろう。

【0036】

1つの実施形態において、第1の電圧源211は、+15VDCの電位を有し、第2の電力供給206は、−5VDCの電位を有し、バイアス供給215は、−16VDCの電位を有することができる。バイアス供給215の電位は、全ての測定電流のレベルにおいて、安定したバイアス電流を提供するように、第1の電圧源211の電位に基づいて選択できる。

【0037】

ELサブ画素が測定されないとき、カレントミラーは、継電器、又はFETにできるスイッチ200によって、パネルから電気的な接続を切断することができる。スイッチは、駆動トランジスタ201の第1の電極、及び第2の電極を流れる駆動電流の流れと測定回路との電気的な接続を選択的にできる。測定の間、スイッチ200は、第1の電圧源211を第1のカレントミラー212に電気的に接続して、測定を可能にする。通常動作の間、スイッチ200は、第1の電圧源211を第1のカレントミラーではなく、第1の供給電極に直接接続することによって、駆動電流の流れから測定回路を除去する。このため、測定回路は、パネルの通常動作には影響を与えることはない。また有利には、カレントミラー212、及び214のトランジスタなどの測定回路の構成素子は、動作電流でなく、測定電流のみのための大きさにできる。一般的に、通常動作は、測定よりも非常に大きな電流を引き出すので、これによって、測定回路の大きさ、及び価格の実質的な縮減が可能になる。

【0038】

〔サンプリング〕

カレントミラーユニット210は、1つのELサブ画素の回路の測定が可能である。複数のサブ画素の電流を測定するためには、1つの実施形態において、本発明は、標準的なOLEDソースドライバとともに使用可能なタイミングスキームを有する相関2重サンプリングを使用する。

【0039】

図3を参照すると、本発明において有用なELパネル30は、3つの主要な構成要素を有する。すなわち、列線32a、32b、及び32cを駆動するソースドライバ31と、行線34a、34b、及び34cを駆動するゲートドライブ33と、サブ画素マトリクス35とである。本発明に係る1つの実施形態では、ソースドライバ31は、線形ソースドライバ14にできる。なお、ソースドライバと、ゲートドライバとは、1つ、又は2つ以上のマイクロチップを有してもよい。なおまた、用語「行」、及び「列」は、ELパネルのいずれの特定の方向をも示唆しない。サブ画素のマトリクスは、概して同一であり、かつ概して行、及び列のアレイに配列される複数のELサブ画素を有する。ELサブ画素はそれぞれ、ELデバイス202を備える駆動回路15を有する。駆動回路はそれぞれ、ELデバイスに電流を印加し、選択トランジスタ36と、駆動トランジスタ201とを有する。スイッチとして動作する選択トランジスタ36は、行線、及び列線を駆動トランジスタ201に電気的に接続する。選択トランジスタのゲートは、適当な行線34に電気的に接続され、選択トランジスタのソース電極、及びドレイン電極は、1つが、適当な列線32に電気的に接続され、1つが、駆動トランジスタのゲート電極に接続される。ソースが、列線、又は駆動トランジスタのゲート電極のいずれに接続されても、選択信号の動作には影響しない。本発明の1つの実施形態において、サブ画素マトリクス35のELデバイス202はそれぞれ、OLEDデバイスにしてもよく、サブ画素マトリクス35の駆動トランジスタは、アモルファスシリコン・トランジスタにしてもよい。

【0040】

また、ELパネルは、第1の電圧源211と、第2の電圧源206とを有する。図10を参照すると、電流は、駆動トランジスタの第1の供給電極204と、第1の電圧源211とを電気的に接続するPVDD母線1011などによって、駆動トランジスタ201に供給できる。ELデバイス202の第2の電極208と、第2の電圧源206とを電気的に接続する薄板カソード1012は、電流経路を完成することができる。明確にするために、図3を再び参照すると、電圧源211、及び206が、図3に示される。ここで、供給にサブ画素を接続する様々なスキーマとともに本発明を採用するように、電圧源211、及び206は、それぞれのサブ画素に接続できる。それぞれの駆動トランジスタの第2の供給電極205は、対応するELデバイスの第1の電極207に電気的に接続できる。

【0041】

図2に示すように、ELパネルは、第1の電源供給211に電気的に接続される測定回路16を有してもよい。この回路は、第1の電圧源と、第2の電圧源とを流れる電流を測定する。これは、キルヒホッフの法則と同様である。

【0042】

本パネルの典型的な動作において、ソースドライバ31は、列線32に適当なアナログ駆動トランジスタ制御信号を駆動する。次いで、ゲートドライバ33は、第1の行線34aを活性化し、適当な制御信号が選択トランジスタ36を介して、適当な駆動トランジスタのゲート電極に通されて、これらのトランジスタに取り付けられたELデバイス202に電流を印加する。次いで、ゲートドライバは、第1の行線34aを非活性にして、選択トランジスタを通った値を、他の行の制御信号が破損することを防止する。ソースドライバは、列線の次の行の制御信号を駆動し、ゲートドライバは、次の行34bを活性化する。この処理は、全ての行で繰り返す。このように、パネル上の全てのサブ画素は、1度に1つの行に適当な制御信号を受信する。行時間(row time)は、1つの行線(34aなど)を活性化する時間と、次(34bなど)を活性化する時間との間の時間である。行時間は、一般的に全ての行で一定である。

【0043】

有利には、本発明に従って、この行ステップを使用して、1度に1つのサブ画素のみを活性化し、列を下方に動かす。図3を参照して、列32aのみを駆動し、全てのサブ画素をオフにして開始すると仮定する。列線32aは、High電圧などのアナログ駆動トランジスタ制御信号を有して、取り付けられるサブ画素に光を発光させることになるであろう。他の全ての列線32b..32cは、Low電圧などの制御信号を有して、取り付けられるサブ画素に光を発光させないであろう。全てのサブ画素がオフなので、パネルは、電流を引き込まない(しかし、以下の「ノイズのソース」を参照のこと)。上部の行から開始して、行は、時間軸の目盛によって示される点で活性化する。行が活性化すると、列32aに取り付けられるサブ画素が動作する。そして、パネルが引き出す総電流が上昇する。ここで図4aを参照すると、サブ画素が活性化し(行線34aなど)、測定回路16によって、その電流が測定される。具体的には、測定されるものは、上述のように第1の電圧源、及び第2の電圧源を介する電流を表す電流測定回路からの電圧信号である。明確にするために、電流を表す電圧信号の測定を「電流測定」と称する。時間2において、次のサブ画素が活性化し(列線34bなど)、電流42が測定される。電流42は、第1のサブ画素からの電流と、第2のサブ画素からの電流との和である。第2の測定42と、第1の測定41との間の差異は、第2のサブ画素により引き出される電流である。このように、処理は、それぞれのサブ画素の電流を測定して、第1の列を下って進む。次いで、第2の列を測定し、第3、第4とパネルの残りについて測定する。なお、測定(41、42など)はそれぞれ、サブ画素を活性化した後にできるだけ早く行われる。理想的な状況では、測定はそれぞれ、次のサブ画素が活性化される前のいずれかの時間に行うことができるが、以下で説明されるように、サブ画素が活性化された後に迅速に測定することによって、自己発熱効果によるエラーを除去する可能性がある。この方法によって、測定結果は、サブ画素のセトリング・タイム(settling time)で許容されることになるであろう範囲で、迅速に行うことが可能になる。

【0044】

相関2重サンプリングユニット220は、測定電流をサンプリングして、経年劣化信号を作り出す。ハードウェアにおいて、図2におけるカレントミラーユニット210からの対応電圧信号を、サンプル及び保持ユニット(sample-and-hold unit)221、及び222にラッチすることによって、電流は、測定される。電圧信号は、I‐Vコンバータ216によって作り出すことができる。差動増幅器223は、連続するサブ画素の測定結果の間の差異をとる。サンプル及び保持ユニット221の出力は、差動増幅器223のプラス端子に電気的に接続され、サンプル及び保持ユニット222の出力は、差動増幅器223のマイナス端子に電気的に接続される。例えば、電流41を測定するときは、測定は、サンプル及び保持ユニット221にラッチされる。次いで、電流42を測定する(ユニット221にラッチされる)前に、ユニット221の出力は、第2のサンプル及び保持ユニット222にラッチされる。次いで電流42を、測定する。これにより、電流41は、ユニット222に保持され、電流42は、ユニット221に保持される。したがって、ユニット221の値からユニット222の値を減ずる差動増幅器の出力は、(電圧信号で示す)電流42から(電圧信号で示す)電流41を減ずるもの、すなわち差異43である。43などのそれぞれの電流の差異は、対応するサブ画素の経年劣化信号にできる。例えば、電流の差異43は、行線34bと、列線32aとに取り付けされたサブ画素の経年劣化信号にできる。このように、行を下り、列を横切ることにより、それぞれのサブ画素の測定と、それぞれのサブ画素が提供する経年劣化信号を測定できる。

【0045】

〔ノイズ源〕

実際には、電流波形は、きれいなステップではなく、波形が安定するのを待ってからようやく測定できる。それぞれのサブ画素を複数測定して、互いに平均化できる。この測定は、次のサブ画素に進む前に連続的に行うことができる。また、これは、別々に測定でき、パネルのサブ画素はそれぞれ、それぞれの経路で測定される。電圧源206と、211との間の容量は、セトリング・タイムになる可能性がある。通常の動作で見られるように、この容量は、内在するキャパシタ、又は外部のキャパシタによって提供される。有利には、測定中に外部のキャパシタとの電気的な結合を切断するために使用することができるスイッチが提供される。これにより、セトリング・タイムを削減することになるであろう。

【0046】

全ての電力供給は、可能な限りノイズがないように保つべきである。いずれかの電力供給のノイズは、電流測定に影響を与えることになるであろう。例えば、行を非活性化するために使用する電源供給(多くの場合VGL、又はVoffと称され、一般的に−8VDC近辺である)のノイズは、選択トランジスタを介して駆動トランジスタに容量的に結合され、電流に影響を与えるので、電流測定のノイズが多くなる。パネルが、分割供給面(split supply plane)などの複数の電源供給領域を有する場合は、これらの領域は、並列に測定できる。この測定では、領域間のノイズを分離し、測定時間を削減できる。

【0047】

1つの主要なノイズ源は、ソースドライバ自体である可能性がある。ソースドライバがスイッチングするときはいつでも、過渡ノイズは、電力供給面、及び個々のサブ画素に結合して、測定ノイズを生じる可能性がある。このノイズを削減するために、ソースドライバからの制御信号は、列を下る間、一定に保つことができる。例えば、RGBストライプパネル上の赤色のサブ画素の列を測定するとき、その行のソースドライバに供給される赤色コード値は、全ての列で一定にできる。これによって、ソースドライバの過渡ノイズを除去できる。

【0048】

ソースドライバは、現在の列(32aなど)の活性化から次の列(32bなど)の活性化に変更しなければならないため、ソースドライバの過渡は、列の最初、及び列の最後において、回避することは不可能である。この結果、いずれかの列の第1のサブ画素、及び続く1つ、又は2つ以上のサブ画素の測定は、過渡によるノイズの影響を受ける。1つの実施形態では、ELパネルは、可視される行の上部、又は下部に、ユーザに可視されない追加の行を有してもよい。ソースドライバの過渡が追加の行においてのみ生じるように十分な追加の行を配置し、可視的なサブ画素の測定が影響を受けないようにすることができる。他の実施形態において、行の開始におけるソースドライバの過渡と、その列の第1の行の測定との間、及びその列の最後の行の測定と、行の最後におけるソースドライバの過渡との間に、遅延を挿入することができる。

【0049】

パネルは、全てのサブ画素がオフのときでさえも、いくらかの電流を引き出す可能性がある。この「暗電流」は、遮断時の駆動トランジスタのリークによるものである可能性がある。暗電流は、DCバイアスノイズを測定電流に付加する。図4において、点49で示すように、これは、第1のサブ画素を活性化する前に、全てのサブ画素をオフにして測定することによって、除去できる。この場合、サブ画素1により引き出される電流は、単に測定41ではなく、測定41から測定49を減じたものになるであろう。

【0050】

〔電流の安定性〕

これまでの説明では、サブ画素がオンし、安定すると、残りの列が終わるまで電流が維持されると仮定された。この仮定を崩す可能性がある2つの効果は、記憶容量リーク効果と、内部サブ画素効果(within-subpixel effects)である。

【0051】

公知の技術である記憶容量は、すべてのサブ画素の一部にでき、駆動トランジスタのゲートと、基準電圧との間を電気的に接続できる。サブ画素の選択トランジスタのリーク電流は、記憶容量の電荷を徐々に抜き取る。駆動トランジスタのゲート電圧が変化して、電流が引き出される。また、サブ画素に取り付けられる列線が時間とともに値が変化している場合、AC素子を有するので、選択トランジスタの寄生容量を介して、記憶容量に結合する可能性がある。記憶容量の値が変化して、電流がサブ画素によって引き出される。

【0052】

記憶容量の値が安定しても、内部サブ画素効果は、測定を破損する可能性がある。共通の内部サブ画素効果は、サブ画素が引き出す電流を時間とともに変化させる可能性があるサブ画素の自己発熱である。a−Si TFTのドリフト移動度は、温度の関数である。温度が上昇すると、移動度が大きくなる(Kagan & Andry, op. cit., sec. 2.2.2, pp. 42−43)。電流が、駆動トランジスタを介して流れるとき、駆動トランジスタ、及びELデバイスの電力損失により、サブ画素が加熱されるので、トランジスタの温度が上昇するとともに、移動度が大きくなる。また、加熱によりVoledが下がる。OLEDが駆動トランジスタのソース端子に取り付けられる場合は、これによって、駆動トランジスタのVgsが上昇する可能性がある。これらの効果によって、トランジスタを流れる電流量が増加する。通常動作の下では、パネルが表示する画像の平均的な容量に基づく平均の温度に安定するので、自己発熱は、重要な効果ではない可能性がある。しかしながら、サブ画素電流を測定するとき、自己発熱は、測定を破損する可能性がある。図4bを参照すると、測定41は、サブ画素1を活性化した後、可能な限り早く行われる。この場合、サブ画素1の自己発熱は、測定に影響を与えない。しかしながら、測定41と、測定42との間の時間において、サブ画素1は、自己発熱して、量421だけ電流が増加するであろう。したがって、サブ画素の電流を表す計算上の差異43は、誤っているであろう。量421によって、過度に大きくなっているであろう。量421は、行時間当たりのサブ画素の電流の上昇である。

【0053】

自己発熱効果、及び同様なノイズ特性を作り出す他の内部サブ画素効果を補正するために、自己発熱を、特性化し、それぞれのサブ画素の既知の自己発熱要素を取り除くことができる。一般的にそれぞれのサブ画素は、それぞれの行時間の間に同一量の電流が上昇する。このため、連続するそれぞれのサブ画素において、活性化する全てのサブ画素の自己発熱を、取り除くことができる。例えば、サブ画素3の電流424を得るために、測定423は、要素421の2倍である自己発熱要素422を減少できる。要素421は、サブ画素当たりの要素であり、既に活性化している2つのサブ画素を乗じる。自己発熱は、何十、又は百もの行時間において、1つのサブ画素をオンすることによって特性化され、オンになっている間に定期的に電流を測定できる。時間に対応する電流の平均的な傾きは、1つの行時間で乗じることによって、行時間421当たりのサブ画素の上昇を計算できる。

【0054】

自己発熱、及び電力損失によるエラーは、測定基準ゲート電圧を低く選択することにより、低減可能である(図5aの510)が、電圧を高くすることによって、信号対雑音比が改善される。測定基準ゲート電圧は、これらの要因の平衡を保つように、パネル配置ごとに選択できる。

【0055】

〔アルゴリズム〕

図5aを参照すると、I−V曲線501は、経年劣化前のサブ画素の測定特性である。I−V曲線502は、経年劣化後のサブ画素の測定特性である。曲線501、及び502は、異なる電流レベルにおける同一の電圧差503、504、505、及び506で示される、主として水平方向のシフトによって分離される。すなわち、経年劣化の1次的な効果は、一定量ゲート電圧軸上でI−V曲線がシフトすることである。MOSFETの飽和領域で維持されるとき、これは、式Id=K(Vgs−Vth)2である(Lurch, N.Fundamentals of electronics, 2e. New York: John Wiley & Sons, 1971, pg. 110)。駆動トランジスタが動作すると、Vthは増加する。Vthが増加すると、Vgsが、それに応じて増加して、Idを一定に維持しなければならない。したがって、Vthが増加するときに、Vgsを一定にすると、Idが低くなる。

【0056】

図5aの例では、測定基準ゲート電圧510において、経年劣化していないサブ画素は、点511で表される電流を作り出す。電流は、そのサブ画素の経年劣化信号である。しかしながら、経年劣化したサブ画素は、そのゲート電圧において、点512aで表される、より低い電流量を作り出す。点511、及び521aは、異なる時間において行われる同一サブ画素の測定結果にできる。例えば、点511は、製造時の測定結果にでき、点512aは、顧客がいくらか使用した後の測定結果にできる。点512aで表される電流は、経年劣化していないサブ画素が電圧513(点512b)で駆動されるときに作り出されるであろう。このため、電圧シフトΔVth514は、電圧510、及び513の間の差異の電圧として計算される。このように、電圧シフト514は、経年劣化していな曲線に経年劣化した曲線を戻すために必要なシフトである。この例では、ΔVth514は、2V弱である。次いで、Vthシフトを補償し、経年劣化していないサブ画素と同一の電流で経年劣化したサブ画素を駆動するために、電圧差514は、指令された全ての駆動電圧(線形コード電圧)に加える。また、さらなる処理のために、パーセント電流(percent current)は、電流512aを電流511で除して計算される。それ故に、経年劣化していないサブ画素は、100%電流を有することになるであろう。パーセント電流は、本発明に従ういくつかのアルゴリズムで使用される。外部環境によって生じる可能性がある負の電流読み出し511は、0に留めるか、又は無視することができる。なお、パーセント電流は、常に測定基準ゲート電圧510において計算される。

【0057】

一般的に、経年劣化したサブ画素の電流は、経年劣化していないサブ画素の電流よりも大きくなる可能性があり、又は小さくなる可能性がある。例えば、温度が高いと、より多くの電流が流れるために、高温度環境下のほとんど経年劣化していないサブ画素は、低温度環境下の経年劣化していないサブ画素よりも多くの電流を引き出す可能性がある。本発明に係る補償アルゴリズムは、いずれの場合も取り扱うことができる。すなわち、ΔVth514は、正にでき、又は負にできる(経年劣化していない画素においては、ゼロにできる)。同様に、パーセント電流は、100%よりも大きくでき、又は小さくできる(経年劣化していない画素においては、正確に100%にできる)。

【0058】

Vthシフトによる電圧差は、全ての電流で同一であるので、I−V曲線のいずれか単一の点を測定して、この差を決定できる。1つの実施形態では、有利には、測定は、高いゲート電圧で行われ、測定の信号対雑音比が増加するが、曲線の何れのゲート電圧を使用できる。

【0059】

Voledシフトは、経年劣化の2次的な効果である。ELデバイスが動作すると、Voledがシフトして、I−V曲線が、もはや経年劣化していない曲線の単なるシフトではなくなる。これは、Voledが電流に非線形に上昇するためである。これにより、低電流と異なるように高電流にVoledが影響を与えることになるであろう。この効果によって、I−V曲線がシフトするとともに、水平方向に広げられる。Voledシフトを補償するために、2つの測定を行い、曲線が広がった大きさを決定できる。又は負荷の下でのOLEDの典型的なVoledを特性化して、開ループの方法でVoledの寄与を推定することが可能である。双方は、容認可能な結果を作り出すことができる。片対数目盛のI−V曲線である図5bを参照すると、要素550は、Vthシフトによるものであり、要素552は、Voledシフトによるものである。Voledシフトは、測定装置を搭載したOLEDサブ画素を、期間が長い時間の標準的な入力信号によって駆動すること、及びVthと、Voledを定期的に測定することによって、特性化できる。2つの測定は、OLEDと、トランジスタとの間の測定装置を搭載したサブ画素にプローブ点を提供することによって、独立に行うことができる。この特性を使用して、パーセント電流は、Vthシフトのみでなく、適当なΔVth、及びVoledにマッピングできる。

【0060】

OLED効率の損失は、3次的な経年劣化効果である。OLEDが経年劣化すると、効率が低下し、同一の電流量では、同一の光量をもはや作り出すことができない。光学センサ、又は付加的な電子機器を要せずにこれを補償するために、Vthシフトの関数としてOLED効率の損失を特性化して、先のレベルの光出力に戻すために必要な追加電流量を推定することが可能である。OLED効率の損失は、測定装置を搭載したOLEDサブ画素を、期間が長い時間の標準的な入力信号によって駆動すること、及びVthと、Voledと、Ioledとを様々な駆動レベルで定期的に測定することによって、特性化できる。効率は、Ioled/Voledとして計算でき、この計算は、Vth、又はパーセント電流に相関してもよい。なお、Vthシフトは、簡単に元に戻されるが、OLED効率はそうではないので、この特性は、Vthが順方向であるときに、最も効率的な結果が得られる。Vthシフトが逆方向である場合、OLED効率の損失と、Vthシフトとの相関は、複雑になる。さらなる処理のために、上述のパーセント電流の計算に類似するパーセント効率は、経年劣化した効率を新しい効率で除することにより計算できる。

【0061】

図9を参照して、実験データへの90などの直線の当てはめ(linear fit)とともに、様々な駆動レベルにおけるパーセント効率の実験プロットを、パーセント電流の関数として示す。プロットが示すように、所与のいずれの駆動レベルにおいて、効率は、パーセント電流に線形の関連になる。この線形モデルにより、効果的な開ループ効率補償が可能になる。同様な結果が「ポリマー発光ダイオードにおける寿命、及び劣化効果("Lifetime and degradation effects in polymer light-emitting diodes," J. App. Phys. 85.4 (1999): 2441-2447)」において、具体的には2445ページの図12で示されるように、Parkerらにより報告される。またParkerらは、単一の機構が、効率の損失(輝度の減少)、及びVoled上昇(電圧増加)の双方に関与することを提案する。

【0062】

Vth、及びVoledを含む駆動トランジスタ、及びELデバイスの特性は、駆動トランジスタ、及びELデバイスの時間に伴う動作によって、時間とともに変化する。パーセント電流は、これらの変動を表す経年劣化信号として使用でき、これらの変動を補償することを可能にする。

【0063】

このアルゴリズムは、OLEDに関連して説明されているが、当業者には明らかなように、他のELデバイスもまた、これらの分析を適用して補償できる。

【0064】

〔実施〕

図6aを参照すると、線形コード値が指令駆動電圧であり、変更線形コード値が補償電圧である補償器の実施が示される。補償器は、1度に1つのサブ画素で動作する。すなわち、複数のサブ画素は、逐次処理できる。例えば、補償は、左から右へ、上から下への従来のスキャン指令において信号源から線形コード値を着信して、それぞれのサブ画素のために実行できる。補償は、補償回路の複数の複製を平行させることによって、又は補償器をパイプラインすることによって、複数の画素で同時に実行できる。これらの技術は、当業者には明らかであろう。

【0065】

補償器60への入力は、サブ画素位置601、及び指令駆動電圧を表すことができるサブ画素の線形コード値602である。補償器は、線形コード値を変更して、線形ソースドライバのための変更線形コード値を作り出す。これは、補償電圧アウト603などにしてもよい。補償器は、サブ画素の経年数を決定するブロック61、OLED効率を随意的に補償するブロック62、経年数に基づいて補償を決定するブロック63、及び補償するブロック64の主要な4つのブロックを有することができる。ブロック61、及び62は、OLED効率の補償に主に関連し、ブロック63、及び64は、電圧補償、特にVth/Voled補償に主に関連する。

【0066】

図6bは、ブロック61、及び62の拡大図である。サブ画素配置601を使用して、製造時に記憶された基準経年劣化信号の測定i0611と、最も新しく記憶された経年劣化信号の測定i1とを読み出す。経年劣化信号の測定は、先に「データ収集」において説明された測定回路が出力する経年劣化信号にしてもよい。測定結果は、それぞれ異なった時間における位置601のサブ画素の経年劣化信号の測定結果にしてもよい。この測定結果は、メモリ619に記憶できる。メモリ619は、フラッシュメモリなどの不揮発性RAM、及びEEPROMなどのROMにできる。i0測定は、NVRAM、又はROMに記憶できる。i1測定は、NVRAMに記憶できる。測定612は、単一の測定、いくつかの測定の平均、測定の指数加重移動平均、又は当業者に明らかであろう他の平滑方法の結果にしてもよい。

【0067】

パーセント電流613は、上述のように、i1/i0として計算でき、0(故障した画素)、1(変化なし)、1未満(電流損失)、1より大きい(電流利得)にできる。一般的に、最新の経年劣化信号の測定結果は、製造時の測定結果よりも小さいので、パーセント電流は、0と1との間になる。パーセント電流は、個々の測定i0、i1と同様に、電流の変動を示すので、メモリ619に直接記憶される場合は、パーセント電流自体を経年劣化信号にできる。

【0068】

パーセント電流613は、次の処理段63に送信されるとともに、モデル695に入力されて、パーセントOLED効率614を決定する。モデル695は、最新の測定時における所与の電流による発光量を、製造時の電流による発光量で除したものである効率614を出力する。電流を得ている画素において、効率の損失を計算することは難しいので、パーセント電流が1よりも大きい場合には、1の効率、すなわち損失がないことが生じる可能性がある。またモデル695は、破線矢印で示すように、線形コード値602の関数にしてもよい。この場合、OLED効率は、指令電流に依存する。線形コード値602をモデル695の入力として含むか否かは、パネル設計の寿命試験、及びモデリングによって決定できる。

【0069】

同時に、補償器は、指令電圧などの線形コード値を602において受信する。この線形コード値は、製造時に測定されたパネルの元のI−V曲線691を通って、所望の電流621を決定する。これを、動作628において、パーセント効率614で除して、所望の電流の光出力を、製造時の値に戻す。結果として生じるブースト電流(boosted voltage)は、曲線691の反転である曲線692を通って、どの指令電流が、効率の損失が存在する下で所望の光量を作り出すことになるかを決定する。曲線692からの値は、効率調整電流622として次の段に通される。

【0070】

効率補償が要求されない場合、随意的なバイパス経路626に示すように、入力電圧602は、変化せずに、効率調整電流622として次の段に送信される。この場合、パーセント電流613は、計算すべきであるが、パーセント効率614は、計算する必要はない。

【0071】

図6cは、図6aの拡大図であるブロック63、及び64である。ブロック63、及び64は、パーセント電流613、及び効率調整電流622を、前段から受信する。「補償を得る」ブロック63は、反転I−V曲線692を介して電流損失623をマッピングする段階と、測定基準ゲート電圧(510)から結果(513)を減じて、VthシフトΔVth631を獲得する段階とを有する。「補償する」ブロック64は、(式1)で与えられる補償電圧アウト603を計算する動作633を有する。

Vout=Vin+ΔVth(1+α(Vg,ref−Vin)) (式1)

ここで、Voutは、603であり、ΔVthは、631であり、αは、アルファ値632であり、Vg,refは、測定基準ゲート電圧510であり、Vinは、効率調整電圧622である。補償電圧アウトは、線形ソースドライバの変更線形コード値として表すことができ、駆動トランジスタ、及びELデバイスの特性の変動を補償できる。

【0072】

ストレートなVthシフトの場合、αはゼロになり、動作633は、効率調整電圧622に加算されるVthシフト量が減少することになるであろう。いずれか特定のサブ画素において、加算量は、新たな測定が行われるまで一定である。したがって、この場合、動作633において加算させる電圧は、測定が行われた後に、予め計算することができ、ブロック63、及び64を無くして、記憶値を検索して加算することが可能になる。これにより、かなりの量の論理回路を省くことができる。

【0073】

〔領域間共通処理、及びビット深度〕

従来の画像処理経路は、典型的には非線形コード値(NLCV)を作り出す。すなわち、輝度に非線形な関係を有するデジタル値を作り出す(Giorgianni & Madden. Digital Color Management: encoding solutions. Reading, Mass.: Addison-Wesley, 1998. Ch. 13, pp. 283- 295)。非線形出力を使用することは、典型的なソースドライバの入力領域に一致し、人間の目の精度範囲にコード値の精度範囲を一致させる。しかしながら、Vthシフトは、電圧領域の動作であるので、線形電圧空間で最も簡単に実行される。線形ソースドライバを使用するとともに、ソースドライバより先に領域変換を実行することで、非線形領域の画像処理経路を、線形領域の補償器に効果的に組み込むことができる。なお、この説明は、デジタル処理に関するものであるが、アナログ処理をアナログシステム、又はデジタル/アナログ混載システムにおいて、実行できる。なおまた、補償器は、電圧以外の線形空間において、動作できる。例えば、補償器は、線形電流空間において、動作できる。

【0074】

図7を参照すると、領域変換ユニット12、及び補償器13の効果を表すジョーンズダイアグラム(Jones-diagram)が示される。この図は、これらのユニットの数学的な効果を示し、実行方法を示すものではない。これらのユニットの実行は、アナログ、又はデジタルにできる。象限Iは、領域変換ユニット12の動作を表す。非線形コード値(NLCV、nonlinear code values)にできる軸701上の非線形入力信号は、変換711を介してマッピングして、軸702上に線形コード値(LCV、linear code values)を形成することによって、変換される。象限IIは、補償器12の動作を表す。軸702上のLCVは、721、及び722などの変換を介してマッピングされて、変更線形信号値(CLCV、changed linear code values)を軸703上に形成する。

【0075】

象限Iを参照すると、領域変換ユニット12は、NLCVなどの非線形入力信号を受信し、LCVに変換する。この変換は、輪郭黒色、及びクラッシュ黒色(contouring and crush blacks)などの好ましくない可視的なアーチファクトを回避するために、十分な解像度により実行すべきである。図7に示すように、デジタルシステムにおいて、NLCV軸701は、量子化できる。この場合、LCV軸702は、隣接する2つのNLCV間の変換711における最も小さい変化を表すのに十分な解像度を有するべきである。これは、NLCVステップ712として示され、LCVステップ713に対応する。LCVは、線形で規定されるので、LCV軸702全体の解像度は、ステップ713を示すために、十分にすべきである。その結果として、LCVは、画像情報の損失を回避するために、NLCVよりも細かい解像度で規定できる。解像度は、ナイキスト・サンプリング理論による類推によって、ステップ713の2倍の解像度にできる。

【0076】

変換711は、経年劣化していないサブ画素の理想的な変換である。変換711は、いずれのサブ画素の経年劣化、又は全体としての画素の経年劣化には関係がない。具体的には、変換711は、Vth、Voled、又はOLED効率のいずれか変化によって、修正されない。全ての色について1つの変換にでき、又はそれぞれの色について1つの変換にできる。有利には、領域変換ユニットは、変換711によって、画像処理経路を補償器から切り離すことによって、2つが情報を共有することなしに、ともに動作することが可能になる。これによって、双方の実施が簡素化される。

【0077】

象限IIを参照すると、補償器13は、画素当たりのバイアスにおいて、LCVを変更線形コード値(CLCV)に変更する。図7において、一般性を失わないストレートなVthシフトである補正である簡単な場合が示される。ストレートなVthシフトは、LCVからCLCVへのストレートな電圧シフトによって、補正できる。他の経年劣化効果は、「実施」において既に説明したように、取り扱うことができる。

【0078】

曲線721は、経年劣化していないサブ画素のための補償器の動作を表す。この場合、CLCVは、LCVと同一にすることができる。曲線722は、経年劣化したサブ画素のための補償器の動作を表す。この場合、CLCVは、問題となるサブ画素のVthシフトを表すオフセットをLCVに加えることができる。この結果として、一般的には、CLCVは、補償のためのヘッドルームを提供するために、LCVよりも大きな範囲が必要になるであろう。例えば、サブ画素が、新しいときに256個のLCVが必要であり、寿命に亘る最大シフトが128LCVである場合、CLCVは、経年劣化が激しいサブ画素の補償のクリッピングを回避するために、384=256+128までの値を表なければならない必要があるであろう。

【0079】

図7において、領域変換ユニット、及び補償器の効果の完全な例を示す。図7の破線矢印に従うと、3のNLCVが、領域変換ユニット12によって、象限Iに示されるように、変換711を介して9のLCVに変換される。経年劣化していないサブ画素では、補償器13は、象限IIに示すように、曲線721によって、9のCLCVとして通過することになるであろう。12CLCV程度のVthシフトを有する経年劣化したサブ画素において、9のLCVは、曲線722によって、9+12=21のCLCVに変換されることになるであろう。

【0080】

実際には、NLCVは、画像処理経路からのコード値にでき、8ビット以上有してもよい。フレームごとに、パネル上のそれぞれのサブ画素のためのNLCVにしてもよい。LCVは、電圧を表す線形値にして、ソースドライバによって、駆動できる。先に説明したように、LCVは、十分な解像度を有するために、NLCVよりも大きなビットを有してもよい。CLCVもまた、電圧を表す線形値にして、ソースドライバによって、駆動できる。先に説明したように、CLCVは、補償のためのヘッドルームを提供するために、LCVよりも大きなビットを有してもよい。本明細書で説明したように、入力NLCVから作り出して、それぞれのサブ画素のLCV、及びCLCVにすることができる。

【0081】

1つの実施形態において、コード値(NLCV)、すなわち画像処理経路からの非線形入力信号は、9ビット幅である。電圧を表すことができる線形コード値は、11ビット幅である。非線形入力信号から線形コード値への変換は、LUT、又は関数により実行できる。補償器は、所望の電圧を表す11ビットの線形コード値を含むことができ、12ビットの変更線形コード値を作り出して、線形ソースドライバ14に送信できる。次いで、線形ソースドライバは、変更線形コード値に応答して、取り付けられたELサブ画素の駆動トランジスタのゲート電極を駆動できる。比較器は、出力が入力よりも深いビット深度を有して、補償のためのヘッドルームを提供できる。すなわち、新しく広げた範囲において、最小線形コード値ステップ75に必要な同一の解像度を維持しながら、電圧範囲78を電圧範囲79に広げることができる。補償器の出力範囲は、曲線71の範囲内で広げることができるとともに、曲線71の範囲よりも大きく広げることができる。

【0082】

パネル設計はそれぞれ、最大Vthシフト73、Voled上昇、及び効率の損失がパネルの設計寿命を超えることになるように決定するように特性化でき、補償器、及びソースドライバは、補償するために十分な範囲を有することができる。この特性化は、標準的なトランジスタの飽和領域Ids式を用いて、必要な電流から必要なゲートバイアス及びトランジスタ寸法まで進めることができる。次いで、a−Siの時間に伴う劣化の従来の様々なモデルを用いて、時間に伴うVthシフトに進めることができる。

【0083】

〔動作のシーケンス〕

〔パネル設計特性〕

この項では、特定のOLEDパネル設計の大量生産との関係で説明される。大量生産を開始する前に、設計が特性化される。加速寿命試験を実行でき、I−V曲線は、様々なレベルに経年劣化された様々なサンプルパネルにおける様々な色の様々なサブ画素について測定される。測定に必要な数、及び形式、並びに経年劣化レベルの数、及び形式は、具体的なパネルの特性に依存する。これらの測定によって、値アルファ(α)を計算できるとともに、測定基準ゲート電圧を選択できる。アルファ(図6c、項目634)は、時間に伴うストレートなシフトからの偏差を表す値である。0のアルファ値は、Vthシフトのみなどの場合のように、全ての経年劣化が電圧軸に対してストレートなシフトであることを示す。測定基準ゲート電圧(図5a、310)は、補償のための経年劣化信号の測定が行われる電圧であり、電力低下を抑えながら良好なS/N比を提供するように選択できる。

【0084】

α値は、最適に計算できる。一例を表1に示す。ΔVthは、いくつかの経年劣化の条件下で、いくつかのゲート電圧で測定できる。次いで、ΔVth差異は、それぞれのΔVthと、測定基準ゲート電圧310におけるΔVthとの間で計算される。Vg差異は、それぞれのゲート電圧と、測定基準ゲート電圧310との間で計算される。次いで、測定基準ゲート電圧310における適当なΔVthを式のΔVthに使用し、適当に計算されたゲート電圧差異を(Vg,ref−Vin)として使用して、式1の内項ΔVth・α(Vg,ref−Vin)をそれぞれの測定について計算して、予測ΔVth差異を得ることができる。次いでα値を繰り返して選択するとともに、好適には数学的に最小化して、予測ΔVth差異と、計算されるΔVth際との間のエラーを低減できる。エラーは、最大差、又はRMS差として表すことができる。また、Vgの差の関数である最小二乗適合などの従来からの他の方法を使用できる。

【0085】

【表1】

【0086】

α、及び測定基準ゲート電圧に加えて、特性は、上述のように、Vthシフトの関数としてVoledシフトを決定し、Vthシフト、サブ画素当たりの自己発熱要素、最大Vthシフト、Voledシフト、及び効率の損失の関数として効率の損失を決定し、非線形‐線形変換、及び補償器に必要な解像度を決定する。必要な解像度は、名称を「RGBWディスプレイの較正(Calibrating RGBW Displays)」という同一出願人の同時係属のAlessiらによる2007年4月13日付の米国出願シリアル番号第11/734934号などのパネル較正手段と併せて特性化できる。この出願は参照することにより本明細書に包含される。また以下の「現場において」で説明されることになるように、特性化は、実施において特性化測定を行う条件を決定する。これら全ての決定は、当業者が行うことができる。

【0087】

〔大量生産〕

設計が特性化されると、量産を開始できる。製造時に、1つ、又は2つ以上のI−V曲線を、作成するパネルごとに測定する。これらのパネルの曲線は、複数のサブ画素の曲線の平均にできる。パネルの種々の色には、別個の曲線にでき、またパネルの種々の領域には、別個の曲線にできる。電流は、現実的なI−V曲線を作成するのに十分な駆動電圧において測定できる。I−V曲線における何らかのエラーは、結果に影響を与える可能性がある。また、測定時において、基準電流、すなわち測定基準ゲート電圧における電流は、パネル上の全てのサブ画素において測定できる。I−V曲線、及び基準電流は、パネルに記憶され、現場に送られる。

【0088】

〔現場において〕

現場に置かれると、パネル上のサブ画素は、駆動される程度に依存して種々の割合で経年劣化する。いくらかの時間の後、1つ、又は2つ以上の画素は、補償に必要とされるのに十分に大きくシフトしている。その時間を決定する方法を以下で考察する。

【0089】

補償するために、補償測定が行われ、適用される。補償測定は、測定基準ゲート電圧におけるそれぞれのサブ画素の電流である。測定は、先に「アルゴリズム」において説明したように適用される。測定は、サブ画素を駆動するときにいつでも適用できるように、次の測定が行われるまで記憶される。全体的なパネル、又はパネルのいずれかのサブセットは、補償測定が行われるときに、測定できる。いずれかのサブ画素を駆動するとき、そのサブ画素の最新の測定を補償に使用できる。またこれは、サブ画素の第1のサブセットを1つの時間で測定でき、第2のサブセットを他の時間に測定でき、最新のパスにおいて全てのサブ画素が測定されていない場合でさえも、パネルに亘る補償が可能であることを意味する。また1つのサブ画素よりも大きなブロックを測定し、同一の補償をブロックの全てのサブ画素に適用するが、この場合、ブロック境界のアーチファクトが導入されないように注意する。また、1つのサブ画素よりも大きなブロックを測定することによって、高い空間周波数パターンの可視的な焼付けへの脆弱性が導入される。このパターンは、ブロックの大きさよりも小さなパターンを有してもよい。この脆弱性は、それぞれのサブ画素に比較して複数のサブ画素のブロックを測定するために必要な時間の低減とのトレードオフになる可能性がある。

【0090】

補償測定を所望の頻度で頻繁に、又は頻繁でなく行うことができる。典型的な範囲は、8時間に1度から4週間に1度にできる。図8において、パネルが活性化する長さとの関係で、補償測定が行われている頻度の一例が示される。この曲線は、単なる例である。実際には、この曲線は、設計の加速寿命試験を通して、具体的なパネル設計について決定できる。測定頻度は、駆動トランジスタ、及びELデバイスの時間にともなう特性変化の割合に基づいて選択できる。パネルが新しいときは、双方は、より早くシフトするので、補償測定は、パネルが古いときよりも新しいときのほうが、より頻繁に行なってもよい。補償測定を行うときを決定する、いくつかの方法がある。例えば、所与のいくつかの駆動電圧において、全体的にパネルを活性化するときに引き出される合計の電流を測定し、同一の測定の先の結果と比較できる。他の例では温度、及び環境光などのパネルに影響を与える環境要因を測定でき、環境温度がいくつかのしきい値よりも大きく変化しているなどの場合に、補償測定を行う。また、パネルの画像領域内、又は画像領域外のいずれかのそれぞれのサブ画素の電流を測定できる。パネルの画像領域の外部の場合、サブ画素は、測定の目的で提供される基準サブ画素にできる。サブ画素は、望ましい環境条件の何かの一部にさらすことができる。例えば、サブ画素は、不透明な材料で覆うことで、環境温度には応答するが、環境光には応答しないようにできる。

【0091】

上述の実施形態は、駆動回路のトランジスタがnチャネルトランジスタであるように構成される。トランジスタがpチャネルトランジスタである実施形態、又は適当な周知の修正を回路に行ったnチャネルと、pチャネルとのいくつかの組み合わせである実施形態もまた、本発明に有用であることは、当業者には理解されるであろう。また、説明される実施形態では、非反転(共通カソード)構造のOLEDが示される。本発明は、反転(共通アノード)構造もまた適用できる。さらに、上述の実施形態は、駆動回路のトランジスタがa−Siトランジスタであるように構成される。上述の実施形態は、時間の関数で安定しないいずれのアクティブマトリクスバックプレーンに適用できる。例えば、有機半導体材料と、酸化亜鉛とで形成されるトランジスタは、時間の関数で変化することが公知である。したがって、同一のアプローチをこのトランジスタに適用できる。さらにまた、トランジスタの経年劣化とは独立にELデバイスの経年劣化を補償できるので、本発明は、LTPS TFTなど経年劣化しないトランジスタを有するアクティブマトリクスバックプレーンにも適用できる。また、本発明は、OLED以外のELデバイスにも適用できる。他のELデバイスの型の劣化モデルは、本明細書で説明される劣化モデルとは異なるが、本発明に係る測定技術、モデリング技術、及び補償技術をなお適用できる。

【符号の説明】

【0092】

10 全体的なシステム

11 非線形入力信号

12 電圧領域変換

13 補償器

14 線形ソースドライバ

15 OLED駆動回路

16 電流測定回路

30 OLEDパネル

31 ソースドライバ

32a 列線

32b 列線

32c 列線

33 ゲートドライバ

34a 行線

34b 行線

34c 行線

35 サブ画素マトリクス

36 選択トランジスタ

41 測定

42 測定

43 差異

49 測定

60 補償器

61 ブロック

62 ブロック

63 ブロック

64 ブロック

71 I−V曲線

73 電圧シフト

74 コード値ステップ

75 電圧ステップ

76 電圧ステップ

78 電圧ステップ

79 電圧ステップ

90 直線の当てはめ

200 スイッチ

201 駆動トランジスタ

202 OLEDデバイス

203 ゲート電極

204 第1の供給電極

205 第2の供給電極

206 電圧源

207 第1の電極

208 第2の電極

210 カレントミラーユニット

211 電圧源

212 第1のカレントミラー

213 第1のカレントミラー出力

214 第2のカレントミラー

215 バイアス供給

216 電流‐電圧コンバータ

220 相関2重サンプリングユニット

221 サンプリング、及び維持ユニット

222 サンプリング、及び維持ユニット

223 差動増幅器

230 アナログ‐デジタルコンバータ

421 自己発熱量

422 自己発熱量

423 測定

424 差異

501 経年劣化していないI−V曲線

502 経年劣化しているI−V曲線

503 電圧の差異

504 電圧の差異

505 電圧の差異

506 電圧の差異

510 測定基準ゲート電圧

511 電流

512a 電流

512b 電流

513 電圧

514 電圧シフト

550 電圧シフト

552 電圧シフト

601 サブ画素配置

602 指令電圧

603 補償電圧

611 電流

612 電流

613 パーセント電流

614 パーセント効率

619 メモリ

621 電流

622 電圧

626 ブロック

628 動作

631 電圧シフト

632 アルファ値

633 動作

691 I−V曲線

692 反転I−V曲線

695 モデル

701 軸

702 軸

703 軸

711 変換の最小変化

712 ステップ

713 ステップ

721 変換

722 変換

1002 記憶容量

1011 母線

1012 薄板カソード

【特許請求の範囲】

【請求項1】

ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置であって、前記駆動回路は、前記駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、前記駆動トランジスタの第2の供給電極に電気的に接続される前記ELデバイスとを有し、

a)前記第1の供給電極、及び前記第2の供給電極を、異なった時間に流れる電流を測定して、前記駆動トランジスタ、及び前記ELデバイスの動作によって時間とともに生じる前記駆動トランジスタ、及び前記ELデバイスの特性の変動を示す経年劣化信号を提供する測定回路と、

b)線形コード値を提供する手段と、

c)前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号に応じて、前記線形コード値を変更する補償器と、

d)前記駆動トランジスタの前記ゲート電極を駆動するために、前記変更線形コード値に応じて、前記アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置。

【請求項2】

前記ELデバイスは、OLEDデバイスである請求項1に記載の装置。

【請求項3】

前記駆動トランジスタは、アモルファスシリコン・トランジスタである請求項1に記載の装置。

【請求項4】

前記第1の供給電極、及び前記第2の供給電極を介する電流の流れに前記測定回路を、選択的に電気的接続するスイッチをさらに有する請求項1に記載の装置。

【請求項5】

前記測定回路は、前記第1の供給電極、及び前記第2の供給電極を介して流れる前記駆動電流の関数であるミラー電流を作り出す第1のカレントミラーと、前記第1のカレントミラーの電圧変動を低減するために、前記第1のカレントミラーにバイアス電流を印加する第2のカレントミラーとを有する請求項1に記載の装置。

【請求項6】

前記測定回路は、電圧信号を作り出すミラー電流に応答する電圧変換器への電流と、前記補償器に前記経年劣化信号を提供する前記電圧信号に応答する手段とをさらに有する請求項5に記載の装置。

【請求項7】

非線形入力信号を受信し、かつ前記非線形入力信号を前記線形コード値に変換する手段をさらに有する請求項1に記載の装置。

【請求項8】

前記変換手段は、ルックアップテーブルを有する請求項7に記載の装置。

【請求項9】

前記補償器は、効率補償手段と、電圧補償手段とを有する請求項1に記載の装置。

【請求項10】

前記補償器は、基準経年劣化信号測定、及び最新の経年劣化信号測定を記憶するメモリをさらに有する請求項1に記載の装置。

【請求項11】

ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する方法であって、前記駆動回路は、前記駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、前記駆動トランジスタの第2の供給電極に電気的に接続される前記ELデバイスとを有し、

a)前記第1の供給電極、及び前記第2の供給電極を、異なった時間に流れる電流を測定して、前記駆動トランジスタ、及び前記ELデバイスの動作によって時間とともに生じる前記駆動トランジスタ、及び前記ELデバイスの特性の変動を示す経年劣化信号を提供するステップと、

b)線形コード値を提供するステップと、

c)前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号に応じて、前記線形コード値を変更するステップと、

d)前記駆動トランジスタの前記ゲート電極を駆動するために、前記変更線形コード値に応じて、前記アナログ駆動トランジスタ制御信号を作り出すステップと、

を有する方法。

【請求項12】

前記ELデバイスは、OLEDデバイスである請求項11に記載の方法。

【請求項13】

前記駆動トランジスタは、アモルファスシリコン・トランジスタである請求項11に記載の方法。

【請求項14】

ステップbは、非線形入力信号を受信するステップと、前記非線形入力信号を前記線形コード値に変換するステップとを有する請求項11に記載の方法。

【請求項15】

前記変換するステップは、ルックアップテーブルを使用するステップを有する請求項14に記載の方法。

【請求項16】

ELパネルの複数のELサブ画素の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置において、第1の電圧源と、第2の電圧源と、複数のELサブ画素とを前記ELパネルに有し、駆動回路のELデバイスは、それぞれのELサブ画素の前記ELデバイスに電流を印加し、駆動回路はそれぞれ、前記第1の電圧源に電気的に接続される第1の供給電極と、ELデバイスの第1の電極に電気的に接続される第2の供給電極とを有する駆動トランジスタを有し、ELデバイスはそれぞれ、前記第2の電圧源に電気的に接続される第2の電極を有し、改良点は、

a)前記第1の電圧源、及び前記第2の電圧源を、異なった時間に流れる電流を測定して、サブ画素の前記駆動トランジスタ、及び前記ELデバイスの動作によって時間とともに生じる前記駆動トランジスタ、及び前記ELデバイスの特性の変動を示すそれぞれのサブ画素の経年劣化信号を提供する測定回路と、

b)それぞれのサブ画素の線形コード値を提供する手段と、

c)それぞれのサブ画素の前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号に応じて、前記線形コード値を変更する補償器と、

d)前記駆動トランジスタの前記ゲート電極を駆動するために、前記変更線形コード値に応じて、前記アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置。

【請求項17】

ELデバイスはそれぞれ、OLEDデバイスであり、駆動トランジスタはそれぞれ、アモルファスシリコン・トランジスタである請求項16に記載の装置。

【請求項18】

前記測定回路は、

a)電圧信号を作り出す電圧変換器への電流と、

b)前記電圧信号に応答して、前記補償器に前記経年劣化信号を提供する相関2重サンプリングユニットと、

を有する請求項16に記載の装置。

【請求項19】

非線形入力信号を受信し、かつ前記非線形入力信号を前記線形コード値に変換する手段をさらに有する請求項16に記載の装置。

【請求項20】

前記補償器は、それぞれのサブ画素の基準経年劣化信号測定、及びそれぞれのサブ画素の最新の経年劣化信号結果を記憶するメモリをさらに有する請求項16に記載の装置。

【請求項21】

前記線形ソースドライバは、1つ、又は2つ以上のマイクロチップを有する請求項16に記載の装置。

【請求項22】

前記補償器は、前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号、及び前記線形コード値に応答して前記線形コード値を変更する請求項1に記載の装置。

【請求項23】

前記補償器は、前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号、及び前記線形コード値に応答して前記線形コード値を変更するステップをさらに有する請求項11に記載の方法。

【請求項24】

前記改良点は、前記補償器が、それぞれのサブ画素の前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号、及び前記線形コード値に応答して前記線形コード値を変更する請求項16に記載の装置。

【請求項1】

ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置であって、前記駆動回路は、前記駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、前記駆動トランジスタの第2の供給電極に電気的に接続される前記ELデバイスとを有し、

a)前記第1の供給電極、及び前記第2の供給電極を、異なった時間に流れる電流を測定して、前記駆動トランジスタ、及び前記ELデバイスの動作によって時間とともに生じる前記駆動トランジスタ、及び前記ELデバイスの特性の変動を示す経年劣化信号を提供する測定回路と、

b)線形コード値を提供する手段と、

c)前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号に応じて、前記線形コード値を変更する補償器と、

d)前記駆動トランジスタの前記ゲート電極を駆動するために、前記変更線形コード値に応じて、前記アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置。

【請求項2】

前記ELデバイスは、OLEDデバイスである請求項1に記載の装置。

【請求項3】

前記駆動トランジスタは、アモルファスシリコン・トランジスタである請求項1に記載の装置。

【請求項4】

前記第1の供給電極、及び前記第2の供給電極を介する電流の流れに前記測定回路を、選択的に電気的接続するスイッチをさらに有する請求項1に記載の装置。

【請求項5】

前記測定回路は、前記第1の供給電極、及び前記第2の供給電極を介して流れる前記駆動電流の関数であるミラー電流を作り出す第1のカレントミラーと、前記第1のカレントミラーの電圧変動を低減するために、前記第1のカレントミラーにバイアス電流を印加する第2のカレントミラーとを有する請求項1に記載の装置。

【請求項6】

前記測定回路は、電圧信号を作り出すミラー電流に応答する電圧変換器への電流と、前記補償器に前記経年劣化信号を提供する前記電圧信号に応答する手段とをさらに有する請求項5に記載の装置。

【請求項7】

非線形入力信号を受信し、かつ前記非線形入力信号を前記線形コード値に変換する手段をさらに有する請求項1に記載の装置。

【請求項8】

前記変換手段は、ルックアップテーブルを有する請求項7に記載の装置。

【請求項9】

前記補償器は、効率補償手段と、電圧補償手段とを有する請求項1に記載の装置。

【請求項10】

前記補償器は、基準経年劣化信号測定、及び最新の経年劣化信号測定を記憶するメモリをさらに有する請求項1に記載の装置。

【請求項11】

ELデバイスに電流を印加する駆動回路の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する方法であって、前記駆動回路は、前記駆動トランジスタの第1の供給電極に電気的に接続される電圧源と、前記駆動トランジスタの第2の供給電極に電気的に接続される前記ELデバイスとを有し、

a)前記第1の供給電極、及び前記第2の供給電極を、異なった時間に流れる電流を測定して、前記駆動トランジスタ、及び前記ELデバイスの動作によって時間とともに生じる前記駆動トランジスタ、及び前記ELデバイスの特性の変動を示す経年劣化信号を提供するステップと、

b)線形コード値を提供するステップと、

c)前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号に応じて、前記線形コード値を変更するステップと、

d)前記駆動トランジスタの前記ゲート電極を駆動するために、前記変更線形コード値に応じて、前記アナログ駆動トランジスタ制御信号を作り出すステップと、

を有する方法。

【請求項12】

前記ELデバイスは、OLEDデバイスである請求項11に記載の方法。

【請求項13】

前記駆動トランジスタは、アモルファスシリコン・トランジスタである請求項11に記載の方法。

【請求項14】

ステップbは、非線形入力信号を受信するステップと、前記非線形入力信号を前記線形コード値に変換するステップとを有する請求項11に記載の方法。

【請求項15】

前記変換するステップは、ルックアップテーブルを使用するステップを有する請求項14に記載の方法。

【請求項16】

ELパネルの複数のELサブ画素の駆動トランジスタのゲート電極に、アナログ駆動トランジスタ制御信号を提供する装置において、第1の電圧源と、第2の電圧源と、複数のELサブ画素とを前記ELパネルに有し、駆動回路のELデバイスは、それぞれのELサブ画素の前記ELデバイスに電流を印加し、駆動回路はそれぞれ、前記第1の電圧源に電気的に接続される第1の供給電極と、ELデバイスの第1の電極に電気的に接続される第2の供給電極とを有する駆動トランジスタを有し、ELデバイスはそれぞれ、前記第2の電圧源に電気的に接続される第2の電極を有し、改良点は、

a)前記第1の電圧源、及び前記第2の電圧源を、異なった時間に流れる電流を測定して、サブ画素の前記駆動トランジスタ、及び前記ELデバイスの動作によって時間とともに生じる前記駆動トランジスタ、及び前記ELデバイスの特性の変動を示すそれぞれのサブ画素の経年劣化信号を提供する測定回路と、

b)それぞれのサブ画素の線形コード値を提供する手段と、

c)それぞれのサブ画素の前記駆動トランジスタ、及び前記ELデバイスの特性の前記変動を補償するために、前記経年劣化信号に応じて、前記線形コード値を変更する補償器と、

d)前記駆動トランジスタの前記ゲート電極を駆動するために、前記変更線形コード値に応じて、前記アナログ駆動トランジスタ制御信号を作り出す線形ソースドライバと、

を有する装置。

【請求項17】

ELデバイスはそれぞれ、OLEDデバイスであり、駆動トランジスタはそれぞれ、アモルファスシリコン・トランジスタである請求項16に記載の装置。

【請求項18】

前記測定回路は、

a)電圧信号を作り出す電圧変換器への電流と、

b)前記電圧信号に応答して、前記補償器に前記経年劣化信号を提供する相関2重サンプリングユニットと、

を有する請求項16に記載の装置。

【請求項19】

非線形入力信号を受信し、かつ前記非線形入力信号を前記線形コード値に変換する手段をさらに有する請求項16に記載の装置。

【請求項20】