アモルファス半導体によるオープン・ベース・フォトトランジスタ・アレイ

【課題】イメージング装置において高い利得を実現し、所望のS/N比を得る。

【解決手段】イメージング装置の光センサアレイは、シリコンのような複数アモルファス半導体から形成されるバイポーラフォトトランジスタを使用する。該トランジスタは、オープンベース素子であって、入射する光子によって発生する正孔により、ベース領域への電流注入が生じる。また、コレクタ領域は、好ましくはアモルファスシリコンの真性層で形成される。該トランジスタは、バイポーラ電流が集積される集積モードか、もしくは、光の強度に応答する電流がモニタされる静的モードで動作する。

【解決手段】イメージング装置の光センサアレイは、シリコンのような複数アモルファス半導体から形成されるバイポーラフォトトランジスタを使用する。該トランジスタは、オープンベース素子であって、入射する光子によって発生する正孔により、ベース領域への電流注入が生じる。また、コレクタ領域は、好ましくはアモルファスシリコンの真性層で形成される。該トランジスタは、バイポーラ電流が集積される集積モードか、もしくは、光の強度に応答する電流がモニタされる静的モードで動作する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、イメージング・アレイに関するものであり、とりわけ、入射光に対する光センサの感度向上に関するものである。

【背景技術】

【0002】

イメージング・センサの1次元アレイまたは2次元アレイを処理回路要素に接続して、アレイが向けられた領域に関するイメージ情報が生成されるようにすることが可能である。各センサは、それが受光する光に応答した信号を発生する。この信号は、センサが受光する光のカラー強度を表すことが可能である。

【0003】

多くのイメージング用途において、電荷結合素子(CCD)が用いられている。CCDアレイの素子は、入射光によって発生する電荷を集積するが、この電荷は、CCDアレイが製作される半導体チップの表面に沿ったポテンシャル井戸に蓄積される。アレイの蓄積された電荷は、チップに組み込まれていない他の回路要素に信号を転送するオン・チップ回路要素に順次シフトされる。

【0004】

CCDは、意図された目的についてはうまく機能するが、各素子(すなわち、ピクセル)において得られる「利得」は、1未満である。利得は、電流レベル(出力電流/光子電流)または電子レベル(出力電子/入力光子)で測定可能である。電子レベルにおける最大の利得が1の場合、特定の素子の出力におけるS/N比が制限される。

【0005】

Theil他に対する米国特許第6,018,187号には、CCDテクノロジに対する代替案としてPINダイオードの利用の記載がある。ピクセル相互接続構造が、シリコン基板のような基板の上部表面に形成されている。ピクセル相互接続構造は、基板表面の選択位置から光センサ・アレイの底部電極まで延びる導電性バイアを備えた、酸化珪素または窒化珪素のような誘電体層である。好ましくは底部電極は、n型ドーパントを含むアモルファス・シリコンから形成される。底部電極の上には、連続真性層が形成される。pドープしたアモルファス・シリコンの連続層によって、真性層がカバーされ、透明導体によって、pドープ層がカバーされる。結果として、底部電極のそれぞれについて、PINダイオードが形成される。PINダイオードは、基板表面より上方に配置されるので、「高設」センサである。ピクセルの相互接続構造によって、高設PINダイオードは、基板レベルで製作された処理回路要素と電気的にリンクすることが可能になる。

【0006】

Mead他に対する米国特許第5,763,909号には、CCDテクノロジとは無関係な代替案の記載がある。バイポーラ・フォトトランジスタは、シリコン基板にドーパントを導入することによって製作される。従来のドーパント注入ステップが利用される。バイポーラ・フォトトランジスタ・アレイが形成されると、特定行におけるフォトトランジスタのベースが、共通行選択線に容量結合される。特定列における全てのフォトトランジスタのエミッタが、共通列選択線に接続される。こうして、各フォトトランジスタを個別に選択することが可能になる。フォトトランジスタ・アレイによって、CCDテクノロジの利用によって得られるよりも大きい利得が得られるようになる。

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明の目的は、フォトセンサ・アレイ内の個々のフォトセンサが、比較的高い利得レベルを実現して、所望のS/N比を得ることが可能になる、イメージング装置を提供することにある。

【課題を解決するための手段】

【0008】

複数アモルファス半導体層から形成されるバイポーラ・フォトトランジスタを利用することによって、イメージング用途に関する感光性が向上する。望ましい実施態様の場合、バイポーラ・フォトトランジスタは、オープン・ベース素子である。入射光子によって発生する正孔によって、ベース正孔電流注入が生じ、光電流のバイポーラ利得が実現する。

【0009】

望ましい構造の場合、各フォトトランジスタは、アモルファス・シリコンのエミッタ、ベース、及び、コレクタ層から形成されるが、他のアモルファス半導体材料(フルオレン・ビチオフェン共重合体の半導体重合体のような)を代用することも可能である。ベース及びエミッタ層は、NPNバイポーラ・トランジスタまたはPNPバイポーラ・トランジスタを形成するようにドープされ、コレクタ層は、ドープされないか、あるいは、ごくわずかしかドープされない、すなわち、コレクタ層は、真性層である。NPN実施態様の場合、エミッタ層は、n型ドーパントの濃度が高い、アモルファス・シリコンの第1の堆積層とすることが可能である。ベース層は、p型ドーパントを含むアモルファス・シリコンとして、エミッタ層の上に堆積させられる。次に、コレクタ層は、連続したアモルファス・シリコン層とすることもできるし、あるいは、誘電体によって各ピクセルが隣接ピクセルから分離された層とすることも可能である。nドープしたアモルファス・シリコンの薄層が、真性コレクタ層の上に形成される。最後に、透明上部電極が堆積させられる。そして、真性コレクタ層が形成される。エミッタ層は、底部電極として機能することができるが、バイポーラ・トランジスタを形成する層の堆積前に、独立した電極層を形成するのが望ましい。PNP応用例の場合、ベース層とエミッタ層の導電タイプが逆にされ、さらに、真性層の上の薄膜層の導電タイプも逆にされる。

【0010】

各フォトトランジスタは、全バイポーラ電流が定期読み取りに備えて集積される集積モードで動作することが可能である。あるいはまた、各フォトトランジスタは、特定ノードにおける電圧をモニタすることによって検知される信号が静的モードで動作することが可能である。前述のように、フォトトランジスタは、オープン・ベース素子である。従って、ベース層は、外部からの制御を受けない。真性コレクタ層に光が入射すると、層内に正孔及び電子が発生する。NPN実施態様の場合、光子によって発生する正孔が、ベース層まで伝導され、ベース正孔電流注入の働きをする。フォトトランジスタのオープン・ベース状態の結果として、バイポーラ利得が得られる。

【0011】

フォトトランジスタ・アレイは、オフ基板回路要素に転送するため、出力信号を検知及び/または増幅する処理回路要素として、同じ基板上に形成されるのが望ましい。本発明の利点は、フォトトランジスタ・レベルで得られる電流利得によって、装置の感度が向上するという点である。光の強度変化の結果として生じる出力の揺らぎと「ノイズ」との弁別がいっそう容易になる。

【発明を実施するための最良の形態】

【0012】

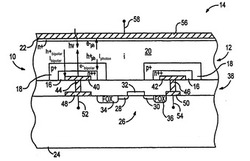

図1を参照すると、フォトトランジスタ・アレイ14の1対のNPNフォトトランジスタ10及び12が、いくつかの異なるアモルファス半導体層から形成されている。アモルファス半導体層は、アモルファス・シリコンから形成されていると解説される。しかし、有機半導体フルオレン・ビチオフェン共重合体のような他の材料も適合する。フォトトランジスタのそれぞれについて、エミッタ16は、n++層であり、ベース18は、p+層であり、コレクタ20は、真性層である。第4のアモルファス・シリコン層22は、真性コレクタ層の上に形成されている。この第4の層は、n+導電タイプである。

【0013】

望ましい実施態様の場合、エミッタ16、ベース18、及び、コレクタ20を形成するアモルファス層が、処理回路要素が形成される、シリコン基板のような基板24上に堆積させられる。典型的な処理回路要素には、ソース/ドレイン領域28及び30と、ゲート32を備える単一トランジスタ26がある。当該技術において周知のように、ソース/ドレイン領域は、イオン注入によって形成され、ゲート32は、酸化物層の上にポリシリコン層を堆積させることによって製作される。2つの電界酸化物領域(FOX)34及び36の間に、トランジスタが形成される。

【0014】

フォトトランジスタ10及び12と基板24内に埋め込まれた処理回路要素の間の接続は、Theil他に対する米国特許第6,018,187号に関連して上述のようなピクセル相互接続構造38によって施される。ピクセル相互接続構造38上の電極40及び42と、この相互接続構造を通る導電性バイア44及び46のアライメントがとられる。バイアによって、電極が基板24の表面の導電性経路48及び50に電気的に接続される。さらに詳細に後述するように、導電性経路は、基板24の下に位置する回路要素または外部回路要素に接続されている。回路接続は、フローティング・ノードとすることも可能なノード52及び54として表されている。可能性の1つとして、フォトトランジスタが、集積モードで動作して、2つのノード52及び54間における電圧変化をモニタする場合、ノード52及び54は、電気的「高」より低いレベルで選択的にリセットすることが可能である。上部電極層56は、ノード58に接続することによってVDDまたは別の高電圧定数に接続される。

【0015】

図1に示す構造を製作する場合、基板24のレベルに形成されるプロセス回路要素は、既知の技法を用いて設けることが可能である。この回路要素は、CMOS(相補形金属酸化膜シリコン)、BiCMOS、または、バイポーラとすることが可能である。ピクセル相互接続構造38は、バイア44及び46がタングステンから形成された、酸化珪素または窒化珪素の層とすることが可能である。タングステン・バイアによって、細くて比較的長い相互接続部を設けることが可能になる。タングステン・バイアは、化学蒸着(CVD)プロセスを利用して形成することが可能である。しかし、他の材料及び他のプロセスを代用することも可能である。

【0016】

オプションにより、電極40及び42が2つ以上の層から形成される。例えば、厚さが約500オングストロームのチタンまたはタングステンからなる下部金属層を利用して、電極のドープした上部半導体層からの集電を強化することが可能である。ドープした半導体は、n型導電性のアモルファス・シリコンとすることが可能である。ドープした半導体材料を利用する場合、動作中にバイアスがかかった場合に、材料が完全な空乏状態になるのを阻止するため、層は十分な厚さとドーパント濃度を備えていなければならない。しかし、エミッタ16を形成して、バイア44及び46に接触させることもできるし、あるいは、バイアに直接接触している薄い金属層に接触させることもできるので、電極40及び42は、全ての用途において必要とされるわけではない。

【0017】

エミッタ16、ベース18、及び、コレクタ20、並びに、薄層22を形成する層は、アモルファス・シリコンが望ましい。シリコン含有ガスを用いて、プラズマ強化化学蒸着(PECVD)を利用した層の堆積を実施することが可能である。シリコンに加えて、このガスには、水素が含まれているので、4層のそれぞれが、アモルファスSi:Hになる。ドープした層の場合、適合するドーパントが含まれている。例えば、ベースの形成にはリンのガスPH3を利用することが可能であり、エミッタ16及び上部薄層22の形成にはホウ素ガスB2H6を利用することが可能である。

【0018】

図1には、フォトトランジスタ10の動作を説明するため、いくつかの記号が含まれている。入射光子は、hvによって表されている。入射光子によって、電子・正孔対が発生する。電子の流れは、記号e−phに関連した矢印によって示されており、正孔の流れは、記号h+phによって表されている。同様に、フォトトランジスタにバイアスを加えた結果としての電子及び正孔の流れは、それぞれ、システムe−bipolar及びh+bipolarによって表されている。電子と正孔の再結合を無視すれば、フォトトランジスタ10の電流利得(β)は、Ibipolar/Iphotonとみなすことが可能である。

【0019】

図1に示すように、正孔h+phはベース18まで流れる。これらの正孔は、ベース正孔電流注入の働きをする。ベースは、電気的に開放状態のままであるため、光電流のバイポーラ利得が得られる。図2及び3では、従来のフォトダイオード60を通る電流の流れと図1のオープン・ベース・フォトトランジスタ10を通る電流の流れが比較されている。図2の場合、フォトダイオード60は、フォトダイオードが受光する光の強度に直接応答する電流Iphotonを発生する。図3の場合、コレクタ領域20からベース領域18に同様の電流が発生する。電流の利得は、VDDノード58から電気的接地ノード52に電流が流れることによって得られる。本発明にとってクリティカルではないが、電流利得は、用途に従って、5〜100に設定することが可能である。従って、図1及び3のフォトトランジスタ10によれば、図2のフォトダイオード60を利用する場合に比べて大幅に改良されることになる。

【0020】

アモルファス・シリコンによるオープン・ベース・フォトトランジスタ・アレイの製作に対する代替案の1つとして、連続ベース層及びコレクタ領域を形成する連続真性層にパターン形成して、セグメント化トランジスタが得られるようにすることも可能である。図4を参照すると、誘電体66によって、第1のフォトトランジスタ10のコレクタ62及びベース63が、第2のフォトトランジスタ12のコレクタ64及びベース65から分離される。誘電体を形成するために選択される材料はクリティカルではない。オプションにより、ベース63及び65とコレクタ62及び64は、空気によって離隔することも可能である。図4には、誘電体66によって分割されたn+層22が、示されている。代替案の1つとして、2つのフォトトランジスタ10及び12の動作に影響しないので、薄層22を連続させることも可能である。もう1つの代替案として、薄層22と電極層56は、両方とも、誘電体66によってセグメント化することも可能である。しかし、これには、フォトトランジスタのそれぞれに対する個別接続が必要になる。多数のデバイスを備えるフォトトランジスタ・アレイの場合、個別接続を必要とするのは望ましくない可能性がある。

【0021】

図5には、本発明のもう1つの実施態様が例示されている。この実施態様の場合、第1及び第2のフォトトランジスタ68及び70はPNP素子である。2つのフォトトランジスタは、図示のように、電極72及び74を備えているが、図5には示されていない基板との相互接続用の接点として、p++エミッタ76を利用することによって、電極を省略することが可能である。エミッタは、PECVDのような既知の技法を利用して堆積させられるアモルファス・シリコン層である。アモルファス・シリコン層は、直接基板上に堆積させることもできるし、あるいは、図1に関連して解説したタイプのようなピクセル相互接続構造上に堆積させることも可能である。

【0022】

第2のアモルファス・シリコン層は、堆積させられると、2つのフォトトランジスタ68及び70のそれぞれに対するオープン・ベース78として機能する。各ベースには、n+導電性のドーパントが含まれている。真性アモルファス・シリコン層は、フォトトランジスタのそれぞれに対するコレクタ80を形成する。真性層には、故意に導入されたドーパントが含まれていないか、あるいは、ごく低レベルのドーパントが含まれている。

【0023】

真性層80の上には、p+ドーパントを含む薄層82がある。最後に、上部電極84は、導電性材料から形成される。

【0024】

PNPフォトトランジスタ68及び70の働きについては、当事者には容易に明らかになるであろう。電気接続は、図1の関連して解説のものと逆である。すなわち、上部電極84は、電気的アースまたは低レベルの定電圧に接続される。底部電極72及び74は、下に位置する基板回路要素または外部回路要素のフローティング・ノードに接続される。光子が入射する結果として発生する電子及び正孔は、逆方向に伝搬し、オープン・ベース78まで伝搬すると、電流注入が生じ、バイポーラ利得が光電流に応答可能になる。

【0025】

図1から5に関連して解説したオープン・ベース・フォトトランジスタは、特定ノードにおける電圧の増大をモニタすることによって信号が検知される静的モードで動作することが可能で、あるいは集積することによって信号が検知される、集積モードで動作させることが可能である。集積モードについては、図6及び7に関連して解説し、静的モードについては、図8及び9に関連して解説することにする。

【0026】

図6の場合、図1のNPNフォトトランジスタ10は、そのエミッタ16が、積分コンデンサ86及びトランジスタ88によって電気的アースにリンクされた、フローティング・ノード52に接続されている。積分コンデンサは、フォトトランジスタ10を通る光電流によって決まる電位まで充電する。積分コンデンサは、故意に追加回路素子とすることもできるし、あるいは、フローティング・ノードに接続された他の寄生キャパシタンス以外の、フォトトランジスタのベースとコレクタの間の寄生キャパシタンスとすることが可能である。トランジスタ88は、集積時間の開始時に、フローティング・ノードを高電圧より低い電位に「リセット」するために利用される。リセットは、トランジスタ88を短期間にわたって「オン」状態にし、次に、「オフ」状態にして、集積期間を開始することによって実施される。集積される電荷は、ソース・フォロワの働きによってビット線90を介して読み取ることが可能である。トランジスタ92及び94は、書き込みアクセス線96が、トランジスタ94を「オン」状態にする信号を受信すると、積分コンデンサの電圧をビット線に転送する。当該技術において周知のように、フォトセンサ・アレイは、行選択線及び列選択線を選択的に起動することによって、順次操作することが可能である。トランジスタ94が、「オフ」状態にある場合、積分コンデンサ86が充電される。定期的に読み取られるのはこの電荷である。集積期間は、フローティング・ノードのリセットと書き込みアクセス線96における適正な信号の受信との間における時間である。

【0027】

図1及び6を比較すると、エミッタ16、ベース18、及び、コレクタ20は、アモルファス・シリコン層によって形成される。トランジスタ88、92、及び、94は、シリコン基板4に内に形成される。例えば、基板の表面に沿った導電経路48が、トランジスタ26のゲート32に接続される場合、図6のトランジスタ92は、図1のトランジスタ26とすることが可能である。

【0028】

図7には、そのコレクタ80が電気的アースに接続され、そのエミッタ76がトランジスタ98のソース/ドレイン領域に接続された、図5のPNPフォトトランジスタ68が示されている。トランジスタ98の他のソース/ドレイン領域は、VDDに接続されている。トランジスタ98は、集積時間の開始時に、フローティング・ノード100を電気的アースを超える電位にリセットするために利用される。フォトトランジスタ68のコレクタ80は、積分コンデンサ102に接続されているが、このコンデンサは、前述のように、独立した回路要素とすることもできるし、あるいは、フォトトランジスタの寄生ベース・コレクタ・キャパシタンス及びフローティング・ノードに接続された他の寄生キャパシタンスとすることも可能である。積分コンデンサの両端間における電圧は、集積時間中にフォトトランジスタを通る全電流によって決まる。この電圧は、書き込み線108によって、トランジスタ106が「オン」状態になると、トランジスタ104及び106によってビット線110に転送される。従って、ビット線110に転送される信号は、集積時間中にフォトトランジスタ68が受光する光の強度によって決まることになる。当該技術において周知のように、フォトトランジスタの2次元アレイは、トランジスタを選択的に起動することによって順次アクセスすることが可能である。

【0029】

図8の場合、図1のオープン・ベース・フォトトランジスタ10が、静的モードで動作させられる。このモードにおいて、回路は、フォトトランジスタのエミッタ16に接続されたノード52における電圧の上昇をモニタする。書き込みアクセス・ライン112に沿った信号によって、トランジスタ114は選択的に「オン」状態になる。アースと出力ライン118の間には、負荷抵抗器116が接続されている。フォトトランジスタ10の読み取り動作中、負荷抵抗器の両端間における電圧降下は、下記の方程式によって示されるように、フォトトランジスタを通る電流によって決まることになる:

【0030】

【数1】

【0031】

図9において、PNPトランジスタ68は、静的モード動作で利用されている。書き込みアクセス・ライン122に沿った信号によって、トランジスタ120を選択的に起動することによって、出力ライン124に沿った電圧をフォトトランジスタ68の出力として読み取ることが可能である。負荷抵抗器126の両端間における電圧降下は、フォトトランジスタを通る電流によって決まる。

【0032】

図6〜9に示す回路は、アモルファス・シリコンによるオープン・ベース・フォトトランジスタに関する可能性のある応用例である。しかし、本発明を逸脱することなく、他の応用例を利用することも可能である。さらに、アモルファス・シリコンの代わりに、他のアモルファス半導体を利用することも可能である。

【0033】

以上の説明及び添付の図面から、当該技術者には本発明に対するさまざまな修正が明らかになるであろう。従って、本発明は、付属の特許請求の範囲によってのみ制限されるものとする。しかしながら、本発明の広汎な応用の可能性に鑑み、以下に本発明の実施態様を幾つか例示する。

【0034】

(実施態様1)イメージング装置であって、基板(24)と、前記基板上のアモルファス半導体バイポーラ・フォトトランジスタ(10及び12;68及び70)からなるアレイが含まれており、前記バイポーラ・フォトトランジスタのそれぞれに、複数のアモルファス半導体層が含まれることと、前記複数のアモルファス半導体層に、少なくとも1つのp型層(18;63及び65;76)と、少なくとも1つのn型層(16;78)が含まれることと、前記バイポーラ・フォトトランジスタの出力(52および54)が前記フォトトランジスタが受光する光に応答することを特徴とする、イメージング装置。

【0035】

(実施態様2)前記バイポーラ・フォトトランジスタ(10及び12;68及び70)が、オープン・ベース素子であることと、各前記バイポーラ・フォトトランジスタが、電気的に開放されたアモルファス半導体ベース層(18;63及び65;78)を備えていることを特徴とする、実施態様1に記載のイメージング装置。

【0036】

(実施態様3)各前記バイポーラ・フォトトランジスタ(10及び12;68及び70)に、真性コレクタ層(20;62及び64;80)が含まれることを特徴とする、実施態様2に記載のイメージング装置。

【0037】

(実施態様4)電気的に開放されたアモルファス半導体ベース層(18;63及び65;78)の少なくとも一部が、前記基板(24)と前記真性コレクタ層(20;62及び64;80)の間に位置することと、前記アモルファス半導体ベース層が、アモルファス・シリコンであることを特徴とする、実施態様3に記載のイメージング装置。

【0038】

(実施態様5)さらに、少なくとも部分的に前記基板(24)内に形成されている処理回路要素(26)が含まれることを特徴とする、実施態様1に記載のイメージング装置。

【0039】

(実施態様6)各前記バイポーラ・フォトトランジスタ(10及び12;68及び70)は、電極(40及び42;72及び74)によって前記処理回路要素(26)に電気的に結合されることを特徴とする、実施態様5に記載のイメージング装置。

【0040】

(実施態様7)各前記バイポーラ・フォトトランジスタ(10及び12)が、p型アモルファス半導体ベース層(18;63及び65)によって、真性コレクタ層(20;62及び64)から間隔をあけて配置されたn型アモルファス半導体エミッタ層(16)を備える、オープン・ベースNPNバイポーラ・トランジスタであることを特徴とする、実施態様1に記載のイメージング装置。

【0041】

(実施態様8)各前記バイポーラ・フォトトランジスタ(10及び12)に、真性コレクタ層(20;62及び64)と接触した第2のn型アモルファス半導体層が含まれており、さらに、透明上部電極(56)が含まれていることを特徴とする、実施態様7に記載のイメージング装置。

【0042】

(実施態様9)各前記バイポーラ・フォトトランジスタ(68及び70)が、n型アモルファス半導体ベース層(78)によって、真性コレクタ層(80)から間隔をあけて配置されたp型アモルファス半導体エミッタ層(76)を備える、オープン・ベースPNPバイポーラ・トランジスタであることを特徴とする、請求項1に記載のイメージング装置。

【図面の簡単な説明】

【0043】

【図1】本発明による2つのオープン・ベース・バイポーラ・フォトトランジスタの側断面図である。

【図2】従来のフォトダイオードの概略図である。

【図3】図1のオープン・ベース・フォトトランジスタの1つと電気的同等物に関する概略図である。

【図4】真性コレクタ層がピクセル位置に従って分割された、図1のフォトトランジスタの側断面図である。

【図5】図1のNPNフォトトランジスタに対する代替案としての、1対のPNPフォトトランジスタの側断面図である。

【図6】集積モードで動作する図1のNPNフォトトランジスタの概略図である。

【図7】集積モードで動作する図5のPNPフォトトランジスタの概略図である。

【図8】静的モードで動作する図1のNPNフォトトランジスタの概略図である。

【図9】静的モードで動作する図5のPNPフォトトランジスタの概略図である。

【符号の説明】

【0044】

10 バイポーラ・フォトトランジスタ

12 バイポーラ・フォトトランジスタ

16 n型層

18 p型層

20 真性コレクタ層

24 基板

26 処理回路要素

40 電極

42 電極

52 バイポーラ・フォトトランジスタの出力

54 バイポーラ・フォトトランジスタの出力

56 透明上部電極

62 真性コレクタ層

63 p型層

64 真性コレクタ層

65 p型層

68 バイポーラ・フォトトランジスタ

70 バイポーラ・フォトトランジスタ

72 電極

74 電極

76 p型層

78 n型層

80 真性コレクタ層

【技術分野】

【0001】

本発明は、一般に、イメージング・アレイに関するものであり、とりわけ、入射光に対する光センサの感度向上に関するものである。

【背景技術】

【0002】

イメージング・センサの1次元アレイまたは2次元アレイを処理回路要素に接続して、アレイが向けられた領域に関するイメージ情報が生成されるようにすることが可能である。各センサは、それが受光する光に応答した信号を発生する。この信号は、センサが受光する光のカラー強度を表すことが可能である。

【0003】

多くのイメージング用途において、電荷結合素子(CCD)が用いられている。CCDアレイの素子は、入射光によって発生する電荷を集積するが、この電荷は、CCDアレイが製作される半導体チップの表面に沿ったポテンシャル井戸に蓄積される。アレイの蓄積された電荷は、チップに組み込まれていない他の回路要素に信号を転送するオン・チップ回路要素に順次シフトされる。

【0004】

CCDは、意図された目的についてはうまく機能するが、各素子(すなわち、ピクセル)において得られる「利得」は、1未満である。利得は、電流レベル(出力電流/光子電流)または電子レベル(出力電子/入力光子)で測定可能である。電子レベルにおける最大の利得が1の場合、特定の素子の出力におけるS/N比が制限される。

【0005】

Theil他に対する米国特許第6,018,187号には、CCDテクノロジに対する代替案としてPINダイオードの利用の記載がある。ピクセル相互接続構造が、シリコン基板のような基板の上部表面に形成されている。ピクセル相互接続構造は、基板表面の選択位置から光センサ・アレイの底部電極まで延びる導電性バイアを備えた、酸化珪素または窒化珪素のような誘電体層である。好ましくは底部電極は、n型ドーパントを含むアモルファス・シリコンから形成される。底部電極の上には、連続真性層が形成される。pドープしたアモルファス・シリコンの連続層によって、真性層がカバーされ、透明導体によって、pドープ層がカバーされる。結果として、底部電極のそれぞれについて、PINダイオードが形成される。PINダイオードは、基板表面より上方に配置されるので、「高設」センサである。ピクセルの相互接続構造によって、高設PINダイオードは、基板レベルで製作された処理回路要素と電気的にリンクすることが可能になる。

【0006】

Mead他に対する米国特許第5,763,909号には、CCDテクノロジとは無関係な代替案の記載がある。バイポーラ・フォトトランジスタは、シリコン基板にドーパントを導入することによって製作される。従来のドーパント注入ステップが利用される。バイポーラ・フォトトランジスタ・アレイが形成されると、特定行におけるフォトトランジスタのベースが、共通行選択線に容量結合される。特定列における全てのフォトトランジスタのエミッタが、共通列選択線に接続される。こうして、各フォトトランジスタを個別に選択することが可能になる。フォトトランジスタ・アレイによって、CCDテクノロジの利用によって得られるよりも大きい利得が得られるようになる。

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明の目的は、フォトセンサ・アレイ内の個々のフォトセンサが、比較的高い利得レベルを実現して、所望のS/N比を得ることが可能になる、イメージング装置を提供することにある。

【課題を解決するための手段】

【0008】

複数アモルファス半導体層から形成されるバイポーラ・フォトトランジスタを利用することによって、イメージング用途に関する感光性が向上する。望ましい実施態様の場合、バイポーラ・フォトトランジスタは、オープン・ベース素子である。入射光子によって発生する正孔によって、ベース正孔電流注入が生じ、光電流のバイポーラ利得が実現する。

【0009】

望ましい構造の場合、各フォトトランジスタは、アモルファス・シリコンのエミッタ、ベース、及び、コレクタ層から形成されるが、他のアモルファス半導体材料(フルオレン・ビチオフェン共重合体の半導体重合体のような)を代用することも可能である。ベース及びエミッタ層は、NPNバイポーラ・トランジスタまたはPNPバイポーラ・トランジスタを形成するようにドープされ、コレクタ層は、ドープされないか、あるいは、ごくわずかしかドープされない、すなわち、コレクタ層は、真性層である。NPN実施態様の場合、エミッタ層は、n型ドーパントの濃度が高い、アモルファス・シリコンの第1の堆積層とすることが可能である。ベース層は、p型ドーパントを含むアモルファス・シリコンとして、エミッタ層の上に堆積させられる。次に、コレクタ層は、連続したアモルファス・シリコン層とすることもできるし、あるいは、誘電体によって各ピクセルが隣接ピクセルから分離された層とすることも可能である。nドープしたアモルファス・シリコンの薄層が、真性コレクタ層の上に形成される。最後に、透明上部電極が堆積させられる。そして、真性コレクタ層が形成される。エミッタ層は、底部電極として機能することができるが、バイポーラ・トランジスタを形成する層の堆積前に、独立した電極層を形成するのが望ましい。PNP応用例の場合、ベース層とエミッタ層の導電タイプが逆にされ、さらに、真性層の上の薄膜層の導電タイプも逆にされる。

【0010】

各フォトトランジスタは、全バイポーラ電流が定期読み取りに備えて集積される集積モードで動作することが可能である。あるいはまた、各フォトトランジスタは、特定ノードにおける電圧をモニタすることによって検知される信号が静的モードで動作することが可能である。前述のように、フォトトランジスタは、オープン・ベース素子である。従って、ベース層は、外部からの制御を受けない。真性コレクタ層に光が入射すると、層内に正孔及び電子が発生する。NPN実施態様の場合、光子によって発生する正孔が、ベース層まで伝導され、ベース正孔電流注入の働きをする。フォトトランジスタのオープン・ベース状態の結果として、バイポーラ利得が得られる。

【0011】

フォトトランジスタ・アレイは、オフ基板回路要素に転送するため、出力信号を検知及び/または増幅する処理回路要素として、同じ基板上に形成されるのが望ましい。本発明の利点は、フォトトランジスタ・レベルで得られる電流利得によって、装置の感度が向上するという点である。光の強度変化の結果として生じる出力の揺らぎと「ノイズ」との弁別がいっそう容易になる。

【発明を実施するための最良の形態】

【0012】

図1を参照すると、フォトトランジスタ・アレイ14の1対のNPNフォトトランジスタ10及び12が、いくつかの異なるアモルファス半導体層から形成されている。アモルファス半導体層は、アモルファス・シリコンから形成されていると解説される。しかし、有機半導体フルオレン・ビチオフェン共重合体のような他の材料も適合する。フォトトランジスタのそれぞれについて、エミッタ16は、n++層であり、ベース18は、p+層であり、コレクタ20は、真性層である。第4のアモルファス・シリコン層22は、真性コレクタ層の上に形成されている。この第4の層は、n+導電タイプである。

【0013】

望ましい実施態様の場合、エミッタ16、ベース18、及び、コレクタ20を形成するアモルファス層が、処理回路要素が形成される、シリコン基板のような基板24上に堆積させられる。典型的な処理回路要素には、ソース/ドレイン領域28及び30と、ゲート32を備える単一トランジスタ26がある。当該技術において周知のように、ソース/ドレイン領域は、イオン注入によって形成され、ゲート32は、酸化物層の上にポリシリコン層を堆積させることによって製作される。2つの電界酸化物領域(FOX)34及び36の間に、トランジスタが形成される。

【0014】

フォトトランジスタ10及び12と基板24内に埋め込まれた処理回路要素の間の接続は、Theil他に対する米国特許第6,018,187号に関連して上述のようなピクセル相互接続構造38によって施される。ピクセル相互接続構造38上の電極40及び42と、この相互接続構造を通る導電性バイア44及び46のアライメントがとられる。バイアによって、電極が基板24の表面の導電性経路48及び50に電気的に接続される。さらに詳細に後述するように、導電性経路は、基板24の下に位置する回路要素または外部回路要素に接続されている。回路接続は、フローティング・ノードとすることも可能なノード52及び54として表されている。可能性の1つとして、フォトトランジスタが、集積モードで動作して、2つのノード52及び54間における電圧変化をモニタする場合、ノード52及び54は、電気的「高」より低いレベルで選択的にリセットすることが可能である。上部電極層56は、ノード58に接続することによってVDDまたは別の高電圧定数に接続される。

【0015】

図1に示す構造を製作する場合、基板24のレベルに形成されるプロセス回路要素は、既知の技法を用いて設けることが可能である。この回路要素は、CMOS(相補形金属酸化膜シリコン)、BiCMOS、または、バイポーラとすることが可能である。ピクセル相互接続構造38は、バイア44及び46がタングステンから形成された、酸化珪素または窒化珪素の層とすることが可能である。タングステン・バイアによって、細くて比較的長い相互接続部を設けることが可能になる。タングステン・バイアは、化学蒸着(CVD)プロセスを利用して形成することが可能である。しかし、他の材料及び他のプロセスを代用することも可能である。

【0016】

オプションにより、電極40及び42が2つ以上の層から形成される。例えば、厚さが約500オングストロームのチタンまたはタングステンからなる下部金属層を利用して、電極のドープした上部半導体層からの集電を強化することが可能である。ドープした半導体は、n型導電性のアモルファス・シリコンとすることが可能である。ドープした半導体材料を利用する場合、動作中にバイアスがかかった場合に、材料が完全な空乏状態になるのを阻止するため、層は十分な厚さとドーパント濃度を備えていなければならない。しかし、エミッタ16を形成して、バイア44及び46に接触させることもできるし、あるいは、バイアに直接接触している薄い金属層に接触させることもできるので、電極40及び42は、全ての用途において必要とされるわけではない。

【0017】

エミッタ16、ベース18、及び、コレクタ20、並びに、薄層22を形成する層は、アモルファス・シリコンが望ましい。シリコン含有ガスを用いて、プラズマ強化化学蒸着(PECVD)を利用した層の堆積を実施することが可能である。シリコンに加えて、このガスには、水素が含まれているので、4層のそれぞれが、アモルファスSi:Hになる。ドープした層の場合、適合するドーパントが含まれている。例えば、ベースの形成にはリンのガスPH3を利用することが可能であり、エミッタ16及び上部薄層22の形成にはホウ素ガスB2H6を利用することが可能である。

【0018】

図1には、フォトトランジスタ10の動作を説明するため、いくつかの記号が含まれている。入射光子は、hvによって表されている。入射光子によって、電子・正孔対が発生する。電子の流れは、記号e−phに関連した矢印によって示されており、正孔の流れは、記号h+phによって表されている。同様に、フォトトランジスタにバイアスを加えた結果としての電子及び正孔の流れは、それぞれ、システムe−bipolar及びh+bipolarによって表されている。電子と正孔の再結合を無視すれば、フォトトランジスタ10の電流利得(β)は、Ibipolar/Iphotonとみなすことが可能である。

【0019】

図1に示すように、正孔h+phはベース18まで流れる。これらの正孔は、ベース正孔電流注入の働きをする。ベースは、電気的に開放状態のままであるため、光電流のバイポーラ利得が得られる。図2及び3では、従来のフォトダイオード60を通る電流の流れと図1のオープン・ベース・フォトトランジスタ10を通る電流の流れが比較されている。図2の場合、フォトダイオード60は、フォトダイオードが受光する光の強度に直接応答する電流Iphotonを発生する。図3の場合、コレクタ領域20からベース領域18に同様の電流が発生する。電流の利得は、VDDノード58から電気的接地ノード52に電流が流れることによって得られる。本発明にとってクリティカルではないが、電流利得は、用途に従って、5〜100に設定することが可能である。従って、図1及び3のフォトトランジスタ10によれば、図2のフォトダイオード60を利用する場合に比べて大幅に改良されることになる。

【0020】

アモルファス・シリコンによるオープン・ベース・フォトトランジスタ・アレイの製作に対する代替案の1つとして、連続ベース層及びコレクタ領域を形成する連続真性層にパターン形成して、セグメント化トランジスタが得られるようにすることも可能である。図4を参照すると、誘電体66によって、第1のフォトトランジスタ10のコレクタ62及びベース63が、第2のフォトトランジスタ12のコレクタ64及びベース65から分離される。誘電体を形成するために選択される材料はクリティカルではない。オプションにより、ベース63及び65とコレクタ62及び64は、空気によって離隔することも可能である。図4には、誘電体66によって分割されたn+層22が、示されている。代替案の1つとして、2つのフォトトランジスタ10及び12の動作に影響しないので、薄層22を連続させることも可能である。もう1つの代替案として、薄層22と電極層56は、両方とも、誘電体66によってセグメント化することも可能である。しかし、これには、フォトトランジスタのそれぞれに対する個別接続が必要になる。多数のデバイスを備えるフォトトランジスタ・アレイの場合、個別接続を必要とするのは望ましくない可能性がある。

【0021】

図5には、本発明のもう1つの実施態様が例示されている。この実施態様の場合、第1及び第2のフォトトランジスタ68及び70はPNP素子である。2つのフォトトランジスタは、図示のように、電極72及び74を備えているが、図5には示されていない基板との相互接続用の接点として、p++エミッタ76を利用することによって、電極を省略することが可能である。エミッタは、PECVDのような既知の技法を利用して堆積させられるアモルファス・シリコン層である。アモルファス・シリコン層は、直接基板上に堆積させることもできるし、あるいは、図1に関連して解説したタイプのようなピクセル相互接続構造上に堆積させることも可能である。

【0022】

第2のアモルファス・シリコン層は、堆積させられると、2つのフォトトランジスタ68及び70のそれぞれに対するオープン・ベース78として機能する。各ベースには、n+導電性のドーパントが含まれている。真性アモルファス・シリコン層は、フォトトランジスタのそれぞれに対するコレクタ80を形成する。真性層には、故意に導入されたドーパントが含まれていないか、あるいは、ごく低レベルのドーパントが含まれている。

【0023】

真性層80の上には、p+ドーパントを含む薄層82がある。最後に、上部電極84は、導電性材料から形成される。

【0024】

PNPフォトトランジスタ68及び70の働きについては、当事者には容易に明らかになるであろう。電気接続は、図1の関連して解説のものと逆である。すなわち、上部電極84は、電気的アースまたは低レベルの定電圧に接続される。底部電極72及び74は、下に位置する基板回路要素または外部回路要素のフローティング・ノードに接続される。光子が入射する結果として発生する電子及び正孔は、逆方向に伝搬し、オープン・ベース78まで伝搬すると、電流注入が生じ、バイポーラ利得が光電流に応答可能になる。

【0025】

図1から5に関連して解説したオープン・ベース・フォトトランジスタは、特定ノードにおける電圧の増大をモニタすることによって信号が検知される静的モードで動作することが可能で、あるいは集積することによって信号が検知される、集積モードで動作させることが可能である。集積モードについては、図6及び7に関連して解説し、静的モードについては、図8及び9に関連して解説することにする。

【0026】

図6の場合、図1のNPNフォトトランジスタ10は、そのエミッタ16が、積分コンデンサ86及びトランジスタ88によって電気的アースにリンクされた、フローティング・ノード52に接続されている。積分コンデンサは、フォトトランジスタ10を通る光電流によって決まる電位まで充電する。積分コンデンサは、故意に追加回路素子とすることもできるし、あるいは、フローティング・ノードに接続された他の寄生キャパシタンス以外の、フォトトランジスタのベースとコレクタの間の寄生キャパシタンスとすることが可能である。トランジスタ88は、集積時間の開始時に、フローティング・ノードを高電圧より低い電位に「リセット」するために利用される。リセットは、トランジスタ88を短期間にわたって「オン」状態にし、次に、「オフ」状態にして、集積期間を開始することによって実施される。集積される電荷は、ソース・フォロワの働きによってビット線90を介して読み取ることが可能である。トランジスタ92及び94は、書き込みアクセス線96が、トランジスタ94を「オン」状態にする信号を受信すると、積分コンデンサの電圧をビット線に転送する。当該技術において周知のように、フォトセンサ・アレイは、行選択線及び列選択線を選択的に起動することによって、順次操作することが可能である。トランジスタ94が、「オフ」状態にある場合、積分コンデンサ86が充電される。定期的に読み取られるのはこの電荷である。集積期間は、フローティング・ノードのリセットと書き込みアクセス線96における適正な信号の受信との間における時間である。

【0027】

図1及び6を比較すると、エミッタ16、ベース18、及び、コレクタ20は、アモルファス・シリコン層によって形成される。トランジスタ88、92、及び、94は、シリコン基板4に内に形成される。例えば、基板の表面に沿った導電経路48が、トランジスタ26のゲート32に接続される場合、図6のトランジスタ92は、図1のトランジスタ26とすることが可能である。

【0028】

図7には、そのコレクタ80が電気的アースに接続され、そのエミッタ76がトランジスタ98のソース/ドレイン領域に接続された、図5のPNPフォトトランジスタ68が示されている。トランジスタ98の他のソース/ドレイン領域は、VDDに接続されている。トランジスタ98は、集積時間の開始時に、フローティング・ノード100を電気的アースを超える電位にリセットするために利用される。フォトトランジスタ68のコレクタ80は、積分コンデンサ102に接続されているが、このコンデンサは、前述のように、独立した回路要素とすることもできるし、あるいは、フォトトランジスタの寄生ベース・コレクタ・キャパシタンス及びフローティング・ノードに接続された他の寄生キャパシタンスとすることも可能である。積分コンデンサの両端間における電圧は、集積時間中にフォトトランジスタを通る全電流によって決まる。この電圧は、書き込み線108によって、トランジスタ106が「オン」状態になると、トランジスタ104及び106によってビット線110に転送される。従って、ビット線110に転送される信号は、集積時間中にフォトトランジスタ68が受光する光の強度によって決まることになる。当該技術において周知のように、フォトトランジスタの2次元アレイは、トランジスタを選択的に起動することによって順次アクセスすることが可能である。

【0029】

図8の場合、図1のオープン・ベース・フォトトランジスタ10が、静的モードで動作させられる。このモードにおいて、回路は、フォトトランジスタのエミッタ16に接続されたノード52における電圧の上昇をモニタする。書き込みアクセス・ライン112に沿った信号によって、トランジスタ114は選択的に「オン」状態になる。アースと出力ライン118の間には、負荷抵抗器116が接続されている。フォトトランジスタ10の読み取り動作中、負荷抵抗器の両端間における電圧降下は、下記の方程式によって示されるように、フォトトランジスタを通る電流によって決まることになる:

【0030】

【数1】

【0031】

図9において、PNPトランジスタ68は、静的モード動作で利用されている。書き込みアクセス・ライン122に沿った信号によって、トランジスタ120を選択的に起動することによって、出力ライン124に沿った電圧をフォトトランジスタ68の出力として読み取ることが可能である。負荷抵抗器126の両端間における電圧降下は、フォトトランジスタを通る電流によって決まる。

【0032】

図6〜9に示す回路は、アモルファス・シリコンによるオープン・ベース・フォトトランジスタに関する可能性のある応用例である。しかし、本発明を逸脱することなく、他の応用例を利用することも可能である。さらに、アモルファス・シリコンの代わりに、他のアモルファス半導体を利用することも可能である。

【0033】

以上の説明及び添付の図面から、当該技術者には本発明に対するさまざまな修正が明らかになるであろう。従って、本発明は、付属の特許請求の範囲によってのみ制限されるものとする。しかしながら、本発明の広汎な応用の可能性に鑑み、以下に本発明の実施態様を幾つか例示する。

【0034】

(実施態様1)イメージング装置であって、基板(24)と、前記基板上のアモルファス半導体バイポーラ・フォトトランジスタ(10及び12;68及び70)からなるアレイが含まれており、前記バイポーラ・フォトトランジスタのそれぞれに、複数のアモルファス半導体層が含まれることと、前記複数のアモルファス半導体層に、少なくとも1つのp型層(18;63及び65;76)と、少なくとも1つのn型層(16;78)が含まれることと、前記バイポーラ・フォトトランジスタの出力(52および54)が前記フォトトランジスタが受光する光に応答することを特徴とする、イメージング装置。

【0035】

(実施態様2)前記バイポーラ・フォトトランジスタ(10及び12;68及び70)が、オープン・ベース素子であることと、各前記バイポーラ・フォトトランジスタが、電気的に開放されたアモルファス半導体ベース層(18;63及び65;78)を備えていることを特徴とする、実施態様1に記載のイメージング装置。

【0036】

(実施態様3)各前記バイポーラ・フォトトランジスタ(10及び12;68及び70)に、真性コレクタ層(20;62及び64;80)が含まれることを特徴とする、実施態様2に記載のイメージング装置。

【0037】

(実施態様4)電気的に開放されたアモルファス半導体ベース層(18;63及び65;78)の少なくとも一部が、前記基板(24)と前記真性コレクタ層(20;62及び64;80)の間に位置することと、前記アモルファス半導体ベース層が、アモルファス・シリコンであることを特徴とする、実施態様3に記載のイメージング装置。

【0038】

(実施態様5)さらに、少なくとも部分的に前記基板(24)内に形成されている処理回路要素(26)が含まれることを特徴とする、実施態様1に記載のイメージング装置。

【0039】

(実施態様6)各前記バイポーラ・フォトトランジスタ(10及び12;68及び70)は、電極(40及び42;72及び74)によって前記処理回路要素(26)に電気的に結合されることを特徴とする、実施態様5に記載のイメージング装置。

【0040】

(実施態様7)各前記バイポーラ・フォトトランジスタ(10及び12)が、p型アモルファス半導体ベース層(18;63及び65)によって、真性コレクタ層(20;62及び64)から間隔をあけて配置されたn型アモルファス半導体エミッタ層(16)を備える、オープン・ベースNPNバイポーラ・トランジスタであることを特徴とする、実施態様1に記載のイメージング装置。

【0041】

(実施態様8)各前記バイポーラ・フォトトランジスタ(10及び12)に、真性コレクタ層(20;62及び64)と接触した第2のn型アモルファス半導体層が含まれており、さらに、透明上部電極(56)が含まれていることを特徴とする、実施態様7に記載のイメージング装置。

【0042】

(実施態様9)各前記バイポーラ・フォトトランジスタ(68及び70)が、n型アモルファス半導体ベース層(78)によって、真性コレクタ層(80)から間隔をあけて配置されたp型アモルファス半導体エミッタ層(76)を備える、オープン・ベースPNPバイポーラ・トランジスタであることを特徴とする、請求項1に記載のイメージング装置。

【図面の簡単な説明】

【0043】

【図1】本発明による2つのオープン・ベース・バイポーラ・フォトトランジスタの側断面図である。

【図2】従来のフォトダイオードの概略図である。

【図3】図1のオープン・ベース・フォトトランジスタの1つと電気的同等物に関する概略図である。

【図4】真性コレクタ層がピクセル位置に従って分割された、図1のフォトトランジスタの側断面図である。

【図5】図1のNPNフォトトランジスタに対する代替案としての、1対のPNPフォトトランジスタの側断面図である。

【図6】集積モードで動作する図1のNPNフォトトランジスタの概略図である。

【図7】集積モードで動作する図5のPNPフォトトランジスタの概略図である。

【図8】静的モードで動作する図1のNPNフォトトランジスタの概略図である。

【図9】静的モードで動作する図5のPNPフォトトランジスタの概略図である。

【符号の説明】

【0044】

10 バイポーラ・フォトトランジスタ

12 バイポーラ・フォトトランジスタ

16 n型層

18 p型層

20 真性コレクタ層

24 基板

26 処理回路要素

40 電極

42 電極

52 バイポーラ・フォトトランジスタの出力

54 バイポーラ・フォトトランジスタの出力

56 透明上部電極

62 真性コレクタ層

63 p型層

64 真性コレクタ層

65 p型層

68 バイポーラ・フォトトランジスタ

70 バイポーラ・フォトトランジスタ

72 電極

74 電極

76 p型層

78 n型層

80 真性コレクタ層

【特許請求の範囲】

【請求項1】

イメージング装置であって、

少なくとも1つのトランジスタ(26)を含む処理回路要素を備えている基板(24)と、

前記基板上のアモルファス半導体バイポーラ・フォトトランジスタ(10、12;68、70)からなるアレイと、前記バイポーラ・フォトトランジスタのそれぞれが、エミッタ(16:76)、ベース(18;63、65;78)、コレクタ(20;62、64;80)を有するとともに、少なくとも1つのp型層(18;63、65;76)及び少なくとも1つのn型層(16;78)を含む複数のアモルファス半導体層を含み、各バイポーラ・フォトトランジスタが、当該フォトトランジスタに受光された光を表す信号をもたらすように構成されている出力(52、54)を有し、各バイポーラ・フォトトランジスタのコレクタが真性コレクタ層(20)を含み、

前記バイポーラ・トランジスタを前記処理回路要素に接続するように配列されている導電性バイア(44、46)を含む、前記基板と前記アモルファス半導体層の間の相互接続構造(38)と、からなり

前記アモルファスシリコンフォトトランジスタ(10、12;68、70)のそれぞれが、当該アモルファス半導体バイポーラ・フォトトランジスタ(10、12;68、70)のコレクタ(20;62、64;80)とベース(18;63、65;78)の間の寄生キャパシタンスを含む積分コンデンサ(102)に接続されていることを特徴とするイメージング装置。

【請求項2】

前記バイポーラ・フォトトランジスタ(10、12;68、70)が、オープン・ベース素子であることと、各前記バイポーラ・フォトトランジスタのベースが、電気的に開放されたアモルファス半導体ベース層(18;63、65;78)であることを特徴とする請求項1に記載のイメージング装置。

【請求項3】

前記電気的に開放されたアモルファス半導体ベース層(18;63、65;78)の少なくとも部分が、前記基板(24)と前記真性コレクタ層(20;62、64;80)の間にあり、前記アモルファス半導体ベース層がアモルファスシリコンであることを特徴とする、請求項2に記載のイメージング装置。

【請求項4】

各前記バイポーラ・フォトトランジスタ(10、12;68、70)が、電極(40、42;72、74)及び前記導電性バイア(44、46)により前記処理回路要素(26)に電気的に結合されることを特徴とする請求項1に記載のイメージング装置。

【請求項5】

各前記バイポーラ・フォトトランジスタ(10、12)が、p型アモルファス半導体ベース層(18;63、65)によって、前記真性コレクタ層(20;62、64)から間隔をあけて配置されたn型アモルファス半導体エミッタ層(16)を備える、オープン・ベースNPNバイポーラ・トランジスタであることを特徴とする請求項1に記載のイメージング装置。

【請求項6】

各前記バイポーラ・フォトトランジスタ(10、12)が、前記真性コレクタ層(20;62、64)と接触した第2のn型アモルファス半導体層を含み、さらに、透明上部電極(56)が含まれていることを特徴とする請求項5に記載のイメージング装置。

【請求項7】

各前記バイポーラ・フォトトランジスタ(68、78)が、n型アモルファス半導体ベース層(78)によって、前記真性コレクタ層(80)から間隔をあけて配置されたp型アモルファス半導体エミッタ層(76)を備える、オープン・ベースPNPバイポーラ・トランジスタであることを特徴とする請求項1に記載のイメージング装置。

【請求項8】

前記積分コンデンサがさらに、前記アモルファス半導体バイポーラ・フォトトランジスタ(10、12;68、70)のコレクタとベースの間の前記寄生キャパシタンスから隔置されているキャパシタ(102)を含むことを特徴とする請求項1に記載のイメージング装置。

【請求項1】

イメージング装置であって、

少なくとも1つのトランジスタ(26)を含む処理回路要素を備えている基板(24)と、

前記基板上のアモルファス半導体バイポーラ・フォトトランジスタ(10、12;68、70)からなるアレイと、前記バイポーラ・フォトトランジスタのそれぞれが、エミッタ(16:76)、ベース(18;63、65;78)、コレクタ(20;62、64;80)を有するとともに、少なくとも1つのp型層(18;63、65;76)及び少なくとも1つのn型層(16;78)を含む複数のアモルファス半導体層を含み、各バイポーラ・フォトトランジスタが、当該フォトトランジスタに受光された光を表す信号をもたらすように構成されている出力(52、54)を有し、各バイポーラ・フォトトランジスタのコレクタが真性コレクタ層(20)を含み、

前記バイポーラ・トランジスタを前記処理回路要素に接続するように配列されている導電性バイア(44、46)を含む、前記基板と前記アモルファス半導体層の間の相互接続構造(38)と、からなり

前記アモルファスシリコンフォトトランジスタ(10、12;68、70)のそれぞれが、当該アモルファス半導体バイポーラ・フォトトランジスタ(10、12;68、70)のコレクタ(20;62、64;80)とベース(18;63、65;78)の間の寄生キャパシタンスを含む積分コンデンサ(102)に接続されていることを特徴とするイメージング装置。

【請求項2】

前記バイポーラ・フォトトランジスタ(10、12;68、70)が、オープン・ベース素子であることと、各前記バイポーラ・フォトトランジスタのベースが、電気的に開放されたアモルファス半導体ベース層(18;63、65;78)であることを特徴とする請求項1に記載のイメージング装置。

【請求項3】

前記電気的に開放されたアモルファス半導体ベース層(18;63、65;78)の少なくとも部分が、前記基板(24)と前記真性コレクタ層(20;62、64;80)の間にあり、前記アモルファス半導体ベース層がアモルファスシリコンであることを特徴とする、請求項2に記載のイメージング装置。

【請求項4】

各前記バイポーラ・フォトトランジスタ(10、12;68、70)が、電極(40、42;72、74)及び前記導電性バイア(44、46)により前記処理回路要素(26)に電気的に結合されることを特徴とする請求項1に記載のイメージング装置。

【請求項5】

各前記バイポーラ・フォトトランジスタ(10、12)が、p型アモルファス半導体ベース層(18;63、65)によって、前記真性コレクタ層(20;62、64)から間隔をあけて配置されたn型アモルファス半導体エミッタ層(16)を備える、オープン・ベースNPNバイポーラ・トランジスタであることを特徴とする請求項1に記載のイメージング装置。

【請求項6】

各前記バイポーラ・フォトトランジスタ(10、12)が、前記真性コレクタ層(20;62、64)と接触した第2のn型アモルファス半導体層を含み、さらに、透明上部電極(56)が含まれていることを特徴とする請求項5に記載のイメージング装置。

【請求項7】

各前記バイポーラ・フォトトランジスタ(68、78)が、n型アモルファス半導体ベース層(78)によって、前記真性コレクタ層(80)から間隔をあけて配置されたp型アモルファス半導体エミッタ層(76)を備える、オープン・ベースPNPバイポーラ・トランジスタであることを特徴とする請求項1に記載のイメージング装置。

【請求項8】

前記積分コンデンサがさらに、前記アモルファス半導体バイポーラ・フォトトランジスタ(10、12;68、70)のコレクタとベースの間の前記寄生キャパシタンスから隔置されているキャパシタ(102)を含むことを特徴とする請求項1に記載のイメージング装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2008−141198(P2008−141198A)

【公開日】平成20年6月19日(2008.6.19)

【国際特許分類】

【出願番号】特願2007−307361(P2007−307361)

【出願日】平成19年11月28日(2007.11.28)

【分割の表示】特願2002−39731(P2002−39731)の分割

【原出願日】平成14年2月18日(2002.2.18)

【出願人】(506076606)アバゴ・テクノロジーズ・ジェネラル・アイピー(シンガポール)プライベート・リミテッド (129)

【Fターム(参考)】

【公開日】平成20年6月19日(2008.6.19)

【国際特許分類】

【出願日】平成19年11月28日(2007.11.28)

【分割の表示】特願2002−39731(P2002−39731)の分割

【原出願日】平成14年2月18日(2002.2.18)

【出願人】(506076606)アバゴ・テクノロジーズ・ジェネラル・アイピー(シンガポール)プライベート・リミテッド (129)

【Fターム(参考)】

[ Back to top ]