アモルファス絶縁体膜及び薄膜トランジスタ

【課題】電気的に高性能、安価並びに低温形成可能なアモルファス絶縁体膜及び薄膜トランジスタを提供する。

【解決手段】Si酸化物アモルファス絶縁体膜中にArを含有し、その膜中のAr量がSiに対して原子数比で3%以上(Ar/Si ≧ 3 at.%)である膜を作製する。また望ましくは前記絶縁体膜中のAr量が、Siに対して原子数比で17%以下(Ar/Si ≦ 17 at.%)の膜を作製する。また、そのアモルファス絶縁体膜を薄膜トランジスタのゲート絶縁膜に用いる。

【解決手段】Si酸化物アモルファス絶縁体膜中にArを含有し、その膜中のAr量がSiに対して原子数比で3%以上(Ar/Si ≧ 3 at.%)である膜を作製する。また望ましくは前記絶縁体膜中のAr量が、Siに対して原子数比で17%以下(Ar/Si ≦ 17 at.%)の膜を作製する。また、そのアモルファス絶縁体膜を薄膜トランジスタのゲート絶縁膜に用いる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アモルファス絶縁体膜及びそれを用いた薄膜トランジスタに関するものである。

【背景技術】

【0002】

近年、液晶、プラズマ或いは有機ELを用いたディスプレイの開発が大型小型問わずに盛んに行われている。それらの画素の駆動デバイスとしての薄膜トランジスタ(TFT)にアモルファスシリコン、低温ポリシリコン及び酸化物半導体薄膜を用いることが試みられている。特に、アモルファス酸化物半導体をチャネルに用いたTFTは室温形成によるプラスティック基板を用いたフレキシブルディスプレイへの適用が可能であるため、非特許文献1にあるように、盛んに研究開発が行われている。

【非特許文献1】Applied Physics Letters, Volume 89, 112123-1 〜 3ページ

【特許文献1】特開平2−90568号公報

【非特許文献2】Journal of Applied Physics, Volume 78, 962 〜 968ページ

【発明の開示】

【発明が解決しようとする課題】

【0003】

非特許文献1のTFTでは、アモルファス酸化物半導体チャネル層としてアモルファスInGaZnO4薄膜がスパッタ法で堆積して用いられている。また同様に、ゲート絶縁膜としてY2O3膜がスパッタ法で堆積して用いられている。ゲート絶縁膜であるY2O3は、TFTのゲート絶縁膜として一般に用いられる酸化シリコン(SiO2)などと比較するとコストが高く、SiO2等のシリコン系アモルファス絶縁体膜への転換が期待されている。

【0004】

SiO2などのシリコン系アモルファス絶縁体膜(絶縁膜ともいう)は一般的に化学気相成長法(CVD法)で製造されることが多い。CVD法で絶縁性能が良好な絶縁体膜を得るには、一般的に300℃以上の成膜温度が必要であり、プラスティック基板上への形成が困難である。

【0005】

一方、TFTに用いるアモルファス酸化物半導体は、前述のように、スパッタ法により300℃以下の成膜温度で形成することが可能である。従って、絶縁体膜の形成工程もアモルファス酸化物半導体と同様にスパッタ法で形成することができれば、プラスティック基板等の耐熱性の低い基板が採用できることから望ましい。

【0006】

しかしながら、スパッタ法で堆積した従来のシリコン系アモルファス絶縁体膜は、CVD法による同膜より絶縁特性に劣るため、これまで実用に供さなかった。このため、プラスティック基板上に素子を形成する場合などはCVD法による成膜時の温度以下の温度での絶縁体膜形成が求められており、特許文献1にあるように、スパッタ法による絶縁体膜形成の高性能化が望まれている。

【0007】

本発明の目的は、Siの酸化物から成るアモルファス絶縁体膜において、良好な特性の絶縁体膜並びにそれを用いた薄膜トランジスタを提供することにある。

【課題を解決するための手段】

【0008】

本願発明者らは、上記従来の課題を解決するため、スパッタ法によるシリコン酸化物アモルファス絶縁体膜について鋭意検討を行った。そして絶縁体膜中のAr量と絶縁特性の相関についての知見を得、絶縁特性が良好なシリコン酸化物アモルファス絶縁体膜を発明するに至ったものである。

【0009】

本発明は上記知見に基づいて完成に至ったものであり、その骨子とするところは、シリコン(Si)酸化物を含むアモルファス絶縁体膜であって、前記絶縁体膜中にArが含有されており、該Ar含有量がSiに対して原子数比で3原子%以上であることを特徴とするものである。

【発明の効果】

【0010】

本発明によれば、絶縁特性の優れた絶縁体膜を得ることができる。また本発明の絶縁体膜を用いることで従来より高性能で、低コストの薄膜トランジスタを低温の製造プロセスにて得ることができる。

【発明を実施するための最良の形態】

【0011】

次に、発明を実施するための最良の形態について説明する。従来は上記特許文献1にあるように、スパッタ法により作製したシリコン酸化物膜の絶縁性低下はスパッタ中のAr粒子が膜にダメージを与えるためであると考えられている。そして、スパッタガス中のArガスをなるべく少なくし、酸素ガスをできるだけ多くした条件で成膜することが、シリコン酸化物膜の絶縁性向上の方法としてとられていた。すなわち、膜中のAr量も少ないほど良しとされた。

【0012】

しかしながら、スパッタガス中のAr対酸素の比率と絶縁性の関係は、シリコン酸化物膜の成膜条件の記載が十分でなく、成膜条件の一貫性に疑問が生じる。また、成膜したシリコン酸化物膜中のAr量とシリコン酸化物膜の絶縁性の相関を詳細に調べた文献は見当たらない。

【0013】

そこで本発明者らはスパッタ法によるシリコン酸化物膜を種々の条件で作製し、その膜中のAr量と絶縁性に関して相関があることを見出した。さらにはスパッタガス中のAr量がたとえ100%(酸素ガスなし)であっても、成膜条件を調整し、Arガスがある特定の範囲内にあるものに関しては、良好な絶縁性を示すことを見いだした。

【0014】

よって、スパッタ中のAr量を減らすことを良しとした従来のシリコン酸化物膜の成膜方法にとらわれず、膜中のAr量を最適範囲内にすることで、絶縁性が良好なシリコン酸化物膜を得ることができることを見出すに至ったわけである。

【0015】

即ち、本発明は、Siの酸化物から成るアモルファス絶縁体膜において、前記絶縁体膜中にArが含有されており、その膜中のAr量がSiに対して原子数比で特定の範囲であるシリコン酸化物アモルファス絶縁体膜を用いるものである。それによって良好な特性の絶縁体膜を得ることができる。更にそれを用いることで、良好な特性を有する薄膜トランジスタ等のデバイスを得ることができる。

【0016】

本発明に係るアモルファス絶縁体膜は、Si酸化物アモルファス絶縁体膜である。そしてその絶縁体膜中にArが含有されており、その膜中のAr量がSiに対して原子数比で3原子%以上(Ar/Si ≧ 3 at.%)である。

【0017】

その比は、望ましくは、Ar/Si ≧ 4 at.%であり、さらに望ましくは、Ar/Si ≧ 5 at.%である。

【0018】

膜中のAr量の上限は、望ましくはAr/Si ≦ 17 at.%であり、さらに望ましくはAr/Si ≦ 16 at.%である。

【0019】

シリコン酸化物アモルファス絶縁体膜は、成膜時の基板および基板ホルダーの電位などの成膜パラメータを調整することで、上記の量のArを含有し、かつ良好な絶縁特性を有する。それにより、シリコン酸化物アモルファス絶縁体膜に1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下となる絶縁体膜を得ることができる。さらに、絶縁体膜に1MV/cmの電界を印加した際の電流密度が3×10-7A/cm2以下と絶縁体膜を得ることができる。

【0020】

本発明のアモルファス絶縁体膜を形成する方法としては、スパッタ法を用いることが望ましい。スパッタ法のうち、rfマグネトロンスパッタ法を用いることがさらに望ましい。また、本発明のアモルファス絶縁体膜は300℃以下の温度で成膜することが望ましく、さらに室温で成膜することが望ましい。成膜時の基板または基板ホルダーまたはその両方の電位が接地電位に対して正、あるいは接地から浮かしたオープンの状態で成膜を行うのが望ましい形態である。

【0021】

本発明のアモルファス絶縁体膜を用いたデバイスとしてはTFTが挙げられる。アモルファス絶縁体膜を用いたTFTは、上記アモルファス絶縁体膜をゲート絶縁膜として用いるものである。

【0022】

そのTFTにおいては、チャネル層として酸化物半導体膜を用いるのが望ましい。さらにアモルファス酸化物半導体膜を用いるのが望ましい形態である。チャネル層はスパッタ法で形成することが望ましい。またはPLD(Pulsed Laser Deposition)法を含めた真空蒸着法で形成することも望ましい形態の1つである。

【0023】

以上により、本発明は絶縁特性の優れたアモルファス絶縁体膜が得られ、それを用いることで従来より高性能で、且つ、低コストのTFTを従来より低温の製造プロセスにて得ることができる。

【0024】

例えば、酸化物半導体薄膜をチャネル層に用いたTFTにおいて性能が高く安定性及び信頼性の高い素子を低コストで提供することが可能となる。また、上記素子をプラスティック基板上など、製造工程中に高温にできない状況下であっても低温で形成することが可能となる。

【0025】

(実験例)

次に、本発明を実験例によりさらに詳細に説明する。本発明者らは、上記従来の課題を解決するため、スパッタ法によるシリコン酸化物アモルファス絶縁体膜の研究を行い、特に絶縁体膜中のAr量と絶縁特性の相関を調べた。スパッタ装置は平行平板型rfマグネトロンスパッタ装置を用い、ターゲットとして直径75mmのSiO2板を用いた。成膜時の設定基板温度は室温設定で行った。

【0026】

基板はガラス基板上に電極としてTi/Au/Ti積層膜を成膜したものを用いた。基板および基板ホルダーの電位は接地から浮かしたオープン状態で成膜を行った。変化させた成膜パラメータは基板位置(ターゲット鉛直上設置およびターゲット斜め上方設置)、成膜圧力(0.06〜2Pa)、成膜時ガス組成(0≦O2/(Ar+O2)≦0.50)、ターゲット電力(10W〜400W)であった。

【0027】

作製したシリコン酸化物アモルファス絶縁体膜の膜中のAr量を蛍光X線分析により測定した。膜中のAr/Si比は成膜パラメータとして成膜ガス組成のAr/O2比を小さくすることで制御した。例えば、成膜ガス中のO2の割合を増すことでAr/Si比を増加させた。また、O2を導入しないArのみの成膜条件時においても、ターゲット電力を小さくすることでAr/Si比は顕著に増加させることができる。

【0028】

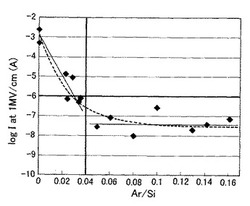

作製した絶縁体膜上に直径0.3mmのAu(40nm)/Ti(5nm)積層電極を形成し、図2に示すような平行平型のキャパシタ素子を作製し、その電流電圧特性を測定した。図1に測定した絶縁体膜の電流電圧測定結果から得られた1MV/cm印加時の電流密度のAr/Si比依存性を示す。

【0029】

図1から読み取れるようにAr/Si ≧ 3 at.%のものは1MV/cm印加時の電流密度1×10-6A/cm2以下のリーク電流特性が得られた。このリーク電流特性を有する膜を図3に示す構造のTFTのゲート絶縁体膜に適用した。その結果、作製プロセス時のエラーによる不良および低抵抗のチャネル半導体層を用いたデバイスを除くと、図4に示すようなTFTの伝達特性のオフ電流値が10-12A以下になり、良好なTFT特性を示した。

【0030】

よってAr/Si ≧ 3 at.%はSi酸化物アモルファス絶縁体膜にとって、良好な絶縁特性を示す膜のひとつの指標になりえる。また図1のグラフより、Ar/Si = 4 at.%を境にAr/Siの小さい領域ではAr量の増加に伴いリーク電流値が減少している。そして、Ar/Si ≧ 4 at.%ではリーク電流値はAr量に対してほぼ一定となる。

【0031】

このことから、Ar/Si比が4 at.%以上の領域で、Ar量増加に伴うリーク電流の低減の効果が最大になることを示している。ここで図1の曲線の変曲点であるAr/Si = 4 at.%は、実験値のプロットに適当な曲線を描いたときの変極点である。実験データのプロット点からAr/Si比の領域を定義すると、Ar/Si ≧ 5 at.%となる。よって、Ar/Si ≧ 5 at.%の領域がAr量増加に伴うリーク電流の低減の効果がより高い確率で得られる領域として定義できる。

【0032】

Ar/Si比の上限値を設定するために、可能な限り高いAr/Si比を有する膜を得るために、スパッタ電力を50,20,10Wと小さくし、Si酸化物アモルファス絶縁体膜を作製した。得られた膜中のAr/Si比は、50W作製膜>10W作製膜>20W作製膜であり、20W以上のスパッタ電力ではスパッタ電力の低下に伴いAr/Si比は増加した。

【0033】

一方、スパッタ電力10Wでは20WよりAr/Si比が小さくなり、20W作製膜中のAr/Si比0.162が膜中Ar/Si比の最大値と考えられる。また、Ar/Si比0.162の膜(20W作製膜)においても、絶縁特性は良好であった。よって本発明のAr/Si比の上限値はAr/Si ≦ 17 at.%と考えられる。実験によるAr/Si比の最大値を小数第3位を切り捨て、実験データのプロットで領域を定義するとAr/Si ≦ 16 at.%となり、リーク電流の低減の効果がより高い確率で得られる領域として定義できる。

【0034】

ArがSi酸化物アモルファス膜中に比較的多量に含まれることで絶縁特性が向上する理由としては必ずしも解明されていないが、本発明者らは以下のように考察した。非特許文献2にあるように、蒸着等の気相からの成膜手法によりSi酸化物膜を成膜した場合、膜内部には多量の微小空隙が生成される。

【0035】

従って、成膜後に真空チャンバーから取り出して大気に晒すだけで、水分子が膜中に浸透し、微小空隙内にとどまる。このような膜中の水分子が膜の絶縁特性を劣化させる(膜中の電気の導通に寄与する)ものと考えられる。

【0036】

本発明の絶縁体膜は真空チャンバー内での成膜中に、微小空隙内にArが導入され、その結果膜中に水分子が浸透すること抑制する。X線反射率測定により本実験例の絶縁体膜の密度を測定したところ、Ar量(Ar/Si比)が増加するにしたがって密度が増加する。このことはArが膜中に導入されることによる絶縁体膜の体積変化はない、もしくは少ないということを意味している。

【0037】

即ち、膜中の微小空隙内にArが存在するという上述のモデルと矛盾しない。よって、絶縁体膜中の微小空隙にあらかじめArを導入することで、真空チャンバーから取り出しで大気に晒すことによる水分子の膜中への浸透を抑えることができ、良好な絶縁特性を維持できたものであると考えられる。

【0038】

上述の成膜条件で作製したSi酸化物アモルファス絶縁体膜中のAr/Si比と絶縁特性の相関をとり、上記Ar/Si比の領域において絶縁特性が良好な膜を得ることができる。しかし、例えばより高エネルギーArイオンが膜に照射される条件などを用いて成膜した場合には、従来例にあるようなArイオン衝撃によりSi-O結合が破壊され、絶縁特性のよくない膜が形成されるものと考えられる。

【0039】

よって、上述のAr/Si比の領域で特性良好な膜が得られるには成膜条件が重要となる。本発明者が用いた条件に準じた成膜条件での絶縁体膜は、上述のAr/Si比を有していれば、1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下、好ましくは3×10-7A/cm2以下である。よって、本発明の絶縁体膜は、従来の成膜条件(高エネルギーArイオン照射条件など)で作製した膜とは異なり、上述のAr/Si比を有し、かつ上述の絶縁特性(電流密度)を有する膜である。

【実施例】

【0040】

次に、本発明を実施例によって具体的に説明するが、本発明はこれらの記載によって何ら限定されるものではない。

【0041】

(実施例1:アモルファス絶縁体膜)

実施例1では、まず、ガラス基板上にそれぞれ5nm、40nm、5nmの厚さのTi,Au,Ti積層膜を形成し下部電極とした。その上にrfマグネトロンスパッタ装置により厚さ100nmのSiO2膜を作製した。成膜条件を以下に記す。基板はターゲット中心鉛直方向から約55度傾いた方向に基板中心があり、ターゲット中心から基板中心までの距離が約130mmになる位置に配置した。

【0042】

基板および基板ホルダーは電気的に絶縁状態(オープン状態)にした。成膜ガスはArのみで、その圧力は0.1Pa、スパッタ電力は20Wであった。成膜時の温度設定ならびに温度計表示温度は20℃であった。下部電極付きの基板のほかに、蛍光X線によるAr/Si組成分析用のSi基板も同時に配置し、これらの基板に同時に成膜を行った。

【0043】

成膜した膜上に直径0.3mmのAu(40nm)/Ti(5nm)積層電極を形成し、図2に示すような平行平型のキャパシタ素子を作製した。図2において、1はガラス基板、2は下部電極(Ti/Au/Ti)、3はSiO2膜、4は上部電極(φ0.3mm、Ti/Au/Ti)である。

【0044】

次に、それらの素子の電流−電圧(I−V)特性を電圧挿印による電流測定により評価した。一方、Ar/Si比評価用Si基板上のSiO2膜は蛍光X線(XRF)分析によりAr量とO量を評価し、別途カーボン基板上のSiO2膜のSi及びOのXRF分析より求めた値を用いて膜中Si原子数に対するAr原子数(Ar/Si比)を求めた。

【0045】

図1は作製したSiO2膜のAr/Si比と1MV/cm電界印加時の電流密度の相関を示す。図1中の一番右にプロットされた点が本実施例により得られたSiO2膜の値である。このように1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下のかつ3×10-7A/cm2以下の良好な絶縁特性の値を示すことが分かった。

【0046】

(実施例2:TFT素子)

実施例2では、本発明のアモルファス絶縁体膜を用いて図3に示すボトムゲート型TFT素子を作製した。

【0047】

図3に示すようにガラス基板11上にゲート電極12として電子ビーム蒸着によりTi(5nm)/Au(40nm)/Ti(5nm)積層膜を形成し、これをフォトリソグラフィー法とリフトオフ法により成形した。

【0048】

その上にゲート絶縁体膜13として厚さ100nmのSiO2膜をrfマグネトロンスパッタ装置用いて成膜した。成膜条件はスパッタ電力400W、スパッタガス圧力0.1Pa、スパッタガス組成Ar/02=50/50、室温成膜とした。その条件でのSiO2膜中のAr量はAr/Si比で4.9%であった。その後、SiO2膜13をフォトリソグラフィー法とエッチング法により成形した。

【0049】

次に、チャネル層14としてInGaO3(ZnO)ターゲットを用いたrfマグネトロンスパッタにより、厚さ40nmのInxGayZnzOv膜を室温で成膜した。得られたInxGayZnzOv膜はアモルファスであった。

【0050】

次に、InxGayZnzOv膜14を必要な大きさにエッチング加工した後、ソース電極15並びにドレイン電極16をフォトリソグラフィー法及びリフトオフ法を用いて形成した。

【0051】

電極材料はAu(150nm)/Ti(5nm)積層膜であり、成膜方法は電子ビーム蒸着法である。以上の工程を経てTFT素子を作製した。得られたTFT素子のうち、ゲート長10μm、ゲート幅60μmのTFT素子の伝達特性(ドレイン電流−ゲート電圧特性)を測定したところ、図4に示す特性が得られた。図4に示すように、高電圧印加においてもゲートリーク電流値が小さく、良好な特性を示すTFT素子が得られた。

【0052】

以上のよう本発明のアモルファス絶縁体膜をTFTのゲート絶縁膜に用いることで、良好な特性のアモルファス酸化物半導体チャネルTFT素子を室温プロセスで得ることができた。これは、室温プロセスのみならず温度を上げたプロセスにおいても有効である。中でもCVDプロセスが適用できない300℃以下のプロセスにおいて特に効果的である。また、TFTチャネルとして結晶性の酸化物半導体を用いたTFTにおいても同様の効果が得られる。

【産業上の利用可能性】

【0053】

本発明のアモルファス絶縁体膜は、各種ディスプレイ等の電子デバイスの部品材料として幅広く利用できる。特に、それを用いたTFTはLCDや有機ELディスプレイ等のスイッチング素子、受光素子、センサ素子等のマトリクスデバイスのスイッチング素子として幅広く利用できる。更にICカードやIDタグ等にも幅広く利用することができる。

【図面の簡単な説明】

【0054】

【図1】本発明のアモルファス絶縁体膜のAr/Si比と1MV/cm印加時の電流密度の相関を示す図である。

【図2】本発明の実験例および実施例1で用いたI−V特性評価用の平行平板キャパシタ素子の構造を示す模式図である。

【図3】本発明の実験例および実施例2で用いたボトムゲート型TFTの構造を示す模式図である。

【図4】本発明のアモルファス絶縁体膜をゲート絶縁膜として用いたボトムゲート型アモルファス酸化物チャネルTFTの伝達特性を示す図である。

【符号の説明】

【0055】

1 ガラス基板

2 下部電極

3 SiO2膜

4 上部電極

11 ガラス電極

12 ゲート電極

13 ゲート絶縁膜

14 チャネル層

15 ドレイン電極

16 ソース電極

【技術分野】

【0001】

本発明は、アモルファス絶縁体膜及びそれを用いた薄膜トランジスタに関するものである。

【背景技術】

【0002】

近年、液晶、プラズマ或いは有機ELを用いたディスプレイの開発が大型小型問わずに盛んに行われている。それらの画素の駆動デバイスとしての薄膜トランジスタ(TFT)にアモルファスシリコン、低温ポリシリコン及び酸化物半導体薄膜を用いることが試みられている。特に、アモルファス酸化物半導体をチャネルに用いたTFTは室温形成によるプラスティック基板を用いたフレキシブルディスプレイへの適用が可能であるため、非特許文献1にあるように、盛んに研究開発が行われている。

【非特許文献1】Applied Physics Letters, Volume 89, 112123-1 〜 3ページ

【特許文献1】特開平2−90568号公報

【非特許文献2】Journal of Applied Physics, Volume 78, 962 〜 968ページ

【発明の開示】

【発明が解決しようとする課題】

【0003】

非特許文献1のTFTでは、アモルファス酸化物半導体チャネル層としてアモルファスInGaZnO4薄膜がスパッタ法で堆積して用いられている。また同様に、ゲート絶縁膜としてY2O3膜がスパッタ法で堆積して用いられている。ゲート絶縁膜であるY2O3は、TFTのゲート絶縁膜として一般に用いられる酸化シリコン(SiO2)などと比較するとコストが高く、SiO2等のシリコン系アモルファス絶縁体膜への転換が期待されている。

【0004】

SiO2などのシリコン系アモルファス絶縁体膜(絶縁膜ともいう)は一般的に化学気相成長法(CVD法)で製造されることが多い。CVD法で絶縁性能が良好な絶縁体膜を得るには、一般的に300℃以上の成膜温度が必要であり、プラスティック基板上への形成が困難である。

【0005】

一方、TFTに用いるアモルファス酸化物半導体は、前述のように、スパッタ法により300℃以下の成膜温度で形成することが可能である。従って、絶縁体膜の形成工程もアモルファス酸化物半導体と同様にスパッタ法で形成することができれば、プラスティック基板等の耐熱性の低い基板が採用できることから望ましい。

【0006】

しかしながら、スパッタ法で堆積した従来のシリコン系アモルファス絶縁体膜は、CVD法による同膜より絶縁特性に劣るため、これまで実用に供さなかった。このため、プラスティック基板上に素子を形成する場合などはCVD法による成膜時の温度以下の温度での絶縁体膜形成が求められており、特許文献1にあるように、スパッタ法による絶縁体膜形成の高性能化が望まれている。

【0007】

本発明の目的は、Siの酸化物から成るアモルファス絶縁体膜において、良好な特性の絶縁体膜並びにそれを用いた薄膜トランジスタを提供することにある。

【課題を解決するための手段】

【0008】

本願発明者らは、上記従来の課題を解決するため、スパッタ法によるシリコン酸化物アモルファス絶縁体膜について鋭意検討を行った。そして絶縁体膜中のAr量と絶縁特性の相関についての知見を得、絶縁特性が良好なシリコン酸化物アモルファス絶縁体膜を発明するに至ったものである。

【0009】

本発明は上記知見に基づいて完成に至ったものであり、その骨子とするところは、シリコン(Si)酸化物を含むアモルファス絶縁体膜であって、前記絶縁体膜中にArが含有されており、該Ar含有量がSiに対して原子数比で3原子%以上であることを特徴とするものである。

【発明の効果】

【0010】

本発明によれば、絶縁特性の優れた絶縁体膜を得ることができる。また本発明の絶縁体膜を用いることで従来より高性能で、低コストの薄膜トランジスタを低温の製造プロセスにて得ることができる。

【発明を実施するための最良の形態】

【0011】

次に、発明を実施するための最良の形態について説明する。従来は上記特許文献1にあるように、スパッタ法により作製したシリコン酸化物膜の絶縁性低下はスパッタ中のAr粒子が膜にダメージを与えるためであると考えられている。そして、スパッタガス中のArガスをなるべく少なくし、酸素ガスをできるだけ多くした条件で成膜することが、シリコン酸化物膜の絶縁性向上の方法としてとられていた。すなわち、膜中のAr量も少ないほど良しとされた。

【0012】

しかしながら、スパッタガス中のAr対酸素の比率と絶縁性の関係は、シリコン酸化物膜の成膜条件の記載が十分でなく、成膜条件の一貫性に疑問が生じる。また、成膜したシリコン酸化物膜中のAr量とシリコン酸化物膜の絶縁性の相関を詳細に調べた文献は見当たらない。

【0013】

そこで本発明者らはスパッタ法によるシリコン酸化物膜を種々の条件で作製し、その膜中のAr量と絶縁性に関して相関があることを見出した。さらにはスパッタガス中のAr量がたとえ100%(酸素ガスなし)であっても、成膜条件を調整し、Arガスがある特定の範囲内にあるものに関しては、良好な絶縁性を示すことを見いだした。

【0014】

よって、スパッタ中のAr量を減らすことを良しとした従来のシリコン酸化物膜の成膜方法にとらわれず、膜中のAr量を最適範囲内にすることで、絶縁性が良好なシリコン酸化物膜を得ることができることを見出すに至ったわけである。

【0015】

即ち、本発明は、Siの酸化物から成るアモルファス絶縁体膜において、前記絶縁体膜中にArが含有されており、その膜中のAr量がSiに対して原子数比で特定の範囲であるシリコン酸化物アモルファス絶縁体膜を用いるものである。それによって良好な特性の絶縁体膜を得ることができる。更にそれを用いることで、良好な特性を有する薄膜トランジスタ等のデバイスを得ることができる。

【0016】

本発明に係るアモルファス絶縁体膜は、Si酸化物アモルファス絶縁体膜である。そしてその絶縁体膜中にArが含有されており、その膜中のAr量がSiに対して原子数比で3原子%以上(Ar/Si ≧ 3 at.%)である。

【0017】

その比は、望ましくは、Ar/Si ≧ 4 at.%であり、さらに望ましくは、Ar/Si ≧ 5 at.%である。

【0018】

膜中のAr量の上限は、望ましくはAr/Si ≦ 17 at.%であり、さらに望ましくはAr/Si ≦ 16 at.%である。

【0019】

シリコン酸化物アモルファス絶縁体膜は、成膜時の基板および基板ホルダーの電位などの成膜パラメータを調整することで、上記の量のArを含有し、かつ良好な絶縁特性を有する。それにより、シリコン酸化物アモルファス絶縁体膜に1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下となる絶縁体膜を得ることができる。さらに、絶縁体膜に1MV/cmの電界を印加した際の電流密度が3×10-7A/cm2以下と絶縁体膜を得ることができる。

【0020】

本発明のアモルファス絶縁体膜を形成する方法としては、スパッタ法を用いることが望ましい。スパッタ法のうち、rfマグネトロンスパッタ法を用いることがさらに望ましい。また、本発明のアモルファス絶縁体膜は300℃以下の温度で成膜することが望ましく、さらに室温で成膜することが望ましい。成膜時の基板または基板ホルダーまたはその両方の電位が接地電位に対して正、あるいは接地から浮かしたオープンの状態で成膜を行うのが望ましい形態である。

【0021】

本発明のアモルファス絶縁体膜を用いたデバイスとしてはTFTが挙げられる。アモルファス絶縁体膜を用いたTFTは、上記アモルファス絶縁体膜をゲート絶縁膜として用いるものである。

【0022】

そのTFTにおいては、チャネル層として酸化物半導体膜を用いるのが望ましい。さらにアモルファス酸化物半導体膜を用いるのが望ましい形態である。チャネル層はスパッタ法で形成することが望ましい。またはPLD(Pulsed Laser Deposition)法を含めた真空蒸着法で形成することも望ましい形態の1つである。

【0023】

以上により、本発明は絶縁特性の優れたアモルファス絶縁体膜が得られ、それを用いることで従来より高性能で、且つ、低コストのTFTを従来より低温の製造プロセスにて得ることができる。

【0024】

例えば、酸化物半導体薄膜をチャネル層に用いたTFTにおいて性能が高く安定性及び信頼性の高い素子を低コストで提供することが可能となる。また、上記素子をプラスティック基板上など、製造工程中に高温にできない状況下であっても低温で形成することが可能となる。

【0025】

(実験例)

次に、本発明を実験例によりさらに詳細に説明する。本発明者らは、上記従来の課題を解決するため、スパッタ法によるシリコン酸化物アモルファス絶縁体膜の研究を行い、特に絶縁体膜中のAr量と絶縁特性の相関を調べた。スパッタ装置は平行平板型rfマグネトロンスパッタ装置を用い、ターゲットとして直径75mmのSiO2板を用いた。成膜時の設定基板温度は室温設定で行った。

【0026】

基板はガラス基板上に電極としてTi/Au/Ti積層膜を成膜したものを用いた。基板および基板ホルダーの電位は接地から浮かしたオープン状態で成膜を行った。変化させた成膜パラメータは基板位置(ターゲット鉛直上設置およびターゲット斜め上方設置)、成膜圧力(0.06〜2Pa)、成膜時ガス組成(0≦O2/(Ar+O2)≦0.50)、ターゲット電力(10W〜400W)であった。

【0027】

作製したシリコン酸化物アモルファス絶縁体膜の膜中のAr量を蛍光X線分析により測定した。膜中のAr/Si比は成膜パラメータとして成膜ガス組成のAr/O2比を小さくすることで制御した。例えば、成膜ガス中のO2の割合を増すことでAr/Si比を増加させた。また、O2を導入しないArのみの成膜条件時においても、ターゲット電力を小さくすることでAr/Si比は顕著に増加させることができる。

【0028】

作製した絶縁体膜上に直径0.3mmのAu(40nm)/Ti(5nm)積層電極を形成し、図2に示すような平行平型のキャパシタ素子を作製し、その電流電圧特性を測定した。図1に測定した絶縁体膜の電流電圧測定結果から得られた1MV/cm印加時の電流密度のAr/Si比依存性を示す。

【0029】

図1から読み取れるようにAr/Si ≧ 3 at.%のものは1MV/cm印加時の電流密度1×10-6A/cm2以下のリーク電流特性が得られた。このリーク電流特性を有する膜を図3に示す構造のTFTのゲート絶縁体膜に適用した。その結果、作製プロセス時のエラーによる不良および低抵抗のチャネル半導体層を用いたデバイスを除くと、図4に示すようなTFTの伝達特性のオフ電流値が10-12A以下になり、良好なTFT特性を示した。

【0030】

よってAr/Si ≧ 3 at.%はSi酸化物アモルファス絶縁体膜にとって、良好な絶縁特性を示す膜のひとつの指標になりえる。また図1のグラフより、Ar/Si = 4 at.%を境にAr/Siの小さい領域ではAr量の増加に伴いリーク電流値が減少している。そして、Ar/Si ≧ 4 at.%ではリーク電流値はAr量に対してほぼ一定となる。

【0031】

このことから、Ar/Si比が4 at.%以上の領域で、Ar量増加に伴うリーク電流の低減の効果が最大になることを示している。ここで図1の曲線の変曲点であるAr/Si = 4 at.%は、実験値のプロットに適当な曲線を描いたときの変極点である。実験データのプロット点からAr/Si比の領域を定義すると、Ar/Si ≧ 5 at.%となる。よって、Ar/Si ≧ 5 at.%の領域がAr量増加に伴うリーク電流の低減の効果がより高い確率で得られる領域として定義できる。

【0032】

Ar/Si比の上限値を設定するために、可能な限り高いAr/Si比を有する膜を得るために、スパッタ電力を50,20,10Wと小さくし、Si酸化物アモルファス絶縁体膜を作製した。得られた膜中のAr/Si比は、50W作製膜>10W作製膜>20W作製膜であり、20W以上のスパッタ電力ではスパッタ電力の低下に伴いAr/Si比は増加した。

【0033】

一方、スパッタ電力10Wでは20WよりAr/Si比が小さくなり、20W作製膜中のAr/Si比0.162が膜中Ar/Si比の最大値と考えられる。また、Ar/Si比0.162の膜(20W作製膜)においても、絶縁特性は良好であった。よって本発明のAr/Si比の上限値はAr/Si ≦ 17 at.%と考えられる。実験によるAr/Si比の最大値を小数第3位を切り捨て、実験データのプロットで領域を定義するとAr/Si ≦ 16 at.%となり、リーク電流の低減の効果がより高い確率で得られる領域として定義できる。

【0034】

ArがSi酸化物アモルファス膜中に比較的多量に含まれることで絶縁特性が向上する理由としては必ずしも解明されていないが、本発明者らは以下のように考察した。非特許文献2にあるように、蒸着等の気相からの成膜手法によりSi酸化物膜を成膜した場合、膜内部には多量の微小空隙が生成される。

【0035】

従って、成膜後に真空チャンバーから取り出して大気に晒すだけで、水分子が膜中に浸透し、微小空隙内にとどまる。このような膜中の水分子が膜の絶縁特性を劣化させる(膜中の電気の導通に寄与する)ものと考えられる。

【0036】

本発明の絶縁体膜は真空チャンバー内での成膜中に、微小空隙内にArが導入され、その結果膜中に水分子が浸透すること抑制する。X線反射率測定により本実験例の絶縁体膜の密度を測定したところ、Ar量(Ar/Si比)が増加するにしたがって密度が増加する。このことはArが膜中に導入されることによる絶縁体膜の体積変化はない、もしくは少ないということを意味している。

【0037】

即ち、膜中の微小空隙内にArが存在するという上述のモデルと矛盾しない。よって、絶縁体膜中の微小空隙にあらかじめArを導入することで、真空チャンバーから取り出しで大気に晒すことによる水分子の膜中への浸透を抑えることができ、良好な絶縁特性を維持できたものであると考えられる。

【0038】

上述の成膜条件で作製したSi酸化物アモルファス絶縁体膜中のAr/Si比と絶縁特性の相関をとり、上記Ar/Si比の領域において絶縁特性が良好な膜を得ることができる。しかし、例えばより高エネルギーArイオンが膜に照射される条件などを用いて成膜した場合には、従来例にあるようなArイオン衝撃によりSi-O結合が破壊され、絶縁特性のよくない膜が形成されるものと考えられる。

【0039】

よって、上述のAr/Si比の領域で特性良好な膜が得られるには成膜条件が重要となる。本発明者が用いた条件に準じた成膜条件での絶縁体膜は、上述のAr/Si比を有していれば、1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下、好ましくは3×10-7A/cm2以下である。よって、本発明の絶縁体膜は、従来の成膜条件(高エネルギーArイオン照射条件など)で作製した膜とは異なり、上述のAr/Si比を有し、かつ上述の絶縁特性(電流密度)を有する膜である。

【実施例】

【0040】

次に、本発明を実施例によって具体的に説明するが、本発明はこれらの記載によって何ら限定されるものではない。

【0041】

(実施例1:アモルファス絶縁体膜)

実施例1では、まず、ガラス基板上にそれぞれ5nm、40nm、5nmの厚さのTi,Au,Ti積層膜を形成し下部電極とした。その上にrfマグネトロンスパッタ装置により厚さ100nmのSiO2膜を作製した。成膜条件を以下に記す。基板はターゲット中心鉛直方向から約55度傾いた方向に基板中心があり、ターゲット中心から基板中心までの距離が約130mmになる位置に配置した。

【0042】

基板および基板ホルダーは電気的に絶縁状態(オープン状態)にした。成膜ガスはArのみで、その圧力は0.1Pa、スパッタ電力は20Wであった。成膜時の温度設定ならびに温度計表示温度は20℃であった。下部電極付きの基板のほかに、蛍光X線によるAr/Si組成分析用のSi基板も同時に配置し、これらの基板に同時に成膜を行った。

【0043】

成膜した膜上に直径0.3mmのAu(40nm)/Ti(5nm)積層電極を形成し、図2に示すような平行平型のキャパシタ素子を作製した。図2において、1はガラス基板、2は下部電極(Ti/Au/Ti)、3はSiO2膜、4は上部電極(φ0.3mm、Ti/Au/Ti)である。

【0044】

次に、それらの素子の電流−電圧(I−V)特性を電圧挿印による電流測定により評価した。一方、Ar/Si比評価用Si基板上のSiO2膜は蛍光X線(XRF)分析によりAr量とO量を評価し、別途カーボン基板上のSiO2膜のSi及びOのXRF分析より求めた値を用いて膜中Si原子数に対するAr原子数(Ar/Si比)を求めた。

【0045】

図1は作製したSiO2膜のAr/Si比と1MV/cm電界印加時の電流密度の相関を示す。図1中の一番右にプロットされた点が本実施例により得られたSiO2膜の値である。このように1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下のかつ3×10-7A/cm2以下の良好な絶縁特性の値を示すことが分かった。

【0046】

(実施例2:TFT素子)

実施例2では、本発明のアモルファス絶縁体膜を用いて図3に示すボトムゲート型TFT素子を作製した。

【0047】

図3に示すようにガラス基板11上にゲート電極12として電子ビーム蒸着によりTi(5nm)/Au(40nm)/Ti(5nm)積層膜を形成し、これをフォトリソグラフィー法とリフトオフ法により成形した。

【0048】

その上にゲート絶縁体膜13として厚さ100nmのSiO2膜をrfマグネトロンスパッタ装置用いて成膜した。成膜条件はスパッタ電力400W、スパッタガス圧力0.1Pa、スパッタガス組成Ar/02=50/50、室温成膜とした。その条件でのSiO2膜中のAr量はAr/Si比で4.9%であった。その後、SiO2膜13をフォトリソグラフィー法とエッチング法により成形した。

【0049】

次に、チャネル層14としてInGaO3(ZnO)ターゲットを用いたrfマグネトロンスパッタにより、厚さ40nmのInxGayZnzOv膜を室温で成膜した。得られたInxGayZnzOv膜はアモルファスであった。

【0050】

次に、InxGayZnzOv膜14を必要な大きさにエッチング加工した後、ソース電極15並びにドレイン電極16をフォトリソグラフィー法及びリフトオフ法を用いて形成した。

【0051】

電極材料はAu(150nm)/Ti(5nm)積層膜であり、成膜方法は電子ビーム蒸着法である。以上の工程を経てTFT素子を作製した。得られたTFT素子のうち、ゲート長10μm、ゲート幅60μmのTFT素子の伝達特性(ドレイン電流−ゲート電圧特性)を測定したところ、図4に示す特性が得られた。図4に示すように、高電圧印加においてもゲートリーク電流値が小さく、良好な特性を示すTFT素子が得られた。

【0052】

以上のよう本発明のアモルファス絶縁体膜をTFTのゲート絶縁膜に用いることで、良好な特性のアモルファス酸化物半導体チャネルTFT素子を室温プロセスで得ることができた。これは、室温プロセスのみならず温度を上げたプロセスにおいても有効である。中でもCVDプロセスが適用できない300℃以下のプロセスにおいて特に効果的である。また、TFTチャネルとして結晶性の酸化物半導体を用いたTFTにおいても同様の効果が得られる。

【産業上の利用可能性】

【0053】

本発明のアモルファス絶縁体膜は、各種ディスプレイ等の電子デバイスの部品材料として幅広く利用できる。特に、それを用いたTFTはLCDや有機ELディスプレイ等のスイッチング素子、受光素子、センサ素子等のマトリクスデバイスのスイッチング素子として幅広く利用できる。更にICカードやIDタグ等にも幅広く利用することができる。

【図面の簡単な説明】

【0054】

【図1】本発明のアモルファス絶縁体膜のAr/Si比と1MV/cm印加時の電流密度の相関を示す図である。

【図2】本発明の実験例および実施例1で用いたI−V特性評価用の平行平板キャパシタ素子の構造を示す模式図である。

【図3】本発明の実験例および実施例2で用いたボトムゲート型TFTの構造を示す模式図である。

【図4】本発明のアモルファス絶縁体膜をゲート絶縁膜として用いたボトムゲート型アモルファス酸化物チャネルTFTの伝達特性を示す図である。

【符号の説明】

【0055】

1 ガラス基板

2 下部電極

3 SiO2膜

4 上部電極

11 ガラス電極

12 ゲート電極

13 ゲート絶縁膜

14 チャネル層

15 ドレイン電極

16 ソース電極

【特許請求の範囲】

【請求項1】

シリコン(Si)酸化物を含むアモルファス絶縁体膜であって、前記絶縁体膜中にArが含有されており、該Ar含有量がSiに対して原子数比で3原子%以上であることを特徴とするアモルファス絶縁体膜。

【請求項2】

前記絶縁体膜中のAr量が、Siに対して原子数比で17原子%以下であることを特徴とする、請求項1に記載のアモルファス絶縁体膜。

【請求項3】

前記絶縁体膜中のAr量が、Siに対して原子数比で16原子%以下であることを特徴とする、請求項1又は2に記載のアモルファス絶縁体膜。

【請求項4】

前記絶縁体膜の電流電圧特性において、絶縁体膜に1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下であることを特徴とする、請求項1から3のいずれか1項に記載のアモルファス絶縁体膜。

【請求項5】

前記絶縁体膜の電流電圧特性において、絶縁体膜に1MV/cmの電界を印加した際の電流密度が3×10-7A/cm2以下であることを特徴とする、請求項1から4のいずれか1項に記載のアモルファス絶縁体膜。

【請求項6】

前記アモルファス絶縁体膜はスパッタ法で製造されていることを特徴とする請求項1乃至5のいずれか1項に記載のアモルファス絶縁体膜。

【請求項7】

請求項1乃至6のいずれか1項に記載のアモルファス絶縁体膜をゲート絶縁膜として用いることを特徴とする薄膜トランジスタ。

【請求項8】

チャネルが酸化物半導体であることを特徴とする請求項7に記載の薄膜トランジスタ。

【請求項9】

チャネルがアモルファス酸化物半導体であることを特徴とする請求項7又は8に記載の薄膜トランジスタ。

【請求項1】

シリコン(Si)酸化物を含むアモルファス絶縁体膜であって、前記絶縁体膜中にArが含有されており、該Ar含有量がSiに対して原子数比で3原子%以上であることを特徴とするアモルファス絶縁体膜。

【請求項2】

前記絶縁体膜中のAr量が、Siに対して原子数比で17原子%以下であることを特徴とする、請求項1に記載のアモルファス絶縁体膜。

【請求項3】

前記絶縁体膜中のAr量が、Siに対して原子数比で16原子%以下であることを特徴とする、請求項1又は2に記載のアモルファス絶縁体膜。

【請求項4】

前記絶縁体膜の電流電圧特性において、絶縁体膜に1MV/cmの電界を印加した際の電流密度が1×10-6A/cm2以下であることを特徴とする、請求項1から3のいずれか1項に記載のアモルファス絶縁体膜。

【請求項5】

前記絶縁体膜の電流電圧特性において、絶縁体膜に1MV/cmの電界を印加した際の電流密度が3×10-7A/cm2以下であることを特徴とする、請求項1から4のいずれか1項に記載のアモルファス絶縁体膜。

【請求項6】

前記アモルファス絶縁体膜はスパッタ法で製造されていることを特徴とする請求項1乃至5のいずれか1項に記載のアモルファス絶縁体膜。

【請求項7】

請求項1乃至6のいずれか1項に記載のアモルファス絶縁体膜をゲート絶縁膜として用いることを特徴とする薄膜トランジスタ。

【請求項8】

チャネルが酸化物半導体であることを特徴とする請求項7に記載の薄膜トランジスタ。

【請求項9】

チャネルがアモルファス酸化物半導体であることを特徴とする請求項7又は8に記載の薄膜トランジスタ。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2008−205098(P2008−205098A)

【公開日】平成20年9月4日(2008.9.4)

【国際特許分類】

【出願番号】特願2007−37994(P2007−37994)

【出願日】平成19年2月19日(2007.2.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成20年9月4日(2008.9.4)

【国際特許分類】

【出願日】平成19年2月19日(2007.2.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]