アライメントマーク及びアライメント方法

【課題】1mm2以下の小さいチップが多数配置されたウェハのアライメントを容易且つ正確に行えるようにする。

【解決手段】アライメントマーク1は、ウェハに対するパターン転写に用いられるレチクル5のスクライブライン領域3に、素子構成要素のパターンを密集して配置することにより構成されている。アライメントマーク1とその周囲環境との間において十分なコントラストを確保できるため、検査・測定設備がアライメントマーク1をユニークマークとして容易に認識することができるので、アライメントマーク認識不良を防止してウェハのアライメントを正確に実施することができる。

【解決手段】アライメントマーク1は、ウェハに対するパターン転写に用いられるレチクル5のスクライブライン領域3に、素子構成要素のパターンを密集して配置することにより構成されている。アライメントマーク1とその周囲環境との間において十分なコントラストを確保できるため、検査・測定設備がアライメントマーク1をユニークマークとして容易に認識することができるので、アライメントマーク認識不良を防止してウェハのアライメントを正確に実施することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体製造の検査・測定工程において使用するアライメントマーク及び当該アライメントマークを使用したアライメント方法に関する。

【背景技術】

【0002】

本願において、アライメントマーク(アライメント構造)という用語は、ウェハ上の絶対位置又は相対位置を識別するために用いられる任意の測定マークを意味する。具体的には、

(1)異なる層に設けられた2つのパターンの間のずれを比較するために露光装置又は重ね合わせターゲットにおけるステージにウェハをアライメントするためのマーク

(2)ライブラリ又は基準ウェハから得られる基準データと比較することによってウェハ上の絶対位置を測定するためのマーク(レジストレーションマーク)

(3)ウェハ上に配線や絶縁膜を所定の形状で形成する工程等の工程を終了する毎に配線の短絡や切断の有無又はパーティクルが付着しているか否か等の検査・解析を行う際の座標の原点を決定するためのマーク

等を総称して本願ではアライメントマークという。

【0003】

図12は特許文献1に開示されたアライメントマーク及びその周辺部の平面図であり、図13は、図12に示すアライメントマークが設けられたチップ領域の平面図である。

【0004】

図12に示すアライメントマーク101は、右上部を切り欠いた3/4円形状を有している。すなわち、アライメントマーク101は、右上部に直角部106を1つだけ有している。図13に示すように、アライメントマーク101は、スクライブライン105に囲まれており且つメモリセル104a〜104dが配置されているチップ能動領域107の隅部に形成されている。ここで、アライメントマーク101は、検査・解析工程を実施する前のエッチング工程においてエッチング除去される部材であるアルミニウムを用いて形成されている。また、図12に示すように、アライメントマーク101の近傍にはアルミニウム配線102が配置されている。アルミニウム配線102の角部は、アライメントマーク101の直角部106と異なる角度にアルミニウム配線102を折り曲げることによって形成されている。このようにすると、アライメントマーク101の近傍に直角部106と同じ向きの直角を有するパターンが存在しないようにすることができる。すなわち、検査・解析装置の位置決め機構の視野領域110においてアライメントマーク101を認識したときに、視野領域110内にアライメントマーク101の直角部106以外の他の直角部を有するパターンが存在しないようにすることができる。これにより、視野領域110内に形成されている十字状位置合わせマーク115の直角部をアライメントマーク101の直角部106に確実に合わせることができるため、アライメントを行う際に検査・解析装置が誤認識や認識不能を生じるおそれがなくなるので、アライメントを確実に行うことができる。

【特許文献1】特開2000−138146号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に開示されたアライメントマーク等の従来のアライメントマークによると、RF−IC(integrated circuit)やディスクリートIC等のようにチップサイズが1mm2 以下の小さい製品を製造する際にアライメントマーク認識不良が発生している。

【0006】

前記に鑑み、本発明は、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを容易且つ正確に行えるようにすることを目的としている。

【課題を解決するための手段】

【0007】

前記の目的を達成するために、従来のアライメントマークによって、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを正確に行うことができない原因を本願発明者が検討した結果、以下のような知見を得るに至った。

【0008】

検査・測定設備を用いた半導体ウェハのアライメントにおいて、CCD(Charge Coupled Device )カメラ等の撮像手段によってウェハの画像を電気信号に変換し、その画像信号に基づいてアライメントマークの位置情報を計測する方式が知られている。ここで、画像信号の分解能を向上させるためには、アライメントマークとその周囲との間のコントラストが要求される。また、前述の方式を用いたアライメントの実施手順としては、まず、アライメントマーク及びその周囲の画像を記憶させておき、次に、縦方向又は横方向にずらした2つの露光ショットによってアライメントマークを転写し、転写されたアライメントマークを認識させる。ところが、チップサイズが1mm2 以下の小チップ品種の場合、露光領域内に占めるスクライブライン領域の割合が大きくなるため、ウェハの画像全体が黒く見えるので、アライメントマークとその周囲とのコントラストが弱くなってしまう。すなわち、前述の特許文献1に開示されたアライメントマーク等の従来のアライメントマークによると、周囲環境に対するコントラストを十分に確保することができないため、検査・測定装置がアライメントマークを認識できないので、アライメント不良が発生してしまう。さらに、従来のアライメントマークによると、低倍率でのアライメントを実施する際(露光ショットによるアライメントマークの転写を小さい縮小倍率で実施する際)には、検査・測定設備の視野領域に対してアライメントマークが小さくなりすぎる結果、アライメントマーク認識不良が発生してしまうという問題が生じる。

【0009】

本発明は、前述の知見に基づくものであって、具体的には、本発明に係るアライメントマークは、ウェハに対するパターン転写に用いられるレチクルのスクライブライン領域に、素子構成要素のパターンを密集して配置することにより構成されている。

【0010】

尚、本発明において、「パターンが密集して配置された領域」とは、例えば複数の凹部が当該凹部の幅と同程度の間隔を置いて配置されている領域をいうものとする。ここで、凹部とは、素子分離を形成する場合にはフィールド酸化膜を形成しない箇所であり、多結晶シリコンや配線を形成する場合にはそれらがエッチングされている箇所である。

【0011】

本発明に係るアライメントマークによると、当該アライメントマークが転写された半導体ウェハにおいて検査・測定設備によりアライメントを実施するために、まず、アライメントマーク及びその周囲環境の画像を記憶させ、次に、縦方向又は横方向にずらした2つの露光ショットによってアライメントマークを認識させた場合に、次のような効果が得られる。すなわち、本発明に係るアライメントマークは、レチクルのスクライブライン領域に、素子構成要素のパターンを密集して配置することにより構成されているため、チップサイズが1mm2 以下となって露光領域内に占めるスクライブライン領域の割合が大きくなったとしても、ウェハの画像全体が黒く見えることを防止することができる。従って、アライメントマークとその周囲環境との間のコントラストについて、検査・測定設備で一般的に必要とされるレベルを確保できるため、アライメントマークを容易に認識することができるので、アライメントマーク認識不良を防止してウェハのアライメントを正確に実施することができる。

【0012】

また、本発明に係るアライメントマークは、半導体製造プロセスにおいてウェハ上の最下層である素子分離の形成工程から上層である配線の形成工程までの各工程で形成可能であるため、ほぼ全ての製造工程での検査・測定において前述の効果を得ることができる。

【0013】

本発明に係るアライメントマークにおいて、前記素子構成要素のパターンのサイズは、チップサイズの1/100以下であることが好ましい。

【0014】

本発明に係るアライメントマークにおいて、前記素子構成要素のパターンはドットパターンであることが好ましい。

【0015】

本発明に係るアライメントマークにおいて、前記素子構成要素は、シリコン領域、素子分離領域又は配線の少なくとも1つであることが好ましい。このようにすると、例えば多結晶シリコン、素子分離、配線等の加工により、アライメントマークを構成する段差を簡単に形成することができる。

【0016】

前記スクライブライン領域が、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有する場合、本発明に係るアライメントマークは、前記複数の第1のスクライブライン領域のうちの2つ以上の第1のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されているか、又は前記複数の第2のスクライブライン領域のうちの2つ以上の第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されていることが好ましい。また、この場合、本発明に係るアライメントマークは、スクライブライン領域の幅全体に亘って配置されていることが特に好ましい。このようにすると、等倍から5倍程度までの低倍率でアライメントを実施する際に、検査・測定設備における画像を記憶させる認識領域(視野領域)に対してアライメントマークの大きさを十分に確保することができる。従って、縦方向(例えば前述の第1の方向)又は横方向(例えば前述の第2の方向)にずらした2つの露光ショットを用いてアライメントを実施する際に、アライメントマークが検査・測定設備の認識領域から外れてしまうという認識不良を防止できるので、アライメントを正確に実施することができる。

【0017】

本発明に係るウェハは、以上に述べた本発明に係るアライメントマークが転写されている。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0018】

本発明に係る第1のアライメント方法は、以上に述べた本発明に係るアライメントマークを2回の露光ショットによってウェハ上の異なる2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行う。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0019】

また、本発明に係る第2のアライメント方法も本発明に係るアライメントマークを用いたアライメント方法であって、レチクルのスクライブライン領域は、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有しており、アライメントマークは、前記複数の第1のスクライブライン領域のうちの2つ以上の第1のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されており、当該アライメントマークを2回の露光ショットによって、ウェハ上における前記第1の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行う。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0020】

また、本発明に係る第3のアライメント方法も本発明に係るアライメントマークを用いたアライメント方法であって、レチクルのスクライブライン領域は、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有しており、アライメントマークは、前記複数の第2のスクライブライン領域のうちの2つ以上の第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されており、当該アライメントマークを2回の露光ショットによって、ウェハ上における前記第2の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行う。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0021】

尚、本発明に係る第1〜第3のアライメント方法において、前記2回の露光ショットの縮小倍率が1倍以上で且つ5倍以下であると、従来と比べて、前述の効果がより顕著に発揮される。

【発明の効果】

【0022】

以上に説明したように、本発明によると、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを行う際にも、検査・測定装置が誤認識を生じたり、認識不能となるおそれがないので、アライメントを確実且つ容易に行うことができる。

【発明を実施するための最良の形態】

【0023】

(実施形態)

以下、本発明の一実施形態に係るアライメントマーク、具体的には、ウェハに対するパターン転写に用いられる露光用レチクル上のアライメントマークについて、図面を参照しながら説明する。

【0024】

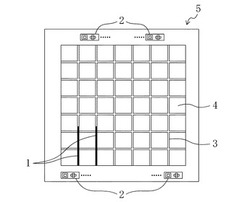

図1は、本実施形態のアライメントマークが設けられた露光用レチクルの平面図である。図1に示すように、露光用レチクル5は、格子状に配置されたスクライブライン領域3と、スクライブライン領域3により区画された複数のチップ領域4とを有している。また、露光用レチクル5の周縁部には重ね合わせマーク2(基準となるレイヤとの重ね合わせずれを測定するためのマーク)が設けられている。

【0025】

本実施形態の特徴として、アライメントマーク1は、レチクル5のスクライブライン領域3に、例えば素子分離領域や配線等の素子構成要素のパターンを密集して配置することにより構成されている。ここで、素子分離領域のパターンとは、例えばバイポーラトランジスタの素子分離のドットパターンであり、配線のパターンとは、例えばタングステンプラグやアルミニウム電極等のドットパターンであり、これらのドットパターンを繰り返し並べて形成することにより、アライメントマーク1が構成されている。

【0026】

尚、各素子構成要素のパターンのサイズは、チップサイズ(チップ領域4のサイズ)の1/100程度以下である。また、素子構成要素のパターンとしては、素子分離領域や配線層の他に、シリコン領域等を用いることができる。

【0027】

以下、図1に示す本実施形態のアライメントマーク(露光用レチクル上のアライメントマーク)1を半導体ウェハに転写していく方法、つまり、本実施形態の半導体ウェハの製造方法について説明する。

【0028】

図2〜図4は本実施形態の半導体ウェハの製造方法の各工程を示す断面図である。尚、以下の説明においては、一般的な技術として使用されているMOS(metal oxide semiconductor )トランジスタのゲート電極形成工程、配線形成工程中において層間絶縁膜を平坦化するCMP(化学的機械的研磨)工程等は省略している。

【0029】

まず、図2に示すように、例えば比抵抗が10〜15Ω・cm程度のP型の半導体基板(シリコンウェハ)8の(100)面上に、本実施形態のアライメントマーク(スクライブライン領域に素子分離領域のパターンを密集して配置することにより構成されたアライメントマーク)が設けられた露光用レチクルを用いて、例えば厚さ約400nm程度のフィールド酸化膜9を形成する。これにより、半導体基板8の表面はトランジスタ領域6とトランジスタ接合分離領域7とに区画される。その後、選択的イオン注入を順次実施することにより、トランジスタ領域6にコレクタ領域10、ベース領域11及びエミッタ領域12を形成すると共に、トランジスタ接合分離領域7に接合分離領域13を形成する。次に、例えば800〜900℃程度で60分程度の熱処理を実施することにより、各不純物拡散領域の注入不純物の活性化を行う。

【0030】

その後、図3に示すように、半導体基板8の表面を覆うように、例えば厚さ1000〜1500nm程度のBPSG(boron-doped phospho-silicate glass)膜14Aを層間絶縁膜として形成する。次に、本実施形態のアライメントマーク(スクライブライン領域にホールパターンを密集して配置することにより構成されたアライメントマーク)が設けられた露光用レチクルを用いたフォトリソグラフィ及びドライエッチングにより、BPSG膜14Aに半導体基板8に到達する複数のホールを形成した後、当該各ホール中にタングステンを埋め込むことにより、プラグ15Aを形成する。その後、プラグ15A上を含むBPSG膜14A上にアルミニウム膜をスパッタリング形成した後、本実施形態のアライメントマーク(スクライブライン領域に電極パターンを密集して配置することにより構成されたアライメントマーク)が設けられた露光用レチクルを用いたフォトリソグラフィ及びドライエッチングにより、前記アルミニウム膜をパターニングして、プラグ15Aと接続するアルミニウム電極16Aを形成する。

【0031】

その後、図4に示すように、図3に示す工程と同様の工程を繰り返し実施する。具体的には、BPSG膜14A及びアルミニウム電極16Aの上にBPSG膜14Bを形成した後、BPSG膜14B中にプラグ15Bを形成し、その後、BPSG膜14B上に、プラグ15Bと接続するアルミニウム電極16Bを形成した後、BPSG膜14B及びアルミニウム電極16Bの上にBPSG膜14Cを形成し、その後、BPSG膜14C中にプラグ15Cを形成した後、BPSG膜14C上に、プラグ15Cと接続するアルミニウム電極16Cを形成する。

【0032】

図5は、本実施形態のアライメントマーク1(スクライブライン領域に素子分離領域のパターンを密集して配置することにより構成されたアライメントマーク)が半導体基板8(シリコンウェハ)に転写された様子を示す平面図である。図5に示すように、転写されたアライメントマーク1の幅及び長さはそれぞれ50μm程度及び10mm程度である。また、図5に示すアライメントマーク1内においては、例えば幅(横方向寸法)及び長さ(縦方向寸法)が4μm程度の複数のトランジスタ領域6が2μm程度の間隔(つまりトランジスタ接合分離領域7の寸法)で規則的に配列されている。図5に示す場合、素子分離領域(フィールド酸化膜9)とトランジスタ領域6とによって、アライメントマーク1となるドットパターンが構成される。

【0033】

図6は、本実施形態のアライメントマーク1(スクライブライン領域に素子分離領域のホールパターン又は電極パターンを密集して配置することにより構成されたアライメントマーク)が半導体基板8(シリコンウェハ)に転写された様子を示す平面図である。図6に示すように、転写されたアライメントマーク1の幅及び長さはそれぞれ50μm程度及び10mm程度である。また、図6に示すアライメントマーク1内においては、直径0.4μm程度のプラグ15A〜15C又は同程度の寸法のアルミニウム電極16A〜16Cが0.4μm程度の間隔で規則的に配列されている。尚、プラグ15A〜15C及びアルミニウム電極16A〜16Cは、下層のトランジスタの配列とは無関係に同一間隔で配列されている。また、図6に示す場合、実際には、プラグ15A〜15Cが埋め込まれる前のホールが規則的に配列された状態が、アライメントマーク1となるドットパターンを構成している。

【0034】

以下、図1に示す本実施形態のアライメントマーク(露光用レチクル上のアライメントマーク)1を使用したアライメント方法、つまり、本実施形態のアライメント方法について説明する。

【0035】

図7は、本実施形態のアライメント方法を説明するための図である。また、図8は、本実施形態のアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。尚、図8において、図1に示す構成要素と同一の構成要素には同一の符号を付し、重複する説明を省略する。

【0036】

図7に示すように、ウェハ19に対して複数の露光ショット20が設定されている。また、図8に示すように、スクライブライン領域3は、第1の方向(図8の縦方向)に沿って延びる複数の第1のスクライブライン領域と、第1の方向に対して垂直な第2の方向(図8の横方向)に沿って延びる複数の第2のスクライブライン領域とを含んでいる。また、図8に示すように、アライメントマーク1は、複数の第1のスクライブライン領域のうち隣り合う2つの第1のスクライブライン領域に同じ10mm程度の長さで配置されている。尚、アライメントマーク1は、第1のスクライブライン領域の幅全体に亘って配置されている。すなわち、アライメントマーク1の幅は50μm程度である。

【0037】

本実施形態のアライメント方法においては、まず、ウェハ19の周縁部に対する露光ショット21において、検査・測定設備の認識領域(視野領域)18を、隣り合う2つの第1のスクライブライン領域上に(つまり縦方向に)配置されている長さ10mm程度、幅50μm程度の2つのアライメントマーク1の少なくとも一部分が当該認識領域18に含まれるように設定し、当該アライメントマーク1及びその周辺部の画像を記憶させる。

【0038】

次に、ウェハ19の中心部に対する露光ショット22においても同様の処理を行った後、露光ショット21及び22のそれぞれと対応する画像の比較結果を用いてウェハ19のアライメントを行う。尚、本実施形態においては、図7に示すように、露光ショット21と露光ショット22とは第1の方向(縦方向)に沿って並んでいる。すなわち、露光ショットを縦方向にスキャンさせている。

【0039】

本実施形態のアライメント方法によると、アライメントマーク1は、スクライブライン領域3に、素子構成要素のパターンを密集して配置することにより構成されているため、チップサイズが1mm2 以下となって露光領域(1つの露光ショット)内に占めるスクライブライン領域3の割合が大きくなったとしても、ウェハ19の画像全体が黒く見えることを防止することができる。従って、アライメントマーク1とその周囲環境との間において十分なコントラストを確保できるため、検査・測定設備がアライメントマーク1をユニークマークとして容易に認識することができるので、アライメントマーク認識不良を防止してウェハ19のアライメントを正確に実施することができる。

【0040】

すなわち、本実施形態によると、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを行う際にも、検査・測定装置が誤認識を生じたり、認識不能となるおそれがないので、アライメントを確実且つ容易に行うことができる。また、このような効果は、アライメントにおける露光ショットの縮小倍率が1倍以上で且つ5倍以下であると、従来と比べて、より顕著に発揮される。

【0041】

また、本実施形態によると、アライメントマーク1は、半導体製造プロセスにおいてウェハ上の最下層である素子分離の形成工程から上層である配線の形成工程までの各工程で形成可能であるため、ほぼ全ての製造工程での検査・測定において前述の効果を得ることができる。さらに、多結晶シリコン、素子分離、配線等の加工により、アライメントマーク1を構成する段差を簡単に形成することができる。

【0042】

尚、本実施形態において、アライメントマーク1を、隣り合う2つのスクライブライン領域3に配置したが、アライメントマーク1を、3つ以上のスクライブライン領域3に配置してもよい。また、各スクライブライン領域3に配置するアライメントマーク1の長さを10mm程度に設定したが、アライメントマーク1の長さについては5mm以上で且つ15mm以下の長さに設定することが好ましい。このようにすると、等倍から5倍程度までの低倍率でアライメントを実施する際に、検査・測定設備における画像を記憶させる認識領域(視野領域)18に対してアライメントマーク1の大きさを十分に確保することができる。従って、第1の方向(縦方向)にずらした2つの露光ショットを用いてアライメントを実施する際に、アライメントマーク1が検査・測定設備の認識領域18から外れてしまうという認識不良を防止できるので、アライメントを正確に実施することができる。尚、アライメントマーク1の長さについては、検査・測定設備の認識領域18の大きさや、スクライブライン領域3に他のアクセサリパターンが配置されること等を考慮した場合にも、5mm以上で且つ15mm以下の長さに設定することが好ましい。

【0043】

図9は、比較例に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(比較例に係るアライメントマークを含む)を示す平面図である。尚、図9において、図1に示す構成要素と同一の構成要素には同一の符号を付し、重複する説明を省略する。図9に示すように、比較例においては、本実施形態のアライメントマーク1に代えて、チップ領域4の隅部に、本実施形態のアライメントマーク1と比較して小さいアライメントマーク51が設けられている。その結果、アライメントを実施する際に、アライメントマーク51が検査・測定設備の認識領域52から外れてしまうという認識不良が生じやすいので、アライメントを正確に実施することができない。

【0044】

また、本実施形態において、アライメントマーク1を、第1の方向(縦方向)に沿って延びるスクライブライン領域3(第1のスクライブライン領域)に配置する場合について、説明したが、これに代えて、アライメントマーク1を、第2の方向(横方向)に沿って延びるスクライブライン領域3(第2のスクライブライン領域)に配置してもよい。以下、その場合(変形例)について詳述する。

【0045】

図10は、変形例のアライメント方法を説明するための図である。また、図11は、変形例のアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。尚、図11において、図1に示す構成要素と同一の構成要素には同一の符号を付し、重複する説明を省略する。

【0046】

図10に示すように、ウェハ19に対して複数の露光ショット20が設定されている。また、図11に示すように、スクライブライン領域3は、第1の方向(図11の縦方向)に沿って延びる複数の第1のスクライブライン領域と、第1の方向に対して垂直な第2の方向(図11の横方向)に沿って延びる複数の第2のスクライブライン領域とを含んでいる。また、図11に示すように、アライメントマーク1は、複数の第2のスクライブライン領域のうち隣り合う2つの第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されている。尚、アライメントマーク1は、第2のスクライブライン領域の幅全体に亘って配置されている。すなわち、アライメントマーク1の幅は50μm程度である。

【0047】

変形例のアライメント方法においては、まず、ウェハ19の周縁部に対する露光ショット21において、検査・測定設備の認識領域(視野領域)18を、隣り合う2つの第2のスクライブライン領域上に(つまり横方向に)配置されている長さ5mm〜15mm程度、幅50μm程度の2つのアライメントマーク1の少なくとも一部分が当該認識領域18に含まれるように設定して、当該アライメントマーク1及びその周辺部の画像を記憶させる。

【0048】

次に、ウェハ19の中心部に対する露光ショット22においても同様の処理を行った後、露光ショット21及び22のそれぞれと対応する画像の比較結果を用いてウェハ19のアライメントを行う。尚、変形例においては、図10に示すように、露光ショット21と露光ショット22とは第2の方向(横方向)に沿って並んでいる。すなわち、露光ショットを横方向にスキャンさせている。

【0049】

以上に述べた変形例のアライメント方法においても、本実施形態のアライメント方法と同様の効果が得られる。

【産業上の利用可能性】

【0050】

本発明は、半導体製造の検査・測定工程において使用するアライメントマーク及び当該アライメントマークを使用したアライメント方法に関し、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを確実且つ容易に行うことができるという効果が得られ、非常に有用である。

【図面の簡単な説明】

【0051】

【図1】本発明の一実施形態に係るアライメントマークが設けられた露光用レチクルの平面図である。

【図2】本発明の一実施形態に係るアライメントマークを半導体ウェハに転写していく方法の一工程を示す断面図である。

【図3】本発明の一実施形態に係るアライメントマークを半導体ウェハに転写していく方法の一工程を示す断面図である。

【図4】本発明の一実施形態に係るアライメントマークを半導体ウェハに転写していく方法の一工程を示す断面図である。

【図5】本発明の一実施形態に係るアライメントマークが半導体ウェハに転写された様子を示す平面図である。

【図6】本発明の一実施形態に係るアライメントマークが半導体ウェハに転写された様子を示す平面図である。

【図7】本発明の一実施形態に係るアライメント方法を説明するための図である。

【図8】本発明の一実施形態に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。

【図9】比較例に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(比較例に係るアライメントマークを含む)を示す平面図である。

【図10】本発明の一実施形態の変形例に係るアライメント方法を説明するための図である。

【図11】本発明の一実施形態の変形例に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。

【図12】特許文献1に開示された従来のアライメントマーク及びその周辺部の平面図である。

【図13】図12に示すアライメントマークが設けられたチップ領域の平面図である。

【符号の説明】

【0052】

1 アライメントマーク

2 重ね合わせマーク

3 スクライブライン領域

4 チップ領域

5 露光用レチクル

6 トランジスタ領域

7 トランジスタ接合分離領域

8 半導体基板

9 フィールド酸化膜

10 コレクタ領域

11 ベース領域

12 エミッタ領域

13 接合分離領域

14A、14B、14C BPSG膜

15A、15B、15C プラグ

16A、16B、16C アルミニウム電極

18 検査・測定設備の画像認識領域

19 ウェハ

20 露光ショット

21 アライメントを実施するための露光ショット(ウェハ周縁部)

22 アライメントを実施するための露光ショット(ウェハ中心部)

【技術分野】

【0001】

本発明は、半導体製造の検査・測定工程において使用するアライメントマーク及び当該アライメントマークを使用したアライメント方法に関する。

【背景技術】

【0002】

本願において、アライメントマーク(アライメント構造)という用語は、ウェハ上の絶対位置又は相対位置を識別するために用いられる任意の測定マークを意味する。具体的には、

(1)異なる層に設けられた2つのパターンの間のずれを比較するために露光装置又は重ね合わせターゲットにおけるステージにウェハをアライメントするためのマーク

(2)ライブラリ又は基準ウェハから得られる基準データと比較することによってウェハ上の絶対位置を測定するためのマーク(レジストレーションマーク)

(3)ウェハ上に配線や絶縁膜を所定の形状で形成する工程等の工程を終了する毎に配線の短絡や切断の有無又はパーティクルが付着しているか否か等の検査・解析を行う際の座標の原点を決定するためのマーク

等を総称して本願ではアライメントマークという。

【0003】

図12は特許文献1に開示されたアライメントマーク及びその周辺部の平面図であり、図13は、図12に示すアライメントマークが設けられたチップ領域の平面図である。

【0004】

図12に示すアライメントマーク101は、右上部を切り欠いた3/4円形状を有している。すなわち、アライメントマーク101は、右上部に直角部106を1つだけ有している。図13に示すように、アライメントマーク101は、スクライブライン105に囲まれており且つメモリセル104a〜104dが配置されているチップ能動領域107の隅部に形成されている。ここで、アライメントマーク101は、検査・解析工程を実施する前のエッチング工程においてエッチング除去される部材であるアルミニウムを用いて形成されている。また、図12に示すように、アライメントマーク101の近傍にはアルミニウム配線102が配置されている。アルミニウム配線102の角部は、アライメントマーク101の直角部106と異なる角度にアルミニウム配線102を折り曲げることによって形成されている。このようにすると、アライメントマーク101の近傍に直角部106と同じ向きの直角を有するパターンが存在しないようにすることができる。すなわち、検査・解析装置の位置決め機構の視野領域110においてアライメントマーク101を認識したときに、視野領域110内にアライメントマーク101の直角部106以外の他の直角部を有するパターンが存在しないようにすることができる。これにより、視野領域110内に形成されている十字状位置合わせマーク115の直角部をアライメントマーク101の直角部106に確実に合わせることができるため、アライメントを行う際に検査・解析装置が誤認識や認識不能を生じるおそれがなくなるので、アライメントを確実に行うことができる。

【特許文献1】特開2000−138146号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に開示されたアライメントマーク等の従来のアライメントマークによると、RF−IC(integrated circuit)やディスクリートIC等のようにチップサイズが1mm2 以下の小さい製品を製造する際にアライメントマーク認識不良が発生している。

【0006】

前記に鑑み、本発明は、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを容易且つ正確に行えるようにすることを目的としている。

【課題を解決するための手段】

【0007】

前記の目的を達成するために、従来のアライメントマークによって、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを正確に行うことができない原因を本願発明者が検討した結果、以下のような知見を得るに至った。

【0008】

検査・測定設備を用いた半導体ウェハのアライメントにおいて、CCD(Charge Coupled Device )カメラ等の撮像手段によってウェハの画像を電気信号に変換し、その画像信号に基づいてアライメントマークの位置情報を計測する方式が知られている。ここで、画像信号の分解能を向上させるためには、アライメントマークとその周囲との間のコントラストが要求される。また、前述の方式を用いたアライメントの実施手順としては、まず、アライメントマーク及びその周囲の画像を記憶させておき、次に、縦方向又は横方向にずらした2つの露光ショットによってアライメントマークを転写し、転写されたアライメントマークを認識させる。ところが、チップサイズが1mm2 以下の小チップ品種の場合、露光領域内に占めるスクライブライン領域の割合が大きくなるため、ウェハの画像全体が黒く見えるので、アライメントマークとその周囲とのコントラストが弱くなってしまう。すなわち、前述の特許文献1に開示されたアライメントマーク等の従来のアライメントマークによると、周囲環境に対するコントラストを十分に確保することができないため、検査・測定装置がアライメントマークを認識できないので、アライメント不良が発生してしまう。さらに、従来のアライメントマークによると、低倍率でのアライメントを実施する際(露光ショットによるアライメントマークの転写を小さい縮小倍率で実施する際)には、検査・測定設備の視野領域に対してアライメントマークが小さくなりすぎる結果、アライメントマーク認識不良が発生してしまうという問題が生じる。

【0009】

本発明は、前述の知見に基づくものであって、具体的には、本発明に係るアライメントマークは、ウェハに対するパターン転写に用いられるレチクルのスクライブライン領域に、素子構成要素のパターンを密集して配置することにより構成されている。

【0010】

尚、本発明において、「パターンが密集して配置された領域」とは、例えば複数の凹部が当該凹部の幅と同程度の間隔を置いて配置されている領域をいうものとする。ここで、凹部とは、素子分離を形成する場合にはフィールド酸化膜を形成しない箇所であり、多結晶シリコンや配線を形成する場合にはそれらがエッチングされている箇所である。

【0011】

本発明に係るアライメントマークによると、当該アライメントマークが転写された半導体ウェハにおいて検査・測定設備によりアライメントを実施するために、まず、アライメントマーク及びその周囲環境の画像を記憶させ、次に、縦方向又は横方向にずらした2つの露光ショットによってアライメントマークを認識させた場合に、次のような効果が得られる。すなわち、本発明に係るアライメントマークは、レチクルのスクライブライン領域に、素子構成要素のパターンを密集して配置することにより構成されているため、チップサイズが1mm2 以下となって露光領域内に占めるスクライブライン領域の割合が大きくなったとしても、ウェハの画像全体が黒く見えることを防止することができる。従って、アライメントマークとその周囲環境との間のコントラストについて、検査・測定設備で一般的に必要とされるレベルを確保できるため、アライメントマークを容易に認識することができるので、アライメントマーク認識不良を防止してウェハのアライメントを正確に実施することができる。

【0012】

また、本発明に係るアライメントマークは、半導体製造プロセスにおいてウェハ上の最下層である素子分離の形成工程から上層である配線の形成工程までの各工程で形成可能であるため、ほぼ全ての製造工程での検査・測定において前述の効果を得ることができる。

【0013】

本発明に係るアライメントマークにおいて、前記素子構成要素のパターンのサイズは、チップサイズの1/100以下であることが好ましい。

【0014】

本発明に係るアライメントマークにおいて、前記素子構成要素のパターンはドットパターンであることが好ましい。

【0015】

本発明に係るアライメントマークにおいて、前記素子構成要素は、シリコン領域、素子分離領域又は配線の少なくとも1つであることが好ましい。このようにすると、例えば多結晶シリコン、素子分離、配線等の加工により、アライメントマークを構成する段差を簡単に形成することができる。

【0016】

前記スクライブライン領域が、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有する場合、本発明に係るアライメントマークは、前記複数の第1のスクライブライン領域のうちの2つ以上の第1のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されているか、又は前記複数の第2のスクライブライン領域のうちの2つ以上の第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されていることが好ましい。また、この場合、本発明に係るアライメントマークは、スクライブライン領域の幅全体に亘って配置されていることが特に好ましい。このようにすると、等倍から5倍程度までの低倍率でアライメントを実施する際に、検査・測定設備における画像を記憶させる認識領域(視野領域)に対してアライメントマークの大きさを十分に確保することができる。従って、縦方向(例えば前述の第1の方向)又は横方向(例えば前述の第2の方向)にずらした2つの露光ショットを用いてアライメントを実施する際に、アライメントマークが検査・測定設備の認識領域から外れてしまうという認識不良を防止できるので、アライメントを正確に実施することができる。

【0017】

本発明に係るウェハは、以上に述べた本発明に係るアライメントマークが転写されている。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0018】

本発明に係る第1のアライメント方法は、以上に述べた本発明に係るアライメントマークを2回の露光ショットによってウェハ上の異なる2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行う。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0019】

また、本発明に係る第2のアライメント方法も本発明に係るアライメントマークを用いたアライメント方法であって、レチクルのスクライブライン領域は、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有しており、アライメントマークは、前記複数の第1のスクライブライン領域のうちの2つ以上の第1のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されており、当該アライメントマークを2回の露光ショットによって、ウェハ上における前記第1の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行う。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0020】

また、本発明に係る第3のアライメント方法も本発明に係るアライメントマークを用いたアライメント方法であって、レチクルのスクライブライン領域は、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有しており、アライメントマークは、前記複数の第2のスクライブライン領域のうちの2つ以上の第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されており、当該アライメントマークを2回の露光ショットによって、ウェハ上における前記第2の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行う。従って、本発明に係るアライメントマークと同様の効果を奏する。

【0021】

尚、本発明に係る第1〜第3のアライメント方法において、前記2回の露光ショットの縮小倍率が1倍以上で且つ5倍以下であると、従来と比べて、前述の効果がより顕著に発揮される。

【発明の効果】

【0022】

以上に説明したように、本発明によると、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを行う際にも、検査・測定装置が誤認識を生じたり、認識不能となるおそれがないので、アライメントを確実且つ容易に行うことができる。

【発明を実施するための最良の形態】

【0023】

(実施形態)

以下、本発明の一実施形態に係るアライメントマーク、具体的には、ウェハに対するパターン転写に用いられる露光用レチクル上のアライメントマークについて、図面を参照しながら説明する。

【0024】

図1は、本実施形態のアライメントマークが設けられた露光用レチクルの平面図である。図1に示すように、露光用レチクル5は、格子状に配置されたスクライブライン領域3と、スクライブライン領域3により区画された複数のチップ領域4とを有している。また、露光用レチクル5の周縁部には重ね合わせマーク2(基準となるレイヤとの重ね合わせずれを測定するためのマーク)が設けられている。

【0025】

本実施形態の特徴として、アライメントマーク1は、レチクル5のスクライブライン領域3に、例えば素子分離領域や配線等の素子構成要素のパターンを密集して配置することにより構成されている。ここで、素子分離領域のパターンとは、例えばバイポーラトランジスタの素子分離のドットパターンであり、配線のパターンとは、例えばタングステンプラグやアルミニウム電極等のドットパターンであり、これらのドットパターンを繰り返し並べて形成することにより、アライメントマーク1が構成されている。

【0026】

尚、各素子構成要素のパターンのサイズは、チップサイズ(チップ領域4のサイズ)の1/100程度以下である。また、素子構成要素のパターンとしては、素子分離領域や配線層の他に、シリコン領域等を用いることができる。

【0027】

以下、図1に示す本実施形態のアライメントマーク(露光用レチクル上のアライメントマーク)1を半導体ウェハに転写していく方法、つまり、本実施形態の半導体ウェハの製造方法について説明する。

【0028】

図2〜図4は本実施形態の半導体ウェハの製造方法の各工程を示す断面図である。尚、以下の説明においては、一般的な技術として使用されているMOS(metal oxide semiconductor )トランジスタのゲート電極形成工程、配線形成工程中において層間絶縁膜を平坦化するCMP(化学的機械的研磨)工程等は省略している。

【0029】

まず、図2に示すように、例えば比抵抗が10〜15Ω・cm程度のP型の半導体基板(シリコンウェハ)8の(100)面上に、本実施形態のアライメントマーク(スクライブライン領域に素子分離領域のパターンを密集して配置することにより構成されたアライメントマーク)が設けられた露光用レチクルを用いて、例えば厚さ約400nm程度のフィールド酸化膜9を形成する。これにより、半導体基板8の表面はトランジスタ領域6とトランジスタ接合分離領域7とに区画される。その後、選択的イオン注入を順次実施することにより、トランジスタ領域6にコレクタ領域10、ベース領域11及びエミッタ領域12を形成すると共に、トランジスタ接合分離領域7に接合分離領域13を形成する。次に、例えば800〜900℃程度で60分程度の熱処理を実施することにより、各不純物拡散領域の注入不純物の活性化を行う。

【0030】

その後、図3に示すように、半導体基板8の表面を覆うように、例えば厚さ1000〜1500nm程度のBPSG(boron-doped phospho-silicate glass)膜14Aを層間絶縁膜として形成する。次に、本実施形態のアライメントマーク(スクライブライン領域にホールパターンを密集して配置することにより構成されたアライメントマーク)が設けられた露光用レチクルを用いたフォトリソグラフィ及びドライエッチングにより、BPSG膜14Aに半導体基板8に到達する複数のホールを形成した後、当該各ホール中にタングステンを埋め込むことにより、プラグ15Aを形成する。その後、プラグ15A上を含むBPSG膜14A上にアルミニウム膜をスパッタリング形成した後、本実施形態のアライメントマーク(スクライブライン領域に電極パターンを密集して配置することにより構成されたアライメントマーク)が設けられた露光用レチクルを用いたフォトリソグラフィ及びドライエッチングにより、前記アルミニウム膜をパターニングして、プラグ15Aと接続するアルミニウム電極16Aを形成する。

【0031】

その後、図4に示すように、図3に示す工程と同様の工程を繰り返し実施する。具体的には、BPSG膜14A及びアルミニウム電極16Aの上にBPSG膜14Bを形成した後、BPSG膜14B中にプラグ15Bを形成し、その後、BPSG膜14B上に、プラグ15Bと接続するアルミニウム電極16Bを形成した後、BPSG膜14B及びアルミニウム電極16Bの上にBPSG膜14Cを形成し、その後、BPSG膜14C中にプラグ15Cを形成した後、BPSG膜14C上に、プラグ15Cと接続するアルミニウム電極16Cを形成する。

【0032】

図5は、本実施形態のアライメントマーク1(スクライブライン領域に素子分離領域のパターンを密集して配置することにより構成されたアライメントマーク)が半導体基板8(シリコンウェハ)に転写された様子を示す平面図である。図5に示すように、転写されたアライメントマーク1の幅及び長さはそれぞれ50μm程度及び10mm程度である。また、図5に示すアライメントマーク1内においては、例えば幅(横方向寸法)及び長さ(縦方向寸法)が4μm程度の複数のトランジスタ領域6が2μm程度の間隔(つまりトランジスタ接合分離領域7の寸法)で規則的に配列されている。図5に示す場合、素子分離領域(フィールド酸化膜9)とトランジスタ領域6とによって、アライメントマーク1となるドットパターンが構成される。

【0033】

図6は、本実施形態のアライメントマーク1(スクライブライン領域に素子分離領域のホールパターン又は電極パターンを密集して配置することにより構成されたアライメントマーク)が半導体基板8(シリコンウェハ)に転写された様子を示す平面図である。図6に示すように、転写されたアライメントマーク1の幅及び長さはそれぞれ50μm程度及び10mm程度である。また、図6に示すアライメントマーク1内においては、直径0.4μm程度のプラグ15A〜15C又は同程度の寸法のアルミニウム電極16A〜16Cが0.4μm程度の間隔で規則的に配列されている。尚、プラグ15A〜15C及びアルミニウム電極16A〜16Cは、下層のトランジスタの配列とは無関係に同一間隔で配列されている。また、図6に示す場合、実際には、プラグ15A〜15Cが埋め込まれる前のホールが規則的に配列された状態が、アライメントマーク1となるドットパターンを構成している。

【0034】

以下、図1に示す本実施形態のアライメントマーク(露光用レチクル上のアライメントマーク)1を使用したアライメント方法、つまり、本実施形態のアライメント方法について説明する。

【0035】

図7は、本実施形態のアライメント方法を説明するための図である。また、図8は、本実施形態のアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。尚、図8において、図1に示す構成要素と同一の構成要素には同一の符号を付し、重複する説明を省略する。

【0036】

図7に示すように、ウェハ19に対して複数の露光ショット20が設定されている。また、図8に示すように、スクライブライン領域3は、第1の方向(図8の縦方向)に沿って延びる複数の第1のスクライブライン領域と、第1の方向に対して垂直な第2の方向(図8の横方向)に沿って延びる複数の第2のスクライブライン領域とを含んでいる。また、図8に示すように、アライメントマーク1は、複数の第1のスクライブライン領域のうち隣り合う2つの第1のスクライブライン領域に同じ10mm程度の長さで配置されている。尚、アライメントマーク1は、第1のスクライブライン領域の幅全体に亘って配置されている。すなわち、アライメントマーク1の幅は50μm程度である。

【0037】

本実施形態のアライメント方法においては、まず、ウェハ19の周縁部に対する露光ショット21において、検査・測定設備の認識領域(視野領域)18を、隣り合う2つの第1のスクライブライン領域上に(つまり縦方向に)配置されている長さ10mm程度、幅50μm程度の2つのアライメントマーク1の少なくとも一部分が当該認識領域18に含まれるように設定し、当該アライメントマーク1及びその周辺部の画像を記憶させる。

【0038】

次に、ウェハ19の中心部に対する露光ショット22においても同様の処理を行った後、露光ショット21及び22のそれぞれと対応する画像の比較結果を用いてウェハ19のアライメントを行う。尚、本実施形態においては、図7に示すように、露光ショット21と露光ショット22とは第1の方向(縦方向)に沿って並んでいる。すなわち、露光ショットを縦方向にスキャンさせている。

【0039】

本実施形態のアライメント方法によると、アライメントマーク1は、スクライブライン領域3に、素子構成要素のパターンを密集して配置することにより構成されているため、チップサイズが1mm2 以下となって露光領域(1つの露光ショット)内に占めるスクライブライン領域3の割合が大きくなったとしても、ウェハ19の画像全体が黒く見えることを防止することができる。従って、アライメントマーク1とその周囲環境との間において十分なコントラストを確保できるため、検査・測定設備がアライメントマーク1をユニークマークとして容易に認識することができるので、アライメントマーク認識不良を防止してウェハ19のアライメントを正確に実施することができる。

【0040】

すなわち、本実施形態によると、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを行う際にも、検査・測定装置が誤認識を生じたり、認識不能となるおそれがないので、アライメントを確実且つ容易に行うことができる。また、このような効果は、アライメントにおける露光ショットの縮小倍率が1倍以上で且つ5倍以下であると、従来と比べて、より顕著に発揮される。

【0041】

また、本実施形態によると、アライメントマーク1は、半導体製造プロセスにおいてウェハ上の最下層である素子分離の形成工程から上層である配線の形成工程までの各工程で形成可能であるため、ほぼ全ての製造工程での検査・測定において前述の効果を得ることができる。さらに、多結晶シリコン、素子分離、配線等の加工により、アライメントマーク1を構成する段差を簡単に形成することができる。

【0042】

尚、本実施形態において、アライメントマーク1を、隣り合う2つのスクライブライン領域3に配置したが、アライメントマーク1を、3つ以上のスクライブライン領域3に配置してもよい。また、各スクライブライン領域3に配置するアライメントマーク1の長さを10mm程度に設定したが、アライメントマーク1の長さについては5mm以上で且つ15mm以下の長さに設定することが好ましい。このようにすると、等倍から5倍程度までの低倍率でアライメントを実施する際に、検査・測定設備における画像を記憶させる認識領域(視野領域)18に対してアライメントマーク1の大きさを十分に確保することができる。従って、第1の方向(縦方向)にずらした2つの露光ショットを用いてアライメントを実施する際に、アライメントマーク1が検査・測定設備の認識領域18から外れてしまうという認識不良を防止できるので、アライメントを正確に実施することができる。尚、アライメントマーク1の長さについては、検査・測定設備の認識領域18の大きさや、スクライブライン領域3に他のアクセサリパターンが配置されること等を考慮した場合にも、5mm以上で且つ15mm以下の長さに設定することが好ましい。

【0043】

図9は、比較例に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(比較例に係るアライメントマークを含む)を示す平面図である。尚、図9において、図1に示す構成要素と同一の構成要素には同一の符号を付し、重複する説明を省略する。図9に示すように、比較例においては、本実施形態のアライメントマーク1に代えて、チップ領域4の隅部に、本実施形態のアライメントマーク1と比較して小さいアライメントマーク51が設けられている。その結果、アライメントを実施する際に、アライメントマーク51が検査・測定設備の認識領域52から外れてしまうという認識不良が生じやすいので、アライメントを正確に実施することができない。

【0044】

また、本実施形態において、アライメントマーク1を、第1の方向(縦方向)に沿って延びるスクライブライン領域3(第1のスクライブライン領域)に配置する場合について、説明したが、これに代えて、アライメントマーク1を、第2の方向(横方向)に沿って延びるスクライブライン領域3(第2のスクライブライン領域)に配置してもよい。以下、その場合(変形例)について詳述する。

【0045】

図10は、変形例のアライメント方法を説明するための図である。また、図11は、変形例のアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。尚、図11において、図1に示す構成要素と同一の構成要素には同一の符号を付し、重複する説明を省略する。

【0046】

図10に示すように、ウェハ19に対して複数の露光ショット20が設定されている。また、図11に示すように、スクライブライン領域3は、第1の方向(図11の縦方向)に沿って延びる複数の第1のスクライブライン領域と、第1の方向に対して垂直な第2の方向(図11の横方向)に沿って延びる複数の第2のスクライブライン領域とを含んでいる。また、図11に示すように、アライメントマーク1は、複数の第2のスクライブライン領域のうち隣り合う2つの第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されている。尚、アライメントマーク1は、第2のスクライブライン領域の幅全体に亘って配置されている。すなわち、アライメントマーク1の幅は50μm程度である。

【0047】

変形例のアライメント方法においては、まず、ウェハ19の周縁部に対する露光ショット21において、検査・測定設備の認識領域(視野領域)18を、隣り合う2つの第2のスクライブライン領域上に(つまり横方向に)配置されている長さ5mm〜15mm程度、幅50μm程度の2つのアライメントマーク1の少なくとも一部分が当該認識領域18に含まれるように設定して、当該アライメントマーク1及びその周辺部の画像を記憶させる。

【0048】

次に、ウェハ19の中心部に対する露光ショット22においても同様の処理を行った後、露光ショット21及び22のそれぞれと対応する画像の比較結果を用いてウェハ19のアライメントを行う。尚、変形例においては、図10に示すように、露光ショット21と露光ショット22とは第2の方向(横方向)に沿って並んでいる。すなわち、露光ショットを横方向にスキャンさせている。

【0049】

以上に述べた変形例のアライメント方法においても、本実施形態のアライメント方法と同様の効果が得られる。

【産業上の利用可能性】

【0050】

本発明は、半導体製造の検査・測定工程において使用するアライメントマーク及び当該アライメントマークを使用したアライメント方法に関し、1mm2 以下の小さいチップが多数配置されたウェハのアライメントを確実且つ容易に行うことができるという効果が得られ、非常に有用である。

【図面の簡単な説明】

【0051】

【図1】本発明の一実施形態に係るアライメントマークが設けられた露光用レチクルの平面図である。

【図2】本発明の一実施形態に係るアライメントマークを半導体ウェハに転写していく方法の一工程を示す断面図である。

【図3】本発明の一実施形態に係るアライメントマークを半導体ウェハに転写していく方法の一工程を示す断面図である。

【図4】本発明の一実施形態に係るアライメントマークを半導体ウェハに転写していく方法の一工程を示す断面図である。

【図5】本発明の一実施形態に係るアライメントマークが半導体ウェハに転写された様子を示す平面図である。

【図6】本発明の一実施形態に係るアライメントマークが半導体ウェハに転写された様子を示す平面図である。

【図7】本発明の一実施形態に係るアライメント方法を説明するための図である。

【図8】本発明の一実施形態に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。

【図9】比較例に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(比較例に係るアライメントマークを含む)を示す平面図である。

【図10】本発明の一実施形態の変形例に係るアライメント方法を説明するための図である。

【図11】本発明の一実施形態の変形例に係るアライメント方法において露光ショットにより半導体ウェハに転写されたレチクルのパターン(アライメントマークを含む)を示す平面図である。

【図12】特許文献1に開示された従来のアライメントマーク及びその周辺部の平面図である。

【図13】図12に示すアライメントマークが設けられたチップ領域の平面図である。

【符号の説明】

【0052】

1 アライメントマーク

2 重ね合わせマーク

3 スクライブライン領域

4 チップ領域

5 露光用レチクル

6 トランジスタ領域

7 トランジスタ接合分離領域

8 半導体基板

9 フィールド酸化膜

10 コレクタ領域

11 ベース領域

12 エミッタ領域

13 接合分離領域

14A、14B、14C BPSG膜

15A、15B、15C プラグ

16A、16B、16C アルミニウム電極

18 検査・測定設備の画像認識領域

19 ウェハ

20 露光ショット

21 アライメントを実施するための露光ショット(ウェハ周縁部)

22 アライメントを実施するための露光ショット(ウェハ中心部)

【特許請求の範囲】

【請求項1】

ウェハに対するパターン転写に用いられるレチクルのスクライブライン領域に、素子構成要素のパターンを密集して配置することにより構成されていることを特徴とするアライメントマーク。

【請求項2】

請求項1に記載のアライメントマークにおいて、

前記素子構成要素のパターンのサイズは、チップサイズの1/100以下であることを特徴とするアライメントマーク。

【請求項3】

請求項1又は2に記載のアライメントマークにおいて、

前記素子構成要素のパターンはドットパターンであることを特徴とするアライメントマーク。

【請求項4】

請求項1〜3のいずれか1項に記載のアライメントマークにおいて、

前記素子構成要素は、シリコン領域、素子分離領域又は配線の少なくとも1つであることを特徴とするアライメントマーク。

【請求項5】

請求項1〜4のいずれか1項に記載のアライメントマークにおいて、

前記スクライブライン領域は、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有することを特徴とするアライメントマーク。

【請求項6】

請求項5に記載のアライメントマークにおいて、

前記複数の第1のスクライブライン領域のうちの2つ以上の第1のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されていることを特徴とするアライメントマーク。

【請求項7】

請求項5に記載のアライメントマークにおいて、

前記複数の第2のスクライブライン領域のうちの2つ以上の第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されていることを特徴とするアライメントマーク。

【請求項8】

請求項6又は7に記載のアライメントマークにおいて、

前記スクライブライン領域の幅全体に亘って配置されていることを特徴とするアライメントマーク。

【請求項9】

請求項1〜8のいずれか1項に記載のアライメントマークが転写されていることを特徴とするウェハ。

【請求項10】

請求項1〜8のいずれか1項に記載のアライメントマークを2回の露光ショットによってウェハ上の異なる2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行うことを特徴とするアライメント方法。

【請求項11】

請求項6に記載のアライメントマークを2回の露光ショットによって、ウェハ上における前記第1の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行うことを特徴とするアライメント方法。

【請求項12】

請求項7に記載のアライメントマークを2回の露光ショットによって、ウェハ上における前記第2の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行うことを特徴とするアライメント方法。

【請求項13】

請求項10〜12のいずれか1項に記載のアライメント方法において、

前記2回の露光ショットの縮小倍率は1倍以上で且つ5倍以下であることを特徴とするアライメント方法。

【請求項1】

ウェハに対するパターン転写に用いられるレチクルのスクライブライン領域に、素子構成要素のパターンを密集して配置することにより構成されていることを特徴とするアライメントマーク。

【請求項2】

請求項1に記載のアライメントマークにおいて、

前記素子構成要素のパターンのサイズは、チップサイズの1/100以下であることを特徴とするアライメントマーク。

【請求項3】

請求項1又は2に記載のアライメントマークにおいて、

前記素子構成要素のパターンはドットパターンであることを特徴とするアライメントマーク。

【請求項4】

請求項1〜3のいずれか1項に記載のアライメントマークにおいて、

前記素子構成要素は、シリコン領域、素子分離領域又は配線の少なくとも1つであることを特徴とするアライメントマーク。

【請求項5】

請求項1〜4のいずれか1項に記載のアライメントマークにおいて、

前記スクライブライン領域は、第1の方向に沿って延びる複数の第1のスクライブライン領域と、前記第1の方向に対して垂直な第2の方向に沿って延びる複数の第2のスクライブライン領域とを有することを特徴とするアライメントマーク。

【請求項6】

請求項5に記載のアライメントマークにおいて、

前記複数の第1のスクライブライン領域のうちの2つ以上の第1のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されていることを特徴とするアライメントマーク。

【請求項7】

請求項5に記載のアライメントマークにおいて、

前記複数の第2のスクライブライン領域のうちの2つ以上の第2のスクライブライン領域に5mm以上で且つ15mm以下の同じ長さで配置されていることを特徴とするアライメントマーク。

【請求項8】

請求項6又は7に記載のアライメントマークにおいて、

前記スクライブライン領域の幅全体に亘って配置されていることを特徴とするアライメントマーク。

【請求項9】

請求項1〜8のいずれか1項に記載のアライメントマークが転写されていることを特徴とするウェハ。

【請求項10】

請求項1〜8のいずれか1項に記載のアライメントマークを2回の露光ショットによってウェハ上の異なる2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行うことを特徴とするアライメント方法。

【請求項11】

請求項6に記載のアライメントマークを2回の露光ショットによって、ウェハ上における前記第1の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行うことを特徴とするアライメント方法。

【請求項12】

請求項7に記載のアライメントマークを2回の露光ショットによって、ウェハ上における前記第2の方向に沿って並ぶ2箇所に転写した後、当該2箇所のそれぞれに転写されたアライメントマーク及びその周辺領域の画像を検査測定装置に記憶させ、当該各画像の比較結果を用いて前記ウェハのアライメントを行うことを特徴とするアライメント方法。

【請求項13】

請求項10〜12のいずれか1項に記載のアライメント方法において、

前記2回の露光ショットの縮小倍率は1倍以上で且つ5倍以下であることを特徴とするアライメント方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2009−251455(P2009−251455A)

【公開日】平成21年10月29日(2009.10.29)

【国際特許分類】

【出願番号】特願2008−101643(P2008−101643)

【出願日】平成20年4月9日(2008.4.9)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成21年10月29日(2009.10.29)

【国際特許分類】

【出願日】平成20年4月9日(2008.4.9)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]