イン−ストリームデータ暗号化/復号の機能を有するメモリシステム

【解決手段】

データストリーム中のデータが、何等かのコントローラの密接な関与なしで、回路によって暗号化処理される場合、メモリシステムの処理能力が改善される。データストリームが複数のソース中で選択されたデータソースおよび複数の行き先中で選択された行き先を持つように、データストリームが全くコントローラの関与なしで制御されることは好ましい。複数のページの処理と、複数のアルゴリズム中から1つ以上の暗号化アルゴリズムの選択がコントローラの関与なしで暗号化および/または復号することを可能にし、並びにコントローラの関与なしで複数の連続する段階でデータを暗号化処理することができるように、暗号化回路を設定できることは好ましい。複数のデータストリームからデータをインターリービング方式で暗号化処理するメモリシステムでは、セッションに割り込まれる時に、セキュリティコンフィギュレーション情報が失われることがあり、そのために、セッションの再開時に処理が継続不能になることがある。セキュリティコンフィギュレーション情報を保持するために、割り込み後に読み取りができるよう、割り込み前に、コントローラが前記セッションのセキュリティコンフィギュレーション情報を保存させることが好ましい。

データストリーム中のデータが、何等かのコントローラの密接な関与なしで、回路によって暗号化処理される場合、メモリシステムの処理能力が改善される。データストリームが複数のソース中で選択されたデータソースおよび複数の行き先中で選択された行き先を持つように、データストリームが全くコントローラの関与なしで制御されることは好ましい。複数のページの処理と、複数のアルゴリズム中から1つ以上の暗号化アルゴリズムの選択がコントローラの関与なしで暗号化および/または復号することを可能にし、並びにコントローラの関与なしで複数の連続する段階でデータを暗号化処理することができるように、暗号化回路を設定できることは好ましい。複数のデータストリームからデータをインターリービング方式で暗号化処理するメモリシステムでは、セッションに割り込まれる時に、セキュリティコンフィギュレーション情報が失われることがあり、そのために、セッションの再開時に処理が継続不能になることがある。セキュリティコンフィギュレーション情報を保持するために、割り込み後に読み取りができるよう、割り込み前に、コントローラが前記セッションのセキュリティコンフィギュレーション情報を保存させることが好ましい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般にメモリシステムに関し、特にイン−ストリームデータ暗号化/復号機能を有するメモリシステムに関する。

【背景技術】

【0002】

モバイル機器市場は、より多くのデータ交換を発生させることにより平均収入の増加を図るよう、コンテンツストレージを備える方向に進んでいる。これは、モバイル機器に保存されている時に、そのコンテンツが保護されていなければならないことを意味する。

【0003】

数年来、ポータブル記憶装置は商業用途に使用されていおり、データをコンピューティングデバイスから他のコンピューティングデバイスへ持ち運んだり、あるいはバックアップデータを保存するために用いられている。ポータブルハードディスクドライブ、ポータブルフラッシュメモリディスクおよびフラッシュメモリカードのようなもっと高機能なポータブル記憶装置は、ストレージ管理の制御用マイクロプロセッサを含んでいる。

【0004】

ポータブル記憶装置に保存されたコンテンツを保護するために、保存されているデータは通常、暗号化され、許可されたユーザだけがデータを復号することが許される。

【0005】

旧来の暗号化の機能を有するポータブル記憶装置では、ストレージ管理用のマイクロプロセッサも暗号化と復号の処理に深く関与している。そのようなシステムは、例えば米国特許6,457,126号に記載されている。この場合では、記憶装置の処理能力および機能はひどく影響を受ける可能性がある。従って、前記の問題を大幅に軽減するローカル記憶装置を提供することは望ましい。

【特許文献1】米国特許6,457,126号

【発明の開示】

【発明が解決しようとする課題】

【0006】

この発明の一側面は、データストリーム中のデータが不揮発性メモリセルに送信され、又は該不揮発性メモリセルから取出しされる時に、あらゆるコントローラあるいはマイクロプロセッサとも密接な関与せず、データストリーム中のデータを回路によって暗号化処理する場合に、メモリシステムの処理能力が改善できる認識に基づくものである。ある実施例では、前記コントローラは暗号化処理に使用されるパラメーターを規定することだけに関与し、処理には関与しない。この実施例の実行では、パラメーターは、コンフィギュレーションレジスタによって設定される。

【0007】

好ましくは、メモリセルはフラッシュメモリセルを有する。さらに、メモリセル、データ暗号化および/または復号に使用する回路、セルおよび回路を制御するコントローラは、メモリカードかメモリスティックのような物体の中に取付けされ、密閉されることが好ましい。

【0008】

データは、ページで前記メモリセルに書き込まれ、またはそれから読出されることができる。暗号化および復号に使用される従来の暗号化アルゴリズムの多くは、通常、ページより小さなデータの単位で作動する。したがって、本発明の他の側面は、前記暗号化回路が、読取りまたは書き込み中の前記データストリーム中の1ページ以上のデータを暗号化処理することと、すべて前記コントローラの関与なしで、前記データストリームが複数のソース中で選択されたデータソースと複数の行き先(destination)中で選択された行き先を持つように、制御される認識に基づくものである。

【0009】

発明の他の側面によれば、前記暗号化回路は、コントローラあるいはマイクロプロセッサの関与なしで、暗号化および/または復号に対する複数のアルゴリズム中で1つ以上の暗号化アルゴリズムの選択ができるように設定できる。設定後、前記コントローラの関与なしで、前記回路は、複数の連続する段階で前記データストリーム中のデータを暗号化処理するようにも、前記回路を設定できる。設定後前記コントローラの関与なしで、複数の連続する段階で、前記暗号化処理は二つ以上の鍵を使用し、二つ以上のタイプの暗号化処理を使用することができる。

【0010】

あるアプリケーションでは、前記メモリシステムは、二つ以上の前記データストリームを取り扱うことが望ましい。この場合では、異なったデータストリーム中のデータがインターリーブ方式で暗号化処理されるように、前記コントローラは前記メモリセルと前記回路を制御する。好ましくは、前記データストリームの処理がインタリービングの間に割り込まれる場合に、各データストリームの暗号化処理用の様々なパラメーターが保存されるので、該データストリームの処理が再開される時、暗号化処理を継続するようパラメーターが回復できる。この特徴の一実施例では、暗号化処理用の様々なパラメーターをセットするために、セキュリティコンフィギュレーションレコードを書き込み操作の最初に作成し、セッションの終了にこれらのパラメーターを保存する。その後、読み込み操作の開始時にこのレコードをメモリから取り戻し、操作の終了に廃棄する。他のデータストリームの処理をさせるために、前記データストリームが一時的に割り込まれる場合、そのようなレコードも保存され、元のデータストリームの処理が再開される時に取り戻される。

【0011】

本発明の上記の様相は、個々に、あるいはそれの任意の組み合せで使用できる。

【発明を実施するための最良の形態】

【0012】

図1のブロック図を用いて、本発明の様々な部分が実行できる実例的なメモリシステムを説明する。図1に示すように、メモリシステム10は、中央処理装置(CPU)12と、バッファ管理ユニット(BMU)14と、ホストインタフェースモジュール(HIM)16と、フラッシュインタフェースモジュール(FIM)18と、フラッシュメモリ20と、ペリフェラルアクセスモジュール(PAM)22を有する。メモリシステム10は、ホストインタフェースバス26およびポート26aを介してホスト装置24と通信する。NANDタイプでもよいフラッシュメモリ20はホスト装置24用のデータ記憶装置を提供する。また、CPU12用のソフトウェアコードはフラッシュメモリ20に保存されてもよい。FIM18は、フラッシュインタフェースバス28とポート28aを介してフラッシュメモリ20に接続される。HIM16は、例えばディジタルカメラと、パソコンと、PDA(Personal Digital Assistant)と、ディジタルメディアプレーヤーと、MP−3プレーヤーと携帯電話、あるいは他のディジタル装置等のホストシステムに接続するのに適する。ペリフェラルアクセスモジュール22は、CPU12との通信用の例えばFIMと、HIMとBMU等の適切なコントローラモジュールを選択する。一つの実施例において、点線に囲まれた枠内のシステム10の中のすべてのコンポーネントを、例えばメモリカードあるいはメモリスティック10’の単一のユニットに封入することができ、好ましくは、カードあるいはスティック中に密閉できる。

【0013】

バッファ管理ユニット14は、ホストダイレクトメモリアクセス(HDMA)32と、フラッシュダイレクトメモリアクセス(FDMA)コントローラ34と、アービタ36と、バッファランダムアクセスメモリ(BRAM)38と、暗号化エンジン40を有する。アービタ36は共有バスアービタであるので、いつでも、ただ一つのマスタあるいはイニシエータ(HDMA32、FDMA34あるいはCPU12でもよい)だけがアクティブ可能になり、スレーブまたはターゲットはBRAM 38である。アービタは、適切なイニシエータの要求をBRAM38に向ける。HDMA32とFDMA34は、HIM16、FIM18、およびBRAM38と、あるいはCPUランダムアクセスメモリ(CPU RAM)12aとの間に伝送されたデータに関与する。HDMA32およびFDMA34の作動は従来の通りで、ここに詳述する必要はない。BRAM38は、ホスト装置24、フラッシュメモリ20およびCPU RAM 12aの間で伝送されるデータを一時的に保持するものである。HDMA32とFDMA34は、HIM16/FIM18とBRAM38あるいはCPU RAM 12aとの間にデータ伝送し、セクター伝送完了を指示するものである。

【0014】

まず最初に、フラッシュメモリ20からのデータをホスト装置24によって読取る場合、メモリ20中の暗号化されたデータは、バス28、FIM18、FDMA34、暗号化されたデータを復号する暗号化エンジン(Crypto−Engine)40によってフェッチされ、BRAM38に保存される。その後、復号されたデータは、BRAM38からHDMA32、HIM16、バス26を介してホスト装置24へ送信される。メモリ20に保存されたデータが復号される鍵及び/またはアルゴリズムと異なる鍵及び/またはアルゴリズムによってホスト装置24に伝送されるデータを再暗号化するように、BRAM38からフェッチされたデータは、HDMA32に伝送される前に、暗号化エンジン(Crypto−Engine)40によって再暗号化できる。さらに代わりの実施例では、データが不正アクセスに対して脆弱となりがちな、BRAM38に復号されたデータを保存する上述の処理よりも、メモリ20からのデータが、BRAM38に伝送される前に復号されて、暗号化エンジン40によって再暗号化されるのが好ましい。その後、前述したように、BRAM38中の暗号化されたデータは、ホスト装置24へ伝送される。これで読取り処理の際のデータストリームを説明した。

【0015】

データがホスト装置24によってメモリ20に書き込まれる場合は、データストリームの方向が逆にされる。例えば、暗号化されていないデータをホスト装置を利用して、バス26、HIM16、HDMA32によって暗号化エンジン40へ伝送する場合、これらのデータは、BRAM38に保存される前にエンジン40によって暗号化されてもよい。その代わりに、暗号化されていないデータをBRAM38に保存してもよい。その後、このデータは、FDMA34に伝送される前に、メモリ20へ伝送される途中で暗号化される。書き込まれたデータが多段の暗号化処理を経過する場合、処理済みのデータをBRAM38に保存する前に、エンジン40が前記の処理を完了するのが好ましい。

【0016】

本発明の1つの側面は、ホスト装置24とメモリ20との間で伝送されるデータストリーム中のデータの前述した暗号化処理を、CPU12の関与が最小となるように実行できれば、装置10の処理能力とそれによる性能を非常に改善することができるという認識に基づいているものである。これは以下説明するように図1に示す。

【0017】

上記の処理では、二つの異なったデータソースおよび行き先があるデータストリームを説明した。読取り処理では、データソースはメモリ20であり、行き先はホスト装置24である。書き込み処理では、データソースはホスト装置24であり、行き先はメモリ20である。さらに、データソース(あるいは行き先)は、対応する行き先(あるいはデータソース)がメモリ20であるCPU12でもよい。さらに、他のオペレーションでは、バルク暗号化およびハッシュオペレーションに対して、データストリームはBMU14からCPU12まででもよい。ソースの中のデータと出力データの行き先及び適用されうる対応する暗号化処理の様々な組み合わせを下記の表に述べる。

【表1】

【0018】

上記の表に示したように、一つの追加されたオペレート可能なモードは、バイパスモードである。バイパスモードは、暗号化エンジン40が存在せずHDMAとFMDAがアービタ36を介して該バイパス路に沿ってBRAM38に直接接続されているように、バイパス路(図1に示せず)に沿って、データストリームに暗号処理せずに、FDMA34がCPU12あるいはBRAM38にアクセスすることができる。本発明の一実施例によれば、例えばデータソースとデータ行き先等のプロセッシング、例えば適用される(あるいは、バイパスモード)暗号化アルゴリズム等の暗号化パラメータは、図1の暗号化エンジン40の機能的ブロックのうち一部のブロック図である図2のコンフィギュレーションレジスタ102をセットすることで、複数のデータソースと、複数の行き先および複数のアルゴリズムからCPU12を用いてあらかじめ選択できる。

【0019】

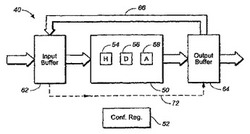

図2は暗号化エンジン40のブロック図で、その構成要素の一部をより詳細に示す。図2に示すように、暗号化エンジン40は、暗号化ブロック50とコンフィギュレーションレジスタ52とを有する。コンフィギュレーションレジスタ52は、選択されたデータソースと、選択されたデータ行き先、および使用される暗号化アルゴリズムあるいはバイパスモードとに関するセキュリティコンフィギュレーション情報あるいはセキュリティコンフィギュレーションレコードを、上記の表と使用すべき鍵(バイパスモードを除いて)に従い、データが暗号化か、復号か、あるいはハッシュされることになっているか(以上これらは「暗号化処理される」という表現に含まれる)、あるいは暗号化処理されないかどうかによって保存するものである。セキュリティコンフィギュレーション情報あるいはレコードは、CPU12によってレジスタ52に書き込まれてもよい。この情報をレジスタ52に保存した後、エンジン40は、CPU12の関与なしで暗号化処理を実施することができる。多くの通常の暗号化アルゴリズムは、データを、128ビットを1単位として処理する。これは、フラッシュメモリのような記憶装置に一度に書き込まれるかまたはそれから読み出されるデータのページのサイズより小さくすることができる。各ページは、通常1つ以上のセクターのデータを保存するが、該セクターのサイズは、ホストシステムによって規定されている。1例は磁気ディスクドライブで確立された規格によるユーザデータの512バイトのセクターで、ユーザデータおよび/またはそれが保存されているブロックに関するオーバーヘッド情報の若干のバイトがプラスされる。

【0020】

CPU12がエンジン40による暗号化処理に関与する必要がないように、また、データの全ページがエンジン40によって一度に1ページより小さな単位で暗号化処理されるように、ロジック回路(図示されていない)をブロック40で使用することができる。一実施例では、暗号化エンジン40はハードウェア回路である。

【0021】

図2に示すように、ブロック54、56および58は、暗号化ブロック50によって実施されるようCPUが選択できる三つの異なる暗号化アルゴリズム(それぞれHash、DES及びAES)を表わす。これらのアルゴリズムと異なる暗号化アルゴリズムも使用できるし、又、本発明の範囲内にある。暗号化ブロック50で処理されるデータと、ホスト装置24あるいはメモリ20、或いはCPU12から発生するデータは、先ず入力バッファ62に保存されて、レジスタ52で特定された暗号化アルゴリズムにより暗号化ブロック50で暗号化処理される。そして、暗号化処理されたデータは、レジスタ52中の行き先情報により、行き先へ伝送される前に、出力バッファ64に保存される。図2はさらに、メモリ20に書き込まされ、又、それから読み出されるデータを暗号化処理しない、入力バッファ62から出力バッファ64までのバイパス路72を含み、これは表のモードのうち1つであり、上述した1つものである。

【0022】

コンフィギュレーションレジスタ52はさらに、暗号化処理中で使用される鍵を保存できる。一実施例では、この鍵は、CPU12(例えば、メモリ20等から)によって読出されて、暗号化ブロック50による暗号化又は復号の前にレジスタ52に保存される。上述した処理は、CPU12がレジスタ52に適切な情報を書き込んだ後、CPU12の関与なしでブロック40中で実施される。図2を簡単化するために、ブロック40中のアルゴリズム、データソースおよび行き先を選択するためにレジスタ52中の情報を使用し、唯一の鍵と選択されたアルゴリズムを暗号化処理に使用するロジック回路は省略されている。処理されたデータが出力バッファ64へ伝送される前に、入力バッファ62中のデータを処理するために、暗号化ブロック50を二度以上使用することが可能である。例えば、データソースからのデータを先ず復号し、データをバッファ64に伝送する前に、異なる鍵および/または異なるアルゴリズムを使用して、復号されたデータを暗号化するのが望ましい。データの暗号化または復号に加えて、データのインテグリティを保証する目的では、データの要約あるいはハッシュ値を得るようにハッシングアルゴリズムをデータに適用することは有用である。これらすべての状況では、復号するためにある鍵を使用した後、暗号化するために異なった鍵を使用するか、データを暗号化するか復号するかだけでなく、要約を得るように、暗号化ブロック50でデータを二度処理することが望ましい。言うまでもなく、データは更に、該データが復号され、ハッシングされ、暗号化される場合、暗号化ブロック50で二回以上処理できる。これらのオペレーションがシーケンシャル段階(多段処理)で連続的に発生する。言いかえれば、多段(即ち、2段階以上)の処理では、暗号化ブロック50でより多く処理するよう暗号化ブロック50によって既に出力バッファ64で処理されたデータを、フィードバックパス66を介して、入力バッファ62へ伝送することにより、データを二度以上、暗号化ブロック50を通して伝送してもよい。二段階以上を考慮する場合、データは追加処理のために、更に追加の回数でフィードバックすることができる。処理の各段階では、異なったアルゴリズムおよび/または鍵を使用してもよい。

【0023】

多段の処理が望まれる場合、CPU12が、データを暗号化処理する回数および多段の処理の各段階で使用される鍵および/またはアルゴリズムを指定するために、セキュリティコンフィギュレーション情報あるいはレコードをレジスタ52に入力するために使用されてもよい。この情報がレジスタ52に書き込まれた後、CPU12は多段の処理に全く関与する必要がなくなる。

【0024】

図1のメモリシステム10はフラッシュメモリを有しているが、このシステムは例えば磁気ディスク、光ディスクCDs等の他のタイプの不揮発性メモリ、他のすべてのタイプの書き換え可能な不揮発性メモリシステムをさらに含んでもよく、上述した様々な利点は、これらの選択できる実施例に同様に適用できる。選択できる実施例では、このメモリは更に、メモリシステムの残りのコンポーネントと共に、同じ物体(例えば、メモリカードやメモリステック等)に密閉することが好ましい。

【0025】

オペレーティングシステム10の読取り処理を図3のフローチャートに示す。CPU12は、ホスト装置24から読取りコマンドを受け取った後、読取り操作を始める(楕円150)。その後、CPU12は、レジスタ52に適切なセキュリティコンフィギュレーション情報あるいはレコードを書き込むことにより、暗号化エンジン40を設定し、さらに読取り操作用にBMU14を設定し、オペレーション用(ブロック152、154)にBRAM38中での例えばメモリスペースの割り付け等の他のパラメーターを設定する。CPU12はさらに、データが読まれるメモリ20中の区域を指定するなど、FIM18を設定する(ブロック156)。その後、暗号化処理を含む上記処理がCPU(エラー訂正を除いて)の関与なしで実行されるように、HDMAエンジン32およびFDMAエンジン34を開始する。ブロック158を参照して、CPUは、割り込みを受信すると、それがFIMの割り込みかどうかチェックする(菱形160)。CPUはFIM割り込みが受信された場合、割り込みがデータストリーム中に一つ以上のエラーがあることを示す割り込みであるかどうかをチェックする(162)。エラーがあることが示される場合、BRAM38中のエラーを修正する為に進み(ブロック164)、データが次に読まれるメモリ20中の区域を変更するよう、FIM18の設定に戻る(ブロック156)。FIM割り込みがデータストリーム中のエラーを示さなかった場合、FIMがオペレーションを完了し、又CPUがFIMの再設定のためにブロック156に戻ることを表す。CPUに検知された割り込みがFIM割り込みでない場合、CPUはデータ割り込みの終了かどうかをチェックする(菱形166)。そうであれば、読取り操作は終了する(楕円168)。そうでなければ、この割り込みは、データの暗号化処理と無関係であり(即ち、クロック割り込み)、又、CPUは当該割り込みを処理し(図示されていない)、割り込みをチェックするために菱形160に戻る。

【0026】

書き込み操作には図3をわずか修正するだけでよい。メモリ20に書き込むデータにECCエラーの取り扱いがないので、書き込み操作でCPU12は菱形162及びブロック164中の処理を省くことができる。CPU12が、書き込み操作中にFIM割り込みを受信する場合、これは、FIMがそのオペレーションの完了したことを表し、CPUもFIMを再設定するためにブロック156に戻る。この違いを除けば、書き込み操作は実質的に読取り操作に似ている。したがって、暗号化エンジン40、BMU14およびFIM18を一度設定すると、システム10は、CPU12の関与なしで、たとえ暗号化エンジン40がページよりはるかに小さな単位でデータを処理することがあっても、データをすべて暗号化処理し(バイパス・モード以外)、そのセッションのページのすべての書き込みあるいは読取りを完了することができる。

【0027】

《インターリービングデータストリーム》

複数のホストアプリケーションが、複数のデータストリームを処理しながら同時に、メモリ20にアクセスできることが望ましい。これが意味することは、あるデータストリームの暗号化処理は、メモリシステム10が他のデータストリームを処理するために、割込んだ際に、完了していなかったかもしれないことである。異なったデータストリームの暗号化処理は、通常異なったパラメーター(例えば、異なった鍵とアルゴリズム、および異なったデータソースと行き先)を用いる。これらのパラメーターは、データストリームの対応するセキュリティコンフィギュレーションレコードに備えられている。特定のデータストリームの割り込まれた処理がその後再開される場合に、その対応するセキュリティコンフィギュレーションレコードが失われないことを保証するために、そのレコードは、CPU RAM 12aに保存するのが好ましい。前に割り込まれたデータストリームの処理を再開する場合、CPU12は、そのデータストリーム用の保存されたセキュリティコンフィギュレーション記録を読み出し、保存されている対応するセキュリティコンフィギュレーションレコードに基づいて、正確なパラメーターを用いて、そのデータストリームの再開された暗号化処理を行うことができる。

【0028】

図4は、複数のデータストリームの処理およびセキュリティコンフィギュレーションレコードの利用の図1および図2のシステムの操作を説明するフローチャートである。CPUは、ホストコマンドが受信されたかをチェックする(ブロック202と菱形204)。ホストコマンドが受信されていた時、例えば最初のデータストリームを暗号化処理する場合、CPUは、コマンドが装置24で実行する最初のアプリケーション等のスタートセッションコマンドかどうかについてチェックする(菱形206)。そうである場合、CPUは書き込みセッションが要求されたかどうかチェックする(菱形208)。若し書き込みセッションが要求されていた場合、CPUはホスト装置からの情報によってセキュリティコンフィギュレーションレコード(例えば選択されたデータソース、選択されたデータ行き先、上記の表テーブルと使用されるべき鍵によって用いられる暗号化アルゴリズム、および、データが暗号化、復号又はハッシュされるべきかどうか)を作成し(ブロック210)、第1データストリーム用の最初のセッションを始める。CPU12は、これらのセキュリティコンフィギュレーション情報あるいはレコードをCPU RAM 12aに保存する。もし要求されたセッションが読取りセッションである場合、CPUは、読み出されるデータ用のセキュリティコンフィギュレーションレコードをメモリ20から読取り(ブロック240)、それをCPU RAM 12aに保存する。その後、CPUは戻り、さらなるホストコマンドを待つ(202)。

【0029】

CPUは、別のホストコマンドを受信すると、スタートセッションコマンドであるかを再びチェックする(菱形206)。そうである場合、ブロック210あるいはブロック240に進み、第2のセッションを始めることができる。これは、第2のデータストリームの暗号化処理を要求するホスト装置24上で作動する、異なった第2のアプリケーション用の新しい第2のセッション等である。上記の第2のデータストリーム用のセキュリティコンフィギュレーション情報あるいはレコードは、CPU RAM 12aに再び保存されるが、これは書き込みと読取りの両セッションがある場合である(ブロック210、240)。追加のセッションは同じ方法で追加のデータストリームのために作成できる。CPUはブロック202に戻り、ホストコマンドがスタートセッションコマンドであるかを確かめるために次のホストコマンドをチェックする(菱形206)。このようにして、CPU12が菱形206中のスタートセッションコマンドでないホストコマンドを検知するまで、前述したように追加セッションが作成される。

【0030】

この場合には、CPU12は、ホストコマンドがセッション終了のコマンドであるかを確かめるべく次のホストコマンドをチェックする(菱形222)。そうでない場合、CPUは、それがデータコマンドであるかをチェックする(菱形224)。それがデータコマンドであると仮定すれば、CPUは、どのデータストリームを処理するかを判断し、前記のデータストリームのセキュリティコンフィギュレーションレコードにより暗号化エンジン40を設定し(レジスタ52に書き込むことで)、暗号化エンジン40は、例えば図3の処理などにより、上述した方式で読取りあるいは書き込み操作を実行する(或いは暗号化エンジン40はバイパスモードでバイパスされる)(ブロック226)。

【0031】

読取りあるいは書き込み処理に割り込みがない場合、セッションの間に処理されるすべてのページが処理されたことを表すセッション終了コマンドをCPUが受信するまでに、処理は継続する(ブロック222)。しかしながら、割り込みがある場合、CPUは、システム10が現在処理しているデータストリームとは異なるデータストリームからのデータを処理するホストデータコマンドを受信する。この場合、暗号化エンジン40は、前記の異なるデータストリームを処理するよう再設定される必要がある。その後、CPUは、CPU RAM 12aから前記の異なるデータストリーム用のセキュリティコンフィギュレーションレコードを読み出し、そして、暗号化エンジン40を再設定し(レジスタ52に読み出されたレコードを書き込むことによって)、その結果、エンジン40が前記の異なったデータストリームを正確に処理する。

【0032】

セッション終了コマンドが書き込みセッションで受け取られた場合(222ブロック)、CPUは、書き込まれたデータと共にセキュリティコンフィギュレーションレコードをメモリ20に保存し、前記のレコードは、それに続く読取り操作で読み出され得る(菱形228およびブロック230)。読取り操作では、RAM12aに保存されたセキュリティコンフィギュレーションレコードが廃棄されるが、メモリ20に保存されたレコードは、将来起こり得る読取り操作のために保持される(ブロック242)。

【0033】

あるアプリケーションにおいては、無許可な操作(tampering)に対してメモリ20中のデータのインテグリティを維持することは重要であろう。メモリ20に保存されているデータが変更、あるいは、破損されないことを保証するために、前記のデータのハッシュ値またはダイジェストを前記のデータから導出することが望ましく、前記のデータのハッシュ値またはダイジェストは前記のデータと共に保存されている。データを読み出されると、ハッシュ値またはダイジェストも同様に読み出され、読み出されたダイジェストあるいはハッシュ値は、前記の読み出されたデータから計算されたダイジェストあるいはハッシュ値と比較され得る。もし、それらの間に差異があれば、メモリ20のデータが変更されたか、破損されたのかもしない。

【0034】

共通のハッシュ関数は連鎖ブロック暗号(chained block cipher)(CBC)であって、メッセージ認証コード(MAC)は、書き込み中または読取り中のデータのブロックから時間系列に従って導き出される。共通のCBC関数は以下に通り。

【0035】

上記の値c0,・・・,crは、データストリームp1,・・・,prのメッセージ認証コード(MAC)である。IVはイニシエーション(開始)ベクトルであり、kは鍵である。したがって、データp1,・・・,prブロックをメモリ20に書き込みたい場合、上記のCBC関数のようなハッシュ関数を使用して、MAC値(例えばc0,・・・,cr)はシステム10における暗号化エンジン40によって前記データブロックから計算され、MAC値、IV、鍵k、および上記の他のパラメータを含む関連セキュリティコンフィギュレーションレコードは、データ自体がメモリ20に書き込まれると共に、メモリ20に書き込まれる。上記の式で、ek(x)は、xが鍵kによって暗号化される処理を表し、ek−1(x)は、xが鍵kを使用して復号されることを表す。

【0036】

その後、データブロックp1,・・・,prをメモリ20か読み出されるときに、関連するセキュリティコンフィギュレーションレコードも同様に読取られ、暗号化エンジン40は、IV、セキュリティコンフィギュレーションレコード中の鍵k、および読み出されたデータから一組のMAC値を計算し、該一組の値をメモリ20から読取った一組のMAC値と比較する。これは二組のMAC値の間に差がある場合、読取られたデータは変更、或いは破損されていたのかもしれない。例えば上記のCBC関数等のハッシュ関数については、シーケンス中の第1番目の値を除いて、各々MAC値は前のMACから導びかれる。これは、MAC値の組がこの場合に、時間の順に連続して導びかれることを表す。

【0037】

ホスト装置24中の複数のアプリケーションが、メモリ20に並行してアクセスできることが望ましく、その結果、ユーザーは他のアプリケーションを使用してメモリ20にアクセスする前に、当該メモリ20の使用中のあるアプリケーションが完了することを待つ必要がない。これは、例えば、読取り処理が割り込まれた時に、データp1,・・・,prのすべてのブロックがすでに読み出されたわけではないことを表すので、前記のメモリシステム(例えば図1および図2に示すシステム10)を装置24で実行している他の異なったアプリケーションに使用できる。しかし、この場合では、全体のデータストリームが読み出される前、且つすべてのMAC値が計算される前に、上記のMAC値計算処理は割込まれてもよい。従って、前記のメモリシステムがデータp1,・・・,pr中の未読のブロックの読取りを再開する場合、前に計算されたMAC値の不完全な組が失われている可能性があり、残りのMAC値の計算は以前に計算したMAC値に依存するため、残りのMAC値を計算することは不可能となる。したがって、本発明の他の特徴は、以前に計算されたMAC値の不完全な組は、セキュリティコンフィギュレーションレコード内の残りの値(例えばIV、鍵k、データソースおよび行き先、アルゴリズム)と共に、例えば図1のCPU RAM 12aなどへ保存することに基づくことである。従って、メモリシステムがデータp1,・・・,pr中の未読のブロックの読取りを再開する場合、以前に計算されたMAC値の不完全な組はまだ利用可能であるので、残りのMAC値を計算することが可能である。

【0038】

ブロック242の読取りセッションの終わりで、セッション終了のコマンドをホスト24によって検知した後、読取ったデータを認証するために、CPUは、メモリ20から読取ったデータから計算されたMAC値をメモリ20に保存された前記のMAC値と比較する。若し、受信したホストコマンドが上記のどれでもない場合、CPU12は単に該コマンドを実行して、ブロック202に戻る(ブロック250)。

【0039】

本発明は様々な実施例を参照して以上述べたが、添付された請求の範囲及びそれに相当するものだけで規定する本発明の範囲を逸脱しない範囲に、変更および修正を行い得ることが理解されたい。ここに引用された文献はすべて参照により盛り込まれる。

【図面の簡単な説明】

【0040】

【図1】図1は、本発明を説明するための、ホスト装置と通信するメモリシステムのブロック図である。

【図2】図2は、図1の暗号化エンジンの一部のブロック図である。

【図3】図3は、本発明の一部分の好適な実施例を説明するための、図1に示されたシステムの作動を説明するフローチャートである。

【図4】図4は、複数のデータストリームを取り扱う場合の図1に示されたシステムの操作およびセキュリティコンフィギュレーションレコードの利用を説明するのに有用なフローチャートである。 記述上の便宜から、本出願では、同一の構成について同じ番号を付している。

【技術分野】

【0001】

本発明は一般にメモリシステムに関し、特にイン−ストリームデータ暗号化/復号機能を有するメモリシステムに関する。

【背景技術】

【0002】

モバイル機器市場は、より多くのデータ交換を発生させることにより平均収入の増加を図るよう、コンテンツストレージを備える方向に進んでいる。これは、モバイル機器に保存されている時に、そのコンテンツが保護されていなければならないことを意味する。

【0003】

数年来、ポータブル記憶装置は商業用途に使用されていおり、データをコンピューティングデバイスから他のコンピューティングデバイスへ持ち運んだり、あるいはバックアップデータを保存するために用いられている。ポータブルハードディスクドライブ、ポータブルフラッシュメモリディスクおよびフラッシュメモリカードのようなもっと高機能なポータブル記憶装置は、ストレージ管理の制御用マイクロプロセッサを含んでいる。

【0004】

ポータブル記憶装置に保存されたコンテンツを保護するために、保存されているデータは通常、暗号化され、許可されたユーザだけがデータを復号することが許される。

【0005】

旧来の暗号化の機能を有するポータブル記憶装置では、ストレージ管理用のマイクロプロセッサも暗号化と復号の処理に深く関与している。そのようなシステムは、例えば米国特許6,457,126号に記載されている。この場合では、記憶装置の処理能力および機能はひどく影響を受ける可能性がある。従って、前記の問題を大幅に軽減するローカル記憶装置を提供することは望ましい。

【特許文献1】米国特許6,457,126号

【発明の開示】

【発明が解決しようとする課題】

【0006】

この発明の一側面は、データストリーム中のデータが不揮発性メモリセルに送信され、又は該不揮発性メモリセルから取出しされる時に、あらゆるコントローラあるいはマイクロプロセッサとも密接な関与せず、データストリーム中のデータを回路によって暗号化処理する場合に、メモリシステムの処理能力が改善できる認識に基づくものである。ある実施例では、前記コントローラは暗号化処理に使用されるパラメーターを規定することだけに関与し、処理には関与しない。この実施例の実行では、パラメーターは、コンフィギュレーションレジスタによって設定される。

【0007】

好ましくは、メモリセルはフラッシュメモリセルを有する。さらに、メモリセル、データ暗号化および/または復号に使用する回路、セルおよび回路を制御するコントローラは、メモリカードかメモリスティックのような物体の中に取付けされ、密閉されることが好ましい。

【0008】

データは、ページで前記メモリセルに書き込まれ、またはそれから読出されることができる。暗号化および復号に使用される従来の暗号化アルゴリズムの多くは、通常、ページより小さなデータの単位で作動する。したがって、本発明の他の側面は、前記暗号化回路が、読取りまたは書き込み中の前記データストリーム中の1ページ以上のデータを暗号化処理することと、すべて前記コントローラの関与なしで、前記データストリームが複数のソース中で選択されたデータソースと複数の行き先(destination)中で選択された行き先を持つように、制御される認識に基づくものである。

【0009】

発明の他の側面によれば、前記暗号化回路は、コントローラあるいはマイクロプロセッサの関与なしで、暗号化および/または復号に対する複数のアルゴリズム中で1つ以上の暗号化アルゴリズムの選択ができるように設定できる。設定後、前記コントローラの関与なしで、前記回路は、複数の連続する段階で前記データストリーム中のデータを暗号化処理するようにも、前記回路を設定できる。設定後前記コントローラの関与なしで、複数の連続する段階で、前記暗号化処理は二つ以上の鍵を使用し、二つ以上のタイプの暗号化処理を使用することができる。

【0010】

あるアプリケーションでは、前記メモリシステムは、二つ以上の前記データストリームを取り扱うことが望ましい。この場合では、異なったデータストリーム中のデータがインターリーブ方式で暗号化処理されるように、前記コントローラは前記メモリセルと前記回路を制御する。好ましくは、前記データストリームの処理がインタリービングの間に割り込まれる場合に、各データストリームの暗号化処理用の様々なパラメーターが保存されるので、該データストリームの処理が再開される時、暗号化処理を継続するようパラメーターが回復できる。この特徴の一実施例では、暗号化処理用の様々なパラメーターをセットするために、セキュリティコンフィギュレーションレコードを書き込み操作の最初に作成し、セッションの終了にこれらのパラメーターを保存する。その後、読み込み操作の開始時にこのレコードをメモリから取り戻し、操作の終了に廃棄する。他のデータストリームの処理をさせるために、前記データストリームが一時的に割り込まれる場合、そのようなレコードも保存され、元のデータストリームの処理が再開される時に取り戻される。

【0011】

本発明の上記の様相は、個々に、あるいはそれの任意の組み合せで使用できる。

【発明を実施するための最良の形態】

【0012】

図1のブロック図を用いて、本発明の様々な部分が実行できる実例的なメモリシステムを説明する。図1に示すように、メモリシステム10は、中央処理装置(CPU)12と、バッファ管理ユニット(BMU)14と、ホストインタフェースモジュール(HIM)16と、フラッシュインタフェースモジュール(FIM)18と、フラッシュメモリ20と、ペリフェラルアクセスモジュール(PAM)22を有する。メモリシステム10は、ホストインタフェースバス26およびポート26aを介してホスト装置24と通信する。NANDタイプでもよいフラッシュメモリ20はホスト装置24用のデータ記憶装置を提供する。また、CPU12用のソフトウェアコードはフラッシュメモリ20に保存されてもよい。FIM18は、フラッシュインタフェースバス28とポート28aを介してフラッシュメモリ20に接続される。HIM16は、例えばディジタルカメラと、パソコンと、PDA(Personal Digital Assistant)と、ディジタルメディアプレーヤーと、MP−3プレーヤーと携帯電話、あるいは他のディジタル装置等のホストシステムに接続するのに適する。ペリフェラルアクセスモジュール22は、CPU12との通信用の例えばFIMと、HIMとBMU等の適切なコントローラモジュールを選択する。一つの実施例において、点線に囲まれた枠内のシステム10の中のすべてのコンポーネントを、例えばメモリカードあるいはメモリスティック10’の単一のユニットに封入することができ、好ましくは、カードあるいはスティック中に密閉できる。

【0013】

バッファ管理ユニット14は、ホストダイレクトメモリアクセス(HDMA)32と、フラッシュダイレクトメモリアクセス(FDMA)コントローラ34と、アービタ36と、バッファランダムアクセスメモリ(BRAM)38と、暗号化エンジン40を有する。アービタ36は共有バスアービタであるので、いつでも、ただ一つのマスタあるいはイニシエータ(HDMA32、FDMA34あるいはCPU12でもよい)だけがアクティブ可能になり、スレーブまたはターゲットはBRAM 38である。アービタは、適切なイニシエータの要求をBRAM38に向ける。HDMA32とFDMA34は、HIM16、FIM18、およびBRAM38と、あるいはCPUランダムアクセスメモリ(CPU RAM)12aとの間に伝送されたデータに関与する。HDMA32およびFDMA34の作動は従来の通りで、ここに詳述する必要はない。BRAM38は、ホスト装置24、フラッシュメモリ20およびCPU RAM 12aの間で伝送されるデータを一時的に保持するものである。HDMA32とFDMA34は、HIM16/FIM18とBRAM38あるいはCPU RAM 12aとの間にデータ伝送し、セクター伝送完了を指示するものである。

【0014】

まず最初に、フラッシュメモリ20からのデータをホスト装置24によって読取る場合、メモリ20中の暗号化されたデータは、バス28、FIM18、FDMA34、暗号化されたデータを復号する暗号化エンジン(Crypto−Engine)40によってフェッチされ、BRAM38に保存される。その後、復号されたデータは、BRAM38からHDMA32、HIM16、バス26を介してホスト装置24へ送信される。メモリ20に保存されたデータが復号される鍵及び/またはアルゴリズムと異なる鍵及び/またはアルゴリズムによってホスト装置24に伝送されるデータを再暗号化するように、BRAM38からフェッチされたデータは、HDMA32に伝送される前に、暗号化エンジン(Crypto−Engine)40によって再暗号化できる。さらに代わりの実施例では、データが不正アクセスに対して脆弱となりがちな、BRAM38に復号されたデータを保存する上述の処理よりも、メモリ20からのデータが、BRAM38に伝送される前に復号されて、暗号化エンジン40によって再暗号化されるのが好ましい。その後、前述したように、BRAM38中の暗号化されたデータは、ホスト装置24へ伝送される。これで読取り処理の際のデータストリームを説明した。

【0015】

データがホスト装置24によってメモリ20に書き込まれる場合は、データストリームの方向が逆にされる。例えば、暗号化されていないデータをホスト装置を利用して、バス26、HIM16、HDMA32によって暗号化エンジン40へ伝送する場合、これらのデータは、BRAM38に保存される前にエンジン40によって暗号化されてもよい。その代わりに、暗号化されていないデータをBRAM38に保存してもよい。その後、このデータは、FDMA34に伝送される前に、メモリ20へ伝送される途中で暗号化される。書き込まれたデータが多段の暗号化処理を経過する場合、処理済みのデータをBRAM38に保存する前に、エンジン40が前記の処理を完了するのが好ましい。

【0016】

本発明の1つの側面は、ホスト装置24とメモリ20との間で伝送されるデータストリーム中のデータの前述した暗号化処理を、CPU12の関与が最小となるように実行できれば、装置10の処理能力とそれによる性能を非常に改善することができるという認識に基づいているものである。これは以下説明するように図1に示す。

【0017】

上記の処理では、二つの異なったデータソースおよび行き先があるデータストリームを説明した。読取り処理では、データソースはメモリ20であり、行き先はホスト装置24である。書き込み処理では、データソースはホスト装置24であり、行き先はメモリ20である。さらに、データソース(あるいは行き先)は、対応する行き先(あるいはデータソース)がメモリ20であるCPU12でもよい。さらに、他のオペレーションでは、バルク暗号化およびハッシュオペレーションに対して、データストリームはBMU14からCPU12まででもよい。ソースの中のデータと出力データの行き先及び適用されうる対応する暗号化処理の様々な組み合わせを下記の表に述べる。

【表1】

【0018】

上記の表に示したように、一つの追加されたオペレート可能なモードは、バイパスモードである。バイパスモードは、暗号化エンジン40が存在せずHDMAとFMDAがアービタ36を介して該バイパス路に沿ってBRAM38に直接接続されているように、バイパス路(図1に示せず)に沿って、データストリームに暗号処理せずに、FDMA34がCPU12あるいはBRAM38にアクセスすることができる。本発明の一実施例によれば、例えばデータソースとデータ行き先等のプロセッシング、例えば適用される(あるいは、バイパスモード)暗号化アルゴリズム等の暗号化パラメータは、図1の暗号化エンジン40の機能的ブロックのうち一部のブロック図である図2のコンフィギュレーションレジスタ102をセットすることで、複数のデータソースと、複数の行き先および複数のアルゴリズムからCPU12を用いてあらかじめ選択できる。

【0019】

図2は暗号化エンジン40のブロック図で、その構成要素の一部をより詳細に示す。図2に示すように、暗号化エンジン40は、暗号化ブロック50とコンフィギュレーションレジスタ52とを有する。コンフィギュレーションレジスタ52は、選択されたデータソースと、選択されたデータ行き先、および使用される暗号化アルゴリズムあるいはバイパスモードとに関するセキュリティコンフィギュレーション情報あるいはセキュリティコンフィギュレーションレコードを、上記の表と使用すべき鍵(バイパスモードを除いて)に従い、データが暗号化か、復号か、あるいはハッシュされることになっているか(以上これらは「暗号化処理される」という表現に含まれる)、あるいは暗号化処理されないかどうかによって保存するものである。セキュリティコンフィギュレーション情報あるいはレコードは、CPU12によってレジスタ52に書き込まれてもよい。この情報をレジスタ52に保存した後、エンジン40は、CPU12の関与なしで暗号化処理を実施することができる。多くの通常の暗号化アルゴリズムは、データを、128ビットを1単位として処理する。これは、フラッシュメモリのような記憶装置に一度に書き込まれるかまたはそれから読み出されるデータのページのサイズより小さくすることができる。各ページは、通常1つ以上のセクターのデータを保存するが、該セクターのサイズは、ホストシステムによって規定されている。1例は磁気ディスクドライブで確立された規格によるユーザデータの512バイトのセクターで、ユーザデータおよび/またはそれが保存されているブロックに関するオーバーヘッド情報の若干のバイトがプラスされる。

【0020】

CPU12がエンジン40による暗号化処理に関与する必要がないように、また、データの全ページがエンジン40によって一度に1ページより小さな単位で暗号化処理されるように、ロジック回路(図示されていない)をブロック40で使用することができる。一実施例では、暗号化エンジン40はハードウェア回路である。

【0021】

図2に示すように、ブロック54、56および58は、暗号化ブロック50によって実施されるようCPUが選択できる三つの異なる暗号化アルゴリズム(それぞれHash、DES及びAES)を表わす。これらのアルゴリズムと異なる暗号化アルゴリズムも使用できるし、又、本発明の範囲内にある。暗号化ブロック50で処理されるデータと、ホスト装置24あるいはメモリ20、或いはCPU12から発生するデータは、先ず入力バッファ62に保存されて、レジスタ52で特定された暗号化アルゴリズムにより暗号化ブロック50で暗号化処理される。そして、暗号化処理されたデータは、レジスタ52中の行き先情報により、行き先へ伝送される前に、出力バッファ64に保存される。図2はさらに、メモリ20に書き込まされ、又、それから読み出されるデータを暗号化処理しない、入力バッファ62から出力バッファ64までのバイパス路72を含み、これは表のモードのうち1つであり、上述した1つものである。

【0022】

コンフィギュレーションレジスタ52はさらに、暗号化処理中で使用される鍵を保存できる。一実施例では、この鍵は、CPU12(例えば、メモリ20等から)によって読出されて、暗号化ブロック50による暗号化又は復号の前にレジスタ52に保存される。上述した処理は、CPU12がレジスタ52に適切な情報を書き込んだ後、CPU12の関与なしでブロック40中で実施される。図2を簡単化するために、ブロック40中のアルゴリズム、データソースおよび行き先を選択するためにレジスタ52中の情報を使用し、唯一の鍵と選択されたアルゴリズムを暗号化処理に使用するロジック回路は省略されている。処理されたデータが出力バッファ64へ伝送される前に、入力バッファ62中のデータを処理するために、暗号化ブロック50を二度以上使用することが可能である。例えば、データソースからのデータを先ず復号し、データをバッファ64に伝送する前に、異なる鍵および/または異なるアルゴリズムを使用して、復号されたデータを暗号化するのが望ましい。データの暗号化または復号に加えて、データのインテグリティを保証する目的では、データの要約あるいはハッシュ値を得るようにハッシングアルゴリズムをデータに適用することは有用である。これらすべての状況では、復号するためにある鍵を使用した後、暗号化するために異なった鍵を使用するか、データを暗号化するか復号するかだけでなく、要約を得るように、暗号化ブロック50でデータを二度処理することが望ましい。言うまでもなく、データは更に、該データが復号され、ハッシングされ、暗号化される場合、暗号化ブロック50で二回以上処理できる。これらのオペレーションがシーケンシャル段階(多段処理)で連続的に発生する。言いかえれば、多段(即ち、2段階以上)の処理では、暗号化ブロック50でより多く処理するよう暗号化ブロック50によって既に出力バッファ64で処理されたデータを、フィードバックパス66を介して、入力バッファ62へ伝送することにより、データを二度以上、暗号化ブロック50を通して伝送してもよい。二段階以上を考慮する場合、データは追加処理のために、更に追加の回数でフィードバックすることができる。処理の各段階では、異なったアルゴリズムおよび/または鍵を使用してもよい。

【0023】

多段の処理が望まれる場合、CPU12が、データを暗号化処理する回数および多段の処理の各段階で使用される鍵および/またはアルゴリズムを指定するために、セキュリティコンフィギュレーション情報あるいはレコードをレジスタ52に入力するために使用されてもよい。この情報がレジスタ52に書き込まれた後、CPU12は多段の処理に全く関与する必要がなくなる。

【0024】

図1のメモリシステム10はフラッシュメモリを有しているが、このシステムは例えば磁気ディスク、光ディスクCDs等の他のタイプの不揮発性メモリ、他のすべてのタイプの書き換え可能な不揮発性メモリシステムをさらに含んでもよく、上述した様々な利点は、これらの選択できる実施例に同様に適用できる。選択できる実施例では、このメモリは更に、メモリシステムの残りのコンポーネントと共に、同じ物体(例えば、メモリカードやメモリステック等)に密閉することが好ましい。

【0025】

オペレーティングシステム10の読取り処理を図3のフローチャートに示す。CPU12は、ホスト装置24から読取りコマンドを受け取った後、読取り操作を始める(楕円150)。その後、CPU12は、レジスタ52に適切なセキュリティコンフィギュレーション情報あるいはレコードを書き込むことにより、暗号化エンジン40を設定し、さらに読取り操作用にBMU14を設定し、オペレーション用(ブロック152、154)にBRAM38中での例えばメモリスペースの割り付け等の他のパラメーターを設定する。CPU12はさらに、データが読まれるメモリ20中の区域を指定するなど、FIM18を設定する(ブロック156)。その後、暗号化処理を含む上記処理がCPU(エラー訂正を除いて)の関与なしで実行されるように、HDMAエンジン32およびFDMAエンジン34を開始する。ブロック158を参照して、CPUは、割り込みを受信すると、それがFIMの割り込みかどうかチェックする(菱形160)。CPUはFIM割り込みが受信された場合、割り込みがデータストリーム中に一つ以上のエラーがあることを示す割り込みであるかどうかをチェックする(162)。エラーがあることが示される場合、BRAM38中のエラーを修正する為に進み(ブロック164)、データが次に読まれるメモリ20中の区域を変更するよう、FIM18の設定に戻る(ブロック156)。FIM割り込みがデータストリーム中のエラーを示さなかった場合、FIMがオペレーションを完了し、又CPUがFIMの再設定のためにブロック156に戻ることを表す。CPUに検知された割り込みがFIM割り込みでない場合、CPUはデータ割り込みの終了かどうかをチェックする(菱形166)。そうであれば、読取り操作は終了する(楕円168)。そうでなければ、この割り込みは、データの暗号化処理と無関係であり(即ち、クロック割り込み)、又、CPUは当該割り込みを処理し(図示されていない)、割り込みをチェックするために菱形160に戻る。

【0026】

書き込み操作には図3をわずか修正するだけでよい。メモリ20に書き込むデータにECCエラーの取り扱いがないので、書き込み操作でCPU12は菱形162及びブロック164中の処理を省くことができる。CPU12が、書き込み操作中にFIM割り込みを受信する場合、これは、FIMがそのオペレーションの完了したことを表し、CPUもFIMを再設定するためにブロック156に戻る。この違いを除けば、書き込み操作は実質的に読取り操作に似ている。したがって、暗号化エンジン40、BMU14およびFIM18を一度設定すると、システム10は、CPU12の関与なしで、たとえ暗号化エンジン40がページよりはるかに小さな単位でデータを処理することがあっても、データをすべて暗号化処理し(バイパス・モード以外)、そのセッションのページのすべての書き込みあるいは読取りを完了することができる。

【0027】

《インターリービングデータストリーム》

複数のホストアプリケーションが、複数のデータストリームを処理しながら同時に、メモリ20にアクセスできることが望ましい。これが意味することは、あるデータストリームの暗号化処理は、メモリシステム10が他のデータストリームを処理するために、割込んだ際に、完了していなかったかもしれないことである。異なったデータストリームの暗号化処理は、通常異なったパラメーター(例えば、異なった鍵とアルゴリズム、および異なったデータソースと行き先)を用いる。これらのパラメーターは、データストリームの対応するセキュリティコンフィギュレーションレコードに備えられている。特定のデータストリームの割り込まれた処理がその後再開される場合に、その対応するセキュリティコンフィギュレーションレコードが失われないことを保証するために、そのレコードは、CPU RAM 12aに保存するのが好ましい。前に割り込まれたデータストリームの処理を再開する場合、CPU12は、そのデータストリーム用の保存されたセキュリティコンフィギュレーション記録を読み出し、保存されている対応するセキュリティコンフィギュレーションレコードに基づいて、正確なパラメーターを用いて、そのデータストリームの再開された暗号化処理を行うことができる。

【0028】

図4は、複数のデータストリームの処理およびセキュリティコンフィギュレーションレコードの利用の図1および図2のシステムの操作を説明するフローチャートである。CPUは、ホストコマンドが受信されたかをチェックする(ブロック202と菱形204)。ホストコマンドが受信されていた時、例えば最初のデータストリームを暗号化処理する場合、CPUは、コマンドが装置24で実行する最初のアプリケーション等のスタートセッションコマンドかどうかについてチェックする(菱形206)。そうである場合、CPUは書き込みセッションが要求されたかどうかチェックする(菱形208)。若し書き込みセッションが要求されていた場合、CPUはホスト装置からの情報によってセキュリティコンフィギュレーションレコード(例えば選択されたデータソース、選択されたデータ行き先、上記の表テーブルと使用されるべき鍵によって用いられる暗号化アルゴリズム、および、データが暗号化、復号又はハッシュされるべきかどうか)を作成し(ブロック210)、第1データストリーム用の最初のセッションを始める。CPU12は、これらのセキュリティコンフィギュレーション情報あるいはレコードをCPU RAM 12aに保存する。もし要求されたセッションが読取りセッションである場合、CPUは、読み出されるデータ用のセキュリティコンフィギュレーションレコードをメモリ20から読取り(ブロック240)、それをCPU RAM 12aに保存する。その後、CPUは戻り、さらなるホストコマンドを待つ(202)。

【0029】

CPUは、別のホストコマンドを受信すると、スタートセッションコマンドであるかを再びチェックする(菱形206)。そうである場合、ブロック210あるいはブロック240に進み、第2のセッションを始めることができる。これは、第2のデータストリームの暗号化処理を要求するホスト装置24上で作動する、異なった第2のアプリケーション用の新しい第2のセッション等である。上記の第2のデータストリーム用のセキュリティコンフィギュレーション情報あるいはレコードは、CPU RAM 12aに再び保存されるが、これは書き込みと読取りの両セッションがある場合である(ブロック210、240)。追加のセッションは同じ方法で追加のデータストリームのために作成できる。CPUはブロック202に戻り、ホストコマンドがスタートセッションコマンドであるかを確かめるために次のホストコマンドをチェックする(菱形206)。このようにして、CPU12が菱形206中のスタートセッションコマンドでないホストコマンドを検知するまで、前述したように追加セッションが作成される。

【0030】

この場合には、CPU12は、ホストコマンドがセッション終了のコマンドであるかを確かめるべく次のホストコマンドをチェックする(菱形222)。そうでない場合、CPUは、それがデータコマンドであるかをチェックする(菱形224)。それがデータコマンドであると仮定すれば、CPUは、どのデータストリームを処理するかを判断し、前記のデータストリームのセキュリティコンフィギュレーションレコードにより暗号化エンジン40を設定し(レジスタ52に書き込むことで)、暗号化エンジン40は、例えば図3の処理などにより、上述した方式で読取りあるいは書き込み操作を実行する(或いは暗号化エンジン40はバイパスモードでバイパスされる)(ブロック226)。

【0031】

読取りあるいは書き込み処理に割り込みがない場合、セッションの間に処理されるすべてのページが処理されたことを表すセッション終了コマンドをCPUが受信するまでに、処理は継続する(ブロック222)。しかしながら、割り込みがある場合、CPUは、システム10が現在処理しているデータストリームとは異なるデータストリームからのデータを処理するホストデータコマンドを受信する。この場合、暗号化エンジン40は、前記の異なるデータストリームを処理するよう再設定される必要がある。その後、CPUは、CPU RAM 12aから前記の異なるデータストリーム用のセキュリティコンフィギュレーションレコードを読み出し、そして、暗号化エンジン40を再設定し(レジスタ52に読み出されたレコードを書き込むことによって)、その結果、エンジン40が前記の異なったデータストリームを正確に処理する。

【0032】

セッション終了コマンドが書き込みセッションで受け取られた場合(222ブロック)、CPUは、書き込まれたデータと共にセキュリティコンフィギュレーションレコードをメモリ20に保存し、前記のレコードは、それに続く読取り操作で読み出され得る(菱形228およびブロック230)。読取り操作では、RAM12aに保存されたセキュリティコンフィギュレーションレコードが廃棄されるが、メモリ20に保存されたレコードは、将来起こり得る読取り操作のために保持される(ブロック242)。

【0033】

あるアプリケーションにおいては、無許可な操作(tampering)に対してメモリ20中のデータのインテグリティを維持することは重要であろう。メモリ20に保存されているデータが変更、あるいは、破損されないことを保証するために、前記のデータのハッシュ値またはダイジェストを前記のデータから導出することが望ましく、前記のデータのハッシュ値またはダイジェストは前記のデータと共に保存されている。データを読み出されると、ハッシュ値またはダイジェストも同様に読み出され、読み出されたダイジェストあるいはハッシュ値は、前記の読み出されたデータから計算されたダイジェストあるいはハッシュ値と比較され得る。もし、それらの間に差異があれば、メモリ20のデータが変更されたか、破損されたのかもしない。

【0034】

共通のハッシュ関数は連鎖ブロック暗号(chained block cipher)(CBC)であって、メッセージ認証コード(MAC)は、書き込み中または読取り中のデータのブロックから時間系列に従って導き出される。共通のCBC関数は以下に通り。

【0035】

上記の値c0,・・・,crは、データストリームp1,・・・,prのメッセージ認証コード(MAC)である。IVはイニシエーション(開始)ベクトルであり、kは鍵である。したがって、データp1,・・・,prブロックをメモリ20に書き込みたい場合、上記のCBC関数のようなハッシュ関数を使用して、MAC値(例えばc0,・・・,cr)はシステム10における暗号化エンジン40によって前記データブロックから計算され、MAC値、IV、鍵k、および上記の他のパラメータを含む関連セキュリティコンフィギュレーションレコードは、データ自体がメモリ20に書き込まれると共に、メモリ20に書き込まれる。上記の式で、ek(x)は、xが鍵kによって暗号化される処理を表し、ek−1(x)は、xが鍵kを使用して復号されることを表す。

【0036】

その後、データブロックp1,・・・,prをメモリ20か読み出されるときに、関連するセキュリティコンフィギュレーションレコードも同様に読取られ、暗号化エンジン40は、IV、セキュリティコンフィギュレーションレコード中の鍵k、および読み出されたデータから一組のMAC値を計算し、該一組の値をメモリ20から読取った一組のMAC値と比較する。これは二組のMAC値の間に差がある場合、読取られたデータは変更、或いは破損されていたのかもしれない。例えば上記のCBC関数等のハッシュ関数については、シーケンス中の第1番目の値を除いて、各々MAC値は前のMACから導びかれる。これは、MAC値の組がこの場合に、時間の順に連続して導びかれることを表す。

【0037】

ホスト装置24中の複数のアプリケーションが、メモリ20に並行してアクセスできることが望ましく、その結果、ユーザーは他のアプリケーションを使用してメモリ20にアクセスする前に、当該メモリ20の使用中のあるアプリケーションが完了することを待つ必要がない。これは、例えば、読取り処理が割り込まれた時に、データp1,・・・,prのすべてのブロックがすでに読み出されたわけではないことを表すので、前記のメモリシステム(例えば図1および図2に示すシステム10)を装置24で実行している他の異なったアプリケーションに使用できる。しかし、この場合では、全体のデータストリームが読み出される前、且つすべてのMAC値が計算される前に、上記のMAC値計算処理は割込まれてもよい。従って、前記のメモリシステムがデータp1,・・・,pr中の未読のブロックの読取りを再開する場合、前に計算されたMAC値の不完全な組が失われている可能性があり、残りのMAC値の計算は以前に計算したMAC値に依存するため、残りのMAC値を計算することは不可能となる。したがって、本発明の他の特徴は、以前に計算されたMAC値の不完全な組は、セキュリティコンフィギュレーションレコード内の残りの値(例えばIV、鍵k、データソースおよび行き先、アルゴリズム)と共に、例えば図1のCPU RAM 12aなどへ保存することに基づくことである。従って、メモリシステムがデータp1,・・・,pr中の未読のブロックの読取りを再開する場合、以前に計算されたMAC値の不完全な組はまだ利用可能であるので、残りのMAC値を計算することが可能である。

【0038】

ブロック242の読取りセッションの終わりで、セッション終了のコマンドをホスト24によって検知した後、読取ったデータを認証するために、CPUは、メモリ20から読取ったデータから計算されたMAC値をメモリ20に保存された前記のMAC値と比較する。若し、受信したホストコマンドが上記のどれでもない場合、CPU12は単に該コマンドを実行して、ブロック202に戻る(ブロック250)。

【0039】

本発明は様々な実施例を参照して以上述べたが、添付された請求の範囲及びそれに相当するものだけで規定する本発明の範囲を逸脱しない範囲に、変更および修正を行い得ることが理解されたい。ここに引用された文献はすべて参照により盛り込まれる。

【図面の簡単な説明】

【0040】

【図1】図1は、本発明を説明するための、ホスト装置と通信するメモリシステムのブロック図である。

【図2】図2は、図1の暗号化エンジンの一部のブロック図である。

【図3】図3は、本発明の一部分の好適な実施例を説明するための、図1に示されたシステムの作動を説明するフローチャートである。

【図4】図4は、複数のデータストリームを取り扱う場合の図1に示されたシステムの操作およびセキュリティコンフィギュレーションレコードの利用を説明するのに有用なフローチャートである。 記述上の便宜から、本出願では、同一の構成について同じ番号を付している。

【特許請求の範囲】

【請求項1】

暗号化されたデータを保存するメモリシステムにおいて、

不揮発性のフラッシュメモリセルと、

前記セルからの、又は前記セルへのデータストリーム中のデータに対して暗号化処理を実行する回路と、

コントローラであって、暗号化アルゴリズムを用いて、暗号化処理するために、前記回路を設定すると共に前記セルと前記回路を制御し、前記回路が設定された後、前記コントローラの関与なしで、前記データストリーム中のデータが前記回路によって暗号化処理されるようするコントローラと、

を備えることを特徴とするシステム。

【請求項2】

データがページの前記セルに書き込まれ、または前記セルから読取られ、前記回路が各々1ページ未満のデータユニットに暗号化処理を実行し、前記コントローラが前記回路を設定し、前記回路が設定された後、前記回路が、前記コントローラの関与なしにデータの複数のページに暗号化処理を実行することを特徴とする請求項1に記載のシステム。

【請求項3】

前記コントローラが前記回路を設定し、前記データストリームが複数のソース中で選択された前記データソースと、複数の行き先中で選択された前記行き先を持つことを特徴とする請求項1に記載のシステム。

【請求項4】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルから始まり、前記コントローラ又はホスト装置に仕向けられることを特徴とする請求項3に記載のシステム。

【請求項5】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラ又はホスト装置から始まることを特徴とする請求項3に記載のシステム。

【請求項6】

前記コントローラが前記回路を設定し、前記データストリームが前記セルからホスト装置まで、又は前記ホスト装置から前記セルまでであり、前記回路をバイパスすることを特徴とする請求項3に記載のシステム。

【請求項7】

前記コントローラが前記回路を設定し、選択された暗号化アルゴリズムが前記暗号化処理で使用されることを特徴とする請求項1に記載のシステム。

【請求項8】

前記コントローラが前記回路を設定し、前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項1に記載のシステム。

【請求項9】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを、一つ以上の鍵を使用して、複数の連続する段階で暗号化処理することを特徴とする請求項8に記載のシステム。

【請求項10】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを一つ以上の暗号化処理によって、複数の連続する段階で暗号化処理することを特徴とする請求項8に記載のシステム。

【請求項11】

暗号化されたデータを保存するメモリカードにおいて、

不揮発性のフラッシュメモリセルと、

前記セルからの、又は前記セルへのデータストリーム中のデータに対して暗号化処理を実行する回路と、

コントローラであって、暗号化アルゴリズムを用いて、暗号化処理するために、前記回路を設定すると共に前記セルと前記回路を制御し、前記回路が設定された後、前記コントローラの関与なしで、前記データストリーム中のデータが前記回路によって暗号化処理されるようするコントローラと、

を備え、

前記メモリセル、前記回路および前記コントローラは、カード中に密閉されていることを特徴とするカード。

【請求項12】

データがページで前記セルに書き込まれ、または前記セルから読み出され、前記回路が各々1ページ未満のデータユニットに暗号化処理を実行し、前記コントローラが前記回路を設定し、前記回路が設定された後、前記コントローラの関与なしで、前記回路がデータの複数ページに暗号化処理を実行することを特徴とする請求項11に記載のカード。

【請求項13】

前記コントローラが前記回路を設定し、前記データストリームが複数のソース中で選択されたデータソースと、複数の行き先中で選択された行き先を持つことを特徴とする請求項11に記載のカード。

【請求項14】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルから始まり、前記コントローラ又はホスト装置に仕向けられることを特徴とする請求項13に記載のカード。

【請求項15】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラ又はホスト装置から始まることを特徴とする請求項13に記載のカード。

【請求項16】

前記コントローラが前記回路を設定し、前記データストリームが前記セルからホスト装置まで、または前記ホスト装置から前記セルまでであり、前記回路をバイパスすることを特徴とする請求項13に記載のカード。

【請求項17】

前記コントローラが前記回路を設定し、選択された暗号化アルゴリズムが暗号化および/または復号で使用されることを特徴とする請求項11に記載のカード。

【請求項18】

前記コントローラが前記回路を設定し、前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項11に記載のカード。

【請求項19】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを、一つ以上の鍵を使用して、複数の連続する段階で暗号化処理することを特徴とする請求項18に記載のカード。

【請求項20】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを一つ以上の暗号化処理によって、複数の連続する段階で暗号化処理することを特徴とする請求項18記載にカード。

【請求項21】

暗号化されたデータを保存するメモリカードにおいて、

不揮発性のフラッシュメモリセルと、

前記セルからの、又は前記セルへのデータストリーム中のデータに対して暗号化処理を実行する回路と、

データをページで前記セルに書き込ませ、または、前記セルから読み出させるコントローラを備え、

前記回路は、各々1ページ未満のデータユニットに暗号化処理を実行し、

前記コントローラの関与なしで、前記データストリームの1ページ以上が暗号化処理され、複数のソース中で選択されたデータソースと複数の行き先中で選択された行き先を用いて、書き込まれ、又は、読み出される、

ことを特徴とするメモリカード。

【請求項22】

セルおよび暗号化回路を制御するコントローラを有するメモリシステムの不揮発性のフラッシュメモリセルにおけるデータを暗号化および/または復号する方法において、

暗号化アルゴリズムを用いて、前記セルからの、又は前記セルへのデータストリーム中のデータに暗号化処理を実行する回路を設定するためにコントローラを用いるステップと、

前記回路が設定された後に前記コントローラの関与なしで、前記データストリーム中のデータが、前記回路によって暗号化処理されるステップと、

を含むことを特徴とする方法。

【請求項23】

データがページで前記セルに書き込まれ、または前記セルから読み出され、前記回路が各々1ページ未満のデータユニットに暗号化処理を実施し、前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、前記回路が設定された後、前記コントローラの関与なしで前記回路がデータの複数のページに暗号化処理することを特徴とする請求項22に記載の方法。

【請求項24】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリームが複数のソース中で選択されたデータソースおよび複数の行き先中で選択された行き先を有することを特徴とする請求項22に記載の方法。

【請求項25】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリーム中のデータが前記セルから始まり、前記コントローラあるいはホスト装置に仕向けられることを特徴とする請求項24に記載の方法。

【請求項26】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラあるいはホスト装置から始まることを特徴とする請求項24に記載の方法。

【請求項27】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリームが、前記セルからホスト装置まで、又は前記ホスト装置から前記セルまでであって、前記回路をバイパスすることを特徴とする請求項24に記載の方法。

【請求項28】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

選択した暗号化アルゴリズムは、前記暗号化処理に使用されることを特徴とする請求項22に記載の方法。

【請求項29】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記設定後、前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項22に記載の方法。

【請求項30】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記設定後、前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で、一つ以上の鍵を使用して暗号化処理することを特徴とする請求項29に記載の方法。

【請求項31】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記設定後、前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で、一つ以上の暗号化処理を使用して暗号化処理することを特徴とする請求項29に記載の方法。

【請求項32】

セルおよび暗号化回路を制御するコントローラを有するメモリシステムの不揮発性のフラッシュメモリセルにおけるデータを暗号化および/または復号する方法において、

前記コントローラの関与なしで、前記回路を用いて1ページ以上のデータを暗号化処理するステップであって、データがページ単位で書き込まれ、または読み出され、また、前記回路が、各々1ページ未満のデータユニットに暗号化処理をするステップと、

前記コントローラの関与なしで、複数のソース中で選択されたデータソースと、複数の行き先中で選択された行き先を有するように、前記データストリームを制御するステップと、

を含むことを特徴とする方法。

【請求項33】

前記暗号化回路を設定することをさらに含み、前記暗号化処理および前記制御が、前記回路の設定によって可能にされることを特徴とする請求項32に記載の方法。

【請求項34】

前記回路を設定することで、複数の暗号化アルゴリズム中で一つ以上の暗号化アルゴリズムの選択が可能となり、前記コントローラの関与なしに、前記選択された暗号化アルゴリズムを使用する前記回路によって、前記データストリーム中のデータが暗号化処理されることを特徴とする請求項33に記載の方法。

【請求項35】

前記回路が設定され、前記データストリーム中のデータが前記セルから始まり、前記コントローラ又はホスト装置に仕向けられることを特徴とする請求項33に記載の方法。

【請求項36】

前記回路が設定され、前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラ又はホスト装置から始まることを特徴とする請求項33に記載の方法。

【請求項37】

前記回路が設定され、前記データストリームが前記セルからホスト装置まで又は前記ホスト装置から前記セルまでであって、前記回路をバイパスすることを特徴とする請求項33に記載の方法。

【請求項38】

前記回路が設定され、前記設定後は、前記コントローラの関与なしに、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項33に記載の方法。

【請求項39】

前記回路が設定され、前記設定後は、前記コントローラの関与なしに、前記回路が前記データストリーム中のデータを、一つ以上の鍵を使用して、複数の連続する段階で暗号化処理することを特徴とする請求項38に記載の方法。

【請求項40】

前記回路が設定され、前記設定後は、前記コントローラの関与なしに、前記回路が前記データストリーム中のデータを、一つ以上の暗号化処理によって複数の連続する段階で暗号化処理することを特徴とする請求項38に記載の方法。

【請求項41】

暗号化されたデータ保存用のメモリシステムにおいて、

不揮発性のフラッシュメモリセルと、

前記セルから又は前記セルへの一つ以上のデータストリーム中のデータに暗号化処理を実行する回路と、

前記セルと前記回路を制御し、異なったデータストリーム中のデータがインターリーブ方式で暗号化処理されるコントローラを備え、

前記セルからデータをアクセスするための少なくとも1つのセッションは、他のセッションによって割り込まれ、

前記コントローラはセッションのセキュリティコンフィギュレーション情報を、前記割り込み前に保存させ、該情報は前記割り込み後に読み出すことができることを特徴とするシステム。

【請求項42】

前記セキュリティコンフィギュレーション情報は、データのソースあるいは行き先に関連する情報、暗号化鍵、暗号化アルゴリズム、および/またはメッセージ認証コードを含むことを特徴とする請求項41に記載のシステム。

【請求項43】

前記コントローラは前記セッションの再開時に、前記セッション用に保存された前記セキュリティコンフィギュレーション情報を読み出させることを特徴とする請求項41に記載のシステム。

【請求項44】

前記コントローラは、一つ以上のデータストリームの各々に対してセキュリティコンフィギュレーション情報を保存させ、割り込み後に前記情報が読み出させることを特徴とする請求項41に記載のシステム。

【請求項45】

前記データストリームからのデータの処理が再開される時に、前記コントローラは、一つ以上のデータストリームの各々に対して保存された前記セキュリティコンフィギュレーション情報を読み出させることを特徴とする請求項44に記載のシステム。

【請求項46】

前記コントローラは、前記割り込み以前に保存された、メッセージ認証コードを含む前記セキュリティコンフィギュレーション情報を読み出し、前記割り込まれたセッションが再開されるときに、前記読み出されたメッセージ認証コードから更新したメッセージ認証コードを導出することを特徴とする請求項41に記載のシステム。

【請求項47】

不揮発性のフラッシュメモリセルと暗号化回路を含む、暗号化されたデータ保存用のメモリシステムにおけるデータを処理する方法において、

前記セルからの、又は前記セルへのデータストリーム中のデータに暗号化処理を行うために前記回路を用いるステップと、

インターリーブ方式で、異なったデータストリーム中のデータを前記回路に暗号化処理させるステップであって、前記セルへの、または前記セルからのデータを処理する、少なくとも1セッションが、他のセッションに割り込まれ、前記少なくとも前記1セッションのセキュリティコンフィギュレーション情報が、前記割り込み前に保存され、前記割り込み後に読み出すことができるステップと、

を含むことを特徴とする方法。

【請求項48】

前記セキュリティコンフィギュレーション情報は、データのソースあるいは行き先に関連する情報、暗号化鍵、暗号化アルゴリズム、および/またはメッセージ認証コードを含むことを特徴とする請求項47に記載の方法。

【請求項49】

前記暗号化処理させる方法が、前記異なったデータストリームの各々に対して、前記セキュリティコンフィギュレーション情報を保存させ、前記割り込み後、前記情報が読み出せることを特徴とする請求項47に記載の方法。

【請求項50】

前記暗号化処理させる方法は、前記データストリームからのデータ処理が再開される時に、前記異なったデータストリームの各々に対して保存された前記セキュリティコンフィギュレーション情報を読み出させるようにすることを特徴とする請求項47に記載の方法。

【請求項51】

前記割り込み以前に保存された、メッセージ認証コードを含む前記セキュリティコンフィギュレーション情報を更に読み出し、前記割り込まれたセッションが再開されるときに、前記読み出されたメッセージ認証コードから更新したメッセージ認証コードを導出することを特徴とする請求項47に記載の方法。

【請求項1】

暗号化されたデータを保存するメモリシステムにおいて、

不揮発性のフラッシュメモリセルと、

前記セルからの、又は前記セルへのデータストリーム中のデータに対して暗号化処理を実行する回路と、

コントローラであって、暗号化アルゴリズムを用いて、暗号化処理するために、前記回路を設定すると共に前記セルと前記回路を制御し、前記回路が設定された後、前記コントローラの関与なしで、前記データストリーム中のデータが前記回路によって暗号化処理されるようするコントローラと、

を備えることを特徴とするシステム。

【請求項2】

データがページの前記セルに書き込まれ、または前記セルから読取られ、前記回路が各々1ページ未満のデータユニットに暗号化処理を実行し、前記コントローラが前記回路を設定し、前記回路が設定された後、前記回路が、前記コントローラの関与なしにデータの複数のページに暗号化処理を実行することを特徴とする請求項1に記載のシステム。

【請求項3】

前記コントローラが前記回路を設定し、前記データストリームが複数のソース中で選択された前記データソースと、複数の行き先中で選択された前記行き先を持つことを特徴とする請求項1に記載のシステム。

【請求項4】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルから始まり、前記コントローラ又はホスト装置に仕向けられることを特徴とする請求項3に記載のシステム。

【請求項5】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラ又はホスト装置から始まることを特徴とする請求項3に記載のシステム。

【請求項6】

前記コントローラが前記回路を設定し、前記データストリームが前記セルからホスト装置まで、又は前記ホスト装置から前記セルまでであり、前記回路をバイパスすることを特徴とする請求項3に記載のシステム。

【請求項7】

前記コントローラが前記回路を設定し、選択された暗号化アルゴリズムが前記暗号化処理で使用されることを特徴とする請求項1に記載のシステム。

【請求項8】

前記コントローラが前記回路を設定し、前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項1に記載のシステム。

【請求項9】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを、一つ以上の鍵を使用して、複数の連続する段階で暗号化処理することを特徴とする請求項8に記載のシステム。

【請求項10】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを一つ以上の暗号化処理によって、複数の連続する段階で暗号化処理することを特徴とする請求項8に記載のシステム。

【請求項11】

暗号化されたデータを保存するメモリカードにおいて、

不揮発性のフラッシュメモリセルと、

前記セルからの、又は前記セルへのデータストリーム中のデータに対して暗号化処理を実行する回路と、

コントローラであって、暗号化アルゴリズムを用いて、暗号化処理するために、前記回路を設定すると共に前記セルと前記回路を制御し、前記回路が設定された後、前記コントローラの関与なしで、前記データストリーム中のデータが前記回路によって暗号化処理されるようするコントローラと、

を備え、

前記メモリセル、前記回路および前記コントローラは、カード中に密閉されていることを特徴とするカード。

【請求項12】

データがページで前記セルに書き込まれ、または前記セルから読み出され、前記回路が各々1ページ未満のデータユニットに暗号化処理を実行し、前記コントローラが前記回路を設定し、前記回路が設定された後、前記コントローラの関与なしで、前記回路がデータの複数ページに暗号化処理を実行することを特徴とする請求項11に記載のカード。

【請求項13】

前記コントローラが前記回路を設定し、前記データストリームが複数のソース中で選択されたデータソースと、複数の行き先中で選択された行き先を持つことを特徴とする請求項11に記載のカード。

【請求項14】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルから始まり、前記コントローラ又はホスト装置に仕向けられることを特徴とする請求項13に記載のカード。

【請求項15】

前記コントローラが前記回路を設定し、前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラ又はホスト装置から始まることを特徴とする請求項13に記載のカード。

【請求項16】

前記コントローラが前記回路を設定し、前記データストリームが前記セルからホスト装置まで、または前記ホスト装置から前記セルまでであり、前記回路をバイパスすることを特徴とする請求項13に記載のカード。

【請求項17】

前記コントローラが前記回路を設定し、選択された暗号化アルゴリズムが暗号化および/または復号で使用されることを特徴とする請求項11に記載のカード。

【請求項18】

前記コントローラが前記回路を設定し、前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項11に記載のカード。

【請求項19】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを、一つ以上の鍵を使用して、複数の連続する段階で暗号化処理することを特徴とする請求項18に記載のカード。

【請求項20】

前記設定後に前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを一つ以上の暗号化処理によって、複数の連続する段階で暗号化処理することを特徴とする請求項18記載にカード。

【請求項21】

暗号化されたデータを保存するメモリカードにおいて、

不揮発性のフラッシュメモリセルと、

前記セルからの、又は前記セルへのデータストリーム中のデータに対して暗号化処理を実行する回路と、

データをページで前記セルに書き込ませ、または、前記セルから読み出させるコントローラを備え、

前記回路は、各々1ページ未満のデータユニットに暗号化処理を実行し、

前記コントローラの関与なしで、前記データストリームの1ページ以上が暗号化処理され、複数のソース中で選択されたデータソースと複数の行き先中で選択された行き先を用いて、書き込まれ、又は、読み出される、

ことを特徴とするメモリカード。

【請求項22】

セルおよび暗号化回路を制御するコントローラを有するメモリシステムの不揮発性のフラッシュメモリセルにおけるデータを暗号化および/または復号する方法において、

暗号化アルゴリズムを用いて、前記セルからの、又は前記セルへのデータストリーム中のデータに暗号化処理を実行する回路を設定するためにコントローラを用いるステップと、

前記回路が設定された後に前記コントローラの関与なしで、前記データストリーム中のデータが、前記回路によって暗号化処理されるステップと、

を含むことを特徴とする方法。

【請求項23】

データがページで前記セルに書き込まれ、または前記セルから読み出され、前記回路が各々1ページ未満のデータユニットに暗号化処理を実施し、前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、前記回路が設定された後、前記コントローラの関与なしで前記回路がデータの複数のページに暗号化処理することを特徴とする請求項22に記載の方法。

【請求項24】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリームが複数のソース中で選択されたデータソースおよび複数の行き先中で選択された行き先を有することを特徴とする請求項22に記載の方法。

【請求項25】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリーム中のデータが前記セルから始まり、前記コントローラあるいはホスト装置に仕向けられることを特徴とする請求項24に記載の方法。

【請求項26】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラあるいはホスト装置から始まることを特徴とする請求項24に記載の方法。

【請求項27】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記データストリームが、前記セルからホスト装置まで、又は前記ホスト装置から前記セルまでであって、前記回路をバイパスすることを特徴とする請求項24に記載の方法。

【請求項28】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

選択した暗号化アルゴリズムは、前記暗号化処理に使用されることを特徴とする請求項22に記載の方法。

【請求項29】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記設定後、前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項22に記載の方法。

【請求項30】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記設定後、前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で、一つ以上の鍵を使用して暗号化処理することを特徴とする請求項29に記載の方法。

【請求項31】

前記コントローラを使用する方法は、前記コントローラを用いて前記回路を設定し、

前記設定後、前記コントローラの関与なしで、前記回路が前記データストリーム中のデータを複数の連続する段階で、一つ以上の暗号化処理を使用して暗号化処理することを特徴とする請求項29に記載の方法。

【請求項32】

セルおよび暗号化回路を制御するコントローラを有するメモリシステムの不揮発性のフラッシュメモリセルにおけるデータを暗号化および/または復号する方法において、

前記コントローラの関与なしで、前記回路を用いて1ページ以上のデータを暗号化処理するステップであって、データがページ単位で書き込まれ、または読み出され、また、前記回路が、各々1ページ未満のデータユニットに暗号化処理をするステップと、

前記コントローラの関与なしで、複数のソース中で選択されたデータソースと、複数の行き先中で選択された行き先を有するように、前記データストリームを制御するステップと、

を含むことを特徴とする方法。

【請求項33】

前記暗号化回路を設定することをさらに含み、前記暗号化処理および前記制御が、前記回路の設定によって可能にされることを特徴とする請求項32に記載の方法。

【請求項34】

前記回路を設定することで、複数の暗号化アルゴリズム中で一つ以上の暗号化アルゴリズムの選択が可能となり、前記コントローラの関与なしに、前記選択された暗号化アルゴリズムを使用する前記回路によって、前記データストリーム中のデータが暗号化処理されることを特徴とする請求項33に記載の方法。

【請求項35】

前記回路が設定され、前記データストリーム中のデータが前記セルから始まり、前記コントローラ又はホスト装置に仕向けられることを特徴とする請求項33に記載の方法。

【請求項36】

前記回路が設定され、前記データストリーム中のデータが前記セルに仕向けられ、前記コントローラ又はホスト装置から始まることを特徴とする請求項33に記載の方法。

【請求項37】

前記回路が設定され、前記データストリームが前記セルからホスト装置まで又は前記ホスト装置から前記セルまでであって、前記回路をバイパスすることを特徴とする請求項33に記載の方法。

【請求項38】

前記回路が設定され、前記設定後は、前記コントローラの関与なしに、前記回路が前記データストリーム中のデータを複数の連続する段階で暗号化処理することを特徴とする請求項33に記載の方法。

【請求項39】

前記回路が設定され、前記設定後は、前記コントローラの関与なしに、前記回路が前記データストリーム中のデータを、一つ以上の鍵を使用して、複数の連続する段階で暗号化処理することを特徴とする請求項38に記載の方法。

【請求項40】

前記回路が設定され、前記設定後は、前記コントローラの関与なしに、前記回路が前記データストリーム中のデータを、一つ以上の暗号化処理によって複数の連続する段階で暗号化処理することを特徴とする請求項38に記載の方法。

【請求項41】

暗号化されたデータ保存用のメモリシステムにおいて、

不揮発性のフラッシュメモリセルと、

前記セルから又は前記セルへの一つ以上のデータストリーム中のデータに暗号化処理を実行する回路と、

前記セルと前記回路を制御し、異なったデータストリーム中のデータがインターリーブ方式で暗号化処理されるコントローラを備え、

前記セルからデータをアクセスするための少なくとも1つのセッションは、他のセッションによって割り込まれ、

前記コントローラはセッションのセキュリティコンフィギュレーション情報を、前記割り込み前に保存させ、該情報は前記割り込み後に読み出すことができることを特徴とするシステム。

【請求項42】

前記セキュリティコンフィギュレーション情報は、データのソースあるいは行き先に関連する情報、暗号化鍵、暗号化アルゴリズム、および/またはメッセージ認証コードを含むことを特徴とする請求項41に記載のシステム。

【請求項43】

前記コントローラは前記セッションの再開時に、前記セッション用に保存された前記セキュリティコンフィギュレーション情報を読み出させることを特徴とする請求項41に記載のシステム。

【請求項44】

前記コントローラは、一つ以上のデータストリームの各々に対してセキュリティコンフィギュレーション情報を保存させ、割り込み後に前記情報が読み出させることを特徴とする請求項41に記載のシステム。

【請求項45】

前記データストリームからのデータの処理が再開される時に、前記コントローラは、一つ以上のデータストリームの各々に対して保存された前記セキュリティコンフィギュレーション情報を読み出させることを特徴とする請求項44に記載のシステム。

【請求項46】

前記コントローラは、前記割り込み以前に保存された、メッセージ認証コードを含む前記セキュリティコンフィギュレーション情報を読み出し、前記割り込まれたセッションが再開されるときに、前記読み出されたメッセージ認証コードから更新したメッセージ認証コードを導出することを特徴とする請求項41に記載のシステム。

【請求項47】

不揮発性のフラッシュメモリセルと暗号化回路を含む、暗号化されたデータ保存用のメモリシステムにおけるデータを処理する方法において、

前記セルからの、又は前記セルへのデータストリーム中のデータに暗号化処理を行うために前記回路を用いるステップと、

インターリーブ方式で、異なったデータストリーム中のデータを前記回路に暗号化処理させるステップであって、前記セルへの、または前記セルからのデータを処理する、少なくとも1セッションが、他のセッションに割り込まれ、前記少なくとも前記1セッションのセキュリティコンフィギュレーション情報が、前記割り込み前に保存され、前記割り込み後に読み出すことができるステップと、

を含むことを特徴とする方法。

【請求項48】

前記セキュリティコンフィギュレーション情報は、データのソースあるいは行き先に関連する情報、暗号化鍵、暗号化アルゴリズム、および/またはメッセージ認証コードを含むことを特徴とする請求項47に記載の方法。

【請求項49】

前記暗号化処理させる方法が、前記異なったデータストリームの各々に対して、前記セキュリティコンフィギュレーション情報を保存させ、前記割り込み後、前記情報が読み出せることを特徴とする請求項47に記載の方法。

【請求項50】

前記暗号化処理させる方法は、前記データストリームからのデータ処理が再開される時に、前記異なったデータストリームの各々に対して保存された前記セキュリティコンフィギュレーション情報を読み出させるようにすることを特徴とする請求項47に記載の方法。

【請求項51】

前記割り込み以前に保存された、メッセージ認証コードを含む前記セキュリティコンフィギュレーション情報を更に読み出し、前記割り込まれたセッションが再開されるときに、前記読み出されたメッセージ認証コードから更新したメッセージ認証コードを導出することを特徴とする請求項47に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公表番号】特表2008−524969(P2008−524969A)

【公表日】平成20年7月10日(2008.7.10)

【国際特許分類】

【出願番号】特願2007−548469(P2007−548469)

【出願日】平成17年12月21日(2005.12.21)

【国際出願番号】PCT/US2005/046586

【国際公開番号】WO2006/071725

【国際公開日】平成18年7月6日(2006.7.6)

【出願人】(507208288)サンディスク コーポレーション (11)

【出願人】(507208554)ディスクレティクス テクノロジーズ リミテッド (2)

【氏名又は名称原語表記】DISCRETIX TECHNOLOGIES LTD.

【Fターム(参考)】

【公表日】平成20年7月10日(2008.7.10)

【国際特許分類】

【出願日】平成17年12月21日(2005.12.21)

【国際出願番号】PCT/US2005/046586

【国際公開番号】WO2006/071725

【国際公開日】平成18年7月6日(2006.7.6)

【出願人】(507208288)サンディスク コーポレーション (11)

【出願人】(507208554)ディスクレティクス テクノロジーズ リミテッド (2)

【氏名又は名称原語表記】DISCRETIX TECHNOLOGIES LTD.

【Fターム(参考)】

[ Back to top ]