インサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法

【課題】トレース対象の命令の実行が同時に生じた場合に、正確な命令発生タイミングを把握すること

【解決手段】タイミング情報生成回路131は、第1CPUコア111、第2CPUコア121の各々からのトレースデータの出力と同期して出力されるプロセッサ1(2)出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力する。トレースメッセージ生成回路132は、各トレースデータと、各トレースデータ取得時のタイムスタンプと、タイミング情報と、を対応付けたトレースメッセージを生成する。トレースメモリ書き込み制御回路144は、トレースメッセージ生成回路132が生成したトレースメッセージをトレースメモリ150に書き込む。

【解決手段】タイミング情報生成回路131は、第1CPUコア111、第2CPUコア121の各々からのトレースデータの出力と同期して出力されるプロセッサ1(2)出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力する。トレースメッセージ生成回路132は、各トレースデータと、各トレースデータ取得時のタイムスタンプと、タイミング情報と、を対応付けたトレースメッセージを生成する。トレースメモリ書き込み制御回路144は、トレースメッセージ生成回路132が生成したトレースメッセージをトレースメモリ150に書き込む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、インサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法に関する。

【背景技術】

【0002】

近年、家電製品等の各製品の機能増加に伴い、当該製品を制御するマイクロコンピュータが高性能化してきている。特に複数のCPU(Central Processing Unit)コア、メモリ等を備え、処理時間を短縮するマルチコア型のマイクロコンピュータが広く使用されるようになってきている。これに伴い、当該マイクロコンピュータを使用したハードウェア及びソフトウェアをデバッグする開発支援装置(以降、インサーキットエミュレータと記載する。)の機能も複雑化してきている。

【0003】

インサーキットエミュレータでは、マイクロコンピュータのマルチコア化に伴い、トレース機能及びタイムスタンプ機能の高性能化が必要となる。トレース機能とは、ソフトウェア開発時に被実行プログラムの実行結果を格納する機能である。タイムスタンプ機能とは、プログラムの開始からトレース対象に設定されたイベントの発生時点までの累積時間、または直前のトレース対象イベントが実行されてからの経過時間を記録し、当該時間情報をプログラムの実行結果と関連付けて記録する機能である。マイクロコンピュータ内にある複数のCPUコアのうち、どのCPUコアがトレース対象イベントを実行した場合であっても、タイムスタンプ機能は、正確にタイムスタンプを生成することが求められる。

【0004】

上述したインサーキットエミュレータに関連する技術を以下に説明する。特許文献1には、タイムスタンプ取得回路の一態様が開示されている。はじめに、図17を参照して一般的なデバッグ環境の構成を説明する。図17は、特許文献1に記載のタイムスタンプ取得回路を一般的なデバッグ環境に組み込んだ例を示す図である。

【0005】

ユーザーターゲットシステム300は、プログラム開発対象のマイクロコンピュータを搭載するシステムである。デバッグチップ320は、プログラム開発対象のマイクロコンピュータが持つ全機能を実現するチップである。デバッグチップ320は、後述するタイムスタンプカウンタ制御回路330を内部に実装している。デバッグチップ320は、ソケット310を介して電気的にユーザーターゲットシステム300と接続されている。デバッグチップ320は、エミュレーションプローブ340を介して、エミュレータ本体350の構成要素であるエミュレーション制御回路360と電気的に接続されている。エミュレーション制御回路360は、後述するオーバーフローカウンタ制御回路370を有している。

【0006】

エミュレータ本体350は、エミュレーション制御回路360と、トレースメモリ380と、ホストI/F390とを有している。これらは、別々のチップに実装されている。エミュレータ本体350は、ホストPC400と、USBケーブル410などによって接続される。ホストPC400では、デバッガプログラムが実行される。ユーザの操作を受け付けるデバッガプログラムは、ホストI/F390を介してエミュレータ本体350と通信を行うことができる。

【0007】

トレースデータの収集は、デバッガプログラムが実行されるホストPC400からの指示によって開始する。また、ホストPC400からの要求により、トレースメモリ380に保存されたトレースメッセージを、エミュレータ本体350からホストPC400へ読み出すことが可能である。

【0008】

図18は、上述のタイムスタンプカウンタ制御回路330及びオーバーフローカウンタ制御回路370を有するタイムスタンプ取得回路の構成を示す図である。当該タイムスタンプ取得回路は、タイムスタンプカウンタ制御回路330と、オーバーフローカウンタ制御回路370とを備える。タイムスタンプカウンタ制御回路330は、複数のプロセッサの各々からトレースデータを収集し、そのトレースデータにタイムスタンプを付加して、トレースメモリ380に書き込みを行う。

【0009】

この複数のプロセッサは、第1CPUコア410を含む第1プロセッサ420と、第2CPUコア430を含む第2プロセッサ440と、から構成される。第1プロセッサ420、及び第2プロセッサ440は、各々が内蔵する第1CPUコア410、及び、第2CPUコア430がトレース対象命令を実行した場合に、トレース対象命令実行検出信号及びトレースデータを出力する。タイムスタンプカウンタ制御回路330には、トレース対象命令実行検出信号及びトレースデータが入力される。

【0010】

タイムスタンプカウンタ制御回路330は、トレースメッセージ生成回路331と、タイムスタンプカウンタ332と、トレースメッセージバッファ333とを有している。タイムスタンプカウンタ332は、トレースメッセージ生成回路331からリセット信号(RES)を受信すると初期化され、ゼロから計数を開始する。タイムスタンプカウンタ332は、所定のクロックに同期して、一定の時間間隔でカウント動作を行う。タイムスタンプカウント値(タイムスタンプカウンタ332のカウントした値)は、トレースメッセージ生成回路331に送出される。タイムスタンプカウンタ332は、フルカウントまで計数し、オーバーフローすると、キャリー信号をOVFカウンタ371及びトレースメッセージ生成回路331に出力する。トレースメッセージ生成回路331は、キャリー信号が出力されると、OVFフラグ334を1に設定する。

【0011】

トレースメッセージ生成回路331は、トレース対象命令実行検出信号を受信した場合、タイムスタンプカウンタ332からカウント値をリードし、OVFフラグ334がセットされている場合にはOVFカウント値要求信号をOVFカウント値生成回路372に送信する。そして、トレースメッセージ生成回路331は、トレースメッセージを生成し、当該メッセージをトレースメッセージバッファ333にエントリする。

【0012】

OVFカウンタ371は、キャリー信号が入力される度にカウントアップするカウンタである。OVFカウンタ371は、トレースメッセージ生成回路331からリセット信号(RES)を受信すると初期化され、0から計測を開始する。OVFカウント値生成回路372は、OVFカウント値要求信号を受け取ると、OVFカウンタ371の値をOVFカウント値バッファ373に供給する。

【0013】

トレースメッセージ生成回路331は、トレースメッセージの作成後にリセット信号(RES)をアクティブにする。

【0014】

トレースメモリ書き込み制御回路374は、トレースメッセージバッファ333内のトレースメッセージを順次トレースメモリ380に書き込む。この際、トレースメモリ書き込み制御回路374は、書き込み対象のトレースメッセージ内のオーバーフローフラグがオフの場合、そのままトレースメッセージをトレースメモリ380に書き込む。書き込み対象のトレースメッセージ内のオーバーフローフラグがオンの場合、トレースメモリ書き込み制御回路374は、OVFカウント値バッファ373の先頭のOVFカウント値を先にトレースメモリ380に書き込み、その後トレースメッセージを書き込む。

【0015】

図19は、特許文献1に記載のトレースメモリ書き込み制御回路374の動作を説明するためのデータ構造図である。図19は、トレースメッセージバッファ333、OVFカウント値バッファ373、及びトレースメモリ380におけるデータ構造の具体例を示している。トレースメッセージバッファ333には六つのエントリがあり、OVFカウント値バッファ373には二つのエントリがある。トレースメッセージバッファ333の四つ目のエントリにはオーバーフローフラグがセット(1個目)されている。そのため、トレースメッセージバッファ333の四つ目のエントリ入力前に、オーバーフローが生じていることがわかる。また、トレースメッセージバッファ333の六つ目のエントリにはオーバーフローフラグがセット(2個目)されている。そのため、トレースメッセージバッファ333の六つ目のエントリ入力前に、2回目のオーバーフローが生じていることがわかる。このオーバーフローのタイミングから、ユーザは、各イベントが生じたタイミングを把握することができる。

【0016】

なお、特許文献2には、マイクロプロセッサシステムにおける共有メモリの制御に関する技術が開示されている。本技術では、マイクロシステムからの制御内容を時系列に沿って表示する手法が開示されている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2010−128681号公報

【特許文献2】特開平5−265795号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

マイクロコンピュータのマルチコア環境において、複数のCPUコアが同時にトレース対象命令を実行する場合がある。しかしながら、一般に、同時に命令が実行されたか否かを考慮したトレース書き込みが行われていない。そのため、デバッガが、トレースメモリ内のメッセージを参照しても、正しいタイムスタンプ値が参照できない恐れがある。

【0019】

例えば、特許文献1に記載の構成において、第1CPUコア410と第2CPUコア430とが同時にトレース対象イベントを実行したことを想定する。しかし、トレースメモリ書き込み制御回路374にトレースメッセージを入力する場合に、これらのイベントが同時に発生したことを通知する手段がない。そのため、トレースメモリ書き込み制御回路374は、便宜的に先にトレースメッセージバッファ333に入力されたトレースメッセージを、先に発生したイベントにかかるメッセージと認識する。さらに、トレースメモリ書き込み制御回路374は、便宜的に後にトレースメッセージバッファ333に入力されたトレースメッセージを、後に発生したイベントにかかるメッセージと認識する。ここで、両トレースメッセージ内のOVFフラグが設定される場合がある。この場合、トレースメモリ書き込み制御回路374は、先に入力されたトレースメッセージの書き込み前にOVFカウント値バッファ373から先頭のOVFカウント値を読み込んでトレースメモリ380に書き込む。さらに、トレースメモリ書き込み制御回路374は、後に入力されたトレースメッセージの書き込み前にOVFカウント値バッファ373から先頭のOVFカウント値を読み込んでトレースメモリ380に書き込む。しかしながら、先のOVFカウント値の書き込みによりOVFカウント値バッファ273が空になる可能性がある。そのため、トレースメモリ書き込み制御回路374は、不定値をトレースメモリ380に書き込む恐れがある。

【0020】

なお、特許文献2でも、同一のタイミングで共有メモリに書き込むことが想定されていないため、正確なタイムスタンプ値を持つトレースデータを参照することができない。

【0021】

このように、上記した技術では、トレース対象の命令の実行が同時に生じた場合に、正確な命令発生タイミングを把握することができない恐れがあった。

【課題を解決するための手段】

【0022】

本発明にかかるインサーキットエミュレータの一態様は、

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、タイムスタンプをカウントするタイムスタンプカウンタがオーバーフローしたことを示すオーバーフローフラグと、前記タイミング情報と、を対応付けたトレースメッセージを生成するトレースメッセージ生成回路と、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込みを行う制御回路であって、前記オーバーフローフラグの設定時には、同じタイミング情報を持つトレースメッセージ群をトレースメモリに書き込む前にオーバーフローカウント値をトレースメモリに書き込み、その後に同じタイミング情報を持つトレースメッセージ群をトレースメモリに書き込む、トレースメモリ書き込み制御回路と、を備えるものである。

【0023】

本発明にかかるトレースメモリ制御システムの一態様は、

第1、第2プロセッサの各々からのトレースデータと、各トレースデータ取得時のタイムスタンプと、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報と、を対応付けたトレースメッセージを出力順に受け付け、トレースメモリに書き込むトレースメモリ書き込み制御回路を備えた装置と、

前記トレースメモリから各トレースメッセージを読み出し、各トレースメッセージ内の前記タイミング情報に基づき、他のトレースメッセージと出力タイミングが異なるかを判別できるように各トレースメッセージを表示する表示情報を生成するデバッグプログラムを実行するホストコンピュータと、を備える、ものである。

【0024】

本発明にかかるトレースメッセージ生成装置の一態様は、

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、前記タイミング情報に基づいて、各トレースメッセージを表示する制御装置に対し、生成したトレースメッセージを供給する、トレースメッセージ生成回路と、を備える、ものである。

【0025】

本発明にかかるトレースメッセージ処理方法の一態様は、

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を生成し、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込む、ものである。

【0026】

本発明では、トレースデータの出力と同期して出力される出力イネーブル信号から、トレースデータの出力タイミングの異同を示すタイミング情報が生成される。トレースメッセージは、タイミング情報とトレースデータが関連付けられてトレースメモリ内に格納される。そして、表示時には、トレースメッセージ内のタイミング情報を参照することにより、出力タイミングの異同を判別できる表示画面が生成される。これにより、トレース対象の命令の実行が同時に生じた場合であっても、正確な発生タイミングを把握することができる。

【発明の効果】

【0027】

本発明によれば、トレース対象の命令の実行が同時に生じた場合であっても、正確な命令発生タイミングを把握することができるインサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法を提供することができる。

【図面の簡単な説明】

【0028】

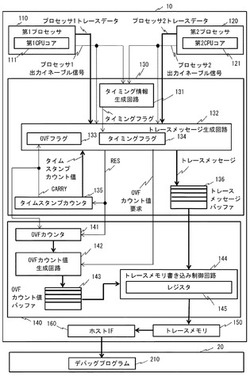

【図1】実施の形態1にかかるインサーキットエミュレータの構成を示すブロック図である。

【図2】実施の形態1にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図3】実施の形態1にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図4】実施の形態1にかかるタイミング情報生成回路の動作を示すフローチャートである。

【図5】実施の形態1にかかるトレースメッセージ生成回路の動作を示すフローチャートである。

【図6】実施の形態1にかかるオーバーフローカウント値生成回路の動作を示すフローチャートである。

【図7】実施の形態1にかかるトレースメモリ書き込み制御回路の動作を示すフローチャートである。

【図8】実施の形態1にかかるトレースメモリ書き込み制御回路の動作を示すフローチャートである。

【図9】実施の形態1にかかるインサーキットエミュレータの動作を示す概念図である。

【図10】実施の形態1にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図11】実施の形態2にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図12】実施の形態2にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図13】実施の形態3にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図14】実施の形態4にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図15】実施の形態4にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図16】実施の形態4にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図17】一般的なデバッグ環境を示すブロック図である。

【図18】特許文献1に記載のタイムスタンプカウンタ制御回路の構成を示すブロック図である。

【図19】特許文献1に記載のトレースメモリ書き込み制御回路の動作を示す図である。

【発明を実施するための形態】

【0029】

<実施の形態1>

以下、図面を参照して本発明の実施の形態について説明する。図1は、本実施の形態にかかるインサーキットエミュレータシステムの構成を示すブロック図である。当該当該インサーキットエミュレータシステムは、インサーキットエミュレータ10と、ホストコンピュータ20と、を備える。

【0030】

インサーキットエミュレータ10は、第1プロセッサ110と、第2プロセッサ120と、タイムスタンプカウンタ制御回路130と、オーバーフローカウンタ制御回路140と、トレースメモリ150と、ホストIF(インターフェイス)160と、を備える。

【0031】

第1プロセッサ110、第2プロセッサ120、及びタイムスタンプ取得回路130は、同一チップ上に実装することができ、デバッグチップとして動作する。タイムスタンプカウンタ制御回路130は、タイミング情報生成回路131と、トレースメッセージ生成回路132と、タイムスタンプカウンタ135と、トレースメッセージバッファ136と、を備える。なお、タイムスタンプカウンタ制御回路130内の各処理部には、クロック信号が入力される。

【0032】

第1プロセッサ110及び第2プロセッサ120は、各々が内蔵する第1CPUコア111、第2CPUコア121がトレース対象命令を実行した場合、出力イネーブル信号(プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号)をタイミング情報生成回路131、及びトレースメッセージ生成回路132に出力し、トレースデータをトレースメッセージ生成回路132に出力する。ここで、第1プロセッサ110、第2プロセッサ120が出力するトレースデータには、第1プロセッサ110、第2プロセッサ120のどちらから出力されているかを示すプロセッサ識別子が含まれる。

【0033】

タイミング情報生成回路131は、第1プロセッサ110、または第2プロセッサ120のトレースデータ出力タイミングを示すタイミング情報を出力する。本実施の形態において、タイミング情報生成回路131は、タイミング情報として1ビットのビット値であるタイミングフラグを出力する。タイミング情報生成回路131は、プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号の少なくとも一方が入力されたタイミングにタイミングフラグを反転する。

【0034】

タイミング情報生成回路131の内部構成の一例を図2に示す。図示するようにタイミング情報生成回路131は、OR回路171と、AND回路172と、D型フリップフロップ173と、NOT回路174と、を備える。各回路の出力信号を図3のタイミングチャートに示す。

【0035】

OR回路171には、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号が入力される。OR回路171は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベル("1"、以下同様である。)である場合にハイレベルをAND回路172に出力し、それ以外の場合(両信号がいずれもロウレベル("0"以下同様である。)である場合)にロウレベルをAND回路172に出力する(図3参照)。

【0036】

AND回路172には、クロック信号と、OR回路171からの出力信号が入力される。AND回路172は、両入力信号が共にハイレベルである場合にD型フリップフロップ173のクロック入力端子にハイレベルを供給し、それ以外の場合にD型フリップフロップ173のクロック入力端子にロウレベルを供給する(図3参照)。

【0037】

D型フリップフロップ173のクロック入力端子には、AND回路172の出力信号が入力される。D型フリップフロップ173の入力端子Dには、D型フリップフロップ173の出力信号の反転信号(NOT回路174の出力信号)が入力される。D型フリップフロップ173は、一般的なディレイ型のフリップフロップと同様の動作を行う。D型フリップフロップ173は、出力信号をトレースメッセージ生成回路132にタイミングフラグ信号として供給する。

【0038】

NOT回路174は、D型フリップフロップ173の出力信号を反転(すなわち、ロウレベルであればハイレベルに変換し、ハイレベルであればロウレベルに変換する。)し、反転信号をD型フリップフロップ173の入力端子Dに供給する。

【0039】

改めて、図3を参照し、各回路の出力信号について説明する。OR回路171は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベルである場合にハイレベルをAND回路172に出力する。そのため、OR回路171は、t2〜t8、t9〜t10、t11〜t12にハイレベルを出力する。

【0040】

AND回路172は、クロック信号とOR回路171の出力信号が共にハイレベルである場合にハイレベルを出力する。よって、AND回路172は、t2〜t2.5(タイミングt2とタイミングt3の中間タイミング、以下同様の記載を行う。)、t3〜t3.5、t4〜t4.5、t5〜t5.5、t6〜t6.5、t7〜t7.5、t9〜t9.5、t11〜t11.5にハイレベルを出力する。

【0041】

D型フリップフロップ173では、前述のようにAND回路172の出力信号がクロック入力端子に供給され、自身の出力信号の反転信号が入力端子Dに供給される。そのため、D型フリップフロップ173は、t2〜t3、t4〜t5、t6〜t7、t9〜t11にハイレベルを出力する。これにより、D型フリップフロップ173の出力信号、すなわちタイミングフラグは、図3に示すように、第1プロセッサ110及び第2プロセッサ130の少なくとも一方のトレース出力タイミングで値を反転している。

【0042】

再び、図1を参照する。トレースメッセージ生成回路132は、OVFフラグ133と、タイミングフラグ134と、を保持する。トレースメッセージ生成回路132は、タイミング情報生成回路131から入力されるタイミングフラグ134をトレースデータ毎に保持する。さらに、トレースメッセージ生成回路132は、タイムスタンプカウンタ135からキャリー信号が入力された場合に、OVFフラグ133をオンに設定する。

【0043】

トレースメッセージ生成回路132は、プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号の一方または双方を受信した場合、OVFフラグ133がオンに設定されているか否かを判定する。OVFフラグ133がオンに設定されている場合、OVFカウント値要求信号をOVFカウント値生成回路142に供給する。OVFカウント値要求信号とは、OVFカウント値生成回路142に対し、OVFカウンタ141のカウント値を用いてOVFカウント値を生成し、生成値をOVFカウント値バッファ143に格納することを要求する信号である。

【0044】

トレースメッセージ生成回路132は、プロセッサ1出力イネーブル信号を受信した場合、第1プロセッサ110からトレースデータ、タイムスタンプカウンタ135からタイムスタンプカウント値、タイミング情報生成回路131からタイミングフラグを受信する。同様に、トレースメッセージ生成回路32は、プロセッサ2出力イネーブル信号を受信した場合、第2プロセッサ120からトレースデータ、タイムスタンプカウンタ135からタイムスタンプカウント値、タイミング情報生成回路131からタイミングフラグを受信する。

【0045】

トレースメッセージ生成回路132は、トレースデータと、タイムスタンプカウント値と、タイミングフラグと、OVFフラグ133の値と、を関連付けたトレースメッセージを生成する。

【0046】

トレースメッセージバッファ136は、FIFO(First In First Out)型の記憶部である。

【0047】

トレースメッセージ生成回路132は、トレースメッセージの作成後にOVFフラグ133の値をクリア(オフ)し、カウンタリセット信号(RES)をタイムスタンプカウンタ135及びOVFカウンタ141に供給する。カウンタリセット信号は、タイムスタンプカウンタ135のカウント値、及びOVFカウンタ141のカウント値をリセットする信号である。トレースメッセージ生成回路132は、生成したトレースメッセージをトレースメッセージバッファ136に入力する。

【0048】

なお、トレースメッセージ生成回路132は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号を受信した場合、プロセッサ毎のトレースメッセージを同時に作成し、トレースメッセージバッファ136に入力する。

【0049】

タイムスタンプカウンタ135は、クロック信号に同期して、一定の時間間隔でカウント動作を行う。タイムスタンプカウンタ135は、カウント値をトレースメッセージ生成回路132に供給する。タイムスタンプカウンタ135は、カウント値が上限値に到達する(オーバーフローする)と、キャリー信号をトレースメッセージ生成回路132及びオーバーフローカウンタ制御回路140に供給する。タイムスタンプカウンタ135は、トレースメッセージ生成回路132からカウンタリセット信号を受信した場合に、カウント値をリセット(0に設定)する。

【0050】

オーバーフローカウンタ制御回路140は、OVFカウンタ141と、OVFカウント値生成回路142と、OVFカウント値バッファ143と、トレースメモリ書き込み制御回路144と、を備える。トレースメモリ書き込み制御回路144は、内部にレジスタ145を有する。

【0051】

OVFカウンタ141は、トレースメッセージ生成回路132からカウンタリセット信号(RES)を受信すると初期化され、ゼロから計数を開始する。OVFカウンタ141は、タイムスタンプカウンタ135から出力されるキャリー信号の入力回数を計数する。

【0052】

OVFカウント値生成回路142は、トレースメッセージ生成回路132からOVFカウント値要求信号が入力される(アクティブになる)と、OVFカウンタ141のカウント値を読み出す。OVFカウント値生成回路142は、読み出したカウント値をOVFカウント値バッファ143に入力する。

【0053】

OVFカウント値バッファ143は、FIFO(First In First Out)型の記憶部である。OVFカウント値バッファ143は、OVFカウント値生成回路142によって生成された順序でカウント値を保持する。

【0054】

トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136からトレースメッセージを順次読み出し、読み出したトレースメッセージをトレースメモリ150に書き込む回路である。

【0055】

トレースメモリ書き込み制御回路144は、内部にレジスタ145を有する。レジスタ145は、トレースメモリ書き込み制御回路144が直近に書き込んだトレースメッセージに含まれるタイミング情報(本実施の形態ではタイミングフラグの値)を保持する。トレースメモリ書き込み制御回路144は、これから書き込むトレースメッセージ内のOVFフラグを抽出し、オンに設定されているか否かを判定する。さらに、トレースメモリ書き込み制御回路144は、これから書き込むトレースメッセージ内のタイミングフラグの値と、レジスタ145が保持するタイミングフラグの値と、を比較する。

【0056】

OVFフラグがオンであり、タイミングフラグの値が一致しない場合、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143の先頭に位置するカウント値を取得する。トレースメモリ書き込み制御回路144は、取得したカウント値をトレースメモリ150に書き込む。その後、トレースメモリ書き込み制御回路144は、書き込み対象のトレースメッセージをトレースメモリ150に書き込む。

【0057】

一方、OVFフラグがオンではない場合、またはタイミングフラグの値が一致する場合、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143からカウント値を取得しない。トレースメモリ書き込み制御回路144は、書き込み対象のトレースメッセージをトレースメモリ150に書き込む。

【0058】

トレースメモリ150は、トレースメモリ書き込み制御回路144から書き込まれるトレースメッセージを格納する記憶部である。

【0059】

ホストIF160は、トレースメモリ150と、デバッグプログラム210と、のデータのやり取りを仲介する処理部である。

【0060】

ホストコンピュータ20は、デバッグプログラム210を実行する。デバッグプログラム210は、第1CPUコアおよび第2CPUコアでのデバッグ対象のプログラムの実行、停止を指示したり、トレースメモリ150に書き込まれたトレースメッセージを取り込んでホストコンピュータの表示装置へ渡し、トレースメッセージの内容を表示させる。ホストコンピュータ20は、液晶ディスプレイ等の表示部と一体化された装置、または接続可能に構成された装置である。ホストコンピュータ20は、CPU(Central Processing Unit)やHDD(Hard Disk Drive)等の補助記憶装置、RAM(Random Access Memory)等の不揮発性メモリを有する。デバッグプログラム210は、補助記憶装置内に格納され、実行時にRAMに適宜読み出されてCPUにより実行される。

【0061】

デバッグプログラム210は、前述の表示部に表示する表示メッセージを取得、生成する

【0062】

続いて、図4を参照して、タイミング情報生成回路131の動作を説明する。図4は、本実施の形態にかかるタイミング情報生成回路131の動作を示すフローチャートである。

【0063】

各CPUコアにてユーザプログラムが実行される前に、タイミング情報生成回路131内のタイミングフラグの値をリセットする(S11)。すなわち、はじめにタイミング情報生成回路131が生成するタイミングフラグの値を0(ロウレベル)とする。タイミングフラグの値のリセットは、ライトアクセスを行うことにより実現する。

【0064】

タイミング情報生成回路131は、第1CPUコア110及び第2CPUコア120がユーザプログラムを実行中であるか否かを判定する(S12)。ユーザプログラムの実行中ではない場合(S12:No)、タイミング情報生成回路131は、処理を終了する。

【0065】

ユーザプログラムの実行中である場合(S12:Yes)、タイミング情報生成回路131は、出力イネーブル信号(プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号)が有効("1"、ハイレベル)であるか否かを判定する(S13)。いずれも有効ではない場合、タイミング情報生成回路131は、S12の処理を再度行う。

【0066】

出力イネーブル信号の一方が有効である場合(S13:Yes)、タイミング情報生成回路131は、タイミングフラグを反転する(S14)。

【0067】

続いて、図5を参照して、トレースメッセージ生成回路132の動作を説明する。図5は、トレースメッセージ生成回路132の動作を示すフローチャートである。

【0068】

各CPUコアにてユーザプログラムが実行される前に、タイムスタンプカウンタ135のカウント値、OVFフラグ133、及びOVFカウンタ141をライトアクセスによりリセットする(S21)。

【0069】

トレースメッセージ生成回路132は、第1CPUコア111及び第2CPUコア121がユーザプログラムを実行中であるか否かを判定する(S22)。ユーザプログラムの実行中ではない場合(S22:No)、トレースメッセージ生成回路132は、処理を終了する。

【0070】

ユーザプログラムの実行中である場合(S22:Yes)、トレースメッセージ生成回路132は、出力イネーブル信号(プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号)が有効である否かを判定する(S23)。出力イネーブル信号が有効ではない場合(S23:No)、トレースメッセージ生成回路132は、S22の処理を再度行う。

【0071】

出力イネーブル信号が有効になった場合(S23:Yes)、トレースメッセージ生成回路132は、OVFフラグ133がオンに設定されているか否かを判定する(S24)。OVFフラグ133がオンに設定されている場合(S24:Yes)、トレースメッセージ生成回路132は、OVFカウント値要求信号をOVFカウント値生成回路142に供給する(S25)。

【0072】

OVFフラグ133がオンに設定されていない場合(S24:No)、トレースメッセージ生成回路132は、OVFカウント値要求信号を出力しない。

【0073】

そして、トレースメッセージ生成回路132は、出力イネーブル信号の受信に応じて、トレースデータ、タイムスタンプカウント値、及びタイミングフラグを取得する(S26)。トレースメッセージ生成回路132は、トレースデータと、タイムスタンプカウント値と、タイミングフラグと、OVFフラグ133の値と、を関連付けたトレースメッセージを生成する(S27)。

【0074】

トレースメッセージ生成回路132は、OVFフラグ133の値をクリア(オフ)すると共に、カウンタリセット信号をタイムスタンプカウンタ135及びOVFカウンタ141に供給する(S28)。トレースメッセージ生成回路132は、生成したトレースメッセージをトレースメッセージバッファ136に入力する(S29)。S29の処理の後、トレースメッセージ生成回路132は、S23の処理を再度行う。

【0075】

続いて、図6を参照して、オーバーフローカウント値生成回路142の動作を説明する。図6は、オーバーフローカウント値生成回路142の動作を示すフローチャートである。

【0076】

オーバーフローカウント値生成回路142は、第1CPUコア111及び第2CPUコア121がユーザプログラムを実行中であるか否かを判定する(S31)。ユーザプログラムの実行中ではない場合(S31:No)、オーバーフローカウント値生成回路142は、処理を終了する。

【0077】

ユーザプログラムの実行中である場合(S31:Yes)、オーバーフローカウント値生成回路142は、OVFカウント値要求信号の受信を受け付ける(S32)。OVFカウント値要求信号を受信しない場合(S32:No)、オーバーフローカウント値生成回路142は、S31から処理を再度行う。

【0078】

OVFカウント値要求信号を受信した場合(S32:Yes)、オーバーフローカウント値生成回路142は、OVFカウンタ141からカウント値を取得する(S33)。そして、OVFカウント値生成回路142は、取得したカウント値をOVFカウント値バッファ143に入力する(S34)。その後、オーバーフローカウント値生成回路142は、S32から処理を再度行う。

【0079】

続いて、図7及び図8を参照して、トレースメモリ書き込み制御回路144の動作を説明する。図7及び図8は、トレースメモリ書き込み制御回路144の動作を示すフローチャートである。

【0080】

各CPUコアにてユーザプログラムが実行される前に、タイミング情報生成回路131内のタイミングフラグの値をリセットする(S41)。すなわち、はじめにタイミング情報生成回路131が生成するタイミングフラグを0とする。

【0081】

トレースメモリ書き込み制御回路144は、第1CPUコア111及び第2CPUコア121がユーザプログラムを実行中であるか否かを判定する(S42)。ユーザプログラムの実行中ではない場合(S42:No)、トレースメモリ書き込み制御回路144は、処理を終了する。

【0082】

ユーザプログラムの実行中である場合(S42:Yes)、トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136にトレースメッセージが格納されているか否かを判定する(S43)。トレースメッセージが格納されていない場合(S43:No)、トレースメモリ書き込み制御回路144は、S42から処理を再度行う。

【0083】

トレースメッセージが格納されている場合(S43:Yes)、トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136の先頭からトレースメッセージを取得する(S44)。トレースメモリ書き込み制御回路144は、取得したトレースメッセージからOVFフラグの値を抽出する。トレースメモリ書き込み制御回路144は、抽出したOVFフラグがオンに設定されているか否かを判定する(S45)。

【0084】

OVFフラグがオンに設定されている場合(S45:Yes)、トレースメモリ書き込み制御回路144は、トレースメッセージ内のタイミングフラグの値を抽出する。トレースメモリ書き込み制御回路144は、抽出したタイミングフラグの値と、レジスタ145が保持する値と、を比較する(S46)。両者が一致しない場合(S46:No)、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143の先頭に格納されたカウント値を取得し(S47)、取得したカウント値をトレースメモリ150に書き込む(S48)。そして、トレースメモリ書き込み制御回路144は、トレースメモリ150のアドレスをインクリメントする(S49)。

【0085】

OVFフラグがオンに設定されていない場合(S45:No)、または書き込み対象のトレースメッセージに含まれるタイミングフラグの値とレジスタ145が保持する値とが一致する場合(S46:Yes)、トレースメモリ書き込み制御回路144は、S47〜S49の処理を行わない。

【0086】

トレースメモリ書き込み制御回路144は、書き込み対象のトレースメッセージからタイミングフラグの値を取得し、取得した値をレジスタ145に上書きする(S50)。トレースメモリ書き込み制御回路144は、トレースメッセージをトレースメモリ150に書き込む(S51)。そして、トレースメモリ書き込み制御回路144は、トレースメモリ150のアドレスをインクリメントする(S52)。

【0087】

トレースメモリ書き込み制御回路144は、トレースメモリ150のアドレスのインクリメント(S52)の後に、再度、トレースメッセージバッファ136にトレースメッセージが格納されているか否かを判定する(S43)。

【0088】

次に、図9の模式図を参照して、各処理部の動作を更に説明する。なお、以下の説明において、参考として上述のフローチャート(図4〜図8)の符号も併せて記載する。タイミング情報生成回路131は、上述した方法により、トレースデータの入力毎に反転するタイミングフラグを生成する(S11〜S14)。この際、タイミング情報生成回路131は、どのプロセッサがトレースデータを出力したか、または複数のプロセッサがトレースデータを出力したか、等に関わらずトレースデータの入力毎にタイミングフラグを反転する。トレースメッセージ生成回路132は、トレースデータに、タイミングフラグ、OVFフラグ及びタイムスタンプカウンタのカウント値を関連付けたトレースメッセージを生成する(S27)。

【0089】

図9では、トレースメッセージ2のトレースデータと、トレースメッセージ3のトレースデータと、が同じタイミングで出力されている。この場合、トレースメッセージ2とトレースメッセージ3は、同じタイミングフラグ、同じOVFフラグ、及び同じタイムスタンプカウント値を持つ。同様に、トレースメッセージ4のトレースデータと、トレースメッセージ5のトレースデータと、が同じタイミングで出力されている。この場合、トレースメッセージ4とトレースメッセージ5は、同じタイミングフラグ、同じOVFフラグ、及び同じタイムスタンプカウント値を持つ。

【0090】

トレースメッセージ生成回路132は、生成したトレースメッセージを順次トレースメッセージバッファ136にエントリする。図9の上部には、トレースメッセージバッファ136にエントリされたトレースメッセージが示されている。

【0091】

トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136からトレースメッセージを取得する。トレースメモリ書き込み制御回路144は、OVFフラグが"0"であれば、タイミングフラグの値をレジスタ145に書き込み(S50)、トレースメッセージをトレースメモリ150に書き込む(S51)。図9では、トレースメッセージバッファ136のトレースメッセージ1〜3は、OVFフラグの値が"0"であるため、トレースメモリ150にそのまま書き込まれる。

【0092】

トレースメモリ書き込み制御回路144は、OVFフラグが"1"であれば、取得したトレースメッセージのタイミングフラグと、レジスタ145の値を比較する(S46)。一致しない場合、トレースメモリ書き込み制御回路144は、直近のトレースデータの発生後にタイムスタンプがオーバーフローし、その後にトレースデータが出力されたと判定する。この場合、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143からOVFカウント値を取得し(S47)、取得したOVFカウント値をトレースメモリ150に書き込む(S48)。そして、トレースメモリ書き込み制御回路144は、タイミングフラグの値をレジスタ145に書き込み(S50)、トレースメッセージをトレースメモリ150に書き込む(S51)。

【0093】

図9では、トレースメッセージ4〜6は、保持するOVFフラグの値が"1"である。トレースメッセージ4のタイミングフラグの値は、直近のトレースメッセージのタイミングフラグと一致しない。そのため、トレースメッセージ4は、"OVFカウント値1"の書き込みの後にトレースメモリ150に書き込まれる。

【0094】

トレースメッセージ5のタイミングフラグの値は、直近のトレースメッセージのタイミングフラグと一致している。そのため、トレースメッセージ5は、トレースメッセージ4と同時に出力されたと判定される。ここで、OVFカウント値("1")は、すでにトレースメモリ150に書き込まれている。そのため、トレースメモリ書き込み制御回路144は、タイミングフラグの値をレジスタ145に書き込み(S50)、OVFカウント値を書き込むことなく、トレースメッセージ5をトレースメモリ150に書き込む(S51)。

【0095】

トレースメッセージ6のタイミングフラグの値は、直近のトレースメッセージのタイミングフラグと一致しない。そのため、トレースメッセージ6は、"OVFカウント値2"の書き込みの後にトレースメモリ150に書き込まれる。

【0096】

次に、ホストコンピュータ20によるトレースメモリの読み出し処理について説明する。ホストコンピュータ20上で実行されるデバッグプログラム210は、第1プロセッサ110及び第2プロセッサ120によるプログラム実行が終了した後に、トレース結果をホストコンピュータ20上(ホストコンピュータ20に接続されたディスプレイ装置等)に表示するため、トレースメモリ150からトレースメッセージとOVFカウント値を読み出す。なお、表示処理部210の処理は、一般にコンピュータが実行するデバッガプログラムとして実現される。デバッグプログラム210は、読み出したトレースメッセージを基に、例えばGUI(Graphical User Interface)形式のユーザに対する表示画面を生成する。

【0097】

デバッグプログラム210が最初に読み出したトレースメッセージに含まれるタイムスタンプの値は、ユーザプログラム実行開始から最初のトレースデータが生成されるまでの時間間隔を示す。

【0098】

デバッグプログラム210は、トレースメッセージを書き込み順に読み出す。デバッグプログラム210は、読み出したトレースメッセージ内のタイミングフラグと、直前に読み出したトレースメッセージ内のタイミングフラグを比較する。タイミングフラグの値が同じである場合、デバッグプログラム210は、これらのトレースメッセージに含まれるトレースデータが同時出力されたと判断する。

【0099】

ここで、タイミングフラグの値が異なる場合、読み出したトレースメッセージ内のトレースデータの発生と、直近のトレースメッセージ内のトレースデータの発生との間隔は、読み出したトレースメッセージに含まれるタイムスタンプ値となる。

【0100】

読み出したトレースメッセージの直近にOVFカウント値が書き込まれている場合、読み出したトレースメッセージ内のトレースデータの発生と、直近のトレースメッセージ内のトレースデータの発生との間隔は、以下の(数1)により算出される。

【0101】

(数1)

(OVFカウント値×タイムスタンプカウンタ135のフルカウント値)+読み出したトレースメッセージのタイムスタンプ値

【0102】

デバッグプログラム210は、タイミングフラグに基づいて、直近のトレースデータとの出力タイミングが同じであるか否か、トレースデータ間の出力間隔等が把握できる表示画面を生成する。例えば、デバッグプログラム210は、図9に示すトレースメモリ150内の構成に類似した画面を生成し、トレースデータ2とトレースデータ3が同時発生したこと、及びトレースデータ4とトレースデータ5が同時発生したこと、を当該画面上に表示すればよい。

【0103】

ここで、本実施の形態にかかるインサーキットエミュレータの効果について再度説明する。上述したように、タイミング情報生成回路131は、トレースデータの入力タイミング毎に反転するタイミングフラグを生成する。図3に示すように、同時にトレースデータが出力された場合、両トレースデータには同じ値を持つタイミングフラグが関連付けられる。そのため、デバッグプログラム210は、同時発生したイベントにかかるトレースメッセージを判別可能な表示画面を生成することができる。

【0104】

<実施の形態2>

本実施の形態にかかるインサーキットエミュレータは、タイミング情報生成回路131の構成が実施の形態1と異なり、ノイズ(グリッチノイズ)を防止できることを特徴とする。本実施の形態にかかるインサーキットエミュレータについて、実施の形態1と異なる点を中心に説明する。なお、以下の説明において、同一符号、同一名称を付した処理部であって、特に言及しない処理部は、基本的に実施の形態1と同様の処理を行う。本実施の形態にかかるインサーキットエミュレータは、タイミング情報生成回路131の構成を除いて、実施の形態1の構成(図1)と同一構成である。はじめに実施の形態1にかかるタイミング情報生成回路131では、問題が起きる場合について説明する。続いて、本実施の形態にかかるタイミング情報生成回路131の構成、及び動作について説明する。

【0105】

図10を参照して、実施の形態1にかかるタイミング情報生成回路131では、問題が起きる場合について説明する。図10は、実施の形態1にかかるタイミング情報生成回路131の動作を示すタイミングチャートであり、縮尺が異なるものの図3と対応するものである。

【0106】

上述のように、AND回路172は、OR回路171(プロセッサ1イネーブル信号とプロセッサ2イネーブル信号の論理和出力)とクロック信号との論理積を出力する。しかし、何らかの誤操作により、クロック信号の立ち上がりがOR回路171の信号立下りよりも若干速く発生する可能性がある。この場合、AND回路172は、一瞬だけハイレベルとなる出力信号を生成する可能性がある。例えば、図10では、AND回路172は、t8において一瞬だけ立ち上がる信号(ノイズの存在する信号)を生成してしまう可能性がある。このようなAND回路172の出力信号を用いた場合、タイミングフラグの値が誤ったものとなる。

【0107】

次に、このような問題を解決するためのタイミング情報生成回路131の構成について説明する。図11は、本実施の形態にかかるタイミング情報生成回路131の構成を示すブロック図である。タイミング情報生成回路131は、OR回路175と、Dラッチ176と、D型フリップフロップ177と、NOT回路178と、を備える。各回路の出力信号を図12のタイミングチャートに示す。

【0108】

OR回路175には、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号が入力される。OR回路175は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベルである場合にハイレベルをDラッチ176のイネーブル端子Eに供給し、それ以外の場合(両信号がいずれもロウレベルである場合)にロウレベルをDラッチ176のイネーブル端子Eに供給する(図12参照)。

【0109】

Dラッチ176は、一般的なDラッチの動作を行う。Dラッチ176のイネーブル端子Eには、OR回路175の出力信号が供給される。また、Dラッチ176の入力端子Dには、クロック信号が入力される。Dラッチ176は、出力信号をD型フリップフロップ177のクロック端子に供給する。

【0110】

D型フリップフロップ177のクロック端子には、Dラッチ176の出力信号が入力され、入力端子Dには自身の出力信号の反転信号(NOT回路178の出力信号)が入力される。D型フリップフロップ177は、一般的なディレイ型のフリップフロップと同様の動作を行う。D型フリップフロップ177は、出力信号をトレースメッセージ生成回路132にタイミングフラグ信号として出力する。

【0111】

NOT回路178は、D型フリップフロップ177の出力信号を反転(すなわち、ロウレベルであればハイレベルに変換し、ハイレベルであればロウレベルに変換する。)し、反転信号をD型フリップフロップ177の入力端子Dに供給する。

【0112】

次に図12を参照し、各回路の出力信号について説明する。なお、図12のプロセッサ1出力イネーブル信号及びプロセッサ2イネーブル信号の波形は、図10と同一である。OR回路175は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベルである場合にハイレベルをDラッチ176に供給する。そのため、OR回路175は、t2〜t8、t9〜t10、t11〜t12にハイレベルを出力する。

【0113】

Dラッチ176は、前述のようにOR回路175の出力信号(E1)をイネーブル端子Eの入力とし、クロック信号CKを入力端子Dの入力とする。Dラッチ176は、信号E1の立ち上がりに同期してクロック信号CKをスルー出力する。また、Dラッチ176は、信号E1の立ち下がりに同期してクロック信号CKを保持し、信号E1が立ち上がるまでその値を出力する。

【0114】

そのため、図12のタイミングt8においてクロック信号が所望のタイミングよりも若干速く立ち上がった場合であっても、Dラッチ176の出力信号Q1はハイレベルのままとなる(クロック信号CKの値が保持される)。そのため、図10に示すようなノイズの影響は受けない。

【0115】

D型フリップフロップ177は、図12に示す出力信号を出力する。なお、実施の構成1(図3)と比べてタイミングフラグの出力波形も変化している。しかし、図12に示すタイミングフラグは、トレースデータの少なくとも一方が出力される毎に値が反転している。そのため、実施の形態1と同様の効果(トレースデータの同時出力を把握することができる)を得ることができる。

【0116】

続いて、本実施の形態にかかるインサーキットエミュレータの効果について再度説明する。上述したように実施の形態1にかかるタイミング情報生成回路131は、クロック信号の入力タイミングのずれに起因して動作が不正確になる恐れがある。一方、本実施の形態にかかるタイミング情報生成回路131は、Dラッチ176を備える構成である。これにより、クロック信号の入力タイミングのずれが生じた場合であっても、このずれに起因するノイズが生じない。ノイズの発生を防止することにより、誤動作の少ないインサーキットエミュレータを実現することができる。

【0117】

<実施の形態3>

本実施の形態にかかるインサーキットエミュレータは、実施の形態2と略同一の構成を有する。以下、本実施の形態にかかるインサーキットエミュレータについて、実施の形態2と異なる点を説明する。

【0118】

図13は、本実施の形態にかかるタイミング情報生成回路131の構成を示すブロック図である。本実施の形態にかかるタイミング情報生成回路131は、D型フリップフロップ179の構成のみが実施の形態2と異なる。

【0119】

D型フリップフロップ179は、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、を接続する。これにより、図12と同一の動作を行う。

【0120】

なお、図示するように、図13の構成ではNOT回路を設ける必要性が無くなる。そのため、回路規模の縮小を実現することができる。

【0121】

<実施の形態4>

本実施の形態にかかるインサーキットエミュレータは、タイミング情報としてタイミングカウント値(所定値までカウントアップし、所定値となった時点でリセットされるカウント値)を用いることを特徴とする。本実施の形態にかかるインサーキットエミュレータについて、実施の形態1と異なる点を中心に説明する。

【0122】

はじめに、本実施の形態にかかるタイミング情報生成回路131の構成について説明する。図14は、本実施の形態にかかるタイミング情報生成回路131の構成を示すブロック図である。

【0123】

タイミング情報生成回路131は、OR回路180と、Dラッチ181と、D型フリップフロップ182と、D型フリップフロップ183と、D型フリップフロップ184と、を備える。

【0124】

OR回路180には、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号が入力される。OR回路180は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の論理和をDラッチ181のイネーブル端子Eに供給する。

【0125】

Dラッチ181は、一般的なDラッチの動作を行う。Dラッチ181のイネーブル端子Eには、OR回路180の出力信号が供給される。また、Dラッチ181の入力端子Dにはクロック信号が入力される。Dラッチ176は、出力信号をD型フリップフロップ182のクロック端子に供給する。

【0126】

D型フリップフロップ182では、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、が接続される。D型フリップフロップ182は、出力端子Qから出力信号D0を出力する。D型フリップフロップ182は、出力端子QBからの出力信号(D0の反転信号)をD型フリップフロップ183のクロック端子に供給する。

【0127】

D型フリップフロップ183では、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、が接続される。D型フリップフロップ182は、出力端子Qから出力信号D1を出力する。D型フリップフロップ182は、出力端子QBからの出力信号(D1の反転信号)をD型フリップフロップ184のクロック端子に供給する。

【0128】

D型フリップフロップ184では、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、が接続される。D型フリップフロップ182は、出力端子Qから出力信号D2を出力する。

【0129】

上述の出力信号D0、D1、D2の順に下位から連結させた3ビット値が、タイミングカウント値(タイミング情報)としてトレースメッセージ生成回路132に供給される。

【0130】

続いて、図15、図16のタイミングチャートに各信号の出力信号を示す。なお、各回路の出力信号(値の変化)は、上述の回路構成に基づいて当然に理解できるため、詳細な説明は省略する。

【0131】

ここで、[D2,D1,D0](信号D0〜D2より生成される3ビット値)は、トレースデータの入力毎にカウントアップし、"111"となった後にリセット("000")される。

【0132】

上述の構成であっても、トレースデータの出力タイミングを正確に把握することができる。すなわち、同時に出力されたトレースデータを把握することができる。なお、トレースメモリ書き込み制御回路144は、本実施の形態においてタイミングフラグを扱う場合と略同一の手法でタイミングカウント値を参照し、トレースメッセージの書き込みを制御すればよい。

【0133】

なお、上述の説明では、3ビットのカウント値を用いて説明を行ったが、nビットの任意のカウント値を用いれば良い。

【0134】

本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0135】

10 インサーキットエミュレータ

110 第1プロセッサ

111 第1CPUコア

120 第2プロセッサ

121 第2CPUコア

130 タイムスタンプ取得回路

131 タイミング情報生成回路

132 トレースメッセージ生成回路

133 OVFフラグ

134 タイミング情報

135 タイムスタンプカウンタ

136 トレースメッセージバッファ

140 オーバーフローカウンタ制御回路

141 OVFカウンタ

142 OVFカウント値生成回路

143 OVFカウント値バッファ

144 トレースメモリ書き込み制御回路

145 レジスタ

150 トレースメモリ

160 ホストIF

171、175,180 OR回路

172 AND回路

173、177、179、182、183、184 D型フリップフロップ

174、178 NOT回路

176、181 Dラッチ

20 ホストコンピュータ

210 デバッグプログラム

【技術分野】

【0001】

本発明は、インサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法に関する。

【背景技術】

【0002】

近年、家電製品等の各製品の機能増加に伴い、当該製品を制御するマイクロコンピュータが高性能化してきている。特に複数のCPU(Central Processing Unit)コア、メモリ等を備え、処理時間を短縮するマルチコア型のマイクロコンピュータが広く使用されるようになってきている。これに伴い、当該マイクロコンピュータを使用したハードウェア及びソフトウェアをデバッグする開発支援装置(以降、インサーキットエミュレータと記載する。)の機能も複雑化してきている。

【0003】

インサーキットエミュレータでは、マイクロコンピュータのマルチコア化に伴い、トレース機能及びタイムスタンプ機能の高性能化が必要となる。トレース機能とは、ソフトウェア開発時に被実行プログラムの実行結果を格納する機能である。タイムスタンプ機能とは、プログラムの開始からトレース対象に設定されたイベントの発生時点までの累積時間、または直前のトレース対象イベントが実行されてからの経過時間を記録し、当該時間情報をプログラムの実行結果と関連付けて記録する機能である。マイクロコンピュータ内にある複数のCPUコアのうち、どのCPUコアがトレース対象イベントを実行した場合であっても、タイムスタンプ機能は、正確にタイムスタンプを生成することが求められる。

【0004】

上述したインサーキットエミュレータに関連する技術を以下に説明する。特許文献1には、タイムスタンプ取得回路の一態様が開示されている。はじめに、図17を参照して一般的なデバッグ環境の構成を説明する。図17は、特許文献1に記載のタイムスタンプ取得回路を一般的なデバッグ環境に組み込んだ例を示す図である。

【0005】

ユーザーターゲットシステム300は、プログラム開発対象のマイクロコンピュータを搭載するシステムである。デバッグチップ320は、プログラム開発対象のマイクロコンピュータが持つ全機能を実現するチップである。デバッグチップ320は、後述するタイムスタンプカウンタ制御回路330を内部に実装している。デバッグチップ320は、ソケット310を介して電気的にユーザーターゲットシステム300と接続されている。デバッグチップ320は、エミュレーションプローブ340を介して、エミュレータ本体350の構成要素であるエミュレーション制御回路360と電気的に接続されている。エミュレーション制御回路360は、後述するオーバーフローカウンタ制御回路370を有している。

【0006】

エミュレータ本体350は、エミュレーション制御回路360と、トレースメモリ380と、ホストI/F390とを有している。これらは、別々のチップに実装されている。エミュレータ本体350は、ホストPC400と、USBケーブル410などによって接続される。ホストPC400では、デバッガプログラムが実行される。ユーザの操作を受け付けるデバッガプログラムは、ホストI/F390を介してエミュレータ本体350と通信を行うことができる。

【0007】

トレースデータの収集は、デバッガプログラムが実行されるホストPC400からの指示によって開始する。また、ホストPC400からの要求により、トレースメモリ380に保存されたトレースメッセージを、エミュレータ本体350からホストPC400へ読み出すことが可能である。

【0008】

図18は、上述のタイムスタンプカウンタ制御回路330及びオーバーフローカウンタ制御回路370を有するタイムスタンプ取得回路の構成を示す図である。当該タイムスタンプ取得回路は、タイムスタンプカウンタ制御回路330と、オーバーフローカウンタ制御回路370とを備える。タイムスタンプカウンタ制御回路330は、複数のプロセッサの各々からトレースデータを収集し、そのトレースデータにタイムスタンプを付加して、トレースメモリ380に書き込みを行う。

【0009】

この複数のプロセッサは、第1CPUコア410を含む第1プロセッサ420と、第2CPUコア430を含む第2プロセッサ440と、から構成される。第1プロセッサ420、及び第2プロセッサ440は、各々が内蔵する第1CPUコア410、及び、第2CPUコア430がトレース対象命令を実行した場合に、トレース対象命令実行検出信号及びトレースデータを出力する。タイムスタンプカウンタ制御回路330には、トレース対象命令実行検出信号及びトレースデータが入力される。

【0010】

タイムスタンプカウンタ制御回路330は、トレースメッセージ生成回路331と、タイムスタンプカウンタ332と、トレースメッセージバッファ333とを有している。タイムスタンプカウンタ332は、トレースメッセージ生成回路331からリセット信号(RES)を受信すると初期化され、ゼロから計数を開始する。タイムスタンプカウンタ332は、所定のクロックに同期して、一定の時間間隔でカウント動作を行う。タイムスタンプカウント値(タイムスタンプカウンタ332のカウントした値)は、トレースメッセージ生成回路331に送出される。タイムスタンプカウンタ332は、フルカウントまで計数し、オーバーフローすると、キャリー信号をOVFカウンタ371及びトレースメッセージ生成回路331に出力する。トレースメッセージ生成回路331は、キャリー信号が出力されると、OVFフラグ334を1に設定する。

【0011】

トレースメッセージ生成回路331は、トレース対象命令実行検出信号を受信した場合、タイムスタンプカウンタ332からカウント値をリードし、OVFフラグ334がセットされている場合にはOVFカウント値要求信号をOVFカウント値生成回路372に送信する。そして、トレースメッセージ生成回路331は、トレースメッセージを生成し、当該メッセージをトレースメッセージバッファ333にエントリする。

【0012】

OVFカウンタ371は、キャリー信号が入力される度にカウントアップするカウンタである。OVFカウンタ371は、トレースメッセージ生成回路331からリセット信号(RES)を受信すると初期化され、0から計測を開始する。OVFカウント値生成回路372は、OVFカウント値要求信号を受け取ると、OVFカウンタ371の値をOVFカウント値バッファ373に供給する。

【0013】

トレースメッセージ生成回路331は、トレースメッセージの作成後にリセット信号(RES)をアクティブにする。

【0014】

トレースメモリ書き込み制御回路374は、トレースメッセージバッファ333内のトレースメッセージを順次トレースメモリ380に書き込む。この際、トレースメモリ書き込み制御回路374は、書き込み対象のトレースメッセージ内のオーバーフローフラグがオフの場合、そのままトレースメッセージをトレースメモリ380に書き込む。書き込み対象のトレースメッセージ内のオーバーフローフラグがオンの場合、トレースメモリ書き込み制御回路374は、OVFカウント値バッファ373の先頭のOVFカウント値を先にトレースメモリ380に書き込み、その後トレースメッセージを書き込む。

【0015】

図19は、特許文献1に記載のトレースメモリ書き込み制御回路374の動作を説明するためのデータ構造図である。図19は、トレースメッセージバッファ333、OVFカウント値バッファ373、及びトレースメモリ380におけるデータ構造の具体例を示している。トレースメッセージバッファ333には六つのエントリがあり、OVFカウント値バッファ373には二つのエントリがある。トレースメッセージバッファ333の四つ目のエントリにはオーバーフローフラグがセット(1個目)されている。そのため、トレースメッセージバッファ333の四つ目のエントリ入力前に、オーバーフローが生じていることがわかる。また、トレースメッセージバッファ333の六つ目のエントリにはオーバーフローフラグがセット(2個目)されている。そのため、トレースメッセージバッファ333の六つ目のエントリ入力前に、2回目のオーバーフローが生じていることがわかる。このオーバーフローのタイミングから、ユーザは、各イベントが生じたタイミングを把握することができる。

【0016】

なお、特許文献2には、マイクロプロセッサシステムにおける共有メモリの制御に関する技術が開示されている。本技術では、マイクロシステムからの制御内容を時系列に沿って表示する手法が開示されている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2010−128681号公報

【特許文献2】特開平5−265795号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

マイクロコンピュータのマルチコア環境において、複数のCPUコアが同時にトレース対象命令を実行する場合がある。しかしながら、一般に、同時に命令が実行されたか否かを考慮したトレース書き込みが行われていない。そのため、デバッガが、トレースメモリ内のメッセージを参照しても、正しいタイムスタンプ値が参照できない恐れがある。

【0019】

例えば、特許文献1に記載の構成において、第1CPUコア410と第2CPUコア430とが同時にトレース対象イベントを実行したことを想定する。しかし、トレースメモリ書き込み制御回路374にトレースメッセージを入力する場合に、これらのイベントが同時に発生したことを通知する手段がない。そのため、トレースメモリ書き込み制御回路374は、便宜的に先にトレースメッセージバッファ333に入力されたトレースメッセージを、先に発生したイベントにかかるメッセージと認識する。さらに、トレースメモリ書き込み制御回路374は、便宜的に後にトレースメッセージバッファ333に入力されたトレースメッセージを、後に発生したイベントにかかるメッセージと認識する。ここで、両トレースメッセージ内のOVFフラグが設定される場合がある。この場合、トレースメモリ書き込み制御回路374は、先に入力されたトレースメッセージの書き込み前にOVFカウント値バッファ373から先頭のOVFカウント値を読み込んでトレースメモリ380に書き込む。さらに、トレースメモリ書き込み制御回路374は、後に入力されたトレースメッセージの書き込み前にOVFカウント値バッファ373から先頭のOVFカウント値を読み込んでトレースメモリ380に書き込む。しかしながら、先のOVFカウント値の書き込みによりOVFカウント値バッファ273が空になる可能性がある。そのため、トレースメモリ書き込み制御回路374は、不定値をトレースメモリ380に書き込む恐れがある。

【0020】

なお、特許文献2でも、同一のタイミングで共有メモリに書き込むことが想定されていないため、正確なタイムスタンプ値を持つトレースデータを参照することができない。

【0021】

このように、上記した技術では、トレース対象の命令の実行が同時に生じた場合に、正確な命令発生タイミングを把握することができない恐れがあった。

【課題を解決するための手段】

【0022】

本発明にかかるインサーキットエミュレータの一態様は、

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、タイムスタンプをカウントするタイムスタンプカウンタがオーバーフローしたことを示すオーバーフローフラグと、前記タイミング情報と、を対応付けたトレースメッセージを生成するトレースメッセージ生成回路と、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込みを行う制御回路であって、前記オーバーフローフラグの設定時には、同じタイミング情報を持つトレースメッセージ群をトレースメモリに書き込む前にオーバーフローカウント値をトレースメモリに書き込み、その後に同じタイミング情報を持つトレースメッセージ群をトレースメモリに書き込む、トレースメモリ書き込み制御回路と、を備えるものである。

【0023】

本発明にかかるトレースメモリ制御システムの一態様は、

第1、第2プロセッサの各々からのトレースデータと、各トレースデータ取得時のタイムスタンプと、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報と、を対応付けたトレースメッセージを出力順に受け付け、トレースメモリに書き込むトレースメモリ書き込み制御回路を備えた装置と、

前記トレースメモリから各トレースメッセージを読み出し、各トレースメッセージ内の前記タイミング情報に基づき、他のトレースメッセージと出力タイミングが異なるかを判別できるように各トレースメッセージを表示する表示情報を生成するデバッグプログラムを実行するホストコンピュータと、を備える、ものである。

【0024】

本発明にかかるトレースメッセージ生成装置の一態様は、

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、前記タイミング情報に基づいて、各トレースメッセージを表示する制御装置に対し、生成したトレースメッセージを供給する、トレースメッセージ生成回路と、を備える、ものである。

【0025】

本発明にかかるトレースメッセージ処理方法の一態様は、

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を生成し、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込む、ものである。

【0026】

本発明では、トレースデータの出力と同期して出力される出力イネーブル信号から、トレースデータの出力タイミングの異同を示すタイミング情報が生成される。トレースメッセージは、タイミング情報とトレースデータが関連付けられてトレースメモリ内に格納される。そして、表示時には、トレースメッセージ内のタイミング情報を参照することにより、出力タイミングの異同を判別できる表示画面が生成される。これにより、トレース対象の命令の実行が同時に生じた場合であっても、正確な発生タイミングを把握することができる。

【発明の効果】

【0027】

本発明によれば、トレース対象の命令の実行が同時に生じた場合であっても、正確な命令発生タイミングを把握することができるインサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法を提供することができる。

【図面の簡単な説明】

【0028】

【図1】実施の形態1にかかるインサーキットエミュレータの構成を示すブロック図である。

【図2】実施の形態1にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図3】実施の形態1にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図4】実施の形態1にかかるタイミング情報生成回路の動作を示すフローチャートである。

【図5】実施の形態1にかかるトレースメッセージ生成回路の動作を示すフローチャートである。

【図6】実施の形態1にかかるオーバーフローカウント値生成回路の動作を示すフローチャートである。

【図7】実施の形態1にかかるトレースメモリ書き込み制御回路の動作を示すフローチャートである。

【図8】実施の形態1にかかるトレースメモリ書き込み制御回路の動作を示すフローチャートである。

【図9】実施の形態1にかかるインサーキットエミュレータの動作を示す概念図である。

【図10】実施の形態1にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図11】実施の形態2にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図12】実施の形態2にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図13】実施の形態3にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図14】実施の形態4にかかるタイミング情報生成回路の内部構成を示すブロック図である。

【図15】実施の形態4にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図16】実施の形態4にかかるタイミング情報生成回路内の各回路の出力信号を示すタイミングチャートである。

【図17】一般的なデバッグ環境を示すブロック図である。

【図18】特許文献1に記載のタイムスタンプカウンタ制御回路の構成を示すブロック図である。

【図19】特許文献1に記載のトレースメモリ書き込み制御回路の動作を示す図である。

【発明を実施するための形態】

【0029】

<実施の形態1>

以下、図面を参照して本発明の実施の形態について説明する。図1は、本実施の形態にかかるインサーキットエミュレータシステムの構成を示すブロック図である。当該当該インサーキットエミュレータシステムは、インサーキットエミュレータ10と、ホストコンピュータ20と、を備える。

【0030】

インサーキットエミュレータ10は、第1プロセッサ110と、第2プロセッサ120と、タイムスタンプカウンタ制御回路130と、オーバーフローカウンタ制御回路140と、トレースメモリ150と、ホストIF(インターフェイス)160と、を備える。

【0031】

第1プロセッサ110、第2プロセッサ120、及びタイムスタンプ取得回路130は、同一チップ上に実装することができ、デバッグチップとして動作する。タイムスタンプカウンタ制御回路130は、タイミング情報生成回路131と、トレースメッセージ生成回路132と、タイムスタンプカウンタ135と、トレースメッセージバッファ136と、を備える。なお、タイムスタンプカウンタ制御回路130内の各処理部には、クロック信号が入力される。

【0032】

第1プロセッサ110及び第2プロセッサ120は、各々が内蔵する第1CPUコア111、第2CPUコア121がトレース対象命令を実行した場合、出力イネーブル信号(プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号)をタイミング情報生成回路131、及びトレースメッセージ生成回路132に出力し、トレースデータをトレースメッセージ生成回路132に出力する。ここで、第1プロセッサ110、第2プロセッサ120が出力するトレースデータには、第1プロセッサ110、第2プロセッサ120のどちらから出力されているかを示すプロセッサ識別子が含まれる。

【0033】

タイミング情報生成回路131は、第1プロセッサ110、または第2プロセッサ120のトレースデータ出力タイミングを示すタイミング情報を出力する。本実施の形態において、タイミング情報生成回路131は、タイミング情報として1ビットのビット値であるタイミングフラグを出力する。タイミング情報生成回路131は、プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号の少なくとも一方が入力されたタイミングにタイミングフラグを反転する。

【0034】

タイミング情報生成回路131の内部構成の一例を図2に示す。図示するようにタイミング情報生成回路131は、OR回路171と、AND回路172と、D型フリップフロップ173と、NOT回路174と、を備える。各回路の出力信号を図3のタイミングチャートに示す。

【0035】

OR回路171には、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号が入力される。OR回路171は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベル("1"、以下同様である。)である場合にハイレベルをAND回路172に出力し、それ以外の場合(両信号がいずれもロウレベル("0"以下同様である。)である場合)にロウレベルをAND回路172に出力する(図3参照)。

【0036】

AND回路172には、クロック信号と、OR回路171からの出力信号が入力される。AND回路172は、両入力信号が共にハイレベルである場合にD型フリップフロップ173のクロック入力端子にハイレベルを供給し、それ以外の場合にD型フリップフロップ173のクロック入力端子にロウレベルを供給する(図3参照)。

【0037】

D型フリップフロップ173のクロック入力端子には、AND回路172の出力信号が入力される。D型フリップフロップ173の入力端子Dには、D型フリップフロップ173の出力信号の反転信号(NOT回路174の出力信号)が入力される。D型フリップフロップ173は、一般的なディレイ型のフリップフロップと同様の動作を行う。D型フリップフロップ173は、出力信号をトレースメッセージ生成回路132にタイミングフラグ信号として供給する。

【0038】

NOT回路174は、D型フリップフロップ173の出力信号を反転(すなわち、ロウレベルであればハイレベルに変換し、ハイレベルであればロウレベルに変換する。)し、反転信号をD型フリップフロップ173の入力端子Dに供給する。

【0039】

改めて、図3を参照し、各回路の出力信号について説明する。OR回路171は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベルである場合にハイレベルをAND回路172に出力する。そのため、OR回路171は、t2〜t8、t9〜t10、t11〜t12にハイレベルを出力する。

【0040】

AND回路172は、クロック信号とOR回路171の出力信号が共にハイレベルである場合にハイレベルを出力する。よって、AND回路172は、t2〜t2.5(タイミングt2とタイミングt3の中間タイミング、以下同様の記載を行う。)、t3〜t3.5、t4〜t4.5、t5〜t5.5、t6〜t6.5、t7〜t7.5、t9〜t9.5、t11〜t11.5にハイレベルを出力する。

【0041】

D型フリップフロップ173では、前述のようにAND回路172の出力信号がクロック入力端子に供給され、自身の出力信号の反転信号が入力端子Dに供給される。そのため、D型フリップフロップ173は、t2〜t3、t4〜t5、t6〜t7、t9〜t11にハイレベルを出力する。これにより、D型フリップフロップ173の出力信号、すなわちタイミングフラグは、図3に示すように、第1プロセッサ110及び第2プロセッサ130の少なくとも一方のトレース出力タイミングで値を反転している。

【0042】

再び、図1を参照する。トレースメッセージ生成回路132は、OVFフラグ133と、タイミングフラグ134と、を保持する。トレースメッセージ生成回路132は、タイミング情報生成回路131から入力されるタイミングフラグ134をトレースデータ毎に保持する。さらに、トレースメッセージ生成回路132は、タイムスタンプカウンタ135からキャリー信号が入力された場合に、OVFフラグ133をオンに設定する。

【0043】

トレースメッセージ生成回路132は、プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号の一方または双方を受信した場合、OVFフラグ133がオンに設定されているか否かを判定する。OVFフラグ133がオンに設定されている場合、OVFカウント値要求信号をOVFカウント値生成回路142に供給する。OVFカウント値要求信号とは、OVFカウント値生成回路142に対し、OVFカウンタ141のカウント値を用いてOVFカウント値を生成し、生成値をOVFカウント値バッファ143に格納することを要求する信号である。

【0044】

トレースメッセージ生成回路132は、プロセッサ1出力イネーブル信号を受信した場合、第1プロセッサ110からトレースデータ、タイムスタンプカウンタ135からタイムスタンプカウント値、タイミング情報生成回路131からタイミングフラグを受信する。同様に、トレースメッセージ生成回路32は、プロセッサ2出力イネーブル信号を受信した場合、第2プロセッサ120からトレースデータ、タイムスタンプカウンタ135からタイムスタンプカウント値、タイミング情報生成回路131からタイミングフラグを受信する。

【0045】

トレースメッセージ生成回路132は、トレースデータと、タイムスタンプカウント値と、タイミングフラグと、OVFフラグ133の値と、を関連付けたトレースメッセージを生成する。

【0046】

トレースメッセージバッファ136は、FIFO(First In First Out)型の記憶部である。

【0047】

トレースメッセージ生成回路132は、トレースメッセージの作成後にOVFフラグ133の値をクリア(オフ)し、カウンタリセット信号(RES)をタイムスタンプカウンタ135及びOVFカウンタ141に供給する。カウンタリセット信号は、タイムスタンプカウンタ135のカウント値、及びOVFカウンタ141のカウント値をリセットする信号である。トレースメッセージ生成回路132は、生成したトレースメッセージをトレースメッセージバッファ136に入力する。

【0048】

なお、トレースメッセージ生成回路132は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号を受信した場合、プロセッサ毎のトレースメッセージを同時に作成し、トレースメッセージバッファ136に入力する。

【0049】

タイムスタンプカウンタ135は、クロック信号に同期して、一定の時間間隔でカウント動作を行う。タイムスタンプカウンタ135は、カウント値をトレースメッセージ生成回路132に供給する。タイムスタンプカウンタ135は、カウント値が上限値に到達する(オーバーフローする)と、キャリー信号をトレースメッセージ生成回路132及びオーバーフローカウンタ制御回路140に供給する。タイムスタンプカウンタ135は、トレースメッセージ生成回路132からカウンタリセット信号を受信した場合に、カウント値をリセット(0に設定)する。

【0050】

オーバーフローカウンタ制御回路140は、OVFカウンタ141と、OVFカウント値生成回路142と、OVFカウント値バッファ143と、トレースメモリ書き込み制御回路144と、を備える。トレースメモリ書き込み制御回路144は、内部にレジスタ145を有する。

【0051】

OVFカウンタ141は、トレースメッセージ生成回路132からカウンタリセット信号(RES)を受信すると初期化され、ゼロから計数を開始する。OVFカウンタ141は、タイムスタンプカウンタ135から出力されるキャリー信号の入力回数を計数する。

【0052】

OVFカウント値生成回路142は、トレースメッセージ生成回路132からOVFカウント値要求信号が入力される(アクティブになる)と、OVFカウンタ141のカウント値を読み出す。OVFカウント値生成回路142は、読み出したカウント値をOVFカウント値バッファ143に入力する。

【0053】

OVFカウント値バッファ143は、FIFO(First In First Out)型の記憶部である。OVFカウント値バッファ143は、OVFカウント値生成回路142によって生成された順序でカウント値を保持する。

【0054】

トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136からトレースメッセージを順次読み出し、読み出したトレースメッセージをトレースメモリ150に書き込む回路である。

【0055】

トレースメモリ書き込み制御回路144は、内部にレジスタ145を有する。レジスタ145は、トレースメモリ書き込み制御回路144が直近に書き込んだトレースメッセージに含まれるタイミング情報(本実施の形態ではタイミングフラグの値)を保持する。トレースメモリ書き込み制御回路144は、これから書き込むトレースメッセージ内のOVFフラグを抽出し、オンに設定されているか否かを判定する。さらに、トレースメモリ書き込み制御回路144は、これから書き込むトレースメッセージ内のタイミングフラグの値と、レジスタ145が保持するタイミングフラグの値と、を比較する。

【0056】

OVFフラグがオンであり、タイミングフラグの値が一致しない場合、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143の先頭に位置するカウント値を取得する。トレースメモリ書き込み制御回路144は、取得したカウント値をトレースメモリ150に書き込む。その後、トレースメモリ書き込み制御回路144は、書き込み対象のトレースメッセージをトレースメモリ150に書き込む。

【0057】

一方、OVFフラグがオンではない場合、またはタイミングフラグの値が一致する場合、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143からカウント値を取得しない。トレースメモリ書き込み制御回路144は、書き込み対象のトレースメッセージをトレースメモリ150に書き込む。

【0058】

トレースメモリ150は、トレースメモリ書き込み制御回路144から書き込まれるトレースメッセージを格納する記憶部である。

【0059】

ホストIF160は、トレースメモリ150と、デバッグプログラム210と、のデータのやり取りを仲介する処理部である。

【0060】

ホストコンピュータ20は、デバッグプログラム210を実行する。デバッグプログラム210は、第1CPUコアおよび第2CPUコアでのデバッグ対象のプログラムの実行、停止を指示したり、トレースメモリ150に書き込まれたトレースメッセージを取り込んでホストコンピュータの表示装置へ渡し、トレースメッセージの内容を表示させる。ホストコンピュータ20は、液晶ディスプレイ等の表示部と一体化された装置、または接続可能に構成された装置である。ホストコンピュータ20は、CPU(Central Processing Unit)やHDD(Hard Disk Drive)等の補助記憶装置、RAM(Random Access Memory)等の不揮発性メモリを有する。デバッグプログラム210は、補助記憶装置内に格納され、実行時にRAMに適宜読み出されてCPUにより実行される。

【0061】

デバッグプログラム210は、前述の表示部に表示する表示メッセージを取得、生成する

【0062】

続いて、図4を参照して、タイミング情報生成回路131の動作を説明する。図4は、本実施の形態にかかるタイミング情報生成回路131の動作を示すフローチャートである。

【0063】

各CPUコアにてユーザプログラムが実行される前に、タイミング情報生成回路131内のタイミングフラグの値をリセットする(S11)。すなわち、はじめにタイミング情報生成回路131が生成するタイミングフラグの値を0(ロウレベル)とする。タイミングフラグの値のリセットは、ライトアクセスを行うことにより実現する。

【0064】

タイミング情報生成回路131は、第1CPUコア110及び第2CPUコア120がユーザプログラムを実行中であるか否かを判定する(S12)。ユーザプログラムの実行中ではない場合(S12:No)、タイミング情報生成回路131は、処理を終了する。

【0065】

ユーザプログラムの実行中である場合(S12:Yes)、タイミング情報生成回路131は、出力イネーブル信号(プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号)が有効("1"、ハイレベル)であるか否かを判定する(S13)。いずれも有効ではない場合、タイミング情報生成回路131は、S12の処理を再度行う。

【0066】

出力イネーブル信号の一方が有効である場合(S13:Yes)、タイミング情報生成回路131は、タイミングフラグを反転する(S14)。

【0067】

続いて、図5を参照して、トレースメッセージ生成回路132の動作を説明する。図5は、トレースメッセージ生成回路132の動作を示すフローチャートである。

【0068】

各CPUコアにてユーザプログラムが実行される前に、タイムスタンプカウンタ135のカウント値、OVFフラグ133、及びOVFカウンタ141をライトアクセスによりリセットする(S21)。

【0069】

トレースメッセージ生成回路132は、第1CPUコア111及び第2CPUコア121がユーザプログラムを実行中であるか否かを判定する(S22)。ユーザプログラムの実行中ではない場合(S22:No)、トレースメッセージ生成回路132は、処理を終了する。

【0070】

ユーザプログラムの実行中である場合(S22:Yes)、トレースメッセージ生成回路132は、出力イネーブル信号(プロセッサ1出力イネーブル信号、プロセッサ2出力イネーブル信号)が有効である否かを判定する(S23)。出力イネーブル信号が有効ではない場合(S23:No)、トレースメッセージ生成回路132は、S22の処理を再度行う。

【0071】

出力イネーブル信号が有効になった場合(S23:Yes)、トレースメッセージ生成回路132は、OVFフラグ133がオンに設定されているか否かを判定する(S24)。OVFフラグ133がオンに設定されている場合(S24:Yes)、トレースメッセージ生成回路132は、OVFカウント値要求信号をOVFカウント値生成回路142に供給する(S25)。

【0072】

OVFフラグ133がオンに設定されていない場合(S24:No)、トレースメッセージ生成回路132は、OVFカウント値要求信号を出力しない。

【0073】

そして、トレースメッセージ生成回路132は、出力イネーブル信号の受信に応じて、トレースデータ、タイムスタンプカウント値、及びタイミングフラグを取得する(S26)。トレースメッセージ生成回路132は、トレースデータと、タイムスタンプカウント値と、タイミングフラグと、OVFフラグ133の値と、を関連付けたトレースメッセージを生成する(S27)。

【0074】

トレースメッセージ生成回路132は、OVFフラグ133の値をクリア(オフ)すると共に、カウンタリセット信号をタイムスタンプカウンタ135及びOVFカウンタ141に供給する(S28)。トレースメッセージ生成回路132は、生成したトレースメッセージをトレースメッセージバッファ136に入力する(S29)。S29の処理の後、トレースメッセージ生成回路132は、S23の処理を再度行う。

【0075】

続いて、図6を参照して、オーバーフローカウント値生成回路142の動作を説明する。図6は、オーバーフローカウント値生成回路142の動作を示すフローチャートである。

【0076】

オーバーフローカウント値生成回路142は、第1CPUコア111及び第2CPUコア121がユーザプログラムを実行中であるか否かを判定する(S31)。ユーザプログラムの実行中ではない場合(S31:No)、オーバーフローカウント値生成回路142は、処理を終了する。

【0077】

ユーザプログラムの実行中である場合(S31:Yes)、オーバーフローカウント値生成回路142は、OVFカウント値要求信号の受信を受け付ける(S32)。OVFカウント値要求信号を受信しない場合(S32:No)、オーバーフローカウント値生成回路142は、S31から処理を再度行う。

【0078】

OVFカウント値要求信号を受信した場合(S32:Yes)、オーバーフローカウント値生成回路142は、OVFカウンタ141からカウント値を取得する(S33)。そして、OVFカウント値生成回路142は、取得したカウント値をOVFカウント値バッファ143に入力する(S34)。その後、オーバーフローカウント値生成回路142は、S32から処理を再度行う。

【0079】

続いて、図7及び図8を参照して、トレースメモリ書き込み制御回路144の動作を説明する。図7及び図8は、トレースメモリ書き込み制御回路144の動作を示すフローチャートである。

【0080】

各CPUコアにてユーザプログラムが実行される前に、タイミング情報生成回路131内のタイミングフラグの値をリセットする(S41)。すなわち、はじめにタイミング情報生成回路131が生成するタイミングフラグを0とする。

【0081】

トレースメモリ書き込み制御回路144は、第1CPUコア111及び第2CPUコア121がユーザプログラムを実行中であるか否かを判定する(S42)。ユーザプログラムの実行中ではない場合(S42:No)、トレースメモリ書き込み制御回路144は、処理を終了する。

【0082】

ユーザプログラムの実行中である場合(S42:Yes)、トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136にトレースメッセージが格納されているか否かを判定する(S43)。トレースメッセージが格納されていない場合(S43:No)、トレースメモリ書き込み制御回路144は、S42から処理を再度行う。

【0083】

トレースメッセージが格納されている場合(S43:Yes)、トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136の先頭からトレースメッセージを取得する(S44)。トレースメモリ書き込み制御回路144は、取得したトレースメッセージからOVFフラグの値を抽出する。トレースメモリ書き込み制御回路144は、抽出したOVFフラグがオンに設定されているか否かを判定する(S45)。

【0084】

OVFフラグがオンに設定されている場合(S45:Yes)、トレースメモリ書き込み制御回路144は、トレースメッセージ内のタイミングフラグの値を抽出する。トレースメモリ書き込み制御回路144は、抽出したタイミングフラグの値と、レジスタ145が保持する値と、を比較する(S46)。両者が一致しない場合(S46:No)、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143の先頭に格納されたカウント値を取得し(S47)、取得したカウント値をトレースメモリ150に書き込む(S48)。そして、トレースメモリ書き込み制御回路144は、トレースメモリ150のアドレスをインクリメントする(S49)。

【0085】

OVFフラグがオンに設定されていない場合(S45:No)、または書き込み対象のトレースメッセージに含まれるタイミングフラグの値とレジスタ145が保持する値とが一致する場合(S46:Yes)、トレースメモリ書き込み制御回路144は、S47〜S49の処理を行わない。

【0086】

トレースメモリ書き込み制御回路144は、書き込み対象のトレースメッセージからタイミングフラグの値を取得し、取得した値をレジスタ145に上書きする(S50)。トレースメモリ書き込み制御回路144は、トレースメッセージをトレースメモリ150に書き込む(S51)。そして、トレースメモリ書き込み制御回路144は、トレースメモリ150のアドレスをインクリメントする(S52)。

【0087】

トレースメモリ書き込み制御回路144は、トレースメモリ150のアドレスのインクリメント(S52)の後に、再度、トレースメッセージバッファ136にトレースメッセージが格納されているか否かを判定する(S43)。

【0088】

次に、図9の模式図を参照して、各処理部の動作を更に説明する。なお、以下の説明において、参考として上述のフローチャート(図4〜図8)の符号も併せて記載する。タイミング情報生成回路131は、上述した方法により、トレースデータの入力毎に反転するタイミングフラグを生成する(S11〜S14)。この際、タイミング情報生成回路131は、どのプロセッサがトレースデータを出力したか、または複数のプロセッサがトレースデータを出力したか、等に関わらずトレースデータの入力毎にタイミングフラグを反転する。トレースメッセージ生成回路132は、トレースデータに、タイミングフラグ、OVFフラグ及びタイムスタンプカウンタのカウント値を関連付けたトレースメッセージを生成する(S27)。

【0089】

図9では、トレースメッセージ2のトレースデータと、トレースメッセージ3のトレースデータと、が同じタイミングで出力されている。この場合、トレースメッセージ2とトレースメッセージ3は、同じタイミングフラグ、同じOVFフラグ、及び同じタイムスタンプカウント値を持つ。同様に、トレースメッセージ4のトレースデータと、トレースメッセージ5のトレースデータと、が同じタイミングで出力されている。この場合、トレースメッセージ4とトレースメッセージ5は、同じタイミングフラグ、同じOVFフラグ、及び同じタイムスタンプカウント値を持つ。

【0090】

トレースメッセージ生成回路132は、生成したトレースメッセージを順次トレースメッセージバッファ136にエントリする。図9の上部には、トレースメッセージバッファ136にエントリされたトレースメッセージが示されている。

【0091】

トレースメモリ書き込み制御回路144は、トレースメッセージバッファ136からトレースメッセージを取得する。トレースメモリ書き込み制御回路144は、OVFフラグが"0"であれば、タイミングフラグの値をレジスタ145に書き込み(S50)、トレースメッセージをトレースメモリ150に書き込む(S51)。図9では、トレースメッセージバッファ136のトレースメッセージ1〜3は、OVFフラグの値が"0"であるため、トレースメモリ150にそのまま書き込まれる。

【0092】

トレースメモリ書き込み制御回路144は、OVFフラグが"1"であれば、取得したトレースメッセージのタイミングフラグと、レジスタ145の値を比較する(S46)。一致しない場合、トレースメモリ書き込み制御回路144は、直近のトレースデータの発生後にタイムスタンプがオーバーフローし、その後にトレースデータが出力されたと判定する。この場合、トレースメモリ書き込み制御回路144は、OVFカウント値バッファ143からOVFカウント値を取得し(S47)、取得したOVFカウント値をトレースメモリ150に書き込む(S48)。そして、トレースメモリ書き込み制御回路144は、タイミングフラグの値をレジスタ145に書き込み(S50)、トレースメッセージをトレースメモリ150に書き込む(S51)。

【0093】

図9では、トレースメッセージ4〜6は、保持するOVFフラグの値が"1"である。トレースメッセージ4のタイミングフラグの値は、直近のトレースメッセージのタイミングフラグと一致しない。そのため、トレースメッセージ4は、"OVFカウント値1"の書き込みの後にトレースメモリ150に書き込まれる。

【0094】

トレースメッセージ5のタイミングフラグの値は、直近のトレースメッセージのタイミングフラグと一致している。そのため、トレースメッセージ5は、トレースメッセージ4と同時に出力されたと判定される。ここで、OVFカウント値("1")は、すでにトレースメモリ150に書き込まれている。そのため、トレースメモリ書き込み制御回路144は、タイミングフラグの値をレジスタ145に書き込み(S50)、OVFカウント値を書き込むことなく、トレースメッセージ5をトレースメモリ150に書き込む(S51)。

【0095】

トレースメッセージ6のタイミングフラグの値は、直近のトレースメッセージのタイミングフラグと一致しない。そのため、トレースメッセージ6は、"OVFカウント値2"の書き込みの後にトレースメモリ150に書き込まれる。

【0096】

次に、ホストコンピュータ20によるトレースメモリの読み出し処理について説明する。ホストコンピュータ20上で実行されるデバッグプログラム210は、第1プロセッサ110及び第2プロセッサ120によるプログラム実行が終了した後に、トレース結果をホストコンピュータ20上(ホストコンピュータ20に接続されたディスプレイ装置等)に表示するため、トレースメモリ150からトレースメッセージとOVFカウント値を読み出す。なお、表示処理部210の処理は、一般にコンピュータが実行するデバッガプログラムとして実現される。デバッグプログラム210は、読み出したトレースメッセージを基に、例えばGUI(Graphical User Interface)形式のユーザに対する表示画面を生成する。

【0097】

デバッグプログラム210が最初に読み出したトレースメッセージに含まれるタイムスタンプの値は、ユーザプログラム実行開始から最初のトレースデータが生成されるまでの時間間隔を示す。

【0098】

デバッグプログラム210は、トレースメッセージを書き込み順に読み出す。デバッグプログラム210は、読み出したトレースメッセージ内のタイミングフラグと、直前に読み出したトレースメッセージ内のタイミングフラグを比較する。タイミングフラグの値が同じである場合、デバッグプログラム210は、これらのトレースメッセージに含まれるトレースデータが同時出力されたと判断する。

【0099】

ここで、タイミングフラグの値が異なる場合、読み出したトレースメッセージ内のトレースデータの発生と、直近のトレースメッセージ内のトレースデータの発生との間隔は、読み出したトレースメッセージに含まれるタイムスタンプ値となる。

【0100】

読み出したトレースメッセージの直近にOVFカウント値が書き込まれている場合、読み出したトレースメッセージ内のトレースデータの発生と、直近のトレースメッセージ内のトレースデータの発生との間隔は、以下の(数1)により算出される。

【0101】

(数1)

(OVFカウント値×タイムスタンプカウンタ135のフルカウント値)+読み出したトレースメッセージのタイムスタンプ値

【0102】

デバッグプログラム210は、タイミングフラグに基づいて、直近のトレースデータとの出力タイミングが同じであるか否か、トレースデータ間の出力間隔等が把握できる表示画面を生成する。例えば、デバッグプログラム210は、図9に示すトレースメモリ150内の構成に類似した画面を生成し、トレースデータ2とトレースデータ3が同時発生したこと、及びトレースデータ4とトレースデータ5が同時発生したこと、を当該画面上に表示すればよい。

【0103】

ここで、本実施の形態にかかるインサーキットエミュレータの効果について再度説明する。上述したように、タイミング情報生成回路131は、トレースデータの入力タイミング毎に反転するタイミングフラグを生成する。図3に示すように、同時にトレースデータが出力された場合、両トレースデータには同じ値を持つタイミングフラグが関連付けられる。そのため、デバッグプログラム210は、同時発生したイベントにかかるトレースメッセージを判別可能な表示画面を生成することができる。

【0104】

<実施の形態2>

本実施の形態にかかるインサーキットエミュレータは、タイミング情報生成回路131の構成が実施の形態1と異なり、ノイズ(グリッチノイズ)を防止できることを特徴とする。本実施の形態にかかるインサーキットエミュレータについて、実施の形態1と異なる点を中心に説明する。なお、以下の説明において、同一符号、同一名称を付した処理部であって、特に言及しない処理部は、基本的に実施の形態1と同様の処理を行う。本実施の形態にかかるインサーキットエミュレータは、タイミング情報生成回路131の構成を除いて、実施の形態1の構成(図1)と同一構成である。はじめに実施の形態1にかかるタイミング情報生成回路131では、問題が起きる場合について説明する。続いて、本実施の形態にかかるタイミング情報生成回路131の構成、及び動作について説明する。

【0105】

図10を参照して、実施の形態1にかかるタイミング情報生成回路131では、問題が起きる場合について説明する。図10は、実施の形態1にかかるタイミング情報生成回路131の動作を示すタイミングチャートであり、縮尺が異なるものの図3と対応するものである。

【0106】

上述のように、AND回路172は、OR回路171(プロセッサ1イネーブル信号とプロセッサ2イネーブル信号の論理和出力)とクロック信号との論理積を出力する。しかし、何らかの誤操作により、クロック信号の立ち上がりがOR回路171の信号立下りよりも若干速く発生する可能性がある。この場合、AND回路172は、一瞬だけハイレベルとなる出力信号を生成する可能性がある。例えば、図10では、AND回路172は、t8において一瞬だけ立ち上がる信号(ノイズの存在する信号)を生成してしまう可能性がある。このようなAND回路172の出力信号を用いた場合、タイミングフラグの値が誤ったものとなる。

【0107】

次に、このような問題を解決するためのタイミング情報生成回路131の構成について説明する。図11は、本実施の形態にかかるタイミング情報生成回路131の構成を示すブロック図である。タイミング情報生成回路131は、OR回路175と、Dラッチ176と、D型フリップフロップ177と、NOT回路178と、を備える。各回路の出力信号を図12のタイミングチャートに示す。

【0108】

OR回路175には、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号が入力される。OR回路175は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベルである場合にハイレベルをDラッチ176のイネーブル端子Eに供給し、それ以外の場合(両信号がいずれもロウレベルである場合)にロウレベルをDラッチ176のイネーブル端子Eに供給する(図12参照)。

【0109】

Dラッチ176は、一般的なDラッチの動作を行う。Dラッチ176のイネーブル端子Eには、OR回路175の出力信号が供給される。また、Dラッチ176の入力端子Dには、クロック信号が入力される。Dラッチ176は、出力信号をD型フリップフロップ177のクロック端子に供給する。

【0110】

D型フリップフロップ177のクロック端子には、Dラッチ176の出力信号が入力され、入力端子Dには自身の出力信号の反転信号(NOT回路178の出力信号)が入力される。D型フリップフロップ177は、一般的なディレイ型のフリップフロップと同様の動作を行う。D型フリップフロップ177は、出力信号をトレースメッセージ生成回路132にタイミングフラグ信号として出力する。

【0111】

NOT回路178は、D型フリップフロップ177の出力信号を反転(すなわち、ロウレベルであればハイレベルに変換し、ハイレベルであればロウレベルに変換する。)し、反転信号をD型フリップフロップ177の入力端子Dに供給する。

【0112】

次に図12を参照し、各回路の出力信号について説明する。なお、図12のプロセッサ1出力イネーブル信号及びプロセッサ2イネーブル信号の波形は、図10と同一である。OR回路175は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の一方がハイレベルである場合にハイレベルをDラッチ176に供給する。そのため、OR回路175は、t2〜t8、t9〜t10、t11〜t12にハイレベルを出力する。

【0113】

Dラッチ176は、前述のようにOR回路175の出力信号(E1)をイネーブル端子Eの入力とし、クロック信号CKを入力端子Dの入力とする。Dラッチ176は、信号E1の立ち上がりに同期してクロック信号CKをスルー出力する。また、Dラッチ176は、信号E1の立ち下がりに同期してクロック信号CKを保持し、信号E1が立ち上がるまでその値を出力する。

【0114】

そのため、図12のタイミングt8においてクロック信号が所望のタイミングよりも若干速く立ち上がった場合であっても、Dラッチ176の出力信号Q1はハイレベルのままとなる(クロック信号CKの値が保持される)。そのため、図10に示すようなノイズの影響は受けない。

【0115】

D型フリップフロップ177は、図12に示す出力信号を出力する。なお、実施の構成1(図3)と比べてタイミングフラグの出力波形も変化している。しかし、図12に示すタイミングフラグは、トレースデータの少なくとも一方が出力される毎に値が反転している。そのため、実施の形態1と同様の効果(トレースデータの同時出力を把握することができる)を得ることができる。

【0116】

続いて、本実施の形態にかかるインサーキットエミュレータの効果について再度説明する。上述したように実施の形態1にかかるタイミング情報生成回路131は、クロック信号の入力タイミングのずれに起因して動作が不正確になる恐れがある。一方、本実施の形態にかかるタイミング情報生成回路131は、Dラッチ176を備える構成である。これにより、クロック信号の入力タイミングのずれが生じた場合であっても、このずれに起因するノイズが生じない。ノイズの発生を防止することにより、誤動作の少ないインサーキットエミュレータを実現することができる。

【0117】

<実施の形態3>

本実施の形態にかかるインサーキットエミュレータは、実施の形態2と略同一の構成を有する。以下、本実施の形態にかかるインサーキットエミュレータについて、実施の形態2と異なる点を説明する。

【0118】

図13は、本実施の形態にかかるタイミング情報生成回路131の構成を示すブロック図である。本実施の形態にかかるタイミング情報生成回路131は、D型フリップフロップ179の構成のみが実施の形態2と異なる。

【0119】

D型フリップフロップ179は、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、を接続する。これにより、図12と同一の動作を行う。

【0120】

なお、図示するように、図13の構成ではNOT回路を設ける必要性が無くなる。そのため、回路規模の縮小を実現することができる。

【0121】

<実施の形態4>

本実施の形態にかかるインサーキットエミュレータは、タイミング情報としてタイミングカウント値(所定値までカウントアップし、所定値となった時点でリセットされるカウント値)を用いることを特徴とする。本実施の形態にかかるインサーキットエミュレータについて、実施の形態1と異なる点を中心に説明する。

【0122】

はじめに、本実施の形態にかかるタイミング情報生成回路131の構成について説明する。図14は、本実施の形態にかかるタイミング情報生成回路131の構成を示すブロック図である。

【0123】

タイミング情報生成回路131は、OR回路180と、Dラッチ181と、D型フリップフロップ182と、D型フリップフロップ183と、D型フリップフロップ184と、を備える。

【0124】

OR回路180には、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号が入力される。OR回路180は、プロセッサ1出力イネーブル信号及びプロセッサ2出力イネーブル信号の論理和をDラッチ181のイネーブル端子Eに供給する。

【0125】

Dラッチ181は、一般的なDラッチの動作を行う。Dラッチ181のイネーブル端子Eには、OR回路180の出力信号が供給される。また、Dラッチ181の入力端子Dにはクロック信号が入力される。Dラッチ176は、出力信号をD型フリップフロップ182のクロック端子に供給する。

【0126】

D型フリップフロップ182では、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、が接続される。D型フリップフロップ182は、出力端子Qから出力信号D0を出力する。D型フリップフロップ182は、出力端子QBからの出力信号(D0の反転信号)をD型フリップフロップ183のクロック端子に供給する。

【0127】

D型フリップフロップ183では、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、が接続される。D型フリップフロップ182は、出力端子Qから出力信号D1を出力する。D型フリップフロップ182は、出力端子QBからの出力信号(D1の反転信号)をD型フリップフロップ184のクロック端子に供給する。

【0128】

D型フリップフロップ184では、出力端子Qからの出力信号の反転信号を出力する出力端子QBと、入力端子Dと、が接続される。D型フリップフロップ182は、出力端子Qから出力信号D2を出力する。

【0129】

上述の出力信号D0、D1、D2の順に下位から連結させた3ビット値が、タイミングカウント値(タイミング情報)としてトレースメッセージ生成回路132に供給される。

【0130】

続いて、図15、図16のタイミングチャートに各信号の出力信号を示す。なお、各回路の出力信号(値の変化)は、上述の回路構成に基づいて当然に理解できるため、詳細な説明は省略する。

【0131】

ここで、[D2,D1,D0](信号D0〜D2より生成される3ビット値)は、トレースデータの入力毎にカウントアップし、"111"となった後にリセット("000")される。

【0132】

上述の構成であっても、トレースデータの出力タイミングを正確に把握することができる。すなわち、同時に出力されたトレースデータを把握することができる。なお、トレースメモリ書き込み制御回路144は、本実施の形態においてタイミングフラグを扱う場合と略同一の手法でタイミングカウント値を参照し、トレースメッセージの書き込みを制御すればよい。

【0133】

なお、上述の説明では、3ビットのカウント値を用いて説明を行ったが、nビットの任意のカウント値を用いれば良い。

【0134】

本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0135】

10 インサーキットエミュレータ

110 第1プロセッサ

111 第1CPUコア

120 第2プロセッサ

121 第2CPUコア

130 タイムスタンプ取得回路

131 タイミング情報生成回路

132 トレースメッセージ生成回路

133 OVFフラグ

134 タイミング情報

135 タイムスタンプカウンタ

136 トレースメッセージバッファ

140 オーバーフローカウンタ制御回路

141 OVFカウンタ

142 OVFカウント値生成回路

143 OVFカウント値バッファ

144 トレースメモリ書き込み制御回路

145 レジスタ

150 トレースメモリ

160 ホストIF

171、175,180 OR回路

172 AND回路

173、177、179、182、183、184 D型フリップフロップ

174、178 NOT回路

176、181 Dラッチ

20 ホストコンピュータ

210 デバッグプログラム

【特許請求の範囲】

【請求項1】

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成するトレースメッセージ生成回路と、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込むトレースメモリ書き込み制御回路と、を備えるインサーキットエミュレータ。

【請求項2】

前記タイミング情報は、1ビットのビット値であり、

前記タイミング情報生成回路は、前記第1、前記第2イネーブル信号のいずれかがトレースメッセージの出力を示す値となる度に前記ビット値を反転させることを特徴とする請求項1に記載のインサーキットエミュレータ。

【請求項3】

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力をイネーブル端子の入力とし、クロック信号をデータ端子の入力とするディレイラッチと、

前記ディレイラッチの出力をクロック端子の入力とし、自身の出力の反転信号をデータ端子の入力とするフリップフロップと、

前記フリップフロップの出力信号を反転し、前記反転信号を生成するNOT回路と、を備え、

前記フリップフロップの出力信号を前記タイミング情報とすることを特徴とする請求項2に記載のインサーキットエミュレータ。

【請求項4】

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力をイネーブル端子の入力とし、クロック信号をデータ端子の入力とするディレイラッチと、

前記ディレイラッチの出力をクロック端子の入力とし、自身の出力信号の反転信号を出力する出力端子と、データ入力端子と、を接続したフリップフロップと、を備え、

前記フリップフロップの出力信号を前記タイミング情報とすることを特徴とする請求項2に記載のインサーキットエミュレータ。

【請求項5】

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力と、クロック信号と、の論理積を出力するAND回路と、

前記AND回路の出力をクロック端子の入力とし、自身の出力の反転信号をデータ端子の入力とするフリップフロップと、

前記フリップフロップの出力信号を反転し、前記反転信号を生成するNOT回路と、を備え、

前記フリップフロップの出力信号を前記タイミング情報とすることを特徴とする請求項2に記載のインサーキットエミュレータ。

【請求項6】

前記タイミング情報は、nビットのnビット値を生成し、

前記タイミング情報生成回路は、前記第1、前記第2イネーブル信号のいずれかがトレースメッセージの出力を示す値となる度に前記nビット値をカウントアップし、前記nビット値が前記nビット以上の値となるタイミングでリセットすることを特徴とする請求項1に記載のインサーキットエミュレータ。

【請求項7】

前記nビット値は、3ビット値であり、

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力をイネーブル端子の入力とし、クロック信号をデータ端子の入力とするディレイラッチと、

第1データ入力端子、第1データ出力端子、前記第1データ出力端子の反転信号を出力する第1データ反転端子、第1クロック端子を有し、前記ディレイラッチの出力を前記第1クロック端子の入力とし、前記第1データ反転端子と前記第1データ入力端子を接続した第1フリップフロップと、

第2データ入力端子、第2データ出力端子、前記第2データ出力端子の反転信号を出力する第2データ反転端子、第2クロック端子を有し、前記第1データ反転端子の出力を前記第2クロック端子の入力とし、前記第2データ反転端子と前記第2データ入力端子を接続した第2フリップフロップと、

第3データ入力端子、第3データ出力端子、前記第3データ出力端子の反転信号を出力する第3データ反転端子、第3クロック端子を有し、前記第2データ反転端子の出力を前記第3クロック端子の入力とし、前記第3データ反転端子と前記第3データ入力端子を接続した第3フリップフロップと、を有し、

前記第1データ出力端子の出力、前記第2データ出力端子の出力、前記第3データ出力端子の出力、を下位ビットから構成することにより前記第3ビット値を生成することを特徴とする請求項6に記載のインサーキットエミュレータ。

【請求項8】

所定クロックに従って、一定時間間隔を係数するタイムスタンプカウンタと、

前記タイムスタンプカウンタのオーバーフローの回数を計数するオーバーフローカウンタと、を更に備え、

前記トレースメッセージ生成回路は、前記タイムスタンプカウンタがオーバーフローしたか否かを示すオーバーフローフラグを保持し、

前記トレースメモリ書き込み制御回路は、直近に前記トレースメモリに書き込んだトレースメッセージに含まれる前記タイミング情報を保持するレジスタを備え、前記オーバーフローフラグがオンであり、かつ書き込み対象のトレースデータの前記タイミング情報と、前記レジスタの前記タイミング情報と、が一致しない場合に前記オーバーフローカウンタのカウント値を前記トレースメモリに書き込む、ことを特徴とする請求項1乃至請求項7のいずれか1項に記載のインサーキットエミュレータ。

【請求項9】

前記トレースメッセージ生成回路は、トレースメッセージの生成毎に、前記タイムスタンプカウンタ及び前記オーバーフローカウンタに対して、カウント値のリセットを要求するカウンタリセット信号を出力することを特徴とする請求項8に記載のインサーキットエミュレータ。

【請求項10】

請求項1乃至9のいずれか1項に記載のインサーキットエミュレータと、

前記トレースメモリから各トレースメッセージを読み出し、各トレースメッセージ内の前記タイミング情報に基づき、他のトレースメッセージと出力タイミングが異なるかを判別できるように各トレースメッセージを表示する表示情報を生成するデバッグプログラムを実行するホストコンピュータと、を備えるエミュレーションシステム。

【請求項11】

第1、第2プロセッサの各々からのトレースデータと、各トレースデータ取得時のタイムスタンプと、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報と、を対応付けたトレースメッセージを出力順に受け付け、トレースメモリに書き込むトレースメモリ書き込み制御回路と、

前記トレースメモリから各トレースメッセージを読み出し、各トレースメッセージ内の前記タイミング情報に基づき、他のトレースメッセージと出力タイミングが異なるかを判別できるように各トレースメッセージを表示する表示情報を生成するデバッグプログラムを実行するホストコンピュータと、を備えるトレースメモリ制御システム。

【請求項12】

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、前記タイミング情報に基づいて、各トレースメッセージを表示する制御装置に対し、生成したトレースメッセージを供給する、トレースメッセージ生成回路と、

を備えるトレースメッセージ生成装置。

【請求項13】

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を生成し、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込む、トレースメッセージ処理方法。

【請求項1】

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成するトレースメッセージ生成回路と、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込むトレースメモリ書き込み制御回路と、を備えるインサーキットエミュレータ。

【請求項2】

前記タイミング情報は、1ビットのビット値であり、

前記タイミング情報生成回路は、前記第1、前記第2イネーブル信号のいずれかがトレースメッセージの出力を示す値となる度に前記ビット値を反転させることを特徴とする請求項1に記載のインサーキットエミュレータ。

【請求項3】

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力をイネーブル端子の入力とし、クロック信号をデータ端子の入力とするディレイラッチと、

前記ディレイラッチの出力をクロック端子の入力とし、自身の出力の反転信号をデータ端子の入力とするフリップフロップと、

前記フリップフロップの出力信号を反転し、前記反転信号を生成するNOT回路と、を備え、

前記フリップフロップの出力信号を前記タイミング情報とすることを特徴とする請求項2に記載のインサーキットエミュレータ。

【請求項4】

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力をイネーブル端子の入力とし、クロック信号をデータ端子の入力とするディレイラッチと、

前記ディレイラッチの出力をクロック端子の入力とし、自身の出力信号の反転信号を出力する出力端子と、データ入力端子と、を接続したフリップフロップと、を備え、

前記フリップフロップの出力信号を前記タイミング情報とすることを特徴とする請求項2に記載のインサーキットエミュレータ。

【請求項5】

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力と、クロック信号と、の論理積を出力するAND回路と、

前記AND回路の出力をクロック端子の入力とし、自身の出力の反転信号をデータ端子の入力とするフリップフロップと、

前記フリップフロップの出力信号を反転し、前記反転信号を生成するNOT回路と、を備え、

前記フリップフロップの出力信号を前記タイミング情報とすることを特徴とする請求項2に記載のインサーキットエミュレータ。

【請求項6】

前記タイミング情報は、nビットのnビット値を生成し、

前記タイミング情報生成回路は、前記第1、前記第2イネーブル信号のいずれかがトレースメッセージの出力を示す値となる度に前記nビット値をカウントアップし、前記nビット値が前記nビット以上の値となるタイミングでリセットすることを特徴とする請求項1に記載のインサーキットエミュレータ。

【請求項7】

前記nビット値は、3ビット値であり、

前記タイミング情報生成回路は、

前記第1出力イネーブル信号と前記第2出力イネーブル信号の論理和を出力するOR回路と、

前記OR回路の出力をイネーブル端子の入力とし、クロック信号をデータ端子の入力とするディレイラッチと、

第1データ入力端子、第1データ出力端子、前記第1データ出力端子の反転信号を出力する第1データ反転端子、第1クロック端子を有し、前記ディレイラッチの出力を前記第1クロック端子の入力とし、前記第1データ反転端子と前記第1データ入力端子を接続した第1フリップフロップと、

第2データ入力端子、第2データ出力端子、前記第2データ出力端子の反転信号を出力する第2データ反転端子、第2クロック端子を有し、前記第1データ反転端子の出力を前記第2クロック端子の入力とし、前記第2データ反転端子と前記第2データ入力端子を接続した第2フリップフロップと、

第3データ入力端子、第3データ出力端子、前記第3データ出力端子の反転信号を出力する第3データ反転端子、第3クロック端子を有し、前記第2データ反転端子の出力を前記第3クロック端子の入力とし、前記第3データ反転端子と前記第3データ入力端子を接続した第3フリップフロップと、を有し、

前記第1データ出力端子の出力、前記第2データ出力端子の出力、前記第3データ出力端子の出力、を下位ビットから構成することにより前記第3ビット値を生成することを特徴とする請求項6に記載のインサーキットエミュレータ。

【請求項8】

所定クロックに従って、一定時間間隔を係数するタイムスタンプカウンタと、

前記タイムスタンプカウンタのオーバーフローの回数を計数するオーバーフローカウンタと、を更に備え、

前記トレースメッセージ生成回路は、前記タイムスタンプカウンタがオーバーフローしたか否かを示すオーバーフローフラグを保持し、

前記トレースメモリ書き込み制御回路は、直近に前記トレースメモリに書き込んだトレースメッセージに含まれる前記タイミング情報を保持するレジスタを備え、前記オーバーフローフラグがオンであり、かつ書き込み対象のトレースデータの前記タイミング情報と、前記レジスタの前記タイミング情報と、が一致しない場合に前記オーバーフローカウンタのカウント値を前記トレースメモリに書き込む、ことを特徴とする請求項1乃至請求項7のいずれか1項に記載のインサーキットエミュレータ。

【請求項9】

前記トレースメッセージ生成回路は、トレースメッセージの生成毎に、前記タイムスタンプカウンタ及び前記オーバーフローカウンタに対して、カウント値のリセットを要求するカウンタリセット信号を出力することを特徴とする請求項8に記載のインサーキットエミュレータ。

【請求項10】

請求項1乃至9のいずれか1項に記載のインサーキットエミュレータと、

前記トレースメモリから各トレースメッセージを読み出し、各トレースメッセージ内の前記タイミング情報に基づき、他のトレースメッセージと出力タイミングが異なるかを判別できるように各トレースメッセージを表示する表示情報を生成するデバッグプログラムを実行するホストコンピュータと、を備えるエミュレーションシステム。

【請求項11】

第1、第2プロセッサの各々からのトレースデータと、各トレースデータ取得時のタイムスタンプと、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報と、を対応付けたトレースメッセージを出力順に受け付け、トレースメモリに書き込むトレースメモリ書き込み制御回路と、

前記トレースメモリから各トレースメッセージを読み出し、各トレースメッセージ内の前記タイミング情報に基づき、他のトレースメッセージと出力タイミングが異なるかを判別できるように各トレースメッセージを表示する表示情報を生成するデバッグプログラムを実行するホストコンピュータと、を備えるトレースメモリ制御システム。

【請求項12】

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力するタイミング情報生成回路と、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、前記タイミング情報に基づいて、各トレースメッセージを表示する制御装置に対し、生成したトレースメッセージを供給する、トレースメッセージ生成回路と、

を備えるトレースメッセージ生成装置。

【請求項13】

第1、第2プロセッサの各々からのトレースデータの出力と同期して出力される第1、第2出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を生成し、

前記第1または前記第2のプロセッサから出力された各トレースデータと、各トレースデータ取得時のタイムスタンプと、前記タイミング情報と、を対応付けたトレースメッセージを生成し、

前記トレースメッセージ生成回路が生成したトレースメッセージをトレースメモリに書き込む、トレースメッセージ処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−109621(P2013−109621A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−254828(P2011−254828)

【出願日】平成23年11月22日(2011.11.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月22日(2011.11.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]