インターフェイス回路

【課題】ホスト機器とサブ機器との間の双方向データ伝送を行うインターフェイス回路において、待機時の消費電流をゼロにする機能を実現し、かつ安定した起動シーケンスを実現する。

【解決手段】ホスト機器1側で、差動信号の電位は、アイドル/スタンバイ状態においてプルアップ素子4によって電源電位にプルアップされている。ノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器2側では、レベル検知回路10によってコモンモード電位が所定レベルよりも下がったことを検知したとき、ノーマル状態になったと判断し、起動する。レベル検知回路10は、通常状態で消費電流が生じないバッファタイプの回路構成で実現される。

【解決手段】ホスト機器1側で、差動信号の電位は、アイドル/スタンバイ状態においてプルアップ素子4によって電源電位にプルアップされている。ノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器2側では、レベル検知回路10によってコモンモード電位が所定レベルよりも下がったことを検知したとき、ノーマル状態になったと判断し、起動する。レベル検知回路10は、通常状態で消費電流が生じないバッファタイプの回路構成で実現される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ホスト機器とメモリカード等のサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するインターフェイス回路に関する。

【背景技術】

【0002】

近年、ホスト機器とメモリカード等のサブ機器との間におけるデータ伝送方式に、様々なインターフェイスが用いられている。その中で、伝送速度を高速化する1つの手段として、差動方式が採用されている(例えば、特許文献1参照)。差動方式を用いれば、低振幅での通信が可能になり、インピーダンス整合を取った状態の理想的な伝送路であれば、数m単位の長距離においても単純な容量負荷としては見えないため、高速に信号伝送を実現することができる。

【0003】

一般に、差動方式の伝送を実現するためのインターフェイス回路は、一定の電流源で動作する回路構成のアナログ回路が多く用いられるため、消費電流が多い。

【0004】

差動インターフェイス回路の消費電流を低減する方法としては、例えば、差動インターフェイスに対し、Wakeupバッファとバイアス検出アンプを搭載し、差動の状態をそれらWakeupバッファとバイアス検出アンプによって検知してから消費電流の多い回路を起動させる方式が提案されている。(例えば、特許文献2参照)

【0005】

また、待機時の消費電流を低減させる方法としては、例えば、差動インターフェイスに対し、差動振幅を検出するアンプ回路を設け、EXOR回路等の組み合わせ回路とによって信号入力を判定する方式が提案されている。(例えば、特許文献3参照)

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−186077号公報

【特許文献2】特許第3987163号公報

【特許文献3】米国特許出願公報第2008/0218238号明細書

【発明の概要】

【発明が解決しようとする課題】

【0007】

近年の携帯端末等のモバイルAV機器においては、待機時の消費電流は、例え数μアンペア程度であっても、電池の保持期間の減少に繋がってしまうため、例えば、機器の待機時間スペックの下方設定を強いられるといった問題を引き起こす。すなわち、システム仕様上、待機時間の消費電流は限りなくゼロに近いことが好ましい。

【0008】

一方、従来の差動インターフェイスの回路方式では、待機時の消費電流をある程度削減することは可能になる。しかしながら、少なくともインターフェイスの起動を検知するための検知回路だけは、機器の待機時においても動作させておく必要がある。したがって、この検知回路について、その消費電流を限りなくゼロに近づけることが要望される。

【0009】

そこで、本発明は、ホスト機器とサブ機器との間の双方向データ伝送を行うインターフェイス回路において、待機時の消費電流をゼロにする機能を実現し、かつ安定した起動シーケンスを実現することを目的とする。

【課題を解決するための手段】

【0010】

本発明の一態様では、ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するインターフェイス回路において、

前記ホスト機器側および前記サブ機器側の少なくともいずれか一方が、データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、

前記サブ機器は、

前記差動信号のコモンモード電位のレベルを検知するレベル検知回路を備え、

前記レベル検知回路によってコモンモード電位が所定レベルよりも下がったことが検知されたとき、データ伝送がノーマル状態になったと判断し、起動する。

【0011】

この態様によると、データ伝送のアイドル/スタンバイ状態において、差動信号の電位は電源電位にプルアップされている。そして、アイドル/スタンバイ状態からノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器側では、レベル検知回路によって、コモンモード電位が所定レベルよりも下がったことを検知したとき、データ伝送がノーマル状態になったと判断し、起動する。このレベル検知回路は、コモンモード電位が所定レベルよりも下がったことが検知できればよいので、通常状態で消費電流が生じないバッファタイプの回路構成で実現することができる。すなわち、機器の待機時において、その消費電流を限りなくゼロに近づけることが可能になる。

【発明の効果】

【0012】

本発明によると、インターフェイスのレベル検知回路を消費電流ゼロでの構成を実現でき、また、起動シーケンスも安定した双方向データ伝送を実現することができる。

【図面の簡単な説明】

【0013】

【図1】実施形態に係るインターフェイス回路を含む構成を示す図である。

【図2】実施形態に係るレベル検知回路の構成の一例である。

【図3】実施形態に係るレベル検知回路の構成の一例である。

【図4】実施形態に係るレベル検知回路の構成の一例である。

【図5】実施形態に係るレベル検知回路の構成の一例である。

【図6】実施形態に係る起動時の電位レベルの変化を示す図である。

【図7】実施形態に係るレベル検知回路のシミュレーション結果を示す図である。

【図8】実施形態に係る起動シーケンスの概念を示す図である。

【図9】比較例としてのレベル検知回路の一例の構成を示す図である。

【図10】比較例としてのレベル検知回路の一例の構成を示す図である。

【図11】比較例としてのレベル検知回路の一例の構成を示す図である。

【発明を実施するための形態】

【0014】

以下、本発明の実施形態を図面に基づいて詳細に説明する。

【0015】

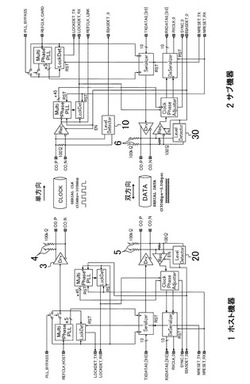

図1は本実施形態に係るインターフェイス回路を含む構成を示す図である。図1に示すように、本実施形態に係るインターフェイス回路は、ホスト機器1とサブ機器2との間で、双方向に、差動信号を用いたデータ伝送を実行する。ホスト機器1には第1のLSIが搭載され、サブ機器2には第2のLSIが搭載される。なお、第1のLSIと第2のLSIのそれぞれについても、インターフェイス回路と呼ぶものとする。

【0016】

本実施形態では、ホスト機器1側が、データ伝送のアイドル/スタンバイ状態において、差動クロックの電位を電源電圧にプルアップする機能を有している。そして、サブ機器2は、送信された差動クロックのコモンモード電位のレベルを検知するレベル検知回路10を備えており、レベル検知回路10によってコモンモード電位レベルが所定レベルよりも下がったことが検知されたとき、データ伝送がノーマル状態になったと判断し、起動する。すなわち、ホスト機器1の動作開始を、差動信号のコモンモード電位の変化によってサブ機器2が検知し、その後、サブ機器2に搭載されたインターフェイス回路が起動される。

【0017】

具体的には、次のような動作が行われる。ホスト機器1のインターフェイスが起動を開始するとき、通常、まず電源が入り、その後パワーダウン信号が解除され、所定のシーケンスによって起動される。その後、ホスト機器1とサブ機器2との通信を開始するときは、まず、ホスト機器1の差動クロック信号が差動ドライバ3を介してサブ機器2に向けて出力される。初期のアイドル/スタンバイ状態では、伝送路の電位は、プルアップ素子4によって電源電圧のレベル例えば1.8Vに固定されている。その後、差動クロックが出力されるにつれて、差動間の中間電位となるコモンモード電位は、ノーマル伝送時の安定電位例えば0.2V電位付近に向けて下降し、収束に向かう。

【0018】

サブ機器2側のレベル検知回路10は、差動信号のレベルを直接モニタするより、コモンモード電位をモニタする構成にすることが望ましい。レベル検知回路10の1段目は、基本的には一般的なバッファで構成されており、電源電圧の約半分の電位付近に閾値があるため、1.8V電源等のインターフェイスにおいては0.9V付近に閾値が決まる。つまり、コモンモード電位がアイドル/スタンバイ状態の電源電圧からノーマル状態の0.2V付近まで降下する間に、レベル検知回路10は、コモンモード電位レベルが所定レベルよりも下がったことを検知する。

【0019】

このように本実施形態によると、単純なバッファで構成されたレベル検知回路を設けるだけで、データ伝送がノーマル状態になったことを検知することが可能になる。すなわち、ノーマル状態になったことを検知するために特別な制御も必要でなく、また、アイドル/スタンバイ状態でもアクティブにしておく必要があるコンパレータ回路を用いる必要もない。したがって、双方向伝送インターフェイスにおいて、アイドル/スタンバイ状態における消費電力を限りなくゼロに近づけることが可能になる。

【0020】

また、サブ機器2は、レベル検知回路10によるレベル検知によってデータ伝送がノーマル状態になったと判断した後、次のような起動シーケンスを行う。まず、差動レシーバを起動させる。その後、PLLを起動することによってクロックを出力させる。しかしながら、PLLの出力クロックは安定に時間がかかるため、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路は、PLLの出力クロックがロックした後に、起動させるシーケンスが望ましい。

【0021】

あるいは、PLLを起動するとともに、差動レシーバで受信したクロックを、PLLをバイパスした状態で上位層へダイレクトに転送する。これにより、PLLのロック時間を待たずとも安定したクロックを上位層に渡すことができる。この場合は、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路を、上位層からリセットした後に、起動させるシーケンスが望ましい。

【0022】

このようなシーケンスにより、アナログ回路とデジタル回路を混載したインターフェイス回路の起動において、アナログ回路で差動のレベルを検知した後、デジタル回路も安定して動作させられるため、誤動作を防止することができる。

【0023】

図2はレベル検知回路10の構成の一例を示す図である。図2に示すレベル検知回路10は、コモンモード電位を入力とする第1のインバータ11と、第1のインバータ11の後段に直列に接続された第2のインバータ12とを備えている。この構成は、データ伝送のアイドル/スタンバイ状態において消費電流は実質的にゼロである。さらに、ドレインが電源に接続されるとともに、ソースが第1のインバータ11を構成する縦積みされたNMOSトランジスタ11a,11b間のノードに接続されており、かつ、ゲートに第1のインバータ11の出力ノードが接続されているNMOSトランジスタ13を備えている。このNMOSトランジスタ13を設けたことによって、ヒステリシス動作が実現される。すなわち、コモンモード電位が“L”から“H”に遷移する場合と“H”から“L”に遷移する場合とで、第1のインバータ11の閾値が異なる電位になる。したがって、図2の構成は、コモンモード電位のノイズに強くなるように、反応しない電位領域すなわち不感帯領域を有している。

【0024】

図3はレベル検知回路10の構成の他の例を示す図である。図3に示すレベル検知回路10は、図2と同様に、コモンモード電位を入力とする第1のインバータ14と、第1のインバータ14の後段に直列に接続された第2のインバータ12とを備えている。さらに、ドレインがグランドに接続されるとともに、ソースが第1のインバータ14を構成する縦積みされたPMOSトランジスタ14a,14b間のノードに接続されており、かつ、ゲートに第1のインバータ14の出力ノードが接続されているPMOSトランジスタ15を備えている。このPMOSトランジスタ15を設けたことによって、図2と同様にヒステリシス動作が実現され、よって図3の構成は、コモンモード電位のノイズに強くなるように、不感帯領域を有している。

【0025】

図2および図3のような構成によって、アイドル/スタンバイ状態での消費電流をゼロにしつつ、差動インターフェイスの起動を検知することが可能になり、かつ、コモンモード電位のノイズに対して耐性を持つことができる。

【0026】

図4はレベル検知回路10の構成の他の例を示す図である。図4に示すレベル検知回路10は、図2および図3と同様に、コモンモード電位を入力とする第1のインバータ16と、第1のインバータ16の後段に直列に接続された第2のインバータ12とを備えている。さらに、図2に示したNMOSトランジスタ13と図3に示したPMOSトランジスタ15の両方を備えている。このような構成によって、トランジスタの性能やサイズにも依存するが、一般的にトランジスタサイズが同じだとすると、PMOSトランジスタのみやNMOSトランジスタのみでヒステリシスを実現した場合と比較して、より広い不感帯領域を確保することができる。

【0027】

図5はレベル検知回路10の構成の他の例を示す図である。図5に示すレベル検知回路10は、コンパレータタイプの回路構成であるが、図2〜図4に示したインバータ2段構成のレベル検知回路と基本的に同等の機能を有している。図5において、コンパレータ17は、コモンモード電位と所定の参照電位とを入力としている。参照電位は、直列に接続された抵抗18a,18bによって電源電圧を抵抗分割することによって、生成されている。また、コンパレータ17の電流源となるPMOSトランジスタ17aは、ゲートにコモンモード電位と同一電位が与えられている。

【0028】

このような構成によって、アイドル/スタンバイ状態において、コモンモード電位が電源電圧にプルアップされていることから、コンパレータ17の電流源となるPMOSトランジスタ17aは、ゲート電位が電源電圧になるため、電流が流れない。すなわち、アイドル/スタンバイ状態において、レベル検知回路10の消費電流をゼロにすることができる。一方、ホスト機器がデータ伝送を開始すると、コモンモード電位が例えば0.2V程度まで降下するため、電源電圧レベルから0.2Vまでの遷移期間を含め、コンパレータ17はアクティブになる。すなわち、アイドル/スタンバイ状態での消費電流をゼロにしつつ、差動インターフェイスの起動を検知することが可能になる。

【0029】

図9〜図11は比較例としてのレベル検知回路の一例を示す。図9のレベル検知回路では、コンパレータの電流源となるPMOSトランジスタに所定電位VREFが印加されているため、一定の電流が定常的に流れている。図10の構成は、単純な構成ではあるが、プロセスや温度の特性ばらつきに弱いだけでなく、レベル低下を一旦検知してしまうと、その後、電流が流れ続ける、という問題がある。また図11の構成は、電流源を持たないコンパレータタイプの回路構成であるが、図10の構成と同様に、プロセスや温度の特性ばらつきに弱いだけでなく、レベル低下を一旦検知してしまうと、その後電流が流れ続けてしまう、という問題がある。

【0030】

図6は本実施形態における起動時の電位レベルの変化を示す図である。図6に示すように、データ伝送がアイドル/スタンバイ状態のときは、差動信号のレベルはいずれも電源電位VDDになっている。この状態からノーマル状態に移行する場合には、差動信号のプラス/マイナスの関係を保ったまま、すなわち、差動信号が“H”(High)または“L”(Low)を示したまま、コモンモード電位を下げていくのが好ましい。これにより、差動信号の値がトグルしたままコモンモード電位を下げる場合に比べて、コモンモードノイズによるコモンモード電位の揺れが少なくなり、より安定するため、レベル検知回路の誤動作を防止することができる。

【0031】

図7は本実施形態に係るレベル検知回路の実際のシミュレーション結果を示す図である。Y軸が検知した電位を示し、X軸は温度とトランジスタのプロセスバリエーションを示す。typはアベレージの特性のことを示し、sはトランジスタの反応が遅いSlow、fは反応の速いFastのことを示す。この結果は、図2〜図5のレベル検知回路によって、どの条件においても、ヒステリシス動作を実現することができ、反応しない不感帯領域を実現できることを証明する。

【0032】

図8は本実施形態に係るレベル検知後の推奨起動シーケンスを示す図である。まず、サブ機器側は初期状態において完全に停止した状態である。ホスト機器が差動信号を送信開始するとともに、サブ機器のレベル検知回路が、アイドル/スタンバイ状態からのアクティブ遷移の検知をコモンモードの電位レベルで行う。サブ機器はその後、起動シーケンスによって、差動レシーバを起動させ、その後PLLを起動し、ロック検知や位相調整回路やシリアルパラレル変換回路などフリップフロップを含むデジタル回路を起動させる。

【0033】

具体的には、PLLを起動すると同時に、差動レシーバで受信したクロックを、PLLをバイパスした状態で上位層へダイレクトに転送するため、まずREFCLK_CARDの信号が出力される。上位層からパワーダウン信号となるNPWDN信号を解除して、アクティブ状態にさせる。その後、PLLの出力信号となるPLLCLK信号が発振し始めるが、通常しばらくの間位相引き込み等の安定時間がかかるため、周波数が不安定な状態が続く。その後にPLLのデジタル回路部のリセット信号となるNRESET_RX_PLL信号を解除し、サブ機器の受信側デジタル回路のリセット信号となるNRESET_RX信号を解除することで、PLLの位相調整回路やシリアルパラレル変換回路などフリップフロップを含むデジタル回路をリセットし、安定した起動シーケンスを実現することが可能となる。

【0034】

また、実際の回路実装としては、PLLの出力クロックのロック状態を検知するロック検知回路を搭載し、起動後にPLLが安定したことを検知してアサートされるLOCKDET信号を元に、ホスト機器とカード機器間通信のノーマル伝送状態へとシフトするシーケンスが望ましい。

【0035】

これにより、アナログ回路とデジタル回路を混載したインターフェイス回路の起動を、差動信号レベルを検知することによって行うことができ、その後安定してノーマル伝送状態へシフトさせるシーケンスが実現できる。

【0036】

なお、図1に示すように、ホスト機器1側が、データ伝送のアイドル/スタンバイ状態において、プルアップ素子5によって差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、差動データ端子におけるコモンモード電位を検知するレベル検知回路20を備えているようにしてもよい。

【0037】

また、サブ機器2側が、データ伝送のアイドル/スタンバイ状態において、プルアップ素子6によって差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、差動クロック端子におけるコモンモード電位を検知する第1のレベル検知回路10と、差動データ端子におけるコモンモード電位を検知する第2のレベル検知回路30とを備えているようにしてもよい。

【産業上の利用可能性】

【0038】

本発明のインターフェイス回路では、待機時において消費電流がゼロの構成を実現でき、起動シーケンスも安定した双方向データ伝送を実現することができるので、例えば、携帯端末等モバイル機器のSDカード用インターフェイスに有用である。

【符号の説明】

【0039】

1 ホスト機器

2 サブ機器

10 レベル検知回路

11,14,16 第1のインバータ

11a,11b 縦積みされたNMOSトランジスタ

12 第2のインバータ

13 NMOSトランジスタ

14a,14b 縦積みされたPMOSトランジスタ

15 PMOSトランジスタ

17 コンパレータ

17a 電流源となるトランジスタ

【技術分野】

【0001】

本発明は、ホスト機器とメモリカード等のサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するインターフェイス回路に関する。

【背景技術】

【0002】

近年、ホスト機器とメモリカード等のサブ機器との間におけるデータ伝送方式に、様々なインターフェイスが用いられている。その中で、伝送速度を高速化する1つの手段として、差動方式が採用されている(例えば、特許文献1参照)。差動方式を用いれば、低振幅での通信が可能になり、インピーダンス整合を取った状態の理想的な伝送路であれば、数m単位の長距離においても単純な容量負荷としては見えないため、高速に信号伝送を実現することができる。

【0003】

一般に、差動方式の伝送を実現するためのインターフェイス回路は、一定の電流源で動作する回路構成のアナログ回路が多く用いられるため、消費電流が多い。

【0004】

差動インターフェイス回路の消費電流を低減する方法としては、例えば、差動インターフェイスに対し、Wakeupバッファとバイアス検出アンプを搭載し、差動の状態をそれらWakeupバッファとバイアス検出アンプによって検知してから消費電流の多い回路を起動させる方式が提案されている。(例えば、特許文献2参照)

【0005】

また、待機時の消費電流を低減させる方法としては、例えば、差動インターフェイスに対し、差動振幅を検出するアンプ回路を設け、EXOR回路等の組み合わせ回路とによって信号入力を判定する方式が提案されている。(例えば、特許文献3参照)

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−186077号公報

【特許文献2】特許第3987163号公報

【特許文献3】米国特許出願公報第2008/0218238号明細書

【発明の概要】

【発明が解決しようとする課題】

【0007】

近年の携帯端末等のモバイルAV機器においては、待機時の消費電流は、例え数μアンペア程度であっても、電池の保持期間の減少に繋がってしまうため、例えば、機器の待機時間スペックの下方設定を強いられるといった問題を引き起こす。すなわち、システム仕様上、待機時間の消費電流は限りなくゼロに近いことが好ましい。

【0008】

一方、従来の差動インターフェイスの回路方式では、待機時の消費電流をある程度削減することは可能になる。しかしながら、少なくともインターフェイスの起動を検知するための検知回路だけは、機器の待機時においても動作させておく必要がある。したがって、この検知回路について、その消費電流を限りなくゼロに近づけることが要望される。

【0009】

そこで、本発明は、ホスト機器とサブ機器との間の双方向データ伝送を行うインターフェイス回路において、待機時の消費電流をゼロにする機能を実現し、かつ安定した起動シーケンスを実現することを目的とする。

【課題を解決するための手段】

【0010】

本発明の一態様では、ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するインターフェイス回路において、

前記ホスト機器側および前記サブ機器側の少なくともいずれか一方が、データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、

前記サブ機器は、

前記差動信号のコモンモード電位のレベルを検知するレベル検知回路を備え、

前記レベル検知回路によってコモンモード電位が所定レベルよりも下がったことが検知されたとき、データ伝送がノーマル状態になったと判断し、起動する。

【0011】

この態様によると、データ伝送のアイドル/スタンバイ状態において、差動信号の電位は電源電位にプルアップされている。そして、アイドル/スタンバイ状態からノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器側では、レベル検知回路によって、コモンモード電位が所定レベルよりも下がったことを検知したとき、データ伝送がノーマル状態になったと判断し、起動する。このレベル検知回路は、コモンモード電位が所定レベルよりも下がったことが検知できればよいので、通常状態で消費電流が生じないバッファタイプの回路構成で実現することができる。すなわち、機器の待機時において、その消費電流を限りなくゼロに近づけることが可能になる。

【発明の効果】

【0012】

本発明によると、インターフェイスのレベル検知回路を消費電流ゼロでの構成を実現でき、また、起動シーケンスも安定した双方向データ伝送を実現することができる。

【図面の簡単な説明】

【0013】

【図1】実施形態に係るインターフェイス回路を含む構成を示す図である。

【図2】実施形態に係るレベル検知回路の構成の一例である。

【図3】実施形態に係るレベル検知回路の構成の一例である。

【図4】実施形態に係るレベル検知回路の構成の一例である。

【図5】実施形態に係るレベル検知回路の構成の一例である。

【図6】実施形態に係る起動時の電位レベルの変化を示す図である。

【図7】実施形態に係るレベル検知回路のシミュレーション結果を示す図である。

【図8】実施形態に係る起動シーケンスの概念を示す図である。

【図9】比較例としてのレベル検知回路の一例の構成を示す図である。

【図10】比較例としてのレベル検知回路の一例の構成を示す図である。

【図11】比較例としてのレベル検知回路の一例の構成を示す図である。

【発明を実施するための形態】

【0014】

以下、本発明の実施形態を図面に基づいて詳細に説明する。

【0015】

図1は本実施形態に係るインターフェイス回路を含む構成を示す図である。図1に示すように、本実施形態に係るインターフェイス回路は、ホスト機器1とサブ機器2との間で、双方向に、差動信号を用いたデータ伝送を実行する。ホスト機器1には第1のLSIが搭載され、サブ機器2には第2のLSIが搭載される。なお、第1のLSIと第2のLSIのそれぞれについても、インターフェイス回路と呼ぶものとする。

【0016】

本実施形態では、ホスト機器1側が、データ伝送のアイドル/スタンバイ状態において、差動クロックの電位を電源電圧にプルアップする機能を有している。そして、サブ機器2は、送信された差動クロックのコモンモード電位のレベルを検知するレベル検知回路10を備えており、レベル検知回路10によってコモンモード電位レベルが所定レベルよりも下がったことが検知されたとき、データ伝送がノーマル状態になったと判断し、起動する。すなわち、ホスト機器1の動作開始を、差動信号のコモンモード電位の変化によってサブ機器2が検知し、その後、サブ機器2に搭載されたインターフェイス回路が起動される。

【0017】

具体的には、次のような動作が行われる。ホスト機器1のインターフェイスが起動を開始するとき、通常、まず電源が入り、その後パワーダウン信号が解除され、所定のシーケンスによって起動される。その後、ホスト機器1とサブ機器2との通信を開始するときは、まず、ホスト機器1の差動クロック信号が差動ドライバ3を介してサブ機器2に向けて出力される。初期のアイドル/スタンバイ状態では、伝送路の電位は、プルアップ素子4によって電源電圧のレベル例えば1.8Vに固定されている。その後、差動クロックが出力されるにつれて、差動間の中間電位となるコモンモード電位は、ノーマル伝送時の安定電位例えば0.2V電位付近に向けて下降し、収束に向かう。

【0018】

サブ機器2側のレベル検知回路10は、差動信号のレベルを直接モニタするより、コモンモード電位をモニタする構成にすることが望ましい。レベル検知回路10の1段目は、基本的には一般的なバッファで構成されており、電源電圧の約半分の電位付近に閾値があるため、1.8V電源等のインターフェイスにおいては0.9V付近に閾値が決まる。つまり、コモンモード電位がアイドル/スタンバイ状態の電源電圧からノーマル状態の0.2V付近まで降下する間に、レベル検知回路10は、コモンモード電位レベルが所定レベルよりも下がったことを検知する。

【0019】

このように本実施形態によると、単純なバッファで構成されたレベル検知回路を設けるだけで、データ伝送がノーマル状態になったことを検知することが可能になる。すなわち、ノーマル状態になったことを検知するために特別な制御も必要でなく、また、アイドル/スタンバイ状態でもアクティブにしておく必要があるコンパレータ回路を用いる必要もない。したがって、双方向伝送インターフェイスにおいて、アイドル/スタンバイ状態における消費電力を限りなくゼロに近づけることが可能になる。

【0020】

また、サブ機器2は、レベル検知回路10によるレベル検知によってデータ伝送がノーマル状態になったと判断した後、次のような起動シーケンスを行う。まず、差動レシーバを起動させる。その後、PLLを起動することによってクロックを出力させる。しかしながら、PLLの出力クロックは安定に時間がかかるため、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路は、PLLの出力クロックがロックした後に、起動させるシーケンスが望ましい。

【0021】

あるいは、PLLを起動するとともに、差動レシーバで受信したクロックを、PLLをバイパスした状態で上位層へダイレクトに転送する。これにより、PLLのロック時間を待たずとも安定したクロックを上位層に渡すことができる。この場合は、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路を、上位層からリセットした後に、起動させるシーケンスが望ましい。

【0022】

このようなシーケンスにより、アナログ回路とデジタル回路を混載したインターフェイス回路の起動において、アナログ回路で差動のレベルを検知した後、デジタル回路も安定して動作させられるため、誤動作を防止することができる。

【0023】

図2はレベル検知回路10の構成の一例を示す図である。図2に示すレベル検知回路10は、コモンモード電位を入力とする第1のインバータ11と、第1のインバータ11の後段に直列に接続された第2のインバータ12とを備えている。この構成は、データ伝送のアイドル/スタンバイ状態において消費電流は実質的にゼロである。さらに、ドレインが電源に接続されるとともに、ソースが第1のインバータ11を構成する縦積みされたNMOSトランジスタ11a,11b間のノードに接続されており、かつ、ゲートに第1のインバータ11の出力ノードが接続されているNMOSトランジスタ13を備えている。このNMOSトランジスタ13を設けたことによって、ヒステリシス動作が実現される。すなわち、コモンモード電位が“L”から“H”に遷移する場合と“H”から“L”に遷移する場合とで、第1のインバータ11の閾値が異なる電位になる。したがって、図2の構成は、コモンモード電位のノイズに強くなるように、反応しない電位領域すなわち不感帯領域を有している。

【0024】

図3はレベル検知回路10の構成の他の例を示す図である。図3に示すレベル検知回路10は、図2と同様に、コモンモード電位を入力とする第1のインバータ14と、第1のインバータ14の後段に直列に接続された第2のインバータ12とを備えている。さらに、ドレインがグランドに接続されるとともに、ソースが第1のインバータ14を構成する縦積みされたPMOSトランジスタ14a,14b間のノードに接続されており、かつ、ゲートに第1のインバータ14の出力ノードが接続されているPMOSトランジスタ15を備えている。このPMOSトランジスタ15を設けたことによって、図2と同様にヒステリシス動作が実現され、よって図3の構成は、コモンモード電位のノイズに強くなるように、不感帯領域を有している。

【0025】

図2および図3のような構成によって、アイドル/スタンバイ状態での消費電流をゼロにしつつ、差動インターフェイスの起動を検知することが可能になり、かつ、コモンモード電位のノイズに対して耐性を持つことができる。

【0026】

図4はレベル検知回路10の構成の他の例を示す図である。図4に示すレベル検知回路10は、図2および図3と同様に、コモンモード電位を入力とする第1のインバータ16と、第1のインバータ16の後段に直列に接続された第2のインバータ12とを備えている。さらに、図2に示したNMOSトランジスタ13と図3に示したPMOSトランジスタ15の両方を備えている。このような構成によって、トランジスタの性能やサイズにも依存するが、一般的にトランジスタサイズが同じだとすると、PMOSトランジスタのみやNMOSトランジスタのみでヒステリシスを実現した場合と比較して、より広い不感帯領域を確保することができる。

【0027】

図5はレベル検知回路10の構成の他の例を示す図である。図5に示すレベル検知回路10は、コンパレータタイプの回路構成であるが、図2〜図4に示したインバータ2段構成のレベル検知回路と基本的に同等の機能を有している。図5において、コンパレータ17は、コモンモード電位と所定の参照電位とを入力としている。参照電位は、直列に接続された抵抗18a,18bによって電源電圧を抵抗分割することによって、生成されている。また、コンパレータ17の電流源となるPMOSトランジスタ17aは、ゲートにコモンモード電位と同一電位が与えられている。

【0028】

このような構成によって、アイドル/スタンバイ状態において、コモンモード電位が電源電圧にプルアップされていることから、コンパレータ17の電流源となるPMOSトランジスタ17aは、ゲート電位が電源電圧になるため、電流が流れない。すなわち、アイドル/スタンバイ状態において、レベル検知回路10の消費電流をゼロにすることができる。一方、ホスト機器がデータ伝送を開始すると、コモンモード電位が例えば0.2V程度まで降下するため、電源電圧レベルから0.2Vまでの遷移期間を含め、コンパレータ17はアクティブになる。すなわち、アイドル/スタンバイ状態での消費電流をゼロにしつつ、差動インターフェイスの起動を検知することが可能になる。

【0029】

図9〜図11は比較例としてのレベル検知回路の一例を示す。図9のレベル検知回路では、コンパレータの電流源となるPMOSトランジスタに所定電位VREFが印加されているため、一定の電流が定常的に流れている。図10の構成は、単純な構成ではあるが、プロセスや温度の特性ばらつきに弱いだけでなく、レベル低下を一旦検知してしまうと、その後、電流が流れ続ける、という問題がある。また図11の構成は、電流源を持たないコンパレータタイプの回路構成であるが、図10の構成と同様に、プロセスや温度の特性ばらつきに弱いだけでなく、レベル低下を一旦検知してしまうと、その後電流が流れ続けてしまう、という問題がある。

【0030】

図6は本実施形態における起動時の電位レベルの変化を示す図である。図6に示すように、データ伝送がアイドル/スタンバイ状態のときは、差動信号のレベルはいずれも電源電位VDDになっている。この状態からノーマル状態に移行する場合には、差動信号のプラス/マイナスの関係を保ったまま、すなわち、差動信号が“H”(High)または“L”(Low)を示したまま、コモンモード電位を下げていくのが好ましい。これにより、差動信号の値がトグルしたままコモンモード電位を下げる場合に比べて、コモンモードノイズによるコモンモード電位の揺れが少なくなり、より安定するため、レベル検知回路の誤動作を防止することができる。

【0031】

図7は本実施形態に係るレベル検知回路の実際のシミュレーション結果を示す図である。Y軸が検知した電位を示し、X軸は温度とトランジスタのプロセスバリエーションを示す。typはアベレージの特性のことを示し、sはトランジスタの反応が遅いSlow、fは反応の速いFastのことを示す。この結果は、図2〜図5のレベル検知回路によって、どの条件においても、ヒステリシス動作を実現することができ、反応しない不感帯領域を実現できることを証明する。

【0032】

図8は本実施形態に係るレベル検知後の推奨起動シーケンスを示す図である。まず、サブ機器側は初期状態において完全に停止した状態である。ホスト機器が差動信号を送信開始するとともに、サブ機器のレベル検知回路が、アイドル/スタンバイ状態からのアクティブ遷移の検知をコモンモードの電位レベルで行う。サブ機器はその後、起動シーケンスによって、差動レシーバを起動させ、その後PLLを起動し、ロック検知や位相調整回路やシリアルパラレル変換回路などフリップフロップを含むデジタル回路を起動させる。

【0033】

具体的には、PLLを起動すると同時に、差動レシーバで受信したクロックを、PLLをバイパスした状態で上位層へダイレクトに転送するため、まずREFCLK_CARDの信号が出力される。上位層からパワーダウン信号となるNPWDN信号を解除して、アクティブ状態にさせる。その後、PLLの出力信号となるPLLCLK信号が発振し始めるが、通常しばらくの間位相引き込み等の安定時間がかかるため、周波数が不安定な状態が続く。その後にPLLのデジタル回路部のリセット信号となるNRESET_RX_PLL信号を解除し、サブ機器の受信側デジタル回路のリセット信号となるNRESET_RX信号を解除することで、PLLの位相調整回路やシリアルパラレル変換回路などフリップフロップを含むデジタル回路をリセットし、安定した起動シーケンスを実現することが可能となる。

【0034】

また、実際の回路実装としては、PLLの出力クロックのロック状態を検知するロック検知回路を搭載し、起動後にPLLが安定したことを検知してアサートされるLOCKDET信号を元に、ホスト機器とカード機器間通信のノーマル伝送状態へとシフトするシーケンスが望ましい。

【0035】

これにより、アナログ回路とデジタル回路を混載したインターフェイス回路の起動を、差動信号レベルを検知することによって行うことができ、その後安定してノーマル伝送状態へシフトさせるシーケンスが実現できる。

【0036】

なお、図1に示すように、ホスト機器1側が、データ伝送のアイドル/スタンバイ状態において、プルアップ素子5によって差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、差動データ端子におけるコモンモード電位を検知するレベル検知回路20を備えているようにしてもよい。

【0037】

また、サブ機器2側が、データ伝送のアイドル/スタンバイ状態において、プルアップ素子6によって差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、差動クロック端子におけるコモンモード電位を検知する第1のレベル検知回路10と、差動データ端子におけるコモンモード電位を検知する第2のレベル検知回路30とを備えているようにしてもよい。

【産業上の利用可能性】

【0038】

本発明のインターフェイス回路では、待機時において消費電流がゼロの構成を実現でき、起動シーケンスも安定した双方向データ伝送を実現することができるので、例えば、携帯端末等モバイル機器のSDカード用インターフェイスに有用である。

【符号の説明】

【0039】

1 ホスト機器

2 サブ機器

10 レベル検知回路

11,14,16 第1のインバータ

11a,11b 縦積みされたNMOSトランジスタ

12 第2のインバータ

13 NMOSトランジスタ

14a,14b 縦積みされたPMOSトランジスタ

15 PMOSトランジスタ

17 コンパレータ

17a 電流源となるトランジスタ

【特許請求の範囲】

【請求項1】

ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するインターフェイス回路であって、

前記ホスト機器側および前記サブ機器側の少なくともいずれか一方が、データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、

前記サブ機器は、

前記差動信号のコモンモード電位のレベルを検知するレベル検知回路を備え、

前記レベル検知回路によってコモンモード電位が所定レベルよりも下がったことが検知されたとき、データ伝送がノーマル状態になったと判断し、起動する

ことを特徴とするインターフェイス回路。

【請求項2】

請求項1記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位を入力とする第1のインバータと、

前記第1のインバータの後段に直列に接続された第2のインバータと、

ドレインが電源に接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のNMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているNMOSトランジスタとを備えたものである

ことを特徴とするインターフェイス回路。

【請求項3】

請求項1記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位を入力とする第1のインバータと、

前記第1のインバータの後段に直列に接続された第2のインバータと、

ドレインがグランドに接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のPMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているPMOSトランジスタとを備えたものである

ことを特徴とするインターフェイス回路。

【請求項4】

請求項1記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位を入力とする第1のインバータと、

前記第1のインバータの後段に直列に接続された第2のインバータと、

ドレインが電源に接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のNMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているNMOSトランジスタと、

ドレインがグランドに接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のPMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているPMOSトランジスタとを備えたものである

ことを特徴とするインターフェイス回路。

【請求項5】

請求項1に記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位と、所定の参照電位とを入力とするコンパレータを備え、

前記コンパレータの電流源となるトランジスタは、ゲートに、前記コモンモード電位が与えられている

ことを特徴とするインターフェイス回路。

【請求項6】

請求項1に記載のインターフェイス回路において、

前記サブ機器は、前記レベル検知回路によるレベル検知によってデータ伝送がノーマル状態になったと判断した後、起動シーケンスにおいて、

差動レシーバを起動させ、

その後、PLLを起動させ、

その後、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路を起動させる

ことを特徴とするインターフェイス回路。

【請求項7】

請求項1に記載のインターフェイス回路において、

前記サブ機器は、前記レベル検知回路によるレベル検知によってデータ伝送がノーマル状態になったと判断した後、起動シーケンスにおいて、

差動レシーバを起動させ、

その後、PLLを起動するとともに、差動レシーバで受信したクロックを、PLLをバイパスして上位層へ転送し、

その後、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路を、上位層からリセットした後に起動させる

ことを特徴とするインターフェイス回路。

【請求項8】

請求項1記載のインターフェイス回路において、

前記ホスト機器側および前記サブ機器側の少なくともいずれか一方は、アイドル/スタンバイ状態からノーマル状態に移行するとき、差動信号がHighまたはLowを示す状態を保ったまま、コモンモード電位を下げる

ことを特徴とするインターフェイス回路。

【請求項9】

ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するために、前記ホスト機器に搭載されたインターフェイス回路であって、

データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、

差動データ端子におけるコモンモード電位を検知するレベル検知回路を備えている

ことを特徴とするインターフェイス回路。

【請求項10】

ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するために、前記サブ機器に搭載されたインターフェイス回路であって、

データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、

差動クロック端子におけるコモンモード電位を検知する第1のレベル検知回路と、

差動データ端子におけるコモンモード電位を検知する第2のレベル検知回路とを備えている

ことを特徴とするインターフェイス回路。

【請求項1】

ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するインターフェイス回路であって、

前記ホスト機器側および前記サブ機器側の少なくともいずれか一方が、データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、

前記サブ機器は、

前記差動信号のコモンモード電位のレベルを検知するレベル検知回路を備え、

前記レベル検知回路によってコモンモード電位が所定レベルよりも下がったことが検知されたとき、データ伝送がノーマル状態になったと判断し、起動する

ことを特徴とするインターフェイス回路。

【請求項2】

請求項1記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位を入力とする第1のインバータと、

前記第1のインバータの後段に直列に接続された第2のインバータと、

ドレインが電源に接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のNMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているNMOSトランジスタとを備えたものである

ことを特徴とするインターフェイス回路。

【請求項3】

請求項1記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位を入力とする第1のインバータと、

前記第1のインバータの後段に直列に接続された第2のインバータと、

ドレインがグランドに接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のPMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているPMOSトランジスタとを備えたものである

ことを特徴とするインターフェイス回路。

【請求項4】

請求項1記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位を入力とする第1のインバータと、

前記第1のインバータの後段に直列に接続された第2のインバータと、

ドレインが電源に接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のNMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているNMOSトランジスタと、

ドレインがグランドに接続されるとともに、ソースが前記第1のインバータを構成する縦積みされた複数のPMOSトランジスタの間のノードに接続されており、かつ、ゲートに前記第1のインバータの出力ノードが接続されているPMOSトランジスタとを備えたものである

ことを特徴とするインターフェイス回路。

【請求項5】

請求項1に記載のインターフェイス回路において、

前記レベル検知回路は、

前記コモンモード電位と、所定の参照電位とを入力とするコンパレータを備え、

前記コンパレータの電流源となるトランジスタは、ゲートに、前記コモンモード電位が与えられている

ことを特徴とするインターフェイス回路。

【請求項6】

請求項1に記載のインターフェイス回路において、

前記サブ機器は、前記レベル検知回路によるレベル検知によってデータ伝送がノーマル状態になったと判断した後、起動シーケンスにおいて、

差動レシーバを起動させ、

その後、PLLを起動させ、

その後、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路を起動させる

ことを特徴とするインターフェイス回路。

【請求項7】

請求項1に記載のインターフェイス回路において、

前記サブ機器は、前記レベル検知回路によるレベル検知によってデータ伝送がノーマル状態になったと判断した後、起動シーケンスにおいて、

差動レシーバを起動させ、

その後、PLLを起動するとともに、差動レシーバで受信したクロックを、PLLをバイパスして上位層へ転送し、

その後、ロック検知回路、位相調整回路およびシリアルパラレル変換回路などフリップフロップを含むデジタル回路を、上位層からリセットした後に起動させる

ことを特徴とするインターフェイス回路。

【請求項8】

請求項1記載のインターフェイス回路において、

前記ホスト機器側および前記サブ機器側の少なくともいずれか一方は、アイドル/スタンバイ状態からノーマル状態に移行するとき、差動信号がHighまたはLowを示す状態を保ったまま、コモンモード電位を下げる

ことを特徴とするインターフェイス回路。

【請求項9】

ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するために、前記ホスト機器に搭載されたインターフェイス回路であって、

データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、

差動データ端子におけるコモンモード電位を検知するレベル検知回路を備えている

ことを特徴とするインターフェイス回路。

【請求項10】

ホスト機器とサブ機器との間で双方向に差動信号を用いたデータ伝送を実行するために、前記サブ機器に搭載されたインターフェイス回路であって、

データ伝送のアイドル/スタンバイ状態において、差動信号の電位を電源電圧にプルアップする機能を有しており、かつ、

差動クロック端子におけるコモンモード電位を検知する第1のレベル検知回路と、

差動データ端子におけるコモンモード電位を検知する第2のレベル検知回路とを備えている

ことを特徴とするインターフェイス回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−42195(P2013−42195A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2009−284138(P2009−284138)

【出願日】平成21年12月15日(2009.12.15)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成21年12月15日(2009.12.15)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]