インターポーザ及びそれを用いた半導体モジュール

【課題】 二つの熱源の間に配置した際に、それら熱源間での熱伝導をより効果的に抑制することができるインターポーザを提供する。

【解決手段】 インターポーザ24は、真空に維持されたキャビティ23を有する本体と、本体の上壁20aと下壁20bにそれぞれ形成された絶縁層22a及び22bと、絶縁層22a及び22bの上にそれぞれ形成された熱反射層21a及び21bとを備える。インターポーザ24は、その上下に搭載された半導体デバイス11aと12aの間を熱的に絶縁する。

【解決手段】 インターポーザ24は、真空に維持されたキャビティ23を有する本体と、本体の上壁20aと下壁20bにそれぞれ形成された絶縁層22a及び22bと、絶縁層22a及び22bの上にそれぞれ形成された熱反射層21a及び21bとを備える。インターポーザ24は、その上下に搭載された半導体デバイス11aと12aの間を熱的に絶縁する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイスの実装技術に関し、さらに言えば、消費電力の大きい半導体デバイスの動作温度の上昇を抑えて安定に動作させることができるインターポーザと、そのインターポーザを用いた半導体モジュールに関するものである。

【背景技術】

【0002】

近年、シリコンを代表とする半導体工業分野の技術進歩は大きく、工業用、民生用を問わず、機器やシステムの小型化、軽量化、低価格化、高機能化などに大きく寄与するに至っている。一方、半導体デバイスへの要求はとどまることがなく、より一層の高集積化、高速化、高度化が期待されると共に、小型化も期待されている。これらの要求に応える策として、半導体デバイスを構成する単位素子(例えばトランジスタ)の寸法を微小化し、搭載される単位素子の数を増大させることがある。この策の利点は、微小化に伴う動作速度の増大(高速化)、高集積化に伴う機能の増大(あるいは必要とされる半導体デバイス数の減少)である。しかしながら、高速化や高集積化に伴い半導体デバイスの内部での消費電力が大きくなり、動作の不安定化あるいはデバイス自体の破壊の危険性が増大する。これらの危険性を低下させるには、半導体デバイスの放熱技術(あるいは冷却技術)が必須である。

【0003】

以前から、半導体デバイスの動作温度を低くする技術が数多く開発されてきた。例えば、大電力の半導体デバイスに放熱フィン(アルミ合金製が多い)を貼り付け、このフィンに空気の流れを吹き付けることにより、半導体デバイスを冷却する技術がある。消費電力が比較的低い(例えば数ワット)場合には、この技術で解決可能である。しかし、最新の半導体デバイスでは、消費電力がいっそう大きくなっており、コンピュータのCPUなどでは100ワット以上に達することもある。このため、このような大消費電力の半導体デバイスでは、放熱が十分でないと、半導体デバイスの温度が上昇し、熱暴走あるいは熱破壊に至ることもある。したがって、半導体デバイスの動作の上限は、放熱技術に支配されているとも言える。

【0004】

半導体デバイスを複数個積層化してなる「半導体モジュール」は、比較的容易に高集積化を実現できる利点がある。このような構成では、下層に配置された半導体デバイスでの電力消費は、この半導体デバイスの温度を上昇させるだけではなく、その上層に配置された半導体デバイスの温度も上昇させる。このため、積層モジュールの上層に、特性が動作温度に敏感な半導体デバイスが配置されている場合には、積層モジュール全体の動作が不安定になる可能性がある。このため、半導体モジュールの場合には、消費電力が大きい半導体デバイスのみを冷却し、積層されている半導体デバイス間で熱伝達が生じないような実装構造が好ましい。

【0005】

積層された半導体デバイス(半導体モジュール)の冷却技術としては、従来、図11に示す実装構造が提案されている。同図は、特許文献1の図1Aとして掲載されているものである。

【0006】

図11において、チップスタック110は、符号110a、110b、110cで示された3個の半導体チップの積層体から構成されている。それぞれのチップ110a、110b、110cには、エッチングで形成されたチャネル175が設けられている(図11では、符号175は代表的なチャネルを示している)。チャネル175内に流体(冷媒)を流すことにより、チップスタック110の冷却が行われるようになっている。この流体は、積層されたチップ110a、110b、110cの間に形成された狭いチャネル175内を流動する。なお、チップ110a、110b、110cが半導体基板から構成されている場合には、その厚さは通常、数百マイクロメータ以下である。

【0007】

各半導体チップ110a、110b、110cの垂直方向には、符号123で示されたTSV(Through Silicon Via, シリコン貫通電極)によって、チップ110a、110b、110c同士は相互接続されている。

【0008】

他方、半導体モジュールでは、積層した半導体デバイスの間に「インターポーザ」と称される配線基板を挟み込むことも行われている。このインターポーザへの要求仕様としては、(1)表面と裏面の間に複数の電気接続路(例えば貫通電極)を有すること、(2)表面あるいは裏面に、あるいは表面及び裏面の双方に電気配線層(再配線層とも称される)を有すること、などがある。このような仕様を満足させると、半導体モジュールの設計および作成が容易となる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許出願公開第2009/031186号明細書

【発明の概要】

【発明が解決しようとする課題】

【0010】

図11に示した従来の半導体デバイスの実装構造では、チャネル175は、あたかも「多数の柱が林立する回廊」のように形成されており、しかも、その高さは数百マイクロメータ以下であるから、チャネル175内に流体(冷媒)を流し込むには、大きな圧力が必要である。

【0011】

また、流体の流れる方向は、図11の符号111の下側にある下向き矢印と右向き矢印で示されているが、その下向き矢印に沿ってチップスタック110の周囲に流入した流体は、右向き矢印に沿ってチップ110a、110b、110cの間にあるチャネル175内に流入するだけではなく、チップ110a、110b、110cの周囲に沿っても流動するであろう。上述したように、チャネル175の高さが低いことと、チップ110a、110b、110cの周囲には広い空間があることを考えると、チャネル175内のみに流体を流し込むことは困難であり、多くの流体はチップ110a、110b、110cの周囲に沿って流れてしまうと思われる。しかも、チップ110a、110b、110cに形成されたチャネル175の形状(流体が流れる方向の形状)は、チップ110a、110b、110c毎に異なるので、各層に形成されたチャネル175の全てにおいて均一な流体の流れを実現することも困難であろう。

【0012】

このような理由から、図11の従来の実装構造では、チップ110a、110b、110cの十分な冷却(あるいはチップ110a、110b、110cからの放熱)を実現することは、必ずしも容易ではない。

【0013】

他方、半導体モジュールにおいて、積層した半導体デバイスの間にインターポーザを挟み込むと、これら半導体デバイス間の物理的な距離が大きくなり、例えば、下層の半導体デバイスの発熱が上層の半導体デバイスに伝達されにくくなる利点がある。しかあし、上述した従来の半導体デバイスの実装技術を高度化して、消費電力の大きい半導体デバイスの動作温度の上昇を抑えて安定に動作させるためには、積層方向に隣接する半導体デバイス間での熱伝導を、積極的に、より少なくするようなインターポーザの新たな構造が望まれる。

【0014】

本発明は、以上のような事情を考慮してなされたものであり、その目的とするところは、二つの熱源の間に配置した際に、それら熱源間での熱伝導をより効果的に抑制することができるインターポーザを提供することにある。

【0015】

本発明の他の目的は、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、隣接する半導体デバイス間での熱伝導をより効果的に抑制し、もってそれら半導体デバイスの温度上昇を抑えて安定に動作させることができるインターポーザを提供することにある。

【0016】

本発明のさらに他の目的は、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイスの温度上昇を抑えて安定に動作させることができる半導体モジュールを提供することにある。

【0017】

ここに明記しない本発明の他の目的は、以下の説明及び添付図面から明らかになる。

【課題を解決するための手段】

【0018】

(1) 本発明の第1の観点によるインターポーザは、

真空に維持されたキャビティを有する本体(構造体)と、

前記キャビティの内壁面に形成された熱反射領域と

を備えていることを特徴とするものである。

【0019】

本発明の第1の観点によるインターポーザは、上述したような構成を有するので、前記本体の一方の側に配置された第1熱源(例えば半導体デバイス)から生じた熱が、伝導によって前記本体を移動する際に、その熱伝導は、真空状態にある前記キャビティによって効果的に抑制される。前記熱の一部は前記キャビティ内を伝導するが、前記キャビティの内壁面には前記熱反射領域が形成されているので、前記キャビティ内を伝導した熱の多くは、前記熱反射領域で反射され、それ以上伝導しない。したがって、前記第1熱源から前記本体中を移動して前記第2熱源に到達する熱の量は、大きく減少する。

【0020】

逆に、前記第2熱源から生じた熱が、前記本体中を移動して前記第1熱源に到達する量も、同様の理由で、非常に少なくなる。

【0021】

このように、前記第1熱源と前記第2熱源が、本発明のインターポーザによって熱的に絶縁されることになるから、本発明のインターポーザによれば、二つの熱源の間に配置した際にそれら熱源間での熱伝導をより効果的に抑制することができる。

【0022】

また、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、積層方向に隣接する半導体デバイスの間に本発明のインターポーザを介在させれば、それら半導体デバイス間での熱伝導をより効果的に抑制することができる。よって、それら半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0023】

(2) 本発明のインターポーザの好ましい例では、前記本体が、第1熱源に隣接する上壁と、第2熱源に隣接する下壁と、前記上壁と前記下壁を連結する側壁を備えており、前記上壁と前記下壁と前記側壁が前記キャビティを画定する。前記上壁と前記下壁と前記側壁は、熱伝導率が低い材料で作製することが好ましい。

【0024】

(3) 本発明のインターポーザの他の好ましい例では、前記熱反射領域が、前記上壁の内面と前記下壁の内面に形成され、前記側壁の内面には形成されない。

【0025】

(4) 本発明のインターポーザのさらに他の好ましい例では、前記上壁と前記下壁と前記側壁が、いずれも単結晶シリコンで形成される。この例では、周知の集積回路作成技術を利用して、前記インターポーザの表面と裏面、あるいは前記上壁と前記下壁に、電子回路あるいは電気配線層を容易に形成できるという利点がある。

【0026】

(5) 本発明のインターポーザのさらに他の好ましい例では、前記上壁と前記下壁が単結晶シリコンで形成され、前記側壁がガラスで形成される。この例では、シリコン単結晶とガラスとを静電接合で気密良くかつ強固に密着させることが可能であるから、真空を維持することが容易である。

【0027】

(6) 本発明のインターポーザのさらに他の好ましい例では、前記上壁と前記下壁が樹脂材料(例えば、プリント基板の素材)で形成され、前記側壁が接着性の高い樹脂材料(例えば、フォトレジスト材料である「SU−8」で形成される。この例では、シリコン単結晶とガラスとを静電接合で気密良くかつ強固に密着させることが可能であるから、真空を維持することが容易である。

【0028】

(7) 本発明のインターポーザのさらに他の好ましい例では、前記本体が貫通電極を備える。

【0029】

(8) 本発明の第2の観点による半導体モジュールは、

本発明の第1の観点によるインターポーザと、

前記インターポーザの一方の側に搭載された第1半導体デバイスと、

前記インターポーザの他方の側に搭載された第2半導体デバイスと

を備えていることを特徴とするものである。

【0030】

本発明の第2の観点による半導体モジュールは、上述した本発明の第1の観点によるインターポーザを含んでいて、そのインターポーザの両側に前記第1半導体デバイスと前記第2半導体デバイスを搭載しているので、前記第1半導体デバイスと前記第2半導体デバイスは、前記インターポーザによって熱的に絶縁される。このため、前記第1半導体デバイスと前記第2半導体デバイスの間での熱伝導をより効果的に抑制することができる。

【0031】

よって、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0032】

(9) 本発明の半導体モジュールの好ましい例では、前記第1半導体デバイスの側に装着された放熱板をさらに備える。

【0033】

(10) 本発明の半導体モジュールの他の好ましい例では、前記第1半導体デバイスと前記第2半導体デバイスと前記インターポーザを包含するケースと、冷却用流体を加圧して前記ケース内に導入する手段をさらに備える。前記ケースは、冷却用流体を導入するインレットと、前記冷却用流体を排出するアウトレットとを有する。

【0034】

(11) 本明細書では、関連する用語を下記のように定義する。

【0035】

・半導体デバイス: 以下の(i)と(ii)を含む半導体デバイス全般を指す。

【0036】

(i) ウェーハプロセスが完了し、半導体ウェーハから切り出された半導体チップ(ベアチップ)。当該半導体チップには、少なくとも1個のトランジスタ、ダイオードなどの半導体素子が配置された、いわゆる集積回路のチップを含む。

【0037】

(ii) パッケージングされた上記の半導体チップ。ボールグリッドアレイ(BGA)、チップサイズパッケージ(CSP)などと称される、種々のパッケージでパッケージングされたものが含まれる。

【0038】

・半導体モジュール: 2個以上の前記半導体デバイスが積層された構造である。積層構造を構成する各層の間の相互接続の手法には、ワイヤボンディング、貫通電極(TSV)などがあるが、その手法は問わない。なお、本明細書では、ワイヤボンディングにより層間接続された半導体モジュールを「ボンディングモジュール」、貫通電極により層間接続された半導体モジュールを「貫通電極モジュール」と呼ぶ。

【0039】

・電子部品: 受動素子とも称されている部品で、抵抗、キャパシタ(コンデンサ)、インダクタ(コイル)などがある。単一の素子(個別部品)を複数個組み合わせた構成(例えば、モジュール抵抗)もある。また、特定の機能を有するセンサやアクチュエータも、電子部品に含まれる。さらには、信号処理回路、駆動回路などが集積化された前記センサや前記アクチュエータも、電子部品に含まれる。

【0040】

・流体: 気体あるいは液体であり、熱伝導で熱を吸収することにより、放熱あるいは排熱効果を有するものである。このような機能を有する流体は、「冷媒」とも称される。具体例としては、(i)フロン類・ノンフロン類(多用されており、種類が多い)、(ii)有機化合物であるブタン、イソブタンなど、(iii)無機化合物である水素、ヘリウム、アンモニア、水、二酸化炭素などがある。

【0041】

(12) 前記熱反射領域は、前記キャビティの内壁面の全体にわたって配置されるとは限らない。前記内壁面の指定された範囲に限定して配置してもよい。例えば、前記キャビティの上壁と下壁にのみ前記熱反射領域を配置し、前記キャビティの側壁には前記熱反射領域を配置しないようにする。さらに、前記上壁の周辺部(側壁に近い部分)に前記熱反射領域を配置しないようにしてもよい。

【0042】

前記キャビティの上壁と下壁と側壁は、同一材料で形成してもよい。例えば、これらを全てシリコン単結晶で構成した場合には、周知の集積回路作成技術を利用して、前記インターポーザの表面と裏面、あるいは、前記上壁と下壁に、電子回路あるいは電気配線層を容易に形成することが可能となる。

【0043】

前記キャビティの上壁と下壁と側壁は、異なる材料で形成してもよい。例えば、上壁と下壁をシリコン単結晶で、側壁をガラスで形成してもよい。この場合、シリコン単結晶とガラスとを静電接合で気密良くかつ強固に密着させることが可能であり、前記キャビティの真空を維持しやすい。また、前記キャビティの上壁と下壁を樹脂材料(例えば、プリント基板の素材)で、側壁を接着性の高い樹脂材料(例えば、フォトレジスト材料である「SU−8」)で形成してもよい。なお、上壁と下壁と側壁は、熱伝導率が低い材料で形成することが好ましい。

【0044】

前記インターポーザの表面と裏面に、電子回路あるいは電気配線層を配置してもよい。また、前記キャビティの内壁面にも、電子回路あるいは電気配線層を配置してもよい。この場合には、前記熱反射領域が前記電子回路等の動作を阻害しない(例えば、電子回路の短絡)ようにするために、前記熱反射領域と前記電子回路等の間に絶縁層を配置することが必要となる。

【0045】

前記インターポーザには、貫通電極を形成してもよい。貫通電極を形成することにより、前記インターポーザの上方に配置された半導体デバイスからの電気信号を、前記インターポーザの下方に配置された半導体デバイスへ伝達することが可能となる。

【0046】

前記インターポーザを2個以上用いて多段の半導体モジュールを構成することもできる。例えば、第1半導体デバイスの表面に第1インターポーザを搭載し、前記第1インターポーザの表面に第2半導体デバイスを搭載し、前記第2半導体デバイスの表面に第2インターポーザを搭載し、前記第2インターポーザの表面に第3半導体デバイスを搭載する、といった構成とすることもできる。

【発明の効果】

【0047】

本発明のインターポーザによれば、二つの熱源の間に配置した際に、それら熱源間での熱伝導をより効果的に抑制することができる。また、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、隣接する半導体デバイス間での熱伝導をより効果的に抑制し、もってそれら半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0048】

本発明の半導体モジュールは、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【図面の簡単な説明】

【0049】

【図1A】ワイヤボンディングを用いた半導体モジュール(ボンディングモジュール)の一般的構成を示す説明図である。

【図1B】貫通電極を用いた半導体モジュール(貫通電極モジュール)の一般的構成を示す説明図である。

【図2A】本発明の第1実施形態のインターポーザの構造を示す要部断面説明図である。

【図2B】本発明の第1実施形態のインターポーザの全体構造を示す断面説明図である。

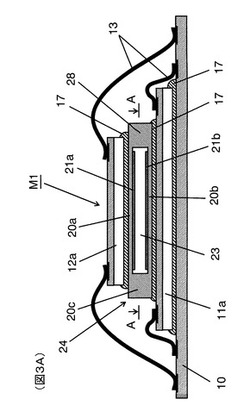

【図3A】本発明の第2実施形態の半導体モジュール(ボンディングモジュール)の全体構造を示す断面説明図である。

【図3B】本発明の第2実施形態の半導体モジュールに使用されたインターポーザの構造を示す、図3AのA−A線に沿った断面説明図である。

【図4A】本発明の第3実施形態の半導体モジュール(第2実施形態の半導体モジュールに放熱板を装着)の全体構造を示す断面説明図である。

【図4B】本発明の第4実施形態の半導体モジュール(第2実施形態の半導体モジュールをケース内に内蔵し、冷却用流体を供給)の全体構造を示す断面説明図である。

【図5A】本発明の第5実施形態の半導体モジュール(貫通電極モジュール)の全体構造を示す断面説明図である。

【図5B】本発明の第5実施形態の半導体モジュールに使用されたインターポーザの構造を示す、図5AのB−B線に沿った断面説明図である。

【図6A】本発明の第6実施形態の半導体モジュール(第5実施形態の半導体モジュール放熱板を装着)の全体構造を示す断面説明図である。

【図6B】本発明の第7実施形態の半導体モジュール(第5実施形態の半導体モジュールケース内に内蔵し、冷却用流体を供給)の全体構造を示す断面説明図である。

【図7】本発明の第2実施形態の半導体モジュールに使用されたインターポーザの製造方法の第1例を示す断面説明図である。

【図8】本発明の第2実施形態の半導体モジュールに使用されたインターポーザの製造方法の第2例を示す断面説明図である。

【図9】本発明の第5実施形態の半導体モジュールに使用されたインターポーザの製造方法の第1例を示す断面説明図である。

【図10】本発明の第5実施形態の半導体モジュールに使用されたインターポーザの製造方法の第2例を示す断面説明図である。

【図11】従来の半導体デバイスの実装構造を示す断面図である。

【発明を実施するための形態】

【0050】

以下、添付図面を参照して、本発明のインターポーザとそれを用いた半導体モジュールの好適な実施形態を説明する。

【0051】

金属細線をボンディングすることにより電気接続を行った半導体モジュール(ボンディングモジュール)の一般的構成を図1Aに、貫通電極を用いて電気接続を行った半導体モジュール(貫通電極モジュール)の一般的構成を、図1Bにそれぞれ示す。いずれの構成においても、二つの半導体デバイス(ここではチップ状の半導体デバイス、すなわち半導体チップとしている)を積層した二層構造になっている。

【0052】

図1Aの半導体モジュールは、樹脂、セラミック、半導体などで構成された基板10の上に第1半導体デバイス11aが接着剤17で固定され、第1半導体デバイス11aの上に第2半導体デバイス12aが接着剤17で固定されている。第1半導体デバイス11a及び第2半導体デバイス12aと基板10との電気接続は、いずれもボンディングワイヤ13を用いて行われている。

【0053】

図1Bの半導体モジュールは、樹脂、セラミック、半導体などで構成された基板10の上に第1半導体デバイス11bが導電性ボール15で固定され、第1半導体デバイス11bの上に第2半導体デバイス12bが導電性ボール15で固定されている。第1半導体デバイス11aの表面と裏面は、第1半導体デバイス11aの内部を貫通する貫通電極14によって相互に電気接続されている。第1半導体デバイス11aと第2半導体デバイス11bの電気接続と、第1半導体デバイス11aと基板10との電気接続は、いずれも導電性ボール15を用いて行われている。さらに、基板10と第1半導体デバイス11bの間と、第1半導体デバイス11bと第2半導体デバイス12bの間には、フィラー16が充填されていて、導電性ボール15による接続強度を増大させている。

【0054】

図1Aと図1Bに示した半導体モジュールには、それぞれ得失がある。

【0055】

図1Aの半導体モジュール(ボンディングモジュール)は、第1半導体デバイス11aと第2半導体デバイス12aを単に積層し、ボンディングワイヤで電気配線を行うだけであるから、新たな技術開発は不要である。ただし、第1半導体デバイス11aの大きさは第2半導体デバイス12aより大きいこと、高さが異なる位置からのワイヤボンディングができること等が要件となる。この手法で、3層以上に半導体デバイスを積層化を行った半導体モジュールもある。なお、図1Aのワイヤボンディングを用いた半導体モジュールの周辺に冷却用の流体(冷媒)を流す場合には、ボンディングワイヤ(金属細線)13が切断されないように、ボンディングワイヤ13の保護を施す必要がある。

【0056】

図1Bの半導体モジュール(貫通電極モジュール)では、下側の第1半導体デバイス11bに貫通電極14を埋め込む技術、多数の導電性ボール15の搭載・溶融・再凝固を安定して行う製造技術、さらには、基板10と第1半導体デバイス11bの間と、第1半導体デバイス11bと第2半導体デバイス12bの間の狭い空間に、フィラーを流し込む技術等が必要となる。この半導体モジュールでは、配線に関わる領域の全てが半導体チップ11b、12bの内部にあるかフィラー16で覆われているので、冷却用の流体(冷媒)の流動があっても半導体モジュールが破壊されることは少ない。

【0057】

(第1実施形態のインターポーザ)

本発明の第1実施形態のインターポーザを図2Aと図2Bに示す。図2Aはこのインターポーザの要部構成を示す部分断面図であり、図2Bは同インターポーザの全体構成を示す断面説明図である。

【0058】

本発明の第1実施形態のインターポーザ24は、上壁20aと、下壁20bと、上壁20a及び下壁20bを相互に連結する側壁20cとからなる本体を備えており、その本体の内部に真空に維持されたキャビティ23が形成されている。インターポーザ24の全体形状は、中空の板状である。上壁20a及び下壁20bは、キャビティ23の天井と床をそれぞれ形成する。側壁20cは、キャビティ23の天井と床をつなぐ周壁を形成する。

【0059】

なお、図2Aに示された符号25と26は、上壁20aと下壁20bがそれぞれ接触している熱源である。熱源25、26の例としては、半導体モジュールを構成している半導体デバイスがある。

【0060】

上壁20a及び下壁20bの内面には、絶縁層22a及び22bがそれぞれ形成されている。枠状の側壁20cの内面にも、絶縁層22cが形成されている。したがって、上壁20a、下壁20b及び側壁20cの内面(つまりキャビティ23の内壁面)の全体が、絶縁層22a、22b及び22cで覆われている。

【0061】

絶縁層22a及び22bの内側には、熱反射層21a及び21bがそれぞれ形成されている。絶縁層22cの内側には、熱反射層21cが形成されている。したがって、絶縁層22a、22b及び22cの表面の全体が、熱反射層21a、21b及び21cで覆われている。なお、熱反射層21a、21b及び21cは、それぞれ熱反射領域を形成するから、図2Bの構成では、絶縁層22a、22b及び22cの全表面が熱反射領域になっていると言うことができる。

【0062】

このように、キャビティ23を形成する本体の内壁面(つまり上壁20a、下壁20b及び側壁20cの内面)は、いずれも、絶縁層22a、22b及び22cと熱反射層21a、21b及び21cの二層で覆われている。

【0063】

熱反射層21a及び21bは、上壁20a及び下壁20bを介して上方及び下方から入射する熱を反射する機能を有しており、金属薄膜などから構成されることが多い。例えば、金やアルミの薄膜が使用可能であり、その表面は鏡面であることが好ましいが、鏡面でなくてもよい。また、熱反射層21a及び21bは、それぞれ、上壁20aの内面(図2A及び図2Bでは下位表面)および下壁20bの内面(図2A及び図2Bでは上位表面)の全体にわたって配置されていることが好ましいが、この限りではない。例えば、上壁20aの内面の指定された領域にのみ、熱反射層21aが配置されている構成としてもよい。下壁20bについても同様である。

【0064】

上壁20a及び下壁20bは、熱伝導率が小さい材料で構成されていることが好ましいが、必ずしもこの限りではない。上壁20a及び下壁20bがシリコン単結晶で構成され、それぞれの外面(図2A及び図2Bでは上位表面)に電子部品やトランジスタなどからなる電子回路、あるいは、電気配線層が配置されている場合には、絶縁層22aと22bをそれぞれ配置することが好ましい。絶縁層22aと22bは、当該電子回路などが熱反射層21a及び21b(これらは金属薄膜であるから導電性を持つ)で短絡することを防止する役割を持つ。このような必要性がない場合は、絶縁層22aと22bは省略できる。

【0065】

キャビティ23は真空に維持されているから、周知ように、キャビティ23の熱伝導率は非常に小さい。

【0066】

図2Aにおいて、上位にある熱源25で発生した熱は、まず、(1)上壁20aと絶縁層22aの内部を伝達され、熱反射層21aの表面に到達する。しかし、この熱の多くは、熱反射層21aの表面で反射され、熱源25の方に戻る。(2)熱反射層21aの表面で反射せずに熱反射層21aを通過した少量の熱は、真空に維持されているキャビティ23の内部に放射される。しかし、真空の熱伝導率は小さいので、キャビティ23の内部を通過して熱反射層21bに到達する熱は、さらに少なくなる。(3)キャビティ23の内部を通過して熱反射層21bまで到達した熱は、熱反射層21bの表面で反射される。このため、熱反射層21bを通過する熱はさらに減少する。その結果、熱源25で発生した熱のうち、熱源26まで到達する量は非常に少なくなる。熱源26で発生した熱についても、同様な状況にあるから、熱源25まで到達する量は非常に少なくなる。

【0067】

以上述べたように、熱源25と26は、インターポーザ24で「熱的に絶縁」されることになる。このため、例えば、熱源26が大電力を消費する半導体デバイスであり、熱源25が熱に敏感な特性を有する半導体デバイスであっても、熱源26が熱源25へ与える影響をインターポーザ24によって大きく低減させることが可能である。

【0068】

インターポーザ24の本体を形成する側壁20cは、真空に維持されたキャビティ23を形成するために必須な構成要素であるが、熱的に絶縁されるべき上壁20aと下壁20bとの間に熱伝導路を形成してしまう。このため、側壁20cの厚さは可能な限り小さく(薄く)設定されることが好ましい。側壁20cを、上壁20aと下壁20bとは異なる素材(熱伝導率が小さいことが好ましい)で構成することも可能である。なお、側壁20cの内面を絶縁する必要がなければ、側壁20cの内面に形成された絶縁層22cは省略可能である。

【0069】

図2Bの構成では、熱反射層21a、21b及び21cをキャビティ23を形成する本体の内面全体に配置しているが、本体の内面の指定された領域に限定して配置してもよい。例えば、キャビティ23の天井と床をそれぞれ形成する上壁20a及び下壁20bの内面にのみ熱反射層21a及び21bを配置し、キャビティ23の周壁を形成する側壁20cの内面の熱反射層21cを省略してもよい。また、熱反射層21a及び21bも、必ずしも上壁20a及び下壁20bの内面全体にそれぞれ配置する必要はなく、指定された領域に限定して配置してもよい。例えば、後述する図3A及び図3Bの構成例のように、上壁20aと下壁20bの側壁20cに近い領域で、それぞれ、熱反射層21aと21bを省略するのである。

【0070】

本発明の第1実施形態のインターポーザ24は、上述したような構成を有しているので、前記本体の一方の側に配置された熱源25(例えば半導体デバイス)から生じた熱が、伝導によって前記本体を移動する際に、その熱伝導は、真空状態にあるキャビティ23によって効果的に抑制される。前記熱の一部はキャビティ23内を伝導するが、キャビティ23の内壁面には、熱反射層21a、21b及び21c(これらは熱反射領域として機能する)が形成されているので、キャビティ23内を伝導した熱の多くは、熱反射層21a、21b及び21cで反射され、それ以上伝導しない。したがって、熱源25から前記本体中を移動して熱源26に到達する熱の量は、大きく減少する。

【0071】

逆に、熱源26から生じた熱が、前記本体中を移動して熱源25に到達する量も、同様の理由で、非常に少なくなる。

【0072】

このように、熱源25と熱源26が、本第1実施形態のインターポーザ24によって熱的に絶縁されることになるから、このインターポーザ24によれば、二つの熱源25と26の間に配置した際にそれら熱源25、26間での熱伝導をより効果的に抑制することができる。

【0073】

また、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、積層方向に隣接する半導体デバイスの間にこのインターポーザ24を介在させれば、それら半導体デバイス間での熱伝導をより効果的に抑制することができる。よって、それら半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0074】

(第2実施形態の半導体モジュール−ボンディングモジュール)

本発明の第2実施形態の半導体モジュールを図3Aと図3Bに示す。図3Aはこの半導体モジュールの全体構成を示す断面図であり、図3Bは図3Aの同半導体モジュールのA−A線に沿った断面図である。

【0075】

本第2実施形態の半導体モジュールM1は、上述した第1実施形態のインターポーザ24を、図1Aに示したボンディングモジュールに適用した例である。

【0076】

図3Aと図3Bに示すように、半導体モジュールM1は、接着剤17などで基板10の上に固定された第1半導体デバイス11aの表面に、インターポーザ24が搭載されており、インターポーザ24の表面に第2半導体デバイス12aが搭載されている。インターポーザ24は、第1半導体デバイス11aの表面に接着剤17などで固定されている。第2半導体デバイス12aは、インターポーザ24の表面に接着剤17などで固定されている。第1半導体デバイス11a及び第2半導体デバイス12aと基板10との電気接続は、いずれもボンディングワイヤ13を用いて行われている。

【0077】

インターポーザ24は、真空に維持されたキャビティ23を有し、キャビティ23の内壁を形成する上壁20a(天井)及び下壁20b(床)に、熱反射層21aと21bがそれぞれ配置されている。熱反射層21bは、図3Bに示すように、下壁20bの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。熱反射層21aも、同様に、上壁20aの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。

【0078】

以上の構成を有する第2実施形態の半導体モジュールM1では、第1半導体デバイス11aと第2半導体デバイス12aの間にインターポーザ24が配置されているため、第1半導体デバイス11aと第2半導体デバイス12aは、インターポーザ24の内部の真空に維持されたキャビティ23によって熱的に絶縁(遮断)される。つまり、第1半導体デバイス11aで発生した熱は、第2半導体デバイス12aに伝達されないし、第2半導体デバイス12aで発生した熱も、第1半導体デバイス11aに伝達されない。このため、第1半導体デバイス11aと第2半導体デバイス12aの間での熱伝導をより効果的に抑制することができる。よって、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイス11a、12aの温度上昇を抑えて安定に動作させることができる。

【0079】

しかし、第1半導体デバイス11aで発生した熱の一部は、側壁20cを通して第2半導体デバイス12aに伝達され、第2半導体デバイス12aで発生した熱の一部も、側壁20cを通して第1半導体デバイス11aに伝達されてしまう。側壁20cを介したこの熱伝達を小さくする対策としては、上述したように、側壁20cの厚さを小さくしたり、側壁20cを第1及び第2の半導体デバイス11a及び12aとは異なる材料(できる限り熱伝導率が小さい材料が好ましい)で形成したりすることが考えられる。

【0080】

第2実施形態の半導体モジュールM1では、第1半導体デバイス11aで発生した熱が第2半導体デバイス12aに伝達されないし、第2半導体デバイス12aで発生した熱も第1半導体デバイス11aに伝達されない。(より正確には「伝達されにくい」である。)しかしながら、第2半導体デバイス12aからの熱放散(例えば、第2半導体デバイス12aの上方空間への熱放散)や、第1半導体デバイス11aからの熱放散(例えば、基板10を介した下方空間への熱伝導)がないと仮定した場合には、時間の経過と共に両半導体デバイス11a及び12aの温度が等しくなるように、熱の移動が行われる。すなわち、時間の経過とともに、インターポーザ24の断熱性が活かされなくなる。現実には、上記の熱放散や熱伝導が行われるので、当該仮定は成立しないが、第1半導体デバイス11aまたは第2半導体デバイス12aからの熱放散や熱伝導を積極的に促進する構成をとることにより、インターポーザ24の断熱効果を増加することができる。以下、その例を第3及び第4の実施形態として示す。

【0081】

(第3実施形態の半導体モジュール−ボンディングモジュール)

本発明の第3実施形態の半導体モジュールを図4Aに示す。この半導体モジュールは、上述した第2実施形態の半導体モジュールM1に放熱板30を装着したものである。放熱板30は、基板10の裏面(下面)に密着して固定されている。

【0082】

第1半導体デバイス11aで発生した熱は、基板10を経由して放熱板30に伝達され、放熱板30の多数の放熱フィンから周囲の空間に放散される。このような放熱機能により、第1半導体デバイス11aの温度上昇が抑制され、結果として、第2半導体デバイス12aの温度上昇が抑制される。

【0083】

本第3実施形態の半導体モジュールでは、このように、第1半導体デバイス11aで発生する熱を、放熱板30により第1半導体デバイス11aの周辺から取り去ることで、発熱する第1半導体デバイス11aの温度上昇が抑制される。また、第1半導体デバイス11aで発生した熱の第2半導体デバイス12aへの伝導は、キャビティ23を有するインターポーザ24で阻止される。こうすることで、インターポーザ24の断熱効果の有効性を増大させている。

【0084】

このような構成をとっているため、第2半導体デバイス12aが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12aの温度上昇が抑制され、したがって、第2半導体デバイス12aの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0085】

(第4実施形態の半導体モジュール−ボンディングモジュール)

本発明の第4実施形態の半導体モジュールを図4Bに示す。この半導体モジュールは、上述した第2実施形態の半導体モジュールM1に、インレット32とアウトレット33を持つケース31を装着したものである。ケース31は、下面を開放した略直方体の箱状であり、基板10の表面(上面)に密着して固定されている、ケース31は、半導体モジュールM1の全体を覆って(包含して)いる。

【0086】

基板10とケース31により、略直方体の内部空間Sが形成されており、半導体モジュールM1はその内部空間Sに所在している。ケース31は、熱を吸収する流体Lを外部から内部空間Sに導入するためのインレット32と、流体Lを内部空間Sから外部に排出するためのアウトレット33とを有している。内部空間Sは、インレット32とアウトレット33を除いて閉じた空間である。

【0087】

矢印35は、インレット32へ流入する冷却用流体Lの流れ、矢印36は、アウトレット33から流出する流体Lの流れを示している。インレット32には、矢印35で示すように流体Lが流れ込み、内部空間Sに入る。流体Lは、内部空間Sを流動した後、矢印36で示すようにアウトレット33から流れ出る。

【0088】

インレット32とアウトレット33には、それぞれ、樹脂製あるいは金属製の管T1とT2の一端が接続されている。管T1の他端と管T2の他端は、それぞれ、流体Lに所定圧力を加えてインレット32に供給するポンプPの送出口と復帰口に接続されている。流体Lの加圧機構としては、流体Lに所定圧力を加えてインレット32に供給するものであればよく、ポンプ以外も使用可能である。

【0089】

熱を吸収する流体Lは、管T1を介して、ポンプPにより所定圧力をもってケース31の内部空間Sに送り込まれる。送り込まれた流体Lは、管T2を介してポンプPまで戻される。流体Lは、このようにして、ポンプP→管T1→内部空間S→管T2→ポンプPと循環する。流体Lは、内部空間Sにおいて半導体モジュールM1から生じた熱を吸収し、また、吸収した熱を外部を流動する間に自然放散する。半導体モジュールM1から生じた熱は、こうしてケース31の外部に放散せしめられる。このため、インレット32に供給される際には、流体Lは冷却されている。

【0090】

流体Lは、半導体モジュールM1で発生した熱を吸収してこれを冷却できるような性質を有しているものが好ましい。このような流体Lの例としては、(1)フロン類・ノンフロン類、(2)ブタン、イソブタンなどの有機化合物、(3)水素、ヘリウム、アンモニア、水、二酸化炭素などの無機化合物がある。いずれも「冷媒」とも称されているが、本第4実施形態においては、冷媒の種類に限定されることはない。

【0091】

下層にある第1半導体デバイス11aで発生した熱は、流体Lに伝達され、流体Lの流れによってアウトレット33から外部へ放散される。この放熱機能により、第1半導体デバイス11aの温度上昇が抑制され、結果として、上層にある第2半導体デバイス12aの温度上昇が抑えられることになる。

【0092】

本第4実施形態の半導体モジュールでは、上記第3実施形態とは異なり、流体Lによって半導体モジュールM1の全体から熱を取り去ることで、発熱する第1半導体デバイス11aの温度上昇が抑制される。また、第1半導体デバイス11aで発生した熱の第2半導体デバイス12aへの伝導は、キャビティ23を有するインターポーザ24で阻止される。こうすることで、インターポーザ24の断熱効果の有効性を増大させている。

【0093】

このような構成をとっているため、第2半導体デバイス12aが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12aの温度上昇が抑制され、したがって、第2半導体デバイス12aの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0094】

(第5実施形態の半導体モジュール−貫通電極モジュール)

本発明の第5実施形態の半導体モジュールを図5Aと図5Bに示す。図5Aはこの半導体モジュールの全体構成を示す断面図であり、図5Bは図5Aの同半導体モジュールのB−B線に沿った断面図である。

【0095】

本第5実施形態の半導体モジュールM2は、上述した第1実施形態のインターポーザ24を、図1Bに示した貫通電極モジュールに適用した例である。

【0096】

図5Aと図5Bに示すように、半導体モジュールM2は、導電性ボール15で基板10の上に固定された第1半導体デバイス11bの表面に、インターポーザ40が搭載されており、インターポーザ40の表面に第2半導体デバイス12bが搭載されている。インターポーザ40は、第1半導体デバイス11bの表面に導電性ボール43で固定されている。第2半導体デバイス12bは、インターポーザ40の表面に導電性ボール43で固定されている。

【0097】

インターポーザ40は、真空に維持されたキャビティ43を有し、キャビティ43の内壁を形成する上壁20a(天井)及び下壁20b(床)に、熱反射層21aと21bがそれぞれ配置されている。熱反射層21bは、図5Bに示すように、下壁20bの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。熱反射層21aも、同様に、上壁20aの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。

【0098】

インターポーザ40の内部には、その表面と裏面を電気接続する貫通電極42が形成されている。ただし、インターポーザ40を構成する要素との間の絶縁膜は、図示されていない。インターポーザ40の下面(裏面)と第1半導体デバイス11bとの電気接続は、導電性ボール43で行われている。インターポーザ40の上面(表面)と第2半導体デバイス12bとの電気接続も、導電性ボール43で行われている。

【0099】

インターポーザ40の表面と裏面には、導電性ボール43と電気接続され、かつ、表裏接続用の貫通電極42と電気接続されている電極パッドのみが描かれているが、これには限定されない。例えば、インターポーザ40の表面あるいは裏面に、1層あるいは2層以上の電気配線層を設け、第2半導体デバイス12bからの配線を再配線して、第1半導体デバイス11bに接続するように構成してもよい。この構成では、インターポーザ40をシリコン単結晶で形成することが好ましいが、これには限定されない。例えば、樹脂性のインターポーザ40に上記した1層あるいは2層以上の配線層を設けてもよい。

【0100】

以上の構成を有する第5実施形態の半導体モジュールM2においても、第1半導体デバイス11bと第2半導体デバイス12bの間にインターポーザ40が配置されているため、第1半導体デバイス11bと第2半導体デバイス12bは、インターポーザ40の内部の真空に維持されたキャビティ41によって熱的に絶縁(遮断)される。つまり、第1半導体デバイス11bで発生した熱は、第2半導体デバイス12bに伝達されないし、第2半導体デバイス12bで発生した熱も、第1半導体デバイス11bに伝達されない。(より正確には「伝達されにくい」である。)このため、第1半導体デバイス11bと第2半導体デバイス12bの間での熱伝導をより効果的に抑制することができる。よって、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイス11b、12bの温度上昇を抑えて安定に動作させることができる。

【0101】

また、上記第2実施形態と同様に、第1半導体デバイス11bで発生した熱の一部は、側壁20cを通して第2半導体デバイス12bに伝達され、第2半導体デバイス12bで発生した熱の一部も、側壁20cを通して第1半導体デバイス11bに伝達されてしまうが、本第5実施形態では貫通電極42が設けられているため、熱的な絶縁性が、上記第2実施形態よりも劣っている。これは、貫通電極42に好適な導電性が高い材料は、一般に熱伝導率も高いため、貫通電極42を介して熱伝導が行われるからである。しかしながら、貫通電極42の大きさ(断面積)を小さくすることにより、熱的な絶縁性の低下を阻止することは可能である。

【0102】

上記第2実施形態と同様に、第1半導体デバイス11bまたは第2半導体デバイス12bからの熱放散や熱伝導を積極的に促進する構成をとることにより、インターポーザ40の断熱効果を増加することができる。以下、その例を第6及び第7の実施形態として示す。

【0103】

(第6実施形態の半導体モジュール−貫通電極モジュール)

本発明の第6実施形態の半導体モジュールを図6Aに示す。この半導体モジュールは、上述した第5実施形態の半導体モジュールM2に放熱板30を装着したものである。放熱板30は、基板10の裏面(下面)に密着して固定されている。

【0104】

第1半導体デバイス11bで発生した熱は、基板10を経由して放熱板30に伝達され、放熱板30の多数の放熱フィンから周囲の空間に放散される。このような放熱機能により、第1半導体デバイス11bの温度上昇が抑制され、結果として、第2半導体デバイス12bの温度上昇が抑制される。

【0105】

本第6実施形態の半導体モジュールでは、このように、第1半導体デバイス11bで発生する熱を、放熱板30により第1半導体デバイス11bの周辺から取り去ることで、発熱する第1半導体デバイス11bの温度上昇が抑制される。また、第1半導体デバイス11bで発生した熱の第2半導体デバイス12bへの伝導は、キャビティ41を有するインターポーザ40で阻止される。こうすることで、インターポーザ40の断熱効果の有効性を増大させている。

【0106】

このような構成をとっているため、第2半導体デバイス12bが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12bの温度上昇が抑制され、したがって、第2半導体デバイス12bの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0107】

(第7実施形態の半導体モジュール−貫通電極モジュール)

本発明の第4実施形態の半導体モジュールを図4Bに示す。この半導体モジュールは、上述した第5実施形態の半導体モジュールM2に、上述した第4実施形態で使用したインレット32とアウトレット33を持つケース31を装着したものである。ケース31は、下面を開放した略直方体の箱状であり、基板10の表面(上面)に密着して固定されている、ケース31は、半導体モジュールM2の全体を覆って(包含して)いる。

【0108】

基板10とケース31により略直方体の内部空間Sが形成されており、半導体モジュールM2は、その内部空間Sに所在している。ケース31は、熱を吸収する流体Lを外部から内部空間Sに導入するためのインレット32と、流体Lを内部空間Sから外部に排出するためのアウトレット33とを有している。内部空間Sは、インレット32とアウトレット33を除いて閉じた空間である。

【0109】

流体Lに所定圧力を加えてインレット32に供給するポンプPと、インレット32及びアウトレット33とポンプPとを接続する管T1とT2、そして、熱を吸収する流体Lは、上述した第4実施形態で使用したものと同じである。

【0110】

流体Lは、ポンプP→管T1→内部空間S→管T2→ポンプPと循環する。流体Lは、内部空間Sにおいて半導体モジュールM2から生じた熱を吸収し、また、吸収した熱を外部を流動する間に自然放散する。半導体モジュールM2から生じた熱は、こうしてケース31の外部に放散せしめられる。

【0111】

下層にある第1半導体デバイス11bで発生した熱は、流体Lに伝達され、流体Lの流れによってアウトレット33から外部へ放散される。この放熱機能により、第1半導体デバイス11bの温度上昇が抑制され、結果として、上層にある第2半導体デバイス12bの温度上昇が抑えられることになる。

【0112】

本第7実施形態の半導体モジュールでは、上記第6実施形態とは異なり、流体Lによって半導体モジュールM2の全体から熱を取り去ることで、発熱する第1半導体デバイス11bの温度上昇が抑制される。また、第1半導体デバイス11bで発生した熱の第2半導体デバイス12bへの伝導は、キャビティ41を有するインターポーザ40で阻止される。こうすることで、インターポーザ40の断熱効果の有効性を増大させている。

【0113】

このような構成をとっているため、第2半導体デバイス12bが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12bの温度上昇が抑制され、したがって、第2半導体デバイス12bの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0114】

(第8実施形態のインターポーザの形成方法)

次に、上述したインターポーザの形成方法について説明する。

【0115】

図7は、本発明の第8実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第1例である。

【0116】

まず、図7(a)に示すように、矩形板状の上壁(上板)50の下面に、矩形の熱反射層51を形成する。熱反射層51は、上壁50の下面の周辺領域を除いて形成されており、その下面の全体を覆っていないが、これには限定されない。上壁50の下面全体を覆っていてもよい。

【0117】

次に、図7(b)に示すように、矩形板状の下壁(下板)54の上面に、矩形の熱反射層53を形成する。熱反射層53も、下壁54の上面の周辺領域を除いて形成されており、その上面の全体を覆っていないが、これには限定されない。下壁54の上面全体を覆っていてもよい。

【0118】

熱反射層51を形成した上壁50と熱反射層53を形成した下壁54は、同一構成であってもよい。つまり、同一構成のものを2個形成してもよい。また、上壁50と下壁54は、熱伝導が小さい素材であることが好ましいが、この限りではない。熱反射層51と53は、例えば、金、アルミニウムなどの金属を蒸着するといった手法で形成することができる。

【0119】

次に、図7(c)に示すように、下壁54の周辺部に側壁52を形成する。側壁54の素材としては、ガラスや樹脂などで使用でき、接着などの手法により下壁54の周辺部に密着せしめられる。

【0120】

次に、図7(d)に示すように、接着材などを用いて、側壁54の上面に上壁50の下面を密着(接合)させる。この密着により、上壁50と下壁54と側壁52が一体化されて、インターポーザの本体が形成され、同時に、その本体の内部にキャビティ55が形成される。キャビティ55は、真空であることが必須であるから、この密着(接合)工程は真空雰囲気中で実施される。

【0121】

以上の工程を経て本発明のインターポーザが作成される。上壁50、下壁54、側壁52といった構成要素の素材と、上壁50と下壁54の密着のための接着材等は、長期にわたってキャビティ55内の真空状態が維持されるように選択される。一例を挙げると、上壁50と下壁54は単結晶シリコン、側壁52はガラスが好適に使用できる。このような素材を採用すれば、下壁54と側壁52との接合、側壁52と上壁50との接合に、静電接合技術を用いることが可能である。さらに、静電接合は真空中で実施され、かつ、当該静電接合の真空封止性は十分に高いため、長期にわたるキャビティ55内の真空が維持されることになる。上壁50と下壁54は単結晶シリコン製であるため、周知の技術を用いて、それぞれの表面に1層以上の配線層を形成することも可能である。

【0122】

なお、図7には示していないが、図7(d)の構成を持つインターポーザの周辺部に、貫通電極を形成することも可能である。例えば、RIE(反応性イオンエッチング)などの加工技術を用いて、上壁50(単結晶シリコン)、側壁52(ガラス)、下壁54(単結晶シリコン)に上下方向の貫通穴を開け、その内部に導電材料を付着あるいは充填することにより、貫通電極を形成することができる。なお、上壁50及び下壁54と前記導電材料との間には、適当な絶縁膜を設けて電気的に絶縁する必要がある。

【0123】

(第9実施形態のインターポーザの形成方法)

図8は、本発明の第9実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第2例である。

【0124】

まず、図8(a)に示すように、矩形板状の上壁(上板)60の下面に、矩形の熱反射層61を形成する。熱反射層61は、上壁60の下面の周辺領域を除いて形成されており、その下面の全体を覆っていないが、これには限定されない。上壁60の下面全体を覆っていてもよい。この工程は、図7(a)のそれと同じである。

【0125】

次に、図8(b)に示すように、側壁63を有する矩形板状の下壁62(下板)(側壁63の内側に窪み67が形成されている)を用意し、側壁63の内側領域の上面(窪み67の底面)に矩形の熱反射層64を形成する。この工程では、上述した第8実施形態(図7)とは異なり、下壁62と側壁63とが一体的に構成されたものを使用している。この構成は、下壁62の母材の中央領域に窪み67を形成し、その窪み67の底面に熱反射層64を形成することにより容易に実現される。具体的に言えば、単結晶シリコン板の上側表面にパターニングされたフォトレジスト層を作成し、このフォトレジスト層をマスクとしてRIEなどでエッチングして、窪みを形成すればよい。ただし、単結晶シリコン板の厚さは、側壁63の厚さ(高さ)と同じにする。続いて、この窪みの底部に金、アルミなどの金属を蒸着等で堆積させ、熱反射層64とする。

【0126】

熱反射層64は、ここでは、下壁62の窪み67の底面の周辺領域を除いて形成されており、その底面の全体を覆っていないが、これには限定されない。熱反射層64は、窪み67の底面全体を覆っていてもよいし、その底面から側壁63の内側面にかけての領域を覆ってもよいし、この内側面から側壁63の上端面に至る領域までを覆っていてもよい。

【0127】

次に、図8(c)に示すように、エポキシ系接着材65などを用いて、側壁63の上端面に上壁60の下面を密着(接合)させる。これにより、上壁60と、側壁63を持つ下壁62とが一体化されて、インターポーザの本体が形成され、同時に、その本体の内部にキャビティ66が形成される。キャビティ66は、真空であることが必須であるから、この密着(接合)工程は真空雰囲気中で実施される。

【0128】

上壁60と、側壁63を持つ下壁62とが、いずれも単結晶シリコンで構成されていて、側壁63の上端面に熱反射層64が形成されていない場合には、図8(c)の工程で上壁60と側壁63とをシリコン・シリコンの熱接合で密着させることも可能である。

【0129】

なお、図8には示していないが、上述した第8実施形態(図7)と同様に、図8(c)の構成を持つインターポーザの周辺部に、貫通電極を形成することも可能である。

【0130】

(第10実施形態のインターポーザの形成方法)

図9は、本発明の第10実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第3例である。

【0131】

まず、図9(a)に示すように、下壁(下板)の母材70aとして矩形のシリコン単結晶板を用意する。

【0132】

次に、図9(b)に示すように、母材70aの周辺部に、周知の手法によって貫通電極71を形成する。具体的に言えば、RIEにより母材70aの周辺部に貫通穴を開け、これら貫通穴の内側面を絶縁層(図示せず)で覆ってから、これら絶縁層の内側に導電性材料を被覆あるいは充填する。こうして貫通穴に導電性を付与することで、貫通電極71が形成される。その後、母材70aの表面と裏面にそれぞれ電気接続用パッド72を形成し、貫通電極71と電気接続する。

【0133】

次に、母材70aの表面側から、パターニングされたマスク(フォトレジストなど)を利用して、窪み73を掘り込む。窪み73の作成には、例えば、TMAH(テトラメチルアンモニアハイドロオキサイド)やKOH(水酸化カリウム)などの異方性エッチング液が利用される。これらのエッチング液では、特定のシリコン結晶面((111)面)でエッチング速度が低いため、窪み73の縁(窪み73の底から基板70の表面にかけての斜面)は露出した(111)面となる。こうして、下壁(下板)70が形成される。その後、窪み73の底面に熱反射層74を形成する。この時の状態は図9(c)のようになる。

【0134】

次に、図9(d)に示すように、矩形のシリコン単結晶板からなる上壁(上板)75の上面から前記した異方性エッチング液で、パッド72を露出させるための開口76を形成する。また、開口76と重ならないように、上壁75の下面に熱反射層77を形成する。

【0135】

次に、図9(c)に示した下壁70の上面に、図9(d)に示した上壁75を密着(接合)させ、図9(e)に示した構造を持つインターポーザを得る。この密着(接合)には、接着材や低融点ガラスなどが用いられる。下壁70の窪み73により、キャビティ78が形成される。キャビティ78内は真空であることが必要であるため、前記密着(接合)工程は真空雰囲気中で実施される。

【0136】

本実施形態では、上壁75と下壁70がいずれもシリコン単結晶から形成されているため、インターポーザの本体の表面と裏面に1層以上の配線層を形成することも可能である。

【0137】

(第11実施形態のインターポーザの形成方法)

図10は、本発明の第11実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第4例である。図10において、図9におけるそれと同一の符号は、同一の構成要素を示している。

【0138】

図10(a)から図10(c)までの工程は、図9(a)から図9(c)の工程までと同じであるから、その説明は省略する。

【0139】

次に、図10(d)に示すように、熱反射層84を備えた上壁(上板)85を形成する。この上壁85は、母材としての単結晶シリコン板の周縁部をエッチング等で斜めに除去してテーパ状とし、その下面に熱反射層84を形成することで、容易に得られる。

【0140】

次に、接着材や低融点ガラスなどを用いて、図10(c)に示した下壁(下板)70の上面に、図10(d)に示した上壁(上板)85を密着(接合)させ、図10(e)に示した構造を得る。窪み73はキャビティ86を構成し、当該キャビティ内は真空であることが必要であるため、前記密着のプロセスは真空雰囲気中で実施される。

【0141】

本実施形態では、上述した第10実施形態(図9)とは異なり、上板85が下板70の窪み73の中に入り込む構成になっている。つまり、下板70の側壁部(パッド72が設けられている部分)の表面を、上板85が覆っていない。この構成では、上板85に開口(図9の開口76に対応する)を設ける必要がなく、製造技術上、簡便であるという利点がある。

【0142】

(変形例)

以上、本発明の実施形態について詳細な説明を行った。本明細書では、インターポーザの構成と、このインターポーザを用いた半導体モジュールについて記載したが、例示した構成以外にも多くの構成が可能である。

【0143】

例えば、第2半導体デバイスの消費電力が第1半導体デバイスの消費電力よりも大きいような構成、半導体デバイスを3層以上に積層した構成、インターポーザを挟み込む上下の半導体デバイスがそれぞれ2個以上の構成(例えば、インターポーザの上面に、同一平面内で複数個の半導体デバイスが配置されている構成)なども可能である。

【0144】

いずれの構成においても、インターポーザの真空層でその両側にある半導体デバイス間の熱的絶縁を図り、高密度・高速の半導体モジュールを実現することが本発明の趣旨である。

【産業上の利用可能性】

【0145】

本発明は、消費電力の増大傾向がある半導体デバイスの冷却を容易にするインターポーザ、および、それを用いた半導体モジュールと実装構造に適用可能である。また、本発明は、電子回路を主体とする半導体モジュールに限定されることなく、他の大電力デバイス(例えば、発光素子モジュール、光通信モジュールなど)にも広く適用可能である。

【符号の説明】

【0146】

11a、11b 半導体デバイス

12a、12b 半導体デバイス

13 ボンディングワイヤ

14 貫通電極

15 導電性ボール

16 フィラー

17 接着剤

20a 上壁

20b 下壁

20c 側壁

21a、21b、21c 熱反射層

22a、22c 絶縁層

23 キャビティ

24 インターポーザ

25、26 熱源

30 放熱板

31 ケース

32 インレット

33 アウトレット

40 インターポーザ

41 キャビティ

42 貫通電極

43 キャビティ

43 導電性ボール

50 上壁

51 熱反射層

52 側壁

53 熱反射層

54 下壁

54 側壁

55 キャビティ

60 上壁

61 熱反射層

62 下壁

63 側壁

64 熱反射層

65 接着材

66 キャビティ

70 下壁

70a 下壁の母材

71 貫通電極

72 電気接続用パッド

74 熱反射層

75 上壁

76 開口

77 熱反射層

78 キャビティ

84 熱反射層

85 上壁

86 キャビティ

L 冷却用流体

M1 半導体モジュール

M2 半導体モジュール

P ポンプ

S 内部空間

T1 管

T2 管

【技術分野】

【0001】

本発明は、半導体デバイスの実装技術に関し、さらに言えば、消費電力の大きい半導体デバイスの動作温度の上昇を抑えて安定に動作させることができるインターポーザと、そのインターポーザを用いた半導体モジュールに関するものである。

【背景技術】

【0002】

近年、シリコンを代表とする半導体工業分野の技術進歩は大きく、工業用、民生用を問わず、機器やシステムの小型化、軽量化、低価格化、高機能化などに大きく寄与するに至っている。一方、半導体デバイスへの要求はとどまることがなく、より一層の高集積化、高速化、高度化が期待されると共に、小型化も期待されている。これらの要求に応える策として、半導体デバイスを構成する単位素子(例えばトランジスタ)の寸法を微小化し、搭載される単位素子の数を増大させることがある。この策の利点は、微小化に伴う動作速度の増大(高速化)、高集積化に伴う機能の増大(あるいは必要とされる半導体デバイス数の減少)である。しかしながら、高速化や高集積化に伴い半導体デバイスの内部での消費電力が大きくなり、動作の不安定化あるいはデバイス自体の破壊の危険性が増大する。これらの危険性を低下させるには、半導体デバイスの放熱技術(あるいは冷却技術)が必須である。

【0003】

以前から、半導体デバイスの動作温度を低くする技術が数多く開発されてきた。例えば、大電力の半導体デバイスに放熱フィン(アルミ合金製が多い)を貼り付け、このフィンに空気の流れを吹き付けることにより、半導体デバイスを冷却する技術がある。消費電力が比較的低い(例えば数ワット)場合には、この技術で解決可能である。しかし、最新の半導体デバイスでは、消費電力がいっそう大きくなっており、コンピュータのCPUなどでは100ワット以上に達することもある。このため、このような大消費電力の半導体デバイスでは、放熱が十分でないと、半導体デバイスの温度が上昇し、熱暴走あるいは熱破壊に至ることもある。したがって、半導体デバイスの動作の上限は、放熱技術に支配されているとも言える。

【0004】

半導体デバイスを複数個積層化してなる「半導体モジュール」は、比較的容易に高集積化を実現できる利点がある。このような構成では、下層に配置された半導体デバイスでの電力消費は、この半導体デバイスの温度を上昇させるだけではなく、その上層に配置された半導体デバイスの温度も上昇させる。このため、積層モジュールの上層に、特性が動作温度に敏感な半導体デバイスが配置されている場合には、積層モジュール全体の動作が不安定になる可能性がある。このため、半導体モジュールの場合には、消費電力が大きい半導体デバイスのみを冷却し、積層されている半導体デバイス間で熱伝達が生じないような実装構造が好ましい。

【0005】

積層された半導体デバイス(半導体モジュール)の冷却技術としては、従来、図11に示す実装構造が提案されている。同図は、特許文献1の図1Aとして掲載されているものである。

【0006】

図11において、チップスタック110は、符号110a、110b、110cで示された3個の半導体チップの積層体から構成されている。それぞれのチップ110a、110b、110cには、エッチングで形成されたチャネル175が設けられている(図11では、符号175は代表的なチャネルを示している)。チャネル175内に流体(冷媒)を流すことにより、チップスタック110の冷却が行われるようになっている。この流体は、積層されたチップ110a、110b、110cの間に形成された狭いチャネル175内を流動する。なお、チップ110a、110b、110cが半導体基板から構成されている場合には、その厚さは通常、数百マイクロメータ以下である。

【0007】

各半導体チップ110a、110b、110cの垂直方向には、符号123で示されたTSV(Through Silicon Via, シリコン貫通電極)によって、チップ110a、110b、110c同士は相互接続されている。

【0008】

他方、半導体モジュールでは、積層した半導体デバイスの間に「インターポーザ」と称される配線基板を挟み込むことも行われている。このインターポーザへの要求仕様としては、(1)表面と裏面の間に複数の電気接続路(例えば貫通電極)を有すること、(2)表面あるいは裏面に、あるいは表面及び裏面の双方に電気配線層(再配線層とも称される)を有すること、などがある。このような仕様を満足させると、半導体モジュールの設計および作成が容易となる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許出願公開第2009/031186号明細書

【発明の概要】

【発明が解決しようとする課題】

【0010】

図11に示した従来の半導体デバイスの実装構造では、チャネル175は、あたかも「多数の柱が林立する回廊」のように形成されており、しかも、その高さは数百マイクロメータ以下であるから、チャネル175内に流体(冷媒)を流し込むには、大きな圧力が必要である。

【0011】

また、流体の流れる方向は、図11の符号111の下側にある下向き矢印と右向き矢印で示されているが、その下向き矢印に沿ってチップスタック110の周囲に流入した流体は、右向き矢印に沿ってチップ110a、110b、110cの間にあるチャネル175内に流入するだけではなく、チップ110a、110b、110cの周囲に沿っても流動するであろう。上述したように、チャネル175の高さが低いことと、チップ110a、110b、110cの周囲には広い空間があることを考えると、チャネル175内のみに流体を流し込むことは困難であり、多くの流体はチップ110a、110b、110cの周囲に沿って流れてしまうと思われる。しかも、チップ110a、110b、110cに形成されたチャネル175の形状(流体が流れる方向の形状)は、チップ110a、110b、110c毎に異なるので、各層に形成されたチャネル175の全てにおいて均一な流体の流れを実現することも困難であろう。

【0012】

このような理由から、図11の従来の実装構造では、チップ110a、110b、110cの十分な冷却(あるいはチップ110a、110b、110cからの放熱)を実現することは、必ずしも容易ではない。

【0013】

他方、半導体モジュールにおいて、積層した半導体デバイスの間にインターポーザを挟み込むと、これら半導体デバイス間の物理的な距離が大きくなり、例えば、下層の半導体デバイスの発熱が上層の半導体デバイスに伝達されにくくなる利点がある。しかあし、上述した従来の半導体デバイスの実装技術を高度化して、消費電力の大きい半導体デバイスの動作温度の上昇を抑えて安定に動作させるためには、積層方向に隣接する半導体デバイス間での熱伝導を、積極的に、より少なくするようなインターポーザの新たな構造が望まれる。

【0014】

本発明は、以上のような事情を考慮してなされたものであり、その目的とするところは、二つの熱源の間に配置した際に、それら熱源間での熱伝導をより効果的に抑制することができるインターポーザを提供することにある。

【0015】

本発明の他の目的は、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、隣接する半導体デバイス間での熱伝導をより効果的に抑制し、もってそれら半導体デバイスの温度上昇を抑えて安定に動作させることができるインターポーザを提供することにある。

【0016】

本発明のさらに他の目的は、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイスの温度上昇を抑えて安定に動作させることができる半導体モジュールを提供することにある。

【0017】

ここに明記しない本発明の他の目的は、以下の説明及び添付図面から明らかになる。

【課題を解決するための手段】

【0018】

(1) 本発明の第1の観点によるインターポーザは、

真空に維持されたキャビティを有する本体(構造体)と、

前記キャビティの内壁面に形成された熱反射領域と

を備えていることを特徴とするものである。

【0019】

本発明の第1の観点によるインターポーザは、上述したような構成を有するので、前記本体の一方の側に配置された第1熱源(例えば半導体デバイス)から生じた熱が、伝導によって前記本体を移動する際に、その熱伝導は、真空状態にある前記キャビティによって効果的に抑制される。前記熱の一部は前記キャビティ内を伝導するが、前記キャビティの内壁面には前記熱反射領域が形成されているので、前記キャビティ内を伝導した熱の多くは、前記熱反射領域で反射され、それ以上伝導しない。したがって、前記第1熱源から前記本体中を移動して前記第2熱源に到達する熱の量は、大きく減少する。

【0020】

逆に、前記第2熱源から生じた熱が、前記本体中を移動して前記第1熱源に到達する量も、同様の理由で、非常に少なくなる。

【0021】

このように、前記第1熱源と前記第2熱源が、本発明のインターポーザによって熱的に絶縁されることになるから、本発明のインターポーザによれば、二つの熱源の間に配置した際にそれら熱源間での熱伝導をより効果的に抑制することができる。

【0022】

また、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、積層方向に隣接する半導体デバイスの間に本発明のインターポーザを介在させれば、それら半導体デバイス間での熱伝導をより効果的に抑制することができる。よって、それら半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0023】

(2) 本発明のインターポーザの好ましい例では、前記本体が、第1熱源に隣接する上壁と、第2熱源に隣接する下壁と、前記上壁と前記下壁を連結する側壁を備えており、前記上壁と前記下壁と前記側壁が前記キャビティを画定する。前記上壁と前記下壁と前記側壁は、熱伝導率が低い材料で作製することが好ましい。

【0024】

(3) 本発明のインターポーザの他の好ましい例では、前記熱反射領域が、前記上壁の内面と前記下壁の内面に形成され、前記側壁の内面には形成されない。

【0025】

(4) 本発明のインターポーザのさらに他の好ましい例では、前記上壁と前記下壁と前記側壁が、いずれも単結晶シリコンで形成される。この例では、周知の集積回路作成技術を利用して、前記インターポーザの表面と裏面、あるいは前記上壁と前記下壁に、電子回路あるいは電気配線層を容易に形成できるという利点がある。

【0026】

(5) 本発明のインターポーザのさらに他の好ましい例では、前記上壁と前記下壁が単結晶シリコンで形成され、前記側壁がガラスで形成される。この例では、シリコン単結晶とガラスとを静電接合で気密良くかつ強固に密着させることが可能であるから、真空を維持することが容易である。

【0027】

(6) 本発明のインターポーザのさらに他の好ましい例では、前記上壁と前記下壁が樹脂材料(例えば、プリント基板の素材)で形成され、前記側壁が接着性の高い樹脂材料(例えば、フォトレジスト材料である「SU−8」で形成される。この例では、シリコン単結晶とガラスとを静電接合で気密良くかつ強固に密着させることが可能であるから、真空を維持することが容易である。

【0028】

(7) 本発明のインターポーザのさらに他の好ましい例では、前記本体が貫通電極を備える。

【0029】

(8) 本発明の第2の観点による半導体モジュールは、

本発明の第1の観点によるインターポーザと、

前記インターポーザの一方の側に搭載された第1半導体デバイスと、

前記インターポーザの他方の側に搭載された第2半導体デバイスと

を備えていることを特徴とするものである。

【0030】

本発明の第2の観点による半導体モジュールは、上述した本発明の第1の観点によるインターポーザを含んでいて、そのインターポーザの両側に前記第1半導体デバイスと前記第2半導体デバイスを搭載しているので、前記第1半導体デバイスと前記第2半導体デバイスは、前記インターポーザによって熱的に絶縁される。このため、前記第1半導体デバイスと前記第2半導体デバイスの間での熱伝導をより効果的に抑制することができる。

【0031】

よって、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0032】

(9) 本発明の半導体モジュールの好ましい例では、前記第1半導体デバイスの側に装着された放熱板をさらに備える。

【0033】

(10) 本発明の半導体モジュールの他の好ましい例では、前記第1半導体デバイスと前記第2半導体デバイスと前記インターポーザを包含するケースと、冷却用流体を加圧して前記ケース内に導入する手段をさらに備える。前記ケースは、冷却用流体を導入するインレットと、前記冷却用流体を排出するアウトレットとを有する。

【0034】

(11) 本明細書では、関連する用語を下記のように定義する。

【0035】

・半導体デバイス: 以下の(i)と(ii)を含む半導体デバイス全般を指す。

【0036】

(i) ウェーハプロセスが完了し、半導体ウェーハから切り出された半導体チップ(ベアチップ)。当該半導体チップには、少なくとも1個のトランジスタ、ダイオードなどの半導体素子が配置された、いわゆる集積回路のチップを含む。

【0037】

(ii) パッケージングされた上記の半導体チップ。ボールグリッドアレイ(BGA)、チップサイズパッケージ(CSP)などと称される、種々のパッケージでパッケージングされたものが含まれる。

【0038】

・半導体モジュール: 2個以上の前記半導体デバイスが積層された構造である。積層構造を構成する各層の間の相互接続の手法には、ワイヤボンディング、貫通電極(TSV)などがあるが、その手法は問わない。なお、本明細書では、ワイヤボンディングにより層間接続された半導体モジュールを「ボンディングモジュール」、貫通電極により層間接続された半導体モジュールを「貫通電極モジュール」と呼ぶ。

【0039】

・電子部品: 受動素子とも称されている部品で、抵抗、キャパシタ(コンデンサ)、インダクタ(コイル)などがある。単一の素子(個別部品)を複数個組み合わせた構成(例えば、モジュール抵抗)もある。また、特定の機能を有するセンサやアクチュエータも、電子部品に含まれる。さらには、信号処理回路、駆動回路などが集積化された前記センサや前記アクチュエータも、電子部品に含まれる。

【0040】

・流体: 気体あるいは液体であり、熱伝導で熱を吸収することにより、放熱あるいは排熱効果を有するものである。このような機能を有する流体は、「冷媒」とも称される。具体例としては、(i)フロン類・ノンフロン類(多用されており、種類が多い)、(ii)有機化合物であるブタン、イソブタンなど、(iii)無機化合物である水素、ヘリウム、アンモニア、水、二酸化炭素などがある。

【0041】

(12) 前記熱反射領域は、前記キャビティの内壁面の全体にわたって配置されるとは限らない。前記内壁面の指定された範囲に限定して配置してもよい。例えば、前記キャビティの上壁と下壁にのみ前記熱反射領域を配置し、前記キャビティの側壁には前記熱反射領域を配置しないようにする。さらに、前記上壁の周辺部(側壁に近い部分)に前記熱反射領域を配置しないようにしてもよい。

【0042】

前記キャビティの上壁と下壁と側壁は、同一材料で形成してもよい。例えば、これらを全てシリコン単結晶で構成した場合には、周知の集積回路作成技術を利用して、前記インターポーザの表面と裏面、あるいは、前記上壁と下壁に、電子回路あるいは電気配線層を容易に形成することが可能となる。

【0043】

前記キャビティの上壁と下壁と側壁は、異なる材料で形成してもよい。例えば、上壁と下壁をシリコン単結晶で、側壁をガラスで形成してもよい。この場合、シリコン単結晶とガラスとを静電接合で気密良くかつ強固に密着させることが可能であり、前記キャビティの真空を維持しやすい。また、前記キャビティの上壁と下壁を樹脂材料(例えば、プリント基板の素材)で、側壁を接着性の高い樹脂材料(例えば、フォトレジスト材料である「SU−8」)で形成してもよい。なお、上壁と下壁と側壁は、熱伝導率が低い材料で形成することが好ましい。

【0044】

前記インターポーザの表面と裏面に、電子回路あるいは電気配線層を配置してもよい。また、前記キャビティの内壁面にも、電子回路あるいは電気配線層を配置してもよい。この場合には、前記熱反射領域が前記電子回路等の動作を阻害しない(例えば、電子回路の短絡)ようにするために、前記熱反射領域と前記電子回路等の間に絶縁層を配置することが必要となる。

【0045】

前記インターポーザには、貫通電極を形成してもよい。貫通電極を形成することにより、前記インターポーザの上方に配置された半導体デバイスからの電気信号を、前記インターポーザの下方に配置された半導体デバイスへ伝達することが可能となる。

【0046】

前記インターポーザを2個以上用いて多段の半導体モジュールを構成することもできる。例えば、第1半導体デバイスの表面に第1インターポーザを搭載し、前記第1インターポーザの表面に第2半導体デバイスを搭載し、前記第2半導体デバイスの表面に第2インターポーザを搭載し、前記第2インターポーザの表面に第3半導体デバイスを搭載する、といった構成とすることもできる。

【発明の効果】

【0047】

本発明のインターポーザによれば、二つの熱源の間に配置した際に、それら熱源間での熱伝導をより効果的に抑制することができる。また、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、隣接する半導体デバイス間での熱伝導をより効果的に抑制し、もってそれら半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0048】

本発明の半導体モジュールは、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【図面の簡単な説明】

【0049】

【図1A】ワイヤボンディングを用いた半導体モジュール(ボンディングモジュール)の一般的構成を示す説明図である。

【図1B】貫通電極を用いた半導体モジュール(貫通電極モジュール)の一般的構成を示す説明図である。

【図2A】本発明の第1実施形態のインターポーザの構造を示す要部断面説明図である。

【図2B】本発明の第1実施形態のインターポーザの全体構造を示す断面説明図である。

【図3A】本発明の第2実施形態の半導体モジュール(ボンディングモジュール)の全体構造を示す断面説明図である。

【図3B】本発明の第2実施形態の半導体モジュールに使用されたインターポーザの構造を示す、図3AのA−A線に沿った断面説明図である。

【図4A】本発明の第3実施形態の半導体モジュール(第2実施形態の半導体モジュールに放熱板を装着)の全体構造を示す断面説明図である。

【図4B】本発明の第4実施形態の半導体モジュール(第2実施形態の半導体モジュールをケース内に内蔵し、冷却用流体を供給)の全体構造を示す断面説明図である。

【図5A】本発明の第5実施形態の半導体モジュール(貫通電極モジュール)の全体構造を示す断面説明図である。

【図5B】本発明の第5実施形態の半導体モジュールに使用されたインターポーザの構造を示す、図5AのB−B線に沿った断面説明図である。

【図6A】本発明の第6実施形態の半導体モジュール(第5実施形態の半導体モジュール放熱板を装着)の全体構造を示す断面説明図である。

【図6B】本発明の第7実施形態の半導体モジュール(第5実施形態の半導体モジュールケース内に内蔵し、冷却用流体を供給)の全体構造を示す断面説明図である。

【図7】本発明の第2実施形態の半導体モジュールに使用されたインターポーザの製造方法の第1例を示す断面説明図である。

【図8】本発明の第2実施形態の半導体モジュールに使用されたインターポーザの製造方法の第2例を示す断面説明図である。

【図9】本発明の第5実施形態の半導体モジュールに使用されたインターポーザの製造方法の第1例を示す断面説明図である。

【図10】本発明の第5実施形態の半導体モジュールに使用されたインターポーザの製造方法の第2例を示す断面説明図である。

【図11】従来の半導体デバイスの実装構造を示す断面図である。

【発明を実施するための形態】

【0050】

以下、添付図面を参照して、本発明のインターポーザとそれを用いた半導体モジュールの好適な実施形態を説明する。

【0051】

金属細線をボンディングすることにより電気接続を行った半導体モジュール(ボンディングモジュール)の一般的構成を図1Aに、貫通電極を用いて電気接続を行った半導体モジュール(貫通電極モジュール)の一般的構成を、図1Bにそれぞれ示す。いずれの構成においても、二つの半導体デバイス(ここではチップ状の半導体デバイス、すなわち半導体チップとしている)を積層した二層構造になっている。

【0052】

図1Aの半導体モジュールは、樹脂、セラミック、半導体などで構成された基板10の上に第1半導体デバイス11aが接着剤17で固定され、第1半導体デバイス11aの上に第2半導体デバイス12aが接着剤17で固定されている。第1半導体デバイス11a及び第2半導体デバイス12aと基板10との電気接続は、いずれもボンディングワイヤ13を用いて行われている。

【0053】

図1Bの半導体モジュールは、樹脂、セラミック、半導体などで構成された基板10の上に第1半導体デバイス11bが導電性ボール15で固定され、第1半導体デバイス11bの上に第2半導体デバイス12bが導電性ボール15で固定されている。第1半導体デバイス11aの表面と裏面は、第1半導体デバイス11aの内部を貫通する貫通電極14によって相互に電気接続されている。第1半導体デバイス11aと第2半導体デバイス11bの電気接続と、第1半導体デバイス11aと基板10との電気接続は、いずれも導電性ボール15を用いて行われている。さらに、基板10と第1半導体デバイス11bの間と、第1半導体デバイス11bと第2半導体デバイス12bの間には、フィラー16が充填されていて、導電性ボール15による接続強度を増大させている。

【0054】

図1Aと図1Bに示した半導体モジュールには、それぞれ得失がある。

【0055】

図1Aの半導体モジュール(ボンディングモジュール)は、第1半導体デバイス11aと第2半導体デバイス12aを単に積層し、ボンディングワイヤで電気配線を行うだけであるから、新たな技術開発は不要である。ただし、第1半導体デバイス11aの大きさは第2半導体デバイス12aより大きいこと、高さが異なる位置からのワイヤボンディングができること等が要件となる。この手法で、3層以上に半導体デバイスを積層化を行った半導体モジュールもある。なお、図1Aのワイヤボンディングを用いた半導体モジュールの周辺に冷却用の流体(冷媒)を流す場合には、ボンディングワイヤ(金属細線)13が切断されないように、ボンディングワイヤ13の保護を施す必要がある。

【0056】

図1Bの半導体モジュール(貫通電極モジュール)では、下側の第1半導体デバイス11bに貫通電極14を埋め込む技術、多数の導電性ボール15の搭載・溶融・再凝固を安定して行う製造技術、さらには、基板10と第1半導体デバイス11bの間と、第1半導体デバイス11bと第2半導体デバイス12bの間の狭い空間に、フィラーを流し込む技術等が必要となる。この半導体モジュールでは、配線に関わる領域の全てが半導体チップ11b、12bの内部にあるかフィラー16で覆われているので、冷却用の流体(冷媒)の流動があっても半導体モジュールが破壊されることは少ない。

【0057】

(第1実施形態のインターポーザ)

本発明の第1実施形態のインターポーザを図2Aと図2Bに示す。図2Aはこのインターポーザの要部構成を示す部分断面図であり、図2Bは同インターポーザの全体構成を示す断面説明図である。

【0058】

本発明の第1実施形態のインターポーザ24は、上壁20aと、下壁20bと、上壁20a及び下壁20bを相互に連結する側壁20cとからなる本体を備えており、その本体の内部に真空に維持されたキャビティ23が形成されている。インターポーザ24の全体形状は、中空の板状である。上壁20a及び下壁20bは、キャビティ23の天井と床をそれぞれ形成する。側壁20cは、キャビティ23の天井と床をつなぐ周壁を形成する。

【0059】

なお、図2Aに示された符号25と26は、上壁20aと下壁20bがそれぞれ接触している熱源である。熱源25、26の例としては、半導体モジュールを構成している半導体デバイスがある。

【0060】

上壁20a及び下壁20bの内面には、絶縁層22a及び22bがそれぞれ形成されている。枠状の側壁20cの内面にも、絶縁層22cが形成されている。したがって、上壁20a、下壁20b及び側壁20cの内面(つまりキャビティ23の内壁面)の全体が、絶縁層22a、22b及び22cで覆われている。

【0061】

絶縁層22a及び22bの内側には、熱反射層21a及び21bがそれぞれ形成されている。絶縁層22cの内側には、熱反射層21cが形成されている。したがって、絶縁層22a、22b及び22cの表面の全体が、熱反射層21a、21b及び21cで覆われている。なお、熱反射層21a、21b及び21cは、それぞれ熱反射領域を形成するから、図2Bの構成では、絶縁層22a、22b及び22cの全表面が熱反射領域になっていると言うことができる。

【0062】

このように、キャビティ23を形成する本体の内壁面(つまり上壁20a、下壁20b及び側壁20cの内面)は、いずれも、絶縁層22a、22b及び22cと熱反射層21a、21b及び21cの二層で覆われている。

【0063】

熱反射層21a及び21bは、上壁20a及び下壁20bを介して上方及び下方から入射する熱を反射する機能を有しており、金属薄膜などから構成されることが多い。例えば、金やアルミの薄膜が使用可能であり、その表面は鏡面であることが好ましいが、鏡面でなくてもよい。また、熱反射層21a及び21bは、それぞれ、上壁20aの内面(図2A及び図2Bでは下位表面)および下壁20bの内面(図2A及び図2Bでは上位表面)の全体にわたって配置されていることが好ましいが、この限りではない。例えば、上壁20aの内面の指定された領域にのみ、熱反射層21aが配置されている構成としてもよい。下壁20bについても同様である。

【0064】

上壁20a及び下壁20bは、熱伝導率が小さい材料で構成されていることが好ましいが、必ずしもこの限りではない。上壁20a及び下壁20bがシリコン単結晶で構成され、それぞれの外面(図2A及び図2Bでは上位表面)に電子部品やトランジスタなどからなる電子回路、あるいは、電気配線層が配置されている場合には、絶縁層22aと22bをそれぞれ配置することが好ましい。絶縁層22aと22bは、当該電子回路などが熱反射層21a及び21b(これらは金属薄膜であるから導電性を持つ)で短絡することを防止する役割を持つ。このような必要性がない場合は、絶縁層22aと22bは省略できる。

【0065】

キャビティ23は真空に維持されているから、周知ように、キャビティ23の熱伝導率は非常に小さい。

【0066】

図2Aにおいて、上位にある熱源25で発生した熱は、まず、(1)上壁20aと絶縁層22aの内部を伝達され、熱反射層21aの表面に到達する。しかし、この熱の多くは、熱反射層21aの表面で反射され、熱源25の方に戻る。(2)熱反射層21aの表面で反射せずに熱反射層21aを通過した少量の熱は、真空に維持されているキャビティ23の内部に放射される。しかし、真空の熱伝導率は小さいので、キャビティ23の内部を通過して熱反射層21bに到達する熱は、さらに少なくなる。(3)キャビティ23の内部を通過して熱反射層21bまで到達した熱は、熱反射層21bの表面で反射される。このため、熱反射層21bを通過する熱はさらに減少する。その結果、熱源25で発生した熱のうち、熱源26まで到達する量は非常に少なくなる。熱源26で発生した熱についても、同様な状況にあるから、熱源25まで到達する量は非常に少なくなる。

【0067】

以上述べたように、熱源25と26は、インターポーザ24で「熱的に絶縁」されることになる。このため、例えば、熱源26が大電力を消費する半導体デバイスであり、熱源25が熱に敏感な特性を有する半導体デバイスであっても、熱源26が熱源25へ与える影響をインターポーザ24によって大きく低減させることが可能である。

【0068】

インターポーザ24の本体を形成する側壁20cは、真空に維持されたキャビティ23を形成するために必須な構成要素であるが、熱的に絶縁されるべき上壁20aと下壁20bとの間に熱伝導路を形成してしまう。このため、側壁20cの厚さは可能な限り小さく(薄く)設定されることが好ましい。側壁20cを、上壁20aと下壁20bとは異なる素材(熱伝導率が小さいことが好ましい)で構成することも可能である。なお、側壁20cの内面を絶縁する必要がなければ、側壁20cの内面に形成された絶縁層22cは省略可能である。

【0069】

図2Bの構成では、熱反射層21a、21b及び21cをキャビティ23を形成する本体の内面全体に配置しているが、本体の内面の指定された領域に限定して配置してもよい。例えば、キャビティ23の天井と床をそれぞれ形成する上壁20a及び下壁20bの内面にのみ熱反射層21a及び21bを配置し、キャビティ23の周壁を形成する側壁20cの内面の熱反射層21cを省略してもよい。また、熱反射層21a及び21bも、必ずしも上壁20a及び下壁20bの内面全体にそれぞれ配置する必要はなく、指定された領域に限定して配置してもよい。例えば、後述する図3A及び図3Bの構成例のように、上壁20aと下壁20bの側壁20cに近い領域で、それぞれ、熱反射層21aと21bを省略するのである。

【0070】

本発明の第1実施形態のインターポーザ24は、上述したような構成を有しているので、前記本体の一方の側に配置された熱源25(例えば半導体デバイス)から生じた熱が、伝導によって前記本体を移動する際に、その熱伝導は、真空状態にあるキャビティ23によって効果的に抑制される。前記熱の一部はキャビティ23内を伝導するが、キャビティ23の内壁面には、熱反射層21a、21b及び21c(これらは熱反射領域として機能する)が形成されているので、キャビティ23内を伝導した熱の多くは、熱反射層21a、21b及び21cで反射され、それ以上伝導しない。したがって、熱源25から前記本体中を移動して熱源26に到達する熱の量は、大きく減少する。

【0071】

逆に、熱源26から生じた熱が、前記本体中を移動して熱源25に到達する量も、同様の理由で、非常に少なくなる。

【0072】

このように、熱源25と熱源26が、本第1実施形態のインターポーザ24によって熱的に絶縁されることになるから、このインターポーザ24によれば、二つの熱源25と26の間に配置した際にそれら熱源25、26間での熱伝導をより効果的に抑制することができる。

【0073】

また、2個以上の半導体デバイスを積層してなる半導体モジュールにおいて、積層方向に隣接する半導体デバイスの間にこのインターポーザ24を介在させれば、それら半導体デバイス間での熱伝導をより効果的に抑制することができる。よって、それら半導体デバイスの温度上昇を抑えて安定に動作させることができる。

【0074】

(第2実施形態の半導体モジュール−ボンディングモジュール)

本発明の第2実施形態の半導体モジュールを図3Aと図3Bに示す。図3Aはこの半導体モジュールの全体構成を示す断面図であり、図3Bは図3Aの同半導体モジュールのA−A線に沿った断面図である。

【0075】

本第2実施形態の半導体モジュールM1は、上述した第1実施形態のインターポーザ24を、図1Aに示したボンディングモジュールに適用した例である。

【0076】

図3Aと図3Bに示すように、半導体モジュールM1は、接着剤17などで基板10の上に固定された第1半導体デバイス11aの表面に、インターポーザ24が搭載されており、インターポーザ24の表面に第2半導体デバイス12aが搭載されている。インターポーザ24は、第1半導体デバイス11aの表面に接着剤17などで固定されている。第2半導体デバイス12aは、インターポーザ24の表面に接着剤17などで固定されている。第1半導体デバイス11a及び第2半導体デバイス12aと基板10との電気接続は、いずれもボンディングワイヤ13を用いて行われている。

【0077】

インターポーザ24は、真空に維持されたキャビティ23を有し、キャビティ23の内壁を形成する上壁20a(天井)及び下壁20b(床)に、熱反射層21aと21bがそれぞれ配置されている。熱反射層21bは、図3Bに示すように、下壁20bの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。熱反射層21aも、同様に、上壁20aの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。

【0078】

以上の構成を有する第2実施形態の半導体モジュールM1では、第1半導体デバイス11aと第2半導体デバイス12aの間にインターポーザ24が配置されているため、第1半導体デバイス11aと第2半導体デバイス12aは、インターポーザ24の内部の真空に維持されたキャビティ23によって熱的に絶縁(遮断)される。つまり、第1半導体デバイス11aで発生した熱は、第2半導体デバイス12aに伝達されないし、第2半導体デバイス12aで発生した熱も、第1半導体デバイス11aに伝達されない。このため、第1半導体デバイス11aと第2半導体デバイス12aの間での熱伝導をより効果的に抑制することができる。よって、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイス11a、12aの温度上昇を抑えて安定に動作させることができる。

【0079】

しかし、第1半導体デバイス11aで発生した熱の一部は、側壁20cを通して第2半導体デバイス12aに伝達され、第2半導体デバイス12aで発生した熱の一部も、側壁20cを通して第1半導体デバイス11aに伝達されてしまう。側壁20cを介したこの熱伝達を小さくする対策としては、上述したように、側壁20cの厚さを小さくしたり、側壁20cを第1及び第2の半導体デバイス11a及び12aとは異なる材料(できる限り熱伝導率が小さい材料が好ましい)で形成したりすることが考えられる。

【0080】

第2実施形態の半導体モジュールM1では、第1半導体デバイス11aで発生した熱が第2半導体デバイス12aに伝達されないし、第2半導体デバイス12aで発生した熱も第1半導体デバイス11aに伝達されない。(より正確には「伝達されにくい」である。)しかしながら、第2半導体デバイス12aからの熱放散(例えば、第2半導体デバイス12aの上方空間への熱放散)や、第1半導体デバイス11aからの熱放散(例えば、基板10を介した下方空間への熱伝導)がないと仮定した場合には、時間の経過と共に両半導体デバイス11a及び12aの温度が等しくなるように、熱の移動が行われる。すなわち、時間の経過とともに、インターポーザ24の断熱性が活かされなくなる。現実には、上記の熱放散や熱伝導が行われるので、当該仮定は成立しないが、第1半導体デバイス11aまたは第2半導体デバイス12aからの熱放散や熱伝導を積極的に促進する構成をとることにより、インターポーザ24の断熱効果を増加することができる。以下、その例を第3及び第4の実施形態として示す。

【0081】

(第3実施形態の半導体モジュール−ボンディングモジュール)

本発明の第3実施形態の半導体モジュールを図4Aに示す。この半導体モジュールは、上述した第2実施形態の半導体モジュールM1に放熱板30を装着したものである。放熱板30は、基板10の裏面(下面)に密着して固定されている。

【0082】

第1半導体デバイス11aで発生した熱は、基板10を経由して放熱板30に伝達され、放熱板30の多数の放熱フィンから周囲の空間に放散される。このような放熱機能により、第1半導体デバイス11aの温度上昇が抑制され、結果として、第2半導体デバイス12aの温度上昇が抑制される。

【0083】

本第3実施形態の半導体モジュールでは、このように、第1半導体デバイス11aで発生する熱を、放熱板30により第1半導体デバイス11aの周辺から取り去ることで、発熱する第1半導体デバイス11aの温度上昇が抑制される。また、第1半導体デバイス11aで発生した熱の第2半導体デバイス12aへの伝導は、キャビティ23を有するインターポーザ24で阻止される。こうすることで、インターポーザ24の断熱効果の有効性を増大させている。

【0084】

このような構成をとっているため、第2半導体デバイス12aが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12aの温度上昇が抑制され、したがって、第2半導体デバイス12aの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0085】

(第4実施形態の半導体モジュール−ボンディングモジュール)

本発明の第4実施形態の半導体モジュールを図4Bに示す。この半導体モジュールは、上述した第2実施形態の半導体モジュールM1に、インレット32とアウトレット33を持つケース31を装着したものである。ケース31は、下面を開放した略直方体の箱状であり、基板10の表面(上面)に密着して固定されている、ケース31は、半導体モジュールM1の全体を覆って(包含して)いる。

【0086】

基板10とケース31により、略直方体の内部空間Sが形成されており、半導体モジュールM1はその内部空間Sに所在している。ケース31は、熱を吸収する流体Lを外部から内部空間Sに導入するためのインレット32と、流体Lを内部空間Sから外部に排出するためのアウトレット33とを有している。内部空間Sは、インレット32とアウトレット33を除いて閉じた空間である。

【0087】

矢印35は、インレット32へ流入する冷却用流体Lの流れ、矢印36は、アウトレット33から流出する流体Lの流れを示している。インレット32には、矢印35で示すように流体Lが流れ込み、内部空間Sに入る。流体Lは、内部空間Sを流動した後、矢印36で示すようにアウトレット33から流れ出る。

【0088】

インレット32とアウトレット33には、それぞれ、樹脂製あるいは金属製の管T1とT2の一端が接続されている。管T1の他端と管T2の他端は、それぞれ、流体Lに所定圧力を加えてインレット32に供給するポンプPの送出口と復帰口に接続されている。流体Lの加圧機構としては、流体Lに所定圧力を加えてインレット32に供給するものであればよく、ポンプ以外も使用可能である。

【0089】

熱を吸収する流体Lは、管T1を介して、ポンプPにより所定圧力をもってケース31の内部空間Sに送り込まれる。送り込まれた流体Lは、管T2を介してポンプPまで戻される。流体Lは、このようにして、ポンプP→管T1→内部空間S→管T2→ポンプPと循環する。流体Lは、内部空間Sにおいて半導体モジュールM1から生じた熱を吸収し、また、吸収した熱を外部を流動する間に自然放散する。半導体モジュールM1から生じた熱は、こうしてケース31の外部に放散せしめられる。このため、インレット32に供給される際には、流体Lは冷却されている。

【0090】

流体Lは、半導体モジュールM1で発生した熱を吸収してこれを冷却できるような性質を有しているものが好ましい。このような流体Lの例としては、(1)フロン類・ノンフロン類、(2)ブタン、イソブタンなどの有機化合物、(3)水素、ヘリウム、アンモニア、水、二酸化炭素などの無機化合物がある。いずれも「冷媒」とも称されているが、本第4実施形態においては、冷媒の種類に限定されることはない。

【0091】

下層にある第1半導体デバイス11aで発生した熱は、流体Lに伝達され、流体Lの流れによってアウトレット33から外部へ放散される。この放熱機能により、第1半導体デバイス11aの温度上昇が抑制され、結果として、上層にある第2半導体デバイス12aの温度上昇が抑えられることになる。

【0092】

本第4実施形態の半導体モジュールでは、上記第3実施形態とは異なり、流体Lによって半導体モジュールM1の全体から熱を取り去ることで、発熱する第1半導体デバイス11aの温度上昇が抑制される。また、第1半導体デバイス11aで発生した熱の第2半導体デバイス12aへの伝導は、キャビティ23を有するインターポーザ24で阻止される。こうすることで、インターポーザ24の断熱効果の有効性を増大させている。

【0093】

このような構成をとっているため、第2半導体デバイス12aが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12aの温度上昇が抑制され、したがって、第2半導体デバイス12aの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0094】

(第5実施形態の半導体モジュール−貫通電極モジュール)

本発明の第5実施形態の半導体モジュールを図5Aと図5Bに示す。図5Aはこの半導体モジュールの全体構成を示す断面図であり、図5Bは図5Aの同半導体モジュールのB−B線に沿った断面図である。

【0095】

本第5実施形態の半導体モジュールM2は、上述した第1実施形態のインターポーザ24を、図1Bに示した貫通電極モジュールに適用した例である。

【0096】

図5Aと図5Bに示すように、半導体モジュールM2は、導電性ボール15で基板10の上に固定された第1半導体デバイス11bの表面に、インターポーザ40が搭載されており、インターポーザ40の表面に第2半導体デバイス12bが搭載されている。インターポーザ40は、第1半導体デバイス11bの表面に導電性ボール43で固定されている。第2半導体デバイス12bは、インターポーザ40の表面に導電性ボール43で固定されている。

【0097】

インターポーザ40は、真空に維持されたキャビティ43を有し、キャビティ43の内壁を形成する上壁20a(天井)及び下壁20b(床)に、熱反射層21aと21bがそれぞれ配置されている。熱反射層21bは、図5Bに示すように、下壁20bの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。熱反射層21aも、同様に、上壁20aの内面をその周辺領域(側壁20cの近傍にある細い矩形枠状の領域)を除いて選択的に覆っている。

【0098】

インターポーザ40の内部には、その表面と裏面を電気接続する貫通電極42が形成されている。ただし、インターポーザ40を構成する要素との間の絶縁膜は、図示されていない。インターポーザ40の下面(裏面)と第1半導体デバイス11bとの電気接続は、導電性ボール43で行われている。インターポーザ40の上面(表面)と第2半導体デバイス12bとの電気接続も、導電性ボール43で行われている。

【0099】

インターポーザ40の表面と裏面には、導電性ボール43と電気接続され、かつ、表裏接続用の貫通電極42と電気接続されている電極パッドのみが描かれているが、これには限定されない。例えば、インターポーザ40の表面あるいは裏面に、1層あるいは2層以上の電気配線層を設け、第2半導体デバイス12bからの配線を再配線して、第1半導体デバイス11bに接続するように構成してもよい。この構成では、インターポーザ40をシリコン単結晶で形成することが好ましいが、これには限定されない。例えば、樹脂性のインターポーザ40に上記した1層あるいは2層以上の配線層を設けてもよい。

【0100】

以上の構成を有する第5実施形態の半導体モジュールM2においても、第1半導体デバイス11bと第2半導体デバイス12bの間にインターポーザ40が配置されているため、第1半導体デバイス11bと第2半導体デバイス12bは、インターポーザ40の内部の真空に維持されたキャビティ41によって熱的に絶縁(遮断)される。つまり、第1半導体デバイス11bで発生した熱は、第2半導体デバイス12bに伝達されないし、第2半導体デバイス12bで発生した熱も、第1半導体デバイス11bに伝達されない。(より正確には「伝達されにくい」である。)このため、第1半導体デバイス11bと第2半導体デバイス12bの間での熱伝導をより効果的に抑制することができる。よって、消費電力の大きい半導体デバイスを含んでいても、積層された半導体デバイス11b、12bの温度上昇を抑えて安定に動作させることができる。

【0101】

また、上記第2実施形態と同様に、第1半導体デバイス11bで発生した熱の一部は、側壁20cを通して第2半導体デバイス12bに伝達され、第2半導体デバイス12bで発生した熱の一部も、側壁20cを通して第1半導体デバイス11bに伝達されてしまうが、本第5実施形態では貫通電極42が設けられているため、熱的な絶縁性が、上記第2実施形態よりも劣っている。これは、貫通電極42に好適な導電性が高い材料は、一般に熱伝導率も高いため、貫通電極42を介して熱伝導が行われるからである。しかしながら、貫通電極42の大きさ(断面積)を小さくすることにより、熱的な絶縁性の低下を阻止することは可能である。

【0102】

上記第2実施形態と同様に、第1半導体デバイス11bまたは第2半導体デバイス12bからの熱放散や熱伝導を積極的に促進する構成をとることにより、インターポーザ40の断熱効果を増加することができる。以下、その例を第6及び第7の実施形態として示す。

【0103】

(第6実施形態の半導体モジュール−貫通電極モジュール)

本発明の第6実施形態の半導体モジュールを図6Aに示す。この半導体モジュールは、上述した第5実施形態の半導体モジュールM2に放熱板30を装着したものである。放熱板30は、基板10の裏面(下面)に密着して固定されている。

【0104】

第1半導体デバイス11bで発生した熱は、基板10を経由して放熱板30に伝達され、放熱板30の多数の放熱フィンから周囲の空間に放散される。このような放熱機能により、第1半導体デバイス11bの温度上昇が抑制され、結果として、第2半導体デバイス12bの温度上昇が抑制される。

【0105】

本第6実施形態の半導体モジュールでは、このように、第1半導体デバイス11bで発生する熱を、放熱板30により第1半導体デバイス11bの周辺から取り去ることで、発熱する第1半導体デバイス11bの温度上昇が抑制される。また、第1半導体デバイス11bで発生した熱の第2半導体デバイス12bへの伝導は、キャビティ41を有するインターポーザ40で阻止される。こうすることで、インターポーザ40の断熱効果の有効性を増大させている。

【0106】

このような構成をとっているため、第2半導体デバイス12bが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12bの温度上昇が抑制され、したがって、第2半導体デバイス12bの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0107】

(第7実施形態の半導体モジュール−貫通電極モジュール)

本発明の第4実施形態の半導体モジュールを図4Bに示す。この半導体モジュールは、上述した第5実施形態の半導体モジュールM2に、上述した第4実施形態で使用したインレット32とアウトレット33を持つケース31を装着したものである。ケース31は、下面を開放した略直方体の箱状であり、基板10の表面(上面)に密着して固定されている、ケース31は、半導体モジュールM2の全体を覆って(包含して)いる。

【0108】

基板10とケース31により略直方体の内部空間Sが形成されており、半導体モジュールM2は、その内部空間Sに所在している。ケース31は、熱を吸収する流体Lを外部から内部空間Sに導入するためのインレット32と、流体Lを内部空間Sから外部に排出するためのアウトレット33とを有している。内部空間Sは、インレット32とアウトレット33を除いて閉じた空間である。

【0109】

流体Lに所定圧力を加えてインレット32に供給するポンプPと、インレット32及びアウトレット33とポンプPとを接続する管T1とT2、そして、熱を吸収する流体Lは、上述した第4実施形態で使用したものと同じである。

【0110】

流体Lは、ポンプP→管T1→内部空間S→管T2→ポンプPと循環する。流体Lは、内部空間Sにおいて半導体モジュールM2から生じた熱を吸収し、また、吸収した熱を外部を流動する間に自然放散する。半導体モジュールM2から生じた熱は、こうしてケース31の外部に放散せしめられる。

【0111】

下層にある第1半導体デバイス11bで発生した熱は、流体Lに伝達され、流体Lの流れによってアウトレット33から外部へ放散される。この放熱機能により、第1半導体デバイス11bの温度上昇が抑制され、結果として、上層にある第2半導体デバイス12bの温度上昇が抑えられることになる。

【0112】

本第7実施形態の半導体モジュールでは、上記第6実施形態とは異なり、流体Lによって半導体モジュールM2の全体から熱を取り去ることで、発熱する第1半導体デバイス11bの温度上昇が抑制される。また、第1半導体デバイス11bで発生した熱の第2半導体デバイス12bへの伝導は、キャビティ41を有するインターポーザ40で阻止される。こうすることで、インターポーザ40の断熱効果の有効性を増大させている。

【0113】

このような構成をとっているため、第2半導体デバイス12bが動作温度に敏感な特性を有していたとしても、第2半導体デバイス12bの温度上昇が抑制され、したがって、第2半導体デバイス12bの動作温度を低くかつ一定にすることが可能である。その結果、動作が安定した半導体モジュールを実現することができる。

【0114】

(第8実施形態のインターポーザの形成方法)

次に、上述したインターポーザの形成方法について説明する。

【0115】

図7は、本発明の第8実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第1例である。

【0116】

まず、図7(a)に示すように、矩形板状の上壁(上板)50の下面に、矩形の熱反射層51を形成する。熱反射層51は、上壁50の下面の周辺領域を除いて形成されており、その下面の全体を覆っていないが、これには限定されない。上壁50の下面全体を覆っていてもよい。

【0117】

次に、図7(b)に示すように、矩形板状の下壁(下板)54の上面に、矩形の熱反射層53を形成する。熱反射層53も、下壁54の上面の周辺領域を除いて形成されており、その上面の全体を覆っていないが、これには限定されない。下壁54の上面全体を覆っていてもよい。

【0118】

熱反射層51を形成した上壁50と熱反射層53を形成した下壁54は、同一構成であってもよい。つまり、同一構成のものを2個形成してもよい。また、上壁50と下壁54は、熱伝導が小さい素材であることが好ましいが、この限りではない。熱反射層51と53は、例えば、金、アルミニウムなどの金属を蒸着するといった手法で形成することができる。

【0119】

次に、図7(c)に示すように、下壁54の周辺部に側壁52を形成する。側壁54の素材としては、ガラスや樹脂などで使用でき、接着などの手法により下壁54の周辺部に密着せしめられる。

【0120】

次に、図7(d)に示すように、接着材などを用いて、側壁54の上面に上壁50の下面を密着(接合)させる。この密着により、上壁50と下壁54と側壁52が一体化されて、インターポーザの本体が形成され、同時に、その本体の内部にキャビティ55が形成される。キャビティ55は、真空であることが必須であるから、この密着(接合)工程は真空雰囲気中で実施される。

【0121】

以上の工程を経て本発明のインターポーザが作成される。上壁50、下壁54、側壁52といった構成要素の素材と、上壁50と下壁54の密着のための接着材等は、長期にわたってキャビティ55内の真空状態が維持されるように選択される。一例を挙げると、上壁50と下壁54は単結晶シリコン、側壁52はガラスが好適に使用できる。このような素材を採用すれば、下壁54と側壁52との接合、側壁52と上壁50との接合に、静電接合技術を用いることが可能である。さらに、静電接合は真空中で実施され、かつ、当該静電接合の真空封止性は十分に高いため、長期にわたるキャビティ55内の真空が維持されることになる。上壁50と下壁54は単結晶シリコン製であるため、周知の技術を用いて、それぞれの表面に1層以上の配線層を形成することも可能である。

【0122】

なお、図7には示していないが、図7(d)の構成を持つインターポーザの周辺部に、貫通電極を形成することも可能である。例えば、RIE(反応性イオンエッチング)などの加工技術を用いて、上壁50(単結晶シリコン)、側壁52(ガラス)、下壁54(単結晶シリコン)に上下方向の貫通穴を開け、その内部に導電材料を付着あるいは充填することにより、貫通電極を形成することができる。なお、上壁50及び下壁54と前記導電材料との間には、適当な絶縁膜を設けて電気的に絶縁する必要がある。

【0123】

(第9実施形態のインターポーザの形成方法)

図8は、本発明の第9実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第2例である。

【0124】

まず、図8(a)に示すように、矩形板状の上壁(上板)60の下面に、矩形の熱反射層61を形成する。熱反射層61は、上壁60の下面の周辺領域を除いて形成されており、その下面の全体を覆っていないが、これには限定されない。上壁60の下面全体を覆っていてもよい。この工程は、図7(a)のそれと同じである。

【0125】

次に、図8(b)に示すように、側壁63を有する矩形板状の下壁62(下板)(側壁63の内側に窪み67が形成されている)を用意し、側壁63の内側領域の上面(窪み67の底面)に矩形の熱反射層64を形成する。この工程では、上述した第8実施形態(図7)とは異なり、下壁62と側壁63とが一体的に構成されたものを使用している。この構成は、下壁62の母材の中央領域に窪み67を形成し、その窪み67の底面に熱反射層64を形成することにより容易に実現される。具体的に言えば、単結晶シリコン板の上側表面にパターニングされたフォトレジスト層を作成し、このフォトレジスト層をマスクとしてRIEなどでエッチングして、窪みを形成すればよい。ただし、単結晶シリコン板の厚さは、側壁63の厚さ(高さ)と同じにする。続いて、この窪みの底部に金、アルミなどの金属を蒸着等で堆積させ、熱反射層64とする。

【0126】

熱反射層64は、ここでは、下壁62の窪み67の底面の周辺領域を除いて形成されており、その底面の全体を覆っていないが、これには限定されない。熱反射層64は、窪み67の底面全体を覆っていてもよいし、その底面から側壁63の内側面にかけての領域を覆ってもよいし、この内側面から側壁63の上端面に至る領域までを覆っていてもよい。

【0127】

次に、図8(c)に示すように、エポキシ系接着材65などを用いて、側壁63の上端面に上壁60の下面を密着(接合)させる。これにより、上壁60と、側壁63を持つ下壁62とが一体化されて、インターポーザの本体が形成され、同時に、その本体の内部にキャビティ66が形成される。キャビティ66は、真空であることが必須であるから、この密着(接合)工程は真空雰囲気中で実施される。

【0128】

上壁60と、側壁63を持つ下壁62とが、いずれも単結晶シリコンで構成されていて、側壁63の上端面に熱反射層64が形成されていない場合には、図8(c)の工程で上壁60と側壁63とをシリコン・シリコンの熱接合で密着させることも可能である。

【0129】

なお、図8には示していないが、上述した第8実施形態(図7)と同様に、図8(c)の構成を持つインターポーザの周辺部に、貫通電極を形成することも可能である。

【0130】

(第10実施形態のインターポーザの形成方法)

図9は、本発明の第10実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第3例である。

【0131】

まず、図9(a)に示すように、下壁(下板)の母材70aとして矩形のシリコン単結晶板を用意する。

【0132】

次に、図9(b)に示すように、母材70aの周辺部に、周知の手法によって貫通電極71を形成する。具体的に言えば、RIEにより母材70aの周辺部に貫通穴を開け、これら貫通穴の内側面を絶縁層(図示せず)で覆ってから、これら絶縁層の内側に導電性材料を被覆あるいは充填する。こうして貫通穴に導電性を付与することで、貫通電極71が形成される。その後、母材70aの表面と裏面にそれぞれ電気接続用パッド72を形成し、貫通電極71と電気接続する。

【0133】

次に、母材70aの表面側から、パターニングされたマスク(フォトレジストなど)を利用して、窪み73を掘り込む。窪み73の作成には、例えば、TMAH(テトラメチルアンモニアハイドロオキサイド)やKOH(水酸化カリウム)などの異方性エッチング液が利用される。これらのエッチング液では、特定のシリコン結晶面((111)面)でエッチング速度が低いため、窪み73の縁(窪み73の底から基板70の表面にかけての斜面)は露出した(111)面となる。こうして、下壁(下板)70が形成される。その後、窪み73の底面に熱反射層74を形成する。この時の状態は図9(c)のようになる。

【0134】

次に、図9(d)に示すように、矩形のシリコン単結晶板からなる上壁(上板)75の上面から前記した異方性エッチング液で、パッド72を露出させるための開口76を形成する。また、開口76と重ならないように、上壁75の下面に熱反射層77を形成する。

【0135】

次に、図9(c)に示した下壁70の上面に、図9(d)に示した上壁75を密着(接合)させ、図9(e)に示した構造を持つインターポーザを得る。この密着(接合)には、接着材や低融点ガラスなどが用いられる。下壁70の窪み73により、キャビティ78が形成される。キャビティ78内は真空であることが必要であるため、前記密着(接合)工程は真空雰囲気中で実施される。

【0136】

本実施形態では、上壁75と下壁70がいずれもシリコン単結晶から形成されているため、インターポーザの本体の表面と裏面に1層以上の配線層を形成することも可能である。

【0137】

(第11実施形態のインターポーザの形成方法)

図10は、本発明の第11実施形態のインターポーザの形成方法を示す。この方法は、上記インターポーザの形成方法の第4例である。図10において、図9におけるそれと同一の符号は、同一の構成要素を示している。

【0138】

図10(a)から図10(c)までの工程は、図9(a)から図9(c)の工程までと同じであるから、その説明は省略する。

【0139】

次に、図10(d)に示すように、熱反射層84を備えた上壁(上板)85を形成する。この上壁85は、母材としての単結晶シリコン板の周縁部をエッチング等で斜めに除去してテーパ状とし、その下面に熱反射層84を形成することで、容易に得られる。

【0140】

次に、接着材や低融点ガラスなどを用いて、図10(c)に示した下壁(下板)70の上面に、図10(d)に示した上壁(上板)85を密着(接合)させ、図10(e)に示した構造を得る。窪み73はキャビティ86を構成し、当該キャビティ内は真空であることが必要であるため、前記密着のプロセスは真空雰囲気中で実施される。

【0141】

本実施形態では、上述した第10実施形態(図9)とは異なり、上板85が下板70の窪み73の中に入り込む構成になっている。つまり、下板70の側壁部(パッド72が設けられている部分)の表面を、上板85が覆っていない。この構成では、上板85に開口(図9の開口76に対応する)を設ける必要がなく、製造技術上、簡便であるという利点がある。

【0142】

(変形例)

以上、本発明の実施形態について詳細な説明を行った。本明細書では、インターポーザの構成と、このインターポーザを用いた半導体モジュールについて記載したが、例示した構成以外にも多くの構成が可能である。

【0143】

例えば、第2半導体デバイスの消費電力が第1半導体デバイスの消費電力よりも大きいような構成、半導体デバイスを3層以上に積層した構成、インターポーザを挟み込む上下の半導体デバイスがそれぞれ2個以上の構成(例えば、インターポーザの上面に、同一平面内で複数個の半導体デバイスが配置されている構成)なども可能である。

【0144】

いずれの構成においても、インターポーザの真空層でその両側にある半導体デバイス間の熱的絶縁を図り、高密度・高速の半導体モジュールを実現することが本発明の趣旨である。

【産業上の利用可能性】

【0145】

本発明は、消費電力の増大傾向がある半導体デバイスの冷却を容易にするインターポーザ、および、それを用いた半導体モジュールと実装構造に適用可能である。また、本発明は、電子回路を主体とする半導体モジュールに限定されることなく、他の大電力デバイス(例えば、発光素子モジュール、光通信モジュールなど)にも広く適用可能である。

【符号の説明】

【0146】

11a、11b 半導体デバイス

12a、12b 半導体デバイス

13 ボンディングワイヤ

14 貫通電極

15 導電性ボール

16 フィラー

17 接着剤

20a 上壁

20b 下壁

20c 側壁

21a、21b、21c 熱反射層

22a、22c 絶縁層

23 キャビティ

24 インターポーザ

25、26 熱源

30 放熱板

31 ケース

32 インレット

33 アウトレット

40 インターポーザ

41 キャビティ

42 貫通電極

43 キャビティ

43 導電性ボール

50 上壁

51 熱反射層

52 側壁

53 熱反射層

54 下壁

54 側壁

55 キャビティ

60 上壁

61 熱反射層

62 下壁

63 側壁

64 熱反射層

65 接着材

66 キャビティ

70 下壁

70a 下壁の母材

71 貫通電極

72 電気接続用パッド

74 熱反射層

75 上壁

76 開口

77 熱反射層

78 キャビティ

84 熱反射層

85 上壁

86 キャビティ

L 冷却用流体

M1 半導体モジュール

M2 半導体モジュール

P ポンプ

S 内部空間

T1 管

T2 管

【特許請求の範囲】

【請求項1】

真空に維持されたキャビティを有する本体と、

前記キャビティの内壁面に形成された熱反射領域と

を備えていることを特徴とするインターポーザ。

【請求項2】

前記本体が、第1熱源に隣接する上壁と、第2熱源に隣接する下壁と、前記上壁と前記下壁を連結する側壁を備えており、前記上壁と前記下壁と前記側壁が前記キャビティを画定することを特徴とする請求項1に記載のインターポーザ。

【請求項3】

前記熱反射領域が、前記上壁の内面と前記下壁の内面に形成され、前記側壁の内面には形成されていないことを特徴とする請求項2に記載のインターポーザ。

【請求項4】

請求項1または3のいずれか1項に記載のインターポーザと、

前記インターポーザの一方の側に搭載された第1半導体デバイスと、

前記インターポーザの他方の側に搭載された第2半導体デバイスと

を備えていることを特徴とする半導体モジュール。

【請求項5】

前記第1半導体デバイスの側に装着された放熱板をさらに備えていることを特徴とする請求項4に記載の半導体モジュール。

【請求項6】

前記第1半導体デバイスと前記第2半導体デバイスと前記インターポーザを包含するケースと、冷却用流体を加圧して前記ケース内に導入する手段とをさらに備えていることを特徴とする請求項4に記載の半導体モジュール。

【請求項1】

真空に維持されたキャビティを有する本体と、

前記キャビティの内壁面に形成された熱反射領域と

を備えていることを特徴とするインターポーザ。

【請求項2】

前記本体が、第1熱源に隣接する上壁と、第2熱源に隣接する下壁と、前記上壁と前記下壁を連結する側壁を備えており、前記上壁と前記下壁と前記側壁が前記キャビティを画定することを特徴とする請求項1に記載のインターポーザ。

【請求項3】

前記熱反射領域が、前記上壁の内面と前記下壁の内面に形成され、前記側壁の内面には形成されていないことを特徴とする請求項2に記載のインターポーザ。

【請求項4】

請求項1または3のいずれか1項に記載のインターポーザと、

前記インターポーザの一方の側に搭載された第1半導体デバイスと、

前記インターポーザの他方の側に搭載された第2半導体デバイスと

を備えていることを特徴とする半導体モジュール。

【請求項5】

前記第1半導体デバイスの側に装着された放熱板をさらに備えていることを特徴とする請求項4に記載の半導体モジュール。

【請求項6】

前記第1半導体デバイスと前記第2半導体デバイスと前記インターポーザを包含するケースと、冷却用流体を加圧して前記ケース内に導入する手段とをさらに備えていることを特徴とする請求項4に記載の半導体モジュール。

【図1A】

【図1B】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図5A】

【図5B】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図11】

【図1B】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図5A】

【図5B】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−142458(P2012−142458A)

【公開日】平成24年7月26日(2012.7.26)

【国際特許分類】

【出願番号】特願2010−294618(P2010−294618)

【出願日】平成22年12月30日(2010.12.30)

【出願人】(503456832)株式会社ザイキューブ (36)

【Fターム(参考)】

【公開日】平成24年7月26日(2012.7.26)

【国際特許分類】

【出願日】平成22年12月30日(2010.12.30)

【出願人】(503456832)株式会社ザイキューブ (36)

【Fターム(参考)】

[ Back to top ]