インターリーブ型力率改善回路用インダクタ

【課題】リアクタとセンサコイルとの誘導結合を実現するためのコアをチョッパ回路の全てにおいて共通にして、インターリーブ型力率改善回路を小型化しつつ、各々のセンサコイルが自身に対応するリアクタに流れる電流が零となる時点を適切に検出する。

【解決手段】リアクタLm及びセンサコイルTm同士を第1結合係数で誘導結合し、リアクタLs及びセンサコイルTs同士を第2結合係数で誘導結合し、リアクタLm,Ls同士を端子101から見て同極性でかつ第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合し、センサコイルTm,Ts同士を端子106から見て同極性でかつ第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合する。

【解決手段】リアクタLm及びセンサコイルTm同士を第1結合係数で誘導結合し、リアクタLs及びセンサコイルTs同士を第2結合係数で誘導結合し、リアクタLm,Ls同士を端子101から見て同極性でかつ第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合し、センサコイルTm,Ts同士を端子106から見て同極性でかつ第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はインダクタに関し、特にインターリーブで動作する一対の力率改善回路に採用されるインダクタに関する。

【背景技術】

【0002】

非特許文献1には、臨界モードかつインターリーブで動作する一対の力率改善回路(以下、単に「インターリーブ型力率改善回路」と称す)が開示されている。インターリーブ型力率改善回路では、昇圧型のチョッパ回路の一対が並列接続されており、リアクタ、ダイオード、スイッチング素子を有している。

【0003】

非特許文献2には、インターリーブ型力率改善回路において、一対のリアクタが誘導結合する場合について説明されている。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】喜多村 守、「1.5kWの低ノイズ高調波対策電源を作れる臨界モード/インターリーブPFC IC R2A20112」、トランジスタ技術2008年5月号、CQ出版株式会社、2008年8月、第176頁乃至第184頁

【非特許文献2】Wei Wen and Yim-Shu Lee, “A Two-channel Interleaved Boost Converter with Reduced Core Loss and Copper Loss”,2004-35th Annual IEEE Power Electronics Specialists Conference,2004.

【発明の概要】

【発明が解決しようとする課題】

【0005】

非特許文献1で示されるように、インターリーブ型力率改善回路が、臨界モードかつインターリーブで動作するには、昇圧型のチョッパ回路の各々においてリアクタに流れる電流が零となる時点を検出する必要がある。この目的のため、チョッパ回路の各々においてリアクタに流れる電流を検出するため、当該リアクタと誘導結合した電流検出用のコイル(以下、単に「センサコイル」と称する)が備えられている。

【0006】

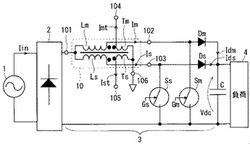

図11は従来のインターリーブ型力率改善回路30の構成を示す回路図である。インターリーブ型力率改善回路30は、リアクタLm,Ls、センサコイルTm,Ts、ダイオードDm,Ds、スイッチング素子Sm,Ss、コンデンサCを備えている。コンデンサCには負荷4が並列に接続されている。

【0007】

インターリーブ型力率改善回路30には整流回路2から直流電流が与えられ、これをリアクタLm,Lsへと分流し、負荷4へと直流電圧を供給する。整流回路2は交流電源1から交流の入力電流Iinを入力し、上述の直流電流を出力する。

【0008】

リアクタLm、ダイオードDm、スイッチング素子Smがマスター側のチョッパ回路を構成し、リアクタLs、ダイオードDs、スイッチング素子Ssがスレーブ側のチョッパ回路を構成する。

【0009】

スイッチング素子Sm,Ssはスイッチング信号Gm,Gsに従ってオン/オフする。リアクタLmに流れるインダクタ電流Imは、スイッチング素子Smのオン/オフに対応して、それぞれスイッチング素子Sm、ダイオードDm及びコンデンサCに流れる。リアクタLsに流れるインダクタ電流Isは、スイッチング素子Ssのオン/オフに対応して、それぞれスイッチング素子Ss、ダイオードDs及びコンデンサCに流れる。

【0010】

電流Im,Isが発生させた磁束の変化はセンサコイルTm,Tsに誘導電圧を生起し、センサコイルTm,Tsにはそれぞれ検知電流Ims,Issが流れる。

【0011】

制御部6は検知電流Ims,Issを検知し、それぞれの値が零となるタイミングを検出する。検知電流Imsの値が零となるタイミングはインダクタ電流Imの値が零となるタイミングと一致し、検知電流Issの値が零となるタイミングはインダクタ電流Isの値が零となるタイミングと一致する。制御部6はコンデンサCの両端電圧Vdc及びその指令値Vdc*をも入力する。

【0012】

図12はスイッチング素子Sm,Ssのオン/オフ動作と、インダクタ電流Im,Isの波形との関係を示すタイミングチャートである。臨界モードかつインターリーブでの動作を実現するため、制御部6は検知電流Imsの値が零となるタイミングでスイッチング信号Gmを活性化させてスイッチング素子Smをオンさせ、両端電圧Vdcが指令値Vdc*に至ればスイッチング信号Gmを非活性化させてスイッチング素子Smをオフさせる。

【0013】

制御部6は検知電流Issの値が零となるタイミングでスイッチング信号Gsを活性化させてスイッチング素子Ssをオンさせ、スイッチング信号Gsをスイッチング信号Gmと同じデューティで活性/非活性させる。通常、一対のチョッパ回路の同士の構成が同一に設計されるので、理想的にはスイッチング信号Gsとスイッチング信号Gmとは同じ周期で繰り返し活性/非活性し、かつこの周期の半分の長さで相互にずれている。

【0014】

上述のような誘導結合を実現するため、チョッパ回路の各々において誘導結合用のコアが必要となる。即ちチョッパ回路の数だけコアが必要となり、インターリーブ型力率改善回路の寸法が大きくなるという問題点がある。

【0015】

コアの個数を低減すべく、リアクタとセンサコイルとの誘導結合を実現するためのコアを、チョッパ回路の全てにおいて共通にすることも考えられる。しかし単純にコアを共通にすれば、いずれのセンサコイルも同じ磁束の変化に基づいて電流を検出することになる。

【0016】

非特許文献2では、並列接続されたチョッパ回路のリアクタ同士が誘導結合する場合について示されているが、センサコイルとの誘導結合についての工夫は示されていない。

【0017】

以上のことから、本願発明は、リアクタとセンサコイルとの誘導結合を実現するためのコアをチョッパ回路の全てにおいて共通にして、インターリーブ型力率改善回路を小型化しつつ、各々のセンサコイルが自身に対応するリアクタに流れる電流が零となる時点を適切に検出する技術を提供することを目的とする。

【課題を解決するための手段】

【0018】

この発明にかかるインターリーブ型力率改善回路用インダクタの第1の態様は、第1端子(101)と、前記第1端子に接続された第1端と、第2端とを有する第1リアクタ(Lm)と、前記第1端子に接続された第1端と、第2端とを有する第2リアクタ(Ls)と、第2端子(106)と、前記第2端子に接続された第1端と、第2端とを有する第1センサコイル(Tm)と、前記第2端子に接続された第1端と、第2端とを有する第2センサコイル(Ts)と、前記第1リアクタ及び前記第1センサコイル同士を第1結合係数で誘導結合し、前記第2リアクタ及び前記第2センサコイル同士を第2結合係数で誘導結合し、前記第1リアクタと前記第2リアクタとを前記第1端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合し、前記第1センサコイルと前記第2センサコイルとを前記第2端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合するコア(10E,10E1,10E2,10I,10Ia,10Ib,10O)とを備える。

【0019】

この発明にかかるインターリーブ型力率改善回路用インダクタの第2の態様はその第1の態様であって、前記コアにおいて、前記第1リアクタが発生させる磁束(φm)のうち前記第2センサコイルに鎖交しない磁束(φmm)と、前記第2リアクタが発生させる磁束(φs)のうち前記第1センサコイルに鎖交しない磁束(φss)とが流れる磁路が存在する。

【0020】

この発明にかかるインターリーブ型力率改善回路用インダクタの第3の態様はその第2の態様であって、前記コアは、中央レグと二つの外側レグとを有するE形コア(10E)と、I形コア(10I)とを備える。前記外側レグの一方には前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回される。前記外側レグの他方には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回される。前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向である。前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向である。前記中央レグには前記第1リアクタ、前記第2リアクタ、前記第1センサコイル及び前記第2センサコイルのいずれもが巻回されない。前記I形コアはE形コアの一対の外側レグと中央レグとを磁気的に接続するヨークとして機能する。

【0021】

この発明にかかるインターリーブ型力率改善回路用インダクタの第4の態様はその第2の態様であって、前記コアは、中央レグと二つの外側レグとを有する第1のE形コア(10E1)と、中央レグと二つの外側レグとを有する第2のE形コア(10E2)とを備える。前記第1のE形コアの前記外側レグの一方には第1のリアクタ(Lm)が巻回される。前記第1のE形コアの前記外側レグの他方には前記第2のリアクタ(Ls)が巻回される。前記第2のE形コアの前記外側レグの一方には前記第1のセンサコイル(Tm)が巻回される。前記第2のE形コアの前記外側レグの他方には第2のセンサコイル(Ts)が巻回される。前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1のE形コア側から見て同方向である。前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第2のE形コア側から見て同方向である。前記第1のE形コアの前記中央レグと前記第2のE形コアの前記中央レグのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されない。前記第1のE形コアの前記外側レグの前記一方と、前記第2のE形コアの前記外側レグの前記一方とが隣接する。前記第1のE形コアの前記外側レグの前記他方と、前記第2のE形コアの前記外側レグの前記他方とが隣接する。

【0022】

この発明にかかるインターリーブ型力率改善回路用インダクタの第5の態様はその第2の態様であって、前記コアはO形コア(10O)を備え、前記O形コアの環状形状に沿った一方向について、前記第1リアクタ(Lm)及び前記第2リアクタ(Ls)のそれぞれの巻線の巻回方向は、互いに逆方向である。当該一方向について、前記第1センサコイル(Tm)及び前記第2センサコイル(Ts)のそれぞれの巻線の巻回方向は、互いに逆方向である。

【0023】

この発明にかかるインターリーブ型力率改善回路用インダクタの第6の態様はその第2の態様であって、前記コアはO形コア(10O)と、第1のI形コア(10Ia)と、第2のI形コア(10Ib)とを備える。前記第1のI形コア及び前記第2のI形コアのそれぞれの一端はギャップ(H2)によって隔てられつつ互いに対向する。前記第1のI形コア及び前記第2のI形コアのそれぞれの他端は前記O形コアの内周に隣接する。前記O形コアには、前記第1のI形コア及び前記第2のI形コアに対して一方側に、前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回される。他方側には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回される。前記第1のI形コア及び前記第2のI形コアのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されない。前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1I形コア側から見て同方向である。前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第1のI形コア10Ia側から見て同方向である。

【発明の効果】

【0024】

この発明にかかるインターリーブ型力率改善回路用インダクタの第1の態様は、共通のコアで第1リアクタ、第2リアクタ、第1センサコイル、第2センサコイルを誘導結合するので、その寸法が小さい。そして第1リアクタと第2リアクタとが同極性で結合するものの、第1のリアクタの方が、第2リアクタよりも強く第1センサコイルと結合する。よって第1センサコイルが検出する磁束(φsm+φm)が最小値を採る時点は、第1リアクタが発生する磁束(φm)が最小値を採る時点と一致する。同様に、第2センサコイルが検出する磁束(φms+φs)が最小値を採る時点は、第2リアクタが発生する磁束(φs)が最小値を採る時点と一致する。よって第1センサコイルに流れる電流(imt)及び第2センサコイルに流れる電流(ist)を検出することにより、インターリーブ型力率改善回路を臨界モードで使用することに資する。

【0025】

この発明にかかるインターリーブ型力率改善回路用インダクタの第2の態様は、第1リアクタと第2リアクタとを第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合し、第1センサコイルと第2センサコイルとを第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合することに資する。

【0026】

この発明にかかるインターリーブ型力率改善回路用インダクタの第3の態様において、E形コア(10E)の中央レグが、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち前記第1センサコイルに鎖交しない磁束(φss)とが流れる磁路として機能する。

【0027】

この発明にかかるインターリーブ型力率改善回路用インダクタの第4の態様において、第1のE形コア(10E1)及び第2のE形コア(10E2)のいずれの中央レグも、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち第1センサコイルに鎖交しない磁束(φss)とが流れる磁路として機能する。

【0028】

この発明にかかるインターリーブ型力率改善回路用インダクタの第5の態様において、O形コアにおける漏れ磁束の発生により、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち第1センサコイルに鎖交しない磁束(φss)とが流れる。

【0029】

この発明にかかるインターリーブ型力率改善回路用インダクタの第6の態様において、第1のI形コア及び第2のI形コアが、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち第1センサコイルに鎖交しない磁束(φss)とが流れる磁路として機能する。

【図面の簡単な説明】

【0030】

【図1】本発明の一実施の形態が適用されるインターリーブ型力率改善回路の構成を示す回路図である。

【図2】インターリーブ型力率改善回路の動作を示す波形図である。

【図3】本発明の一実施にかかるインダクタの構成の第1例を示す模式図である。

【図4】本発明の一実施にかかるインダクタの構成の第2例を示す模式図である。

【図5】本発明の一実施にかかるインダクタの構成の第1例の変形を示す模式図である。

【図6】本発明の一実施にかかるインダクタの構成の第3例を示す模式図である。

【図7】本発明の一実施にかかるインダクタの構成の第3例を示す模式図である。

【図8】本発明の一実施にかかるインダクタの構成の第1例の他の変形を示す模式図である。

【図9】本発明の一実施にかかるインダクタの構成の第2例の変形を示す模式図である。

【図10】本発明の一実施にかかるインダクタの構成の第3例の変形を示す模式図である。

【図11】従来のインターリーブ型力率改善回路の構成を示す回路図である。

【図12】スイッチング素子のオン/オフ動作と、インダクタ電流の波形との関係を示すタイミングチャートである。

【発明を実施するための形態】

【0031】

<インターリーブ型力率改善回路3の動作>

図1に示されるインターリーブ型力率改善回路3は、スイッチング素子Sm,Ss、ダイオードDm,Ds、インダクタ10及びコンデンサCを有している。コンデンサCには並列に負荷4が接続されている。

【0032】

整流回路2には交流電源1から交流の入力電流Iinが入力する。整流回路2は入力電流Iinを例えば全波整流してインダクタ10へと直流電流を供給する。

【0033】

インダクタ10は端子101〜106と、リアクタLm,Ls、センサコイルTm,Tsを備える。整流回路2の高電位側出力端(図中「+」で示す)は端子101に接続される。

【0034】

リアクタLmは、端子101に接続された第1端と、端子102に接続された第2端とを有する。リアクタLsは、端子101に接続された第1端と、端子103に接続された第2端を有する。

【0035】

センサコイルTmは、端子106に接続された第1端と、端子104に接続された第2端とを有する。センサコイルTsは、端子106に接続された第1端と、端子105に接続された第2端とを有する。

【0036】

端子102にはダイオードDmのアノード及びスイッチング素子Smの一端が接続され、端子103にはダイオードDsのアノード及びスイッチング素子Ssの一端が接続される。

【0037】

コンデンサCの一端にはダイオードDm,Dsのそれぞれのアノードに接続され、コンデンサCの他端はスイッチング素子Sm,Ssのそれぞれの他端及び整流回路2の低電位側出力端(図中「−」で示す)に接続される。

【0038】

インダクタ10において、黒丸はリアクタLm,Ls及びセンサコイルTm,Ts同士の誘導結合の極性を示す。リアクタLm及びセンサコイルTm同士は第1結合係数で誘導結合し、リアクタLs及びセンサコイルTs同士は第2結合係数で誘導結合する。リアクタLm,Ls同士は端子101から見て同極性で誘導結合する。センサコイルTm,Ts同士は端子106から見て同極性で誘導結合する。図1では第1結合係数、第2結合係数のいずれも負である場合が示されている(リアクタLmの黒丸とセンサコイルTmの黒丸とは隣接して示されており、リアクタLsの黒丸とセンサコイルTsの黒丸とは隣接して示されている)。

【0039】

但し、リアクタLm,Ls同士の誘導結合の強さ、及びセンサコイルTm,Ts同士の誘導結合の強さは、いずれも第1結合係数及び第2結合係数のいずれの大きさよりも小さい。

【0040】

図2は、インターリーブ型力率改善回路3の動作を示す波形図である。スイッチング信号Gm,Gsの活性/非活性はそれぞれ波形のハイ/ローと対応する。ダイオードDmに流れるダイオード電流Idmはスイッチング信号Gmが立ち上がる時点t1,t5で立ち下がり、スイッチング信号Gmが立ち下がる時点t2で立ち上がる。ダイオードDsに流れるダイオード電流Idsはスイッチング信号Gsが立ち上がる時点t3で立ち下がり、スイッチング信号Gsが立ち下がる時点t4で立ち上がる。

【0041】

ダイオード電流Idmは時点t2〜t5において減少し、特にスイッチング信号Gsが活性化する時点t3〜t4において減少率は高まる。同様に、ダイオード電流Idsは時点t1〜t3及び時点t4以降において減少し、スイッチング信号Gmが活性化する時点t1〜t2において減少率は高まる。

【0042】

このようなダイオード電流の減少率の変動は、リアクタLm,Ls同士が誘導結合することに起因する。かかる誘導結合によってインダクタ電流Im,Isも、その減少率が変動する。具体的には、インダクタ電流Imは時点t2〜t5において減少し、特にスイッチング信号Gsが活性化する時点t3〜t4において減少率は高まる。同様に、インダクタ電流Isは時点t1〜t3及び時点t4以降において減少するが、スイッチング信号Gmが活性化する時点t1〜t2において減少率は高まる。このようなインダクタ電流Im,Isの振る舞いは非特許文献2にも開示されており、公知であるので、詳細な解析は割愛する。

【0043】

リアクタLm,Lsにそれぞれインダクタ電流Im,Isが流れることにより、それぞれ磁束φm,φsが発生する。今、簡単のため、第1結合係数が非常に大きくてリアクタLmとセンサコイルTmとが密に結合し、センサコイルTmには磁束φmが全て鎖交する場合を考察する。

【0044】

リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さいので、磁束φsの一部φsm(<φs)がセンサコイルTmに鎖交する。以上のことから、センサコイルTmに鎖交する磁束はφm+φsmとなる。

【0045】

通常、インターリーブ型力率改善回路3ではリアクタLm,Lsの特性が等しく設定され、かつ電圧Vdcを一定に保つ制御が行われるので、インダクタ電流Im,Isのそれぞれが呈する波形は周期の半分の長さで相互にずれている。

【0046】

よってインダクタ電流Im,Isの和たる入力電流Iinはインダクタ電流Im,Isの周期の半分の周期で繰り返される波形を呈する。当該波形は時点t1,t3,t5で最小を採る。

【0047】

そしてリアクタLm,Lsの特性が等しく設定されるので、磁束φm,φsはインダクタ電流Im,Isと同様、それぞれが呈する波形は周期の半分の長さで相互にずれている。

【0048】

よって磁束φm+φsも入力電流Iinと同様に時点t1,t3,t5で最小値を採る波形を呈する。よって磁束φm+φsが最小値を採るタイミングは、スイッチング信号Gm,Gsの立ち上がりの基準として採用することはできない。スイッチング素子Sm,Ssのいずれをオンするのかが区別できないからである。

【0049】

これに対して、φm+φsmは図示されるように、時点t3において採る値よりも、時点t1,t5において採る値の方が小さい。これは以下の理由による。時点t3においてインダクタ電流Isが零となることを反映して磁束φsが零となり、磁束φm+φsmは磁束φmと同じ値を採る。他方、時点t1,t5においてはインダクタ電流Imが零となることを反映して磁束φmが零となり、磁束φm+φsmは磁束φsmと同じ値を採る。

【0050】

上述のように磁束φm,φsは相互に周期の半分でずれているので、時点t1,t5において磁束φsが採る値は、時点t3において磁束φmが採る値と等しい。よって時点t1,t5において磁束φsm(<φs)が採る値は時点t3において磁束φmが採る値よりも小さい。従って、磁束φm+φsmは図示されるように、時点t1,t5において最小値を採る。

【0051】

このようにして磁束φm+φsmが最小値をとるタイミングで、スイッチング信号Gmを立ち上がらせ、スイッチング素子Smをオフからオンへと制御することができる。かかる制御によって、リアクタLm、ダイオードDm、スイッチング素子Smを有する昇圧チョッパ回路に、臨界モードでの動作をさせることができる。

【0052】

同様に、第2結合係数が非常に大きくてリアクタLsとセンサコイルTsとが密に結合し、センサコイルTsには磁束φsが全て鎖交する場合を考察する。

【0053】

リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さいので、磁束φmの一部φms(<φm)がセンサコイルTsに鎖交する。そしてセンサコイルTsに鎖交する磁束はφm+φmsとなる。そして磁束φs+φmsが最小値をとるタイミングで、スイッチング信号Gsを立ち上がらせ、スイッチング素子Ssをオフからオンへと制御することができる。かかる制御によって、リアクタLs、ダイオードDs、スイッチング素子Ssを有する昇圧チョッパ回路に、臨界モードでの動作をさせることができる。

【0054】

以上のように、センサコイルTm,Tsに鎖交する磁束がそれぞれ最小値を採るタイミングを検出することにより、インターリーブ型力率改善回路3にインターリーブ動作をさせることができる。

【0055】

より具体的には、端子106(ここでは接地されている)から端子104,105にそれぞれ流れる検出電流Imt,Istを検出し、これらが最小値を採るタイミングを検出すればよい。検出電流Imt,Istは、それぞれ磁束φm+φsm及び磁束φs+φmsに比例した値を採るからである。

【0056】

よって制御部6は検出電流Imt,Istを検出し、公知技術によってそれぞれが最小値を採るタイミングを検出し、当該タイミングでそれぞれスイッチング信号Gm,Gsを立ち上がらせればよい。スイッチング信号Gm,Gsを立ち下げる技術は図11を用いて説明したように公知技術であるので、ここでは詳細な説明を割愛する。

【0057】

以上のようにインダクタ10によれば、リアクタLmとセンサコイルTmとの誘導結合、リアクタLsとセンサコイルTsとの誘導結合を実現するためのコアをチョッパ回路の全てにおいて共通にできる。よってインターリーブ型力率改善回路30を小型化しつつ、各々のセンサコイルTm,Tsが自身に対応するリアクタLm、Lsに流れる電流が零となる時点を適切に検出することができる。

【0058】

<インダクタ10の具体的構造>

以下、上述のような誘導結合を実現するためのインダクタ10の具体的構成について説明する。

【0059】

図3はインダクタ10の構成の第1例を示す模式図である。インダクタ10はE形コア10EとI形コア10Iとを有している。

【0060】

E形コア10Eの外側レグの一方にはリアクタLmとセンサコイルTmが巻回され、他方にはリアクタLsとセンサコイルTsが巻回され、中央レグにはリアクタLm,Ls、センサコイルTm,Tsのいずれも巻回されてはいない。

【0061】

I形コア10IはE形コア10Eの一対の外側レグと中央レグとを磁気的に接続するヨークとして機能する。

【0062】

リアクタLm,Ls同士が端子101から見て同極性で誘導結合すべく、リアクタLm,Lsのそれぞれの巻線の巻回方向は、端子101からみて同方向、ここではI形コア10Iとは反対側から見て時計回り方向である。センサコイルTm,Ts同士が端子106から見て同極性で誘導結合すべく、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、端子106からみて同方向、ここではI形コア10Iとは反対側から見て反時計回り方向である。

【0063】

このようにリアクタLmとセンサコイルTmのそれぞれの巻線は同じレグに巻回されるものの、それらの巻回方向は相互に反対向きであるので、端子101からインダクタ電流Imが流れるときには端子106から検出電流Imtが流れる。また、リアクタLsとセンサコイルTsのそれぞれの巻線は同じレグに巻回されるものの、それらの巻回方向は相互に反対向きであるので、端子101からインダクタ電流Isが流れるときには端子106から検出電流Istが流れる。

【0064】

リアクタLmとセンサコイルTmのそれぞれの巻線の巻回方向は相互に同方向であったり、リアクタLsとセンサコイルTsのそれぞれの巻線の巻回方向は相互に同方向であったりしてもよい。この場合、制御部6は検出電流Imt,Istの絶対値が最小値を採るタイミングを検出し、当該タイミングでそれぞれスイッチング信号Gm,Gsを立ち上がらせればよい。

【0065】

磁束φm,φsは、それぞれ白抜き矢印、及び白抜き破線矢印で示される。E形コア10Eの中央レグには磁束φmのうち、リアクタLs、センサコイルTsに鎖交しない磁束φmm(=φm−φms)が流れる。更に中央レグには磁束φsのうち、リアクタLm、センサコイルTmに鎖交しない磁束φss(=φs−φsm)も流れる。

【0066】

このように磁束φmm,φssが流れる中央レグが存在することにより、リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さくすることができる。

【0067】

第1結合係数、第2結合係数を大きくするためには、例えばリアクタLm、センサコイルTmのそれぞれの巻線を重ねて巻回したり、リアクタLs、センサコイルTsのそれぞれの巻線を重ねて巻回したりすればよい。これは以下の他例でも同様である。

【0068】

図4はインダクタ10の構成の第2例を示す模式図である。インダクタ10はE形コア10E1,10E2を有している。

【0069】

E形コア10E1の外側レグの一方にはリアクタLmが巻回され、他方にはリアクタLsが巻回される。E形コア10E2の外側レグの一方にはセンサコイルTmが巻回され、他方にはセンサコイルTsが巻回される。E形コア10E1の外側レグの一方とE形コア10E2の外側レグの一方とが隣接し、E形コア10E1の外側レグの他方とE形コア10E2の外側レグの他方とが隣接し、E形コア10E1の中央レグとE形コア10E2の中央レグとが隣接する。E形コア10E1の中央レグとE形コア10E2の中央レグのいずれにも、リアクタLm,Ls、センサコイルTm,Tsのいずれもが巻回されてはいない。

【0070】

リアクタLm,Lsのそれぞれの巻線の巻回方向は、端子101からみて同方向、ここではE形コア10E1側から見て時計回り方向である。センサコイルTm,Ts同士が端子106から見て同極性で誘導結合すべく、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、端子106からみて同方向、ここではE形コア10E2側から見て時計回り方向である。

【0071】

このように組み合わされたE形コア10E1,10E2のいずれの中央レグも、磁束φmm,φssが流れる磁路となる。よって第2例も図3で示された第1例と同様に機能することは明白であり、第1例と同様に、リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さくすることができる。

【0072】

図5は図3で示された第1例の変形の一つを示す模式図であり、E形コア10Eの中央レグとIコア10Iとの間にギャップH1が存在する場合の構成を示す。このようにギャップH1が存在しても、磁束φmm,φssが中央レグに流れる限り、φms<φm,φsm<φsが成立し、インダクタ10としての機能が果たされる。

【0073】

図6はインダクタ10の構成の第3例を示す模式図である。インダクタ10はO形コア10OとI形コア10Ia,10Ibとを有している。I形コア10Ia,10Ibのそれぞれの一端はギャップH2によって隔てられつつ互いに対向する。I形コア10Ia,10Ibのそれぞれの他端はO形コア10Oの内周に隣接する。

【0074】

O形コア10OにはI形コア10Ia,10Ibに対して一方側に、リアクタLmとセンサコイルTmが巻回され、他方側にはリアクタLsとセンサコイルTsが巻回される。I形コア10Ia,10IbにはリアクタLm,Ls、センサコイルTm,Tsのいずれも巻回されてはいない。

【0075】

リアクタLm,Ls同士が端子101から見て同極性で誘導結合すべく、リアクタLm,Lsのそれぞれの巻線の巻回方向は、端子101からみて同方向、ここではI形コア10Ia側から見て時計回り方向である。センサコイルTm,Ts同士が端子106から見て同極性で誘導結合すべく、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、端子106からみて同方向、ここではI形コア10Ia側から見て反時計回り方向である。

【0076】

また、O形コア10Oに関してみれば、O形コア10Oの環状形状に沿った一方向について、リアクタLm,Lsのそれぞれの巻線の巻回方向は、互いに逆方向となる。また当該一方向について、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、互いに逆方向となる。

【0077】

図7もインダクタ10の構成の第3例を示す模式図である。図6においてO形コア10O及びI形コア10Ia,10Ibで構成された形状を、二つのE型コアE1,E2で形成している。

【0078】

図7に示された構成は、図4に示された第2例のE形コア10E1の中央レグとE形コア10E2の中央レグとが隣接せずにギャップH2によって隔てられつつ互いに対向する点で相違する。その他、リアクタLm,Ls、センサコイルTm,Tsが巻回される位置、巻回方向については第2例と同様であるので、詳細な説明は省略する。

【0079】

このように組み合わされたO形コア10O及びI形コア10Ia,10Ib、あるいはE形コア10E1,10E2も、図5で示された第1例の変形と同様に機能することは明白であり、第1例と同様に、リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さくすることができる。

【0080】

図8は図3で示された第1例の他の変形を示す模式図であり、E形コア10Eの中央レグとIコア10Iとの間にギャップH1が、E形コア10Eの一対の外側レグとIコア10Iとの間にギャップH3,H4が、それぞれ存在する場合の構成を示す。このようにギャップH1,H3,H4が存在しても、磁束φmm,φssが中央レグに流れる限り、φms<φm,φsm<φsが成立し、インダクタ10としての機能が果たされる。

【0081】

図9は図4で示された第2例の変形の一つを示す模式図であり、E形コア10E1,10E2の間には、対応するレグ同士の間にギャップH2,H5,H6が、それぞれ存在する場合の構成を示す。このようにリアクタLmが設けられるコア10E1と、センサコイルTmが設けられるコア10E2との間にギャップH5が存在する場合には、磁束φmの全てがセンサコイルTmに鎖交するとは限らない。リアクタLsが設けられるコア10E1と、センサコイルTsが設けられるコア10E2との間にギャップH5が存在する場合には、磁束φmの全てがセンサコイルTmに鎖交するとは限らない。

【0082】

このような場合でも磁束φmm,φssが流れれば、センサコイルTmに鎖交する磁束は磁束φm+φsmに比例し、センサコイルTsに鎖交する磁束は磁束φs+φmsに比例するので、インダクタ10としての機能が果たされる。

【0083】

図10は第3例の変形を示す模式図である。インダクタ10はO形コア10Oを有するものの、I形コア10Ia,10Ibを有していない。O形コア10Oの環状形状に沿った一方向について、リアクタLm,Lsのそれぞれの巻線の巻回方向は、互いに逆方向となる。また当該一方向について、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、互いに逆方向となる。

【0084】

このような場合でも、例えば磁気飽和によっていわゆる漏れ磁束として磁束φmm,φssが流れれば、φms<φm,φsm<φsが成立し、インダクタ10としての機能が果たされる。

【0085】

以上のように、インダクタ10は、ギャップが設けられる場合はあるものの、共通のコアでリアクタLm、Ls、センサコイルTm,Tsを誘導結合するので、その寸法が小さい。そしてセンサコイルTmが検出する磁束(φsm+φm)が最小値を採る時点は、リアクタLmが発生する磁束φmが最小値を採る時点と一致する。同様に、センサコイルTsが検出する磁束(φs+φms)が最小値を採る時点は、リアクタLsが発生する磁束φsが最小値を採る時点と一致する。よってインダクタ10を採用することで、センサコイルTmに流れる検出電流Imt及びセンサコイルTsに流れる検出電流istを検出することにより、インターリーブ型力率改善回路30を臨界モードで使用する制御ができる。

【0086】

また、リアクタLmが発生させる磁束φmのうちセンサコイルTsに鎖交しない磁束φmmと、リアクタLsが発生させる磁束φsのうちセンサコイルTmに鎖交しない磁束φssとが流れる磁路が存在することは、リアクタLm,Ls同士を第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合し、センサコイルTm,Ts同士を第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合することに資する。

【符号の説明】

【0087】

101〜106 端子

Lm,Ls リアクタ

Tm,Ts センスコイル

10E,10E1,10E2 E形コア

10I,10Ia,10Ib I形コア

10O O形コア

【技術分野】

【0001】

本発明はインダクタに関し、特にインターリーブで動作する一対の力率改善回路に採用されるインダクタに関する。

【背景技術】

【0002】

非特許文献1には、臨界モードかつインターリーブで動作する一対の力率改善回路(以下、単に「インターリーブ型力率改善回路」と称す)が開示されている。インターリーブ型力率改善回路では、昇圧型のチョッパ回路の一対が並列接続されており、リアクタ、ダイオード、スイッチング素子を有している。

【0003】

非特許文献2には、インターリーブ型力率改善回路において、一対のリアクタが誘導結合する場合について説明されている。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】喜多村 守、「1.5kWの低ノイズ高調波対策電源を作れる臨界モード/インターリーブPFC IC R2A20112」、トランジスタ技術2008年5月号、CQ出版株式会社、2008年8月、第176頁乃至第184頁

【非特許文献2】Wei Wen and Yim-Shu Lee, “A Two-channel Interleaved Boost Converter with Reduced Core Loss and Copper Loss”,2004-35th Annual IEEE Power Electronics Specialists Conference,2004.

【発明の概要】

【発明が解決しようとする課題】

【0005】

非特許文献1で示されるように、インターリーブ型力率改善回路が、臨界モードかつインターリーブで動作するには、昇圧型のチョッパ回路の各々においてリアクタに流れる電流が零となる時点を検出する必要がある。この目的のため、チョッパ回路の各々においてリアクタに流れる電流を検出するため、当該リアクタと誘導結合した電流検出用のコイル(以下、単に「センサコイル」と称する)が備えられている。

【0006】

図11は従来のインターリーブ型力率改善回路30の構成を示す回路図である。インターリーブ型力率改善回路30は、リアクタLm,Ls、センサコイルTm,Ts、ダイオードDm,Ds、スイッチング素子Sm,Ss、コンデンサCを備えている。コンデンサCには負荷4が並列に接続されている。

【0007】

インターリーブ型力率改善回路30には整流回路2から直流電流が与えられ、これをリアクタLm,Lsへと分流し、負荷4へと直流電圧を供給する。整流回路2は交流電源1から交流の入力電流Iinを入力し、上述の直流電流を出力する。

【0008】

リアクタLm、ダイオードDm、スイッチング素子Smがマスター側のチョッパ回路を構成し、リアクタLs、ダイオードDs、スイッチング素子Ssがスレーブ側のチョッパ回路を構成する。

【0009】

スイッチング素子Sm,Ssはスイッチング信号Gm,Gsに従ってオン/オフする。リアクタLmに流れるインダクタ電流Imは、スイッチング素子Smのオン/オフに対応して、それぞれスイッチング素子Sm、ダイオードDm及びコンデンサCに流れる。リアクタLsに流れるインダクタ電流Isは、スイッチング素子Ssのオン/オフに対応して、それぞれスイッチング素子Ss、ダイオードDs及びコンデンサCに流れる。

【0010】

電流Im,Isが発生させた磁束の変化はセンサコイルTm,Tsに誘導電圧を生起し、センサコイルTm,Tsにはそれぞれ検知電流Ims,Issが流れる。

【0011】

制御部6は検知電流Ims,Issを検知し、それぞれの値が零となるタイミングを検出する。検知電流Imsの値が零となるタイミングはインダクタ電流Imの値が零となるタイミングと一致し、検知電流Issの値が零となるタイミングはインダクタ電流Isの値が零となるタイミングと一致する。制御部6はコンデンサCの両端電圧Vdc及びその指令値Vdc*をも入力する。

【0012】

図12はスイッチング素子Sm,Ssのオン/オフ動作と、インダクタ電流Im,Isの波形との関係を示すタイミングチャートである。臨界モードかつインターリーブでの動作を実現するため、制御部6は検知電流Imsの値が零となるタイミングでスイッチング信号Gmを活性化させてスイッチング素子Smをオンさせ、両端電圧Vdcが指令値Vdc*に至ればスイッチング信号Gmを非活性化させてスイッチング素子Smをオフさせる。

【0013】

制御部6は検知電流Issの値が零となるタイミングでスイッチング信号Gsを活性化させてスイッチング素子Ssをオンさせ、スイッチング信号Gsをスイッチング信号Gmと同じデューティで活性/非活性させる。通常、一対のチョッパ回路の同士の構成が同一に設計されるので、理想的にはスイッチング信号Gsとスイッチング信号Gmとは同じ周期で繰り返し活性/非活性し、かつこの周期の半分の長さで相互にずれている。

【0014】

上述のような誘導結合を実現するため、チョッパ回路の各々において誘導結合用のコアが必要となる。即ちチョッパ回路の数だけコアが必要となり、インターリーブ型力率改善回路の寸法が大きくなるという問題点がある。

【0015】

コアの個数を低減すべく、リアクタとセンサコイルとの誘導結合を実現するためのコアを、チョッパ回路の全てにおいて共通にすることも考えられる。しかし単純にコアを共通にすれば、いずれのセンサコイルも同じ磁束の変化に基づいて電流を検出することになる。

【0016】

非特許文献2では、並列接続されたチョッパ回路のリアクタ同士が誘導結合する場合について示されているが、センサコイルとの誘導結合についての工夫は示されていない。

【0017】

以上のことから、本願発明は、リアクタとセンサコイルとの誘導結合を実現するためのコアをチョッパ回路の全てにおいて共通にして、インターリーブ型力率改善回路を小型化しつつ、各々のセンサコイルが自身に対応するリアクタに流れる電流が零となる時点を適切に検出する技術を提供することを目的とする。

【課題を解決するための手段】

【0018】

この発明にかかるインターリーブ型力率改善回路用インダクタの第1の態様は、第1端子(101)と、前記第1端子に接続された第1端と、第2端とを有する第1リアクタ(Lm)と、前記第1端子に接続された第1端と、第2端とを有する第2リアクタ(Ls)と、第2端子(106)と、前記第2端子に接続された第1端と、第2端とを有する第1センサコイル(Tm)と、前記第2端子に接続された第1端と、第2端とを有する第2センサコイル(Ts)と、前記第1リアクタ及び前記第1センサコイル同士を第1結合係数で誘導結合し、前記第2リアクタ及び前記第2センサコイル同士を第2結合係数で誘導結合し、前記第1リアクタと前記第2リアクタとを前記第1端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合し、前記第1センサコイルと前記第2センサコイルとを前記第2端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合するコア(10E,10E1,10E2,10I,10Ia,10Ib,10O)とを備える。

【0019】

この発明にかかるインターリーブ型力率改善回路用インダクタの第2の態様はその第1の態様であって、前記コアにおいて、前記第1リアクタが発生させる磁束(φm)のうち前記第2センサコイルに鎖交しない磁束(φmm)と、前記第2リアクタが発生させる磁束(φs)のうち前記第1センサコイルに鎖交しない磁束(φss)とが流れる磁路が存在する。

【0020】

この発明にかかるインターリーブ型力率改善回路用インダクタの第3の態様はその第2の態様であって、前記コアは、中央レグと二つの外側レグとを有するE形コア(10E)と、I形コア(10I)とを備える。前記外側レグの一方には前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回される。前記外側レグの他方には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回される。前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向である。前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向である。前記中央レグには前記第1リアクタ、前記第2リアクタ、前記第1センサコイル及び前記第2センサコイルのいずれもが巻回されない。前記I形コアはE形コアの一対の外側レグと中央レグとを磁気的に接続するヨークとして機能する。

【0021】

この発明にかかるインターリーブ型力率改善回路用インダクタの第4の態様はその第2の態様であって、前記コアは、中央レグと二つの外側レグとを有する第1のE形コア(10E1)と、中央レグと二つの外側レグとを有する第2のE形コア(10E2)とを備える。前記第1のE形コアの前記外側レグの一方には第1のリアクタ(Lm)が巻回される。前記第1のE形コアの前記外側レグの他方には前記第2のリアクタ(Ls)が巻回される。前記第2のE形コアの前記外側レグの一方には前記第1のセンサコイル(Tm)が巻回される。前記第2のE形コアの前記外側レグの他方には第2のセンサコイル(Ts)が巻回される。前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1のE形コア側から見て同方向である。前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第2のE形コア側から見て同方向である。前記第1のE形コアの前記中央レグと前記第2のE形コアの前記中央レグのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されない。前記第1のE形コアの前記外側レグの前記一方と、前記第2のE形コアの前記外側レグの前記一方とが隣接する。前記第1のE形コアの前記外側レグの前記他方と、前記第2のE形コアの前記外側レグの前記他方とが隣接する。

【0022】

この発明にかかるインターリーブ型力率改善回路用インダクタの第5の態様はその第2の態様であって、前記コアはO形コア(10O)を備え、前記O形コアの環状形状に沿った一方向について、前記第1リアクタ(Lm)及び前記第2リアクタ(Ls)のそれぞれの巻線の巻回方向は、互いに逆方向である。当該一方向について、前記第1センサコイル(Tm)及び前記第2センサコイル(Ts)のそれぞれの巻線の巻回方向は、互いに逆方向である。

【0023】

この発明にかかるインターリーブ型力率改善回路用インダクタの第6の態様はその第2の態様であって、前記コアはO形コア(10O)と、第1のI形コア(10Ia)と、第2のI形コア(10Ib)とを備える。前記第1のI形コア及び前記第2のI形コアのそれぞれの一端はギャップ(H2)によって隔てられつつ互いに対向する。前記第1のI形コア及び前記第2のI形コアのそれぞれの他端は前記O形コアの内周に隣接する。前記O形コアには、前記第1のI形コア及び前記第2のI形コアに対して一方側に、前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回される。他方側には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回される。前記第1のI形コア及び前記第2のI形コアのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されない。前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1I形コア側から見て同方向である。前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第1のI形コア10Ia側から見て同方向である。

【発明の効果】

【0024】

この発明にかかるインターリーブ型力率改善回路用インダクタの第1の態様は、共通のコアで第1リアクタ、第2リアクタ、第1センサコイル、第2センサコイルを誘導結合するので、その寸法が小さい。そして第1リアクタと第2リアクタとが同極性で結合するものの、第1のリアクタの方が、第2リアクタよりも強く第1センサコイルと結合する。よって第1センサコイルが検出する磁束(φsm+φm)が最小値を採る時点は、第1リアクタが発生する磁束(φm)が最小値を採る時点と一致する。同様に、第2センサコイルが検出する磁束(φms+φs)が最小値を採る時点は、第2リアクタが発生する磁束(φs)が最小値を採る時点と一致する。よって第1センサコイルに流れる電流(imt)及び第2センサコイルに流れる電流(ist)を検出することにより、インターリーブ型力率改善回路を臨界モードで使用することに資する。

【0025】

この発明にかかるインターリーブ型力率改善回路用インダクタの第2の態様は、第1リアクタと第2リアクタとを第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合し、第1センサコイルと第2センサコイルとを第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合することに資する。

【0026】

この発明にかかるインターリーブ型力率改善回路用インダクタの第3の態様において、E形コア(10E)の中央レグが、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち前記第1センサコイルに鎖交しない磁束(φss)とが流れる磁路として機能する。

【0027】

この発明にかかるインターリーブ型力率改善回路用インダクタの第4の態様において、第1のE形コア(10E1)及び第2のE形コア(10E2)のいずれの中央レグも、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち第1センサコイルに鎖交しない磁束(φss)とが流れる磁路として機能する。

【0028】

この発明にかかるインターリーブ型力率改善回路用インダクタの第5の態様において、O形コアにおける漏れ磁束の発生により、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち第1センサコイルに鎖交しない磁束(φss)とが流れる。

【0029】

この発明にかかるインターリーブ型力率改善回路用インダクタの第6の態様において、第1のI形コア及び第2のI形コアが、第1リアクタが発生させる磁束(φm)のうち第2センサコイルに鎖交しない磁束(φmm)と、第2リアクタが発生させる磁束(φs)のうち第1センサコイルに鎖交しない磁束(φss)とが流れる磁路として機能する。

【図面の簡単な説明】

【0030】

【図1】本発明の一実施の形態が適用されるインターリーブ型力率改善回路の構成を示す回路図である。

【図2】インターリーブ型力率改善回路の動作を示す波形図である。

【図3】本発明の一実施にかかるインダクタの構成の第1例を示す模式図である。

【図4】本発明の一実施にかかるインダクタの構成の第2例を示す模式図である。

【図5】本発明の一実施にかかるインダクタの構成の第1例の変形を示す模式図である。

【図6】本発明の一実施にかかるインダクタの構成の第3例を示す模式図である。

【図7】本発明の一実施にかかるインダクタの構成の第3例を示す模式図である。

【図8】本発明の一実施にかかるインダクタの構成の第1例の他の変形を示す模式図である。

【図9】本発明の一実施にかかるインダクタの構成の第2例の変形を示す模式図である。

【図10】本発明の一実施にかかるインダクタの構成の第3例の変形を示す模式図である。

【図11】従来のインターリーブ型力率改善回路の構成を示す回路図である。

【図12】スイッチング素子のオン/オフ動作と、インダクタ電流の波形との関係を示すタイミングチャートである。

【発明を実施するための形態】

【0031】

<インターリーブ型力率改善回路3の動作>

図1に示されるインターリーブ型力率改善回路3は、スイッチング素子Sm,Ss、ダイオードDm,Ds、インダクタ10及びコンデンサCを有している。コンデンサCには並列に負荷4が接続されている。

【0032】

整流回路2には交流電源1から交流の入力電流Iinが入力する。整流回路2は入力電流Iinを例えば全波整流してインダクタ10へと直流電流を供給する。

【0033】

インダクタ10は端子101〜106と、リアクタLm,Ls、センサコイルTm,Tsを備える。整流回路2の高電位側出力端(図中「+」で示す)は端子101に接続される。

【0034】

リアクタLmは、端子101に接続された第1端と、端子102に接続された第2端とを有する。リアクタLsは、端子101に接続された第1端と、端子103に接続された第2端を有する。

【0035】

センサコイルTmは、端子106に接続された第1端と、端子104に接続された第2端とを有する。センサコイルTsは、端子106に接続された第1端と、端子105に接続された第2端とを有する。

【0036】

端子102にはダイオードDmのアノード及びスイッチング素子Smの一端が接続され、端子103にはダイオードDsのアノード及びスイッチング素子Ssの一端が接続される。

【0037】

コンデンサCの一端にはダイオードDm,Dsのそれぞれのアノードに接続され、コンデンサCの他端はスイッチング素子Sm,Ssのそれぞれの他端及び整流回路2の低電位側出力端(図中「−」で示す)に接続される。

【0038】

インダクタ10において、黒丸はリアクタLm,Ls及びセンサコイルTm,Ts同士の誘導結合の極性を示す。リアクタLm及びセンサコイルTm同士は第1結合係数で誘導結合し、リアクタLs及びセンサコイルTs同士は第2結合係数で誘導結合する。リアクタLm,Ls同士は端子101から見て同極性で誘導結合する。センサコイルTm,Ts同士は端子106から見て同極性で誘導結合する。図1では第1結合係数、第2結合係数のいずれも負である場合が示されている(リアクタLmの黒丸とセンサコイルTmの黒丸とは隣接して示されており、リアクタLsの黒丸とセンサコイルTsの黒丸とは隣接して示されている)。

【0039】

但し、リアクタLm,Ls同士の誘導結合の強さ、及びセンサコイルTm,Ts同士の誘導結合の強さは、いずれも第1結合係数及び第2結合係数のいずれの大きさよりも小さい。

【0040】

図2は、インターリーブ型力率改善回路3の動作を示す波形図である。スイッチング信号Gm,Gsの活性/非活性はそれぞれ波形のハイ/ローと対応する。ダイオードDmに流れるダイオード電流Idmはスイッチング信号Gmが立ち上がる時点t1,t5で立ち下がり、スイッチング信号Gmが立ち下がる時点t2で立ち上がる。ダイオードDsに流れるダイオード電流Idsはスイッチング信号Gsが立ち上がる時点t3で立ち下がり、スイッチング信号Gsが立ち下がる時点t4で立ち上がる。

【0041】

ダイオード電流Idmは時点t2〜t5において減少し、特にスイッチング信号Gsが活性化する時点t3〜t4において減少率は高まる。同様に、ダイオード電流Idsは時点t1〜t3及び時点t4以降において減少し、スイッチング信号Gmが活性化する時点t1〜t2において減少率は高まる。

【0042】

このようなダイオード電流の減少率の変動は、リアクタLm,Ls同士が誘導結合することに起因する。かかる誘導結合によってインダクタ電流Im,Isも、その減少率が変動する。具体的には、インダクタ電流Imは時点t2〜t5において減少し、特にスイッチング信号Gsが活性化する時点t3〜t4において減少率は高まる。同様に、インダクタ電流Isは時点t1〜t3及び時点t4以降において減少するが、スイッチング信号Gmが活性化する時点t1〜t2において減少率は高まる。このようなインダクタ電流Im,Isの振る舞いは非特許文献2にも開示されており、公知であるので、詳細な解析は割愛する。

【0043】

リアクタLm,Lsにそれぞれインダクタ電流Im,Isが流れることにより、それぞれ磁束φm,φsが発生する。今、簡単のため、第1結合係数が非常に大きくてリアクタLmとセンサコイルTmとが密に結合し、センサコイルTmには磁束φmが全て鎖交する場合を考察する。

【0044】

リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さいので、磁束φsの一部φsm(<φs)がセンサコイルTmに鎖交する。以上のことから、センサコイルTmに鎖交する磁束はφm+φsmとなる。

【0045】

通常、インターリーブ型力率改善回路3ではリアクタLm,Lsの特性が等しく設定され、かつ電圧Vdcを一定に保つ制御が行われるので、インダクタ電流Im,Isのそれぞれが呈する波形は周期の半分の長さで相互にずれている。

【0046】

よってインダクタ電流Im,Isの和たる入力電流Iinはインダクタ電流Im,Isの周期の半分の周期で繰り返される波形を呈する。当該波形は時点t1,t3,t5で最小を採る。

【0047】

そしてリアクタLm,Lsの特性が等しく設定されるので、磁束φm,φsはインダクタ電流Im,Isと同様、それぞれが呈する波形は周期の半分の長さで相互にずれている。

【0048】

よって磁束φm+φsも入力電流Iinと同様に時点t1,t3,t5で最小値を採る波形を呈する。よって磁束φm+φsが最小値を採るタイミングは、スイッチング信号Gm,Gsの立ち上がりの基準として採用することはできない。スイッチング素子Sm,Ssのいずれをオンするのかが区別できないからである。

【0049】

これに対して、φm+φsmは図示されるように、時点t3において採る値よりも、時点t1,t5において採る値の方が小さい。これは以下の理由による。時点t3においてインダクタ電流Isが零となることを反映して磁束φsが零となり、磁束φm+φsmは磁束φmと同じ値を採る。他方、時点t1,t5においてはインダクタ電流Imが零となることを反映して磁束φmが零となり、磁束φm+φsmは磁束φsmと同じ値を採る。

【0050】

上述のように磁束φm,φsは相互に周期の半分でずれているので、時点t1,t5において磁束φsが採る値は、時点t3において磁束φmが採る値と等しい。よって時点t1,t5において磁束φsm(<φs)が採る値は時点t3において磁束φmが採る値よりも小さい。従って、磁束φm+φsmは図示されるように、時点t1,t5において最小値を採る。

【0051】

このようにして磁束φm+φsmが最小値をとるタイミングで、スイッチング信号Gmを立ち上がらせ、スイッチング素子Smをオフからオンへと制御することができる。かかる制御によって、リアクタLm、ダイオードDm、スイッチング素子Smを有する昇圧チョッパ回路に、臨界モードでの動作をさせることができる。

【0052】

同様に、第2結合係数が非常に大きくてリアクタLsとセンサコイルTsとが密に結合し、センサコイルTsには磁束φsが全て鎖交する場合を考察する。

【0053】

リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さいので、磁束φmの一部φms(<φm)がセンサコイルTsに鎖交する。そしてセンサコイルTsに鎖交する磁束はφm+φmsとなる。そして磁束φs+φmsが最小値をとるタイミングで、スイッチング信号Gsを立ち上がらせ、スイッチング素子Ssをオフからオンへと制御することができる。かかる制御によって、リアクタLs、ダイオードDs、スイッチング素子Ssを有する昇圧チョッパ回路に、臨界モードでの動作をさせることができる。

【0054】

以上のように、センサコイルTm,Tsに鎖交する磁束がそれぞれ最小値を採るタイミングを検出することにより、インターリーブ型力率改善回路3にインターリーブ動作をさせることができる。

【0055】

より具体的には、端子106(ここでは接地されている)から端子104,105にそれぞれ流れる検出電流Imt,Istを検出し、これらが最小値を採るタイミングを検出すればよい。検出電流Imt,Istは、それぞれ磁束φm+φsm及び磁束φs+φmsに比例した値を採るからである。

【0056】

よって制御部6は検出電流Imt,Istを検出し、公知技術によってそれぞれが最小値を採るタイミングを検出し、当該タイミングでそれぞれスイッチング信号Gm,Gsを立ち上がらせればよい。スイッチング信号Gm,Gsを立ち下げる技術は図11を用いて説明したように公知技術であるので、ここでは詳細な説明を割愛する。

【0057】

以上のようにインダクタ10によれば、リアクタLmとセンサコイルTmとの誘導結合、リアクタLsとセンサコイルTsとの誘導結合を実現するためのコアをチョッパ回路の全てにおいて共通にできる。よってインターリーブ型力率改善回路30を小型化しつつ、各々のセンサコイルTm,Tsが自身に対応するリアクタLm、Lsに流れる電流が零となる時点を適切に検出することができる。

【0058】

<インダクタ10の具体的構造>

以下、上述のような誘導結合を実現するためのインダクタ10の具体的構成について説明する。

【0059】

図3はインダクタ10の構成の第1例を示す模式図である。インダクタ10はE形コア10EとI形コア10Iとを有している。

【0060】

E形コア10Eの外側レグの一方にはリアクタLmとセンサコイルTmが巻回され、他方にはリアクタLsとセンサコイルTsが巻回され、中央レグにはリアクタLm,Ls、センサコイルTm,Tsのいずれも巻回されてはいない。

【0061】

I形コア10IはE形コア10Eの一対の外側レグと中央レグとを磁気的に接続するヨークとして機能する。

【0062】

リアクタLm,Ls同士が端子101から見て同極性で誘導結合すべく、リアクタLm,Lsのそれぞれの巻線の巻回方向は、端子101からみて同方向、ここではI形コア10Iとは反対側から見て時計回り方向である。センサコイルTm,Ts同士が端子106から見て同極性で誘導結合すべく、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、端子106からみて同方向、ここではI形コア10Iとは反対側から見て反時計回り方向である。

【0063】

このようにリアクタLmとセンサコイルTmのそれぞれの巻線は同じレグに巻回されるものの、それらの巻回方向は相互に反対向きであるので、端子101からインダクタ電流Imが流れるときには端子106から検出電流Imtが流れる。また、リアクタLsとセンサコイルTsのそれぞれの巻線は同じレグに巻回されるものの、それらの巻回方向は相互に反対向きであるので、端子101からインダクタ電流Isが流れるときには端子106から検出電流Istが流れる。

【0064】

リアクタLmとセンサコイルTmのそれぞれの巻線の巻回方向は相互に同方向であったり、リアクタLsとセンサコイルTsのそれぞれの巻線の巻回方向は相互に同方向であったりしてもよい。この場合、制御部6は検出電流Imt,Istの絶対値が最小値を採るタイミングを検出し、当該タイミングでそれぞれスイッチング信号Gm,Gsを立ち上がらせればよい。

【0065】

磁束φm,φsは、それぞれ白抜き矢印、及び白抜き破線矢印で示される。E形コア10Eの中央レグには磁束φmのうち、リアクタLs、センサコイルTsに鎖交しない磁束φmm(=φm−φms)が流れる。更に中央レグには磁束φsのうち、リアクタLm、センサコイルTmに鎖交しない磁束φss(=φs−φsm)も流れる。

【0066】

このように磁束φmm,φssが流れる中央レグが存在することにより、リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さくすることができる。

【0067】

第1結合係数、第2結合係数を大きくするためには、例えばリアクタLm、センサコイルTmのそれぞれの巻線を重ねて巻回したり、リアクタLs、センサコイルTsのそれぞれの巻線を重ねて巻回したりすればよい。これは以下の他例でも同様である。

【0068】

図4はインダクタ10の構成の第2例を示す模式図である。インダクタ10はE形コア10E1,10E2を有している。

【0069】

E形コア10E1の外側レグの一方にはリアクタLmが巻回され、他方にはリアクタLsが巻回される。E形コア10E2の外側レグの一方にはセンサコイルTmが巻回され、他方にはセンサコイルTsが巻回される。E形コア10E1の外側レグの一方とE形コア10E2の外側レグの一方とが隣接し、E形コア10E1の外側レグの他方とE形コア10E2の外側レグの他方とが隣接し、E形コア10E1の中央レグとE形コア10E2の中央レグとが隣接する。E形コア10E1の中央レグとE形コア10E2の中央レグのいずれにも、リアクタLm,Ls、センサコイルTm,Tsのいずれもが巻回されてはいない。

【0070】

リアクタLm,Lsのそれぞれの巻線の巻回方向は、端子101からみて同方向、ここではE形コア10E1側から見て時計回り方向である。センサコイルTm,Ts同士が端子106から見て同極性で誘導結合すべく、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、端子106からみて同方向、ここではE形コア10E2側から見て時計回り方向である。

【0071】

このように組み合わされたE形コア10E1,10E2のいずれの中央レグも、磁束φmm,φssが流れる磁路となる。よって第2例も図3で示された第1例と同様に機能することは明白であり、第1例と同様に、リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さくすることができる。

【0072】

図5は図3で示された第1例の変形の一つを示す模式図であり、E形コア10Eの中央レグとIコア10Iとの間にギャップH1が存在する場合の構成を示す。このようにギャップH1が存在しても、磁束φmm,φssが中央レグに流れる限り、φms<φm,φsm<φsが成立し、インダクタ10としての機能が果たされる。

【0073】

図6はインダクタ10の構成の第3例を示す模式図である。インダクタ10はO形コア10OとI形コア10Ia,10Ibとを有している。I形コア10Ia,10Ibのそれぞれの一端はギャップH2によって隔てられつつ互いに対向する。I形コア10Ia,10Ibのそれぞれの他端はO形コア10Oの内周に隣接する。

【0074】

O形コア10OにはI形コア10Ia,10Ibに対して一方側に、リアクタLmとセンサコイルTmが巻回され、他方側にはリアクタLsとセンサコイルTsが巻回される。I形コア10Ia,10IbにはリアクタLm,Ls、センサコイルTm,Tsのいずれも巻回されてはいない。

【0075】

リアクタLm,Ls同士が端子101から見て同極性で誘導結合すべく、リアクタLm,Lsのそれぞれの巻線の巻回方向は、端子101からみて同方向、ここではI形コア10Ia側から見て時計回り方向である。センサコイルTm,Ts同士が端子106から見て同極性で誘導結合すべく、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、端子106からみて同方向、ここではI形コア10Ia側から見て反時計回り方向である。

【0076】

また、O形コア10Oに関してみれば、O形コア10Oの環状形状に沿った一方向について、リアクタLm,Lsのそれぞれの巻線の巻回方向は、互いに逆方向となる。また当該一方向について、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、互いに逆方向となる。

【0077】

図7もインダクタ10の構成の第3例を示す模式図である。図6においてO形コア10O及びI形コア10Ia,10Ibで構成された形状を、二つのE型コアE1,E2で形成している。

【0078】

図7に示された構成は、図4に示された第2例のE形コア10E1の中央レグとE形コア10E2の中央レグとが隣接せずにギャップH2によって隔てられつつ互いに対向する点で相違する。その他、リアクタLm,Ls、センサコイルTm,Tsが巻回される位置、巻回方向については第2例と同様であるので、詳細な説明は省略する。

【0079】

このように組み合わされたO形コア10O及びI形コア10Ia,10Ib、あるいはE形コア10E1,10E2も、図5で示された第1例の変形と同様に機能することは明白であり、第1例と同様に、リアクタLm,Ls同士の誘導結合の強さや、センサコイルTm,Ts同士の誘導結合の強さは、第1結合係数、第2結合係数よりも小さくすることができる。

【0080】

図8は図3で示された第1例の他の変形を示す模式図であり、E形コア10Eの中央レグとIコア10Iとの間にギャップH1が、E形コア10Eの一対の外側レグとIコア10Iとの間にギャップH3,H4が、それぞれ存在する場合の構成を示す。このようにギャップH1,H3,H4が存在しても、磁束φmm,φssが中央レグに流れる限り、φms<φm,φsm<φsが成立し、インダクタ10としての機能が果たされる。

【0081】

図9は図4で示された第2例の変形の一つを示す模式図であり、E形コア10E1,10E2の間には、対応するレグ同士の間にギャップH2,H5,H6が、それぞれ存在する場合の構成を示す。このようにリアクタLmが設けられるコア10E1と、センサコイルTmが設けられるコア10E2との間にギャップH5が存在する場合には、磁束φmの全てがセンサコイルTmに鎖交するとは限らない。リアクタLsが設けられるコア10E1と、センサコイルTsが設けられるコア10E2との間にギャップH5が存在する場合には、磁束φmの全てがセンサコイルTmに鎖交するとは限らない。

【0082】

このような場合でも磁束φmm,φssが流れれば、センサコイルTmに鎖交する磁束は磁束φm+φsmに比例し、センサコイルTsに鎖交する磁束は磁束φs+φmsに比例するので、インダクタ10としての機能が果たされる。

【0083】

図10は第3例の変形を示す模式図である。インダクタ10はO形コア10Oを有するものの、I形コア10Ia,10Ibを有していない。O形コア10Oの環状形状に沿った一方向について、リアクタLm,Lsのそれぞれの巻線の巻回方向は、互いに逆方向となる。また当該一方向について、センサコイルTm,Tsのそれぞれの巻線の巻回方向は、互いに逆方向となる。

【0084】

このような場合でも、例えば磁気飽和によっていわゆる漏れ磁束として磁束φmm,φssが流れれば、φms<φm,φsm<φsが成立し、インダクタ10としての機能が果たされる。

【0085】

以上のように、インダクタ10は、ギャップが設けられる場合はあるものの、共通のコアでリアクタLm、Ls、センサコイルTm,Tsを誘導結合するので、その寸法が小さい。そしてセンサコイルTmが検出する磁束(φsm+φm)が最小値を採る時点は、リアクタLmが発生する磁束φmが最小値を採る時点と一致する。同様に、センサコイルTsが検出する磁束(φs+φms)が最小値を採る時点は、リアクタLsが発生する磁束φsが最小値を採る時点と一致する。よってインダクタ10を採用することで、センサコイルTmに流れる検出電流Imt及びセンサコイルTsに流れる検出電流istを検出することにより、インターリーブ型力率改善回路30を臨界モードで使用する制御ができる。

【0086】

また、リアクタLmが発生させる磁束φmのうちセンサコイルTsに鎖交しない磁束φmmと、リアクタLsが発生させる磁束φsのうちセンサコイルTmに鎖交しない磁束φssとが流れる磁路が存在することは、リアクタLm,Ls同士を第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合し、センサコイルTm,Ts同士を第1結合係数及び第2結合係数のいずれの大きさよりも小さい強さで結合することに資する。

【符号の説明】

【0087】

101〜106 端子

Lm,Ls リアクタ

Tm,Ts センスコイル

10E,10E1,10E2 E形コア

10I,10Ia,10Ib I形コア

10O O形コア

【特許請求の範囲】

【請求項1】

第1端子(101)と、

前記第1端子に接続された第1端と、第2端とを有する第1リアクタ(Lm)と、

前記第1端子に接続された第1端と、第2端とを有する第2リアクタ(Ls)と、

第2端子(106)と、

前記第2端子に接続された第1端と、第2端とを有する第1センサコイル(Tm)と、

前記第2端子に接続された第1端と、第2端とを有する第2センサコイル(Ts)と、

前記第1リアクタ及び前記第1センサコイル同士を第1結合係数で誘導結合し、前記第2リアクタ及び前記第2センサコイル同士を第2結合係数で誘導結合し、前記第1リアクタと前記第2リアクタとを前記第1端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合し、前記第1センサコイルと前記第2センサコイルとを前記第2端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合するコア(10E,10E1,10E2,10I,10Ia,10Ib,10O)と

を備える、インターリーブ型力率改善回路用インダクタ。

【請求項2】

前記コアにおいて、前記第1リアクタが発生させる磁束(φm)のうち前記第2センサコイルに鎖交しない磁束(φmm)と、前記第2リアクタが発生させる磁束(φs)のうち前記第1センサコイルに鎖交しない磁束(φss)とが流れる磁路が存在する、請求項1記載のインターリーブ型力率改善回路用インダクタ。

【請求項3】

前記コアは、中央レグと二つの外側レグとを有するE形コア(10E)と、I形コア(10I)とを備え、

前記外側レグの一方には前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回され、

前記外側レグの他方には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回され、

前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向であり、

前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向であり、

前記中央レグには前記第1リアクタ、前記第2リアクタ、前記第1センサコイル及び前記第2センサコイルのいずれもが巻回されず、

前記I形コアはE形コアの一対の外側レグと中央レグとを磁気的に接続するヨークとして機能する、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【請求項4】

前記コアは、中央レグと二つの外側レグとを有する第1のE形コア(10E1)と、中央レグと二つの外側レグとを有する第2のE形コア(10E2)とを備え、

前記第1のE形コアの前記外側レグの一方には第1のリアクタ(Lm)が巻回され、前記第1のE形コアの前記外側レグの他方には前記第2のリアクタ(Ls)が巻回され、

前記第2のE形コアの前記外側レグの一方には前記第1のセンサコイル(Tm)が巻回され、前記第2のE形コアの前記外側レグの他方には第2のセンサコイル(Ts)が巻回され、

前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1のE形コア側から見て同方向であり、

前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第2のE形コア側から見て同方向であり、

前記第1のE形コアの前記中央レグと前記第2のE形コアの前記中央レグのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されず、

前記第1のE形コアの前記外側レグの前記一方と、前記第2のE形コアの前記外側レグの前記一方とが隣接し、

前記第1のE形コアの前記外側レグの前記他方と、前記第2のE形コアの前記外側レグの前記他方とが隣接する、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【請求項5】

前記コアはO形コア(10O)を備え、

前記O形コアの環状形状に沿った一方向について、前記第1リアクタ(Lm)及び前記第2リアクタ(Ls)のそれぞれの巻線の巻回方向は、互いに逆方向であり、

当該一方向について、前記第1センサコイル(Tm)及び前記第2センサコイル(Ts)のそれぞれの巻線の巻回方向は、互いに逆方向である、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【請求項6】

前記コアはO形コア(10O)と、第1のI形コア(10Ia)と、第2のI形コア(10Ib)とを備え、

前記第1のI形コア及び前記第2のI形コアのそれぞれの一端はギャップ(H2)によって隔てられつつ互いに対向し、

前記第1のI形コア及び前記第2のI形コアのそれぞれの他端は前記O形コアの内周に隣接し、

前記O形コアには、前記第1のI形コア及び前記第2のI形コアに対して一方側に、前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回され、他方側には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回され、

前記第1のI形コア及び前記第2のI形コアのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されず、

前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1I形コア側から見て同方向であり、

前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第1のI形コア10Ia側から見て同方向である、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【請求項1】

第1端子(101)と、

前記第1端子に接続された第1端と、第2端とを有する第1リアクタ(Lm)と、

前記第1端子に接続された第1端と、第2端とを有する第2リアクタ(Ls)と、

第2端子(106)と、

前記第2端子に接続された第1端と、第2端とを有する第1センサコイル(Tm)と、

前記第2端子に接続された第1端と、第2端とを有する第2センサコイル(Ts)と、

前記第1リアクタ及び前記第1センサコイル同士を第1結合係数で誘導結合し、前記第2リアクタ及び前記第2センサコイル同士を第2結合係数で誘導結合し、前記第1リアクタと前記第2リアクタとを前記第1端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合し、前記第1センサコイルと前記第2センサコイルとを前記第2端子から見て同極性でかつ前記第1結合係数及び前記第2結合係数のいずれの大きさよりも小さい強さで結合するコア(10E,10E1,10E2,10I,10Ia,10Ib,10O)と

を備える、インターリーブ型力率改善回路用インダクタ。

【請求項2】

前記コアにおいて、前記第1リアクタが発生させる磁束(φm)のうち前記第2センサコイルに鎖交しない磁束(φmm)と、前記第2リアクタが発生させる磁束(φs)のうち前記第1センサコイルに鎖交しない磁束(φss)とが流れる磁路が存在する、請求項1記載のインターリーブ型力率改善回路用インダクタ。

【請求項3】

前記コアは、中央レグと二つの外側レグとを有するE形コア(10E)と、I形コア(10I)とを備え、

前記外側レグの一方には前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回され、

前記外側レグの他方には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回され、

前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向であり、

前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記I形コアとは反対側から見て同方向であり、

前記中央レグには前記第1リアクタ、前記第2リアクタ、前記第1センサコイル及び前記第2センサコイルのいずれもが巻回されず、

前記I形コアはE形コアの一対の外側レグと中央レグとを磁気的に接続するヨークとして機能する、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【請求項4】

前記コアは、中央レグと二つの外側レグとを有する第1のE形コア(10E1)と、中央レグと二つの外側レグとを有する第2のE形コア(10E2)とを備え、

前記第1のE形コアの前記外側レグの一方には第1のリアクタ(Lm)が巻回され、前記第1のE形コアの前記外側レグの他方には前記第2のリアクタ(Ls)が巻回され、

前記第2のE形コアの前記外側レグの一方には前記第1のセンサコイル(Tm)が巻回され、前記第2のE形コアの前記外側レグの他方には第2のセンサコイル(Ts)が巻回され、

前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1のE形コア側から見て同方向であり、

前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第2のE形コア側から見て同方向であり、

前記第1のE形コアの前記中央レグと前記第2のE形コアの前記中央レグのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されず、

前記第1のE形コアの前記外側レグの前記一方と、前記第2のE形コアの前記外側レグの前記一方とが隣接し、

前記第1のE形コアの前記外側レグの前記他方と、前記第2のE形コアの前記外側レグの前記他方とが隣接する、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【請求項5】

前記コアはO形コア(10O)を備え、

前記O形コアの環状形状に沿った一方向について、前記第1リアクタ(Lm)及び前記第2リアクタ(Ls)のそれぞれの巻線の巻回方向は、互いに逆方向であり、

当該一方向について、前記第1センサコイル(Tm)及び前記第2センサコイル(Ts)のそれぞれの巻線の巻回方向は、互いに逆方向である、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【請求項6】

前記コアはO形コア(10O)と、第1のI形コア(10Ia)と、第2のI形コア(10Ib)とを備え、

前記第1のI形コア及び前記第2のI形コアのそれぞれの一端はギャップ(H2)によって隔てられつつ互いに対向し、

前記第1のI形コア及び前記第2のI形コアのそれぞれの他端は前記O形コアの内周に隣接し、

前記O形コアには、前記第1のI形コア及び前記第2のI形コアに対して一方側に、前記第1リアクタ(Lm)と前記第1センサコイル(Tm)とが巻回され、他方側には前記第2リアクタ(Ls)と前記第2センサコイル(Ts)とが巻回され、

前記第1のI形コア及び前記第2のI形コアのいずれにも、前記第1のリアクタ、前記第2のリアクタ、前記第1のセンサコイル、前記第2のセンサコイルのいずれもが巻回されず、

前記第1リアクタ及び前記第2リアクタのそれぞれの巻線の巻回方向は、前記第1I形コア側から見て同方向であり、

前記第1センサコイル及び前記第2センサコイルのそれぞれの巻線の巻回方向は、前記第1のI形コア10Ia側から見て同方向である、請求項2記載のインターリーブ型力率改善回路用インダクタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−106484(P2013−106484A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−250300(P2011−250300)

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000002853)ダイキン工業株式会社 (7,604)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000002853)ダイキン工業株式会社 (7,604)

【Fターム(参考)】

[ Back to top ]