インダクタチップ、その製造方法及び実装方法

【課題】複数のインダクタを積層した薄型のインダクタチップを提供する。

【解決手段】インダクタチップは、基板1と、この基板1上において上下に離隔して配置された複数層の薄膜のインダクタ3−1〜3−4と、この各層毎のインダクタ3−1〜3−4をそれぞれ被覆する複数層の層間絶縁膜4−1〜4−4と、横方向に離隔して配置されて各層のインダクタ3−1〜3−4にそれぞれ接続された複数のプラグ6と、この複数のプラグ6の上端にそれぞれ接合され、最上層の層間絶縁膜4−1上において離隔して配置された複数のパッド7とを備えている。各層のインダクタ3−1〜3−4は、スパイラル状パターンをそれぞれ有し、この各パターンが各層毎に横方向にずらして配置されている。複数のプラグ6は、層間絶縁膜4−1〜4−4を貫通して最上層の層間絶縁膜4−4の表面に引き出されている。

【解決手段】インダクタチップは、基板1と、この基板1上において上下に離隔して配置された複数層の薄膜のインダクタ3−1〜3−4と、この各層毎のインダクタ3−1〜3−4をそれぞれ被覆する複数層の層間絶縁膜4−1〜4−4と、横方向に離隔して配置されて各層のインダクタ3−1〜3−4にそれぞれ接続された複数のプラグ6と、この複数のプラグ6の上端にそれぞれ接合され、最上層の層間絶縁膜4−1上において離隔して配置された複数のパッド7とを備えている。各層のインダクタ3−1〜3−4は、スパイラル状パターンをそれぞれ有し、この各パターンが各層毎に横方向にずらして配置されている。複数のプラグ6は、層間絶縁膜4−1〜4−4を貫通して最上層の層間絶縁膜4−4の表面に引き出されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄型受動部品の1つである薄型インダクタ部品、特に、インダクタを高密度に積層したインダクタチップとその製造方法及び実装方法に関するものである。

【背景技術】

【0002】

従来、薄型受動部品を積層する技術としては、例えば、次のような文献に記載されるものがあった。

【0003】

【非特許文献1】荻野等「集積受動素子の開発」、第17回エレクトロニクス実装学術講演大会集、2003年3月、13B−16、p.177−178

【非特許文献2】益・岡田「シリコン上の高周波受動素子技術」、応用物理、2004年9月、第73巻、第9号、p.1172−1178

【0004】

非特許文献1に示されているように、近年の電子機器の小型化は、急激であり、特に、携帯電話に代表されるモバイル機器は小型・軽量化の要求が高く、かつ、高機能化の要求も高まっている。携帯電話等の高周波(RF)送受信回路回路を含むデバイスは、コンデンサ、抵抗、インダクタ等の受動部品を多く搭載する。現在での実装面積におけるこの受動部品の割合は60%程度を占めており、小型化の大きな障害となっている。そこで、非特許文献1では、薄膜多層配線技術を適用し、ガラス基板上に銅配線を用いてQ値の高いインダクタ及び特性の良好なキャパシタを実現し、又、これらを集積化することでRFフィルタを試作し、従来比1/3の実装面積となる集積化受動素子を実現している。

【0005】

又、非特許文献2に示されているように、シリコン上に高周波用受動部品を搭載する開発も進んでいる。

【発明の開示】

【発明が解決しようとする課題】

【0006】

従来の受動部品は部品単体で、ある程度の大きさと厚みがあるために、表面実装する以外に実装方法がなく、従って実装面積を削減するためには部品の大きさを小さくするしか方法がなく、その方向で小型化が進められてきた。しかし、その小型化も限界に近くなってきており、物性的にも限界に近づいている。更に、部品の小型化に伴い、部品を実装するマウンタ(搭載機)が対応できなくなってきている。

【0007】

即ち、受動部品では1つの部品がある程度の大きさと厚みを有しているために、平面的に表面実装しなければならないので、今後の小型軽量、高機能化のための実装面積の減少と実装部品点数の増加に対応できない。特に、受動部品の1つであるインダクタは、これを基板上において平面的に形成しようとすると、形成面積が非常に大きくなるので、小型化が限界に達してきており、この限界を超えて小型化できても、小さすぎて実際にマウンタでハンドリング(把持)することが不可能になる。

【0008】

本発明は、上記のような限界をなくし、狭い実装面積に、多くのインダクタを実装する薄型のインダクタチップとその製造方法及び実装方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

前記課題を解決するために、本発明のインダクタチップは、基板と、前記基板上において上下に離隔して配置された複数層の薄膜のインダクタと、前記各層毎のインダクタをそれぞれ被覆する複数層の層間絶縁膜と、横方向に離隔して配置されて前記各層のインダクタにそれぞれ接続された複数のプラグと、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極とを備えている。

【0010】

ここで、前記複数層のインダクタは、各層毎に所定形状のパターンを有し、前記各パターンが前記各層毎に横方向にずらして配置されている。前記複数のプラグは、前記複数層の層間絶縁膜を上方向に貫通して前記最上層の層間絶縁膜の表面に引き出されている。又、前記各パターンは、例えば、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、配置されている。

【0011】

本発明のインダクタチップの製造方法は、基板上にプロテクト絶縁膜を形成するプロテクト絶縁膜形成工程と、下層のインダクタ形成工程と、下層の層間絶縁膜形成工程と、上層のインダクタ・層間絶縁膜形成工程と、プラグ形成工程と、電極形成工程と、パッシベーション膜・開口形成工程とを有している。

【0012】

前記下層のインダクタ形成工程では、前記プロテクト絶縁膜上に下層のメタル膜を形成し、前記下層のメタル膜をパターニング及びエッチングして、下層のスパイラル状パターンを有する下層の薄膜のインダクタを形成する。下層の層間絶縁膜形成工程では、前記下層のインダクタを含む前記プロテクト絶縁膜の全面に、下層の層間絶縁膜を形成する。前記上層のインダクタ・層間絶縁膜形成工程では、前記下層の層間絶縁膜上に上層のメタル膜を形成し、前記上層のメタル膜をパターニング及びエッチングして、前記下層のスパイラル状パターンに対して横方向にずれて配置された上層のスパイラル状薄膜パターンを有する上層の薄膜のインダクタを形成する上層のインダクタ形成処理と、前記上層のインダクタを含む前記下層の層間絶縁膜の全面に、上層の層間絶縁膜を形成する上層の層間絶縁膜形成処理と、を交互に繰り返す。前記各層のスパイラル状パターンは、例えば、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、形成される。

【0013】

前記プラグ形成工程では、横方向に離隔して開孔される複数のコンタクトホール(接続孔)であって、前記各コンタクトホールの下端がこれに対応する前記各層のインダクタにそれぞれ位置し、前記各コンタクトホースの上端が前記最上層の層間絶縁膜の表面に位置し、前記複数層の層間絶縁膜を上方向に貫通する前記複数のコンタクトホールを形成し、前記各コンタクトホール中にメタルをそれぞれ充填して複数のプラグを形成する。前記電極形成工程では、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極を形成する。更に、前記パッシベーション膜・開口形成工程では、前記複数の電極を含む前記最上層の層間絶縁膜の全面にパッシベーション膜を形成し、前記パッシベーション膜における前記複数の電極箇所をエッチングにより開口して前記複数の電極を露出させる。

【0014】

本発明のインダクタチップの実装方法では、前記インダクタチップを用い、前記基板をバックグラインド(底面研磨)により薄膜化し、プリント基板を含む他の基板に埋め込むようにしている。

【発明の効果】

【0015】

請求項1〜7に係る発明によれば、次のような効果を有している。

(A) 積層構造のインダクタチップにより、複数のインダクタを有するアレイを容易に製造できる。しかも、基板をバックグラインドにより薄型化することにより、インダクタチップの全体の厚さを例えば数十μmという薄型に容易にできる。

【0016】

(B) 複数のプラグの位置が重ならないように、各層のインダクタのパターンをずらした状態で積層し、それらのプラグを介して複数の電極に接続する構造であるので、各電極を離間した状態で容易に配置形成でき、製造も容易である。

【0017】

請求項8に係る発明によれば、次のような効果を有している。

(C) 基板をバックグラインドにより薄型化するので、インダクタチップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型のインダクタチップを実装する場合、複数のインダクタを一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【0018】

(D) 各電極は離間した状態で配置されているので、実装時における外部回路との結線作業が容易になり、より実装コストを削減できる。従って、例えば積層構造の薄型の部品内蔵プリント基板等を容易に製造できる。

【発明を実施するための最良の形態】

【0019】

本発明のインダクタチップは、シリコン基板等の基板と、アルミニュウム等で形成され、前記基板上において上下に離隔して配置された複数層の薄膜のインダクタと、前記各層毎のインダクタをそれぞれ被覆する複数層の層間絶縁膜と、タングステン(W)等で形成され、横方向に離隔して配置されて前記各層のインダクタにそれぞれ接続された複数のプラグと、アルミニュウム等で形成され、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極とを備えている。

【0020】

ここで、前記各層のインダクタは、スパイラル状パターンをそれぞれ有し、前記各パターンが前記各層毎に横方向にずらして配置されている。例えば、前記各パターンは、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、配置されている。前記複数のプラグは、前記複数層の層間絶縁膜を上方向に貫通して前記最上層の層間絶縁膜の表面に引き出されている。

【実施例1】

【0021】

(構造)

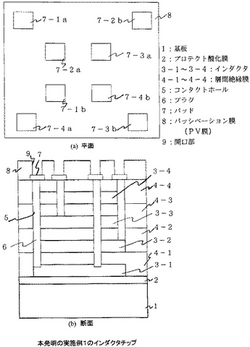

図1(a)、(b)は本発明の実施例1を示すインダクタチップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。

【0022】

このインダクタチップは、全体の厚さが例えば100μm以下、好ましくは50μm以下の積層構造をしており、底面がバックグラインドにより薄膜化(例えば、100μm以下、好ましくは50μm以下に薄膜化)される基板(例えば、シリコン基板、ガラス基板、アルミナ基板、ガラス・アルミナ基板等)1を有している。基板1上には保護用のプロテクト絶縁膜(例えば、プロテクト酸化膜等)2が被着され、この絶縁膜2上に、複数層(例えば、4層)の角形のスパイラル状インダクタ3−1〜3−4が、p−TEOS等を用いて形成された層間絶縁膜4−1〜4−4を介して積層されている。各層のスパイラル状インダクタ3−1〜3−4は、フォトリソグラフィ等により形成された同一形状の薄膜メタルパターン(例えば、薄膜アルミニュウムパターン、薄膜銅パターン等)からなる積層構造となっている。この積層構造では、絶縁膜2上に1層目のインダクタ3−1が形成されて1層目の層間絶縁膜4−1により覆われ、プラグ位置が重ならないように、その上に所定角度(例えば、90°)右回転して2層目のインダクタ3−2が形成されて2層目の層間絶縁膜4−2により覆われ、プラグ位置が重ならないように、その上に180°右回転して3層目のインダクタ3−3が形成されて3層目の層間絶縁膜4−32により覆われ、更に、プラグ位置が重ならないように、その上に270°右回転して4層目のインダクタ3−4が形成されて4層目の層間絶縁膜4−4により覆われている。

【0023】

各層のインダクタ3−1〜3−4の初端部と終端部とに位置する垂直方向には、複数のコンタクトホール5が形成され、これらのコンタクトホール5中に結線用メタル(例えば、タングステン等)が埋設されて複数のプラグ6が形成されている。複数のプラグ6の上端面は、4層目の層間絶縁膜4−4の表面と同一面に位置しており、それらのプラグ6の上端面上に、メタル(例えば、アルミニュウム等)からなる複数の電極(例えば、パッド7)7−1a,7−1b〜7−4a,7−4bが形成されている。

【0024】

図1(b)に示すように、パッド7−1aはプラグ6を介して1層目のインダクタ3−1の初端部に接続され、それと離間したパッド7−1bはプラグ6を介して1層目のインダクタ3−1の終端部に接続されている。同様に、パッド7−2aと7−2bは各プラグ6を介して2層目のインダクタ3−2の初端部と終端部に接続され、パッド7−3aと7−3bは各プラグ6を介して3層目のインダクタ3−3の初端部と終端部に接続され、パッド7−4aと7−4bは各プラグ6を介して4層目のインダクタ3−4の初端部と終端部に接続されている。4層目の層間絶縁膜4−4は、窒化膜(SiN)等の不活性化膜であるパッシベーション膜(以下「PV膜」という。)8により覆われ、このPV膜8における各パッド7−1a,7−1b〜7−4a,7−4b箇所のみに開口部9が形成されてその各パッド7−1a,7−1b〜7−4a,7−4bが露出している。

【0025】

(製造方法)

図2(a)、(b)〜図5(a)、(b)は、図1のインダクタチップの製造方法例を示す概略の工程図であり、図2(a)、(b)は1層目のインダクタ3−1箇所の平面図とその縦断面図、図3(a)、(b)は2層目のインダクタ3−2箇所の平面図とその縦断面図、図4(a)、(b)は3層目のインダクタ3−3箇所の平面図とその縦断面図、及び図5(a)、(b)は4層目のインダクタ3−4箇所の平面図とその縦断面図である。

【0026】

図1のインダクタチップは、例えば、以下のような工程(1)〜(5)により製造される。

【0027】

(1) 図2の工程

例えば、シリコンウェハ1Aの上に水蒸気を流しつつ加熱し、プロテククト酸化膜である絶縁膜2を形成する。その上にアルミニウムをスパッタリング法により全面に形成し、レジストを塗布し、UVキュア(紫外線熱処理)した後、露光機で露光し、現像し、エッチング装置によりエッチングを行って、所定間隔離れて配置された複数の1層目の角形スパイラル状インダクタ3−1を形成する。各1層目のインダクタ3−1は、左上の初端部3−1aから右回転方向に巻装され、終端部3−1bが中央左下に位置している。

【0028】

(2) 図3の工程

複数の1層目のインダクタ3−1を含む絶縁膜2の全面に、p−TEOSを用いて化学的気相成長法(以下「CVD法」という。)により1層目の層間絶縁膜4−1を形成し、その上に、図2と同様に、所定間隔離れた複数の2層目の角形スパイラル状インダクタ3−2を形成する。この際、各2層目のインダクタ3−2のパターンは、各1層目のインダクタ3−1のパターンに対して例えば右回りに90°回転させて形成する。そのため、各2層目のインダクタ3−2の初端部3−2aは右上に移動し、終端部3−2bが中央左上に移動している。

【0029】

(3) 図4の工程

複数の2層目のインダクタ3−2を含む1層目の層間絶縁膜4−1の全面に、p−TEOSを用いてCVD法により2層目の層間絶縁膜4−2を形成し、その上に、図2と同様に、所定間隔離れた複数の3層目の角形スパイラル状インダクタ3−3を形成する。この際、各3層目のインダクタ3−3のパターンは、各1層目のインダクタ3−1のパターンに対して例えば右回りに180°回転させて形成する。そのため、各3層目のインダクタ3−3の初端部3−3aは右下に移動し、終端部3−3bが中央右上に移動している。

【0030】

(4) 図5の工程

複数の3層目のインダクタ3−3を含む2層目の層間絶縁膜4−2の全面に、p−TEOSを用いてCVD法により3層目の層間絶縁膜4−3を形成し、その上に、図2と同様に、所定間隔離れた複数の4層目の角形スパイラル状インダクタ3−4を形成する。この際、各4層目のインダクタ3−4のパターンは、各1層目のインダクタ3−1のパターンに対して例えば右回りに270°回転させて形成する。そのため、各4層目のインダクタ3−4の初端部3−4aは左下に移動し、終端部3−4bが中央右下に移動している。

【0031】

(5) 図1の工程

複数の4層目のインダクタ3−4を含む3層目の層間絶縁膜4−3の全面に、CVD法により4層目の層間絶縁膜4−4を形成する。各層のインダクタ3−1〜3−4の初端部3−1a〜3−4aと終端部3−1b〜3−4bに、それぞれ垂直方向のコンタクトホール5を形成し、その中に、CVD法によりタングステンのフラグ6を埋め込む。そして、表面にあるタングステンを、化学的機械的研磨法(以下「CMP法」という。)により取り去る。次に、スパッタリング法により、全面にアルミニュウム膜を形成し、このアルミニュウム膜をフォトリソグラフィを用いて選択的にエッチングし、プラグ6の上にアルミニュウム膜からなる複数のパッド7を形成する。

【0032】

複数のパッド7を含む4層目の層間絶縁膜4−4上に、CVD法により、窒化膜からなるPV膜8を形成する。フォトリソグラフィにより、複数のパッド7上のPV膜8のみをエッチングして複数の開口部9を形成し、その複数のパッド7を露出させる。これにより、積層構造のインダクタ3−1〜3−4を有するインダクタアレイが形成できる。このインダクタアレイが形成されたシリコンウェハ1Aをバックグラインドして薄膜化し、ダイシング(切断)により個片化すれば、図1に示す積層構造のインダクタチップが得られる。

【0033】

このようにして製造されたインダクタチップは、例えば、実装時においてプリント基板等の上にダイスボンディング(固着)し、そのインダクタチップのパッド7−1a,7−1b〜7−4a,7−4bを必要な他の部品とワイヤボンディング(ワイヤ接続)等で結線することにより、所望の回路動作を行わせることができる。又、インダクタチップを基板内等に埋め込む際には、半田ボールや導電性ペースト等を用いて接続することもできる。

【0034】

(効果等)

本実施例1では、次の(a)〜(d)のような効果等を有している。

【0035】

(a) 積層構造のインダクタチップにより、複数のインダクタ3−1〜3−4を有するアレイを容易に製造できる。しかも、基板1をバックグラインドにより薄型化するので、インダクタチップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型のインダクタチップを使用する場合、複数のインダクタ3−1〜3−4を一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【0036】

(b) 複数のプラグ6の位置が重ならないように、各層のインダクタ3−1〜3−4のパターンを所定角度(例えば、90°)回転させた状態で積層し、これらを垂直方向に埋設したプラグ6を介してパッド7−1a,7−1b〜7−4a,7−4bに接続する構造であるので、各パッド7−1a,7−1b〜7−4a,7−4bを離間した状態で容易に配置形成でき、製造も容易である。しかも、実装時における外部回路との結線作業が容易になり、より実装コストを削減できる。

【0037】

(c) インダクタ3−1〜3−4の積層数、或いはインダクタパターンの回転方向や回転角度は、図示のものに限定されず、任意の積層数や角度でよく、例えば、インダクタ3−1〜3−4の積層数等に応じてインダクタパターンの回転角度を適宜設定すればよい。又、各インダクタ3−1〜3−4のパターンは、円形スパイラル状等の他の形状にしてもよい。

【0038】

(d) 使用材料や製造工程等は、種々変更できる。例えば、基板1としてガラス基板、アルミナ基板、或いはガラス・アルミナ基板等、保護用の絶縁膜2として窒化膜等を使用してもよい。スパイラル状インダクタ3−1〜3−4やパッド7として使用しているアルミニュウム箔は、エッチングが容易であるが、これ以外の銅箔等を使用してもよい。銅箔は、エッチングがしづらいので、電気メッキ法等で形成することになるが、導電性がアルミニュウムよりも良い。又、層間絶縁膜4−1〜4−4としてp−TEOS以外の材料、プラグ6としてアルミニュウム等、PV膜8として樹脂等を使用してもよく、それに応じて製造方法を適宜変更すればよい。

【実施例2】

【0039】

(構造・製造方法)

図6(a)、(b)は本発明の実施例2を示すインダクタチップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。この図6において、実施例1を示す図1中の要素と共通の要素には共通の符号が付されている。

【0040】

実施例1では、各層の角形スパイラル状インダクタ3−1〜3−4を90℃ずつ右回転させて形成し、複数のプラグ6の位置が重ならないようにしているが、本実施例2では、各層の角形スパイラル状インダクタ3−1〜3−4の形成位置を任意の方向に平行移動することにより、複数のプラグ6の位置が重ならないようにしている点のみが異なる。

【0041】

図6(b)の平面図では、各層のインダクタ3−1〜3−4が平行移動して形成され、これに接続されたパッド7−1a,7−1b〜7−4a,7−4bがチップ表面の片側のみに配置された例が示されている。その他の構成や、製造方法は、実施例1とほぼ同様である。

【0042】

(効果等)

本実施例2では、実施例1の(a)〜(d)の効果等を有する他に、更に次の(e)のような効果等がある。

【0043】

(e) 図7は、図6(a)の他の平面図である。

本実施例2では、実施例1のように各層のインダクタ3−1〜3−4を回転させないで平行移動しているので、これに接続されるパッド7−1a,7−1b〜7−4a,7−4bをインダクタチップ表面の片側に局在させることができる。そのため、図7に示すように、インダクタチップ表面の他の片側に空き領域を設けることができ、この空き領域に他の小型のチップ等の部品10を積層することができる。このように、本実施例2では、複数のインダクタ3−1〜3−4を積層することにより、高密度実装が可能になり、その上、他のチップ等の部品10を積層することが可能になるので、更なる高密度化を達成できる。

【実施例3】

【0044】

図8は、本発明の実施例3を示すインダクタチップを用いた部品内蔵プリント基板の概略の断面図である。

【0045】

この図8では、上記実施例1、2の薄型のインダクタチップ20等をプリント基板に内蔵させた部品内蔵プリント基板の実装例が示されている。この部品内蔵プリント基板の製造では、例えば、薄型のインダクタチップ20の他に、予め薄型の抵抗チップ21、コンデンサチップ22、及び半導体集積回路チップ(以下「LSIチップ」という。)23等の薄型部品を製造しておく。そして、プリント基板本体24上に、例えば、コンデンサチップ22及びLSIチップ23等を固着し、アルミニュウム箔、銅箔等の1層目配線層25−1により結線し、これらを樹脂絶縁膜26により被覆して1層目を形成する。更に、1層目の上に、インダクタチップ20及び抵抗チップ21等を固着し、1層目配線層25−1にビアホール27を介して接続された2層目配線層25−2によって結線し、これらを樹脂絶縁膜26により被覆して2層目を形成する等すれば、図8のような積層構造の薄型の部品内蔵プリント基板を容易に製造できる。

【0046】

インダクタチップ20等の他の実装例としては、例えば、プリント基板本体24内に図示しない収納凹部を形成し、この収納凹部内にインダクタチップ20等を搭載して樹脂絶縁膜26等により被覆する等、種々の実装形態が可能である。

【図面の簡単な説明】

【0047】

【図1】本発明の実施例1を示すインダクタチップの概略の構成図である。

【図2】図1の1層目のインダクタ3−1箇所の平面図とその縦断面図である。

【図3】図1の2層目のインダクタ3−2箇所の平面図とその縦断面図である。

【図4】図1の3層目のインダクタ3−3箇所の平面図とその縦断面図である。

【図5】図1の4層目のインダクタ3−4箇所の平面図とその縦断面図である。

【図6】本発明の実施例2を示すインダクタチップの概略の構成図である。

【図7】図6(a)の他の平面図である。

【図8】本発明の実施例3を示す部品内蔵プリント基板の概略の断面図である。

【符号の説明】

【0048】

1 基板

1A シリコンウェハ

2 プロテクト酸化膜

3−1〜3−4 インダクタ

4−1〜4−4 層間絶縁膜

5 コンタクトホール

6 プラグ

7 パッド

8 パッシベーション膜(PV膜)

9 開口部

10 部品

20 インダクタチップ

24 プリント基板本体

【技術分野】

【0001】

本発明は、薄型受動部品の1つである薄型インダクタ部品、特に、インダクタを高密度に積層したインダクタチップとその製造方法及び実装方法に関するものである。

【背景技術】

【0002】

従来、薄型受動部品を積層する技術としては、例えば、次のような文献に記載されるものがあった。

【0003】

【非特許文献1】荻野等「集積受動素子の開発」、第17回エレクトロニクス実装学術講演大会集、2003年3月、13B−16、p.177−178

【非特許文献2】益・岡田「シリコン上の高周波受動素子技術」、応用物理、2004年9月、第73巻、第9号、p.1172−1178

【0004】

非特許文献1に示されているように、近年の電子機器の小型化は、急激であり、特に、携帯電話に代表されるモバイル機器は小型・軽量化の要求が高く、かつ、高機能化の要求も高まっている。携帯電話等の高周波(RF)送受信回路回路を含むデバイスは、コンデンサ、抵抗、インダクタ等の受動部品を多く搭載する。現在での実装面積におけるこの受動部品の割合は60%程度を占めており、小型化の大きな障害となっている。そこで、非特許文献1では、薄膜多層配線技術を適用し、ガラス基板上に銅配線を用いてQ値の高いインダクタ及び特性の良好なキャパシタを実現し、又、これらを集積化することでRFフィルタを試作し、従来比1/3の実装面積となる集積化受動素子を実現している。

【0005】

又、非特許文献2に示されているように、シリコン上に高周波用受動部品を搭載する開発も進んでいる。

【発明の開示】

【発明が解決しようとする課題】

【0006】

従来の受動部品は部品単体で、ある程度の大きさと厚みがあるために、表面実装する以外に実装方法がなく、従って実装面積を削減するためには部品の大きさを小さくするしか方法がなく、その方向で小型化が進められてきた。しかし、その小型化も限界に近くなってきており、物性的にも限界に近づいている。更に、部品の小型化に伴い、部品を実装するマウンタ(搭載機)が対応できなくなってきている。

【0007】

即ち、受動部品では1つの部品がある程度の大きさと厚みを有しているために、平面的に表面実装しなければならないので、今後の小型軽量、高機能化のための実装面積の減少と実装部品点数の増加に対応できない。特に、受動部品の1つであるインダクタは、これを基板上において平面的に形成しようとすると、形成面積が非常に大きくなるので、小型化が限界に達してきており、この限界を超えて小型化できても、小さすぎて実際にマウンタでハンドリング(把持)することが不可能になる。

【0008】

本発明は、上記のような限界をなくし、狭い実装面積に、多くのインダクタを実装する薄型のインダクタチップとその製造方法及び実装方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

前記課題を解決するために、本発明のインダクタチップは、基板と、前記基板上において上下に離隔して配置された複数層の薄膜のインダクタと、前記各層毎のインダクタをそれぞれ被覆する複数層の層間絶縁膜と、横方向に離隔して配置されて前記各層のインダクタにそれぞれ接続された複数のプラグと、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極とを備えている。

【0010】

ここで、前記複数層のインダクタは、各層毎に所定形状のパターンを有し、前記各パターンが前記各層毎に横方向にずらして配置されている。前記複数のプラグは、前記複数層の層間絶縁膜を上方向に貫通して前記最上層の層間絶縁膜の表面に引き出されている。又、前記各パターンは、例えば、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、配置されている。

【0011】

本発明のインダクタチップの製造方法は、基板上にプロテクト絶縁膜を形成するプロテクト絶縁膜形成工程と、下層のインダクタ形成工程と、下層の層間絶縁膜形成工程と、上層のインダクタ・層間絶縁膜形成工程と、プラグ形成工程と、電極形成工程と、パッシベーション膜・開口形成工程とを有している。

【0012】

前記下層のインダクタ形成工程では、前記プロテクト絶縁膜上に下層のメタル膜を形成し、前記下層のメタル膜をパターニング及びエッチングして、下層のスパイラル状パターンを有する下層の薄膜のインダクタを形成する。下層の層間絶縁膜形成工程では、前記下層のインダクタを含む前記プロテクト絶縁膜の全面に、下層の層間絶縁膜を形成する。前記上層のインダクタ・層間絶縁膜形成工程では、前記下層の層間絶縁膜上に上層のメタル膜を形成し、前記上層のメタル膜をパターニング及びエッチングして、前記下層のスパイラル状パターンに対して横方向にずれて配置された上層のスパイラル状薄膜パターンを有する上層の薄膜のインダクタを形成する上層のインダクタ形成処理と、前記上層のインダクタを含む前記下層の層間絶縁膜の全面に、上層の層間絶縁膜を形成する上層の層間絶縁膜形成処理と、を交互に繰り返す。前記各層のスパイラル状パターンは、例えば、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、形成される。

【0013】

前記プラグ形成工程では、横方向に離隔して開孔される複数のコンタクトホール(接続孔)であって、前記各コンタクトホールの下端がこれに対応する前記各層のインダクタにそれぞれ位置し、前記各コンタクトホースの上端が前記最上層の層間絶縁膜の表面に位置し、前記複数層の層間絶縁膜を上方向に貫通する前記複数のコンタクトホールを形成し、前記各コンタクトホール中にメタルをそれぞれ充填して複数のプラグを形成する。前記電極形成工程では、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極を形成する。更に、前記パッシベーション膜・開口形成工程では、前記複数の電極を含む前記最上層の層間絶縁膜の全面にパッシベーション膜を形成し、前記パッシベーション膜における前記複数の電極箇所をエッチングにより開口して前記複数の電極を露出させる。

【0014】

本発明のインダクタチップの実装方法では、前記インダクタチップを用い、前記基板をバックグラインド(底面研磨)により薄膜化し、プリント基板を含む他の基板に埋め込むようにしている。

【発明の効果】

【0015】

請求項1〜7に係る発明によれば、次のような効果を有している。

(A) 積層構造のインダクタチップにより、複数のインダクタを有するアレイを容易に製造できる。しかも、基板をバックグラインドにより薄型化することにより、インダクタチップの全体の厚さを例えば数十μmという薄型に容易にできる。

【0016】

(B) 複数のプラグの位置が重ならないように、各層のインダクタのパターンをずらした状態で積層し、それらのプラグを介して複数の電極に接続する構造であるので、各電極を離間した状態で容易に配置形成でき、製造も容易である。

【0017】

請求項8に係る発明によれば、次のような効果を有している。

(C) 基板をバックグラインドにより薄型化するので、インダクタチップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型のインダクタチップを実装する場合、複数のインダクタを一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【0018】

(D) 各電極は離間した状態で配置されているので、実装時における外部回路との結線作業が容易になり、より実装コストを削減できる。従って、例えば積層構造の薄型の部品内蔵プリント基板等を容易に製造できる。

【発明を実施するための最良の形態】

【0019】

本発明のインダクタチップは、シリコン基板等の基板と、アルミニュウム等で形成され、前記基板上において上下に離隔して配置された複数層の薄膜のインダクタと、前記各層毎のインダクタをそれぞれ被覆する複数層の層間絶縁膜と、タングステン(W)等で形成され、横方向に離隔して配置されて前記各層のインダクタにそれぞれ接続された複数のプラグと、アルミニュウム等で形成され、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極とを備えている。

【0020】

ここで、前記各層のインダクタは、スパイラル状パターンをそれぞれ有し、前記各パターンが前記各層毎に横方向にずらして配置されている。例えば、前記各パターンは、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、配置されている。前記複数のプラグは、前記複数層の層間絶縁膜を上方向に貫通して前記最上層の層間絶縁膜の表面に引き出されている。

【実施例1】

【0021】

(構造)

図1(a)、(b)は本発明の実施例1を示すインダクタチップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。

【0022】

このインダクタチップは、全体の厚さが例えば100μm以下、好ましくは50μm以下の積層構造をしており、底面がバックグラインドにより薄膜化(例えば、100μm以下、好ましくは50μm以下に薄膜化)される基板(例えば、シリコン基板、ガラス基板、アルミナ基板、ガラス・アルミナ基板等)1を有している。基板1上には保護用のプロテクト絶縁膜(例えば、プロテクト酸化膜等)2が被着され、この絶縁膜2上に、複数層(例えば、4層)の角形のスパイラル状インダクタ3−1〜3−4が、p−TEOS等を用いて形成された層間絶縁膜4−1〜4−4を介して積層されている。各層のスパイラル状インダクタ3−1〜3−4は、フォトリソグラフィ等により形成された同一形状の薄膜メタルパターン(例えば、薄膜アルミニュウムパターン、薄膜銅パターン等)からなる積層構造となっている。この積層構造では、絶縁膜2上に1層目のインダクタ3−1が形成されて1層目の層間絶縁膜4−1により覆われ、プラグ位置が重ならないように、その上に所定角度(例えば、90°)右回転して2層目のインダクタ3−2が形成されて2層目の層間絶縁膜4−2により覆われ、プラグ位置が重ならないように、その上に180°右回転して3層目のインダクタ3−3が形成されて3層目の層間絶縁膜4−32により覆われ、更に、プラグ位置が重ならないように、その上に270°右回転して4層目のインダクタ3−4が形成されて4層目の層間絶縁膜4−4により覆われている。

【0023】

各層のインダクタ3−1〜3−4の初端部と終端部とに位置する垂直方向には、複数のコンタクトホール5が形成され、これらのコンタクトホール5中に結線用メタル(例えば、タングステン等)が埋設されて複数のプラグ6が形成されている。複数のプラグ6の上端面は、4層目の層間絶縁膜4−4の表面と同一面に位置しており、それらのプラグ6の上端面上に、メタル(例えば、アルミニュウム等)からなる複数の電極(例えば、パッド7)7−1a,7−1b〜7−4a,7−4bが形成されている。

【0024】

図1(b)に示すように、パッド7−1aはプラグ6を介して1層目のインダクタ3−1の初端部に接続され、それと離間したパッド7−1bはプラグ6を介して1層目のインダクタ3−1の終端部に接続されている。同様に、パッド7−2aと7−2bは各プラグ6を介して2層目のインダクタ3−2の初端部と終端部に接続され、パッド7−3aと7−3bは各プラグ6を介して3層目のインダクタ3−3の初端部と終端部に接続され、パッド7−4aと7−4bは各プラグ6を介して4層目のインダクタ3−4の初端部と終端部に接続されている。4層目の層間絶縁膜4−4は、窒化膜(SiN)等の不活性化膜であるパッシベーション膜(以下「PV膜」という。)8により覆われ、このPV膜8における各パッド7−1a,7−1b〜7−4a,7−4b箇所のみに開口部9が形成されてその各パッド7−1a,7−1b〜7−4a,7−4bが露出している。

【0025】

(製造方法)

図2(a)、(b)〜図5(a)、(b)は、図1のインダクタチップの製造方法例を示す概略の工程図であり、図2(a)、(b)は1層目のインダクタ3−1箇所の平面図とその縦断面図、図3(a)、(b)は2層目のインダクタ3−2箇所の平面図とその縦断面図、図4(a)、(b)は3層目のインダクタ3−3箇所の平面図とその縦断面図、及び図5(a)、(b)は4層目のインダクタ3−4箇所の平面図とその縦断面図である。

【0026】

図1のインダクタチップは、例えば、以下のような工程(1)〜(5)により製造される。

【0027】

(1) 図2の工程

例えば、シリコンウェハ1Aの上に水蒸気を流しつつ加熱し、プロテククト酸化膜である絶縁膜2を形成する。その上にアルミニウムをスパッタリング法により全面に形成し、レジストを塗布し、UVキュア(紫外線熱処理)した後、露光機で露光し、現像し、エッチング装置によりエッチングを行って、所定間隔離れて配置された複数の1層目の角形スパイラル状インダクタ3−1を形成する。各1層目のインダクタ3−1は、左上の初端部3−1aから右回転方向に巻装され、終端部3−1bが中央左下に位置している。

【0028】

(2) 図3の工程

複数の1層目のインダクタ3−1を含む絶縁膜2の全面に、p−TEOSを用いて化学的気相成長法(以下「CVD法」という。)により1層目の層間絶縁膜4−1を形成し、その上に、図2と同様に、所定間隔離れた複数の2層目の角形スパイラル状インダクタ3−2を形成する。この際、各2層目のインダクタ3−2のパターンは、各1層目のインダクタ3−1のパターンに対して例えば右回りに90°回転させて形成する。そのため、各2層目のインダクタ3−2の初端部3−2aは右上に移動し、終端部3−2bが中央左上に移動している。

【0029】

(3) 図4の工程

複数の2層目のインダクタ3−2を含む1層目の層間絶縁膜4−1の全面に、p−TEOSを用いてCVD法により2層目の層間絶縁膜4−2を形成し、その上に、図2と同様に、所定間隔離れた複数の3層目の角形スパイラル状インダクタ3−3を形成する。この際、各3層目のインダクタ3−3のパターンは、各1層目のインダクタ3−1のパターンに対して例えば右回りに180°回転させて形成する。そのため、各3層目のインダクタ3−3の初端部3−3aは右下に移動し、終端部3−3bが中央右上に移動している。

【0030】

(4) 図5の工程

複数の3層目のインダクタ3−3を含む2層目の層間絶縁膜4−2の全面に、p−TEOSを用いてCVD法により3層目の層間絶縁膜4−3を形成し、その上に、図2と同様に、所定間隔離れた複数の4層目の角形スパイラル状インダクタ3−4を形成する。この際、各4層目のインダクタ3−4のパターンは、各1層目のインダクタ3−1のパターンに対して例えば右回りに270°回転させて形成する。そのため、各4層目のインダクタ3−4の初端部3−4aは左下に移動し、終端部3−4bが中央右下に移動している。

【0031】

(5) 図1の工程

複数の4層目のインダクタ3−4を含む3層目の層間絶縁膜4−3の全面に、CVD法により4層目の層間絶縁膜4−4を形成する。各層のインダクタ3−1〜3−4の初端部3−1a〜3−4aと終端部3−1b〜3−4bに、それぞれ垂直方向のコンタクトホール5を形成し、その中に、CVD法によりタングステンのフラグ6を埋め込む。そして、表面にあるタングステンを、化学的機械的研磨法(以下「CMP法」という。)により取り去る。次に、スパッタリング法により、全面にアルミニュウム膜を形成し、このアルミニュウム膜をフォトリソグラフィを用いて選択的にエッチングし、プラグ6の上にアルミニュウム膜からなる複数のパッド7を形成する。

【0032】

複数のパッド7を含む4層目の層間絶縁膜4−4上に、CVD法により、窒化膜からなるPV膜8を形成する。フォトリソグラフィにより、複数のパッド7上のPV膜8のみをエッチングして複数の開口部9を形成し、その複数のパッド7を露出させる。これにより、積層構造のインダクタ3−1〜3−4を有するインダクタアレイが形成できる。このインダクタアレイが形成されたシリコンウェハ1Aをバックグラインドして薄膜化し、ダイシング(切断)により個片化すれば、図1に示す積層構造のインダクタチップが得られる。

【0033】

このようにして製造されたインダクタチップは、例えば、実装時においてプリント基板等の上にダイスボンディング(固着)し、そのインダクタチップのパッド7−1a,7−1b〜7−4a,7−4bを必要な他の部品とワイヤボンディング(ワイヤ接続)等で結線することにより、所望の回路動作を行わせることができる。又、インダクタチップを基板内等に埋め込む際には、半田ボールや導電性ペースト等を用いて接続することもできる。

【0034】

(効果等)

本実施例1では、次の(a)〜(d)のような効果等を有している。

【0035】

(a) 積層構造のインダクタチップにより、複数のインダクタ3−1〜3−4を有するアレイを容易に製造できる。しかも、基板1をバックグラインドにより薄型化するので、インダクタチップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型のインダクタチップを使用する場合、複数のインダクタ3−1〜3−4を一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【0036】

(b) 複数のプラグ6の位置が重ならないように、各層のインダクタ3−1〜3−4のパターンを所定角度(例えば、90°)回転させた状態で積層し、これらを垂直方向に埋設したプラグ6を介してパッド7−1a,7−1b〜7−4a,7−4bに接続する構造であるので、各パッド7−1a,7−1b〜7−4a,7−4bを離間した状態で容易に配置形成でき、製造も容易である。しかも、実装時における外部回路との結線作業が容易になり、より実装コストを削減できる。

【0037】

(c) インダクタ3−1〜3−4の積層数、或いはインダクタパターンの回転方向や回転角度は、図示のものに限定されず、任意の積層数や角度でよく、例えば、インダクタ3−1〜3−4の積層数等に応じてインダクタパターンの回転角度を適宜設定すればよい。又、各インダクタ3−1〜3−4のパターンは、円形スパイラル状等の他の形状にしてもよい。

【0038】

(d) 使用材料や製造工程等は、種々変更できる。例えば、基板1としてガラス基板、アルミナ基板、或いはガラス・アルミナ基板等、保護用の絶縁膜2として窒化膜等を使用してもよい。スパイラル状インダクタ3−1〜3−4やパッド7として使用しているアルミニュウム箔は、エッチングが容易であるが、これ以外の銅箔等を使用してもよい。銅箔は、エッチングがしづらいので、電気メッキ法等で形成することになるが、導電性がアルミニュウムよりも良い。又、層間絶縁膜4−1〜4−4としてp−TEOS以外の材料、プラグ6としてアルミニュウム等、PV膜8として樹脂等を使用してもよく、それに応じて製造方法を適宜変更すればよい。

【実施例2】

【0039】

(構造・製造方法)

図6(a)、(b)は本発明の実施例2を示すインダクタチップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。この図6において、実施例1を示す図1中の要素と共通の要素には共通の符号が付されている。

【0040】

実施例1では、各層の角形スパイラル状インダクタ3−1〜3−4を90℃ずつ右回転させて形成し、複数のプラグ6の位置が重ならないようにしているが、本実施例2では、各層の角形スパイラル状インダクタ3−1〜3−4の形成位置を任意の方向に平行移動することにより、複数のプラグ6の位置が重ならないようにしている点のみが異なる。

【0041】

図6(b)の平面図では、各層のインダクタ3−1〜3−4が平行移動して形成され、これに接続されたパッド7−1a,7−1b〜7−4a,7−4bがチップ表面の片側のみに配置された例が示されている。その他の構成や、製造方法は、実施例1とほぼ同様である。

【0042】

(効果等)

本実施例2では、実施例1の(a)〜(d)の効果等を有する他に、更に次の(e)のような効果等がある。

【0043】

(e) 図7は、図6(a)の他の平面図である。

本実施例2では、実施例1のように各層のインダクタ3−1〜3−4を回転させないで平行移動しているので、これに接続されるパッド7−1a,7−1b〜7−4a,7−4bをインダクタチップ表面の片側に局在させることができる。そのため、図7に示すように、インダクタチップ表面の他の片側に空き領域を設けることができ、この空き領域に他の小型のチップ等の部品10を積層することができる。このように、本実施例2では、複数のインダクタ3−1〜3−4を積層することにより、高密度実装が可能になり、その上、他のチップ等の部品10を積層することが可能になるので、更なる高密度化を達成できる。

【実施例3】

【0044】

図8は、本発明の実施例3を示すインダクタチップを用いた部品内蔵プリント基板の概略の断面図である。

【0045】

この図8では、上記実施例1、2の薄型のインダクタチップ20等をプリント基板に内蔵させた部品内蔵プリント基板の実装例が示されている。この部品内蔵プリント基板の製造では、例えば、薄型のインダクタチップ20の他に、予め薄型の抵抗チップ21、コンデンサチップ22、及び半導体集積回路チップ(以下「LSIチップ」という。)23等の薄型部品を製造しておく。そして、プリント基板本体24上に、例えば、コンデンサチップ22及びLSIチップ23等を固着し、アルミニュウム箔、銅箔等の1層目配線層25−1により結線し、これらを樹脂絶縁膜26により被覆して1層目を形成する。更に、1層目の上に、インダクタチップ20及び抵抗チップ21等を固着し、1層目配線層25−1にビアホール27を介して接続された2層目配線層25−2によって結線し、これらを樹脂絶縁膜26により被覆して2層目を形成する等すれば、図8のような積層構造の薄型の部品内蔵プリント基板を容易に製造できる。

【0046】

インダクタチップ20等の他の実装例としては、例えば、プリント基板本体24内に図示しない収納凹部を形成し、この収納凹部内にインダクタチップ20等を搭載して樹脂絶縁膜26等により被覆する等、種々の実装形態が可能である。

【図面の簡単な説明】

【0047】

【図1】本発明の実施例1を示すインダクタチップの概略の構成図である。

【図2】図1の1層目のインダクタ3−1箇所の平面図とその縦断面図である。

【図3】図1の2層目のインダクタ3−2箇所の平面図とその縦断面図である。

【図4】図1の3層目のインダクタ3−3箇所の平面図とその縦断面図である。

【図5】図1の4層目のインダクタ3−4箇所の平面図とその縦断面図である。

【図6】本発明の実施例2を示すインダクタチップの概略の構成図である。

【図7】図6(a)の他の平面図である。

【図8】本発明の実施例3を示す部品内蔵プリント基板の概略の断面図である。

【符号の説明】

【0048】

1 基板

1A シリコンウェハ

2 プロテクト酸化膜

3−1〜3−4 インダクタ

4−1〜4−4 層間絶縁膜

5 コンタクトホール

6 プラグ

7 パッド

8 パッシベーション膜(PV膜)

9 開口部

10 部品

20 インダクタチップ

24 プリント基板本体

【特許請求の範囲】

【請求項1】

基板と、

前記基板上において上下に離隔して配置された複数層の薄膜のインダクタであって、前記各層のインダクタは所定形状のパターンを有し、前記各パターンが前記各層毎に横方向にずらして配置された前記複数層のインダクタと、

前記各層毎のインダクタをそれぞれ被覆する複数層の層間絶縁膜と、

横方向に離隔して配置されて前記各層のインダクタにそれぞれ接続された複数のプラグであって、前記複数層の層間絶縁膜を上方向に貫通して前記最上層の層間絶縁膜の表面に引き出された前記複数のプラグと、

前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極と、

を備えたことを特徴とするインダクタチップ。

【請求項2】

請求項1記載のインダクタチップにおいて、

前記各パターンは、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、配置されていることを特徴とするインダクタチップ。

【請求項3】

請求項1又は2記載のインダクタチップにおいて、

前記基板と前記最下層のインダクタとの間に、プロテクト絶縁膜が形成され、

前記最上層の層間絶縁膜は、前記複数の電極を露出させた状態でパッシベーション膜により被覆されていることを特徴とするインダクタチップ。

【請求項4】

請求項1〜3のいずれか1項に記載のインダクタチップにおいて、

前記基板は、シリコン基板、ガラス基板、アルミナ基板、又は、ガラス・アルミナ基板のいずれか1つにより構成され、

前記インダクタ及び/又は前記電極は、アルミニュウム又は銅により形成されていることを特徴とするインダクタチップ。

【請求項5】

基板上にプロテクト絶縁膜を形成するプロテクト絶縁膜形成工程と、

前記プロテクト絶縁膜上に下層のメタル膜を形成し、前記下層のメタル膜をパターニング及びエッチングして、下層のスパイラル状パターンを有する下層の薄膜のインダクタを形成する下層のインダクタ形成工程と、

前記下層のインダクタを含む前記プロテクト絶縁膜の全面に、下層の層間絶縁膜を形成する下層の層間絶縁膜形成工程と、

前記下層の層間絶縁膜上に上層のメタル膜を形成し、前記上層のメタル膜をパターニング及びエッチングして、前記下層のスパイラル状パターンに対して横方向にずれて配置された上層のスパイラル状薄膜パターンを有する上層の薄膜のインダクタを形成する上層のインダクタ形成処理と、前記上層のインダクタを含む前記下層の層間絶縁膜の全面に、上層の層間絶縁膜を形成する上層の層間絶縁膜形成処理と、を交互に繰り返す上層のインダクタ・層間絶縁膜形成工程と、

横方向に離隔して開孔される複数のコンタクトホールであって、前記各コンタクトホールの下端がこれに対応する前記各層のインダクタにそれぞれ位置し、前記各コンタクトホースの上端が前記最上層の層間絶縁膜の表面に位置し、前記複数層の層間絶縁膜を上方向に貫通する前記複数のコンタクトホールを形成し、前記各コンタクトホール中にメタルをそれぞれ充填して複数のプラグを形成するプラグ形成工程と、

前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極を形成する電極形成工程と、

前記複数の電極を含む前記最上層の層間絶縁膜の全面にパッシベーション膜を形成し、前記パッシベーション膜における前記複数の電極箇所をエッチングにより開口して前記複数の電極を露出させるパッシベーション膜・開口形成工程と、

を有することを特徴とするインダクタチップの製造方法。

【請求項6】

請求項5記載のインダクタチップの製造方法において、

前記各層のスパイラル状パターンは、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、形成されることを特徴とするインダクタチップの製造方法。

【請求項7】

請求項5又は6記載のインダクタチップの製造方法において、

前記基板として、シリコン基板、ガラス基板、アルミナ基板、又は、ガラス・アルミナ基板のいずれか1つを用い、

前記インダクタ及び/又は前記電極は、アルミニュウム又は銅により形成することを特徴とするインダクタチップの製造方法。

【請求項8】

請求項1〜4のいずれか1項に記載のインダクタチップを用い、

前記基板をバックグラインドにより薄膜化し、プリント基板を含む他の基板に埋め込むことを特徴とするインダクタチップの実装方法。

【請求項1】

基板と、

前記基板上において上下に離隔して配置された複数層の薄膜のインダクタであって、前記各層のインダクタは所定形状のパターンを有し、前記各パターンが前記各層毎に横方向にずらして配置された前記複数層のインダクタと、

前記各層毎のインダクタをそれぞれ被覆する複数層の層間絶縁膜と、

横方向に離隔して配置されて前記各層のインダクタにそれぞれ接続された複数のプラグであって、前記複数層の層間絶縁膜を上方向に貫通して前記最上層の層間絶縁膜の表面に引き出された前記複数のプラグと、

前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極と、

を備えたことを特徴とするインダクタチップ。

【請求項2】

請求項1記載のインダクタチップにおいて、

前記各パターンは、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、配置されていることを特徴とするインダクタチップ。

【請求項3】

請求項1又は2記載のインダクタチップにおいて、

前記基板と前記最下層のインダクタとの間に、プロテクト絶縁膜が形成され、

前記最上層の層間絶縁膜は、前記複数の電極を露出させた状態でパッシベーション膜により被覆されていることを特徴とするインダクタチップ。

【請求項4】

請求項1〜3のいずれか1項に記載のインダクタチップにおいて、

前記基板は、シリコン基板、ガラス基板、アルミナ基板、又は、ガラス・アルミナ基板のいずれか1つにより構成され、

前記インダクタ及び/又は前記電極は、アルミニュウム又は銅により形成されていることを特徴とするインダクタチップ。

【請求項5】

基板上にプロテクト絶縁膜を形成するプロテクト絶縁膜形成工程と、

前記プロテクト絶縁膜上に下層のメタル膜を形成し、前記下層のメタル膜をパターニング及びエッチングして、下層のスパイラル状パターンを有する下層の薄膜のインダクタを形成する下層のインダクタ形成工程と、

前記下層のインダクタを含む前記プロテクト絶縁膜の全面に、下層の層間絶縁膜を形成する下層の層間絶縁膜形成工程と、

前記下層の層間絶縁膜上に上層のメタル膜を形成し、前記上層のメタル膜をパターニング及びエッチングして、前記下層のスパイラル状パターンに対して横方向にずれて配置された上層のスパイラル状薄膜パターンを有する上層の薄膜のインダクタを形成する上層のインダクタ形成処理と、前記上層のインダクタを含む前記下層の層間絶縁膜の全面に、上層の層間絶縁膜を形成する上層の層間絶縁膜形成処理と、を交互に繰り返す上層のインダクタ・層間絶縁膜形成工程と、

横方向に離隔して開孔される複数のコンタクトホールであって、前記各コンタクトホールの下端がこれに対応する前記各層のインダクタにそれぞれ位置し、前記各コンタクトホースの上端が前記最上層の層間絶縁膜の表面に位置し、前記複数層の層間絶縁膜を上方向に貫通する前記複数のコンタクトホールを形成し、前記各コンタクトホール中にメタルをそれぞれ充填して複数のプラグを形成するプラグ形成工程と、

前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極を形成する電極形成工程と、

前記複数の電極を含む前記最上層の層間絶縁膜の全面にパッシベーション膜を形成し、前記パッシベーション膜における前記複数の電極箇所をエッチングにより開口して前記複数の電極を露出させるパッシベーション膜・開口形成工程と、

を有することを特徴とするインダクタチップの製造方法。

【請求項6】

請求項5記載のインダクタチップの製造方法において、

前記各層のスパイラル状パターンは、前記各層毎に回転角度をずらして、又は、前記各層毎に平行移動によりずらして、形成されることを特徴とするインダクタチップの製造方法。

【請求項7】

請求項5又は6記載のインダクタチップの製造方法において、

前記基板として、シリコン基板、ガラス基板、アルミナ基板、又は、ガラス・アルミナ基板のいずれか1つを用い、

前記インダクタ及び/又は前記電極は、アルミニュウム又は銅により形成することを特徴とするインダクタチップの製造方法。

【請求項8】

請求項1〜4のいずれか1項に記載のインダクタチップを用い、

前記基板をバックグラインドにより薄膜化し、プリント基板を含む他の基板に埋め込むことを特徴とするインダクタチップの実装方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−186037(P2006−186037A)

【公開日】平成18年7月13日(2006.7.13)

【国際特許分類】

【出願番号】特願2004−376660(P2004−376660)

【出願日】平成16年12月27日(2004.12.27)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(596091004)株式会社マルチ (18)

【出願人】(899000068)学校法人早稲田大学 (602)

【出願人】(502273096)株式会社関東学院大学表面工学研究所 (52)

【Fターム(参考)】

【公開日】平成18年7月13日(2006.7.13)

【国際特許分類】

【出願日】平成16年12月27日(2004.12.27)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(596091004)株式会社マルチ (18)

【出願人】(899000068)学校法人早稲田大学 (602)

【出願人】(502273096)株式会社関東学院大学表面工学研究所 (52)

【Fターム(参考)】

[ Back to top ]