インバータ装置

【課題】

パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを効果的に回避する。

【解決手段】

高電位側のIGBT121及び低電位側のIGBT123を有するIGBTモジュール113と、高電位側IGBT121及びIGBT123を駆動する信号を出力するゲート駆動IC101と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と低電位側のIGBT123のコレクタ端子117との間に設けられた容量128と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と高電位側IGBT121のエミッタ端子116との間に設けられた抵抗127と、を有するインバータ装置。

パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを効果的に回避する。

【解決手段】

高電位側のIGBT121及び低電位側のIGBT123を有するIGBTモジュール113と、高電位側IGBT121及びIGBT123を駆動する信号を出力するゲート駆動IC101と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と低電位側のIGBT123のコレクタ端子117との間に設けられた容量128と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と高電位側IGBT121のエミッタ端子116との間に設けられた抵抗127と、を有するインバータ装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、インバータ装置に関する。

【背景技術】

【0002】

一般にハイブリッド自動車のモータ駆動用などのインバータ装置にはIGBTモジュールなどのパワーモジュールが用いられ、42V〜600Vの主回路電圧が印加されている。このパワーモジュールの駆動回路は「ゲート駆動回路」と呼ばれ、IGBTのソース端子やエミッタ端子のパワーグランド電位を基準として、高電位側(P側)と低電位側(N側)の駆動回路にはそれぞれ独立に絶縁された駆動電源が供給されている。

【0003】

パワーモジュールのゲート駆動回路にはゲート駆動ICを用いることが知られている(例えば特許文献1参照)。ゲート駆動ICはプリント基板上に搭載され、その基準電位はパワーモジュールの低電位側トランジスタの基準電位と同じになっている。

【0004】

ゲート駆動ICを動作させると、IGBTモジュール内の寄生インダクタンスなどの影響で、ゲート駆動ICの高電位側IGBTを駆動する信号の基準電位端子の電位が、ゲート駆動ICの基準電位端子の電位よりも低くなる逆サージ現象(アンダーシュート)が起こる場合がある。このとき、サージ量が大きい(〜30V)とゲート駆動ICが誤動作してしまう場合があり、この問題を解決するために、ゲート駆動ICの高電位側信号の基準電位端子とゲート駆動ICの基準電位端子間にクランプダイオードを挿入するものが知られている。

【0005】

【特許文献1】特開2004−304929号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記従来技術のクランプダイオードで逆サージを完全にクランプするには、ダイオードの通電能力としてIGBTと同程度の通電能力が必要であり、プリント基板上に搭載できる一般的なダイオードでは電流は数Aしか流せず、ハイブリッド自動車などを用途とするインバータのようにIGBTに数100Aの電流を流すような場合にはクランプの効果は不充分であった。

【0007】

本発明の目的は、パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを効果的に回避することである。

【課題を解決するための手段】

【0008】

本発明は、高電位側トランジスタ及び低電位側トランジスタを有するパワーモジュールと、高電位側トランジスタ及び低電位側トランジスタを駆動する信号を出力するゲート駆動ICと、ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と低電位側トランジスタのコレクタ端子との間に設けられた容量と、ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と高電位側トランジスタのエミッタ端子との間に設けられたインピーダンスと、を有するインバータ装置である。

【発明の効果】

【0009】

本発明によれば、パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを回避することができる。

【発明を実施するための最良の形態】

【0010】

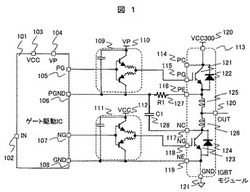

図1は、本発明の一実施形態をなすインバータ装置のゲート駆動回路を示す。

【0011】

ゲート駆動IC101が外部バッファ109及び111を介してIGBTモジュール113を駆動する。ゲート駆動IC101には電源端子VCC103,GND108間及びVP104,PGND106間に電源電圧15Vがかけられている。電源端子VCC103,GND108はICの電源/グランド端子かつ低電位側IGBT駆動信号用電源/基準電位端子である。また電源端子VP104,PGND106は高電位側IGBT駆動信号用電源/基準電位端子である。これら電源/基準電位端子VCC103,GND108とVP104,PGND106は絶縁されている。

【0012】

ゲート駆動IC101の入力信号端子IN102に入力信号を与えると高電位側IGBT駆動信号が端子PG105,PGND106間に出力され、低電位側IGBT駆動信号が端子NG107,GND108間に出力される。

【0013】

高電位側IGBT駆動信号は外部バッファ109を介してIGBTモジュール113の高電位側IGBTのゲート端子PG115とエミッタ端子PE116間に入力される。外部バッファ109の電源端子110はゲート駆動IC101の電源端子VP104と接続されており、グランド端子は高電位側IGBT駆動信号用基準電位端子PGND106に接続されている。

【0014】

また低電位側IGBT駆動信号は外部バッファ111を介してIGBTモジュール113の低電位側IGBTのゲート端子NG118とエミッタ端子NE119間に入力される。外部バッファ111の電源端子112はゲート駆動IC101の電源端子VCC103と接続されており、グランド端子はゲート駆動ICのグランド端子GND108に接続されている。

【0015】

IGBTモジュール113は高電位側電源端子VCC300端子120とGND端子121間に300Vがかけられている。IGBTモジュール113に駆動信号が入力されるとIGBT121及び123が駆動され、出力端子OUT120に電力が出力される。

【0016】

IGBTモジュール113のIGBT121及び123のコレクタ−エミッタ間にはそれぞれダイオード122及び124が設置されている。これはモータなどの誘導負荷を有するインバータにおいて、通電時に誘導負荷に蓄えられたエネルギーをIGBTがターン・オフしたときに電流として放出させるためのもので、フリー・ホイール・ダイオード(FWD)と呼ばれるものである。

【0017】

従来、ゲート駆動ICの高電位側基準電位端子PGND106と低電位側基準電位端子GND108の間にクランプダイオード200を入れていた。これは次の理由による。ゲート駆動IC101を動作させると、IGBTモジュール113内の寄生インダクタンス125,126などの影響で、ゲート駆動IC101の高電位側IGBTを駆動する信号の基準電位端子PGND106の電位が基準電位端子GND108の電位よりも低くなる逆サージ現象(アンダーシュート)が起こる場合がある。このとき、サージ量が大きい(〜30V)とゲート駆動IC101が誤動作してしまう場合がある。この問題を対策するためにゲート駆動ICの高電位側信号の基準電位端子PGNDとICの基準電位端子GND間にクランプダイオードを挿入していた。

【0018】

しかし、逆サージを完全にクランプするにはダイオードの通電能力としてIGBTと同程度の通電能力が必要となり、プリント基板上に搭載できる一般的なダイオードでは電流は数Aしか流せず、ハイブリッド自動車用途のインバータのようにIGBTに数100Aの電流を流すような場合にはクランプの効果は不充分であった。

【0019】

ここで従来例にあったダイオードを無くし、ゲート駆動IC101のPGND端子106とIGBTモジュール113の低電位側IGBT123のコレクタ端子NC117との間に容量(C1)128を設け、ゲート駆動ICのPGND端子106と高電位側IGBTのエミッタ端子PE116との間にインピーダンスとしての抵抗(R1)127を設けた。そして、高電位側IGBT駆動信号用外部バッファ109の基準電位(グランド)はゲート駆動IC101のPGND端子106と接続した。

【0020】

なお、R1及びC1は式1を満足するように設定されている。

【0021】

R1×C1≫√(Lec×C1) (式1)

ただしLecは前記PE端子116と前記NC端子117との間のインダクタンスである。ここでLecは10nH、C1は68nF、抵抗R1は5.8Ωとする。LecとC1による共振が起こる周波数は1/2π√(Lec・C1)、R1とC1でフィルタリングできる周波数は1/2πR1・C1なので、(式1)が成り立つ時、1/2πR1・C1≪1/2π√(Lec・C1)となり、共振周波数をフィルタリングする事ができる。

【0022】

以上により、高電位側IGBT121のエミッタ端子PE116と低電位側IGBT123のコレクタ端子NC117の間において容量(C1)128によってPGNDはNCとAC的にカップリングされ、抵抗(R1)127によってPGND端子106とPE端子116間の接続が弱まる。これによりPE−NC間の逆サージがPGND−NC間に伝わりにくくなる。なお、逆サージが現れるゲート駆動ICの高電位側IGBT121を駆動する信号の基準電位端子PGND106とゲート駆動IC101の基準電位端子GND108の区間のうち、低電位側IGBT123のコレクタ端子NC117とゲート駆動IC101の基準電位端子GND108の区間は既にIGBTモジュール113内においてフリー・ホイール・ダイオード124が入っておりクランプされる。そこで残りの高電位側IGBTのエミッタ端子PEと低電位側IGBTのコレクタ端子NCの間に着眼する。容量によってPGNDはNCとAC的にカップリングされる。そしてインピーダンスによってPGNDとPE間の接続が弱まるとともにインピーダンスに抵抗成分を含ませた場合には寄生インダクタンスと前記容量によるLC発振が防止(ダンピング)される。これによりPE−NC間の逆サージが伝わりにくくなり、PGND−GND間の逆サージが回避される。

【0023】

図2は本実施形態において逆サージをシミュレーションした結果波形である。また図3は従来例において逆サージをシミュレーションした結果波形である。図3ではPGND−GND間逆サージが−25V程度出ているのに対して、図2ではPGND−GND間逆サージがほとんど出ていない。

【0024】

また図4は本実施形態の外部バッファ回路を示す図である。図4の外部バッファ回路109はバイポーラトランジスタによるエミッタフォロア型のプッシュプル回路となっている。npnトランジスタ505のコレクタに電源端子501が接続され、エミッタは抵抗506の一方の端子に接続されている。抵抗506の他方の端子は抵抗508の一方に接続され、他方はpnpトランジスタ507のエミッタに接続されている。pnpトランジスタ507のコレクタは外部バッファ回路のグランド端子502に接続されている。npnトランジスタ505及びpnpトランジスタ507のベースは外部バッファ回路109の入力端子503に接続されている。また抵抗506と抵抗508の接点は外部バッファ回路109の出力端子504に接続されている。入力端子503に入った信号はバッファリングされて出力端子504に出力される。また容量509はバイパスコンデンサで、外部バッファ109の電源501/グランド502間の電源環境を安定化させている。

【0025】

図5は、本発明の他の実施形態をなすインバータ装置のゲート駆動回路を示す。以下に示す事項以外は、図1の実施形態と同様である。

【0026】

図1のゲート駆動回路にゲートクランプ回路601及び604が装備されている。ゲートクランプ回路601はNORゲート602とN型MOSFET603から構成されている。このNORゲート602の2つの入力のうち、一つはゲート駆動IC101の高電位側駆動信号端子105に、そして他方は高電位側IGBT121のゲート端子115に接続され、出力はN型MOSFET603のゲート端子に接続されている。N型MOSFET603のドレイン端子は高電位側IGBT121のゲート端子115に、そしてソース端子は高電位側IGBT121のエミッタ端子116に接続されている。

【0027】

そしてゲート駆動IC101の高電位側駆動信号と高電位側IGBT121のゲート電圧の両方がLレベルになるとNORゲート602はHレベルを出力し、N型MOSFET603をオンさせて高電位側IGBT121のゲート端子115とエミッタ端子116を短絡する。これにより高電位側IGBT121のゲート端子をLレベルにしている間にコレクタ−エミッタ間電圧が変動しても、ゲート−コレクタ間寄生容量によるゲート電圧のカップリングノイズを小さく抑える事ができる。

【0028】

なお、ゲートクランプ回路604は、高電位側1GBT121に対するゲートクランプ回路601と同様に、低電位側IGBT123に対して作用するものである。

【0029】

以上の実施形態においては、ゲート駆動ICの高電位側駆動信号の基準電位端子PGNDとIGBTモジュールの低電位側IGBTのコレクタ端子NC端子間に容量を設け、またIGBTモジュールの高電位側IGBTのエミッタ端子PEとPGNDの間にインピーダンスを設けるので、PGNDは容量によってNCとAC的にカップリングされ、インピーダンスによってPGNDとPE間の接続が弱まるとともにインピーダンスに抵抗成分を含ませた場合には寄生インダクタンスと前記容量によるLC発振が防止(ダンピング)される。これによりPE−NC間の逆サージが伝わりにくくなり、PGND−GND間の逆サージを回避する事ができる。

【図面の簡単な説明】

【0030】

【図1】本発明の一実施形態をなすインバータ装置のゲート駆動回路を示す。

【図2】本発明による逆サージをシミュレーションした波形を示す。

【図3】従来技術による逆サージをシミュレーションした波形を示す。

【図4】図1の外部バッファ回路を示す。

【図5】本発明の他の実施形態をなすインバータ装置のゲート駆動回路を示す。

【符号の説明】

【0031】

101 ゲート駆動IC

106 高電位側IGBT駆動信号用基準電位端子

113 IGBTモジュール

121,123 IGBT

127 抵抗

128 容量

【技術分野】

【0001】

本発明は、インバータ装置に関する。

【背景技術】

【0002】

一般にハイブリッド自動車のモータ駆動用などのインバータ装置にはIGBTモジュールなどのパワーモジュールが用いられ、42V〜600Vの主回路電圧が印加されている。このパワーモジュールの駆動回路は「ゲート駆動回路」と呼ばれ、IGBTのソース端子やエミッタ端子のパワーグランド電位を基準として、高電位側(P側)と低電位側(N側)の駆動回路にはそれぞれ独立に絶縁された駆動電源が供給されている。

【0003】

パワーモジュールのゲート駆動回路にはゲート駆動ICを用いることが知られている(例えば特許文献1参照)。ゲート駆動ICはプリント基板上に搭載され、その基準電位はパワーモジュールの低電位側トランジスタの基準電位と同じになっている。

【0004】

ゲート駆動ICを動作させると、IGBTモジュール内の寄生インダクタンスなどの影響で、ゲート駆動ICの高電位側IGBTを駆動する信号の基準電位端子の電位が、ゲート駆動ICの基準電位端子の電位よりも低くなる逆サージ現象(アンダーシュート)が起こる場合がある。このとき、サージ量が大きい(〜30V)とゲート駆動ICが誤動作してしまう場合があり、この問題を解決するために、ゲート駆動ICの高電位側信号の基準電位端子とゲート駆動ICの基準電位端子間にクランプダイオードを挿入するものが知られている。

【0005】

【特許文献1】特開2004−304929号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記従来技術のクランプダイオードで逆サージを完全にクランプするには、ダイオードの通電能力としてIGBTと同程度の通電能力が必要であり、プリント基板上に搭載できる一般的なダイオードでは電流は数Aしか流せず、ハイブリッド自動車などを用途とするインバータのようにIGBTに数100Aの電流を流すような場合にはクランプの効果は不充分であった。

【0007】

本発明の目的は、パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを効果的に回避することである。

【課題を解決するための手段】

【0008】

本発明は、高電位側トランジスタ及び低電位側トランジスタを有するパワーモジュールと、高電位側トランジスタ及び低電位側トランジスタを駆動する信号を出力するゲート駆動ICと、ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と低電位側トランジスタのコレクタ端子との間に設けられた容量と、ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と高電位側トランジスタのエミッタ端子との間に設けられたインピーダンスと、を有するインバータ装置である。

【発明の効果】

【0009】

本発明によれば、パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを回避することができる。

【発明を実施するための最良の形態】

【0010】

図1は、本発明の一実施形態をなすインバータ装置のゲート駆動回路を示す。

【0011】

ゲート駆動IC101が外部バッファ109及び111を介してIGBTモジュール113を駆動する。ゲート駆動IC101には電源端子VCC103,GND108間及びVP104,PGND106間に電源電圧15Vがかけられている。電源端子VCC103,GND108はICの電源/グランド端子かつ低電位側IGBT駆動信号用電源/基準電位端子である。また電源端子VP104,PGND106は高電位側IGBT駆動信号用電源/基準電位端子である。これら電源/基準電位端子VCC103,GND108とVP104,PGND106は絶縁されている。

【0012】

ゲート駆動IC101の入力信号端子IN102に入力信号を与えると高電位側IGBT駆動信号が端子PG105,PGND106間に出力され、低電位側IGBT駆動信号が端子NG107,GND108間に出力される。

【0013】

高電位側IGBT駆動信号は外部バッファ109を介してIGBTモジュール113の高電位側IGBTのゲート端子PG115とエミッタ端子PE116間に入力される。外部バッファ109の電源端子110はゲート駆動IC101の電源端子VP104と接続されており、グランド端子は高電位側IGBT駆動信号用基準電位端子PGND106に接続されている。

【0014】

また低電位側IGBT駆動信号は外部バッファ111を介してIGBTモジュール113の低電位側IGBTのゲート端子NG118とエミッタ端子NE119間に入力される。外部バッファ111の電源端子112はゲート駆動IC101の電源端子VCC103と接続されており、グランド端子はゲート駆動ICのグランド端子GND108に接続されている。

【0015】

IGBTモジュール113は高電位側電源端子VCC300端子120とGND端子121間に300Vがかけられている。IGBTモジュール113に駆動信号が入力されるとIGBT121及び123が駆動され、出力端子OUT120に電力が出力される。

【0016】

IGBTモジュール113のIGBT121及び123のコレクタ−エミッタ間にはそれぞれダイオード122及び124が設置されている。これはモータなどの誘導負荷を有するインバータにおいて、通電時に誘導負荷に蓄えられたエネルギーをIGBTがターン・オフしたときに電流として放出させるためのもので、フリー・ホイール・ダイオード(FWD)と呼ばれるものである。

【0017】

従来、ゲート駆動ICの高電位側基準電位端子PGND106と低電位側基準電位端子GND108の間にクランプダイオード200を入れていた。これは次の理由による。ゲート駆動IC101を動作させると、IGBTモジュール113内の寄生インダクタンス125,126などの影響で、ゲート駆動IC101の高電位側IGBTを駆動する信号の基準電位端子PGND106の電位が基準電位端子GND108の電位よりも低くなる逆サージ現象(アンダーシュート)が起こる場合がある。このとき、サージ量が大きい(〜30V)とゲート駆動IC101が誤動作してしまう場合がある。この問題を対策するためにゲート駆動ICの高電位側信号の基準電位端子PGNDとICの基準電位端子GND間にクランプダイオードを挿入していた。

【0018】

しかし、逆サージを完全にクランプするにはダイオードの通電能力としてIGBTと同程度の通電能力が必要となり、プリント基板上に搭載できる一般的なダイオードでは電流は数Aしか流せず、ハイブリッド自動車用途のインバータのようにIGBTに数100Aの電流を流すような場合にはクランプの効果は不充分であった。

【0019】

ここで従来例にあったダイオードを無くし、ゲート駆動IC101のPGND端子106とIGBTモジュール113の低電位側IGBT123のコレクタ端子NC117との間に容量(C1)128を設け、ゲート駆動ICのPGND端子106と高電位側IGBTのエミッタ端子PE116との間にインピーダンスとしての抵抗(R1)127を設けた。そして、高電位側IGBT駆動信号用外部バッファ109の基準電位(グランド)はゲート駆動IC101のPGND端子106と接続した。

【0020】

なお、R1及びC1は式1を満足するように設定されている。

【0021】

R1×C1≫√(Lec×C1) (式1)

ただしLecは前記PE端子116と前記NC端子117との間のインダクタンスである。ここでLecは10nH、C1は68nF、抵抗R1は5.8Ωとする。LecとC1による共振が起こる周波数は1/2π√(Lec・C1)、R1とC1でフィルタリングできる周波数は1/2πR1・C1なので、(式1)が成り立つ時、1/2πR1・C1≪1/2π√(Lec・C1)となり、共振周波数をフィルタリングする事ができる。

【0022】

以上により、高電位側IGBT121のエミッタ端子PE116と低電位側IGBT123のコレクタ端子NC117の間において容量(C1)128によってPGNDはNCとAC的にカップリングされ、抵抗(R1)127によってPGND端子106とPE端子116間の接続が弱まる。これによりPE−NC間の逆サージがPGND−NC間に伝わりにくくなる。なお、逆サージが現れるゲート駆動ICの高電位側IGBT121を駆動する信号の基準電位端子PGND106とゲート駆動IC101の基準電位端子GND108の区間のうち、低電位側IGBT123のコレクタ端子NC117とゲート駆動IC101の基準電位端子GND108の区間は既にIGBTモジュール113内においてフリー・ホイール・ダイオード124が入っておりクランプされる。そこで残りの高電位側IGBTのエミッタ端子PEと低電位側IGBTのコレクタ端子NCの間に着眼する。容量によってPGNDはNCとAC的にカップリングされる。そしてインピーダンスによってPGNDとPE間の接続が弱まるとともにインピーダンスに抵抗成分を含ませた場合には寄生インダクタンスと前記容量によるLC発振が防止(ダンピング)される。これによりPE−NC間の逆サージが伝わりにくくなり、PGND−GND間の逆サージが回避される。

【0023】

図2は本実施形態において逆サージをシミュレーションした結果波形である。また図3は従来例において逆サージをシミュレーションした結果波形である。図3ではPGND−GND間逆サージが−25V程度出ているのに対して、図2ではPGND−GND間逆サージがほとんど出ていない。

【0024】

また図4は本実施形態の外部バッファ回路を示す図である。図4の外部バッファ回路109はバイポーラトランジスタによるエミッタフォロア型のプッシュプル回路となっている。npnトランジスタ505のコレクタに電源端子501が接続され、エミッタは抵抗506の一方の端子に接続されている。抵抗506の他方の端子は抵抗508の一方に接続され、他方はpnpトランジスタ507のエミッタに接続されている。pnpトランジスタ507のコレクタは外部バッファ回路のグランド端子502に接続されている。npnトランジスタ505及びpnpトランジスタ507のベースは外部バッファ回路109の入力端子503に接続されている。また抵抗506と抵抗508の接点は外部バッファ回路109の出力端子504に接続されている。入力端子503に入った信号はバッファリングされて出力端子504に出力される。また容量509はバイパスコンデンサで、外部バッファ109の電源501/グランド502間の電源環境を安定化させている。

【0025】

図5は、本発明の他の実施形態をなすインバータ装置のゲート駆動回路を示す。以下に示す事項以外は、図1の実施形態と同様である。

【0026】

図1のゲート駆動回路にゲートクランプ回路601及び604が装備されている。ゲートクランプ回路601はNORゲート602とN型MOSFET603から構成されている。このNORゲート602の2つの入力のうち、一つはゲート駆動IC101の高電位側駆動信号端子105に、そして他方は高電位側IGBT121のゲート端子115に接続され、出力はN型MOSFET603のゲート端子に接続されている。N型MOSFET603のドレイン端子は高電位側IGBT121のゲート端子115に、そしてソース端子は高電位側IGBT121のエミッタ端子116に接続されている。

【0027】

そしてゲート駆動IC101の高電位側駆動信号と高電位側IGBT121のゲート電圧の両方がLレベルになるとNORゲート602はHレベルを出力し、N型MOSFET603をオンさせて高電位側IGBT121のゲート端子115とエミッタ端子116を短絡する。これにより高電位側IGBT121のゲート端子をLレベルにしている間にコレクタ−エミッタ間電圧が変動しても、ゲート−コレクタ間寄生容量によるゲート電圧のカップリングノイズを小さく抑える事ができる。

【0028】

なお、ゲートクランプ回路604は、高電位側1GBT121に対するゲートクランプ回路601と同様に、低電位側IGBT123に対して作用するものである。

【0029】

以上の実施形態においては、ゲート駆動ICの高電位側駆動信号の基準電位端子PGNDとIGBTモジュールの低電位側IGBTのコレクタ端子NC端子間に容量を設け、またIGBTモジュールの高電位側IGBTのエミッタ端子PEとPGNDの間にインピーダンスを設けるので、PGNDは容量によってNCとAC的にカップリングされ、インピーダンスによってPGNDとPE間の接続が弱まるとともにインピーダンスに抵抗成分を含ませた場合には寄生インダクタンスと前記容量によるLC発振が防止(ダンピング)される。これによりPE−NC間の逆サージが伝わりにくくなり、PGND−GND間の逆サージを回避する事ができる。

【図面の簡単な説明】

【0030】

【図1】本発明の一実施形態をなすインバータ装置のゲート駆動回路を示す。

【図2】本発明による逆サージをシミュレーションした波形を示す。

【図3】従来技術による逆サージをシミュレーションした波形を示す。

【図4】図1の外部バッファ回路を示す。

【図5】本発明の他の実施形態をなすインバータ装置のゲート駆動回路を示す。

【符号の説明】

【0031】

101 ゲート駆動IC

106 高電位側IGBT駆動信号用基準電位端子

113 IGBTモジュール

121,123 IGBT

127 抵抗

128 容量

【特許請求の範囲】

【請求項1】

高電位側トランジスタ及び低電位側トランジスタを有するパワーモジュールと、

前記高電位側トランジスタ及び前記低電位側トランジスタを駆動する信号を出力するゲート駆動ICと、

前記ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と前記低電位側トランジスタのコレクタ端子との間に設けられた容量と、

前記ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と前記高電位側トランジスタのエミッタ端子との間に設けられたインピーダンスと、

を有するインバータ装置。

【請求項2】

請求項1に記載のインバータ装置であって、

前記パワーモジュールの前記高電位側トランジスタまたは前記低電位側トランジスタをそれぞれ駆動するバッファ回路を有し、

前記バッファ回路の基準電位端子は前記ゲート駆動ICの前記高電位側トランジスタ駆動信号用基準電位端子と接続されているインバータ装置。

【請求項3】

請求項1記載のインバータ装置であって、

前記ゲート駆動回路の高電位側トランジスタ駆動信号がオフ信号かつ前記パワーモジュールの前記高電位側トランジスタがオフとなっている時にそのゲート端子とエミッタ端子を短絡するゲートクランプ回路を有し、

前記ゲートクランプ回路の基準電位端子は前記エミッタ端子と接続されているインバータ装置。

【請求項4】

請求項1記載のインバータ装置であって、

前記インピーダンスは抵抗であるインバータ装置。

【請求項5】

請求項4記載のインバータ装置であって、

前記容量をR、前記抵抗をC、前記パワーモジュールの前記高電位側トランジスタのエミッタ端子と前記低電位側トランジスタのコレクタ端子との間のインダクタンスをLec、前記高電位側トランジスタのゲート端子とエミッタ端子との間の容量をCpgとしたとき、

RC>√LecCpg

であるインバータ装置。

【請求項1】

高電位側トランジスタ及び低電位側トランジスタを有するパワーモジュールと、

前記高電位側トランジスタ及び前記低電位側トランジスタを駆動する信号を出力するゲート駆動ICと、

前記ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と前記低電位側トランジスタのコレクタ端子との間に設けられた容量と、

前記ゲート駆動ICの高電位側トランジスタ駆動信号用基準電位端子と前記高電位側トランジスタのエミッタ端子との間に設けられたインピーダンスと、

を有するインバータ装置。

【請求項2】

請求項1に記載のインバータ装置であって、

前記パワーモジュールの前記高電位側トランジスタまたは前記低電位側トランジスタをそれぞれ駆動するバッファ回路を有し、

前記バッファ回路の基準電位端子は前記ゲート駆動ICの前記高電位側トランジスタ駆動信号用基準電位端子と接続されているインバータ装置。

【請求項3】

請求項1記載のインバータ装置であって、

前記ゲート駆動回路の高電位側トランジスタ駆動信号がオフ信号かつ前記パワーモジュールの前記高電位側トランジスタがオフとなっている時にそのゲート端子とエミッタ端子を短絡するゲートクランプ回路を有し、

前記ゲートクランプ回路の基準電位端子は前記エミッタ端子と接続されているインバータ装置。

【請求項4】

請求項1記載のインバータ装置であって、

前記インピーダンスは抵抗であるインバータ装置。

【請求項5】

請求項4記載のインバータ装置であって、

前記容量をR、前記抵抗をC、前記パワーモジュールの前記高電位側トランジスタのエミッタ端子と前記低電位側トランジスタのコレクタ端子との間のインダクタンスをLec、前記高電位側トランジスタのゲート端子とエミッタ端子との間の容量をCpgとしたとき、

RC>√LecCpg

であるインバータ装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2009−254056(P2009−254056A)

【公開日】平成21年10月29日(2009.10.29)

【国際特許分類】

【出願番号】特願2008−96698(P2008−96698)

【出願日】平成20年4月3日(2008.4.3)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成21年10月29日(2009.10.29)

【国際特許分類】

【出願日】平成20年4月3日(2008.4.3)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]