インバータ装置

【課題】パワー半導体スイッチング素子とユニポーラ型ダイオードとを並列接続したスイッチング回路(インバータ装置)において、リンギングによるノイズの低減化を図る。

【解決手段】主回路19に流れる主回路電流が所定値以下のときは、Si−IGBT12はゲート抵抗12gによってスイッチング駆動する。ここで、主回路電流検出カレントトランス18が検出した主回路電流が閾値以上になると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33をONからOFFにする。これにより、Si−IGBT12はゲート抵抗12gとゲート抵抗31の和で動作する。すなわち、Si−IGBT12のゲート駆動回路のゲート抵抗値を大きくなる。これにより、Si−IGBT12のコレクタ−エミッタ間電圧のdv/dt、つまり、ユニポーラ型ダイオード14のリカバリdv/dtが小さくなるのでリンギングによるノイズを低減させることができる。

【解決手段】主回路19に流れる主回路電流が所定値以下のときは、Si−IGBT12はゲート抵抗12gによってスイッチング駆動する。ここで、主回路電流検出カレントトランス18が検出した主回路電流が閾値以上になると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33をONからOFFにする。これにより、Si−IGBT12はゲート抵抗12gとゲート抵抗31の和で動作する。すなわち、Si−IGBT12のゲート駆動回路のゲート抵抗値を大きくなる。これにより、Si−IGBT12のコレクタ−エミッタ間電圧のdv/dt、つまり、ユニポーラ型ダイオード14のリカバリdv/dtが小さくなるのでリンギングによるノイズを低減させることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体スイッチング素子とダイオードとが逆並列に接続された半導体モジュールを備えたインバータ装置に関し、特に、パワー半導体スイッチング素子に、炭化ケイ素や窒化ガリウムなどのワイドギャップ半導体のユニポーラデバイスから成るダイオードが逆並列に接続されたパワー半導体モジュールに対してゲート駆動を行うインバータ装置に関する。

【背景技術】

【0002】

近年、電子が存在しない禁止帯領域(バンドギャップエリア)の幅が広いワイドギャップ半導体素子として、炭化ケイ素(以下、SiCという)や窒化ガリウム(以下、GaNという)などの材料を用いた半導体素子が注目を浴びている。これらの材料は、通常の半導体素子の材料として使用されているシリコン(以下、Siという)より約10倍程度の高い絶縁破壊電圧強度を有している。したがって、これらのワイドギャップ半導体素子は、耐圧を確保するためのドリフト層を、Siを用いた通常の半導体素子に対して1/10程度まで薄くすることができるため、パワーデバイスの低オン電圧化を実現することが可能である。これにより、Siを用いた半導体素子の場合ではバイポーラ素子しか使用できないような高耐圧領域でも、SiCなどを用いたワイドギャップ半導体素子では、ユニポーラ素子を使用することができる。

【0003】

また、インバータ装置に用いられるパワー半導体モジュールとしては、スイッチングデバイス(半導体スイッチング素子)に逆並列に還流用のダイオードが接続されている。このとき、従来のパワー半導体モジュールでは、還流用のダイオードとしてSi−PiNダイオード(p-Intrinsic-n Diode)が使用されている。このSi−PiNダイオードはバイポーラ型の半導体素子(バイポーラ型ダイオード)であり、順方向バイアスで大電流を通電させる場合、伝導度変調により順方向電圧降下が低くなるような構造となっている。

【0004】

しかし、バイポーラ型ダイオードであるSi−PiNダイオードは、順方向バイアス状態から逆バイアス状態に至る過程で、伝導度変調によりSi−PiNダイオードに残留したキャリアが逆回復電流(リカバリ電流)として発生するという特性を有する。このとき、Si−PiNダイオードにおいては、残留するキャリアの寿命が長いために逆回復電流が大きくなる。そのため、この逆回復電流により、パワー半導体スイッチング素子のターンオン時の損失(以下、ターンオン損失Eonという)や、還流用のダイオードが逆回復したときにそのダイオードに発生する逆回復損失(以下、リカバリ損失Errという)が大きくなるという欠点がある。

【0005】

一方、ショットキーバリアダイオード(以下、SBDという)はユニポーラ型の半導体素子(ユニポーラ型ダイオード)であり、伝導度変調によるキャリア発生が殆ど生じないので、インバータ装置でSBDが使用される場合は、還流用のダイオードの逆回復電流(リカバリ電流)が非常に小さいために、パワー半導体スイッチング素子のターンオン損失Eonや還流用のダイオードのリカバリ損失Errを小さくすることができる。

【0006】

このとき、Siは絶縁破壊電界強度が低いため、高耐圧を持たせる構造でユニポーラ型ダイオードのSBDを作製すると、通電時に大きな抵抗が生じるために、Si−SBDでは耐圧は200V程度が限界である。一方、SiCはSiの10倍の絶縁破壊電界強度を有するために、SiCを用いることにより200Vよりさらに高耐圧のSiC−SBDを実現することが可能となり、かつ、ターンオン損失Eonやリカバリ損失Errを低減させることで、インバータの損失を低減させて効率の高いパワー半導体モジュールを実現させることができる。

【0007】

また、還流用のダイオードのリカバリ損失Errは、そのダイオードの逆回復時の電圧変化率、すなわち、還流用のダイオードのリカバリdv/dtの大きさに起因することが知られている。図2は、ユニポーラ型ダイオードとバイポーラ型ダイオードのリカバリdv/dtの電流依存性を示す特性図であり、横軸に主回路電流(I)、縦軸にリカバリdv/dtを示している。さらに詳しく述べると、図2は、ユニポーラ型ダイオードとしてSiC−SBDを用いた場合と、バイポーラ型ダイオードとしてSi−PiNダイオードを用いた場合の、それぞれのリカバリdv/dtの電流依存性を示している。

【0008】

すなわち、還流用のダイオードのリカバリdv/dtの電流依存性は、バイポーラ型ダイオードを用いた場合には、図2の特性(a)に示すように電流値に反比例し、ユニポーラ型ダイオードを用いた場合には、図2の特性(b)に示すように電流値に比例し、その変化傾向も顕著であることが広く知られている。

【0009】

このような前提条件に基づいて、パワー半導体スイッチング素子と逆並列にバイポーラ型ダイオードを用いた電力変換器のゲート駆動回路が、例えば、特許文献1などに開示されている。この技術に開示されたゲート駆動回路では、パワー半導体スイッチング素子と逆並列にバイポーラ型ダイオードを用いているために、図2の特性(a)に示すように、ターンオン時の主回路電流Iが小さい場合にはリカバリdv/dtが大きいために、パワー半導体スイッチング素子のゲート抵抗値を大きくして発生ノイズを低減させて、パワー半導体スイッチング素子などの素子破壊を防いでいる。また、主回路電流Iが大きい場合には、リカバリdv/dtが小さいためにゲート抵抗値を小さくしてターンオン損失を抑制している。

【0010】

ここで、還流用のダイオードはパワー半導体スイッチング素子と逆並列に接続されているために、そのダイオードのリカバリdv/dtは、パワー半導体スイッチング素子のdv/dtと同期している。したがって、パワー半導体スイッチング素子のdv/dtを抑えることで、そのダイオードのリカバリdv/dtも抑えることが可能になる。パワー半導体スイッチング素子のdv/dtは、ゲート抵抗値を大きくすることでゲートに流れる電流値を制限してゲート電圧の立ち上がりを遅くすることができ、これによりパワー半導体スイッチング素子のdv/dtも抑えることが知られている。したがって、還流用のダイオードのリカバリdv/dtを制御するためには、これと同期するパワー半導体スイッチング素子のゲート抵抗値、すなわちゲートインピーダンスを制御することが有用である。特許文献1においては、この性質を利用してバイポーラ型ダイオードのリカバリdv/dtの制御を行っている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開平11−69779号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

すなわち、前記特許文献1のゲート駆動方式では、パワー半導体スイッチング素子と逆並列に接続された還流用のダイオードとしてバイポーラ型ダイオードを使用しているため、パワー半導体スイッチング素子のターンオン時の主回路電流値が小さい場合においては、そのパワー半導体スイッチング素子のゲート抵抗値を大きくしてバイポーラ型ダイオードのリカバリdv/dtを小さくし、パワー半導体スイッチング素子のターンオン時の主回路電流の振動を抑えることでノイズの低減や素子破壊の抑制を行っている。また、パワー半導体スイッチング素子のターンオン時の主回路電流値が大きい場合においては、パワー半導体スイッチング素子のゲート抵抗値を小さくすることでターンオンを高速化してターンオン損失を抑制している。このような制御方法は、図2の特性(a)に示すようなリカバリdv/dtの電流依存性を有したバイポーラ型ダイオードに対しては有効である。

【0013】

しかしながら、SiC−SBDのようなユニポーラ型ダイオードにおいては、図2の特性(b)に示すように、バイポーラ型ダイオードのリカバリdv/dtの電流依存性と大きく異なっている。言い換えると、ユニポーラ型ダイオードとしてSiC−SBDを用いることで低減できる還流用のダイオードのリカバリ損失Errにおいて、このリカバリ損失Errの要因となる還流用のダイオードのリカバリdv/dtは、図2の特性(b)に示すように、電流値に比例して大きくなり、その電流依存性はバイポーラ型ダイオードに比べて顕著である。したがって、ユニポーラ型ダイオードを用いた場合は、バイポーラ型ダイオードを用いた場合のように大電流時にゲート抵抗値を小さくするような駆動制御を行うことができない。これについて、以下、詳細に説明する。

【0014】

図3は、バイポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は従来例、(b−1)と(b−2)は特許文献1適用時を示す。すなわち、図3は、主回路電流の大電流時においてバイポーラ型ダイオードを用いた場合の、パワー半導体スイッチング素子のターンオン時の動作波形図であり、(a−1)は従来例であるゲート抵抗値を変えない場合のコレクタ−エミッタ間電圧Vce、(a−2)は従来例であるゲート抵抗値を変えない場合のコレクタ電流Ic、(b−1)は特許文献1を適用してゲート抵抗値を小さくした場合のコレクタ−エミッタ間電圧Vce、(b−2)は特許文献1を適用してゲート抵抗値を小さくした場合のコレクタ電流Icの動作波形を表わしている。なお、横軸は、いずれの図も時間を示し、縦軸は、それぞれ、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vce及びコレクタ電流Icを示している。また、バイポーラ型ダイオードとしてはSi−PiNダイオードを用いている。なお、当該バイポーラ型ダイオードは、パワー半導体スイッチング素子に逆並列に接続されている。

【0015】

すなわち、パワー半導体スイッチング素子に逆並列にバイポーラ型ダイオードを用いたインバータ装置に所定値以上の大電流が流れている場合は、図3(a−1)のように大電流時にはパワー半導体スイッチング素子におけるコレクタ−エミッタ間電圧Vceのdv/dtが小さいため(つまり、バイポーラ型ダイオードのリカバリdv/dtが小さいため)、特許文献1を適用してゲート抵抗値を小さくすると、図3(b−1)のようにパワー半導体スイッチング素子におけるコレクタ−エミッタ間電圧Vceのdv/dtが大きくなり(つまり、バイポーラ型ダイオードのリカバリdv/dtが大きくなり)ターンオン損失を低減させることができる。

【0016】

さらに、詳しく述べると、パワー半導体スイッチング素子のゲート抵抗値が大きい場合には、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が大きいために、ターンオン時(時刻t1)におけるゲート信号の立ち上がり波形が緩やかになるので、図3(a−1)のように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが小さくなる。すなわち、コレクタ−エミッタ間電圧Vceの立ち下がりが緩やかになる。そこで、特許文献1を適用してゲート抵抗値を小さくすると、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が小さくなる。そのため、ターンオン時(時刻t1)におけるゲート信号の立ち下がり波形が急峻になるので、図3(b−1)のように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが大きくなる。すなわち、コレクタ−エミッタ間電圧Vceの立ち下がりが急峻になる。その結果、パワー半導体スイッチング素子のターンオン損失を低減させることができる。

【0017】

図4は、ユニポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は従来例、(b−1)と(b−2)は特許文献1適用時を示す。すなわち、図4は、主回路電流の大電流時におけるユニポーラ型ダイオードを用いた場合のパワー半導体スイッチング素子のターンオン時の動作波形図であり、(a−1)は所定のゲート抵抗値の場合のコレクターエミッタ間電圧Vce、(a−2)は所定のゲート抵抗値の場合のコレクタ電流Ic、(b−1)は特許文献1を適用してゲート抵抗値を小さくした場合のコレクターエミッタ間電圧Vce、(b−2)は特許文献1を適用してゲート抵抗を小さくした場合のコレクタ電流Ic、の各動作波形を表わしている。なお、横軸は、いずれの図も時間を示し、縦軸は、それぞれ、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vce及びコレクタ電流Icを示している。また、ユニポーラ型ダイオードとしてはSiC−SBDを用いている。

【0018】

すなわち、パワー半導体スイッチング素子と逆並列にユニポーラ型ダイオードを用いたインバータ装置に大電流が流れている場合には、図2で示したようにユニポーラ型ダイオードのリカバリdv/dtが大きい。言い換えると、ユニポーラ型ダイオードを用いた場合は、図4(a−1)に示すように、大電流が流れている場合には、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが大きい(立下りが急峻である)。したがって、図4(a―2)に示すように、パワー半導体スイッチング素子のターンオン時におけるコレクタ電流Icに若干の跳ね上がりの振動(リンギング)が発生するおそれがある。

【0019】

そのため、ユニポーラ型ダイオードを用いた場合は、大電流が流れているときに特許文献1のゲート駆動方式を適用してゲート抵抗値をさらに小さくすると、図4(b−1)に示すように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtがさらに大きくなり、その結果、図4(b−2)に示すように、コレクタ電流Icのリンギングが非常に大きくなる。

【0020】

言い換えると、パワー半導体スイッチング素子のゲート抵抗値を小さくするにしたがって、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が益々小さくなるため、ターンオン時の時刻t1におけるゲート信号の立ち上がり波形が益々急峻になる。その結果、図4(b−1)のように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが大きく(急峻に)なり、図4(b−2)のようにコレクタ電流Icのリンギングが益々大きくなる。

【0021】

すなわち、特許文献1のゲート駆動方式は、バイポーラ型ダイオードにおいては、リカバリdv/dtによるコレクタ電流の振動を抑制してターンオン損失を低減させることができるが、特許文献1のゲート駆動方式をユニポーラ型ダイオードに適用した場合には、大電流時においてコレクタ電流Icの跳ね上がりの振動(リンギング)が大きくなるおそれがある。言い換えると、特許文献1のゲート駆動方式をユニポーラ型ダイオードに適用した場合には、パワー半導体スイッチング素子のターンオン時の主回路電流値が小さい場合にゲート抵抗値を大きくすることでターンオン損失がさらに増え、主回路電流が大きい場合にゲート抵抗値を小さくすることで電流値に比例して高速化されていたリカバリdv/dtがさらに大きくなり、インバータから発生する放射ノイズが増大したり、負荷であるモータの絶縁劣化が早くなるなどの不具合が生じる。

【0022】

本発明は、このような事情に鑑みてなされたものであり、パワー半導体スイッチング素子に逆並列に接続される還流用のダイオードとしてユニポーラ型ダイオードを適用した場合でも、当該パワー半導体スイッチング素子のコレクタ電流のリンギングを抑制することができるインバータ装置を提供することを課題とする。

【課題を解決するための手段】

【0023】

前記課題を解決するために、本発明のインバータ装置は以下のように構成した。すなわち、本発明のインバータ装置は、パワー半導体スイッチング素子とユニポーラ型ダイオードとが逆並列に接続されたパワー半導体モジュールを備えたインバータ装置であって、前記パワー半導体モジュールに流れる電流を検出する電流検出手段と、前記電流検出手段が検出した電流値が所定値より大きいときに、前記パワー半導体スイッチング素子を駆動するゲート駆動回路のゲートインピーダンスを大きくするように、該ゲートインピーダンスを切り替えるゲートインピーダンス切替手段とを備えることを特徴とする。

【発明の効果】

【0024】

本発明によれば、還流用のダイオードとしてユニポーラ型ダイオードを用いた場合でも、コレクタ電流のリンギングを抑制することが可能なインバータ装置を提供することができる。

【図面の簡単な説明】

【0025】

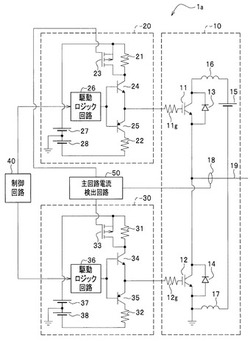

【図1】本発明の第1実施形態におけるインバータ装置の構成図である。

【図2】ユニポーラ型ダイオードとバイポーラ型ダイオードのリカバリdv/dtの電流依存性を示す特性図である。

【図3】バイポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は従来例、(b−1)と(b−2)は特許文献1適用時を示す。

【図4】ユニポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は第1実施形態、(b−1)と(b−2)は従来例を示す。

【図5】本発明の第1実施形態に係るインバータ装置の動作を示す各部の波形図である。

【図6】ユニポーラ型ダイオード使用時の第1実施形態と従来例の動作波形図であり、(a−1)と(a−2)は第1実施形態、(b−1)と(b−2)は従来例を示す。

【図7】本発明の第2実施形態におけるインバータ装置の構成図である。

【図8】本発明の第2実施形態に係るインバータ装置の動作を示す各部の波形図である。

【図9】本発明の第3実施形態におけるインバータ装置の構成図である。

【図10】本発明の第3実施形態に係るインバータ装置の動作を示す各部の波形図である。

【発明を実施するための形態】

【0026】

《概要》

本発明の実施形態に係るインバータ装置は、パワー半導体スイッチング素子と、SiCやGaNなどのワイドギャップ半導体のユニポーラ型ダイオードとが逆並列に接続されたパワー半導体モジュールを備えたインバータ装置であって、そのインバータ装置の主回路電流が所定値より大きい場合には、パワー半導体スイッチング素子をスイッチング駆動するためのゲート抵抗値(ゲートインピーダンス)を大きくするように構成したことを特徴とする。これにより、ユニポーラ型ダイオードのリカバリdv/dtを低減させて、パワー半導体スイッチング素子のターンオン損失やユニポーラ型ダイオードのリカバリ損失を少なくすることができると共に、パワー半導体スイッチング素子のコレクタ電流の振動による跳ね上がり(リンギング)を抑制することができる。

【0027】

また、本発明の実施形態に係るインバータ装置は、PWM(Pulse Width Modulation)制御を行うインバータ装置の主回路電流が所定値より大きい場合には、パワー半導体スイッチング素子をスイッチング駆動するためのゲート抵抗値(ゲートインピーダンス)を大きくすると共に、インバータ装置を駆動するためのPWM信号のパルス数を低減させるように構成したことを特徴としている。これにより、ターンオン損失、リカバリ損失、及びリンギングを抑制することができると共に、パワー半導体スイッチング素子のスイッチング損失を低減させることができる。

【0028】

以下、本発明に係るインバータ装置の幾つかの実施形態について図面を参照しながら詳細に説明する。なお、各実施形態を説明するための全図において、同一の構成要素は原則として同一の符号を付し、その繰り返しの説明は省略する。

【0029】

《第1実施形態》

〈インバータ装置の構成〉

図1は、本発明の第1実施形態におけるインバータ装置の構成図である。なお、一般的には、インバータ装置はフルブリッジ回路で構成されているが、図1では、本実施形態の説明の便宜上、ハーフブリッジ回路のインバータ装置を示している。

【0030】

先ず、本発明の第1実施形態に係るインバータ装置の構成について説明する。図1に示すように、インバータ装置1aは、インバータ主回路10、上アーム駆動/制御回路20、下アーム駆動/制御回路30、制御回路40、及び主回路電流検出回路50を備えて構成されている。

【0031】

インバータ主回路10は、直列に接続された2つのパワー半導体スイッチング素子であるSi−IGBT(Silicon Insulated Gate Bipolar Transistor)11,12と、ゲート抵抗11g,12gと、各Si−IGBT11,12にそれぞれ逆並列に接続されたユニポーラ型ダイオード13,14と、主回路電源15と、主回路インダクタンス16,17と、主回路電流検出カレントトランス(CT)18と、及び主回路19とを備えて構成されている。

【0032】

Si−IGBT11,12は、ゲート端子に入力された信号によって、コレクタ端子とエミッタ端子との間の導通と非導通とを切り替えるパワー半導体スイッチング素子である。Si−IGBT11とユニポーラ型ダイオード13、及び、Si−IGBT12とユニポーラ型ダイオード14は、それぞれ、パワー半導体モジュールを構成している。また、主回路電源15は、正極端子と負極端子との間に直流電圧を印加する直流電源である。さらに、主回路電流検出カレントトランス(CT)18は、主回路19に流れる電流に応じた信号を出力する電流検出手段である。

【0033】

主回路電源15の正極端子には主回路インダクタンス16の一方の端子が接続されている。主回路インダクタンス16の他方の端子は、直列に接続されたSi−IGBT11のコレクタ端子に接続されている。また、主回路電源15の負極端子には主回路インダクタンス17の一方の端子が接続されている。主回路インダクタンス17の他方の端子は、直列に接続されたSi−IGBT12のエミッタ端子に接続されていると共に、グランドに接続されている。また、Si−IGBT11のエミッタ端子とSi−IGBT12のコレクタ端子とが接続されているノードから、主回路電流検出カレントトランス(CT)18と主回路19とを介して、図示しない負荷に接続されている。

【0034】

また、上アームのSi−IGBT11のゲート端子は、ゲート抵抗11gを介して、上アームのSi−IGBT11を駆動する上アーム駆動/制御回路20に接続されている。同様に、下アームのSi−IGBT12のゲート端子は、ゲート抵抗12gを介して、下アームのSi−IGBT12を駆動する下アーム駆動/制御回路30に接続されている。

【0035】

下アーム駆動/制御回路30は、ゲート抵抗31,32と、ゲート抵抗切替用pMOS(positive channel Metal Oxide Semiconductor)33と、npnトランジスタ34と、pnpトランジスタ35と、駆動ロジック回路36、及び下アーム駆動/制御回路電源37,38とを備えて構成されている。なお、npnトランジスタ34及びpnpトランジスタ35は、それぞれ、pMOS及びnMOS(negative channel Metal Oxide Semiconductor)などに代替可能である。

【0036】

下アーム駆動/制御回路30の回路構成は次のようになっている。すなわち、ゲート抵抗切替用pMOS33とゲート抵抗31とが並列に接続され、該ゲート抵抗切替用pMOS33のソース側が下アーム駆動/制御回路電源37の正極に接続され、該ゲート抵抗切替用pMOS33のドレイン側がnpnトランジスタ34のコレクタ端子に接続されている。また、該npnトランジスタ34のエミッタ端子はpnpトランジスタ35のエミッタ端子に接続されると共に、インバータ主回路10におけるゲート抵抗11gの一方の端子に接続されている。さらに、該pnpトランジスタ35のコレクタ端子はゲート抵抗32の一端に接続され、該ゲート抵抗32の他端は下アーム駆動/制御回路電源38の負極に接続されている。そして、下アーム駆動/制御回路電源38の正極は前記下アーム駆動/制御回路電源37の負極に接続されると共にグランドに接続されている。また、制御信号系としては、ゲート抵抗切替用pMOS33のゲート端子が主回路電流検出回路50に接続され、npnトランジスタ34とpnpトランジスタ35のそれぞれのベース端子は駆動ロジック回路36の一端に接続され、該駆動ロジック回路36の他端は制御回路40に接続されている。

【0037】

このような回路構成において、駆動ロジック回路36は、制御回路40からの駆動信号(例えば、PWM信号)を入力して、npnトランジスタ34とpnpトランジスタ35とを交互にスイッチング動作させる。また、npnトランジスタ34とpnpトランジスタ35は、駆動ロジック回路36の駆動信号(例えば、PWM信号)を増幅して下アームのSi−IGBT12をスイッチング駆動(例えば、PWM駆動)させる。

【0038】

上アーム駆動/制御回路20も同様の構成であって、ゲート抵抗21,22、ゲート抵抗切替用pMOS23、npnトランジスタ24、pnpトランジスタ25、駆動ロジック回路26、及び上アーム駆動/制御回路電源27,28を備えて構成されている。なお、上アーム駆動/制御回路20の回路構成は、下アーム駆動/制御回路30の回路構成と同じであるので、重複する説明は省略する。

【0039】

主回路電流検出回路50は、検出端子が主回路電流検出カレントトランス(CT)18に接続され、上アームの制御端子が、上アーム駆動/制御回路20のゲート抵抗切替用pMOS23のゲート端子に接続され、下アームの制御端子が下アーム駆動/制御回路30のゲート抵抗切替用pMOS33のゲート端子に接続されている。主回路電流検出回路50は、インバータ主回路10の主回路電流検出カレントトランス(CT)18からの主回路電流検出信号を入力し、上アーム駆動/制御回路20のゲート抵抗切替用pMOS23及び下アーム駆動/制御回路30のゲート抵抗切替用pMOS33をON/OFF制御する。

【0040】

また、制御回路40は、上アーム駆動/制御回路20の駆動ロジック回路26と下アーム駆動/制御回路30の駆動ロジック回路36とに、それぞれの制御信号線を接続している。したがって、制御回路40は、上アーム駆動/制御回路20の駆動ロジック回路26を制御してnpnトランジスタ24及びpnpトランジスタ25を駆動制御させると共に、下アーム駆動/制御回路30の駆動ロジック回路36を制御してnpnトランジスタ34及びpnpトランジスタ35を駆動制御させることができる。これによって、上アームのSi−IGBT11と下アームのSi−IGBT12は、それぞれ、制御回路40で生成されたPWM信号によってPWM制御のスイッチング動作を行うことができる。あるいは、制御回路40は、上アームのSi−IGBT11と下アームのSi−IGBT12を交互に180度通電するようにスイッチング動作を行わせてもよい。

【0041】

本発明の第1実施形態では、ユニポーラ型ダイオードのように、リカバリdv/dtが電流値に比例する特性を有する還流用のダイオードを、パワー半導体スイッチング素子と逆並列に接続したパワー半導体モジュールとして用いた場合において、主回路電流検出回路50が検出した主回路電流の大きさに応じて、上アーム駆動/制御回路20及び下アーム駆動/制御回路30が、それぞれ、ゲート抵抗21とゲート抵抗22を接続/短絡して、Si−IGBT11及びSi−IGBT12のゲート抵抗値(ゲートインピーダンス)を切り替え制御するように構成されている。ここで、ゲート抵抗とは、上アームのSi−IGBT11と下アームのSi−IGBT12のスイッチング動作を安定的に行うために、ゲート端子とゲート電源との間に設けられた抵抗のことである。

【0042】

〈第1実施形態におけるインバータ装置の動作〉

図1に示すインバータ装置1aの基本的な動作を以下に説明する。制御回路40からの制御信号によって、上アーム駆動/制御回路20の駆動ロジック回路26及び下アーム駆動/制御回路30の駆動ロジック回路36を制御し、パワー半導体スイッチング素子であるSi−IGBT11とSi−IGBT12を交互にON/OFF動作させることにより、主回路電源15の直流電圧が交流電圧に変換され、主回路19に交流電流(主回路電流)が流れて負荷(図示せず)に供給されると共に、主回路19に流れた主回路電流は、主回路電流検出カレントトランス(CT)18で検出されて主回路電流検出回路50へ供給される。なお、制御回路40は、Si−IGBT11とSi−IGBT12をPWM制御してもよいし、Si−IGBT11とSi−IGBT12をそれぞれ電気角180度ごとにON/OFFして矩形波制御してもよい。あるいは、制御回路40は、矩形波制御をベースにして通電角を制御するデューティ幅制御(位相制御)を行ってもよい。

【0043】

ここで、Si−IGBT11とSi−IGBT12のON/OFF動作について概略説明する。Si−IGBT11がONしたときは、Si−IGBT12はOFFとなるが、このSi−IGBT12に逆並列に接続された還流用のダイオードであるユニポーラ型ダイオード14がターンオンして還流電流が流れる。同様にして、Si−IGBT12がONしたときは、Si−IGBT11はOFFとなるが、このSi−IGBT11に逆並列に接続された還流用のダイオードであるユニポーラ型ダイオード13がターンオンして還流電流が流れる。このようなスイッチング動作の過程において、Si−IGBT11,12のそれぞれのターンオン時にはユニポーラ型ダイオード13,14のそれぞれに逆回復電圧(リカバリ電圧)が発生する。

【0044】

上アーム駆動/制御回路20と下アーム駆動/制御回路30は同じ構成であって、かつ同じ動作を行うので、本実施形態に係るSi−IGBT11,12のターンオン時のコレクタ−エミッタ間電圧変化の推移(つまり、ユニポーラ型ダイオード13,14のリカバリ電圧変化の推移)については、便宜上、下アーム駆動/制御回路30を用いて説明する。したがって、上アーム駆動/制御回路20の動作説明は、重複を避けるために省略する。

【0045】

すなわち、本実施形態では、ユニポーラ型ダイオードのように、リカバリdv/dtが電流値に比例する特性を有する還流用のダイオードを用いた場合において、上アーム駆動/制御回路20及び下アーム駆動/制御回路30が、主回路電流検出カレントトランス18で検出された主回路電流に基づいて、Si−IGBT11及びSi−IGBT12のゲート抵抗値を切り替える制御を行うが、本実施形態では、下アーム駆動/制御回路30を用いてこの動作を説明する。

【0046】

図5は、本発明の第1実施形態に係るインバータ装置の動作を示す各部の波形図であり、(a)は主回路電流、(b)は制御回路の下アームPWM信号、(c)は主回路電流が所定の閾値よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33のゲート端子へ送信する下アームのゲート抵抗切替信号、(d)は下アームのユニポーラ型ダイオード14の逆回復時の電圧変化率(リカバリdv/dt)を示している。なお、いずれの図も横軸は時間を表わし、縦軸はそれぞれのレベルを表わしている。また、主回路電流(a)は、図1において図示しない負荷から主回路19を通ってSi−IGBT12のコレクタからエミッタへ流れる電流(コレクタ電流Ic)の方向を正極として表わしている。なお、制御回路の下アームPWM信号(b)は、主回路電流(a)を生成するために、駆動ロジック回路36を介して下アームのSi−IGBT12のゲート部分に供給される信号である。

【0047】

ここで、図5の主回路電流(a)と逆回復時の電圧変化率(d)(つまり、リカバリdv/dt)との関係について説明する。主回路電流(a)(つまり、コレクタ電流Ic)は、例えば、半サイクル10msecでSi−IGBT12のコレクタからエミッタへ正弦波状に流れている。このとき、Si−IGBT12は、例えば、100μsecのキャリア周波数でスイッチング駆動している。なお、このときのスイッチング駆動の信号は、デューティ比制御を行うPWM信号によるキャリア周波数でもよいし、デューティ比制御を行わないでデューティ比が50%のON/OFF信号によるキャリア周波数であってもよい。いずれの場合においても、Si−IGBT12は、100μsecのキャリア周波数でスイッチング駆動することになる。すなわち、主回路電流(コレクタ電流Ic)の半サイクル10msecの間にSi−IGBT12は100回のスイッチング駆動を行う。したがって、Si−IGBT12がスイッチング駆動を行うごとに、Si−IGBT12のコレクタ電圧にdv/dtが発生する(つまり、ユニポーラ型ダイオード14にリカバリdv/dtが発生する。)このときにキャリア周波数で発生する毎サイクルの逆回復時の電圧変化率(d)(つまり、リカバリdv/dt)は、主回路電流(a)(つまり、コレクタ電流Ic)が増加するにしたがって大きくなる。そのため、主回路電流(a)(つまり、コレクタ電流Ic)が所定の電流値まで上昇したら、Si−IGBT12のゲート抵抗値を大きくして、キャリア周波数の毎サイクル時における逆回復時の電圧変化率(d)(つまり、リカバリdv/dt)を減少させている。これについての詳細は、以下に説明する。

【0048】

なお、ここでは、制御回路40が図5(b)のようにPWM制御を行うことによって、主回路電流を図5(a)のように正弦波にしている。しかし、これに限らず、制御回路40がON/OFFのキャリア周波数で180度通電制御を行い、Si−IGBT11とSi−IGBT12をキャリア周波数で交互にON/OFFさせて矩形波を出力し、インバータ装置1aの出力側のフィルタ(図1では図示せず)によって高調波を除去し、出力電流(主回路電流)を図5(a)のように正弦波状にしてもよい。

【0049】

次に、図1及び図5を用いて、本発明の第1実施形態に係るインバータの動作について説明する。時刻t0において、正弦波の主回路電流(a)がゼロから上昇し始めると、ユニポーラ型ダイオード14の逆回復時の電圧変化率(d)も上昇する。このとき、主回路電流検出カレントトランス18で検出された主回路電流が所定値より小さい場合は、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームのゲート抵抗切替信号(c)はONとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gのみの抵抗値である。

【0050】

やがて、時刻t1において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)よりも大きくなると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にOFF信号を伝達する。すなわち、下アームのゲート抵抗切替信号(c)はONからOFFとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がOFF状態のため、ゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となる。そのため、Si−IGBT12のターンオン時の電流変化率(di/dt)が小さくなり、逆並列に接続されたユニポーラ型ダイオード14の逆回復時の電圧変化率(d)、すなわちリカバリdv/dtは、時刻t1以降においては、破線のレベル(図5(d)の従来例のレベル)から実線のレベル(図5(d)の第1実施形態のレベル)に低減する。その結果、Si−IGBT11のコレクタ−エミッタ間電圧Vceのサージ電圧(リンギング電圧)を低減させることができる。

【0051】

そして、時刻t1から時刻t2までは、主回路電流(a)の上昇に伴って、ユニポーラ型ダイオード14の逆回復時の電圧変化率(d)、すなわち、リカバリdv/dtは上昇するが、Si−IGBT12のゲート抵抗値は、ゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となるため、ユニポーラ型ダイオード14のリカバリdv/dtは従来例より低いレベルで推移する。

【0052】

次に、時刻t2以降においては、主回路電流(a)の低下に伴って、ユニポーラ型ダイオード14の逆回復時の電圧変化率(d)、すなわち、リカバリdv/dtは低下する。そして、時刻t3において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)まで低下すると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームのゲート抵抗切替信号(c)はOFFからONとなる。

【0053】

したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gの抵抗値のみとなる。その結果、時刻t3以降においてはリカバリdv/dtは従来例と同じレベルまで上昇するが、このときは主回路電流(a)が所定の閾値Ith1より低下しているのでリカバリdv/dtの値も低くなっている。そして、時刻t4において主回路電流(a)がゼロになるとリカバリdv/dtの値もゼロとなる。

【0054】

なお、主回路電流検出回路50は、主回路電流検出カレントトランス18に限らず、シャント抵抗やセンス機能付きのIGBTなどを使用する回路を用いることで、主回路電流を容易に検出することができる。また、主回路電流を検出する箇所は、図1で示した主回路19の位置に限ることはなく、Si−IGBT12のエミッタ、Si−IGBT12のコレクタ、ユニポーラ型ダイオード14、または上アーム側のユニポーラ型ダイオード13などの箇所でも検出することが可能である。なお、上アーム側のユニポーラ型ダイオード13で主回路電流を検出できるのは、下アームのSi−IGBT12がON状態のときに図示しない負荷を通った主回路電流が上アームのユニポーラ型ダイオード13を還流するためである。すなわち、主回路電流を検出する箇所は、下アームのSi−IGBT12と逆並列のユニポーラ型ダイオード14とからなるパワー半導体モジュールに流れる電流を検出できる箇所であれば、いずれの箇所でもよい。

【0055】

図6は、ユニポーラ型ダイオード使用時の第1実施形態と従来例の動作波形図であり、(a−1)と(a−2)は第1実施形態、(b−1)と(b−2)は従来例を示す。すなわち、図6は、主回路電流の大電流時におけるユニポーラ型ダイオードを用いた場合のパワー半導体スイッチング素子のターンオン時の動作波形図であり、(a−1)は第1実施形態のコレクタ−エミッタ間電圧Vce、(a−2)は第1実施形態のコレクタ電流Ic、(b−1)は従来例のコレクタ−エミッタ間電圧Vce、(b−2)は従来例のコレクタ電流Ic、の各動作波形を表わしている。なお、横軸は、いずれの図も時間を示し、縦軸は、それぞれ、パワー半導体スイッチング素子(下アームのSi−IGBT12)のコレクタ−エミッタ間電圧Vce及びコレクタ電流Icを示している。また、ユニポーラ型ダイオードとしてはSiC−SBDを用いている。

【0056】

図6の(b−1),(b−2)に示すように、従来例では、パワー半導体スイッチング素子のゲート抵抗値が固定されているために、主回路電流が大電流のときはパワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vce(すなわち、ユニポーラ型ダイオードのリカバリdv/dt)が大きくなり、パワー半導体スイッチング素子のコレクタ電流Icにやや大きい跳ね上がりの振動(リンギング)が発生している。

【0057】

ところが、第1実施形態の場合は、主回路電流が大電流のときにはパワー半導体スイッチング素子(つまり、Si−IGBT12)のゲート抵抗値を大きくしているので(ゲート抵抗31の抵抗値とゲート抵抗12gの抵抗値の和にしているので)、Si−IGBT12のゲート抵抗値が一定である従来例に比べて、図6の(a−1),(a−2)に示すように、パワー半導体スイッチング素子(Si−IGBT12)のコレクタ電流Icの跳ね上がりの振動(リンギング)は小さくなっている。このようにして、主回路電流の大きさに応じて2段階でゲート抵抗値を変化させることにより、主回路電流の大電流時におけるユニポーラ型ダイオードのリカバリdv/dtを低減させることができるため、コレクタ電流Icのリンギングを抑えてインバータ装置1aから発生する放射ノイズを低減させ、負荷であるモータの絶縁抵抗の長寿命化を実現することが可能となる。

【0058】

言い換えると、主回路電流が大電流時にはパワー半導体スイッチング素子のゲート抵抗値を大きくすることによって、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が大きくなるため、パワー半導体スイッチング素子のターンオン時のゲート信号の立ち上がり波形が緩やかになる。その結果、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが小さくなり(つまり、ユニポーラ型ダイオードのリカバリdv/dtが小さくなり)、図6の(a−2)のようにコレクタ電流Icのリンギングを小さくすることができる。

【0059】

《第2実施形態》

図7は、本発明の第2実施形態におけるインバータ装置の構成図である。図7に示す第2実施形態のインバータ装置1bについては、図1に示す第1実施形態のインバータ装置1aと同じ構成要素は同一の符号が付されている。第2実施形態のインバータ装置1bが第1実施形態のインバータ装置1aと異なる点は、主回路電流検出回路50から制御回路40へ制御信号線51が接続されているところである。

【0060】

すなわち、前記の第1実施形態のインバータ装置1aにおいては、主回路電流検出回路50が、主回路電流検出カレントトランス18の検出した主回路電流の大きさに基づいてパワー半導体スイッチング素子(つまり、Si−IGBT11,12)のゲート抵抗値を変化させ、そのパワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dt(つまり、ユニポーラ型ダイオードのリカバリdv/dt)を抑制していた。第2実施形態のインバータ装置1bでは、これに加えて、主回路電流検出回路50から制御回路40へ制御信号線51によって制御信号を伝達し、主回路電流検出カレントトランス18が検出した主回路電流の大きさに基づいてPWM信号のスイッチング回数を制御している。これによって、パワー半導体スイッチング素子のコレクタ電流Icの跳ね上がりの振動を抑制すると共に、PWM信号のスイッチングロスによる効率低下を抑制することができる。

【0061】

図8は、本発明の第2実施形態に係るインバータ装置の動作を示す各部の波形図であり、(a)は主回路電流Ic、(b)は第2実施形態の制御回路の下アームPWM信号、(c)は従来例の制御回路の下アームPWM信号、(d)は主回路電流が所定の閾値よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33のゲート端子へ送信する下アームのゲート抵抗切替信号、(e)は下アームのユニポーラ型ダイオード14の逆回復時の電圧変化率(リカバリdv/dt)を示している。いずれの図も横軸は時間を表わし、縦軸はそれぞれのレベルを表わしている。なお、主回路電流Ic(a)は、図示しない負荷から主回路19を通ってSi−IGBT12のコレクタ−エミッタに流れる電流(コレクタ電流Ic)の方向を正極として表わしている。さらに、第2実施形態の制御回路の下アームPWM信号(b)、及び従来例の制御回路の下アームPWM信号(c)は、それぞれ、主回路電流(a)を生成するために、駆動ロジック回路36を介して下アームのSi−IGBT12のゲート部分に供給される信号を示している。

【0062】

図8の時刻t0において、正弦波の主回路電流(a)がゼロから上昇し始めると、ユニポーラ型ダイオード14の出力電圧の電圧変化率(e)も上昇する。このとき、主回路電流検出カレントトランス18で検出された主回路電流が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)より小さい場合は、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームゲート抵抗切替信号(d)はONとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gの抵抗値のみとなる。

【0063】

やがて、時刻t1において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1よりも大きくなると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にOFF信号を伝達する。すなわち、下アームのゲート抵抗切替信号(d)はOFFとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がOFF状態のため、ゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となる。そのため、Si−IGBT12のターンオン時の電流変化率(di/dt)が小さくなり、逆並列に接続されたユニポーラ型ダイオード14の逆回復時の電圧変化率(e)、すなわちリカバリdv/dtは、時刻t1以降においては、図8(e)の破線のレベル(従来例のレベル)から実線のレベル(第2実施形態のレベル)に低減する。その結果、Si−IGBT12のコレクタ電流Icのリンギングを低減することができる。

【0064】

そして、時刻t1から時刻t2までは、主回路電流(a)の上昇に伴って、逆回復時の電圧変化率(e)、すなわち、リカバリdv/dtは上昇するが、Si−IGBT12のゲート抵抗値がゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となるために、ユニポーラ型ダイオード14のリカバリdv/dtは従来例より低いレベルで推移する。

【0065】

次に、時刻t2以降においては、主回路電流(a)の低下に伴って、ユニポーラ型ダイオード14の逆回復時の電圧変化率(e)、すなわち、リカバリdv/dtは低下する。そして、時刻t3において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)まで低下すると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームのゲート抵抗切替信号(d)はONとなる。

【0066】

したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gの抵抗値のみとなる。その結果、時刻t3以降においてリカバリdv/dtが従来例と同じレベルまで上昇するが、このときは主回路電流(a)が所定値より低下しているのでリカバリdv/dtの値も低くなっている。そして、時刻t4において主回路電流(a)がゼロになるとリカバリdv/dtの値もゼロとなる。

【0067】

さらに、本実施形態では、主回路電流検出回路50が、主回路電流検出カレントトランス18の検出した主回路電流の情報を制御回路40へ伝達している。これによって、制御回路40は、主回路電流の検出値が大きい場合には、駆動ロジック回路36へ出力するPWM信号の出力パルス数を少なくしている。

【0068】

すなわち、図8に示すように、パワー半導体スイッチング素子(Si−IGBT12)が駆動する電気角180度の間においては、通常は、従来例の制御回路の下アームPWM信号(c)に示すような、間引きのないPWM信号に基づいてSi−IGBT12のスイッチング制御を行うことにより、主回路電流(a)は正弦波の状態になる。しかし、このような間引きのないPWM信号で各パワー半導体スイッチング素子を駆動すると、スイッチング回数が多くなってパワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失が増加してしまう。

【0069】

そこで、図8における時刻t1から時刻t3の間は、主回路電流(a)が所定の閾値Ith1よりも大きくなる。この間は、制御回路40が、第2実施形態の制御回路の下アームPWM信号(b)に示すように、PWM信号の間引きを行い、出力パルス数を少なくする。これによって、主回路電流(a)が大電流のときは、パワー半導体スイッチング素子(Si−IGBT12)のスイッチング回数を低減させてそのパワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失を減少させることができる。その結果、インバータ装置1bの効率低下を抑制することができる。

【0070】

以上述べたように、通常は主回路電流が大きい場合に、ゲート抵抗値を大きくすると、パワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失が増大するが、主回路電流が大きいときには、制御回路40から駆動ロジック回路36へ出力するPWM信号の出力パルス数を小さくすることによって、パワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失を低減させることができる。このため、本実施形態を適用したインバータ装置1bでは、インバータ装置1bで発生する放射ノイズを低減させて負荷であるモータの絶縁抵抗の長寿命化を実現させることができると共に、インバータ装置1bの電力損失を低減させることができる。

【0071】

なお、PWM信号の間引きを多くすることによってパワー半導体スイッチング素子のスイッチング損失を減少させて効率を向上させることができるが、その反面、PWM信号の間引きを多くすることによって主回路電流に歪みが生じて正弦波を維持できなくなるというトレードオフの関係がある。したがって、実機によるカットアンドトライによって、最適なトレードオフの関係になるようにPWM信号のスイッチング回数の最適な低減化を行うことが望ましい。

【0072】

《第3実施形態》

図9は、本発明の第3実施形態におけるインバータ装置の構成図である。図9に示す第3実施形態のインバータ装置1cについては、図7に示す第2実施形態のインバータ装置1bと同じ構成要素は同一の符号が付されている。第3実施形態のインバータ装置1cが第2実施形態のインバータ装置1bと異なる点は、パワー半導体スイッチング素子のゲート抵抗値(ゲートインピーダンス)を3段階で切り替えているところである。

【0073】

先ず、図9に示す第3実施形態に係るインバータ装置1cの構成について、重複説明を避けて説明するする。図9に示すように、本発明の第3実施形態におけるインバータ装置1cは、インバータ主回路10、上アーム駆動/制御回路20a、下アーム駆動/制御回路30a、制御回路40、及び主回路電流検出回路50を備えて構成されている。なお、インバータ主回路10と制御回路40は図1と同じであるので構成の説明は省略する。

【0074】

下アーム駆動/制御回路30aの回路構成は次のようになっている。すなわち、下アーム駆動/制御回路電源37の正極が、ゲート抵抗切替用pMOS33aのソース端子とゲート抵抗切替用pMOS33bのソース端子とに接続されている。そして、ゲート抵抗切替用pMOS33aのソース端子がゲート抵抗31aの一端に接続され、該ゲート抵抗切替用pMOS33aのドレイン端子が前記ゲート抵抗31aの他端に接続されている(すなわち、ゲート抵抗切替用pMOS33aとゲート抵抗31aとが並列に接続されている)。さらに、ゲート抵抗切替用pMOS33aのドレイン端子がnpnトランジスタ34のコレクタ端子に接続されている。また、ゲート抵抗切替用pMOS33bのドレイン端子はゲート抵抗31bの一端に接続され、該ゲート抵抗31bの他端はnpnトランジスタ34のコレクタ端子に接続されている。

【0075】

また、該npnトランジスタ34のエミッタ端子は、pnpトランジスタ35のエミッタ端子に接続されると共に、インバータ主回路10におけるゲート抵抗12gの一方の端子に接続されている。さらに、該pnpトランジスタ35のコレクタ端子はゲート抵抗32の一端に接続され、該ゲート抵抗32の他端は下アーム駆動/制御回路電源38の負極に接続されている。そして、該下アーム駆動/制御回路電源38の正極は、前記下アーム駆動/制御回路電源37の負極に接続されると共にグランドに接続されている。また、制御信号系としては、ゲート抵抗切替用pMOS33aのゲート端子とゲート抵抗切替用pMOS33bのゲート端子が、それぞれ、主回路電流検出回路50の制御端子に接続されている。さらに、npnトランジスタ34のベース端子とpnpトランジスタ35のベース端子は、駆動ロジック回路36の制御端子に接続され、該駆動ロジック回路36の信号入力端子は制御回路40に接続されている。

【0076】

このような回路構成において、駆動ロジック回路36は、制御回路40からの駆動信号(例えば、PWM信号)を入力して、npnトランジスタ34とpnpトランジスタ35とを交互にスイッチング動作させる。また、npnトランジスタ34とpnpトランジスタ35とは、駆動ロジック回路36の駆動信号(例えば、PWM信号)を増幅して下アームのSi−IGBT12をスイッチング駆動(例えば、PWM駆動)させる。

【0077】

なお、上アーム駆動/制御回路20aの回路構成は、下アーム駆動/制御回路30aの回路構成と同じであるので、重複する説明は省略する。

【0078】

すなわち、図9に示すように、本発明の第3実施形態におけるインバータ装置1cは、下アームのSi−IGBT12のゲート抵抗値を3段階で切り替えるために、ゲート抵抗31aに並列に接続されたゲート抵抗切替用pMOS33aと、ゲート抵抗31bに直列に接続されたゲート抵抗切替用pMOS33bとが設けられている。同様にして、上アームのSi−IGBT11のゲート抵抗値を3段階で切り替えるために、ゲート抵抗21aに並列に接続されたゲート抵抗切替用pMOS23aと、ゲート抵抗21bに直列に接続されたゲート抵抗切替用pMOS23bとが設けられている。その他の構成要素は図7に示す第2実施形態のインバータ装置1bと同じである。

【0079】

図10は、本発明の第3実施形態に係るインバータ装置の動作を示す各部の波形図であり、(a)は主回路電流、(b)は第3実施形態の制御回路の下アームPWM信号、(c)は従来例の制御回路の下アームPWM信号、(d)は主回路電流が第1の閾値よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33aのゲート端子へ送信する下アームの第1ゲート抵抗切替信号、(e)は主回路電流が第2の閾値(但し、第2の閾値>第1の閾値)よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33bのゲート端子へ送信する下アームの第2ゲート抵抗切替信号、(f)は下アームのユニポーラ型ダイオード14の逆回復時の電圧変化率(リカバリdv/dt)を示している。いずれの図も横軸は時間を表わし、縦軸はそれぞれのレベルを表わしている。なお、主回路電流(a)は、図示しない負荷から主回路19を通ってSi−IGBT12のコレクタ−エミッタに流れる電流(コレクタ電流Ic)の方向を正極として表わしている。さらに、第3実施形態の制御回路の下アームPWM信号(b)、及び従来例の制御回路の下アームPWM信号(c)は、それぞれ、主回路電流(a)を生成するために、駆動ロジック回路36を介して下アームのSi−IGBT12のゲート部分へ供給されるPWM信号である。

【0080】

図10の時刻t0において、正弦波の主回路電流(a)がゼロから上昇し始めると、ユニポーラ型ダイオード14の逆回復時の電圧変化率(f)、すなわち、リカバリdv/dtも上昇する。このとき、主回路電流検出カレントトランス18で検出された主回路電流(a)が第1の閾値Ith1(例えば、主回路電流のピーク値の1/3)より小さい場合は、主回路電流検出回路50はゲート抵抗切替用pMOS33a,33bの各制御端子にON信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)と第2ゲート抵抗切替信号(e)とが共にONとなる。これにより、npnトランジスタ34のコレクタ端子と、下アーム駆動/制御回路電源37の正極との間の抵抗値は0となるので、インバータ主回路10における下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗12gの抵抗値のみとなる。

【0081】

やがて、時刻t1において、主回路電流検出カレントトランス18で検出された主回路電流(a)が第1の閾値Ith1(例えば、主回路電流のピーク値の1/3)よりも大きくなると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33bの制御端子にON信号を伝達したまま、ゲート抵抗切替用pMOS33aの制御端子にOFF信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)がOFFで、第2ゲート抵抗切替信号(e)がONとなる。

【0082】

これによって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aがOFF状態でゲート抵抗切替用pMOS33bがON状態であるため、ゲート抵抗31a、ゲート抵抗31bの並列接続による抵抗値とゲート抵抗12gの抵抗値との和となる。時刻t1以降のゲート抵抗値は、時刻t0〜t1のゲート抵抗値よりも大きい。そのため、Si−IGBT12のターンオン時の電流変化率(di/dt)が小さくなり、逆並列に接続されたユニポーラ型ダイオード14の逆回復時の電圧変化率(f)、すなわちリカバリdv/dtは、時刻t1以降においては、図10(f)の破線のレベル(従来例のレベル)から実線のレベル(第3実施形態のレベル)に低減する。その結果、Si−IGBT12のコレクタ電流Icのリンギングを低減させることができる。

【0083】

さらに、時刻t2において、主回路電流検出カレントトランス18で検出された主回路電流(a)が第2の閾値Ith2(例えば、主回路電流のピーク値の2/3)より大きくなると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33aの制御端子にOFF信号を伝達したまま、ゲート抵抗切替用pMOS33bの制御端子にもOFF信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)がOFF、第2ゲート抵抗切替信号(e)がOFFとなる。

【0084】

これによって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aとゲート抵抗切替用pMOS33bが共にOFF状態であるため、ゲート抵抗31aの抵抗値とゲート抵抗12gの抵抗値との和となる。時刻t2以降のゲート抵抗値は、時刻t1〜t2のゲート抵抗値よりも大きい。そのため、時刻t2以降においては、Si−IGBT12のターンオン時の電流変化率(di/dt)がさらに小さくなる。すなわち、時刻t2以降において、ユニポーラ型ダイオード14の逆回復時の電圧変化率(e)、つまり、リカバリdv/dtがさらに減少する。これによって、インバータ装置1cのサージ電圧(リンギング電圧)をさらに低減させることが可能となる。

【0085】

また、時刻t2から時刻t3までは主回路電流(a)の上昇に伴ってリカバリdv/dtは上昇するが、Si−IGBT12のゲート抵抗値は、ゲート抵抗31aの抵抗値とゲート抵抗12gの抵抗値との和となる。そのために、図10(f)の実線で示す第3実施形態のリカバリdv/dtは、破線で示す従来例のリカバリdv/dtに比べてかなり小さな値となっている。

【0086】

次に、時刻t3から時刻t4までは主回路電流(a)の減少に伴って逆回復時の電圧変化率(f)、すなわち、リカバリdv/dtも減少し、時刻t4において主回路電流(a)が第2の閾値Ith2(例えば、主回路電流のピーク値の2/3)よりも小さくなると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33aの制御端子にOFF信号を伝達したまま、ゲート抵抗切替用pMOS33bの制御端子にはON信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)がOFFで、第2ゲート抵抗切替信号(e)がONとなる。

【0087】

これによって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aがOFF状態で、ゲート抵抗切替用pMOS33bがONの状態であるため、ゲート抵抗31a、ゲート抵抗31bの並列接続による抵抗値とゲート抵抗12gの抵抗値との和となる。時刻t4以降のゲート抵抗値は、時刻t3〜t4のゲート抵抗値よりも小さい。したがって、時刻t4以降においても、第3実施形態のリカバリdv/dtは、従来例の破線のレベルより低い実線のレベル(図10(f)の第3実施形態のレベル)に低減した状態で減少する。

【0088】

次に、時刻t5になると、主回路電流検出カレントトランス18で検出された主回路電流が第1の閾値Ith1(例えば、主回路電流のピーク値の1/3)よりも小さくなるので、時刻t5以降においては、主回路電流検出回路50は、ゲート抵抗切替用pMOS33aとゲート抵抗切替用pMOS33bとにON信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)と第2ゲート抵抗切替信号(e)が共にONとなる。したがって、インバータ主回路10の下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aとゲート抵抗切替用pMOS33bとが共にON状態であるため、ゲート抵抗12gの抵抗値のみとなる。時刻t5以降のゲート抵抗値は、時刻t4〜t5のゲート抵抗値よりも小さい。これによって、主回路電流(a)が第1の閾値Ith1以下のときは、ユニポーラ型ダイオード14の逆回復時の電圧変化率(f)、つまり、リカバリdv/dtは従来例と同じ値で低下するが、このときは、主回路電流(a)が小さいためにリカバリdv/dtも小さくなっているので、インバータ装置1cにサージ電圧(リンギング電圧)が生じるおそれはない。

【0089】

すなわち、前記の図6で示したように、従来例のようにゲート抵抗値が固定されている場合であって、パワー半導体スイッチング素子に大電流が流れているときには、逆並列に接続されたユニポーラ型ダイオードのリカバリdv/dtが大きい。そのために、図6(b−2)のようにコレクタ電流Icに大きな振動電流が発生する。ところが、本発明の第3実施形態の場合は、パワー半導体スイッチング素子の電流が大きくなると3段階でゲート抵抗を大きくするため、ユニポーラ型ダイオード14のリカバリdv/dtをきめ細かに低く抑えることができる。これによって、図6(a−2)のようにコレクタ電流Icには大きな振動電流は発生しなくなる。また、このようにしてリカバリdv/dtを低減させることにより、インバータ装置1cから発生する放射ノイズを低減させて、モータの絶縁抵抗の長寿命化を実現することができる。

【0090】

言い換えると、ゲート抵抗値を多段階に変化させてユニポーラ型ダイオードのリカバリdv/dtを多段階で制御することにより、リカバリdv/dtの主回路電流に対する依存性をきめ細かに低減させることができる。これにより、主回路電流が変化してもリカバリdv/dtをより平坦な値に保持することができるので、インバータ装置1cから発生する放射ノイズを低減させて、モータの絶縁抵抗のさらなる長寿命化を実現することができる。

なお、ゲート抵抗切替用pMOSとゲート抵抗との並列組み合わせ(例えば、ゲート抵抗切替用pMOS33aとゲート抵抗31aとの並列組み合わせ)の一組に対して、ゲート抵抗切替用pMOSとゲート抵抗との直列組み合わせ(例えば、ゲート抵抗切替用pMOS33bとゲート抵抗31bとの直列組み合わせ)を多段に設けることにより、ゲート抵抗の抵抗値を何段階にも可変させることが可能である。

【0091】

さらに、本発明の第3実施形態では、第2実施形態と同様に、主回路電流検出回路50が、主回路電流検出カレントトランス18の検出した主回路電流の検出情報を制御回路40へ伝達している。これによって、主回路電流の検出値が大きい場合には、制御回路40は、駆動ロジック回路26,36へ出力するPWM信号のパルス数を低減させている。

【0092】

さらに詳しく説明すると、図10に示すように、主回路電流(a)が第1の閾値Ith1より小さい期間(時刻t0〜t1、及び時刻t5〜t6)においては、第3実施形態の制御回路の下アームPWM信号(b)は、従来例の制御回路の下アームPWM信号(c)と同じパルス数であって、PWM信号のパルス数を低減させていない。そして、主回路電流(a)が第1の閾値Ith1より大きくて第2の閾値Ith2より小さい期間(時刻t1〜t2、及び時刻t4〜t5)においては、第3実施形態の制御回路の下アームPWM信号(b)は、従来例の制御回路の下アームPWM信号(c)よりわずかにパルス数を低減させる。

【0093】

さらに、主回路電流(a)が第2の閾値Ith2より大きい期間(時刻t2〜t4)においては、第3実施形態の制御回路の下アームPWM信号(b)は、従来例の制御回路の下アームPWM信号(c)に比べてPWM信号のパルス数をより多く低減させている。

【0094】

すなわち、一般的には、主回路電流が大きい場合にゲート抵抗値を大きくすると、パワー半導体スイッチング素子のスイッチング損失が増大するが、本実施形態のように、主回路電流が大きいときには制御回路40から出力するPWM信号のパルス数を低減させることにより、パワー半導体スイッチング素子のスイッチング損失を低減させることができる。しかも、主回路電流の大きさに応じて3段階でPWM信号のパルス数を低減させることができる。そのため、本実施形態を適用したインバータ装置では、そのインバータ装置から発生する放射ノイズを低減させてモータの絶縁抵抗の長寿命化を実現すると共に、主回路電流の大きさに応じてインバータ装置のスイッチング損失をきめ細かに低減させることもできる。

【0095】

《まとめ》

以上説明したように、本発明のインバータ装置は、パワー半導体スイッチング素子とユニポーラ型ダイオードとが逆並列に接続されたインバータ装置であって、主回路電流が所定値より大きいときに、パワー半導体スイッチング素子を駆動するゲート駆動回路のゲート抵抗値を大きくしてユニポーラ型ダイオードのリカバリdv/dtを抑制し、ターンオン損失、リカバリ損失、及びリンギングによるノイズを低減させることができる。また、主回路電流が所定値より大きいときに、パワー半導体スイッチング素子をPWM制御するスイッチング回数を低減させてスイッチング損失を低減させることができる。

【0096】

さらに詳しく述べると、インバータ装置の還流用のダイオードとして、SiCなどのワイドギャップ半導体であるショットキーバリアダイオード(SBD)、すなわちユニポーラ型ダイオードを用いて、ターンオン損失やリカバリ損失の低減化と高耐圧化を図っている。このとき、ユニポーラ型ダイオードのリカバリdv/dtは電流値に比例して大きくなるので、主回路電流が所定値より大きい場合にはパワー半導体スイッチング素子のゲート抵抗値(ゲートインピーダンス)を大きくしている。したがって、主回路電流が所定値より大きくなっても、パワー半導体スイッチング素子のコレクタ電流のリンギングが抑制され、インバータから発生する放射ノイズを低減させることができる。その結果、インバータ装置の負荷であるモータの絶縁抵抗の長寿命化を実現させることができる。また、主回路電流が所定値より大きい場合には、インバータ装置を駆動するためのPWM信号のパルス数を少なくすることで、放射ノイズの低減化とインバータ装置のスイッチング損失を低減することができる。言い換えると、リカバリdv/dtに起因するリンギングを抑制すると共にスイッチング損失を低減させたインバータ装置を提供することができる。

【0097】

ここで、請求項で述べる電流検出手段は、主回路電流検出カレントトランス(CT)18と主回路電流検出回路50とによって実現される。また、ゲートインピーダンスは、ゲート抵抗11g,12g,21,22,21a,21b,31,32,31a,31bであって、ゲートインピーダンス切替手段は、ゲート抵抗切替用pMOS23,23a,23b,33,33a,33bによって実現される。さらに、スイッチング回数低減手段は、PWM信号を生成する制御回路40の内部機能によって実現される。

【0098】

また、パワー半導体スイッチング素子は、シリコン(Si)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、またはダイヤモンドなどの材料によって生成され、絶縁ゲートバイポーラトランジスタ(Insulated Gate Bipolar Transistor:IGBT)、接合型電界効果トランジスタ(Junction Field Effect Transistor:JFET)、金属酸化膜型電界効果トランジスタ(Metal Oxide Semiconductor-Field Effect Transistor:MOSFET)、などのパワー半導体デバイスとして実現される。

【0099】

さらに、ユニポーラ型ダイオードは、Si、SiC、GaN、またはダイヤモンドなどのワイドギャップ半導体などから成り、例えば、ショットキーバリアダイオード(Schottky Barrier Diode:SBD)などとして実現される。このようなSBDは、リカバリdv/dtが電流値に比例して大きくなる特性を有している。

【0100】

以上、本発明に係るインバータ装置の実施形態について具体的に説明したが、本発明は前記した各実施形態の内容に限定されるものではなく、その要旨を逸脱しない範囲で種々の変更が可能であることは言うまでもない。言い換えると、上述した各実施形態は、本発明の内容を分かりやすく説明するために詳細に例示したものであり、必ずしも前記で説明した全ての構成を備えるものに限定されるものではない。また、ある実施形態の構成の一部を他の実施形態の構成に置き換えることも可能であり、さらに、ある実施形態の構成に他の実施形態の構成を加えることも可能である。例えば、インバータ装置の主回路電流が大きくなるにしたがってゲート抵抗値を段階的に大きくするように切り替えるのではなく、主回路電流が大きくなるにしたがってゲート抵抗値が連続的に大きくなるように連続可変させてもよい。

【産業上の利用可能性】

【0101】

本発明のインバータ装置によれば、パワー半導体スイッチング素子のターンオン損失及びスイッチング損失や、還流用ダイオードのリカバリ損失を低減させたり、スイッチングノイズを低減させることができるので、品質の高い電源が要求される各種機器としても有効に利用することが可能である。

【符号の説明】

【0102】

1a,1b,1c インバータ装置

10 インバータ主回路

11,12 Si−IGBT(パワー半導体スイッチング素子)

11g,12g,21,22,21a,21b,31,32,31a,31b ゲート抵抗(ゲートインピーダンス)

13,14 ユニポーラ型ダイオード

15 主回路電源

16,17 主回路インダクタンス

18 主回路電流検出カレントトランス(電流検出手段)

19 主回路

20,20a 上アーム駆動/制御回路

23,23a,23b,33,33a,33b ゲート抵抗切替用pMOS(ゲートインピーダンス切替手段)

24,34 npnトランジスタ

25,35 pnpトランジスタ

26,36 駆動ロジック回路

27,28,37,38 駆動/制御回路電源

30,30a 下アーム駆動/制御回路

40 制御回路(スイッチング回数低減手段)

50 主回路電流検出回路(電流検出手段)

51 制御信号線

【技術分野】

【0001】

本発明は、半導体スイッチング素子とダイオードとが逆並列に接続された半導体モジュールを備えたインバータ装置に関し、特に、パワー半導体スイッチング素子に、炭化ケイ素や窒化ガリウムなどのワイドギャップ半導体のユニポーラデバイスから成るダイオードが逆並列に接続されたパワー半導体モジュールに対してゲート駆動を行うインバータ装置に関する。

【背景技術】

【0002】

近年、電子が存在しない禁止帯領域(バンドギャップエリア)の幅が広いワイドギャップ半導体素子として、炭化ケイ素(以下、SiCという)や窒化ガリウム(以下、GaNという)などの材料を用いた半導体素子が注目を浴びている。これらの材料は、通常の半導体素子の材料として使用されているシリコン(以下、Siという)より約10倍程度の高い絶縁破壊電圧強度を有している。したがって、これらのワイドギャップ半導体素子は、耐圧を確保するためのドリフト層を、Siを用いた通常の半導体素子に対して1/10程度まで薄くすることができるため、パワーデバイスの低オン電圧化を実現することが可能である。これにより、Siを用いた半導体素子の場合ではバイポーラ素子しか使用できないような高耐圧領域でも、SiCなどを用いたワイドギャップ半導体素子では、ユニポーラ素子を使用することができる。

【0003】

また、インバータ装置に用いられるパワー半導体モジュールとしては、スイッチングデバイス(半導体スイッチング素子)に逆並列に還流用のダイオードが接続されている。このとき、従来のパワー半導体モジュールでは、還流用のダイオードとしてSi−PiNダイオード(p-Intrinsic-n Diode)が使用されている。このSi−PiNダイオードはバイポーラ型の半導体素子(バイポーラ型ダイオード)であり、順方向バイアスで大電流を通電させる場合、伝導度変調により順方向電圧降下が低くなるような構造となっている。

【0004】

しかし、バイポーラ型ダイオードであるSi−PiNダイオードは、順方向バイアス状態から逆バイアス状態に至る過程で、伝導度変調によりSi−PiNダイオードに残留したキャリアが逆回復電流(リカバリ電流)として発生するという特性を有する。このとき、Si−PiNダイオードにおいては、残留するキャリアの寿命が長いために逆回復電流が大きくなる。そのため、この逆回復電流により、パワー半導体スイッチング素子のターンオン時の損失(以下、ターンオン損失Eonという)や、還流用のダイオードが逆回復したときにそのダイオードに発生する逆回復損失(以下、リカバリ損失Errという)が大きくなるという欠点がある。

【0005】

一方、ショットキーバリアダイオード(以下、SBDという)はユニポーラ型の半導体素子(ユニポーラ型ダイオード)であり、伝導度変調によるキャリア発生が殆ど生じないので、インバータ装置でSBDが使用される場合は、還流用のダイオードの逆回復電流(リカバリ電流)が非常に小さいために、パワー半導体スイッチング素子のターンオン損失Eonや還流用のダイオードのリカバリ損失Errを小さくすることができる。

【0006】

このとき、Siは絶縁破壊電界強度が低いため、高耐圧を持たせる構造でユニポーラ型ダイオードのSBDを作製すると、通電時に大きな抵抗が生じるために、Si−SBDでは耐圧は200V程度が限界である。一方、SiCはSiの10倍の絶縁破壊電界強度を有するために、SiCを用いることにより200Vよりさらに高耐圧のSiC−SBDを実現することが可能となり、かつ、ターンオン損失Eonやリカバリ損失Errを低減させることで、インバータの損失を低減させて効率の高いパワー半導体モジュールを実現させることができる。

【0007】

また、還流用のダイオードのリカバリ損失Errは、そのダイオードの逆回復時の電圧変化率、すなわち、還流用のダイオードのリカバリdv/dtの大きさに起因することが知られている。図2は、ユニポーラ型ダイオードとバイポーラ型ダイオードのリカバリdv/dtの電流依存性を示す特性図であり、横軸に主回路電流(I)、縦軸にリカバリdv/dtを示している。さらに詳しく述べると、図2は、ユニポーラ型ダイオードとしてSiC−SBDを用いた場合と、バイポーラ型ダイオードとしてSi−PiNダイオードを用いた場合の、それぞれのリカバリdv/dtの電流依存性を示している。

【0008】

すなわち、還流用のダイオードのリカバリdv/dtの電流依存性は、バイポーラ型ダイオードを用いた場合には、図2の特性(a)に示すように電流値に反比例し、ユニポーラ型ダイオードを用いた場合には、図2の特性(b)に示すように電流値に比例し、その変化傾向も顕著であることが広く知られている。

【0009】

このような前提条件に基づいて、パワー半導体スイッチング素子と逆並列にバイポーラ型ダイオードを用いた電力変換器のゲート駆動回路が、例えば、特許文献1などに開示されている。この技術に開示されたゲート駆動回路では、パワー半導体スイッチング素子と逆並列にバイポーラ型ダイオードを用いているために、図2の特性(a)に示すように、ターンオン時の主回路電流Iが小さい場合にはリカバリdv/dtが大きいために、パワー半導体スイッチング素子のゲート抵抗値を大きくして発生ノイズを低減させて、パワー半導体スイッチング素子などの素子破壊を防いでいる。また、主回路電流Iが大きい場合には、リカバリdv/dtが小さいためにゲート抵抗値を小さくしてターンオン損失を抑制している。

【0010】

ここで、還流用のダイオードはパワー半導体スイッチング素子と逆並列に接続されているために、そのダイオードのリカバリdv/dtは、パワー半導体スイッチング素子のdv/dtと同期している。したがって、パワー半導体スイッチング素子のdv/dtを抑えることで、そのダイオードのリカバリdv/dtも抑えることが可能になる。パワー半導体スイッチング素子のdv/dtは、ゲート抵抗値を大きくすることでゲートに流れる電流値を制限してゲート電圧の立ち上がりを遅くすることができ、これによりパワー半導体スイッチング素子のdv/dtも抑えることが知られている。したがって、還流用のダイオードのリカバリdv/dtを制御するためには、これと同期するパワー半導体スイッチング素子のゲート抵抗値、すなわちゲートインピーダンスを制御することが有用である。特許文献1においては、この性質を利用してバイポーラ型ダイオードのリカバリdv/dtの制御を行っている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開平11−69779号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

すなわち、前記特許文献1のゲート駆動方式では、パワー半導体スイッチング素子と逆並列に接続された還流用のダイオードとしてバイポーラ型ダイオードを使用しているため、パワー半導体スイッチング素子のターンオン時の主回路電流値が小さい場合においては、そのパワー半導体スイッチング素子のゲート抵抗値を大きくしてバイポーラ型ダイオードのリカバリdv/dtを小さくし、パワー半導体スイッチング素子のターンオン時の主回路電流の振動を抑えることでノイズの低減や素子破壊の抑制を行っている。また、パワー半導体スイッチング素子のターンオン時の主回路電流値が大きい場合においては、パワー半導体スイッチング素子のゲート抵抗値を小さくすることでターンオンを高速化してターンオン損失を抑制している。このような制御方法は、図2の特性(a)に示すようなリカバリdv/dtの電流依存性を有したバイポーラ型ダイオードに対しては有効である。

【0013】

しかしながら、SiC−SBDのようなユニポーラ型ダイオードにおいては、図2の特性(b)に示すように、バイポーラ型ダイオードのリカバリdv/dtの電流依存性と大きく異なっている。言い換えると、ユニポーラ型ダイオードとしてSiC−SBDを用いることで低減できる還流用のダイオードのリカバリ損失Errにおいて、このリカバリ損失Errの要因となる還流用のダイオードのリカバリdv/dtは、図2の特性(b)に示すように、電流値に比例して大きくなり、その電流依存性はバイポーラ型ダイオードに比べて顕著である。したがって、ユニポーラ型ダイオードを用いた場合は、バイポーラ型ダイオードを用いた場合のように大電流時にゲート抵抗値を小さくするような駆動制御を行うことができない。これについて、以下、詳細に説明する。

【0014】

図3は、バイポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は従来例、(b−1)と(b−2)は特許文献1適用時を示す。すなわち、図3は、主回路電流の大電流時においてバイポーラ型ダイオードを用いた場合の、パワー半導体スイッチング素子のターンオン時の動作波形図であり、(a−1)は従来例であるゲート抵抗値を変えない場合のコレクタ−エミッタ間電圧Vce、(a−2)は従来例であるゲート抵抗値を変えない場合のコレクタ電流Ic、(b−1)は特許文献1を適用してゲート抵抗値を小さくした場合のコレクタ−エミッタ間電圧Vce、(b−2)は特許文献1を適用してゲート抵抗値を小さくした場合のコレクタ電流Icの動作波形を表わしている。なお、横軸は、いずれの図も時間を示し、縦軸は、それぞれ、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vce及びコレクタ電流Icを示している。また、バイポーラ型ダイオードとしてはSi−PiNダイオードを用いている。なお、当該バイポーラ型ダイオードは、パワー半導体スイッチング素子に逆並列に接続されている。

【0015】

すなわち、パワー半導体スイッチング素子に逆並列にバイポーラ型ダイオードを用いたインバータ装置に所定値以上の大電流が流れている場合は、図3(a−1)のように大電流時にはパワー半導体スイッチング素子におけるコレクタ−エミッタ間電圧Vceのdv/dtが小さいため(つまり、バイポーラ型ダイオードのリカバリdv/dtが小さいため)、特許文献1を適用してゲート抵抗値を小さくすると、図3(b−1)のようにパワー半導体スイッチング素子におけるコレクタ−エミッタ間電圧Vceのdv/dtが大きくなり(つまり、バイポーラ型ダイオードのリカバリdv/dtが大きくなり)ターンオン損失を低減させることができる。

【0016】

さらに、詳しく述べると、パワー半導体スイッチング素子のゲート抵抗値が大きい場合には、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が大きいために、ターンオン時(時刻t1)におけるゲート信号の立ち上がり波形が緩やかになるので、図3(a−1)のように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが小さくなる。すなわち、コレクタ−エミッタ間電圧Vceの立ち下がりが緩やかになる。そこで、特許文献1を適用してゲート抵抗値を小さくすると、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が小さくなる。そのため、ターンオン時(時刻t1)におけるゲート信号の立ち下がり波形が急峻になるので、図3(b−1)のように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが大きくなる。すなわち、コレクタ−エミッタ間電圧Vceの立ち下がりが急峻になる。その結果、パワー半導体スイッチング素子のターンオン損失を低減させることができる。

【0017】

図4は、ユニポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は従来例、(b−1)と(b−2)は特許文献1適用時を示す。すなわち、図4は、主回路電流の大電流時におけるユニポーラ型ダイオードを用いた場合のパワー半導体スイッチング素子のターンオン時の動作波形図であり、(a−1)は所定のゲート抵抗値の場合のコレクターエミッタ間電圧Vce、(a−2)は所定のゲート抵抗値の場合のコレクタ電流Ic、(b−1)は特許文献1を適用してゲート抵抗値を小さくした場合のコレクターエミッタ間電圧Vce、(b−2)は特許文献1を適用してゲート抵抗を小さくした場合のコレクタ電流Ic、の各動作波形を表わしている。なお、横軸は、いずれの図も時間を示し、縦軸は、それぞれ、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vce及びコレクタ電流Icを示している。また、ユニポーラ型ダイオードとしてはSiC−SBDを用いている。

【0018】

すなわち、パワー半導体スイッチング素子と逆並列にユニポーラ型ダイオードを用いたインバータ装置に大電流が流れている場合には、図2で示したようにユニポーラ型ダイオードのリカバリdv/dtが大きい。言い換えると、ユニポーラ型ダイオードを用いた場合は、図4(a−1)に示すように、大電流が流れている場合には、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが大きい(立下りが急峻である)。したがって、図4(a―2)に示すように、パワー半導体スイッチング素子のターンオン時におけるコレクタ電流Icに若干の跳ね上がりの振動(リンギング)が発生するおそれがある。

【0019】

そのため、ユニポーラ型ダイオードを用いた場合は、大電流が流れているときに特許文献1のゲート駆動方式を適用してゲート抵抗値をさらに小さくすると、図4(b−1)に示すように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtがさらに大きくなり、その結果、図4(b−2)に示すように、コレクタ電流Icのリンギングが非常に大きくなる。

【0020】

言い換えると、パワー半導体スイッチング素子のゲート抵抗値を小さくするにしたがって、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が益々小さくなるため、ターンオン時の時刻t1におけるゲート信号の立ち上がり波形が益々急峻になる。その結果、図4(b−1)のように、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが大きく(急峻に)なり、図4(b−2)のようにコレクタ電流Icのリンギングが益々大きくなる。

【0021】

すなわち、特許文献1のゲート駆動方式は、バイポーラ型ダイオードにおいては、リカバリdv/dtによるコレクタ電流の振動を抑制してターンオン損失を低減させることができるが、特許文献1のゲート駆動方式をユニポーラ型ダイオードに適用した場合には、大電流時においてコレクタ電流Icの跳ね上がりの振動(リンギング)が大きくなるおそれがある。言い換えると、特許文献1のゲート駆動方式をユニポーラ型ダイオードに適用した場合には、パワー半導体スイッチング素子のターンオン時の主回路電流値が小さい場合にゲート抵抗値を大きくすることでターンオン損失がさらに増え、主回路電流が大きい場合にゲート抵抗値を小さくすることで電流値に比例して高速化されていたリカバリdv/dtがさらに大きくなり、インバータから発生する放射ノイズが増大したり、負荷であるモータの絶縁劣化が早くなるなどの不具合が生じる。

【0022】

本発明は、このような事情に鑑みてなされたものであり、パワー半導体スイッチング素子に逆並列に接続される還流用のダイオードとしてユニポーラ型ダイオードを適用した場合でも、当該パワー半導体スイッチング素子のコレクタ電流のリンギングを抑制することができるインバータ装置を提供することを課題とする。

【課題を解決するための手段】

【0023】

前記課題を解決するために、本発明のインバータ装置は以下のように構成した。すなわち、本発明のインバータ装置は、パワー半導体スイッチング素子とユニポーラ型ダイオードとが逆並列に接続されたパワー半導体モジュールを備えたインバータ装置であって、前記パワー半導体モジュールに流れる電流を検出する電流検出手段と、前記電流検出手段が検出した電流値が所定値より大きいときに、前記パワー半導体スイッチング素子を駆動するゲート駆動回路のゲートインピーダンスを大きくするように、該ゲートインピーダンスを切り替えるゲートインピーダンス切替手段とを備えることを特徴とする。

【発明の効果】

【0024】

本発明によれば、還流用のダイオードとしてユニポーラ型ダイオードを用いた場合でも、コレクタ電流のリンギングを抑制することが可能なインバータ装置を提供することができる。

【図面の簡単な説明】

【0025】

【図1】本発明の第1実施形態におけるインバータ装置の構成図である。

【図2】ユニポーラ型ダイオードとバイポーラ型ダイオードのリカバリdv/dtの電流依存性を示す特性図である。

【図3】バイポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は従来例、(b−1)と(b−2)は特許文献1適用時を示す。

【図4】ユニポーラ型ダイオード使用時の従来例と特許文献1適用時の動作波形図であり、(a−1)と(a−2)は第1実施形態、(b−1)と(b−2)は従来例を示す。

【図5】本発明の第1実施形態に係るインバータ装置の動作を示す各部の波形図である。

【図6】ユニポーラ型ダイオード使用時の第1実施形態と従来例の動作波形図であり、(a−1)と(a−2)は第1実施形態、(b−1)と(b−2)は従来例を示す。

【図7】本発明の第2実施形態におけるインバータ装置の構成図である。

【図8】本発明の第2実施形態に係るインバータ装置の動作を示す各部の波形図である。

【図9】本発明の第3実施形態におけるインバータ装置の構成図である。

【図10】本発明の第3実施形態に係るインバータ装置の動作を示す各部の波形図である。

【発明を実施するための形態】

【0026】

《概要》

本発明の実施形態に係るインバータ装置は、パワー半導体スイッチング素子と、SiCやGaNなどのワイドギャップ半導体のユニポーラ型ダイオードとが逆並列に接続されたパワー半導体モジュールを備えたインバータ装置であって、そのインバータ装置の主回路電流が所定値より大きい場合には、パワー半導体スイッチング素子をスイッチング駆動するためのゲート抵抗値(ゲートインピーダンス)を大きくするように構成したことを特徴とする。これにより、ユニポーラ型ダイオードのリカバリdv/dtを低減させて、パワー半導体スイッチング素子のターンオン損失やユニポーラ型ダイオードのリカバリ損失を少なくすることができると共に、パワー半導体スイッチング素子のコレクタ電流の振動による跳ね上がり(リンギング)を抑制することができる。

【0027】

また、本発明の実施形態に係るインバータ装置は、PWM(Pulse Width Modulation)制御を行うインバータ装置の主回路電流が所定値より大きい場合には、パワー半導体スイッチング素子をスイッチング駆動するためのゲート抵抗値(ゲートインピーダンス)を大きくすると共に、インバータ装置を駆動するためのPWM信号のパルス数を低減させるように構成したことを特徴としている。これにより、ターンオン損失、リカバリ損失、及びリンギングを抑制することができると共に、パワー半導体スイッチング素子のスイッチング損失を低減させることができる。

【0028】

以下、本発明に係るインバータ装置の幾つかの実施形態について図面を参照しながら詳細に説明する。なお、各実施形態を説明するための全図において、同一の構成要素は原則として同一の符号を付し、その繰り返しの説明は省略する。

【0029】

《第1実施形態》

〈インバータ装置の構成〉

図1は、本発明の第1実施形態におけるインバータ装置の構成図である。なお、一般的には、インバータ装置はフルブリッジ回路で構成されているが、図1では、本実施形態の説明の便宜上、ハーフブリッジ回路のインバータ装置を示している。

【0030】

先ず、本発明の第1実施形態に係るインバータ装置の構成について説明する。図1に示すように、インバータ装置1aは、インバータ主回路10、上アーム駆動/制御回路20、下アーム駆動/制御回路30、制御回路40、及び主回路電流検出回路50を備えて構成されている。

【0031】

インバータ主回路10は、直列に接続された2つのパワー半導体スイッチング素子であるSi−IGBT(Silicon Insulated Gate Bipolar Transistor)11,12と、ゲート抵抗11g,12gと、各Si−IGBT11,12にそれぞれ逆並列に接続されたユニポーラ型ダイオード13,14と、主回路電源15と、主回路インダクタンス16,17と、主回路電流検出カレントトランス(CT)18と、及び主回路19とを備えて構成されている。

【0032】

Si−IGBT11,12は、ゲート端子に入力された信号によって、コレクタ端子とエミッタ端子との間の導通と非導通とを切り替えるパワー半導体スイッチング素子である。Si−IGBT11とユニポーラ型ダイオード13、及び、Si−IGBT12とユニポーラ型ダイオード14は、それぞれ、パワー半導体モジュールを構成している。また、主回路電源15は、正極端子と負極端子との間に直流電圧を印加する直流電源である。さらに、主回路電流検出カレントトランス(CT)18は、主回路19に流れる電流に応じた信号を出力する電流検出手段である。

【0033】

主回路電源15の正極端子には主回路インダクタンス16の一方の端子が接続されている。主回路インダクタンス16の他方の端子は、直列に接続されたSi−IGBT11のコレクタ端子に接続されている。また、主回路電源15の負極端子には主回路インダクタンス17の一方の端子が接続されている。主回路インダクタンス17の他方の端子は、直列に接続されたSi−IGBT12のエミッタ端子に接続されていると共に、グランドに接続されている。また、Si−IGBT11のエミッタ端子とSi−IGBT12のコレクタ端子とが接続されているノードから、主回路電流検出カレントトランス(CT)18と主回路19とを介して、図示しない負荷に接続されている。

【0034】

また、上アームのSi−IGBT11のゲート端子は、ゲート抵抗11gを介して、上アームのSi−IGBT11を駆動する上アーム駆動/制御回路20に接続されている。同様に、下アームのSi−IGBT12のゲート端子は、ゲート抵抗12gを介して、下アームのSi−IGBT12を駆動する下アーム駆動/制御回路30に接続されている。

【0035】

下アーム駆動/制御回路30は、ゲート抵抗31,32と、ゲート抵抗切替用pMOS(positive channel Metal Oxide Semiconductor)33と、npnトランジスタ34と、pnpトランジスタ35と、駆動ロジック回路36、及び下アーム駆動/制御回路電源37,38とを備えて構成されている。なお、npnトランジスタ34及びpnpトランジスタ35は、それぞれ、pMOS及びnMOS(negative channel Metal Oxide Semiconductor)などに代替可能である。

【0036】

下アーム駆動/制御回路30の回路構成は次のようになっている。すなわち、ゲート抵抗切替用pMOS33とゲート抵抗31とが並列に接続され、該ゲート抵抗切替用pMOS33のソース側が下アーム駆動/制御回路電源37の正極に接続され、該ゲート抵抗切替用pMOS33のドレイン側がnpnトランジスタ34のコレクタ端子に接続されている。また、該npnトランジスタ34のエミッタ端子はpnpトランジスタ35のエミッタ端子に接続されると共に、インバータ主回路10におけるゲート抵抗11gの一方の端子に接続されている。さらに、該pnpトランジスタ35のコレクタ端子はゲート抵抗32の一端に接続され、該ゲート抵抗32の他端は下アーム駆動/制御回路電源38の負極に接続されている。そして、下アーム駆動/制御回路電源38の正極は前記下アーム駆動/制御回路電源37の負極に接続されると共にグランドに接続されている。また、制御信号系としては、ゲート抵抗切替用pMOS33のゲート端子が主回路電流検出回路50に接続され、npnトランジスタ34とpnpトランジスタ35のそれぞれのベース端子は駆動ロジック回路36の一端に接続され、該駆動ロジック回路36の他端は制御回路40に接続されている。

【0037】

このような回路構成において、駆動ロジック回路36は、制御回路40からの駆動信号(例えば、PWM信号)を入力して、npnトランジスタ34とpnpトランジスタ35とを交互にスイッチング動作させる。また、npnトランジスタ34とpnpトランジスタ35は、駆動ロジック回路36の駆動信号(例えば、PWM信号)を増幅して下アームのSi−IGBT12をスイッチング駆動(例えば、PWM駆動)させる。

【0038】

上アーム駆動/制御回路20も同様の構成であって、ゲート抵抗21,22、ゲート抵抗切替用pMOS23、npnトランジスタ24、pnpトランジスタ25、駆動ロジック回路26、及び上アーム駆動/制御回路電源27,28を備えて構成されている。なお、上アーム駆動/制御回路20の回路構成は、下アーム駆動/制御回路30の回路構成と同じであるので、重複する説明は省略する。

【0039】

主回路電流検出回路50は、検出端子が主回路電流検出カレントトランス(CT)18に接続され、上アームの制御端子が、上アーム駆動/制御回路20のゲート抵抗切替用pMOS23のゲート端子に接続され、下アームの制御端子が下アーム駆動/制御回路30のゲート抵抗切替用pMOS33のゲート端子に接続されている。主回路電流検出回路50は、インバータ主回路10の主回路電流検出カレントトランス(CT)18からの主回路電流検出信号を入力し、上アーム駆動/制御回路20のゲート抵抗切替用pMOS23及び下アーム駆動/制御回路30のゲート抵抗切替用pMOS33をON/OFF制御する。

【0040】

また、制御回路40は、上アーム駆動/制御回路20の駆動ロジック回路26と下アーム駆動/制御回路30の駆動ロジック回路36とに、それぞれの制御信号線を接続している。したがって、制御回路40は、上アーム駆動/制御回路20の駆動ロジック回路26を制御してnpnトランジスタ24及びpnpトランジスタ25を駆動制御させると共に、下アーム駆動/制御回路30の駆動ロジック回路36を制御してnpnトランジスタ34及びpnpトランジスタ35を駆動制御させることができる。これによって、上アームのSi−IGBT11と下アームのSi−IGBT12は、それぞれ、制御回路40で生成されたPWM信号によってPWM制御のスイッチング動作を行うことができる。あるいは、制御回路40は、上アームのSi−IGBT11と下アームのSi−IGBT12を交互に180度通電するようにスイッチング動作を行わせてもよい。

【0041】

本発明の第1実施形態では、ユニポーラ型ダイオードのように、リカバリdv/dtが電流値に比例する特性を有する還流用のダイオードを、パワー半導体スイッチング素子と逆並列に接続したパワー半導体モジュールとして用いた場合において、主回路電流検出回路50が検出した主回路電流の大きさに応じて、上アーム駆動/制御回路20及び下アーム駆動/制御回路30が、それぞれ、ゲート抵抗21とゲート抵抗22を接続/短絡して、Si−IGBT11及びSi−IGBT12のゲート抵抗値(ゲートインピーダンス)を切り替え制御するように構成されている。ここで、ゲート抵抗とは、上アームのSi−IGBT11と下アームのSi−IGBT12のスイッチング動作を安定的に行うために、ゲート端子とゲート電源との間に設けられた抵抗のことである。

【0042】

〈第1実施形態におけるインバータ装置の動作〉

図1に示すインバータ装置1aの基本的な動作を以下に説明する。制御回路40からの制御信号によって、上アーム駆動/制御回路20の駆動ロジック回路26及び下アーム駆動/制御回路30の駆動ロジック回路36を制御し、パワー半導体スイッチング素子であるSi−IGBT11とSi−IGBT12を交互にON/OFF動作させることにより、主回路電源15の直流電圧が交流電圧に変換され、主回路19に交流電流(主回路電流)が流れて負荷(図示せず)に供給されると共に、主回路19に流れた主回路電流は、主回路電流検出カレントトランス(CT)18で検出されて主回路電流検出回路50へ供給される。なお、制御回路40は、Si−IGBT11とSi−IGBT12をPWM制御してもよいし、Si−IGBT11とSi−IGBT12をそれぞれ電気角180度ごとにON/OFFして矩形波制御してもよい。あるいは、制御回路40は、矩形波制御をベースにして通電角を制御するデューティ幅制御(位相制御)を行ってもよい。

【0043】

ここで、Si−IGBT11とSi−IGBT12のON/OFF動作について概略説明する。Si−IGBT11がONしたときは、Si−IGBT12はOFFとなるが、このSi−IGBT12に逆並列に接続された還流用のダイオードであるユニポーラ型ダイオード14がターンオンして還流電流が流れる。同様にして、Si−IGBT12がONしたときは、Si−IGBT11はOFFとなるが、このSi−IGBT11に逆並列に接続された還流用のダイオードであるユニポーラ型ダイオード13がターンオンして還流電流が流れる。このようなスイッチング動作の過程において、Si−IGBT11,12のそれぞれのターンオン時にはユニポーラ型ダイオード13,14のそれぞれに逆回復電圧(リカバリ電圧)が発生する。

【0044】

上アーム駆動/制御回路20と下アーム駆動/制御回路30は同じ構成であって、かつ同じ動作を行うので、本実施形態に係るSi−IGBT11,12のターンオン時のコレクタ−エミッタ間電圧変化の推移(つまり、ユニポーラ型ダイオード13,14のリカバリ電圧変化の推移)については、便宜上、下アーム駆動/制御回路30を用いて説明する。したがって、上アーム駆動/制御回路20の動作説明は、重複を避けるために省略する。

【0045】

すなわち、本実施形態では、ユニポーラ型ダイオードのように、リカバリdv/dtが電流値に比例する特性を有する還流用のダイオードを用いた場合において、上アーム駆動/制御回路20及び下アーム駆動/制御回路30が、主回路電流検出カレントトランス18で検出された主回路電流に基づいて、Si−IGBT11及びSi−IGBT12のゲート抵抗値を切り替える制御を行うが、本実施形態では、下アーム駆動/制御回路30を用いてこの動作を説明する。

【0046】

図5は、本発明の第1実施形態に係るインバータ装置の動作を示す各部の波形図であり、(a)は主回路電流、(b)は制御回路の下アームPWM信号、(c)は主回路電流が所定の閾値よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33のゲート端子へ送信する下アームのゲート抵抗切替信号、(d)は下アームのユニポーラ型ダイオード14の逆回復時の電圧変化率(リカバリdv/dt)を示している。なお、いずれの図も横軸は時間を表わし、縦軸はそれぞれのレベルを表わしている。また、主回路電流(a)は、図1において図示しない負荷から主回路19を通ってSi−IGBT12のコレクタからエミッタへ流れる電流(コレクタ電流Ic)の方向を正極として表わしている。なお、制御回路の下アームPWM信号(b)は、主回路電流(a)を生成するために、駆動ロジック回路36を介して下アームのSi−IGBT12のゲート部分に供給される信号である。

【0047】

ここで、図5の主回路電流(a)と逆回復時の電圧変化率(d)(つまり、リカバリdv/dt)との関係について説明する。主回路電流(a)(つまり、コレクタ電流Ic)は、例えば、半サイクル10msecでSi−IGBT12のコレクタからエミッタへ正弦波状に流れている。このとき、Si−IGBT12は、例えば、100μsecのキャリア周波数でスイッチング駆動している。なお、このときのスイッチング駆動の信号は、デューティ比制御を行うPWM信号によるキャリア周波数でもよいし、デューティ比制御を行わないでデューティ比が50%のON/OFF信号によるキャリア周波数であってもよい。いずれの場合においても、Si−IGBT12は、100μsecのキャリア周波数でスイッチング駆動することになる。すなわち、主回路電流(コレクタ電流Ic)の半サイクル10msecの間にSi−IGBT12は100回のスイッチング駆動を行う。したがって、Si−IGBT12がスイッチング駆動を行うごとに、Si−IGBT12のコレクタ電圧にdv/dtが発生する(つまり、ユニポーラ型ダイオード14にリカバリdv/dtが発生する。)このときにキャリア周波数で発生する毎サイクルの逆回復時の電圧変化率(d)(つまり、リカバリdv/dt)は、主回路電流(a)(つまり、コレクタ電流Ic)が増加するにしたがって大きくなる。そのため、主回路電流(a)(つまり、コレクタ電流Ic)が所定の電流値まで上昇したら、Si−IGBT12のゲート抵抗値を大きくして、キャリア周波数の毎サイクル時における逆回復時の電圧変化率(d)(つまり、リカバリdv/dt)を減少させている。これについての詳細は、以下に説明する。

【0048】

なお、ここでは、制御回路40が図5(b)のようにPWM制御を行うことによって、主回路電流を図5(a)のように正弦波にしている。しかし、これに限らず、制御回路40がON/OFFのキャリア周波数で180度通電制御を行い、Si−IGBT11とSi−IGBT12をキャリア周波数で交互にON/OFFさせて矩形波を出力し、インバータ装置1aの出力側のフィルタ(図1では図示せず)によって高調波を除去し、出力電流(主回路電流)を図5(a)のように正弦波状にしてもよい。

【0049】

次に、図1及び図5を用いて、本発明の第1実施形態に係るインバータの動作について説明する。時刻t0において、正弦波の主回路電流(a)がゼロから上昇し始めると、ユニポーラ型ダイオード14の逆回復時の電圧変化率(d)も上昇する。このとき、主回路電流検出カレントトランス18で検出された主回路電流が所定値より小さい場合は、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームのゲート抵抗切替信号(c)はONとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gのみの抵抗値である。

【0050】

やがて、時刻t1において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)よりも大きくなると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にOFF信号を伝達する。すなわち、下アームのゲート抵抗切替信号(c)はONからOFFとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がOFF状態のため、ゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となる。そのため、Si−IGBT12のターンオン時の電流変化率(di/dt)が小さくなり、逆並列に接続されたユニポーラ型ダイオード14の逆回復時の電圧変化率(d)、すなわちリカバリdv/dtは、時刻t1以降においては、破線のレベル(図5(d)の従来例のレベル)から実線のレベル(図5(d)の第1実施形態のレベル)に低減する。その結果、Si−IGBT11のコレクタ−エミッタ間電圧Vceのサージ電圧(リンギング電圧)を低減させることができる。

【0051】

そして、時刻t1から時刻t2までは、主回路電流(a)の上昇に伴って、ユニポーラ型ダイオード14の逆回復時の電圧変化率(d)、すなわち、リカバリdv/dtは上昇するが、Si−IGBT12のゲート抵抗値は、ゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となるため、ユニポーラ型ダイオード14のリカバリdv/dtは従来例より低いレベルで推移する。

【0052】

次に、時刻t2以降においては、主回路電流(a)の低下に伴って、ユニポーラ型ダイオード14の逆回復時の電圧変化率(d)、すなわち、リカバリdv/dtは低下する。そして、時刻t3において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)まで低下すると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームのゲート抵抗切替信号(c)はOFFからONとなる。

【0053】

したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gの抵抗値のみとなる。その結果、時刻t3以降においてはリカバリdv/dtは従来例と同じレベルまで上昇するが、このときは主回路電流(a)が所定の閾値Ith1より低下しているのでリカバリdv/dtの値も低くなっている。そして、時刻t4において主回路電流(a)がゼロになるとリカバリdv/dtの値もゼロとなる。

【0054】

なお、主回路電流検出回路50は、主回路電流検出カレントトランス18に限らず、シャント抵抗やセンス機能付きのIGBTなどを使用する回路を用いることで、主回路電流を容易に検出することができる。また、主回路電流を検出する箇所は、図1で示した主回路19の位置に限ることはなく、Si−IGBT12のエミッタ、Si−IGBT12のコレクタ、ユニポーラ型ダイオード14、または上アーム側のユニポーラ型ダイオード13などの箇所でも検出することが可能である。なお、上アーム側のユニポーラ型ダイオード13で主回路電流を検出できるのは、下アームのSi−IGBT12がON状態のときに図示しない負荷を通った主回路電流が上アームのユニポーラ型ダイオード13を還流するためである。すなわち、主回路電流を検出する箇所は、下アームのSi−IGBT12と逆並列のユニポーラ型ダイオード14とからなるパワー半導体モジュールに流れる電流を検出できる箇所であれば、いずれの箇所でもよい。

【0055】

図6は、ユニポーラ型ダイオード使用時の第1実施形態と従来例の動作波形図であり、(a−1)と(a−2)は第1実施形態、(b−1)と(b−2)は従来例を示す。すなわち、図6は、主回路電流の大電流時におけるユニポーラ型ダイオードを用いた場合のパワー半導体スイッチング素子のターンオン時の動作波形図であり、(a−1)は第1実施形態のコレクタ−エミッタ間電圧Vce、(a−2)は第1実施形態のコレクタ電流Ic、(b−1)は従来例のコレクタ−エミッタ間電圧Vce、(b−2)は従来例のコレクタ電流Ic、の各動作波形を表わしている。なお、横軸は、いずれの図も時間を示し、縦軸は、それぞれ、パワー半導体スイッチング素子(下アームのSi−IGBT12)のコレクタ−エミッタ間電圧Vce及びコレクタ電流Icを示している。また、ユニポーラ型ダイオードとしてはSiC−SBDを用いている。

【0056】

図6の(b−1),(b−2)に示すように、従来例では、パワー半導体スイッチング素子のゲート抵抗値が固定されているために、主回路電流が大電流のときはパワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vce(すなわち、ユニポーラ型ダイオードのリカバリdv/dt)が大きくなり、パワー半導体スイッチング素子のコレクタ電流Icにやや大きい跳ね上がりの振動(リンギング)が発生している。

【0057】

ところが、第1実施形態の場合は、主回路電流が大電流のときにはパワー半導体スイッチング素子(つまり、Si−IGBT12)のゲート抵抗値を大きくしているので(ゲート抵抗31の抵抗値とゲート抵抗12gの抵抗値の和にしているので)、Si−IGBT12のゲート抵抗値が一定である従来例に比べて、図6の(a−1),(a−2)に示すように、パワー半導体スイッチング素子(Si−IGBT12)のコレクタ電流Icの跳ね上がりの振動(リンギング)は小さくなっている。このようにして、主回路電流の大きさに応じて2段階でゲート抵抗値を変化させることにより、主回路電流の大電流時におけるユニポーラ型ダイオードのリカバリdv/dtを低減させることができるため、コレクタ電流Icのリンギングを抑えてインバータ装置1aから発生する放射ノイズを低減させ、負荷であるモータの絶縁抵抗の長寿命化を実現することが可能となる。

【0058】

言い換えると、主回路電流が大電流時にはパワー半導体スイッチング素子のゲート抵抗値を大きくすることによって、そのゲート抵抗値とパワー半導体スイッチング素子の寄生容量(C)とによる時定数が大きくなるため、パワー半導体スイッチング素子のターンオン時のゲート信号の立ち上がり波形が緩やかになる。その結果、パワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dtが小さくなり(つまり、ユニポーラ型ダイオードのリカバリdv/dtが小さくなり)、図6の(a−2)のようにコレクタ電流Icのリンギングを小さくすることができる。

【0059】

《第2実施形態》

図7は、本発明の第2実施形態におけるインバータ装置の構成図である。図7に示す第2実施形態のインバータ装置1bについては、図1に示す第1実施形態のインバータ装置1aと同じ構成要素は同一の符号が付されている。第2実施形態のインバータ装置1bが第1実施形態のインバータ装置1aと異なる点は、主回路電流検出回路50から制御回路40へ制御信号線51が接続されているところである。

【0060】

すなわち、前記の第1実施形態のインバータ装置1aにおいては、主回路電流検出回路50が、主回路電流検出カレントトランス18の検出した主回路電流の大きさに基づいてパワー半導体スイッチング素子(つまり、Si−IGBT11,12)のゲート抵抗値を変化させ、そのパワー半導体スイッチング素子のコレクタ−エミッタ間電圧Vceのdv/dt(つまり、ユニポーラ型ダイオードのリカバリdv/dt)を抑制していた。第2実施形態のインバータ装置1bでは、これに加えて、主回路電流検出回路50から制御回路40へ制御信号線51によって制御信号を伝達し、主回路電流検出カレントトランス18が検出した主回路電流の大きさに基づいてPWM信号のスイッチング回数を制御している。これによって、パワー半導体スイッチング素子のコレクタ電流Icの跳ね上がりの振動を抑制すると共に、PWM信号のスイッチングロスによる効率低下を抑制することができる。

【0061】

図8は、本発明の第2実施形態に係るインバータ装置の動作を示す各部の波形図であり、(a)は主回路電流Ic、(b)は第2実施形態の制御回路の下アームPWM信号、(c)は従来例の制御回路の下アームPWM信号、(d)は主回路電流が所定の閾値よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33のゲート端子へ送信する下アームのゲート抵抗切替信号、(e)は下アームのユニポーラ型ダイオード14の逆回復時の電圧変化率(リカバリdv/dt)を示している。いずれの図も横軸は時間を表わし、縦軸はそれぞれのレベルを表わしている。なお、主回路電流Ic(a)は、図示しない負荷から主回路19を通ってSi−IGBT12のコレクタ−エミッタに流れる電流(コレクタ電流Ic)の方向を正極として表わしている。さらに、第2実施形態の制御回路の下アームPWM信号(b)、及び従来例の制御回路の下アームPWM信号(c)は、それぞれ、主回路電流(a)を生成するために、駆動ロジック回路36を介して下アームのSi−IGBT12のゲート部分に供給される信号を示している。

【0062】

図8の時刻t0において、正弦波の主回路電流(a)がゼロから上昇し始めると、ユニポーラ型ダイオード14の出力電圧の電圧変化率(e)も上昇する。このとき、主回路電流検出カレントトランス18で検出された主回路電流が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)より小さい場合は、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームゲート抵抗切替信号(d)はONとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gの抵抗値のみとなる。

【0063】

やがて、時刻t1において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1よりも大きくなると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にOFF信号を伝達する。すなわち、下アームのゲート抵抗切替信号(d)はOFFとなる。したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がOFF状態のため、ゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となる。そのため、Si−IGBT12のターンオン時の電流変化率(di/dt)が小さくなり、逆並列に接続されたユニポーラ型ダイオード14の逆回復時の電圧変化率(e)、すなわちリカバリdv/dtは、時刻t1以降においては、図8(e)の破線のレベル(従来例のレベル)から実線のレベル(第2実施形態のレベル)に低減する。その結果、Si−IGBT12のコレクタ電流Icのリンギングを低減することができる。

【0064】

そして、時刻t1から時刻t2までは、主回路電流(a)の上昇に伴って、逆回復時の電圧変化率(e)、すなわち、リカバリdv/dtは上昇するが、Si−IGBT12のゲート抵抗値がゲート抵抗12gの抵抗値とゲート抵抗31の抵抗値との和となるために、ユニポーラ型ダイオード14のリカバリdv/dtは従来例より低いレベルで推移する。

【0065】

次に、時刻t2以降においては、主回路電流(a)の低下に伴って、ユニポーラ型ダイオード14の逆回復時の電圧変化率(e)、すなわち、リカバリdv/dtは低下する。そして、時刻t3において、主回路電流検出カレントトランス18で検出された主回路電流(a)が所定の閾値Ith1(例えば、主回路電流のピーク値の1/2)まで低下すると、主回路電流検出回路50はゲート抵抗切替用pMOS33の制御端子にON信号を伝達する。すなわち、下アームのゲート抵抗切替信号(d)はONとなる。

【0066】

したがって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33がON状態のため、ゲート抵抗12gの抵抗値のみとなる。その結果、時刻t3以降においてリカバリdv/dtが従来例と同じレベルまで上昇するが、このときは主回路電流(a)が所定値より低下しているのでリカバリdv/dtの値も低くなっている。そして、時刻t4において主回路電流(a)がゼロになるとリカバリdv/dtの値もゼロとなる。

【0067】

さらに、本実施形態では、主回路電流検出回路50が、主回路電流検出カレントトランス18の検出した主回路電流の情報を制御回路40へ伝達している。これによって、制御回路40は、主回路電流の検出値が大きい場合には、駆動ロジック回路36へ出力するPWM信号の出力パルス数を少なくしている。

【0068】

すなわち、図8に示すように、パワー半導体スイッチング素子(Si−IGBT12)が駆動する電気角180度の間においては、通常は、従来例の制御回路の下アームPWM信号(c)に示すような、間引きのないPWM信号に基づいてSi−IGBT12のスイッチング制御を行うことにより、主回路電流(a)は正弦波の状態になる。しかし、このような間引きのないPWM信号で各パワー半導体スイッチング素子を駆動すると、スイッチング回数が多くなってパワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失が増加してしまう。

【0069】

そこで、図8における時刻t1から時刻t3の間は、主回路電流(a)が所定の閾値Ith1よりも大きくなる。この間は、制御回路40が、第2実施形態の制御回路の下アームPWM信号(b)に示すように、PWM信号の間引きを行い、出力パルス数を少なくする。これによって、主回路電流(a)が大電流のときは、パワー半導体スイッチング素子(Si−IGBT12)のスイッチング回数を低減させてそのパワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失を減少させることができる。その結果、インバータ装置1bの効率低下を抑制することができる。

【0070】

以上述べたように、通常は主回路電流が大きい場合に、ゲート抵抗値を大きくすると、パワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失が増大するが、主回路電流が大きいときには、制御回路40から駆動ロジック回路36へ出力するPWM信号の出力パルス数を小さくすることによって、パワー半導体スイッチング素子(Si−IGBT12)のスイッチング損失を低減させることができる。このため、本実施形態を適用したインバータ装置1bでは、インバータ装置1bで発生する放射ノイズを低減させて負荷であるモータの絶縁抵抗の長寿命化を実現させることができると共に、インバータ装置1bの電力損失を低減させることができる。

【0071】

なお、PWM信号の間引きを多くすることによってパワー半導体スイッチング素子のスイッチング損失を減少させて効率を向上させることができるが、その反面、PWM信号の間引きを多くすることによって主回路電流に歪みが生じて正弦波を維持できなくなるというトレードオフの関係がある。したがって、実機によるカットアンドトライによって、最適なトレードオフの関係になるようにPWM信号のスイッチング回数の最適な低減化を行うことが望ましい。

【0072】

《第3実施形態》

図9は、本発明の第3実施形態におけるインバータ装置の構成図である。図9に示す第3実施形態のインバータ装置1cについては、図7に示す第2実施形態のインバータ装置1bと同じ構成要素は同一の符号が付されている。第3実施形態のインバータ装置1cが第2実施形態のインバータ装置1bと異なる点は、パワー半導体スイッチング素子のゲート抵抗値(ゲートインピーダンス)を3段階で切り替えているところである。

【0073】

先ず、図9に示す第3実施形態に係るインバータ装置1cの構成について、重複説明を避けて説明するする。図9に示すように、本発明の第3実施形態におけるインバータ装置1cは、インバータ主回路10、上アーム駆動/制御回路20a、下アーム駆動/制御回路30a、制御回路40、及び主回路電流検出回路50を備えて構成されている。なお、インバータ主回路10と制御回路40は図1と同じであるので構成の説明は省略する。

【0074】

下アーム駆動/制御回路30aの回路構成は次のようになっている。すなわち、下アーム駆動/制御回路電源37の正極が、ゲート抵抗切替用pMOS33aのソース端子とゲート抵抗切替用pMOS33bのソース端子とに接続されている。そして、ゲート抵抗切替用pMOS33aのソース端子がゲート抵抗31aの一端に接続され、該ゲート抵抗切替用pMOS33aのドレイン端子が前記ゲート抵抗31aの他端に接続されている(すなわち、ゲート抵抗切替用pMOS33aとゲート抵抗31aとが並列に接続されている)。さらに、ゲート抵抗切替用pMOS33aのドレイン端子がnpnトランジスタ34のコレクタ端子に接続されている。また、ゲート抵抗切替用pMOS33bのドレイン端子はゲート抵抗31bの一端に接続され、該ゲート抵抗31bの他端はnpnトランジスタ34のコレクタ端子に接続されている。

【0075】

また、該npnトランジスタ34のエミッタ端子は、pnpトランジスタ35のエミッタ端子に接続されると共に、インバータ主回路10におけるゲート抵抗12gの一方の端子に接続されている。さらに、該pnpトランジスタ35のコレクタ端子はゲート抵抗32の一端に接続され、該ゲート抵抗32の他端は下アーム駆動/制御回路電源38の負極に接続されている。そして、該下アーム駆動/制御回路電源38の正極は、前記下アーム駆動/制御回路電源37の負極に接続されると共にグランドに接続されている。また、制御信号系としては、ゲート抵抗切替用pMOS33aのゲート端子とゲート抵抗切替用pMOS33bのゲート端子が、それぞれ、主回路電流検出回路50の制御端子に接続されている。さらに、npnトランジスタ34のベース端子とpnpトランジスタ35のベース端子は、駆動ロジック回路36の制御端子に接続され、該駆動ロジック回路36の信号入力端子は制御回路40に接続されている。

【0076】

このような回路構成において、駆動ロジック回路36は、制御回路40からの駆動信号(例えば、PWM信号)を入力して、npnトランジスタ34とpnpトランジスタ35とを交互にスイッチング動作させる。また、npnトランジスタ34とpnpトランジスタ35とは、駆動ロジック回路36の駆動信号(例えば、PWM信号)を増幅して下アームのSi−IGBT12をスイッチング駆動(例えば、PWM駆動)させる。

【0077】

なお、上アーム駆動/制御回路20aの回路構成は、下アーム駆動/制御回路30aの回路構成と同じであるので、重複する説明は省略する。

【0078】

すなわち、図9に示すように、本発明の第3実施形態におけるインバータ装置1cは、下アームのSi−IGBT12のゲート抵抗値を3段階で切り替えるために、ゲート抵抗31aに並列に接続されたゲート抵抗切替用pMOS33aと、ゲート抵抗31bに直列に接続されたゲート抵抗切替用pMOS33bとが設けられている。同様にして、上アームのSi−IGBT11のゲート抵抗値を3段階で切り替えるために、ゲート抵抗21aに並列に接続されたゲート抵抗切替用pMOS23aと、ゲート抵抗21bに直列に接続されたゲート抵抗切替用pMOS23bとが設けられている。その他の構成要素は図7に示す第2実施形態のインバータ装置1bと同じである。

【0079】

図10は、本発明の第3実施形態に係るインバータ装置の動作を示す各部の波形図であり、(a)は主回路電流、(b)は第3実施形態の制御回路の下アームPWM信号、(c)は従来例の制御回路の下アームPWM信号、(d)は主回路電流が第1の閾値よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33aのゲート端子へ送信する下アームの第1ゲート抵抗切替信号、(e)は主回路電流が第2の閾値(但し、第2の閾値>第1の閾値)よりも大きいか否かによって主回路電流検出回路50がゲート抵抗切替用pMOS33bのゲート端子へ送信する下アームの第2ゲート抵抗切替信号、(f)は下アームのユニポーラ型ダイオード14の逆回復時の電圧変化率(リカバリdv/dt)を示している。いずれの図も横軸は時間を表わし、縦軸はそれぞれのレベルを表わしている。なお、主回路電流(a)は、図示しない負荷から主回路19を通ってSi−IGBT12のコレクタ−エミッタに流れる電流(コレクタ電流Ic)の方向を正極として表わしている。さらに、第3実施形態の制御回路の下アームPWM信号(b)、及び従来例の制御回路の下アームPWM信号(c)は、それぞれ、主回路電流(a)を生成するために、駆動ロジック回路36を介して下アームのSi−IGBT12のゲート部分へ供給されるPWM信号である。

【0080】

図10の時刻t0において、正弦波の主回路電流(a)がゼロから上昇し始めると、ユニポーラ型ダイオード14の逆回復時の電圧変化率(f)、すなわち、リカバリdv/dtも上昇する。このとき、主回路電流検出カレントトランス18で検出された主回路電流(a)が第1の閾値Ith1(例えば、主回路電流のピーク値の1/3)より小さい場合は、主回路電流検出回路50はゲート抵抗切替用pMOS33a,33bの各制御端子にON信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)と第2ゲート抵抗切替信号(e)とが共にONとなる。これにより、npnトランジスタ34のコレクタ端子と、下アーム駆動/制御回路電源37の正極との間の抵抗値は0となるので、インバータ主回路10における下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗12gの抵抗値のみとなる。

【0081】

やがて、時刻t1において、主回路電流検出カレントトランス18で検出された主回路電流(a)が第1の閾値Ith1(例えば、主回路電流のピーク値の1/3)よりも大きくなると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33bの制御端子にON信号を伝達したまま、ゲート抵抗切替用pMOS33aの制御端子にOFF信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)がOFFで、第2ゲート抵抗切替信号(e)がONとなる。

【0082】

これによって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aがOFF状態でゲート抵抗切替用pMOS33bがON状態であるため、ゲート抵抗31a、ゲート抵抗31bの並列接続による抵抗値とゲート抵抗12gの抵抗値との和となる。時刻t1以降のゲート抵抗値は、時刻t0〜t1のゲート抵抗値よりも大きい。そのため、Si−IGBT12のターンオン時の電流変化率(di/dt)が小さくなり、逆並列に接続されたユニポーラ型ダイオード14の逆回復時の電圧変化率(f)、すなわちリカバリdv/dtは、時刻t1以降においては、図10(f)の破線のレベル(従来例のレベル)から実線のレベル(第3実施形態のレベル)に低減する。その結果、Si−IGBT12のコレクタ電流Icのリンギングを低減させることができる。

【0083】

さらに、時刻t2において、主回路電流検出カレントトランス18で検出された主回路電流(a)が第2の閾値Ith2(例えば、主回路電流のピーク値の2/3)より大きくなると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33aの制御端子にOFF信号を伝達したまま、ゲート抵抗切替用pMOS33bの制御端子にもOFF信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)がOFF、第2ゲート抵抗切替信号(e)がOFFとなる。

【0084】

これによって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aとゲート抵抗切替用pMOS33bが共にOFF状態であるため、ゲート抵抗31aの抵抗値とゲート抵抗12gの抵抗値との和となる。時刻t2以降のゲート抵抗値は、時刻t1〜t2のゲート抵抗値よりも大きい。そのため、時刻t2以降においては、Si−IGBT12のターンオン時の電流変化率(di/dt)がさらに小さくなる。すなわち、時刻t2以降において、ユニポーラ型ダイオード14の逆回復時の電圧変化率(e)、つまり、リカバリdv/dtがさらに減少する。これによって、インバータ装置1cのサージ電圧(リンギング電圧)をさらに低減させることが可能となる。

【0085】

また、時刻t2から時刻t3までは主回路電流(a)の上昇に伴ってリカバリdv/dtは上昇するが、Si−IGBT12のゲート抵抗値は、ゲート抵抗31aの抵抗値とゲート抵抗12gの抵抗値との和となる。そのために、図10(f)の実線で示す第3実施形態のリカバリdv/dtは、破線で示す従来例のリカバリdv/dtに比べてかなり小さな値となっている。

【0086】

次に、時刻t3から時刻t4までは主回路電流(a)の減少に伴って逆回復時の電圧変化率(f)、すなわち、リカバリdv/dtも減少し、時刻t4において主回路電流(a)が第2の閾値Ith2(例えば、主回路電流のピーク値の2/3)よりも小さくなると、主回路電流検出回路50は、ゲート抵抗切替用pMOS33aの制御端子にOFF信号を伝達したまま、ゲート抵抗切替用pMOS33bの制御端子にはON信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)がOFFで、第2ゲート抵抗切替信号(e)がONとなる。

【0087】

これによって、下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aがOFF状態で、ゲート抵抗切替用pMOS33bがONの状態であるため、ゲート抵抗31a、ゲート抵抗31bの並列接続による抵抗値とゲート抵抗12gの抵抗値との和となる。時刻t4以降のゲート抵抗値は、時刻t3〜t4のゲート抵抗値よりも小さい。したがって、時刻t4以降においても、第3実施形態のリカバリdv/dtは、従来例の破線のレベルより低い実線のレベル(図10(f)の第3実施形態のレベル)に低減した状態で減少する。

【0088】

次に、時刻t5になると、主回路電流検出カレントトランス18で検出された主回路電流が第1の閾値Ith1(例えば、主回路電流のピーク値の1/3)よりも小さくなるので、時刻t5以降においては、主回路電流検出回路50は、ゲート抵抗切替用pMOS33aとゲート抵抗切替用pMOS33bとにON信号を伝達する。すなわち、第1ゲート抵抗切替信号(d)と第2ゲート抵抗切替信号(e)が共にONとなる。したがって、インバータ主回路10の下アームのSi−IGBT12のゲート抵抗値は、ゲート抵抗切替用pMOS33aとゲート抵抗切替用pMOS33bとが共にON状態であるため、ゲート抵抗12gの抵抗値のみとなる。時刻t5以降のゲート抵抗値は、時刻t4〜t5のゲート抵抗値よりも小さい。これによって、主回路電流(a)が第1の閾値Ith1以下のときは、ユニポーラ型ダイオード14の逆回復時の電圧変化率(f)、つまり、リカバリdv/dtは従来例と同じ値で低下するが、このときは、主回路電流(a)が小さいためにリカバリdv/dtも小さくなっているので、インバータ装置1cにサージ電圧(リンギング電圧)が生じるおそれはない。

【0089】

すなわち、前記の図6で示したように、従来例のようにゲート抵抗値が固定されている場合であって、パワー半導体スイッチング素子に大電流が流れているときには、逆並列に接続されたユニポーラ型ダイオードのリカバリdv/dtが大きい。そのために、図6(b−2)のようにコレクタ電流Icに大きな振動電流が発生する。ところが、本発明の第3実施形態の場合は、パワー半導体スイッチング素子の電流が大きくなると3段階でゲート抵抗を大きくするため、ユニポーラ型ダイオード14のリカバリdv/dtをきめ細かに低く抑えることができる。これによって、図6(a−2)のようにコレクタ電流Icには大きな振動電流は発生しなくなる。また、このようにしてリカバリdv/dtを低減させることにより、インバータ装置1cから発生する放射ノイズを低減させて、モータの絶縁抵抗の長寿命化を実現することができる。

【0090】

言い換えると、ゲート抵抗値を多段階に変化させてユニポーラ型ダイオードのリカバリdv/dtを多段階で制御することにより、リカバリdv/dtの主回路電流に対する依存性をきめ細かに低減させることができる。これにより、主回路電流が変化してもリカバリdv/dtをより平坦な値に保持することができるので、インバータ装置1cから発生する放射ノイズを低減させて、モータの絶縁抵抗のさらなる長寿命化を実現することができる。

なお、ゲート抵抗切替用pMOSとゲート抵抗との並列組み合わせ(例えば、ゲート抵抗切替用pMOS33aとゲート抵抗31aとの並列組み合わせ)の一組に対して、ゲート抵抗切替用pMOSとゲート抵抗との直列組み合わせ(例えば、ゲート抵抗切替用pMOS33bとゲート抵抗31bとの直列組み合わせ)を多段に設けることにより、ゲート抵抗の抵抗値を何段階にも可変させることが可能である。

【0091】

さらに、本発明の第3実施形態では、第2実施形態と同様に、主回路電流検出回路50が、主回路電流検出カレントトランス18の検出した主回路電流の検出情報を制御回路40へ伝達している。これによって、主回路電流の検出値が大きい場合には、制御回路40は、駆動ロジック回路26,36へ出力するPWM信号のパルス数を低減させている。

【0092】

さらに詳しく説明すると、図10に示すように、主回路電流(a)が第1の閾値Ith1より小さい期間(時刻t0〜t1、及び時刻t5〜t6)においては、第3実施形態の制御回路の下アームPWM信号(b)は、従来例の制御回路の下アームPWM信号(c)と同じパルス数であって、PWM信号のパルス数を低減させていない。そして、主回路電流(a)が第1の閾値Ith1より大きくて第2の閾値Ith2より小さい期間(時刻t1〜t2、及び時刻t4〜t5)においては、第3実施形態の制御回路の下アームPWM信号(b)は、従来例の制御回路の下アームPWM信号(c)よりわずかにパルス数を低減させる。

【0093】

さらに、主回路電流(a)が第2の閾値Ith2より大きい期間(時刻t2〜t4)においては、第3実施形態の制御回路の下アームPWM信号(b)は、従来例の制御回路の下アームPWM信号(c)に比べてPWM信号のパルス数をより多く低減させている。

【0094】

すなわち、一般的には、主回路電流が大きい場合にゲート抵抗値を大きくすると、パワー半導体スイッチング素子のスイッチング損失が増大するが、本実施形態のように、主回路電流が大きいときには制御回路40から出力するPWM信号のパルス数を低減させることにより、パワー半導体スイッチング素子のスイッチング損失を低減させることができる。しかも、主回路電流の大きさに応じて3段階でPWM信号のパルス数を低減させることができる。そのため、本実施形態を適用したインバータ装置では、そのインバータ装置から発生する放射ノイズを低減させてモータの絶縁抵抗の長寿命化を実現すると共に、主回路電流の大きさに応じてインバータ装置のスイッチング損失をきめ細かに低減させることもできる。

【0095】

《まとめ》

以上説明したように、本発明のインバータ装置は、パワー半導体スイッチング素子とユニポーラ型ダイオードとが逆並列に接続されたインバータ装置であって、主回路電流が所定値より大きいときに、パワー半導体スイッチング素子を駆動するゲート駆動回路のゲート抵抗値を大きくしてユニポーラ型ダイオードのリカバリdv/dtを抑制し、ターンオン損失、リカバリ損失、及びリンギングによるノイズを低減させることができる。また、主回路電流が所定値より大きいときに、パワー半導体スイッチング素子をPWM制御するスイッチング回数を低減させてスイッチング損失を低減させることができる。

【0096】

さらに詳しく述べると、インバータ装置の還流用のダイオードとして、SiCなどのワイドギャップ半導体であるショットキーバリアダイオード(SBD)、すなわちユニポーラ型ダイオードを用いて、ターンオン損失やリカバリ損失の低減化と高耐圧化を図っている。このとき、ユニポーラ型ダイオードのリカバリdv/dtは電流値に比例して大きくなるので、主回路電流が所定値より大きい場合にはパワー半導体スイッチング素子のゲート抵抗値(ゲートインピーダンス)を大きくしている。したがって、主回路電流が所定値より大きくなっても、パワー半導体スイッチング素子のコレクタ電流のリンギングが抑制され、インバータから発生する放射ノイズを低減させることができる。その結果、インバータ装置の負荷であるモータの絶縁抵抗の長寿命化を実現させることができる。また、主回路電流が所定値より大きい場合には、インバータ装置を駆動するためのPWM信号のパルス数を少なくすることで、放射ノイズの低減化とインバータ装置のスイッチング損失を低減することができる。言い換えると、リカバリdv/dtに起因するリンギングを抑制すると共にスイッチング損失を低減させたインバータ装置を提供することができる。

【0097】

ここで、請求項で述べる電流検出手段は、主回路電流検出カレントトランス(CT)18と主回路電流検出回路50とによって実現される。また、ゲートインピーダンスは、ゲート抵抗11g,12g,21,22,21a,21b,31,32,31a,31bであって、ゲートインピーダンス切替手段は、ゲート抵抗切替用pMOS23,23a,23b,33,33a,33bによって実現される。さらに、スイッチング回数低減手段は、PWM信号を生成する制御回路40の内部機能によって実現される。

【0098】

また、パワー半導体スイッチング素子は、シリコン(Si)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、またはダイヤモンドなどの材料によって生成され、絶縁ゲートバイポーラトランジスタ(Insulated Gate Bipolar Transistor:IGBT)、接合型電界効果トランジスタ(Junction Field Effect Transistor:JFET)、金属酸化膜型電界効果トランジスタ(Metal Oxide Semiconductor-Field Effect Transistor:MOSFET)、などのパワー半導体デバイスとして実現される。

【0099】

さらに、ユニポーラ型ダイオードは、Si、SiC、GaN、またはダイヤモンドなどのワイドギャップ半導体などから成り、例えば、ショットキーバリアダイオード(Schottky Barrier Diode:SBD)などとして実現される。このようなSBDは、リカバリdv/dtが電流値に比例して大きくなる特性を有している。

【0100】

以上、本発明に係るインバータ装置の実施形態について具体的に説明したが、本発明は前記した各実施形態の内容に限定されるものではなく、その要旨を逸脱しない範囲で種々の変更が可能であることは言うまでもない。言い換えると、上述した各実施形態は、本発明の内容を分かりやすく説明するために詳細に例示したものであり、必ずしも前記で説明した全ての構成を備えるものに限定されるものではない。また、ある実施形態の構成の一部を他の実施形態の構成に置き換えることも可能であり、さらに、ある実施形態の構成に他の実施形態の構成を加えることも可能である。例えば、インバータ装置の主回路電流が大きくなるにしたがってゲート抵抗値を段階的に大きくするように切り替えるのではなく、主回路電流が大きくなるにしたがってゲート抵抗値が連続的に大きくなるように連続可変させてもよい。

【産業上の利用可能性】

【0101】

本発明のインバータ装置によれば、パワー半導体スイッチング素子のターンオン損失及びスイッチング損失や、還流用ダイオードのリカバリ損失を低減させたり、スイッチングノイズを低減させることができるので、品質の高い電源が要求される各種機器としても有効に利用することが可能である。

【符号の説明】

【0102】

1a,1b,1c インバータ装置

10 インバータ主回路

11,12 Si−IGBT(パワー半導体スイッチング素子)

11g,12g,21,22,21a,21b,31,32,31a,31b ゲート抵抗(ゲートインピーダンス)

13,14 ユニポーラ型ダイオード

15 主回路電源

16,17 主回路インダクタンス

18 主回路電流検出カレントトランス(電流検出手段)

19 主回路

20,20a 上アーム駆動/制御回路

23,23a,23b,33,33a,33b ゲート抵抗切替用pMOS(ゲートインピーダンス切替手段)

24,34 npnトランジスタ

25,35 pnpトランジスタ

26,36 駆動ロジック回路

27,28,37,38 駆動/制御回路電源

30,30a 下アーム駆動/制御回路

40 制御回路(スイッチング回数低減手段)

50 主回路電流検出回路(電流検出手段)

51 制御信号線

【特許請求の範囲】

【請求項1】

パワー半導体スイッチング素子とユニポーラ型ダイオードとが逆並列に接続されたパワー半導体モジュールを備えたインバータ装置であって、

前記パワー半導体モジュールに流れる電流を検出する電流検出手段と、

前記電流検出手段が検出した電流値が所定値より大きいときに、前記パワー半導体スイッチング素子を駆動するゲート駆動回路のゲートインピーダンスを大きくするように、該ゲートインピーダンスを切り替えるゲートインピーダンス切替手段と、

を備えることを特徴とするインバータ装置。

【請求項2】

前記パワー半導体スイッチング素子はPWM制御を行うものであって、

前記電流検出手段が検出した電流値が所定値より大きいときに、前記PWM制御のスイッチング回数を低減させるスイッチング回数低減手段をさらに備えることを特徴とする請求項1に記載のインバータ装置。

【請求項3】

前記ゲートインピーダンス切替手段は、前記電流検出手段が検出した電流値の大きさに応じて前記ゲートインピーダンスを2段階以上に可変させることを特徴とする請求項1または請求項2に記載のインバータ装置。

【請求項4】

前記スイッチング回数低減手段は、前記電流検出手段が検出した電流値の大きさに応じて前記PWM制御のスイッチング回数を2段階以上に可変させることを特徴とする請求項2または請求項3に記載のインバータ装置。

【請求項5】

前記パワー半導体スイッチング素子は、シリコン、炭化ケイ素、窒化ガリウム、またはダイヤモンドの少なくとも1つの材料によって生成されていることを特徴とする請求項1ないし請求項4のいずれか1項に記載のインバータ装置。

【請求項6】

前記パワー半導体スイッチング素子は、絶縁ゲートバイポーラトランジスタ、接合型電界効果トランジスタ、金属酸化膜型電界効果トランジスタのいずれかであることを特徴とする請求項5に記載のインバータ装置。

【請求項7】

前記ユニポーラ型ダイオードは、シリコン、炭化ケイ素、窒化ガリウム、またはダイヤモンドの少なくとも1つの材料によって生成されたワイドギャップ半導体であることを特徴とする請求項1ないし請求項6のいずれか1項に記載のインバータ装置。

【請求項8】

前記ユニポーラ型ダイオードは、逆回復時の電圧変化率が電流値に比例して大きくなるショットキーバリアダイオードであることを特徴とする請求項7に記載のインバータ装置。

【請求項1】

パワー半導体スイッチング素子とユニポーラ型ダイオードとが逆並列に接続されたパワー半導体モジュールを備えたインバータ装置であって、

前記パワー半導体モジュールに流れる電流を検出する電流検出手段と、

前記電流検出手段が検出した電流値が所定値より大きいときに、前記パワー半導体スイッチング素子を駆動するゲート駆動回路のゲートインピーダンスを大きくするように、該ゲートインピーダンスを切り替えるゲートインピーダンス切替手段と、

を備えることを特徴とするインバータ装置。

【請求項2】

前記パワー半導体スイッチング素子はPWM制御を行うものであって、

前記電流検出手段が検出した電流値が所定値より大きいときに、前記PWM制御のスイッチング回数を低減させるスイッチング回数低減手段をさらに備えることを特徴とする請求項1に記載のインバータ装置。

【請求項3】

前記ゲートインピーダンス切替手段は、前記電流検出手段が検出した電流値の大きさに応じて前記ゲートインピーダンスを2段階以上に可変させることを特徴とする請求項1または請求項2に記載のインバータ装置。

【請求項4】

前記スイッチング回数低減手段は、前記電流検出手段が検出した電流値の大きさに応じて前記PWM制御のスイッチング回数を2段階以上に可変させることを特徴とする請求項2または請求項3に記載のインバータ装置。

【請求項5】

前記パワー半導体スイッチング素子は、シリコン、炭化ケイ素、窒化ガリウム、またはダイヤモンドの少なくとも1つの材料によって生成されていることを特徴とする請求項1ないし請求項4のいずれか1項に記載のインバータ装置。

【請求項6】

前記パワー半導体スイッチング素子は、絶縁ゲートバイポーラトランジスタ、接合型電界効果トランジスタ、金属酸化膜型電界効果トランジスタのいずれかであることを特徴とする請求項5に記載のインバータ装置。

【請求項7】

前記ユニポーラ型ダイオードは、シリコン、炭化ケイ素、窒化ガリウム、またはダイヤモンドの少なくとも1つの材料によって生成されたワイドギャップ半導体であることを特徴とする請求項1ないし請求項6のいずれか1項に記載のインバータ装置。

【請求項8】

前記ユニポーラ型ダイオードは、逆回復時の電圧変化率が電流値に比例して大きくなるショットキーバリアダイオードであることを特徴とする請求項7に記載のインバータ装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−110878(P2013−110878A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−254698(P2011−254698)

【出願日】平成23年11月22日(2011.11.22)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月22日(2011.11.22)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]