インバータ駆動装置

【課題】電気的に絶縁された回路間で電力伝達と信号伝達を行う構成を有していても、回路基板の小型化を容易に実現できる、インバータ駆動装置の提供をすること。

【解決手段】PWM信号S1を互いに相補する2つの波形信号S3A,S3Bに変換する変換回路と、下アーム素子47Aに駆動信号S7Aを伝達する下アーム回路212と,上アーム素子47Bに駆動信号S7Bを伝達する上アーム回路213と、下アーム回路212と上アーム回路213に給電を行うトランス36とを備え、トランス36が、2つの波形信号S3A,S3Bのうち、波形信号S3Aを下アーム回路212に伝達し、波形信号S3Bを上アーム回路213に伝達する、インバータ駆動装置。

【解決手段】PWM信号S1を互いに相補する2つの波形信号S3A,S3Bに変換する変換回路と、下アーム素子47Aに駆動信号S7Aを伝達する下アーム回路212と,上アーム素子47Bに駆動信号S7Bを伝達する上アーム回路213と、下アーム回路212と上アーム回路213に給電を行うトランス36とを備え、トランス36が、2つの波形信号S3A,S3Bのうち、波形信号S3Aを下アーム回路212に伝達し、波形信号S3Bを上アーム回路213に伝達する、インバータ駆動装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気的に絶縁された回路間で電力伝達と信号伝達が行われるインバータ駆動装置に関する。

【背景技術】

【0002】

従来、電気的に絶縁された回路間での電力伝達手段として、プッシュプルコンバータやフライバックコンバータ等の絶縁型スイッチング電源用の電源トランスが使用され、電気的に絶縁された回路間での信号伝達手段として、フォトカプラや磁気カプラ等の絶縁通信素子が使用されていた。すなわち、電力伝達と信号伝達の用途毎に、それぞれ異なる絶縁部品が使われていた。

【0003】

電気的に絶縁された回路間で電力伝達と信号伝達を行うことが可能な構成が開示された先行技術文献として、例えば、特許文献1,2が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭58−103095号公報

【特許文献2】特開2009−44837号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

FA機器や車載機器を問わず、パワーエレクトロニクスユニットの小型化が推進されている中で、そのユニット内部の回路基板の小型化も同様に求められている。ところが、パワーエレクトロニクスユニットでは、絶縁破壊による感電・漏電を防止するため、モータやアクチュエータ等を駆動する駆動回路などの高電圧回路部と、制御回路(例えば、マイクロコンピュータ(以下、「マイコン」という))などの低電圧回路部とを電気的に絶縁する必要がある。絶縁に必要な距離はJIS等で規格化されていて、高電圧/低電圧回路部間の電位差に比例して、絶縁距離は長くなる。そのため、高電圧を扱うパワーエレクトロニクスユニットでは、絶縁距離が長くなる傾向があり、そのユニット内部の回路基板上の絶縁部品も絶縁距離を確保するために体格の大きなものを使用しなければならず、ユニット内部の回路基板を小型化することは容易ではない。

【0006】

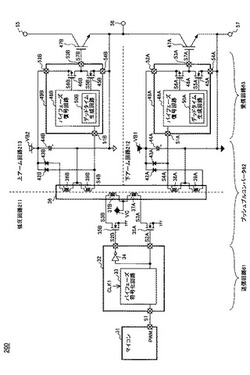

このようなパワーエレクトロニクスユニットの一例として、インバータ駆動装置が挙げられる。図1は、インバータ駆動装置の一例を示したものである。図1に示されるインバータ駆動装置100は、低電圧回路部として低圧回路11を有し、高電圧回路部として下アーム回路12及び上アーム回路13を有している。

【0007】

低圧回路11の電源IC2Aは、トランジスタ3A,4Aの駆動を制御することによって、トランス10Aを介して、下アーム回路12側の電源電圧VB1を生成する。電源電圧VB1は、IGBTなどの半導体スイッチング素子17Aを駆動する駆動回路19Aの動作電源である。同様に、低圧回路11の電源IC2Bは、トランジスタ3B,4Bの駆動を制御することによって、トランス10Bを介して、上アーム回路13側の電源電圧VB2を生成する。電源電圧VB2は、IGBTなどの半導体スイッチング素子17Bを駆動する駆動回路19Bの動作電源である。

【0008】

一方、低圧回路11のマイコン1は、トランジスタ5Aの駆動をPWM制御することによって、フォトカプラ11Aを介して、半導体スイッチング素子17Aを駆動する駆動回路19Aの動作を制御する。フォトカプラ11Aは、半導体スイッチング素子17Aの駆動信号を伝達するための信号伝達素子である。同様に、マイコン1は、トランジスタ5Bの駆動をPWM制御することによって、フォトカプラ11Bを介して、半導体スイッチング素子17Bを駆動する駆動回路19Bの動作を制御する。フォトカプラ11Bは、半導体スイッチング素子17Bの駆動信号を伝達するための信号伝達素子である。

【0009】

このように、インバータ駆動装置100は、低圧回路11と下アーム回路12との間の電力伝達手段及び信号伝達手段として、トランス10A及びフォトカプラ11Aを備え、低圧回路11と上アーム回路13との間の電力伝達手段及び信号伝達手段として、トランス10B及びフォトカプラ11Bを備えている。

【0010】

しかしながら、図1に例示されるようなインバータ駆動装置の構成では、アーム回路毎に電力伝達手段と信号伝達手段が必要なため、回路基板を小型化することが難しい。

【0011】

そこで、本発明は、電気的に絶縁された回路間で電力伝達と信号伝達を行う構成を有していても、回路基板の小型化を容易に実現できる、インバータ駆動装置の提供を目的とする。

【課題を解決するための手段】

【0012】

上記目的を達成するため、本発明に係るインバータ駆動装置は、

入力信号を互いに相補する2つの波形信号に変換する変換回路と、

第1の半導体スイッチング素子に駆動信号を伝達する下アーム回路と、

第2の半導体スイッチング素子に駆動信号を伝達する上アーム回路と、

前記下アーム回路と前記上アーム回路に給電を行うトランスとを備え、

前記トランスが、前記2つの波形信号のうち、一方の波形信号を前記下アーム回路に伝達し、他方の波形信号を前記上アーム回路に伝達する、ことを特徴とするものである。

【発明の効果】

【0013】

本発明によれば、電気的に絶縁された回路間で電力伝達と信号伝達を行う構成を有していても、回路基板の小型化を容易に実現できる。

【図面の簡単な説明】

【0014】

【図1】インバータ駆動装置100の構成図である。

【図2】本発明の一実施形態であるインバータ駆動装置200の構成図である。

【図3】インバータ駆動装置200の各部の信号波形である。

【図4】デッドタイム生成回路60の構成図である。

【図5】デッドタイムDT1,DT2が付与された場合の信号波形である。

【図6】本発明のインバータ駆動装置の実施例であるモータ駆動装置300の構成図である。

【発明を実施するための形態】

【0015】

以下、図面を参照しながら、本発明を実施するための形態の説明を行う。図2は、本発明の一実施形態であるインバータ駆動装置200の構成図である。図3は、インバータ駆動装置200の各部の信号波形である。図2に示される各構成部品が基板上に実装され、回路基板を構成する。

【0016】

SiCを用いたインバータ駆動装置200は、半導体スイッチング素子17Aと17Bによって構成されるハーフブリッジ回路を備え、半導体スイッチング素子17A,17Bを駆動することによって、17Aと17Bとの接続点であるノード56に接続される不図示の負荷に流れる電流を制御する。半導体スイッチング素子17A,17B及び後述する他のトランジスタは、電流の導通・遮断が可能な半導体素子である。その具体例として、IGBT,MOSFET,バイポーラトランジスタなどのトランジスタが挙げられる。以下、半導体スイッチング素子17Aを下アーム素子17Aといい、半導体スイッチング素子17Bを上アーム素子17Bという。

【0017】

インバータ駆動装置200は、低電圧回路部として低圧回路211を有し、高電圧回路部として下アーム回路212及び上アーム回路213を有している。より詳細には、インバータ駆動装置200は、マイコン31と、送信回路61と、プッシュプルコンバータ62と、受信回路63とを備えている。

【0018】

マイコン31は、送信回路61の符号化IC32に入力される入力信号として、下アーム素子17Aと上アーム素子17Bを駆動するためのPWM信号S1を出力する制御部である。

【0019】

送信回路61の符号化IC32は、クロック信号CLK1に従って、PWM信号S1をバイフェーズ符号化するバイフェーズ符号化回路33を備えている。送信回路61の符号化IC32は、プッシュプルコンバータ62のローサイドMOSFET35Aの駆動信号として、バイフェーズ符号化回路33がPWM信号S1をバイフェーズ符号化することにより得られたバイフェーズ符号化信号S2Aを出力する。また、符号化IC32は、プッシュプルコンバータ62のハイサイドMOSFET35Bの駆動信号として、バイフェーズ符号化信号S2Aを反転回路34によって反転させた相補信号S2B(バイフェーズ符号化信号S2B)を出力する(図3参照)。

【0020】

ローサイドMOSFET35Aは、トランス36のローサイド一次巻線37Aに印加されるローサイド入力電圧信号として、バイフェーズ符号化信号S2Aのレベルを反転させたバイフェーズ符号化信号S3Aを出力する。一方、ハイサイドMOSFET35Bは、トランス36のハイサイド一次巻線37Bに印加されるハイサイド入力電圧信号として、バイフェーズ符号化信号S2Bのレベルを反転させたバイフェーズ符号化信号S3Bを出力する。

【0021】

つまり、送信回路61、並びにローサイドMOSFET35A及びハイサイドMOSFET35Bによって、PWM信号S1が、互いに相補する2つのバイフェーズ符号化された信号S3A,S3Bに変換されている。

【0022】

プッシュプルコンバータ62は、下アーム回路212と上アーム回路213のそれぞれに電力と信号を伝達できるように、1入力2出力の電源トランス36を備えている。トランス36の一次側のセンタータップには入力電圧VCが供給される。入力電圧VCは、低圧回路211側の電源電圧である。トランス36の二次側のローサイドの二次巻線(38A,39A)の両端にはダイオード42A,43Aのアノードが接続され、トランス36の二次側のハイサイドの二次巻線(38B,39B)の両端にはダイオード42B,43Bのアノードが接続されている。トランス36の二次側のローサイドのセンタータップには、電解コンデンサ44Aの負極端子及び下アーム素子47Aのエミッタが接続され、トランス36の二次側のハイサイドのセンタータップには、電解コンデンサ44Bの負極端子及び上アーム素子47Bのエミッタが接続されている。電解コンデンサ44Aの正極端子は、ダイオード42A,43Aのカソードに接続され、電解コンデンサ44Bの正極端子は、ダイオード42B,43Bのカソードに接続されている。

【0023】

したがって、この構成によれば、トランス35は、一次側の入力電圧VCとバイフェーズ符号化信号S3A,S3Bとに基づいて、二次側の下アーム回路212側の電源電圧VB1の電力伝達と、二次側の上アーム回路213側の電源電圧VB2の電力伝達とを行うことができる。そして、下アーム回路212と上アーム回路213の両方に給電可能なトランス36が、ローサイドの二次巻線(38A,39A)から出力される出力波形信号S4Aとして、バイフェーズ符号化信号S3Aを下アーム回路212に伝達できるとともに、ハイサイドの二次巻線(38B,39B)から出力される出力波形信号S4Bとして、バイフェーズ符号化信号S3Bを上アーム回路213に伝達できる(図3参照)。

【0024】

受信回路63は、出力波形信号S4Aに従って下アーム素子47Aを駆動するローサイドの駆動IC49Aと、出力波形信号S4Bに従って上アーム素子47Bを駆動するハイサイドの駆動IC49Bとを備えている。駆動IC49Aは、バイフェーズ符号化された出力波形信号S4Aを復号するバイフェーズ復号回路48Aを備え、駆動IC49Bは、バイフェーズ符号化された出力波形信号S4Bを復号するバイフェーズ復号回路48Bを備えている。

【0025】

下アーム回路212の駆動IC49Aは、下アーム素子47Aの駆動信号として、バイフェーズ復号回路48Aが出力波形信号S4Aを復調することにより得られたゲート信号S7Aを出力する。バイフェーズ復号回路48Aは、出力波形信号S4Aを復調してプリドライブ信号S6Aを生成する。ハイサイドトランジスタ46Aは、プリドライブ信号S6Aに基づいて、オン/オフする。ハイサイドトランジスタ46Aがオン状態のとき、下アーム素子47Aはオン状態であり、ハイサイドトランジスタ46Aがオフ状態のとき、下アーム素子47Aはオフ状態である。上アーム回路213についても同様である。すなわち、駆動IC49Bは、上アーム素子47Bの駆動信号として、バイフェーズ復号回路48Bが出力波形信号S4Bを復調することにより得られたゲート信号S7Bを出力する(図3参照)。

【0026】

したがって、図2の構成によれば、図1に信号伝達手段として例示したフォトカプラ17A,17Bを削除することができる。また、上アーム回路と下アーム回路への電力伝達及び信号伝達を一つのトランス36で行うことができる。つまり、回路基板の小型化を容易に実現でき、部品点数やコストの削減を容易に実現できる。

【0027】

ところで、本発明のインバータ駆動装置の下アーム回路と上アーム回路のそれぞれに、デッドタイム付与手段が備えられていると、上アーム素子と下アーム素子に流れる貫通電流の発生を防ぐ点で好適である。このデッドタイム付与手段は、バイフェーズ符号化された信号を復号した信号に、そのバイフェーズ符号化された信号に含まれるクロック成分を利用して、デッドタイムを付与する。

【0028】

例えば、図2の場合、トランス36の二次側から下アーム回路212と上アーム回路213のそれぞれに伝達されるバイフェーズ符号化された出力波形信号S4A,S4Bは、その位相差が180°反転しているが、そのクロック成分の位相差は零である。そのため、そのクロック成分から抽出して生成されたクロック信号(以下、「クロック信号CLK2」という)の位相差も零である。つまり、クロック信号CLK2を利用してデッドタイムを生成すれば、ゲート信号S7A,S7Bのそれぞれにデッドタイムを遅延無く付与することができる。デッドタイム付与手段の具体例を図4に示す。

【0029】

図4は、デッドタイム生成回路50の構成図である。デッドタイム生成回路50は、2段のDフリップフロップ61,62と、AND回路63とを備えたデッドタイム付与手段である。Dフリップフロップの数に応じてデッドタイムの長さを伸縮でき、その数を増やした分だけデッドタイムの長さを伸ばすことができる。デッドタイム生成回路50の出力信号S9が、上述のゲート信号S7A,S7B(又は、プリドライブ信号S6A,S6B)として生成される。

【0030】

図5は、デッドタイムDT1,DT2が付与された場合の信号波形である。下アーム側のバイフェーズ復号回路48Aは、バイフェーズ符号化された出力波形信号S4Aを復調することによって、復調PWM信号S8Aを生成する。下アーム側のデッドタイム生成回路50Aは、復調PWM信号S8Aの立ち上がりエッジからデッドタイムDT2だけ遅延したデッドタイム付与PWM信号S9Aを生成する。駆動IC49Aは、下アーム素子47Aのゲートに印加されるゲート信号S7Aとして、デッドタイム付与PWM信号S9Aを出力する。デッドタイム付与PWM信号S9Aがハイレベルのとき、下アーム素子47Aはオンし、デッドタイム付与PWM信号S9Aがローレベルのとき、下アーム素子47Aはオフする。

【0031】

同様に、上アーム側のバイフェーズ復号回路48Bは、バイフェーズ符号化された出力波形信号S4Bを復調することによって、復調PWM信号S8Bを生成する。上アーム側のデッドタイム生成回路50Bは、復調PWM信号S8Bの立ち上がりエッジからデッドタイムDT1だけ遅延したデッドタイム付与PWM信号S9Bを生成する。駆動IC49Bは、上アーム素子47Bのゲートに印加されるゲート信号S7Bとして、デッドタイム付与PWM信号S9Bを出力する。デッドタイム付与PWM信号S9Bがハイレベルのとき、上アーム素子47Bはオンし、デッドタイム付与PWM信号S9Bがローレベルのとき、上アーム素子47Bはオフする。

【0032】

したがって、一般に精確なデッドタイムを付与するにはクリスタル等の発振子を使ったクロック回路が必要であるが、上記のデッドタイム付与手段を設けることによって、そのようなクロック回路が無くても、精確なデッドタイムを付与することができる。

【0033】

図6は、本発明のインバータ駆動装置の実施例であるモータ駆動装置300の構成図である。モータ駆動装置300は、モータ80を駆動する駆動装置であって、半導体スイッチング素子SW1〜SW6(例えば、IGBT)から構成されるインバータ回路と、そのインバータ回路を駆動する駆動回路部70とを備えている。駆動回路部70は、MCU71と、P/S−IC(72U,72V,72W)と、トランス(73U,73V,73W)と、プリドライバ(74U,74V,74W)とを備えている。

【0034】

MCU71は、モータ80を駆動するためのPWM信号を、各相のP/S−ICに出力するマイコンである。P/S−IC72Uは、MCU71から出力されたPWM信号をバイフェーズ符号化し、そのバイフェーズ符号化した信号でトランス73Uを駆動する電源ICである。トランス73Uから出力される電力でプリドライバ74U1,74U2を動作させる。また、トランス73Uから出力される信号を受信して復号したプリドライバ74U1,74U2が、デッドタイムを付与してIGBT等の半導体スイッチング素子SW1,SW2を駆動する。他のV相、W相についても同様である。このような構成によれば、電源電圧E1を動作電源電圧とする半導体スイッチング素子SW1〜SW6のスイッチ動作により生成される3相交流電流によって、モータ80の駆動が可能である。

【0035】

なお、本構成は、例えば、FA機器のモータ、エアコンや冷蔵庫等の家庭用電化製品のモータ、モータとエンジンを併用するいわゆるハイブリッド車両や電気自動車等の車載モータなどの駆動装置にも適用できる。

【0036】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【0037】

例えば、本発明の実施例としてモータ駆動装置の場合を例に挙げたが、スイッチング電源装置に適用することもできる。

【符号の説明】

【0038】

10A,10B トランス

11A,11B フォトカプラ

17A,47A 下アーム素子(半導体スイッチング素子)

17B,47B 上アーム素子(半導体スイッチング素子)

19A,19B 駆動回路

31 マイコン

32 符号化IC

33 バイフェーズ符号化回路33

36 トランス

49A,49B 駆動IC

50 デッドタイム生成回路

61,62 Dフリッププロップ

70 駆動回路部

80 モータ

100,200 インバータ駆動装置

300 モータ駆動装置

S1 PWM信号

S2A,S2B,S3A,S3B,S4A,S4B バイフェーズ符号化信号

S7A,S7B ゲート信号

【技術分野】

【0001】

本発明は、電気的に絶縁された回路間で電力伝達と信号伝達が行われるインバータ駆動装置に関する。

【背景技術】

【0002】

従来、電気的に絶縁された回路間での電力伝達手段として、プッシュプルコンバータやフライバックコンバータ等の絶縁型スイッチング電源用の電源トランスが使用され、電気的に絶縁された回路間での信号伝達手段として、フォトカプラや磁気カプラ等の絶縁通信素子が使用されていた。すなわち、電力伝達と信号伝達の用途毎に、それぞれ異なる絶縁部品が使われていた。

【0003】

電気的に絶縁された回路間で電力伝達と信号伝達を行うことが可能な構成が開示された先行技術文献として、例えば、特許文献1,2が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭58−103095号公報

【特許文献2】特開2009−44837号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

FA機器や車載機器を問わず、パワーエレクトロニクスユニットの小型化が推進されている中で、そのユニット内部の回路基板の小型化も同様に求められている。ところが、パワーエレクトロニクスユニットでは、絶縁破壊による感電・漏電を防止するため、モータやアクチュエータ等を駆動する駆動回路などの高電圧回路部と、制御回路(例えば、マイクロコンピュータ(以下、「マイコン」という))などの低電圧回路部とを電気的に絶縁する必要がある。絶縁に必要な距離はJIS等で規格化されていて、高電圧/低電圧回路部間の電位差に比例して、絶縁距離は長くなる。そのため、高電圧を扱うパワーエレクトロニクスユニットでは、絶縁距離が長くなる傾向があり、そのユニット内部の回路基板上の絶縁部品も絶縁距離を確保するために体格の大きなものを使用しなければならず、ユニット内部の回路基板を小型化することは容易ではない。

【0006】

このようなパワーエレクトロニクスユニットの一例として、インバータ駆動装置が挙げられる。図1は、インバータ駆動装置の一例を示したものである。図1に示されるインバータ駆動装置100は、低電圧回路部として低圧回路11を有し、高電圧回路部として下アーム回路12及び上アーム回路13を有している。

【0007】

低圧回路11の電源IC2Aは、トランジスタ3A,4Aの駆動を制御することによって、トランス10Aを介して、下アーム回路12側の電源電圧VB1を生成する。電源電圧VB1は、IGBTなどの半導体スイッチング素子17Aを駆動する駆動回路19Aの動作電源である。同様に、低圧回路11の電源IC2Bは、トランジスタ3B,4Bの駆動を制御することによって、トランス10Bを介して、上アーム回路13側の電源電圧VB2を生成する。電源電圧VB2は、IGBTなどの半導体スイッチング素子17Bを駆動する駆動回路19Bの動作電源である。

【0008】

一方、低圧回路11のマイコン1は、トランジスタ5Aの駆動をPWM制御することによって、フォトカプラ11Aを介して、半導体スイッチング素子17Aを駆動する駆動回路19Aの動作を制御する。フォトカプラ11Aは、半導体スイッチング素子17Aの駆動信号を伝達するための信号伝達素子である。同様に、マイコン1は、トランジスタ5Bの駆動をPWM制御することによって、フォトカプラ11Bを介して、半導体スイッチング素子17Bを駆動する駆動回路19Bの動作を制御する。フォトカプラ11Bは、半導体スイッチング素子17Bの駆動信号を伝達するための信号伝達素子である。

【0009】

このように、インバータ駆動装置100は、低圧回路11と下アーム回路12との間の電力伝達手段及び信号伝達手段として、トランス10A及びフォトカプラ11Aを備え、低圧回路11と上アーム回路13との間の電力伝達手段及び信号伝達手段として、トランス10B及びフォトカプラ11Bを備えている。

【0010】

しかしながら、図1に例示されるようなインバータ駆動装置の構成では、アーム回路毎に電力伝達手段と信号伝達手段が必要なため、回路基板を小型化することが難しい。

【0011】

そこで、本発明は、電気的に絶縁された回路間で電力伝達と信号伝達を行う構成を有していても、回路基板の小型化を容易に実現できる、インバータ駆動装置の提供を目的とする。

【課題を解決するための手段】

【0012】

上記目的を達成するため、本発明に係るインバータ駆動装置は、

入力信号を互いに相補する2つの波形信号に変換する変換回路と、

第1の半導体スイッチング素子に駆動信号を伝達する下アーム回路と、

第2の半導体スイッチング素子に駆動信号を伝達する上アーム回路と、

前記下アーム回路と前記上アーム回路に給電を行うトランスとを備え、

前記トランスが、前記2つの波形信号のうち、一方の波形信号を前記下アーム回路に伝達し、他方の波形信号を前記上アーム回路に伝達する、ことを特徴とするものである。

【発明の効果】

【0013】

本発明によれば、電気的に絶縁された回路間で電力伝達と信号伝達を行う構成を有していても、回路基板の小型化を容易に実現できる。

【図面の簡単な説明】

【0014】

【図1】インバータ駆動装置100の構成図である。

【図2】本発明の一実施形態であるインバータ駆動装置200の構成図である。

【図3】インバータ駆動装置200の各部の信号波形である。

【図4】デッドタイム生成回路60の構成図である。

【図5】デッドタイムDT1,DT2が付与された場合の信号波形である。

【図6】本発明のインバータ駆動装置の実施例であるモータ駆動装置300の構成図である。

【発明を実施するための形態】

【0015】

以下、図面を参照しながら、本発明を実施するための形態の説明を行う。図2は、本発明の一実施形態であるインバータ駆動装置200の構成図である。図3は、インバータ駆動装置200の各部の信号波形である。図2に示される各構成部品が基板上に実装され、回路基板を構成する。

【0016】

SiCを用いたインバータ駆動装置200は、半導体スイッチング素子17Aと17Bによって構成されるハーフブリッジ回路を備え、半導体スイッチング素子17A,17Bを駆動することによって、17Aと17Bとの接続点であるノード56に接続される不図示の負荷に流れる電流を制御する。半導体スイッチング素子17A,17B及び後述する他のトランジスタは、電流の導通・遮断が可能な半導体素子である。その具体例として、IGBT,MOSFET,バイポーラトランジスタなどのトランジスタが挙げられる。以下、半導体スイッチング素子17Aを下アーム素子17Aといい、半導体スイッチング素子17Bを上アーム素子17Bという。

【0017】

インバータ駆動装置200は、低電圧回路部として低圧回路211を有し、高電圧回路部として下アーム回路212及び上アーム回路213を有している。より詳細には、インバータ駆動装置200は、マイコン31と、送信回路61と、プッシュプルコンバータ62と、受信回路63とを備えている。

【0018】

マイコン31は、送信回路61の符号化IC32に入力される入力信号として、下アーム素子17Aと上アーム素子17Bを駆動するためのPWM信号S1を出力する制御部である。

【0019】

送信回路61の符号化IC32は、クロック信号CLK1に従って、PWM信号S1をバイフェーズ符号化するバイフェーズ符号化回路33を備えている。送信回路61の符号化IC32は、プッシュプルコンバータ62のローサイドMOSFET35Aの駆動信号として、バイフェーズ符号化回路33がPWM信号S1をバイフェーズ符号化することにより得られたバイフェーズ符号化信号S2Aを出力する。また、符号化IC32は、プッシュプルコンバータ62のハイサイドMOSFET35Bの駆動信号として、バイフェーズ符号化信号S2Aを反転回路34によって反転させた相補信号S2B(バイフェーズ符号化信号S2B)を出力する(図3参照)。

【0020】

ローサイドMOSFET35Aは、トランス36のローサイド一次巻線37Aに印加されるローサイド入力電圧信号として、バイフェーズ符号化信号S2Aのレベルを反転させたバイフェーズ符号化信号S3Aを出力する。一方、ハイサイドMOSFET35Bは、トランス36のハイサイド一次巻線37Bに印加されるハイサイド入力電圧信号として、バイフェーズ符号化信号S2Bのレベルを反転させたバイフェーズ符号化信号S3Bを出力する。

【0021】

つまり、送信回路61、並びにローサイドMOSFET35A及びハイサイドMOSFET35Bによって、PWM信号S1が、互いに相補する2つのバイフェーズ符号化された信号S3A,S3Bに変換されている。

【0022】

プッシュプルコンバータ62は、下アーム回路212と上アーム回路213のそれぞれに電力と信号を伝達できるように、1入力2出力の電源トランス36を備えている。トランス36の一次側のセンタータップには入力電圧VCが供給される。入力電圧VCは、低圧回路211側の電源電圧である。トランス36の二次側のローサイドの二次巻線(38A,39A)の両端にはダイオード42A,43Aのアノードが接続され、トランス36の二次側のハイサイドの二次巻線(38B,39B)の両端にはダイオード42B,43Bのアノードが接続されている。トランス36の二次側のローサイドのセンタータップには、電解コンデンサ44Aの負極端子及び下アーム素子47Aのエミッタが接続され、トランス36の二次側のハイサイドのセンタータップには、電解コンデンサ44Bの負極端子及び上アーム素子47Bのエミッタが接続されている。電解コンデンサ44Aの正極端子は、ダイオード42A,43Aのカソードに接続され、電解コンデンサ44Bの正極端子は、ダイオード42B,43Bのカソードに接続されている。

【0023】

したがって、この構成によれば、トランス35は、一次側の入力電圧VCとバイフェーズ符号化信号S3A,S3Bとに基づいて、二次側の下アーム回路212側の電源電圧VB1の電力伝達と、二次側の上アーム回路213側の電源電圧VB2の電力伝達とを行うことができる。そして、下アーム回路212と上アーム回路213の両方に給電可能なトランス36が、ローサイドの二次巻線(38A,39A)から出力される出力波形信号S4Aとして、バイフェーズ符号化信号S3Aを下アーム回路212に伝達できるとともに、ハイサイドの二次巻線(38B,39B)から出力される出力波形信号S4Bとして、バイフェーズ符号化信号S3Bを上アーム回路213に伝達できる(図3参照)。

【0024】

受信回路63は、出力波形信号S4Aに従って下アーム素子47Aを駆動するローサイドの駆動IC49Aと、出力波形信号S4Bに従って上アーム素子47Bを駆動するハイサイドの駆動IC49Bとを備えている。駆動IC49Aは、バイフェーズ符号化された出力波形信号S4Aを復号するバイフェーズ復号回路48Aを備え、駆動IC49Bは、バイフェーズ符号化された出力波形信号S4Bを復号するバイフェーズ復号回路48Bを備えている。

【0025】

下アーム回路212の駆動IC49Aは、下アーム素子47Aの駆動信号として、バイフェーズ復号回路48Aが出力波形信号S4Aを復調することにより得られたゲート信号S7Aを出力する。バイフェーズ復号回路48Aは、出力波形信号S4Aを復調してプリドライブ信号S6Aを生成する。ハイサイドトランジスタ46Aは、プリドライブ信号S6Aに基づいて、オン/オフする。ハイサイドトランジスタ46Aがオン状態のとき、下アーム素子47Aはオン状態であり、ハイサイドトランジスタ46Aがオフ状態のとき、下アーム素子47Aはオフ状態である。上アーム回路213についても同様である。すなわち、駆動IC49Bは、上アーム素子47Bの駆動信号として、バイフェーズ復号回路48Bが出力波形信号S4Bを復調することにより得られたゲート信号S7Bを出力する(図3参照)。

【0026】

したがって、図2の構成によれば、図1に信号伝達手段として例示したフォトカプラ17A,17Bを削除することができる。また、上アーム回路と下アーム回路への電力伝達及び信号伝達を一つのトランス36で行うことができる。つまり、回路基板の小型化を容易に実現でき、部品点数やコストの削減を容易に実現できる。

【0027】

ところで、本発明のインバータ駆動装置の下アーム回路と上アーム回路のそれぞれに、デッドタイム付与手段が備えられていると、上アーム素子と下アーム素子に流れる貫通電流の発生を防ぐ点で好適である。このデッドタイム付与手段は、バイフェーズ符号化された信号を復号した信号に、そのバイフェーズ符号化された信号に含まれるクロック成分を利用して、デッドタイムを付与する。

【0028】

例えば、図2の場合、トランス36の二次側から下アーム回路212と上アーム回路213のそれぞれに伝達されるバイフェーズ符号化された出力波形信号S4A,S4Bは、その位相差が180°反転しているが、そのクロック成分の位相差は零である。そのため、そのクロック成分から抽出して生成されたクロック信号(以下、「クロック信号CLK2」という)の位相差も零である。つまり、クロック信号CLK2を利用してデッドタイムを生成すれば、ゲート信号S7A,S7Bのそれぞれにデッドタイムを遅延無く付与することができる。デッドタイム付与手段の具体例を図4に示す。

【0029】

図4は、デッドタイム生成回路50の構成図である。デッドタイム生成回路50は、2段のDフリップフロップ61,62と、AND回路63とを備えたデッドタイム付与手段である。Dフリップフロップの数に応じてデッドタイムの長さを伸縮でき、その数を増やした分だけデッドタイムの長さを伸ばすことができる。デッドタイム生成回路50の出力信号S9が、上述のゲート信号S7A,S7B(又は、プリドライブ信号S6A,S6B)として生成される。

【0030】

図5は、デッドタイムDT1,DT2が付与された場合の信号波形である。下アーム側のバイフェーズ復号回路48Aは、バイフェーズ符号化された出力波形信号S4Aを復調することによって、復調PWM信号S8Aを生成する。下アーム側のデッドタイム生成回路50Aは、復調PWM信号S8Aの立ち上がりエッジからデッドタイムDT2だけ遅延したデッドタイム付与PWM信号S9Aを生成する。駆動IC49Aは、下アーム素子47Aのゲートに印加されるゲート信号S7Aとして、デッドタイム付与PWM信号S9Aを出力する。デッドタイム付与PWM信号S9Aがハイレベルのとき、下アーム素子47Aはオンし、デッドタイム付与PWM信号S9Aがローレベルのとき、下アーム素子47Aはオフする。

【0031】

同様に、上アーム側のバイフェーズ復号回路48Bは、バイフェーズ符号化された出力波形信号S4Bを復調することによって、復調PWM信号S8Bを生成する。上アーム側のデッドタイム生成回路50Bは、復調PWM信号S8Bの立ち上がりエッジからデッドタイムDT1だけ遅延したデッドタイム付与PWM信号S9Bを生成する。駆動IC49Bは、上アーム素子47Bのゲートに印加されるゲート信号S7Bとして、デッドタイム付与PWM信号S9Bを出力する。デッドタイム付与PWM信号S9Bがハイレベルのとき、上アーム素子47Bはオンし、デッドタイム付与PWM信号S9Bがローレベルのとき、上アーム素子47Bはオフする。

【0032】

したがって、一般に精確なデッドタイムを付与するにはクリスタル等の発振子を使ったクロック回路が必要であるが、上記のデッドタイム付与手段を設けることによって、そのようなクロック回路が無くても、精確なデッドタイムを付与することができる。

【0033】

図6は、本発明のインバータ駆動装置の実施例であるモータ駆動装置300の構成図である。モータ駆動装置300は、モータ80を駆動する駆動装置であって、半導体スイッチング素子SW1〜SW6(例えば、IGBT)から構成されるインバータ回路と、そのインバータ回路を駆動する駆動回路部70とを備えている。駆動回路部70は、MCU71と、P/S−IC(72U,72V,72W)と、トランス(73U,73V,73W)と、プリドライバ(74U,74V,74W)とを備えている。

【0034】

MCU71は、モータ80を駆動するためのPWM信号を、各相のP/S−ICに出力するマイコンである。P/S−IC72Uは、MCU71から出力されたPWM信号をバイフェーズ符号化し、そのバイフェーズ符号化した信号でトランス73Uを駆動する電源ICである。トランス73Uから出力される電力でプリドライバ74U1,74U2を動作させる。また、トランス73Uから出力される信号を受信して復号したプリドライバ74U1,74U2が、デッドタイムを付与してIGBT等の半導体スイッチング素子SW1,SW2を駆動する。他のV相、W相についても同様である。このような構成によれば、電源電圧E1を動作電源電圧とする半導体スイッチング素子SW1〜SW6のスイッチ動作により生成される3相交流電流によって、モータ80の駆動が可能である。

【0035】

なお、本構成は、例えば、FA機器のモータ、エアコンや冷蔵庫等の家庭用電化製品のモータ、モータとエンジンを併用するいわゆるハイブリッド車両や電気自動車等の車載モータなどの駆動装置にも適用できる。

【0036】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【0037】

例えば、本発明の実施例としてモータ駆動装置の場合を例に挙げたが、スイッチング電源装置に適用することもできる。

【符号の説明】

【0038】

10A,10B トランス

11A,11B フォトカプラ

17A,47A 下アーム素子(半導体スイッチング素子)

17B,47B 上アーム素子(半導体スイッチング素子)

19A,19B 駆動回路

31 マイコン

32 符号化IC

33 バイフェーズ符号化回路33

36 トランス

49A,49B 駆動IC

50 デッドタイム生成回路

61,62 Dフリッププロップ

70 駆動回路部

80 モータ

100,200 インバータ駆動装置

300 モータ駆動装置

S1 PWM信号

S2A,S2B,S3A,S3B,S4A,S4B バイフェーズ符号化信号

S7A,S7B ゲート信号

【特許請求の範囲】

【請求項1】

入力信号を互いに相補する2つの波形信号に変換する変換回路と、

第1の半導体スイッチング素子に駆動信号を伝達する下アーム回路と、

第2の半導体スイッチング素子に駆動信号を伝達する上アーム回路と、

前記下アーム回路と前記上アーム回路に給電を行うトランスとを備え、

前記トランスが、前記2つの波形信号のうち、一方の波形信号を前記下アーム回路に伝達し、他方の波形信号を前記上アーム回路に伝達する、インバータ駆動装置。

【請求項2】

前記2つの波形信号が、バイフェーズ符号化された信号であって、

前記下アーム回路と前記上アーム回路のそれぞれが、

バイフェーズ符号化された信号を復号する復号手段と、

復号した信号に、バイフェーズ符号化された信号に含まれるクロック成分を利用してデッドタイムを付与するデッドタイム付与手段とを備える、インバータ駆動装置。

【請求項1】

入力信号を互いに相補する2つの波形信号に変換する変換回路と、

第1の半導体スイッチング素子に駆動信号を伝達する下アーム回路と、

第2の半導体スイッチング素子に駆動信号を伝達する上アーム回路と、

前記下アーム回路と前記上アーム回路に給電を行うトランスとを備え、

前記トランスが、前記2つの波形信号のうち、一方の波形信号を前記下アーム回路に伝達し、他方の波形信号を前記上アーム回路に伝達する、インバータ駆動装置。

【請求項2】

前記2つの波形信号が、バイフェーズ符号化された信号であって、

前記下アーム回路と前記上アーム回路のそれぞれが、

バイフェーズ符号化された信号を復号する復号手段と、

復号した信号に、バイフェーズ符号化された信号に含まれるクロック成分を利用してデッドタイムを付与するデッドタイム付与手段とを備える、インバータ駆動装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−95409(P2012−95409A)

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願番号】特願2010−239221(P2010−239221)

【出願日】平成22年10月26日(2010.10.26)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願日】平成22年10月26日(2010.10.26)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]