インピーダンス変換型集中定数ブランチカプラによる電力多分配回路

【課題】

ブランチラインカプラを用いて構成される4分配回路について、その回路構成法の提案。更に集中定数化回路において、素子数の低減、更には特性の改善を目的とする。

【解決手段】

λ/4伝送線路と3λ/4伝送線路の組み合わせを工夫し、キャパシタやインダクタ等の素子数を基本回路の8個から減らし6個としたインピーダンス変換型のブランチラインカプラを考案した。さらに、それらを用いて4分配回路構成を検討することで、通常22個の素子数を18〜14個と大幅に減らすことに成功した。

本発明の電力4分配回路は、携帯電話、衛星通信などの移動通信装置や固定の通信装置の外来電波入出力部において信号を分配する回路や電力増幅回路やアンテナ等の給配電回路として利用できる。

ブランチラインカプラを用いて構成される4分配回路について、その回路構成法の提案。更に集中定数化回路において、素子数の低減、更には特性の改善を目的とする。

【解決手段】

λ/4伝送線路と3λ/4伝送線路の組み合わせを工夫し、キャパシタやインダクタ等の素子数を基本回路の8個から減らし6個としたインピーダンス変換型のブランチラインカプラを考案した。さらに、それらを用いて4分配回路構成を検討することで、通常22個の素子数を18〜14個と大幅に減らすことに成功した。

本発明の電力4分配回路は、携帯電話、衛星通信などの移動通信装置や固定の通信装置の外来電波入出力部において信号を分配する回路や電力増幅回路やアンテナ等の給配電回路として利用できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、インピーダンス変換型集中定数ブランチラインカプラを用いた電力多分配回路に関する。特に、集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを組み合わせた電力4分配回路に関する。

【背景技術】

【0002】

マイクロ波、ミリ波は通常数1GHzを越えるに非常に広い周波数範囲の電磁波で、携帯電話や衛星通信、テレビ放送、レーダーのほか、物性研究などの物理学の分野でも広く用いられており、さらに医学や天文学、またマイクロ波加熱、高エネルギー発生など、その利用範囲は極めて広い。

マイクロ波、ミリ波の信号を2方向に分配し、その2つの出力信号間に90度の位相差を与える回路として良く知られているものに分布定数ブランチラインカプラがある。この回路は構成要素である伝送線路の長さが波長の1/4であるため、回路サイズとして大型になりやすい。この解決法の1つとしてキャパシタやインダクタ等の集中定数素子を構成要素として取り入れる方法がある。これにより、基板上の回路占有面積を格段に小さくすることができる。この時、用いるキャパシタやインダクタ等の素子数は基本回路においては8個である。

一方、インピーダンス変換型集中定数90度ハイブリッドカプラに関し、キャパシタやインダクタ等の素子数が6個のものが知られている(非特許文献1)。また、ブランチラインカプラを用いた4分配回路において、標準型4分配回路とインピーダンス変換型4分配回路について周波数特性の比較がなされている(非特許文献2)。

【0003】

【非特許文献1】電子情報通信学会ソサイエティ大会講演論文集, p75 (2005)

【非特許文献2】電子情報通信学会技術研究報告, 107(394), 7-12(2007)

【発明の開示】

【発明が解決しようとする課題】

【0004】

ブランチラインカプラは90度の奇数倍の位相差を与えるマイクロ波、ミリ波回路素子の一つとして、信号分配・合成器、半導体電力増幅器、アレーアンテナ給電系、ミキサ、半導体移相器等、多種多様に用いられている。

本発明は、ブランチラインカプラを3個用いて構成される4分配回路について、その回路構成法の提案するものであり、更に集中定数化回路において、素子数の低減、更には特性の改善を目的とするものである。

【課題を解決するための手段】

【0005】

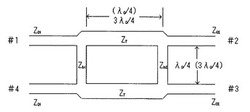

図6.1に示すλ/4伝送線路と3λ/4伝送線路の組み合わせを工夫し、図6.4、図6.5に示すようにキャパシタやインダクタ等の素子数を基本回路の8個から減らし6個としたインピーダンス変換型のブランチラインカプラを考案した。さらに、それらを用いて4分配回路構成を検討することで、通常22個の素子数を18〜14個と大幅に減らすことに成功し本発明を完成した。

以下、本発明を詳細に説明する。

【0006】

図6.1はλ/4伝送線路と3λ/4伝送線路の組み合わせの中で特にCase CまたはCase Dの場合を示しており、Guptaの回路モデルを前提としている。即ち、ポート#1およびポート#4には基準インピーダンスZ01、ポート#2およびポート#3には規格化負荷インピーダンスZ02が接続され、4本の伝送線路の規格化特性インピーダンスをzb1、zb2、zTとする。また、これらの逆数(アドミッタンス)をy02、yb1、yb2、yTとする。

この時、ポート1を入力端子とすると中心周波数において、条件式及び設計式は

【0007】

【数1】

【数2】

【数3】

となる。kは結合係数である。

【0008】

Case C(ブランチラインがλ0/4、スルーラインが3λ0/4)に等価変換を適用すると、図6.2が得られる。図6.2(b)はシャント部分を示す。

【0009】

Case Cの図6.2(a)のシリーズの素子値は

【数4】

となる。図6.2(b)のP1、P2の回路についてclを求めると

【0010】

【数5】

【数6】

となる。

【0011】

Case D(ブランチラインが3λ0/4、スルーラインがλ0/4)に等価変換を適用すると、図6.3が得られる。

【0012】

Case Dの図6.3(a)のシリーズの素子値は

【数7】

となる。図6.3(b)のについてclを求めると

【数8】

【数9】

となる。

【0013】

Case C、Case Dのどちらの場合でも積clによってP1、P2の回路は3通りに分類される。

C(容量性)の場合: cl > 1

シャント成分を除去できる場合: cl = 1

L(誘導性)の場合: cl > 1

【0014】

<Case C、Dにおけるcl=1の場合>

Case Cの式(6.5)においてcl=1とすると式(6.10)が、式(6.6)において

cl=1とすると式(6.11)が得られる。

【数10】

【数11】

同様に、Case Dの式(6.8)においてcl=1とすると式(6.12)が、式(6.9)においてcl=1とすると式(6.13)が得られる。

【数12】

【数13】

ここで、k>0であるから、式(6.10)、式(6.11)または、式(6.12)、式(6.13)は同時に成立しない。また、z02≠1である。このことは、シャント成分を除去することができるのはインピーダンス変換型の場合に限られ、P1回路か、P2回路のどちらか一方であることを意味している。

【0015】

これらのことより、cl=1となり、素子数を低減させたCase Cの回路を図6.4、に示す。同様に、cl=1となり、素子数を低減させたCase Dの回路を図6.5に示す。ここでは、均等分配(k=1)を仮定している。

【0016】

<インピーダンス変換型集中定数ブランチカップラ(Case C,Case D)を用いた4分配回路>

インピーダンス変換型Case C(図6.4)とインピーダンス変換型Case D(図6.5)を用いて、4分配回路を構成した。

インピーダンス変換型Case C(図6.4)を(a)−(b)とつないだ4分配回路をtype C1、(b)−(a)とつないだ4分配回路をtype C2として、図7.1、図7.2にその等価回路を示す。同様にインピーダンス変換型Case D(図6.5)を(a)−(b)とつないだ4分配回路をtype D1、(b)−(a)とつないだ4分配回路をtype D2として、図7.3、図7.4にその等価回路を示す。

【0017】

<発明の効果>

本発明の回路においては、ポートからの入力は無反射でアイソレーションがとれており、また出力ポートに信号が1/4ずつ均等分配される。

また、従来型の素子数を22個から18個以下に低減しても、分配特性、反射・アイソレーション特性は劣化しない。

【実施例】

【0018】

本発明を以下の実施例および参考例で説明するが本発明はそれらに限定されない。

実施例1

素子18(キャパシタ6、インダクタ12)の回路図を図1Aに示す。また、その周波数特性を図1A-a〜1A-eに示す。

【0019】

実施例2

素子18(キャパシタ12、インダクタ6)の回路図を図1Bに示す。また、その周波数特性を図1B-a〜1B-eに示す。

【0020】

実施例3

素子16(キャパシタ6、インダクタ10)の回路図を図2Aに示す。また、その周波数特性を図2A-a〜2A-eに示す。

【0021】

実施例4

素子16(キャパシタ10、インダクタ6)の回路図を図2Bに示す。また、その周波数特性を図2B-a〜2B-eに示す。

【0022】

実施例5

素子14(キャパシタ8、インダクタ6)の回路図を図3Aに示す。また、その周波数特性を図3A-a〜3A-eに示す。

【0023】

実施例6

素子14(キャパシタ6、インダクタ8)の回路図を図3Bに示す。また、その周波数特性を図3B-a〜3B-eに示す。

【0024】

参考例

素子22(キャパシタ12、インダクタ12)の回路図を図4に示す。また、その周波数特性を図4-a〜4-eに示す。

【産業上の利用可能性】

【0025】

本発明のインピーダンス変換型集中定数ブランチラインカプラを用いた電力多分配回路、特に、集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを組み合わせた電力4分配回路は、携帯電話、衛星通信などの移動通信装置や固定の通信装置の外来電波入出力部において信号を分配する回路として利用できる。また、電力増幅回路やアンテナ等の給配電回路として利用できる。

【図面の簡単な説明】

【0026】

【図1A】素子18(キャパシタ6、インダクタ12)の回路図である。

【図1A−a】図1AのTerm1から入力した場合の反射・アイソレーション特性である。

【図1A−b】図1AのTerm1から入力した場合の分配特性である。

【図1A−c】図1AのTerm2から入力した場合の反射・アイソレーション特性である。

【図1A−d】図1AのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図1A−e】図1AのTerm1から入力した場合の位相特性である。

【0027】

【図1B】素子18(キャパシタ12、インダクタ6)の回路図である。

【図1B−a】図1BのTerm1から入力した場合の反射・アイソレーション特性である。

【図1B−b】図1BのTerm1から入力した場合の分配特性である。

【図1B−c】図1BのTerm2から入力した場合の反射・アイソレーション特性である。

【図1B−d】図1BのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図1B−e】図1BのTerm1から入力した場合の位相特性である。

【0028】

【図2A】素子16(キャパシタ6、インダクタ10)の回路図である。

【図2A−a】図2AのTerm1から入力した場合の反射・アイソレーション特性である。

【図2A−b】図2AのTerm1から入力した場合の分配特性である。

【図2A−c】図2AのTerm2から入力した場合の反射・アイソレーション特性である。

【図2A−d】図2AのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図2A−e】図2AのTerm1から入力した場合の位相特性である。

【0029】

【図2B】素子16(キャパシタ10、インダクタ6)の回路図である。

【図2B−a】図2BのTerm1から入力した場合の反射・アイソレーション特性である。

【図2B−b】図2BのTerm1から入力した場合の分配特性である。

【図2B−c】図2BのTerm2から入力した場合の反射・アイソレーション特性である。

【図2B−d】図2BのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図2B−e】図2BのTerm1から入力した場合の位相特性である。

【0030】

【図3A】素子14(キャパシタ8、インダクタ6)の回路図である。

【図3A−a】図3AのTerm1から入力した場合の反射・アイソレーション特性である。

【図3A−b】図3AのTerm1から入力した場合の分配特性である。

【図3A−c】図3AのTerm2から入力した場合の反射・アイソレーション特性である。

【図3A−d】図3AのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図3A−e】図3AのTerm1から入力した場合の位相特性である。

【0031】

【図3B】素子14(キャパシタ6、インダクタ8)の回路図である。

【図3B−a】図3BのTerm1から入力した場合の反射・アイソレーション特性である。

【図3B−b】図3BのTerm1から入力した場合の分配特性である。

【図3B−c】図3BのTerm2から入力した場合の反射・アイソレーション特性である。

【図3B−d】図3BのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。

【図3B−e】図3BのTerm1から入力した場合の位相特性である。

【0032】

【図4】素子22(キャパシタ12、インダクタ10)の回路図である。

【図4−a】図4のTerm1から入力した場合の反射・アイソレーション特性である。

【図4−b】図4のTerm1から入力した場合の分配特性である。

【図4−c】図4のTerm2から入力した場合の反射・アイソレーション特性である。

【図4−d】図4のTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図4−e】図4のTerm1から入力した場合の位相特性である。

【0033】

【図6.1】伝送線路型Case C(Case D)ブランチカプラである。

【図6.2】Case C(ブランチラインがλ0/4、スルーラインが3λ0/4)に等価変換を適用。 (a)は等価変換、(b)はシャント部分P1回路(P2回路)である。

【図6.3】Case D(ブランチラインが3λ0/4、スルーラインがλ0/4)に等価変換を適用。(a)は等価交換、(b)はシャント部分P1回路(P2回路)である。

【図6.4】素子数を低減させたインピーダンス変換型Case Cの回路である。

【図6.5】素子数を低減させたインピーダンス変換型Case Dの回路である。

【0034】

【図7.1】type C1 等価回路 cT=2、l1=1、lb1=1、lb2=0.5 素子数 C-6 L-12 計18素子

【図7.2】type C2 等価回路 cT=1、l1=2、lb1=1、lb2=2 素子数 C-6 L-10 計16素子

【図7.3】type D1 等価回路 cT=1、l1=1、lb1=2、lb2=0.5 素子数 C-12 L-6 計18素子

【図7.4】type D2 等価回路 cT=0.5、l1=1、lb1=0.5、lb2=1 素子数 C-10 L-6 計16素子

【技術分野】

【0001】

本発明は、インピーダンス変換型集中定数ブランチラインカプラを用いた電力多分配回路に関する。特に、集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを組み合わせた電力4分配回路に関する。

【背景技術】

【0002】

マイクロ波、ミリ波は通常数1GHzを越えるに非常に広い周波数範囲の電磁波で、携帯電話や衛星通信、テレビ放送、レーダーのほか、物性研究などの物理学の分野でも広く用いられており、さらに医学や天文学、またマイクロ波加熱、高エネルギー発生など、その利用範囲は極めて広い。

マイクロ波、ミリ波の信号を2方向に分配し、その2つの出力信号間に90度の位相差を与える回路として良く知られているものに分布定数ブランチラインカプラがある。この回路は構成要素である伝送線路の長さが波長の1/4であるため、回路サイズとして大型になりやすい。この解決法の1つとしてキャパシタやインダクタ等の集中定数素子を構成要素として取り入れる方法がある。これにより、基板上の回路占有面積を格段に小さくすることができる。この時、用いるキャパシタやインダクタ等の素子数は基本回路においては8個である。

一方、インピーダンス変換型集中定数90度ハイブリッドカプラに関し、キャパシタやインダクタ等の素子数が6個のものが知られている(非特許文献1)。また、ブランチラインカプラを用いた4分配回路において、標準型4分配回路とインピーダンス変換型4分配回路について周波数特性の比較がなされている(非特許文献2)。

【0003】

【非特許文献1】電子情報通信学会ソサイエティ大会講演論文集, p75 (2005)

【非特許文献2】電子情報通信学会技術研究報告, 107(394), 7-12(2007)

【発明の開示】

【発明が解決しようとする課題】

【0004】

ブランチラインカプラは90度の奇数倍の位相差を与えるマイクロ波、ミリ波回路素子の一つとして、信号分配・合成器、半導体電力増幅器、アレーアンテナ給電系、ミキサ、半導体移相器等、多種多様に用いられている。

本発明は、ブランチラインカプラを3個用いて構成される4分配回路について、その回路構成法の提案するものであり、更に集中定数化回路において、素子数の低減、更には特性の改善を目的とするものである。

【課題を解決するための手段】

【0005】

図6.1に示すλ/4伝送線路と3λ/4伝送線路の組み合わせを工夫し、図6.4、図6.5に示すようにキャパシタやインダクタ等の素子数を基本回路の8個から減らし6個としたインピーダンス変換型のブランチラインカプラを考案した。さらに、それらを用いて4分配回路構成を検討することで、通常22個の素子数を18〜14個と大幅に減らすことに成功し本発明を完成した。

以下、本発明を詳細に説明する。

【0006】

図6.1はλ/4伝送線路と3λ/4伝送線路の組み合わせの中で特にCase CまたはCase Dの場合を示しており、Guptaの回路モデルを前提としている。即ち、ポート#1およびポート#4には基準インピーダンスZ01、ポート#2およびポート#3には規格化負荷インピーダンスZ02が接続され、4本の伝送線路の規格化特性インピーダンスをzb1、zb2、zTとする。また、これらの逆数(アドミッタンス)をy02、yb1、yb2、yTとする。

この時、ポート1を入力端子とすると中心周波数において、条件式及び設計式は

【0007】

【数1】

【数2】

【数3】

となる。kは結合係数である。

【0008】

Case C(ブランチラインがλ0/4、スルーラインが3λ0/4)に等価変換を適用すると、図6.2が得られる。図6.2(b)はシャント部分を示す。

【0009】

Case Cの図6.2(a)のシリーズの素子値は

【数4】

となる。図6.2(b)のP1、P2の回路についてclを求めると

【0010】

【数5】

【数6】

となる。

【0011】

Case D(ブランチラインが3λ0/4、スルーラインがλ0/4)に等価変換を適用すると、図6.3が得られる。

【0012】

Case Dの図6.3(a)のシリーズの素子値は

【数7】

となる。図6.3(b)のについてclを求めると

【数8】

【数9】

となる。

【0013】

Case C、Case Dのどちらの場合でも積clによってP1、P2の回路は3通りに分類される。

C(容量性)の場合: cl > 1

シャント成分を除去できる場合: cl = 1

L(誘導性)の場合: cl > 1

【0014】

<Case C、Dにおけるcl=1の場合>

Case Cの式(6.5)においてcl=1とすると式(6.10)が、式(6.6)において

cl=1とすると式(6.11)が得られる。

【数10】

【数11】

同様に、Case Dの式(6.8)においてcl=1とすると式(6.12)が、式(6.9)においてcl=1とすると式(6.13)が得られる。

【数12】

【数13】

ここで、k>0であるから、式(6.10)、式(6.11)または、式(6.12)、式(6.13)は同時に成立しない。また、z02≠1である。このことは、シャント成分を除去することができるのはインピーダンス変換型の場合に限られ、P1回路か、P2回路のどちらか一方であることを意味している。

【0015】

これらのことより、cl=1となり、素子数を低減させたCase Cの回路を図6.4、に示す。同様に、cl=1となり、素子数を低減させたCase Dの回路を図6.5に示す。ここでは、均等分配(k=1)を仮定している。

【0016】

<インピーダンス変換型集中定数ブランチカップラ(Case C,Case D)を用いた4分配回路>

インピーダンス変換型Case C(図6.4)とインピーダンス変換型Case D(図6.5)を用いて、4分配回路を構成した。

インピーダンス変換型Case C(図6.4)を(a)−(b)とつないだ4分配回路をtype C1、(b)−(a)とつないだ4分配回路をtype C2として、図7.1、図7.2にその等価回路を示す。同様にインピーダンス変換型Case D(図6.5)を(a)−(b)とつないだ4分配回路をtype D1、(b)−(a)とつないだ4分配回路をtype D2として、図7.3、図7.4にその等価回路を示す。

【0017】

<発明の効果>

本発明の回路においては、ポートからの入力は無反射でアイソレーションがとれており、また出力ポートに信号が1/4ずつ均等分配される。

また、従来型の素子数を22個から18個以下に低減しても、分配特性、反射・アイソレーション特性は劣化しない。

【実施例】

【0018】

本発明を以下の実施例および参考例で説明するが本発明はそれらに限定されない。

実施例1

素子18(キャパシタ6、インダクタ12)の回路図を図1Aに示す。また、その周波数特性を図1A-a〜1A-eに示す。

【0019】

実施例2

素子18(キャパシタ12、インダクタ6)の回路図を図1Bに示す。また、その周波数特性を図1B-a〜1B-eに示す。

【0020】

実施例3

素子16(キャパシタ6、インダクタ10)の回路図を図2Aに示す。また、その周波数特性を図2A-a〜2A-eに示す。

【0021】

実施例4

素子16(キャパシタ10、インダクタ6)の回路図を図2Bに示す。また、その周波数特性を図2B-a〜2B-eに示す。

【0022】

実施例5

素子14(キャパシタ8、インダクタ6)の回路図を図3Aに示す。また、その周波数特性を図3A-a〜3A-eに示す。

【0023】

実施例6

素子14(キャパシタ6、インダクタ8)の回路図を図3Bに示す。また、その周波数特性を図3B-a〜3B-eに示す。

【0024】

参考例

素子22(キャパシタ12、インダクタ12)の回路図を図4に示す。また、その周波数特性を図4-a〜4-eに示す。

【産業上の利用可能性】

【0025】

本発明のインピーダンス変換型集中定数ブランチラインカプラを用いた電力多分配回路、特に、集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを組み合わせた電力4分配回路は、携帯電話、衛星通信などの移動通信装置や固定の通信装置の外来電波入出力部において信号を分配する回路として利用できる。また、電力増幅回路やアンテナ等の給配電回路として利用できる。

【図面の簡単な説明】

【0026】

【図1A】素子18(キャパシタ6、インダクタ12)の回路図である。

【図1A−a】図1AのTerm1から入力した場合の反射・アイソレーション特性である。

【図1A−b】図1AのTerm1から入力した場合の分配特性である。

【図1A−c】図1AのTerm2から入力した場合の反射・アイソレーション特性である。

【図1A−d】図1AのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図1A−e】図1AのTerm1から入力した場合の位相特性である。

【0027】

【図1B】素子18(キャパシタ12、インダクタ6)の回路図である。

【図1B−a】図1BのTerm1から入力した場合の反射・アイソレーション特性である。

【図1B−b】図1BのTerm1から入力した場合の分配特性である。

【図1B−c】図1BのTerm2から入力した場合の反射・アイソレーション特性である。

【図1B−d】図1BのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図1B−e】図1BのTerm1から入力した場合の位相特性である。

【0028】

【図2A】素子16(キャパシタ6、インダクタ10)の回路図である。

【図2A−a】図2AのTerm1から入力した場合の反射・アイソレーション特性である。

【図2A−b】図2AのTerm1から入力した場合の分配特性である。

【図2A−c】図2AのTerm2から入力した場合の反射・アイソレーション特性である。

【図2A−d】図2AのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図2A−e】図2AのTerm1から入力した場合の位相特性である。

【0029】

【図2B】素子16(キャパシタ10、インダクタ6)の回路図である。

【図2B−a】図2BのTerm1から入力した場合の反射・アイソレーション特性である。

【図2B−b】図2BのTerm1から入力した場合の分配特性である。

【図2B−c】図2BのTerm2から入力した場合の反射・アイソレーション特性である。

【図2B−d】図2BのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図2B−e】図2BのTerm1から入力した場合の位相特性である。

【0030】

【図3A】素子14(キャパシタ8、インダクタ6)の回路図である。

【図3A−a】図3AのTerm1から入力した場合の反射・アイソレーション特性である。

【図3A−b】図3AのTerm1から入力した場合の分配特性である。

【図3A−c】図3AのTerm2から入力した場合の反射・アイソレーション特性である。

【図3A−d】図3AのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図3A−e】図3AのTerm1から入力した場合の位相特性である。

【0031】

【図3B】素子14(キャパシタ6、インダクタ8)の回路図である。

【図3B−a】図3BのTerm1から入力した場合の反射・アイソレーション特性である。

【図3B−b】図3BのTerm1から入力した場合の分配特性である。

【図3B−c】図3BのTerm2から入力した場合の反射・アイソレーション特性である。

【図3B−d】図3BのTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。

【図3B−e】図3BのTerm1から入力した場合の位相特性である。

【0032】

【図4】素子22(キャパシタ12、インダクタ10)の回路図である。

【図4−a】図4のTerm1から入力した場合の反射・アイソレーション特性である。

【図4−b】図4のTerm1から入力した場合の分配特性である。

【図4−c】図4のTerm2から入力した場合の反射・アイソレーション特性である。

【図4−d】図4のTerm2から入力した場合の分配特性、Term3から入力した場合の反射・アイソレーション特性である。である。

【図4−e】図4のTerm1から入力した場合の位相特性である。

【0033】

【図6.1】伝送線路型Case C(Case D)ブランチカプラである。

【図6.2】Case C(ブランチラインがλ0/4、スルーラインが3λ0/4)に等価変換を適用。 (a)は等価変換、(b)はシャント部分P1回路(P2回路)である。

【図6.3】Case D(ブランチラインが3λ0/4、スルーラインがλ0/4)に等価変換を適用。(a)は等価交換、(b)はシャント部分P1回路(P2回路)である。

【図6.4】素子数を低減させたインピーダンス変換型Case Cの回路である。

【図6.5】素子数を低減させたインピーダンス変換型Case Dの回路である。

【0034】

【図7.1】type C1 等価回路 cT=2、l1=1、lb1=1、lb2=0.5 素子数 C-6 L-12 計18素子

【図7.2】type C2 等価回路 cT=1、l1=2、lb1=1、lb2=2 素子数 C-6 L-10 計16素子

【図7.3】type D1 等価回路 cT=1、l1=1、lb1=2、lb2=0.5 素子数 C-12 L-6 計18素子

【図7.4】type D2 等価回路 cT=0.5、l1=1、lb1=0.5、lb2=1 素子数 C-10 L-6 計16素子

【特許請求の範囲】

【請求項1】

集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを用いた電力多分配回路。

【請求項2】

集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを3個組み合わせた請求項1に記載の電力多分配回路。

【請求項3】

電力多分配器の素子数が18個以下である請求項1または2に記載の電力多分配回路。

【請求項4】

集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラが、回路の入力ポート及びアイソレーションポートに規格化基準アドミッタンスy0=1が接続されており、出力端子である直接ポート及び結合ポート側に規格化アドミッタンスy02が接続されているインピーダンス変換型集中定数90度ハイブリッドカプラである請求項1〜3に記載の電力多分配回路。

【請求項5】

インピーダンス変換型集中定数90度ハイブリッドカプラにおいて、y02が均等信号電力配分では、y02=2またはy02=1/2、信号電力配分では、y02=3またはy02=1/3である請求項4に記載の電力多分配回路。

【請求項1】

集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを用いた電力多分配回路。

【請求項2】

集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラを3個組み合わせた請求項1に記載の電力多分配回路。

【請求項3】

電力多分配器の素子数が18個以下である請求項1または2に記載の電力多分配回路。

【請求項4】

集中定数素子の素子数6のインピーダンス変換型集中定数ブランチラインカプラが、回路の入力ポート及びアイソレーションポートに規格化基準アドミッタンスy0=1が接続されており、出力端子である直接ポート及び結合ポート側に規格化アドミッタンスy02が接続されているインピーダンス変換型集中定数90度ハイブリッドカプラである請求項1〜3に記載の電力多分配回路。

【請求項5】

インピーダンス変換型集中定数90度ハイブリッドカプラにおいて、y02が均等信号電力配分では、y02=2またはy02=1/2、信号電力配分では、y02=3またはy02=1/3である請求項4に記載の電力多分配回路。

【図1A】

【図1B】

【図2A】

【図2B】

【図3A】

【図3B】

【図4】

【図6.1】

【図6.2】

【図6.3】

【図6.4】

【図6.5】

【図7.1】

【図7.2】

【図7.3】

【図7.4】

【図1A−a】

【図1A−b】

【図1A−c】

【図1A−d】

【図1A−e】

【図1B−a】

【図1B−b】

【図1B−c】

【図1B−d】

【図1B−e】

【図2A−a】

【図2A−b】

【図2A−c】

【図2A−d】

【図2A−e】

【図2B−a】

【図2B−b】

【図2B−c】

【図2B−d】

【図2B−e】

【図3A−a】

【図3A−b】

【図3A−c】

【図3A−d】

【図3A−e】

【図3B−a】

【図3B−b】

【図3B−c】

【図3B−d】

【図3B−e】

【図4−a】

【図4−b】

【図4−c】

【図4−d】

【図4−e】

【図1B】

【図2A】

【図2B】

【図3A】

【図3B】

【図4】

【図6.1】

【図6.2】

【図6.3】

【図6.4】

【図6.5】

【図7.1】

【図7.2】

【図7.3】

【図7.4】

【図1A−a】

【図1A−b】

【図1A−c】

【図1A−d】

【図1A−e】

【図1B−a】

【図1B−b】

【図1B−c】

【図1B−d】

【図1B−e】

【図2A−a】

【図2A−b】

【図2A−c】

【図2A−d】

【図2A−e】

【図2B−a】

【図2B−b】

【図2B−c】

【図2B−d】

【図2B−e】

【図3A−a】

【図3A−b】

【図3A−c】

【図3A−d】

【図3A−e】

【図3B−a】

【図3B−b】

【図3B−c】

【図3B−d】

【図3B−e】

【図4−a】

【図4−b】

【図4−c】

【図4−d】

【図4−e】

【公開番号】特開2009−194587(P2009−194587A)

【公開日】平成21年8月27日(2009.8.27)

【国際特許分類】

【出願番号】特願2008−32650(P2008−32650)

【出願日】平成20年2月14日(2008.2.14)

【出願人】(305060567)国立大学法人富山大学 (194)

【公開日】平成21年8月27日(2009.8.27)

【国際特許分類】

【出願日】平成20年2月14日(2008.2.14)

【出願人】(305060567)国立大学法人富山大学 (194)

[ Back to top ]