ウェアレベル制御ロジックを含むメモリシステム

【課題】不揮発性メモリのバッファ領域のウェアレベルを緩和するメモリシステムが提供される。

【解決手段】本発明によるメモリシステムは使用者領域とバッファ領域を有する不揮発性メモリと、前記不揮発性メモリのウェアレベル情報に基づいて、前記使用者領域の一部ブロックを前記バッファ領域に転換する動作を管理するためのウェアレベル制御ロジックと、を含む。前記ウェアレベル情報は前記使用者領域のプログラム−消去サイクル情報、ECCエラー率情報、又は消去ループ回数情報であり得る。本発明によると、バッファ領域のP/Eサイクル耐久性(endurance)を増加するか、或いはECCエラー率や消去ループ回数の増加率を減らすことによって、メモリシステムの性能を向上させ得る。

【解決手段】本発明によるメモリシステムは使用者領域とバッファ領域を有する不揮発性メモリと、前記不揮発性メモリのウェアレベル情報に基づいて、前記使用者領域の一部ブロックを前記バッファ領域に転換する動作を管理するためのウェアレベル制御ロジックと、を含む。前記ウェアレベル情報は前記使用者領域のプログラム−消去サイクル情報、ECCエラー率情報、又は消去ループ回数情報であり得る。本発明によると、バッファ領域のP/Eサイクル耐久性(endurance)を増加するか、或いはECCエラー率や消去ループ回数の増加率を減らすことによって、メモリシステムの性能を向上させ得る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体メモリ装置に関し、さらに具体的には不揮発性メモリに基づくメモリシステム、及びそのモード転換動作に関する。

【背景技術】

【0002】

半導体メモリ装置は一般的にDRAM、SRAM等のような揮発性メモリ装置とEEPROM、FRAM(登録商標)、PRAM、MRAM、フラッシュメモリ等のような不揮発性メモリ装置とに区分することができる。揮発性メモリ装置は電源が遮断される時、格納したデータを失うが、不揮発性メモリは電源が遮断されでも格納したデータを保存する。特に、フラッシュメモリは速い読出し速度、低い電力消費、大容量データ格納等の長所を有する。このようなことから、フラッシュメモリを含むメモリシステムはデータ保存媒体として広く使われている。

不揮発性メモリを含むメモリシステムはファイルデータを効率的に管理し、システムの性能を向上するために、データを使用者領域(user area)に格納する前にバッファ領域に格納する。このようなプログラム方式によれば、マージ動作(merge operation)やブロック消去(block erase)回数等を減らし得る。そして、メモリコントローラ内のSRAMバッファの使用量を減らすことができる長所がある。

しかし、このようなプログラム方式はバッファ領域に格納するファイルデータのサイズが大きくなることから、バッファ領域の空間が不足する可能性があり、バッファ領域と使用者領域との間のファイルデータの移動が頻繁に発生してメモリシステムの性能が低下し得る。また、全てプログラム動作の時にバッファ領域を使用するので、バッファ領域のウェアレベル(wear level)が使用者領域に比べて速く増加する問題点がある。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許出願公開第2006−0152981号明細書

【特許文献2】韓国特許出願公開第10−2008−0069822号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の目的は不揮発性メモリのバッファ領域のウェアレベルを緩和するメモリシステムを提供することにある。

【課題を解決するための手段】

【0005】

本発明の実施形態によるメモリシステムは使用者領域とバッファ領域とを有する不揮発性メモリと、前記不揮発性メモリのウェアレベル情報に基づいて、前記使用者領域の一部ブロックを前記バッファ領域に転換する動作(以下、‘モード転換動作’と称する)を管理するためのウェアレベル制御ロジックと、を含む。

【0006】

実施形態として、前記使用者領域にはメモリセル当たりN(Nは2以上である自然数)ビットデータが格納され、前記バッファ領域にはメモリセル当たりM(MはNより小さい自然数)ビットデータが格納される。前記バッファ領域にはシングルビットデータが格納され得る。不揮発性メモリは外部から入力されたデータを前記バッファ領域に格納した次に、前記バッファ領域に格納されたデータを前記使用者領域へ移動する。

【0007】

他の実施形態として、前記ウェアレベル情報は前記使用者領域のプログラム−消去サイクル情報であり得る。前記ウェアレベル制御ロジックは前記プログラム−消去サイクル情報にしたがって、段階的にモード転換動作を遂行できる。

【0008】

その他の実施形態として、前記ウェアレベル情報はECCエラー率情報であり得る。前記ウェアレベル制御ロジックは前記ECCエラー率情報にしたがって、段階的にモード転換動作を遂行できる。

【0009】

その他の実施形態として、前記ウェアレベル情報は消去ループ回数情報であり得る。前記ウェアレベル制御ロジックは前記消去ループ回数情報にしたがって、段階的にモード転換動作を遂行できる。

【発明の効果】

【0010】

本発明によるメモリシステムはウェアレベル情報(例えば、プログラム−消去サイクル、ECCエラー率、消去ループ回数等)に基づいて、使用者領域の一部メモリブロックを段階的にバッファ領域にモード転換を遂行できる。本発明によると、バッファ領域のP/Eサイクル耐久性(endurance)を増加するか、或いはECCエラー率や消去ループ回数の増加率を減らすことによって、メモリシステムの性能を向上させることができる。

【図面の簡単な説明】

【0011】

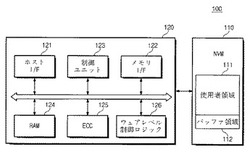

【図1】本発明によるメモリシステムを概略的に示すブロック図である。

【図2】プログラム−消去サイクルに基づいてモード転換動作を説明するためのブロック図である。

【図3】図2に図示されたメモリシステムのプログラム−消去サイクルにしたがう使用者領域及びバッファ領域の耐久性を示す表である。

【図4A】図2に図示されたメモリシステムのプログラム−消去サイクルにしたがうモード変換動作を説明するための概念図である。

【図4B】図2に図示されたメモリシステムのプログラム−消去サイクルにしたがうモード変換動作を説明するための概念図である。

【図5】図2に図示されたメモリシステムのモード転換動作を遂行するためのマッピングテーブルを例示的に示す表である。

【図6】ECCエラー率に基づいたモード転換動作を説明するためのブロック図である。

【図7A】図6に図示されたメモリシステムのECCエラー率にしたがうモード変換動作を説明するための概念図である。

【図7B】図6に図示されたメモリシステムのECCエラー率にしたがうモード変換動作を説明するための概念図である。

【図8】消去ループ回数に基づいたモード転換動作を説明するためのブロック図である。

【図9】図8に図示された消去ループカウンターを説明するためのダイヤグラムである。

【図10A】図8に図示されたメモリシステムの消去ループ回数にしたがうモード変換動作を説明するための概念図である。

【図10B】図8に図示されたメモリシステムの消去ループ回数にしたがうモード変換動作を説明するための概念図である。

【図11】本発明によるメモリシステムの多様な適用例を示すブロック図である。

【図12】本発明によるメモリシステムの多様な適用例を示すブロック図である。

【図13】本発明の実施形態によるメモリシステムをメモリカードシステムに適用した例を示すブロック図である。

【図14】本発明の実施形態によるメモリシステムをソリッドステートドライブ(SSD)システムに適用した例を示すブロック図である。

【図15】図14に図示されたSSDコントローラの構成を例示的に示すブロック図である。

【図16】本発明の実施形態によるメモリシステムを電子装置で具現された例を示すブロック図である。

【図17】本発明に使用されるフラッシュメモリを例示的に示すブロック図である。

【図18】図17に図示されたメモリブロックBLK1の3次元構造を例示的に示す斜視図である。

【図19】図18に図示されたメモリブロックBLK1の等価回路図である。

【発明を実施するための形態】

【0012】

以下で、本発明が属する技術分野で通常の知識を有する者が本発明の技術的思想を容易に実施できる程度、詳細に説明するために、本発明の実施形態を添付された図面を参照して説明する。

【0013】

図1は本発明によるメモリシステムを概略的に示すブロック図である。図1を参照すれば、本発明によるメモリシステム100は不揮発性メモリ(NVM、110)及びメモリコントローラ120を含む。

【0014】

不揮発性メモリ110はメモリコントローラ120によって制御され、メモリコントローラ120の要請に対応する動作(例えば、読出し又は書込み動作等)を遂行できる。不揮発性メモリ110は使用者領域111とバッファ領域112とを含む。使用者領域111は低速動作を遂行するメモリ(以下、低速不揮発性メモリ)で具現され、バッファ領域112は高速動作を遂行するメモリ(以下、高速不揮発性メモリ)で具現され得る。

【0015】

高速不揮発性メモリは高速動作に適合であり、低速不揮発性メモリは低速動作に適合なマッピングスキームを使用するように構成され得る。例えば、低速不揮発性メモリを構成する使用者領域111はブロックマッピングスキームを通じて管理され、高速不揮発性メモリを構成するバッファ領域112はページマッピングスキームを通じて管理され得る。ページマッピングスキームは動作性能(例えば、書込み性能)の低下を発生させるマージ動作を必要としないので、バッファ領域112は高速に動作できる。反面に、ブロックマッピングスキームは動作性能(例えば、書込み性能)の低下を発生させるマージ動作を必要とするので、使用者領域111は相対的に低速に動作する。

【0016】

一方、バッファ領域112はセル当たり1−ビットデータを格納する単一レベルセルフラッシュメモリ(SLC flash memory)で構成され、使用者領域111はセル当たりN−ビットデータNは2又はそれより大きい整数)を格納するマルチ−レベルセルフラッシュメモリ(MLC flash memory)で構成され得る。又は、使用者及びバッファ領域111、112の各々はマルチ−レベルフラッシュメモリで構成され得る。例えば、使用者領域111はセル当たりN−ビットデータを格納し、バッファ領域112はセル当たりM−ビットデータを格納できる。ここで、MはNより小さい自然数である。一方、使用者領域111とバッファ領域112とは1つのメモリ装置で具現されるか、或いは別のメモリ装置で具現されることもあり得る。

【0017】

メモリコントローラ120は外部(例えば、ホスト)の要請に応答して不揮発性メモリ110に対する読出し及び書込み動作を制御する。メモリコントローラ120はホストインターフェイス121、メモリインターフェイス122、制御ユニット123、RAM124、ECC回路125、及びウェアレベル制御ロジック(Wear Level Control Logic)126を含む。

【0018】

ホストインターフェイス121は外部(例えば、ホスト)とのインターフェイスを提供し、メモリインターフェイス122は不揮発性メモリ110とのインターフェイスを提供する。ホストインターフェイス121は1つ又はそれより多いチャンネル(又は、ポート)(図示せず)を通じてホスト(図示せず)に連結され得る。例えば、ホストインターフェイス121はPATAバス(parallel AT attachment bus)とSATAバス(serial AT attachment)との中でいずれか1つ又はこれら全てを通じてホストと連結され得る。又は、ホストインターフェイス121はSCSI、USB等を通じて外部に連結されることもあり得る。

【0019】

制御ユニット123は不揮発性メモリ110に対する全般的な動作(例えば、読出し、書込み、ファイルシステム管理等)を制御することができる。例えば、たとえ図面には図示していないが、制御ユニット123は中央処理装置(CPU)、プロセッサー(processor)、SRAM、DMA制御器等を含むことができる。例示的な制御ユニット123は特許文献1に開示され、本出願の参照として包含される。

【0020】

制御ユニット123は不揮発性メモリ110のバッファ領域112に格納されたデータを使用者領域111へ移す動作を管理することができる。ここで、バッファ領域112に格納されたデータはフラッシュ動作によってRAM124でダンプされたデータであってよく、ホストの書込み要請によって外部から提供されたデータであってもよい。

【0021】

バッファ領域112で使用者領域111へデータを移す動作は多様な方式を通じて遂行できる。例えば、バッファ領域112の余裕空間が予め設定された空間(例えば、30%)以下であるか否かにしたがって開始され得る。他の例として、決められた時間毎に周期的に開始されてもよい。その他の例として、不揮発性メモリ110のアイドル時間(idle time)を感知することによって開始されることもあり得る。

【0022】

RAM124は制御ユニット123の制御にしたがって動作し、ワークメモリ(work memory)、バッファメモリ(buffer memory)、キャッシュメモリ(cache memory)等として使用され得る。RAM124は1つのチップで構成されるか、或いは不揮発性メモリ110の各領域に対応する複数のチップで構成され得る。

【0023】

RAM124がワークメモリとして使用される場合に、制御ユニット123によって処理されるデータが臨時格納される。RAM124がバッファメモリとして使用される場合には、ホストから不揮発性メモリ110へ又は不揮発性メモリ110からホストへ伝送されるデータをバッファリングするのに使用される。RAM124がキャッシュメモリとして使用される場合(以下、キャッシュスキームと称する)に、RAM124は低速の不揮発性メモリ110が高速に動作するようにする。キャッシュスキームによれば、キャッシュメモリ(RAM、124)に格納されたファイルデータが不揮発性メモリ110のバッファ領域112にダンプ(dump)される。制御ユニット123はダンプ動作にしたがうマッピングテーブル(mapping table)を管理することができる。

【0024】

RAM124は不揮発性メモリ110がフラッシュメモリである場合にフラッシュ変換階層FTLを駆動するための駆動メモリとして使用され得る。フラッシュ変換階層FTLはフラッシュメモリのマージ動作(merge operation)やマッピングテーブル(mapping table)等を管理するのに使用される。

【0025】

一方、ホスト(図示せず)は書込み(write)、読出し(read)の以外にフラッシュキャッシュ(flush cache)のようなコマンドをメモリシステム100へ提供する。メモリシステム100はフラッシュキャッシュコマンドを受信する時、データ一貫性(data consistency)を維持するために、キャッシュメモリ124に格納されているファイルデータを不揮発性メモリ110のバッファ領域112に格納する。このような一連の動作をフラッシュ動作(flush operation)と称する。制御ユニット123はフラッシュ動作の時にキャッシュメモリ124のファイルデータを不揮発性メモリ110のバッファ領域112にダンプする動作を管理することができる。

【0026】

ECC回路125は不揮発性メモリ110から受信したデータのエラービットを訂正するためのエラー訂正コードECCを生成する。ECC回路125は不揮発性メモリ110に提供されるデータのエラー訂正エンコーディングを遂行して、パリティー(parity)ビットが付加されたデータを形成する。パリティービットは不揮発性メモリ110に格納され得る。また、ECC回路125は出力されたデータに対してエラー訂正デコーディングを遂行し、遂行結果にしたがってエラー訂正デコーディングの成功の可否を判断することができる。ECC回路125は判断結果にしたがって指示信号を出力し、パリティービットを使用してデータのエラービットを訂正できる。

【0027】

ECC回路125はLDPC(low density parity check) code、BCH code、turbo code、リードソロモンコード(Reed−Solomon code)、convolution code、RSC(recursive systematic code)、TCM(trellis−coded modulation)、BCM(Block coded modulation)等の符号化変調(coded modulation)を使用してエラーを訂正することができる。ECC回路125はエラーを訂正するための回路、システム又は装置を全て含むことができる。

【0028】

ウェアレベル制御ロジック126は不揮発性メモリ110のウェアレベル(wear level)に基づいて、使用者領域111の一部ブロックをバッファ領域112に転換する動作を管理することができる。このような動作をモード転換動作(mode change operation)と称する。ウェアレベル制御ロジック126は不揮発性メモリ110のウェアレベルが一定のレベルに到達する時、使用者領域111の1つ又はその以上のメモリブロックをMLCモードからSLCモードに転換する動作を管理することができる。

【0029】

ウェアレベル制御ロジック126はハードウェアやソフトウェアで具現され得る。即ち、ウェアレベル制御ロジック126はメモリコントローラ120内に1つのチップやモジュールで設置されるか、或いはフロッピー(登録商標)ディスクやコンパクトディスク又はUSB等のような外装メモリを通じて連結されることもあり得る。一方、ウェアレベル制御ロジック126は使用者によってプログラムできる形態で具現されることもあり得る。

【0030】

不揮発性メモリ110のウェアレベルはプログラム−消去サイクル(P/Eサイクル)、ECCエラー率、又は消去ループ回数等のようなパラメーター(以下、ウェアレベルパラメーターと称する)を通じて知ることができる。不揮発性メモリ110は一般的にP/Eサイクル、ECCエラー率、消去ループ回数が増加するほど、ウェアレベル(wear level)が増加する。以下では、ウェアレベルパラメーターに基づいたメモリシステム100のモード転換動作が詳細に説明される。

【0031】

図2はプログラム−消去サイクルに基づいてモード転換動作を説明するためのブロック図である。図2を参照すれば、メモリシステム200は不揮発性メモリ210及びメモリコントローラ220を含む。不揮発性メモリ210は使用者領域211及びバッファ領域212を含む。使用者領域211はメモリセル当たり2ビット以上を格納するMLC領域にモード設定され、バッファ領域212はシングルビットを格納するSLC領域にモード設定されている。

【0032】

不揮発性メモリ210はプログラム−消去動作を反複して遂行できる許容限度が定まっている。これをP/Eサイクル耐久性(endurance)と称する。P/Eサイクル耐久性はメモリセル当たり格納するデータビット数にしたがって異なり得る。一般的にセル当たり格納するデータビット数が小さいほど、P/Eサイクル耐久性は増加する。

【0033】

一方、使用者領域211にプログラムされる全てのデータは先にバッファ領域212に格納される。その次にバッファ領域212で使用者領域211へデータを移す動作が遂行される。このようなプログラム方式をOBP(On−chip Buffered Program)と称する。OBP方式によれば、バッファ領域212に対するプログラム−消去動作が反復的に遂行されるので、バッファ領域212のP/Eサイクル耐久性が良くなければならない。図2に図示されたメモリシステム200は使用者領域211の一部をバッファ領域212へモード転換することによって、バッファ領域212のP/Eサイクル耐久性を増加することができる。

【0034】

続いて、図2を参照すれば、メモリコントローラ220は制御ユニット223及びウェアレベル制御ロジック226を含む。制御ユニット223は不揮発性メモリ210のプログラム−消去サイクルP/Eに関する情報をウェアレベル制御ロジック226へ提供する。ウェアレベル制御ロジック226はP/E情報に基づいて、使用者領域211の一部メモリブロックに対するモード転換動作(mode change operation)を遂行する。

【0035】

例えば、不揮発性メモリ210は100個のメモリブロックで構成され、使用者領域211は98個の3ビットMLCメモリブロックで構成され、バッファ領域212は2個のSLCメモリブロックで構成されていると仮定する。ウェアレベル制御ロジック226はP/Eサイクルが予め決められた回数に到達する時、使用者領域211の一部MLCメモリブロックをSLCメモリブロックに転換する。

【0036】

図3は図2に図示されたメモリシステムのプログラム−消去サイクルにしたがう使用者領域及びバッファ領域の耐久性を示す表である。図3は、SLCバッファ領域(図2参照、212)は2%であり、3ビットMLC使用者領域(図2参照、211)は98%であると仮定する。また、図3はMLC使用者領域211にプログラムされる全てデータは先にSLCバッファ領域212に格納されると仮定する。

【0037】

図3を参照すれば、MLC使用者領域211の耐久性(MLC[E])が0.5K、1.0K、1.5Kである時、SLCバッファ領域212の耐久性(SLC[E])は各々75K、150K、225Kである。MLC使用者領域211のP/Eサイクルを1000回保障するためには、不揮発性メモリ(図2参照、200)はSLCバッファ領域(図2参照、212)のP/Eサイクルを150、000回を保障しなければならない。SLCバッファ領域212及びMLC使用者領域211の耐久性の相関関係は数式1のように表現できる。

【0038】

[数式1]

SLC[E]=MLC[E]×3×(MLCブロック数/SLCブロック数)

【0039】

SLCバッファ領域の耐久性(SLC[E])はMLC使用者領域の耐久性(MLC[E])が増加するほど、増加し、SLCバッファ領域のブロック数が多くほど、減少する。SLCバッファ領域212の耐久性はMLC使用者領域211の耐久性より10倍以上大きい。これはMLC使用者領域211として使用した一部メモリブロックをSLCバッファ領域212へモードを転換しても90%以上の耐久性をそのまま使用することを意味する。

【0040】

図4A及び図4Bは図2に図示されたメモリシステムのプログラム−消去サイクルにしたがうモード変換動作を説明するための概念図である。図4Aは不揮発性メモリ(図2参照、210のMLC使用者領域(図2参照、211)のP/Eサイクル使用パーセント(%)にしたがうモード転換動作を示し、図4BはSLCバッファ領域212のP/Eサイクル使用パーセント(%)にしたがうモード転換動作を示す。

【0041】

図4Aを参照すれば、MLC使用者領域211のP/Eサイクル初期(0%)に、MLC使用者領域211は98%であり、SLCバッファ領域212は2%である。即ち、不揮発性メモリ210は全体100個のメモリブロックの中で98個のメモリブロックを使用者領域として使用し、2個のメモリブロックをバッファ領域として使用されている。

【0042】

MLC使用者領域211のP/Eサイクルが25%遂行された場合に、MLC使用者領域211の一部メモリブロック(例えば、2個のメモリブロック)はSLCバッファ領域212に転換される。

【0043】

例えば、MLC使用者領域211のP/Eサイクル耐久性が1000回であるとすれば、P/Eサイクルが250回遂行される時、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理されてバッドブロック(bad block)になる。上の例で、SLCバッファ領域212に転換されたメモリブロックは100K以上のP/Eサイクルに該当する耐久性を有することができる(図3参照)。

【0044】

MLC使用者領域211のP/Eサイクルが50%遂行された場合に、MLC使用者領域211の他の一部メモリブロックがSLCバッファ領域212に転換される。上の例で、P/Eサイクルが500回遂行される時、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理される。この時、MLC使用者領域211のメモリブロックは94個である。

【0045】

同様に、MLC使用者領域211のP/Eサイクルが75%遂行された場合に、MLC使用者領域211のその他の一部メモリブロックがSLCバッファ領域212に転換される。上の例で、P/Eサイクルが750回遂行される時、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理される。この時、MLC使用者領域211のメモリブロックは92個である。

【0046】

図4Bを参照すれば、SLC使用者領域212のP/Eサイクル初期(0%)で、不揮発性メモリ210は全体100個のメモリブロックの中で98個のメモリブロックを使用者領域として使用し、2個のメモリブロックをバッファ領域として使用している。

【0047】

SLCバッファ領域212のP/Eサイクルが70%遂行された場合に、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。この時、SLCバッファ領域212は4個のメモリブロックを有する。新しくSLCバッファ領域に転換されたメモリブロックは既存のSLCバッファ領域212のメモリブロックより多いP/Eサイクルを有することができる。全体的にSLCバッファ領域212のP/Eサイクル耐久性は増える。

【0048】

SLCバッファ領域212のP/Eサイクルが80%遂行された場合に、MLC使用者領域211の他の一部メモリブロックがSLCバッファ領域212に転換される。この時、最初からSLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理され得る。この時、MLC使用者領域211のメモリブロックは94個である。

【0049】

同様に、SLCバッファ領域212のP/Eサイクルが90%遂行された場合に、MLC使用者領域211のその他の一部メモリブロックがSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用された4個のメモリブロックはウェアアウト(wear−out)として処理され得る。この時、MLC使用者領域211のメモリブロックは92個である。

【0050】

図4A及び図4BはP/Eサイクルにしたがって4段階に分かられて使用者領域211をバッファ領域212に転換する例を示す。使用者領域211は初期に98%の使用量を有し、徐々に減って最終的に92%の使用量を有する。しかし、使用者領域211の空間が減る代わりに、バッファ領域212のP/Eサイクル耐久性は大きく増大されて、全体的にメモリシステム200の性能は大きく向上され得る。

【0051】

図5は図2に図示されたメモリシステムのモード転換動作を遂行するためのマッピングテーブルを例示的に示す。図5に図示されたマッピングテーブルはMLC使用者領域(図2参照、211)のP/Eサイクルが25%遂行された場合を示す。

【0052】

図5を参照すれば、不揮発性メモリ(図2参照、210)は100個のメモリブロック001〜100を有する。第1及び第2メモリブロック001、002はP/Eサイクル初期にSLCモード、即ちSLCバッファ領域(図2参照、212)に割当されている。第3乃至第100メモリブロック003〜100はMLCモード、即ちMLC使用者領域211に割当されている。MLC使用者領域211のP/Eサイクルが25%遂行されれば、第1及び第2メモリブロック001、002はウェア−アウトされ、第3及び第4メモリブロック003、004はSLCモードに転換される。即ち、第3及び第4メモリブロック003、004はSLCバッファ領域212にモード転換される。

【0053】

再び図2を参照すれば、本発明の実施形態によるメモリシステム200はプログラム−消去サイクル(P/E cycle)情報に基づいて、使用者領域211の一部メモリブロックを段階的にバッファ領域212にモード転換を遂行できる。本発明によると、バッファ領域212のP/Eサイクル耐久性が良くなることによって、メモリシステム200の性能が向上され得る。

【0054】

図6はECCエラー率に基づいたモード転換動作を説明するためのブロック図である。図6を参照すれば、メモリシステム300は不揮発性メモリ310及びメモリコントローラ320を含む。不揮発性メモリ310は使用者領域311及びバッファ領域312を含み、メモリコントローラ320はECC回路325及びウェアレベル制御ロジック326を含む。

【0055】

不揮発性メモリ310を使用する分だけ、ECCエラー率は増加する。ECC回路325はエラーを訂正できる最大ビット数が定まっている。OBP方式によれば、バッファ領域312に対するプログラムや読出し動作が反復的に遂行されるので、使用者領域311よりバッファ領域312のECCエラー率がさらに速い速度で増加する。図6に図示されたメモリシステム300は使用者領域311の一部をバッファ領域312にモード転換することによって、バッファ領域312のECCエラー増加率を減らすことができる。

【0056】

続いて、図6を参照すれば、ECC回路325は不揮発性メモリ310のECCエラー率(error rate)に関する情報をウェアレベル制御ロジック326へ提供する。ウェアレベル制御ロジック326はECCエラー率に基づいて、使用者領域311の一部メモリブロックに対するモード転換動作を遂行する。例えば、ウェアレベル制御ロジック326はECCエラー率が予め決められたエラー率に到達する時、使用者領域311の一部メモリブロックをバッファ領域312に転換する。

【0057】

図7A及び図7Bは図6に図示されたメモリシステムのECCエラー率にしたがうモード変換動作を説明するための概念図である。図7AはMLC使用者領域のECCエラー率にしたがうモード変換動作を示し、図7BはSLCバッファ領域のECCエラー率にしたがう全て変換動作を示す。図7A及び図7Bでは説明を簡単にするため、ECC回路(図6参照、325)の訂正可能であるECCエラービットは100であることと仮定する。

【0058】

図7Aを参照すれば、MLC使用者領域311のECCエラー率が0%〜10%である区間で、MLC使用者領域311は99個のメモリブロックを有し、SLCバッファ領域は1個のメモリブロックを有すると仮定する。ECCエラー率が10%〜20%である場合に、MLC使用者領域311の一部メモリブロック(例えば、1つのメモリブロック)はSLCバッファ領域312に転換される。そして、SLCバッファ領域312として使用されたメモリブロックはウェアアウト(wear−out)として処理される。この時、MLC使用者領域311は98個のメモリブロックに構成される。このような方法に、ECCエラー率が90%〜100%である場合に、MLC使用者領域311の9個のメモリブロックはSLCバッファ領域312に転換される。この時、MLC使用者領域311は90個のメモリブロックに構成される。

【0059】

図7Bを参照すれば、SLCバッファ領域312のECCエラー率が0%〜80%である区間で、MLC使用者領域311は99個のメモリブロックを有し、SLCバッファ領域は1個のメモリブロックを有すると仮定する。SLCバッファ領域312のECCエラー率が2%ずつ増加することによって、MLC使用者領域311の1つのメモリブロックはSLCバッファ領域312に転換される。そして、ECCエラー率が100%になる前に、SLCバッファ領域312として使用された一部メモリブロックはウェアアウト(wear−out)として処理され得る。

【0060】

図7A及び図7BはECCエラー率にしたがって10段階に分けられて使用者領域311をバッファ領域312に転換する例を示す。使用者領域311は初期に99%の使用量を有し、徐々に減って最終的に90%の使用量を有する。しかし、使用者領域311の空間が減った変わりに、バッファ領域312のビットエラー増加率は減少して、全体的にメモリシステム300の性能は向上され得る。

【0061】

図8は消去ループ回数に基づいたモード転換動作を説明するためのブロック図である。図8を参照すれば、メモリシステム400は不揮発性メモリ410及びメモリコントローラ420を含む。不揮発性メモリ410は使用者領域411、バッファ領域412、及び消去ループカウンター413を含む。メモリコントローラ420はウェアレベル制御ロジック426を含む。

【0062】

不揮発性メモリ410を使用する分だけ、消去ループ(Erase Loop)の回数は増加する。消去ループ回数は不揮発性メモリ410のウェアレベルパラメーターとして使用され得る。消去ループカウンター(図8参照、413)は最大消去ループ回数が定まっている。OBP方式によれば、バッファ領域412に対するプログラム、読出し、消去動作が反復的に遂行されるので、使用者領域411よりバッファ領域412のウェアレベル(wear−level)がさらに速い速度で増加する。図8に図示されたメモリシステム400は使用者領域411の一部をバッファ領域412にモード転換することによって、バッファ領域412の消去ループ回数の増加率を減らすことができる。

【0063】

消去ループカウンター413は不揮発性メモリ410の消去ループ回数に関する情報をウェアレベル制御ロジック426へ提供する。ウェアレベル制御ロジック426は消去ループ回数に基づいて、使用者領域411の一部メモリブロックに対するモード転換動作を遂行する。例えば、ウェアレベル制御ロジック426は消去ループ回数が予め決められた回数に到達する時、使用者領域411の一部MLCメモリブロックをSLCメモリブロックに転換する。

【0064】

図9は図8に図示された消去ループカウンターを説明するためのダイヤグラムである。図9を参照すれば、不揮発性メモリ(図8参照、410)の各々のメモリセルは閾値電圧によってプログラム状態P及び消去状態Eを有することができる。プログラム状態は1つ又はその以上であり得る。メモリブロックに消去電圧が提供されれば、メモリセルの閾値電圧は消去状態Eへ移動される。以後、メモリセルが消去状態にあるか否かを検証するために消去検証電圧Veが提供される。このような消去動作は全てメモリセルが消去状態Eになるまで反複される。

【0065】

図9を参照すれば、第1消去ループ(EL=1)の間に消去状態Eに到達しないメモリセルが存在するので、第2消去ループ(EL=2)が進行される。第2消去ループ(EL=2)でも消去状態Eに至らなかったセルが存在するので、第3消去ループ(EL=3)が遂行される。第3消去ループ(EL=3)で全てメモリセルが消去状態になる。この時、消去ループカウンター(図8参照、413)に該当する消去ループ回数情報をウェアレベル制御ロジック(図8参照、426)へ提供する。

【0066】

図10A及び図10Bは図8に図示されたメモリシステムの消去ループ回数にしたがうモード変換動作を説明するための概念図である。図10AはMLC使用者領域411の消去ループ回数にしたがうモード転換動作を示し、図10BはSLCバッファ領域412のモード転換動作を示す。図10A及び図10Bでは説明を簡単にするため、消去ループカウンター(図8参照、413)の最大消去ループカウント回数は10であることと仮定する。

【0067】

図10Aを参照すれば、MLC使用者領域411の消去ループ回数が最大消去ループカウント回数の0%〜50%の区間にある場合、MLC使用者領域411は95%であり、SLCバッファ領域は5%である。即ち、消去ループ回数が0〜5である区間で、不揮発性メモリ410は全体100個のメモリブロックの中で95個のメモリブロックを使用者領域として使用し、5個のメモリブロックをバッファ領域として使用する。

【0068】

消去ループ回数が6〜10である場合に、MLC使用者領域411の一部メモリブロック(例えば、5個のメモリブロック)はSLCバッファ領域412に転換される。そして、SLCバッファ領域412として使用されたメモリブロックはウェアアウト(wear−out)として処理される。上の例で、MLC使用者領域411は90個のメモリブロックで構成される。

【0069】

図10Bを参照すれば、SLC使用者領域412の消去ループ回数が最大消去ループカウント回数の0%〜90%の区間にある場合、MLC使用者領域411は95%であり、SLCバッファ領域は5%である。そして消去ループ回数が最大消去ループカウント回数の90%〜100%である場合に、MLC使用者領域411の一部メモリブロック(例えば、5個のメモリブロック)はSLCバッファ領域412に転換される。そして、SLCバッファ領域412として使用されたメモリブロックはウェアアウト(wear−out)として処理される。上の例で、MLC使用者領域411は90個のメモリブロックで構成される。

【0070】

図10A及び図10Bは消去ループ回数にしたがって2段階に分けて使用者領域411をバッファ領域412に転換する例を示す。使用者領域411は初期に95%の使用量を有し、徐々に減って最終的に90%の使用量を有する。しかし、使用者領域411の空間が減った代わりに、バッファ領域412の消去ループ回数の増加率が減るので、全体的にメモリシステム400の性能は向上され得る。

【0071】

本発明の実施形態によるメモリシステムは様々な製品に適用又は応用され得る。本発明の実施形態によるメモリシステムはパーソナルコンピューター、デジタルカメラ、ビデオカメラ(camcorder)、携帯電話、MP3、PMP、PSP、PDA等のような電子装置のみでなく、メモリカード、USBメモリ、ソリッドステートドライブ(Solid State Drive、以下、SSDと称する)等のような格納装置で具現され得る。

【0072】

図11及び図12は本発明によるメモリシステムの多様な適用例を示すブロック図である。図11及び図12を参照すれば、メモリシステム1000、2000は格納装置1100、2100及びホスト1200、2200を含む。格納装置1100、2100はフラッシュメモリ1110、2110及びメモリコントローラ1120、2120を含む。

【0073】

格納装置1100、2100はメモリカード(例えば、SD、MMC等)や着脱可能である移動式格納装置(例えば、USBメモリ等)のような格納媒体を含む。格納装置1100、2100はホスト1200、2200に連結されて使用され得る。格納装置1100、2100はホストインターフェイスを通じてホストとデータを通信する。格納装置1100、2100はホスト1200、2200から電源が供給されて内部動作を遂行できる。

【0074】

図11を参照すれば、ウェアレベル制御ロジック1101はフラッシュメモリ1110内に包含され得る。図12を参照すれば、ウェアレベル制御ロジック2201はホスト2200内に包含され得る。本発明の実施形態によるメモリシステム1000、2000はウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0075】

図13は本発明の実施形態によるメモリシステムをメモリカードシステムに適用した例を示すブロック図である。メモリカードシステム3000はホスト3100とメモリカード3200とを含む。ホスト3100はホストコントローラ3110、ホスト接続ユニット3120、及びDRAM3130を含む。

【0076】

ホスト3100はメモリカード3200にデータを書き込むか、或いはメモリカード3200に格納されたデータを読み出す。ホストコントローラ3110はコマンド(例えば、書込みコマンド)、ホスト3100の内のクロック発生器(図示せず)で発生したクロック信号CLK、及びデータDATを、ホスト接続ユニット3120を通じてメモリカード3200へ伝送する。DRAM3130はホスト3100のメインメモリである。

【0077】

メモリカード3200はカード接続ユニット3210、カードコントローラ3220、及びフラッシュメモリ3230を含む。カードコントローラ3220はカード接続ユニット3210を通じて受信されたコマンドに応答して、カードコントローラ3220内にあるクロック発生器(図示せず)で発生したクロック信号に同期してデータをフラッシュメモリ3230に格納する。フラッシュメモリ3230はホスト3100から伝送されたデータを格納する。例えば、ホスト3100がデジタルカメラである場合には映像データを格納する。

【0078】

図13に図示されたメモリカードシステム3000はホストコントローラ3110、カードコントローラ3220、又はフラッシュメモリ3230の内部にウェアレベル制御ロジック(図示せず)を含むことができる。上述したように、本発明はウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0079】

図14は本発明の実施形態によるメモリシステムをソリッドステートドライブ(SSD)システムに適用した例を示すブロック図である。図14を参照すれば、SSDシステム4000はホスト4100とSSD4200とを含む。ホスト4100はホストインターフェイス4111、ホストコントローラ4120、及びDRAM4130を含む。

【0080】

ホスト4100はSSD4200にデータを書き込むか、或いはSSD4200に格納されたデータを読み出す。ホストコントローラ4120はコマンド、アドレス、制御信号等の信号SGLをホストインターフェイス4111を通じてSSD4200へ伝送する。DRAM4130はホスト4100のメインメモリである。

【0081】

SSD4200はホストインターフェイス4211を通じてホスト4100と信号SGLを通信し、電源コネクター(power connector)4221を通じて電源が入力される。SSD4200は複数の不揮発性メモリ4201〜420n、SSDコントローラ4210、及び補助電源装置4220を含むことができる。ここで、複数の不揮発性メモリ4201〜420nはNANDフラッシュメモリ以外にもPRAM、MRAM、ReRAM、FRAM(登録商標)等で具現され得る。

【0082】

複数の不揮発性メモリ4201〜420nはSSD4200の格納媒体として使用される。複数の不揮発性メモリ4201〜420nは複数のチャンネルCH1〜CHnを通じてSSDコントローラ4210に連結され得る。1つのチャンネルには1つ又はその以上の不揮発性メモリが連結され得る。1つのチャンネルに連結される不揮発性メモリは同一のデータバスに連結され得る。

【0083】

SSDコントローラ4210はホストインターフェイス4211を通じてホスト4100と信号SGLを通信する。ここで、信号SGLにはコマンド、アドレス、データ等が包含され得る。SSDコントローラ4210はホスト4100のコマンドにしたがって該当不揮発性メモリにデータを書き込むか、或いは該当不揮発性メモリからデータを読出す。SSDコントローラ4210の内部構成は図15を参照して詳細に説明される。

【0084】

補助電源装置4220は電源コネクター4221を通じてホスト4100に連結される。補助電源装置4220はホスト4100から電源PWRを受信し、充電することができる。一方、補助電源装置4220はSSD4200の内部に位置するか、或いはSSD4200の外に位置することもできる。例えば、補助電源装置4220はメインボードに位置し、SSD4200へ補助電源を提供することもできる。

【0085】

図15は図14に図示されたSSDコントローラ4210の構成を例示的に示すブロック図である。図15を参照すれば、SSDコントローラ4210はNVMインターフェイス4211、ホストインターフェイス4212、ウェアレベル制御ロジック4213、制御ユニット4214、及びSRAM4215を含む。

【0086】

NVMインターフェイス4211はホスト4100のメインメモリから伝達されたデータを各々のチャンネルCH1〜CHnへスキャッタリング(Scattering)する。そして、NVMインターフェイス4211は不揮発性メモリ4201〜420nから読み出したデータをホストインターフェイス4212を経由してホスト4100へ伝達する。

【0087】

ホストインターフェイス4212はホスト4100のプロトコルに対応してSSD4200とのインターフェイシングを提供する。ホストインターフェイス4212はUSB(Universal Serial Bus)、SCSI(Small Computer System Interface)、PCI express、ATA、PATA(Parallel ATA)、SATA(Serial ATA)、SAS(Serial Attached SCSI)等を利用してホスト4100と通信できる。また、ホストインターフェイス4212はホスト4100がSSD4200をハードディスクドライブ(HDD)として認識するようにサポートするディスクエミュレーション(Disk Emulation)機能を遂行できる。

【0088】

ウェアレベル制御ロジック4213は上述したように不揮発性メモリ4201〜420nのモード転換動作を管理することができる。制御ユニット4214はホスト4100から入力された信号SGLを分析し、処理する。制御ユニット4214はホストインターフェイス4212やNVMインターフェイス4211を通じてホスト4100や不揮発性メモリ4201〜420nを制御する。制御ユニット4214はSSD4200を駆動するためのファームウェアにしたがって不揮発性メモリ4201〜420nの動作を制御する。

【0089】

SRAM4215は不揮発性メモリ4201〜420nの効率的な管理をするために使用されるソフトウェアS/Wを駆動するのに使用され得る。また、SRAM4215はホスト4100のメインメモリから入力されたメタデータを格納するか、或いはキャッシュデータを格納できる。急なパワーオフ動作の時に、SRAM4215に格納されたメタデータやキャッシュデータは補助電源装置4220を利用して不揮発性メモリ4201〜420nに格納され得る。

【0090】

再び図14を参照すれば、本発明の実施形態によるSSDシステム4000は上述したように、ウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0091】

図16は本発明の実施形態によるメモリシステムを電子装置で具現された例を示すブロック図である。ここで、電子装置5000はパーソナルコンピューター(PC)で具現されるか、或いはノート型コンピューター、携帯電話、PDA(Personal Digital Assistant)、及びカメラ等のような携帯用電子装置で具現され得る。

【0092】

図16を参照すれば、電子装置5000はメモリシステム5100、電源装置5200、補助電源装置5250、中央処理装置5300、DRAM5400、及び使用者インターフェイス5500を含む。メモリシステム5100はフラッシュメモリ5110及びメモリコントローラ5120を含む。メモリシステム5100は電子装置5000内に備えられ得る。

【0093】

上述したように、本発明による電子装置5000はウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0094】

本発明の実施形態によるメモリシステムは2次元構造を有するフラッシュメモリのみでなく、3次元構造を有するフラッシュメモリにも適用され得る。図17は本発明に使用されるフラッシュメモリを例示的に示すブロック図である。図17を参照すれば、フラッシュメモリ6000は3次元セルアレイ6110、データ入出力回路6120、アドレスデコーダー6130、及び制御ロジック6140を含む。

【0095】

3次元セルアレイ6110は複数のメモリブロックBLK1〜BLKzを含む。各々のメモリブロックは3次元構造(又は垂直構造)を有することができる。2次元構造(又は水平構造)を有するメモリブロックでは、メモリセルが基板と水平方向に形成される。しかし、3次元構造を有するメモリブロックでは、メモリセルが基板と垂直方向に形成される。各々のメモリブロックはフラッシュメモリ6100の消去単位を成す。

【0096】

データ入出力回路6120は複数のビットラインBLsを通じて3次元セルアレイ6110に連結される。データ入出力回路6120は外部からデータDATAが入力されるか、或いは3次元セルアレイ6110から読み出したデータDATAを外部へ出力する。アドレスデコーダー6130は複数のワードラインWLs及び選択ラインGSL、SSLを通じて3次元セルアレイ6110に連結される。アドレスデコーダー6130はアドレスADDRを受信しワードラインを選択する。

【0097】

制御ロジック6140はフラッシュメモリ6000のプログラム、読出し、消去等の動作を制御する。例えば、制御ロジック6140はプログラム動作の時に、アドレスデコーダー6130を制御することによって、選択ワードラインにプログラム電圧が提供されるようにし、データ入出力回路6120を制御することによって、データがプログラムされるようにすることができる。

【0098】

図18は図17に図示されたメモリブロックBLK1の3次元構造を例示的に示す斜視図である。図18を参照すれば、メモリブロックBLK1は基板SUBと垂直方向に形成されている。基板SUBにはn+ドーピング領域が形成される。基板SUBの上にはゲート電極膜(gate electrode layer)と絶縁膜(insulation layer)とが交互に蒸着される。そして、ゲート電極膜(gate electrode layer)と絶縁膜(insulation layer)との間には電荷格納膜(charge storage layer)が形成され得る。

【0099】

ゲート電極膜と絶縁膜とを垂直方向にパターニング(vertical patterning)すれば、V字形状のピラー(pillar)が形成される。ピラーはゲート電極膜と絶縁膜を貫通して基板SUBに連結される。ピラー(Pillar)の外殻部分(O)はチャンネル半導体に構成されることが可能で、内部Iはシリコン酸化物(Silicon Oxide)のような絶縁物質で構成され得る。

【0100】

続いて、図18を参照すれば、メモリブロックBLK1のゲート電極膜(gate electrode layer)は接地選択ラインGSL、複数のワードラインWL1〜WL8、及びストリング選択ラインSSLに連結され得る。そして、メモリブロックBLK1のピラー(pillar)は複数のビットラインBL1〜BL3に連結され得る。図18では、1つのメモリブロックBLK1が2つの選択ラインGSL、SSL、8個のワードラインWL1〜WL8、及び3個のビットラインBL1〜BL3を有することと図示されているが、実際にはこれらより多いか、或いは少ないことがあり得る。

【0101】

図19は図18に図示されたメモリブロックBLK1の等価回路図である。図19を参照すれば、ビットラインBL1〜BL3と共通ソースラインCSLとの間にはNANDストリングNS11〜NS33が連結されている。各々のNANDストリング(例えば、NS11はストリング選択トランジスターSST、複数のメモリセルMC1〜MC8、及び接地選択トランジスターGSTを含む。

【0102】

ストリング選択トランジスターSSTはストリング選択ライン(String Selection Line;SSL1〜SSL3)に連結されている。複数のメモリセルMC1〜MC8は各々対応するワードラインWL1〜WL8に連結されている。そして接地選択トランジスターGSTは接地選択ライン(Ground Selection Line;GSL1〜GSL3)に連結されている。ストリング選択トランジスター(SSTはビットラインBL)はビットラインに連結されている。接地選択トランジスター(GSTは共通ソースラインCSL;Common Source Line)に連結されている。

【0103】

続いて図19を参照すれば、同一高さのワードライン(例えば、WL1)は共通に連結され、接地選択ラインGSL1〜GSL3及びストリング選択ラインSSL1〜SSL3は分離されている。第1ワードラインWL1に連結され、NANDストリングNS11、NS12、NS13に属しているメモリセル(以下、ページと称する)をプログラムする場合には、第1ワードラインWL1と第1選択ラインSSL1、GSL1とが選択される。

【0104】

本発明の範囲又は、技術的思想を逸脱することなしに本発明の実施形態が多様に修正や変更され得ることは当業者にとって自明である。上述した内容に鑑み、それらの本発明の修正及び変更は、以下の請求項及び、それと均等なものの範囲内に属する。

【符号の説明】

【0105】

100、200、300、400 ・・・メモリシステム

110 ・・・不揮発性メモリ

111 ・・・使用者領域

112 ・・・バッファ領域

120 ・・・メモリコントローラ

121 ・・・ホストインターフェイス

122 ・・・メモリインターフェイス

123 ・・・制御ユニット

124 ・・・RAM

125 ・・・ECC回路

126 ・・・ウェアレベル制御ロジック

【技術分野】

【0001】

本発明は半導体メモリ装置に関し、さらに具体的には不揮発性メモリに基づくメモリシステム、及びそのモード転換動作に関する。

【背景技術】

【0002】

半導体メモリ装置は一般的にDRAM、SRAM等のような揮発性メモリ装置とEEPROM、FRAM(登録商標)、PRAM、MRAM、フラッシュメモリ等のような不揮発性メモリ装置とに区分することができる。揮発性メモリ装置は電源が遮断される時、格納したデータを失うが、不揮発性メモリは電源が遮断されでも格納したデータを保存する。特に、フラッシュメモリは速い読出し速度、低い電力消費、大容量データ格納等の長所を有する。このようなことから、フラッシュメモリを含むメモリシステムはデータ保存媒体として広く使われている。

不揮発性メモリを含むメモリシステムはファイルデータを効率的に管理し、システムの性能を向上するために、データを使用者領域(user area)に格納する前にバッファ領域に格納する。このようなプログラム方式によれば、マージ動作(merge operation)やブロック消去(block erase)回数等を減らし得る。そして、メモリコントローラ内のSRAMバッファの使用量を減らすことができる長所がある。

しかし、このようなプログラム方式はバッファ領域に格納するファイルデータのサイズが大きくなることから、バッファ領域の空間が不足する可能性があり、バッファ領域と使用者領域との間のファイルデータの移動が頻繁に発生してメモリシステムの性能が低下し得る。また、全てプログラム動作の時にバッファ領域を使用するので、バッファ領域のウェアレベル(wear level)が使用者領域に比べて速く増加する問題点がある。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許出願公開第2006−0152981号明細書

【特許文献2】韓国特許出願公開第10−2008−0069822号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の目的は不揮発性メモリのバッファ領域のウェアレベルを緩和するメモリシステムを提供することにある。

【課題を解決するための手段】

【0005】

本発明の実施形態によるメモリシステムは使用者領域とバッファ領域とを有する不揮発性メモリと、前記不揮発性メモリのウェアレベル情報に基づいて、前記使用者領域の一部ブロックを前記バッファ領域に転換する動作(以下、‘モード転換動作’と称する)を管理するためのウェアレベル制御ロジックと、を含む。

【0006】

実施形態として、前記使用者領域にはメモリセル当たりN(Nは2以上である自然数)ビットデータが格納され、前記バッファ領域にはメモリセル当たりM(MはNより小さい自然数)ビットデータが格納される。前記バッファ領域にはシングルビットデータが格納され得る。不揮発性メモリは外部から入力されたデータを前記バッファ領域に格納した次に、前記バッファ領域に格納されたデータを前記使用者領域へ移動する。

【0007】

他の実施形態として、前記ウェアレベル情報は前記使用者領域のプログラム−消去サイクル情報であり得る。前記ウェアレベル制御ロジックは前記プログラム−消去サイクル情報にしたがって、段階的にモード転換動作を遂行できる。

【0008】

その他の実施形態として、前記ウェアレベル情報はECCエラー率情報であり得る。前記ウェアレベル制御ロジックは前記ECCエラー率情報にしたがって、段階的にモード転換動作を遂行できる。

【0009】

その他の実施形態として、前記ウェアレベル情報は消去ループ回数情報であり得る。前記ウェアレベル制御ロジックは前記消去ループ回数情報にしたがって、段階的にモード転換動作を遂行できる。

【発明の効果】

【0010】

本発明によるメモリシステムはウェアレベル情報(例えば、プログラム−消去サイクル、ECCエラー率、消去ループ回数等)に基づいて、使用者領域の一部メモリブロックを段階的にバッファ領域にモード転換を遂行できる。本発明によると、バッファ領域のP/Eサイクル耐久性(endurance)を増加するか、或いはECCエラー率や消去ループ回数の増加率を減らすことによって、メモリシステムの性能を向上させることができる。

【図面の簡単な説明】

【0011】

【図1】本発明によるメモリシステムを概略的に示すブロック図である。

【図2】プログラム−消去サイクルに基づいてモード転換動作を説明するためのブロック図である。

【図3】図2に図示されたメモリシステムのプログラム−消去サイクルにしたがう使用者領域及びバッファ領域の耐久性を示す表である。

【図4A】図2に図示されたメモリシステムのプログラム−消去サイクルにしたがうモード変換動作を説明するための概念図である。

【図4B】図2に図示されたメモリシステムのプログラム−消去サイクルにしたがうモード変換動作を説明するための概念図である。

【図5】図2に図示されたメモリシステムのモード転換動作を遂行するためのマッピングテーブルを例示的に示す表である。

【図6】ECCエラー率に基づいたモード転換動作を説明するためのブロック図である。

【図7A】図6に図示されたメモリシステムのECCエラー率にしたがうモード変換動作を説明するための概念図である。

【図7B】図6に図示されたメモリシステムのECCエラー率にしたがうモード変換動作を説明するための概念図である。

【図8】消去ループ回数に基づいたモード転換動作を説明するためのブロック図である。

【図9】図8に図示された消去ループカウンターを説明するためのダイヤグラムである。

【図10A】図8に図示されたメモリシステムの消去ループ回数にしたがうモード変換動作を説明するための概念図である。

【図10B】図8に図示されたメモリシステムの消去ループ回数にしたがうモード変換動作を説明するための概念図である。

【図11】本発明によるメモリシステムの多様な適用例を示すブロック図である。

【図12】本発明によるメモリシステムの多様な適用例を示すブロック図である。

【図13】本発明の実施形態によるメモリシステムをメモリカードシステムに適用した例を示すブロック図である。

【図14】本発明の実施形態によるメモリシステムをソリッドステートドライブ(SSD)システムに適用した例を示すブロック図である。

【図15】図14に図示されたSSDコントローラの構成を例示的に示すブロック図である。

【図16】本発明の実施形態によるメモリシステムを電子装置で具現された例を示すブロック図である。

【図17】本発明に使用されるフラッシュメモリを例示的に示すブロック図である。

【図18】図17に図示されたメモリブロックBLK1の3次元構造を例示的に示す斜視図である。

【図19】図18に図示されたメモリブロックBLK1の等価回路図である。

【発明を実施するための形態】

【0012】

以下で、本発明が属する技術分野で通常の知識を有する者が本発明の技術的思想を容易に実施できる程度、詳細に説明するために、本発明の実施形態を添付された図面を参照して説明する。

【0013】

図1は本発明によるメモリシステムを概略的に示すブロック図である。図1を参照すれば、本発明によるメモリシステム100は不揮発性メモリ(NVM、110)及びメモリコントローラ120を含む。

【0014】

不揮発性メモリ110はメモリコントローラ120によって制御され、メモリコントローラ120の要請に対応する動作(例えば、読出し又は書込み動作等)を遂行できる。不揮発性メモリ110は使用者領域111とバッファ領域112とを含む。使用者領域111は低速動作を遂行するメモリ(以下、低速不揮発性メモリ)で具現され、バッファ領域112は高速動作を遂行するメモリ(以下、高速不揮発性メモリ)で具現され得る。

【0015】

高速不揮発性メモリは高速動作に適合であり、低速不揮発性メモリは低速動作に適合なマッピングスキームを使用するように構成され得る。例えば、低速不揮発性メモリを構成する使用者領域111はブロックマッピングスキームを通じて管理され、高速不揮発性メモリを構成するバッファ領域112はページマッピングスキームを通じて管理され得る。ページマッピングスキームは動作性能(例えば、書込み性能)の低下を発生させるマージ動作を必要としないので、バッファ領域112は高速に動作できる。反面に、ブロックマッピングスキームは動作性能(例えば、書込み性能)の低下を発生させるマージ動作を必要とするので、使用者領域111は相対的に低速に動作する。

【0016】

一方、バッファ領域112はセル当たり1−ビットデータを格納する単一レベルセルフラッシュメモリ(SLC flash memory)で構成され、使用者領域111はセル当たりN−ビットデータNは2又はそれより大きい整数)を格納するマルチ−レベルセルフラッシュメモリ(MLC flash memory)で構成され得る。又は、使用者及びバッファ領域111、112の各々はマルチ−レベルフラッシュメモリで構成され得る。例えば、使用者領域111はセル当たりN−ビットデータを格納し、バッファ領域112はセル当たりM−ビットデータを格納できる。ここで、MはNより小さい自然数である。一方、使用者領域111とバッファ領域112とは1つのメモリ装置で具現されるか、或いは別のメモリ装置で具現されることもあり得る。

【0017】

メモリコントローラ120は外部(例えば、ホスト)の要請に応答して不揮発性メモリ110に対する読出し及び書込み動作を制御する。メモリコントローラ120はホストインターフェイス121、メモリインターフェイス122、制御ユニット123、RAM124、ECC回路125、及びウェアレベル制御ロジック(Wear Level Control Logic)126を含む。

【0018】

ホストインターフェイス121は外部(例えば、ホスト)とのインターフェイスを提供し、メモリインターフェイス122は不揮発性メモリ110とのインターフェイスを提供する。ホストインターフェイス121は1つ又はそれより多いチャンネル(又は、ポート)(図示せず)を通じてホスト(図示せず)に連結され得る。例えば、ホストインターフェイス121はPATAバス(parallel AT attachment bus)とSATAバス(serial AT attachment)との中でいずれか1つ又はこれら全てを通じてホストと連結され得る。又は、ホストインターフェイス121はSCSI、USB等を通じて外部に連結されることもあり得る。

【0019】

制御ユニット123は不揮発性メモリ110に対する全般的な動作(例えば、読出し、書込み、ファイルシステム管理等)を制御することができる。例えば、たとえ図面には図示していないが、制御ユニット123は中央処理装置(CPU)、プロセッサー(processor)、SRAM、DMA制御器等を含むことができる。例示的な制御ユニット123は特許文献1に開示され、本出願の参照として包含される。

【0020】

制御ユニット123は不揮発性メモリ110のバッファ領域112に格納されたデータを使用者領域111へ移す動作を管理することができる。ここで、バッファ領域112に格納されたデータはフラッシュ動作によってRAM124でダンプされたデータであってよく、ホストの書込み要請によって外部から提供されたデータであってもよい。

【0021】

バッファ領域112で使用者領域111へデータを移す動作は多様な方式を通じて遂行できる。例えば、バッファ領域112の余裕空間が予め設定された空間(例えば、30%)以下であるか否かにしたがって開始され得る。他の例として、決められた時間毎に周期的に開始されてもよい。その他の例として、不揮発性メモリ110のアイドル時間(idle time)を感知することによって開始されることもあり得る。

【0022】

RAM124は制御ユニット123の制御にしたがって動作し、ワークメモリ(work memory)、バッファメモリ(buffer memory)、キャッシュメモリ(cache memory)等として使用され得る。RAM124は1つのチップで構成されるか、或いは不揮発性メモリ110の各領域に対応する複数のチップで構成され得る。

【0023】

RAM124がワークメモリとして使用される場合に、制御ユニット123によって処理されるデータが臨時格納される。RAM124がバッファメモリとして使用される場合には、ホストから不揮発性メモリ110へ又は不揮発性メモリ110からホストへ伝送されるデータをバッファリングするのに使用される。RAM124がキャッシュメモリとして使用される場合(以下、キャッシュスキームと称する)に、RAM124は低速の不揮発性メモリ110が高速に動作するようにする。キャッシュスキームによれば、キャッシュメモリ(RAM、124)に格納されたファイルデータが不揮発性メモリ110のバッファ領域112にダンプ(dump)される。制御ユニット123はダンプ動作にしたがうマッピングテーブル(mapping table)を管理することができる。

【0024】

RAM124は不揮発性メモリ110がフラッシュメモリである場合にフラッシュ変換階層FTLを駆動するための駆動メモリとして使用され得る。フラッシュ変換階層FTLはフラッシュメモリのマージ動作(merge operation)やマッピングテーブル(mapping table)等を管理するのに使用される。

【0025】

一方、ホスト(図示せず)は書込み(write)、読出し(read)の以外にフラッシュキャッシュ(flush cache)のようなコマンドをメモリシステム100へ提供する。メモリシステム100はフラッシュキャッシュコマンドを受信する時、データ一貫性(data consistency)を維持するために、キャッシュメモリ124に格納されているファイルデータを不揮発性メモリ110のバッファ領域112に格納する。このような一連の動作をフラッシュ動作(flush operation)と称する。制御ユニット123はフラッシュ動作の時にキャッシュメモリ124のファイルデータを不揮発性メモリ110のバッファ領域112にダンプする動作を管理することができる。

【0026】

ECC回路125は不揮発性メモリ110から受信したデータのエラービットを訂正するためのエラー訂正コードECCを生成する。ECC回路125は不揮発性メモリ110に提供されるデータのエラー訂正エンコーディングを遂行して、パリティー(parity)ビットが付加されたデータを形成する。パリティービットは不揮発性メモリ110に格納され得る。また、ECC回路125は出力されたデータに対してエラー訂正デコーディングを遂行し、遂行結果にしたがってエラー訂正デコーディングの成功の可否を判断することができる。ECC回路125は判断結果にしたがって指示信号を出力し、パリティービットを使用してデータのエラービットを訂正できる。

【0027】

ECC回路125はLDPC(low density parity check) code、BCH code、turbo code、リードソロモンコード(Reed−Solomon code)、convolution code、RSC(recursive systematic code)、TCM(trellis−coded modulation)、BCM(Block coded modulation)等の符号化変調(coded modulation)を使用してエラーを訂正することができる。ECC回路125はエラーを訂正するための回路、システム又は装置を全て含むことができる。

【0028】

ウェアレベル制御ロジック126は不揮発性メモリ110のウェアレベル(wear level)に基づいて、使用者領域111の一部ブロックをバッファ領域112に転換する動作を管理することができる。このような動作をモード転換動作(mode change operation)と称する。ウェアレベル制御ロジック126は不揮発性メモリ110のウェアレベルが一定のレベルに到達する時、使用者領域111の1つ又はその以上のメモリブロックをMLCモードからSLCモードに転換する動作を管理することができる。

【0029】

ウェアレベル制御ロジック126はハードウェアやソフトウェアで具現され得る。即ち、ウェアレベル制御ロジック126はメモリコントローラ120内に1つのチップやモジュールで設置されるか、或いはフロッピー(登録商標)ディスクやコンパクトディスク又はUSB等のような外装メモリを通じて連結されることもあり得る。一方、ウェアレベル制御ロジック126は使用者によってプログラムできる形態で具現されることもあり得る。

【0030】

不揮発性メモリ110のウェアレベルはプログラム−消去サイクル(P/Eサイクル)、ECCエラー率、又は消去ループ回数等のようなパラメーター(以下、ウェアレベルパラメーターと称する)を通じて知ることができる。不揮発性メモリ110は一般的にP/Eサイクル、ECCエラー率、消去ループ回数が増加するほど、ウェアレベル(wear level)が増加する。以下では、ウェアレベルパラメーターに基づいたメモリシステム100のモード転換動作が詳細に説明される。

【0031】

図2はプログラム−消去サイクルに基づいてモード転換動作を説明するためのブロック図である。図2を参照すれば、メモリシステム200は不揮発性メモリ210及びメモリコントローラ220を含む。不揮発性メモリ210は使用者領域211及びバッファ領域212を含む。使用者領域211はメモリセル当たり2ビット以上を格納するMLC領域にモード設定され、バッファ領域212はシングルビットを格納するSLC領域にモード設定されている。

【0032】

不揮発性メモリ210はプログラム−消去動作を反複して遂行できる許容限度が定まっている。これをP/Eサイクル耐久性(endurance)と称する。P/Eサイクル耐久性はメモリセル当たり格納するデータビット数にしたがって異なり得る。一般的にセル当たり格納するデータビット数が小さいほど、P/Eサイクル耐久性は増加する。

【0033】

一方、使用者領域211にプログラムされる全てのデータは先にバッファ領域212に格納される。その次にバッファ領域212で使用者領域211へデータを移す動作が遂行される。このようなプログラム方式をOBP(On−chip Buffered Program)と称する。OBP方式によれば、バッファ領域212に対するプログラム−消去動作が反復的に遂行されるので、バッファ領域212のP/Eサイクル耐久性が良くなければならない。図2に図示されたメモリシステム200は使用者領域211の一部をバッファ領域212へモード転換することによって、バッファ領域212のP/Eサイクル耐久性を増加することができる。

【0034】

続いて、図2を参照すれば、メモリコントローラ220は制御ユニット223及びウェアレベル制御ロジック226を含む。制御ユニット223は不揮発性メモリ210のプログラム−消去サイクルP/Eに関する情報をウェアレベル制御ロジック226へ提供する。ウェアレベル制御ロジック226はP/E情報に基づいて、使用者領域211の一部メモリブロックに対するモード転換動作(mode change operation)を遂行する。

【0035】

例えば、不揮発性メモリ210は100個のメモリブロックで構成され、使用者領域211は98個の3ビットMLCメモリブロックで構成され、バッファ領域212は2個のSLCメモリブロックで構成されていると仮定する。ウェアレベル制御ロジック226はP/Eサイクルが予め決められた回数に到達する時、使用者領域211の一部MLCメモリブロックをSLCメモリブロックに転換する。

【0036】

図3は図2に図示されたメモリシステムのプログラム−消去サイクルにしたがう使用者領域及びバッファ領域の耐久性を示す表である。図3は、SLCバッファ領域(図2参照、212)は2%であり、3ビットMLC使用者領域(図2参照、211)は98%であると仮定する。また、図3はMLC使用者領域211にプログラムされる全てデータは先にSLCバッファ領域212に格納されると仮定する。

【0037】

図3を参照すれば、MLC使用者領域211の耐久性(MLC[E])が0.5K、1.0K、1.5Kである時、SLCバッファ領域212の耐久性(SLC[E])は各々75K、150K、225Kである。MLC使用者領域211のP/Eサイクルを1000回保障するためには、不揮発性メモリ(図2参照、200)はSLCバッファ領域(図2参照、212)のP/Eサイクルを150、000回を保障しなければならない。SLCバッファ領域212及びMLC使用者領域211の耐久性の相関関係は数式1のように表現できる。

【0038】

[数式1]

SLC[E]=MLC[E]×3×(MLCブロック数/SLCブロック数)

【0039】

SLCバッファ領域の耐久性(SLC[E])はMLC使用者領域の耐久性(MLC[E])が増加するほど、増加し、SLCバッファ領域のブロック数が多くほど、減少する。SLCバッファ領域212の耐久性はMLC使用者領域211の耐久性より10倍以上大きい。これはMLC使用者領域211として使用した一部メモリブロックをSLCバッファ領域212へモードを転換しても90%以上の耐久性をそのまま使用することを意味する。

【0040】

図4A及び図4Bは図2に図示されたメモリシステムのプログラム−消去サイクルにしたがうモード変換動作を説明するための概念図である。図4Aは不揮発性メモリ(図2参照、210のMLC使用者領域(図2参照、211)のP/Eサイクル使用パーセント(%)にしたがうモード転換動作を示し、図4BはSLCバッファ領域212のP/Eサイクル使用パーセント(%)にしたがうモード転換動作を示す。

【0041】

図4Aを参照すれば、MLC使用者領域211のP/Eサイクル初期(0%)に、MLC使用者領域211は98%であり、SLCバッファ領域212は2%である。即ち、不揮発性メモリ210は全体100個のメモリブロックの中で98個のメモリブロックを使用者領域として使用し、2個のメモリブロックをバッファ領域として使用されている。

【0042】

MLC使用者領域211のP/Eサイクルが25%遂行された場合に、MLC使用者領域211の一部メモリブロック(例えば、2個のメモリブロック)はSLCバッファ領域212に転換される。

【0043】

例えば、MLC使用者領域211のP/Eサイクル耐久性が1000回であるとすれば、P/Eサイクルが250回遂行される時、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理されてバッドブロック(bad block)になる。上の例で、SLCバッファ領域212に転換されたメモリブロックは100K以上のP/Eサイクルに該当する耐久性を有することができる(図3参照)。

【0044】

MLC使用者領域211のP/Eサイクルが50%遂行された場合に、MLC使用者領域211の他の一部メモリブロックがSLCバッファ領域212に転換される。上の例で、P/Eサイクルが500回遂行される時、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理される。この時、MLC使用者領域211のメモリブロックは94個である。

【0045】

同様に、MLC使用者領域211のP/Eサイクルが75%遂行された場合に、MLC使用者領域211のその他の一部メモリブロックがSLCバッファ領域212に転換される。上の例で、P/Eサイクルが750回遂行される時、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理される。この時、MLC使用者領域211のメモリブロックは92個である。

【0046】

図4Bを参照すれば、SLC使用者領域212のP/Eサイクル初期(0%)で、不揮発性メモリ210は全体100個のメモリブロックの中で98個のメモリブロックを使用者領域として使用し、2個のメモリブロックをバッファ領域として使用している。

【0047】

SLCバッファ領域212のP/Eサイクルが70%遂行された場合に、MLC使用者領域211の2個のメモリブロックはSLCバッファ領域212に転換される。この時、SLCバッファ領域212は4個のメモリブロックを有する。新しくSLCバッファ領域に転換されたメモリブロックは既存のSLCバッファ領域212のメモリブロックより多いP/Eサイクルを有することができる。全体的にSLCバッファ領域212のP/Eサイクル耐久性は増える。

【0048】

SLCバッファ領域212のP/Eサイクルが80%遂行された場合に、MLC使用者領域211の他の一部メモリブロックがSLCバッファ領域212に転換される。この時、最初からSLCバッファ領域212として使用されたメモリブロックはウェアアウト(wear−out)として処理され得る。この時、MLC使用者領域211のメモリブロックは94個である。

【0049】

同様に、SLCバッファ領域212のP/Eサイクルが90%遂行された場合に、MLC使用者領域211のその他の一部メモリブロックがSLCバッファ領域212に転換される。そして、SLCバッファ領域212として使用された4個のメモリブロックはウェアアウト(wear−out)として処理され得る。この時、MLC使用者領域211のメモリブロックは92個である。

【0050】

図4A及び図4BはP/Eサイクルにしたがって4段階に分かられて使用者領域211をバッファ領域212に転換する例を示す。使用者領域211は初期に98%の使用量を有し、徐々に減って最終的に92%の使用量を有する。しかし、使用者領域211の空間が減る代わりに、バッファ領域212のP/Eサイクル耐久性は大きく増大されて、全体的にメモリシステム200の性能は大きく向上され得る。

【0051】

図5は図2に図示されたメモリシステムのモード転換動作を遂行するためのマッピングテーブルを例示的に示す。図5に図示されたマッピングテーブルはMLC使用者領域(図2参照、211)のP/Eサイクルが25%遂行された場合を示す。

【0052】

図5を参照すれば、不揮発性メモリ(図2参照、210)は100個のメモリブロック001〜100を有する。第1及び第2メモリブロック001、002はP/Eサイクル初期にSLCモード、即ちSLCバッファ領域(図2参照、212)に割当されている。第3乃至第100メモリブロック003〜100はMLCモード、即ちMLC使用者領域211に割当されている。MLC使用者領域211のP/Eサイクルが25%遂行されれば、第1及び第2メモリブロック001、002はウェア−アウトされ、第3及び第4メモリブロック003、004はSLCモードに転換される。即ち、第3及び第4メモリブロック003、004はSLCバッファ領域212にモード転換される。

【0053】

再び図2を参照すれば、本発明の実施形態によるメモリシステム200はプログラム−消去サイクル(P/E cycle)情報に基づいて、使用者領域211の一部メモリブロックを段階的にバッファ領域212にモード転換を遂行できる。本発明によると、バッファ領域212のP/Eサイクル耐久性が良くなることによって、メモリシステム200の性能が向上され得る。

【0054】

図6はECCエラー率に基づいたモード転換動作を説明するためのブロック図である。図6を参照すれば、メモリシステム300は不揮発性メモリ310及びメモリコントローラ320を含む。不揮発性メモリ310は使用者領域311及びバッファ領域312を含み、メモリコントローラ320はECC回路325及びウェアレベル制御ロジック326を含む。

【0055】

不揮発性メモリ310を使用する分だけ、ECCエラー率は増加する。ECC回路325はエラーを訂正できる最大ビット数が定まっている。OBP方式によれば、バッファ領域312に対するプログラムや読出し動作が反復的に遂行されるので、使用者領域311よりバッファ領域312のECCエラー率がさらに速い速度で増加する。図6に図示されたメモリシステム300は使用者領域311の一部をバッファ領域312にモード転換することによって、バッファ領域312のECCエラー増加率を減らすことができる。

【0056】

続いて、図6を参照すれば、ECC回路325は不揮発性メモリ310のECCエラー率(error rate)に関する情報をウェアレベル制御ロジック326へ提供する。ウェアレベル制御ロジック326はECCエラー率に基づいて、使用者領域311の一部メモリブロックに対するモード転換動作を遂行する。例えば、ウェアレベル制御ロジック326はECCエラー率が予め決められたエラー率に到達する時、使用者領域311の一部メモリブロックをバッファ領域312に転換する。

【0057】

図7A及び図7Bは図6に図示されたメモリシステムのECCエラー率にしたがうモード変換動作を説明するための概念図である。図7AはMLC使用者領域のECCエラー率にしたがうモード変換動作を示し、図7BはSLCバッファ領域のECCエラー率にしたがう全て変換動作を示す。図7A及び図7Bでは説明を簡単にするため、ECC回路(図6参照、325)の訂正可能であるECCエラービットは100であることと仮定する。

【0058】

図7Aを参照すれば、MLC使用者領域311のECCエラー率が0%〜10%である区間で、MLC使用者領域311は99個のメモリブロックを有し、SLCバッファ領域は1個のメモリブロックを有すると仮定する。ECCエラー率が10%〜20%である場合に、MLC使用者領域311の一部メモリブロック(例えば、1つのメモリブロック)はSLCバッファ領域312に転換される。そして、SLCバッファ領域312として使用されたメモリブロックはウェアアウト(wear−out)として処理される。この時、MLC使用者領域311は98個のメモリブロックに構成される。このような方法に、ECCエラー率が90%〜100%である場合に、MLC使用者領域311の9個のメモリブロックはSLCバッファ領域312に転換される。この時、MLC使用者領域311は90個のメモリブロックに構成される。

【0059】

図7Bを参照すれば、SLCバッファ領域312のECCエラー率が0%〜80%である区間で、MLC使用者領域311は99個のメモリブロックを有し、SLCバッファ領域は1個のメモリブロックを有すると仮定する。SLCバッファ領域312のECCエラー率が2%ずつ増加することによって、MLC使用者領域311の1つのメモリブロックはSLCバッファ領域312に転換される。そして、ECCエラー率が100%になる前に、SLCバッファ領域312として使用された一部メモリブロックはウェアアウト(wear−out)として処理され得る。

【0060】

図7A及び図7BはECCエラー率にしたがって10段階に分けられて使用者領域311をバッファ領域312に転換する例を示す。使用者領域311は初期に99%の使用量を有し、徐々に減って最終的に90%の使用量を有する。しかし、使用者領域311の空間が減った変わりに、バッファ領域312のビットエラー増加率は減少して、全体的にメモリシステム300の性能は向上され得る。

【0061】

図8は消去ループ回数に基づいたモード転換動作を説明するためのブロック図である。図8を参照すれば、メモリシステム400は不揮発性メモリ410及びメモリコントローラ420を含む。不揮発性メモリ410は使用者領域411、バッファ領域412、及び消去ループカウンター413を含む。メモリコントローラ420はウェアレベル制御ロジック426を含む。

【0062】

不揮発性メモリ410を使用する分だけ、消去ループ(Erase Loop)の回数は増加する。消去ループ回数は不揮発性メモリ410のウェアレベルパラメーターとして使用され得る。消去ループカウンター(図8参照、413)は最大消去ループ回数が定まっている。OBP方式によれば、バッファ領域412に対するプログラム、読出し、消去動作が反復的に遂行されるので、使用者領域411よりバッファ領域412のウェアレベル(wear−level)がさらに速い速度で増加する。図8に図示されたメモリシステム400は使用者領域411の一部をバッファ領域412にモード転換することによって、バッファ領域412の消去ループ回数の増加率を減らすことができる。

【0063】

消去ループカウンター413は不揮発性メモリ410の消去ループ回数に関する情報をウェアレベル制御ロジック426へ提供する。ウェアレベル制御ロジック426は消去ループ回数に基づいて、使用者領域411の一部メモリブロックに対するモード転換動作を遂行する。例えば、ウェアレベル制御ロジック426は消去ループ回数が予め決められた回数に到達する時、使用者領域411の一部MLCメモリブロックをSLCメモリブロックに転換する。

【0064】

図9は図8に図示された消去ループカウンターを説明するためのダイヤグラムである。図9を参照すれば、不揮発性メモリ(図8参照、410)の各々のメモリセルは閾値電圧によってプログラム状態P及び消去状態Eを有することができる。プログラム状態は1つ又はその以上であり得る。メモリブロックに消去電圧が提供されれば、メモリセルの閾値電圧は消去状態Eへ移動される。以後、メモリセルが消去状態にあるか否かを検証するために消去検証電圧Veが提供される。このような消去動作は全てメモリセルが消去状態Eになるまで反複される。

【0065】

図9を参照すれば、第1消去ループ(EL=1)の間に消去状態Eに到達しないメモリセルが存在するので、第2消去ループ(EL=2)が進行される。第2消去ループ(EL=2)でも消去状態Eに至らなかったセルが存在するので、第3消去ループ(EL=3)が遂行される。第3消去ループ(EL=3)で全てメモリセルが消去状態になる。この時、消去ループカウンター(図8参照、413)に該当する消去ループ回数情報をウェアレベル制御ロジック(図8参照、426)へ提供する。

【0066】

図10A及び図10Bは図8に図示されたメモリシステムの消去ループ回数にしたがうモード変換動作を説明するための概念図である。図10AはMLC使用者領域411の消去ループ回数にしたがうモード転換動作を示し、図10BはSLCバッファ領域412のモード転換動作を示す。図10A及び図10Bでは説明を簡単にするため、消去ループカウンター(図8参照、413)の最大消去ループカウント回数は10であることと仮定する。

【0067】

図10Aを参照すれば、MLC使用者領域411の消去ループ回数が最大消去ループカウント回数の0%〜50%の区間にある場合、MLC使用者領域411は95%であり、SLCバッファ領域は5%である。即ち、消去ループ回数が0〜5である区間で、不揮発性メモリ410は全体100個のメモリブロックの中で95個のメモリブロックを使用者領域として使用し、5個のメモリブロックをバッファ領域として使用する。

【0068】

消去ループ回数が6〜10である場合に、MLC使用者領域411の一部メモリブロック(例えば、5個のメモリブロック)はSLCバッファ領域412に転換される。そして、SLCバッファ領域412として使用されたメモリブロックはウェアアウト(wear−out)として処理される。上の例で、MLC使用者領域411は90個のメモリブロックで構成される。

【0069】

図10Bを参照すれば、SLC使用者領域412の消去ループ回数が最大消去ループカウント回数の0%〜90%の区間にある場合、MLC使用者領域411は95%であり、SLCバッファ領域は5%である。そして消去ループ回数が最大消去ループカウント回数の90%〜100%である場合に、MLC使用者領域411の一部メモリブロック(例えば、5個のメモリブロック)はSLCバッファ領域412に転換される。そして、SLCバッファ領域412として使用されたメモリブロックはウェアアウト(wear−out)として処理される。上の例で、MLC使用者領域411は90個のメモリブロックで構成される。

【0070】

図10A及び図10Bは消去ループ回数にしたがって2段階に分けて使用者領域411をバッファ領域412に転換する例を示す。使用者領域411は初期に95%の使用量を有し、徐々に減って最終的に90%の使用量を有する。しかし、使用者領域411の空間が減った代わりに、バッファ領域412の消去ループ回数の増加率が減るので、全体的にメモリシステム400の性能は向上され得る。

【0071】

本発明の実施形態によるメモリシステムは様々な製品に適用又は応用され得る。本発明の実施形態によるメモリシステムはパーソナルコンピューター、デジタルカメラ、ビデオカメラ(camcorder)、携帯電話、MP3、PMP、PSP、PDA等のような電子装置のみでなく、メモリカード、USBメモリ、ソリッドステートドライブ(Solid State Drive、以下、SSDと称する)等のような格納装置で具現され得る。

【0072】

図11及び図12は本発明によるメモリシステムの多様な適用例を示すブロック図である。図11及び図12を参照すれば、メモリシステム1000、2000は格納装置1100、2100及びホスト1200、2200を含む。格納装置1100、2100はフラッシュメモリ1110、2110及びメモリコントローラ1120、2120を含む。

【0073】

格納装置1100、2100はメモリカード(例えば、SD、MMC等)や着脱可能である移動式格納装置(例えば、USBメモリ等)のような格納媒体を含む。格納装置1100、2100はホスト1200、2200に連結されて使用され得る。格納装置1100、2100はホストインターフェイスを通じてホストとデータを通信する。格納装置1100、2100はホスト1200、2200から電源が供給されて内部動作を遂行できる。

【0074】

図11を参照すれば、ウェアレベル制御ロジック1101はフラッシュメモリ1110内に包含され得る。図12を参照すれば、ウェアレベル制御ロジック2201はホスト2200内に包含され得る。本発明の実施形態によるメモリシステム1000、2000はウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0075】

図13は本発明の実施形態によるメモリシステムをメモリカードシステムに適用した例を示すブロック図である。メモリカードシステム3000はホスト3100とメモリカード3200とを含む。ホスト3100はホストコントローラ3110、ホスト接続ユニット3120、及びDRAM3130を含む。

【0076】

ホスト3100はメモリカード3200にデータを書き込むか、或いはメモリカード3200に格納されたデータを読み出す。ホストコントローラ3110はコマンド(例えば、書込みコマンド)、ホスト3100の内のクロック発生器(図示せず)で発生したクロック信号CLK、及びデータDATを、ホスト接続ユニット3120を通じてメモリカード3200へ伝送する。DRAM3130はホスト3100のメインメモリである。

【0077】

メモリカード3200はカード接続ユニット3210、カードコントローラ3220、及びフラッシュメモリ3230を含む。カードコントローラ3220はカード接続ユニット3210を通じて受信されたコマンドに応答して、カードコントローラ3220内にあるクロック発生器(図示せず)で発生したクロック信号に同期してデータをフラッシュメモリ3230に格納する。フラッシュメモリ3230はホスト3100から伝送されたデータを格納する。例えば、ホスト3100がデジタルカメラである場合には映像データを格納する。

【0078】

図13に図示されたメモリカードシステム3000はホストコントローラ3110、カードコントローラ3220、又はフラッシュメモリ3230の内部にウェアレベル制御ロジック(図示せず)を含むことができる。上述したように、本発明はウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0079】

図14は本発明の実施形態によるメモリシステムをソリッドステートドライブ(SSD)システムに適用した例を示すブロック図である。図14を参照すれば、SSDシステム4000はホスト4100とSSD4200とを含む。ホスト4100はホストインターフェイス4111、ホストコントローラ4120、及びDRAM4130を含む。

【0080】

ホスト4100はSSD4200にデータを書き込むか、或いはSSD4200に格納されたデータを読み出す。ホストコントローラ4120はコマンド、アドレス、制御信号等の信号SGLをホストインターフェイス4111を通じてSSD4200へ伝送する。DRAM4130はホスト4100のメインメモリである。

【0081】

SSD4200はホストインターフェイス4211を通じてホスト4100と信号SGLを通信し、電源コネクター(power connector)4221を通じて電源が入力される。SSD4200は複数の不揮発性メモリ4201〜420n、SSDコントローラ4210、及び補助電源装置4220を含むことができる。ここで、複数の不揮発性メモリ4201〜420nはNANDフラッシュメモリ以外にもPRAM、MRAM、ReRAM、FRAM(登録商標)等で具現され得る。

【0082】

複数の不揮発性メモリ4201〜420nはSSD4200の格納媒体として使用される。複数の不揮発性メモリ4201〜420nは複数のチャンネルCH1〜CHnを通じてSSDコントローラ4210に連結され得る。1つのチャンネルには1つ又はその以上の不揮発性メモリが連結され得る。1つのチャンネルに連結される不揮発性メモリは同一のデータバスに連結され得る。

【0083】

SSDコントローラ4210はホストインターフェイス4211を通じてホスト4100と信号SGLを通信する。ここで、信号SGLにはコマンド、アドレス、データ等が包含され得る。SSDコントローラ4210はホスト4100のコマンドにしたがって該当不揮発性メモリにデータを書き込むか、或いは該当不揮発性メモリからデータを読出す。SSDコントローラ4210の内部構成は図15を参照して詳細に説明される。

【0084】

補助電源装置4220は電源コネクター4221を通じてホスト4100に連結される。補助電源装置4220はホスト4100から電源PWRを受信し、充電することができる。一方、補助電源装置4220はSSD4200の内部に位置するか、或いはSSD4200の外に位置することもできる。例えば、補助電源装置4220はメインボードに位置し、SSD4200へ補助電源を提供することもできる。

【0085】

図15は図14に図示されたSSDコントローラ4210の構成を例示的に示すブロック図である。図15を参照すれば、SSDコントローラ4210はNVMインターフェイス4211、ホストインターフェイス4212、ウェアレベル制御ロジック4213、制御ユニット4214、及びSRAM4215を含む。

【0086】

NVMインターフェイス4211はホスト4100のメインメモリから伝達されたデータを各々のチャンネルCH1〜CHnへスキャッタリング(Scattering)する。そして、NVMインターフェイス4211は不揮発性メモリ4201〜420nから読み出したデータをホストインターフェイス4212を経由してホスト4100へ伝達する。

【0087】

ホストインターフェイス4212はホスト4100のプロトコルに対応してSSD4200とのインターフェイシングを提供する。ホストインターフェイス4212はUSB(Universal Serial Bus)、SCSI(Small Computer System Interface)、PCI express、ATA、PATA(Parallel ATA)、SATA(Serial ATA)、SAS(Serial Attached SCSI)等を利用してホスト4100と通信できる。また、ホストインターフェイス4212はホスト4100がSSD4200をハードディスクドライブ(HDD)として認識するようにサポートするディスクエミュレーション(Disk Emulation)機能を遂行できる。

【0088】

ウェアレベル制御ロジック4213は上述したように不揮発性メモリ4201〜420nのモード転換動作を管理することができる。制御ユニット4214はホスト4100から入力された信号SGLを分析し、処理する。制御ユニット4214はホストインターフェイス4212やNVMインターフェイス4211を通じてホスト4100や不揮発性メモリ4201〜420nを制御する。制御ユニット4214はSSD4200を駆動するためのファームウェアにしたがって不揮発性メモリ4201〜420nの動作を制御する。

【0089】

SRAM4215は不揮発性メモリ4201〜420nの効率的な管理をするために使用されるソフトウェアS/Wを駆動するのに使用され得る。また、SRAM4215はホスト4100のメインメモリから入力されたメタデータを格納するか、或いはキャッシュデータを格納できる。急なパワーオフ動作の時に、SRAM4215に格納されたメタデータやキャッシュデータは補助電源装置4220を利用して不揮発性メモリ4201〜420nに格納され得る。

【0090】

再び図14を参照すれば、本発明の実施形態によるSSDシステム4000は上述したように、ウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0091】

図16は本発明の実施形態によるメモリシステムを電子装置で具現された例を示すブロック図である。ここで、電子装置5000はパーソナルコンピューター(PC)で具現されるか、或いはノート型コンピューター、携帯電話、PDA(Personal Digital Assistant)、及びカメラ等のような携帯用電子装置で具現され得る。

【0092】

図16を参照すれば、電子装置5000はメモリシステム5100、電源装置5200、補助電源装置5250、中央処理装置5300、DRAM5400、及び使用者インターフェイス5500を含む。メモリシステム5100はフラッシュメモリ5110及びメモリコントローラ5120を含む。メモリシステム5100は電子装置5000内に備えられ得る。

【0093】

上述したように、本発明による電子装置5000はウェアレベル制御ロジックを利用して、フラッシュメモリの使用者領域の一部をバッファ領域に転換することによって、全体システムの性能を向上させ得る。

【0094】

本発明の実施形態によるメモリシステムは2次元構造を有するフラッシュメモリのみでなく、3次元構造を有するフラッシュメモリにも適用され得る。図17は本発明に使用されるフラッシュメモリを例示的に示すブロック図である。図17を参照すれば、フラッシュメモリ6000は3次元セルアレイ6110、データ入出力回路6120、アドレスデコーダー6130、及び制御ロジック6140を含む。

【0095】

3次元セルアレイ6110は複数のメモリブロックBLK1〜BLKzを含む。各々のメモリブロックは3次元構造(又は垂直構造)を有することができる。2次元構造(又は水平構造)を有するメモリブロックでは、メモリセルが基板と水平方向に形成される。しかし、3次元構造を有するメモリブロックでは、メモリセルが基板と垂直方向に形成される。各々のメモリブロックはフラッシュメモリ6100の消去単位を成す。

【0096】

データ入出力回路6120は複数のビットラインBLsを通じて3次元セルアレイ6110に連結される。データ入出力回路6120は外部からデータDATAが入力されるか、或いは3次元セルアレイ6110から読み出したデータDATAを外部へ出力する。アドレスデコーダー6130は複数のワードラインWLs及び選択ラインGSL、SSLを通じて3次元セルアレイ6110に連結される。アドレスデコーダー6130はアドレスADDRを受信しワードラインを選択する。

【0097】

制御ロジック6140はフラッシュメモリ6000のプログラム、読出し、消去等の動作を制御する。例えば、制御ロジック6140はプログラム動作の時に、アドレスデコーダー6130を制御することによって、選択ワードラインにプログラム電圧が提供されるようにし、データ入出力回路6120を制御することによって、データがプログラムされるようにすることができる。

【0098】

図18は図17に図示されたメモリブロックBLK1の3次元構造を例示的に示す斜視図である。図18を参照すれば、メモリブロックBLK1は基板SUBと垂直方向に形成されている。基板SUBにはn+ドーピング領域が形成される。基板SUBの上にはゲート電極膜(gate electrode layer)と絶縁膜(insulation layer)とが交互に蒸着される。そして、ゲート電極膜(gate electrode layer)と絶縁膜(insulation layer)との間には電荷格納膜(charge storage layer)が形成され得る。

【0099】

ゲート電極膜と絶縁膜とを垂直方向にパターニング(vertical patterning)すれば、V字形状のピラー(pillar)が形成される。ピラーはゲート電極膜と絶縁膜を貫通して基板SUBに連結される。ピラー(Pillar)の外殻部分(O)はチャンネル半導体に構成されることが可能で、内部Iはシリコン酸化物(Silicon Oxide)のような絶縁物質で構成され得る。

【0100】

続いて、図18を参照すれば、メモリブロックBLK1のゲート電極膜(gate electrode layer)は接地選択ラインGSL、複数のワードラインWL1〜WL8、及びストリング選択ラインSSLに連結され得る。そして、メモリブロックBLK1のピラー(pillar)は複数のビットラインBL1〜BL3に連結され得る。図18では、1つのメモリブロックBLK1が2つの選択ラインGSL、SSL、8個のワードラインWL1〜WL8、及び3個のビットラインBL1〜BL3を有することと図示されているが、実際にはこれらより多いか、或いは少ないことがあり得る。

【0101】

図19は図18に図示されたメモリブロックBLK1の等価回路図である。図19を参照すれば、ビットラインBL1〜BL3と共通ソースラインCSLとの間にはNANDストリングNS11〜NS33が連結されている。各々のNANDストリング(例えば、NS11はストリング選択トランジスターSST、複数のメモリセルMC1〜MC8、及び接地選択トランジスターGSTを含む。

【0102】

ストリング選択トランジスターSSTはストリング選択ライン(String Selection Line;SSL1〜SSL3)に連結されている。複数のメモリセルMC1〜MC8は各々対応するワードラインWL1〜WL8に連結されている。そして接地選択トランジスターGSTは接地選択ライン(Ground Selection Line;GSL1〜GSL3)に連結されている。ストリング選択トランジスター(SSTはビットラインBL)はビットラインに連結されている。接地選択トランジスター(GSTは共通ソースラインCSL;Common Source Line)に連結されている。

【0103】

続いて図19を参照すれば、同一高さのワードライン(例えば、WL1)は共通に連結され、接地選択ラインGSL1〜GSL3及びストリング選択ラインSSL1〜SSL3は分離されている。第1ワードラインWL1に連結され、NANDストリングNS11、NS12、NS13に属しているメモリセル(以下、ページと称する)をプログラムする場合には、第1ワードラインWL1と第1選択ラインSSL1、GSL1とが選択される。

【0104】

本発明の範囲又は、技術的思想を逸脱することなしに本発明の実施形態が多様に修正や変更され得ることは当業者にとって自明である。上述した内容に鑑み、それらの本発明の修正及び変更は、以下の請求項及び、それと均等なものの範囲内に属する。

【符号の説明】

【0105】

100、200、300、400 ・・・メモリシステム

110 ・・・不揮発性メモリ

111 ・・・使用者領域

112 ・・・バッファ領域

120 ・・・メモリコントローラ

121 ・・・ホストインターフェイス

122 ・・・メモリインターフェイス

123 ・・・制御ユニット

124 ・・・RAM

125 ・・・ECC回路

126 ・・・ウェアレベル制御ロジック

【特許請求の範囲】

【請求項1】

使用者領域とバッファ領域とを有する不揮発性メモリと、

前記不揮発性メモリのウェアレベル情報に基づいて、前記使用者領域の一部メモリブロックを前記バッファ領域に転換する動作(以下、‘モード転換動作’と称する)を管理するためのウェアレベル制御ロジックと、を含むメモリシステム。

【請求項2】

前記ウェアレベル情報は前記バッファ領域のウェアレベル情報であることを特徴とする請求項1に記載のメモリシステム。

【請求項3】

前記ウェアレベル情報はプログラム−消去サイクル情報であることを特徴とする請求項2に記載のメモリシステム。

【請求項4】

前記ウェアレベル情報はECCエラー率情報であることを特徴とする請求項2に記載のメモリシステム。

【請求項5】

前記ウェアレベル情報は消去ループ回数情報であることを特徴とする請求項2に記載のメモリシステム。

【請求項6】

前記ウェアレベル情報は前記使用者領域のウェアレベル情報であることを特徴とする請求項1に記載のメモリシステム。

【請求項7】

前記ウェアレベル情報はプログラム−消去サイクル情報であることを特徴とする請求項6に記載のメモリシステム。

【請求項8】

前記ウェアレベル情報はECCエラー率情報であることを特徴とする請求項6に記載のメモリシステム。

【請求項9】

前記ウェアレベル情報は消去ループ回数情報であることを特徴とする請求項6に記載のメモリシステム。

【請求項10】

前記使用者領域にはメモリセル当たりN(Nは2以上である自然数)ビットデータが格納され、前記バッファ領域にはメモリセル当たりM(MはNより小さい自然数)ビットデータが格納される請求項1に記載のメモリシステム。

【請求項1】

使用者領域とバッファ領域とを有する不揮発性メモリと、

前記不揮発性メモリのウェアレベル情報に基づいて、前記使用者領域の一部メモリブロックを前記バッファ領域に転換する動作(以下、‘モード転換動作’と称する)を管理するためのウェアレベル制御ロジックと、を含むメモリシステム。

【請求項2】

前記ウェアレベル情報は前記バッファ領域のウェアレベル情報であることを特徴とする請求項1に記載のメモリシステム。

【請求項3】

前記ウェアレベル情報はプログラム−消去サイクル情報であることを特徴とする請求項2に記載のメモリシステム。

【請求項4】

前記ウェアレベル情報はECCエラー率情報であることを特徴とする請求項2に記載のメモリシステム。

【請求項5】

前記ウェアレベル情報は消去ループ回数情報であることを特徴とする請求項2に記載のメモリシステム。

【請求項6】

前記ウェアレベル情報は前記使用者領域のウェアレベル情報であることを特徴とする請求項1に記載のメモリシステム。

【請求項7】

前記ウェアレベル情報はプログラム−消去サイクル情報であることを特徴とする請求項6に記載のメモリシステム。

【請求項8】

前記ウェアレベル情報はECCエラー率情報であることを特徴とする請求項6に記載のメモリシステム。

【請求項9】

前記ウェアレベル情報は消去ループ回数情報であることを特徴とする請求項6に記載のメモリシステム。

【請求項10】

前記使用者領域にはメモリセル当たりN(Nは2以上である自然数)ビットデータが格納され、前記バッファ領域にはメモリセル当たりM(MはNより小さい自然数)ビットデータが格納される請求項1に記載のメモリシステム。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9】

【図10A】

【図10B】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9】

【図10A】

【図10B】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−114679(P2013−114679A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2012−249984(P2012−249984)

【出願日】平成24年11月14日(2012.11.14)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成24年11月14日(2012.11.14)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]