エピタキシャルウエーハ及びその製造方法

【課題】 本発明は、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハ及びその製造方法を提供することを目的とする。

【解決手段】 撮像素子製造用のエピタキシャルウエーハを製造する方法であって、前記エピタキシャル層の成長前に、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

【解決手段】 撮像素子製造用のエピタキシャルウエーハを製造する方法であって、前記エピタキシャル層の成長前に、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像素子製造用のエピタキシャルウエーハ及びその製造方法に関する。

【背景技術】

【0002】

固体撮像素子に用いられるシリコンウエーハとしては、フォトダイオード(撮像素子)を形成する際に、光電効果によってキャリアを発生させたり、そのキャリアを井戸型ポテンシャルによって溜めておいたりする際の均一な動作を確保するため、面内およびウエーハ間の抵抗率を均一にすることが可能であるエピタキシャルウエーハが用いられる。フォトダイオードはこのエピタキシャル層内に形成されるが、フォトダイオードからの不要な電荷を流すためにフォトダイオードを形成する層よりも下側に抵抗率の低いエピタキシャル層を形成する2層エピタキシャル層や多層エピタキシャル層が用いられることもある。例えば、n型シリコンウエーハに、抵抗率の低いエピタキシャル層(n+層:ドーパントが多いので+を付けて表現することが多い)を成長させ、その上に通常抵抗率のエピタキシャル層を成長させたn/n+/nという構造などが比較的多く用いられている。

【0003】

撮像素子製造用のシリコンウエーハに関する特徴としては、ゲッタリング技術が挙げられる。撮像素子では白傷などと呼ばれる映像上の欠陥が発生することがあり、これは不純物などに起因することが知られている。この不純物を防止する手法としては、シリコンウエーハ内に酸素析出物(BMD)を形成したり(イントリンシックゲッタリング)、シリコンウエーハの下面側に機械的なダメージや歪を形成したり(イクストリンシックゲッタリング)して、撮像素子製造中の熱環境を利用して歪場に不純物を捕らえるゲッタリング技術が知られている。撮像素子製造用のシリコンウエーハではこのゲッタリング能力を更に向上させるために特許文献1、2などで開示されている炭素をドープしてBMDを向上(増加及び制御)させる方法が用いられてきている。

【0004】

次に、エピタキシャル層に関する特徴としては先にも述べた抵抗率の均一性はもちろんであるが、エピタキシャル層の厚さも特徴的である。エピタキシャル層にはフォトダイオードが形成されるが、この部分ではレンズで集光され色フィルタによって色分けされた光で光電効果を起こし、それによって発生したキャリア数を光の強度として感知する。光の進入深さは波長によって異なり、例えば光の強度が半分になる深さは青色で約0.3μm、赤色であれば3μm程度である。赤色を効率よく受光するためにはエピタキシャル層の厚さが最低でも3μm程度は必要であるため、その下部に形成されるキャリアを放出する領域を合わせると4μm以上は必要であり、メモリーやロジックなどに使われるエピタキシャル層の厚さよりは厚く成長させるのが一般的である。厚いエピタキシャル層の記載例として、特許文献3〜5では厚さに関する議論はほとんど行われていないが2−10μmまたは1−20μmなどと記載されている。更に特許文献6、7では実施例にて11μmまたは12μmのエピタキシャル層の厚さが記載されており、撮像素子用に厚いエピタキシャル層が用いられている例は過去にも存在する。しかしながらエピタキシャル層の厚さを厚く成長させるとその分コストアップになるため無制限に厚くすることはできず、従って実際に撮像素子に用いられる現実のエピタキシャル層の厚さは4−6μm程度が現実的な厚さである。

【0005】

しかしながら近年、シリコンウエーハに含まれている不純物分布が悪影響をもたらすことがわかってきた。シリコンウエーハは一般にCZ法(MCZ法を含む)により育成されたシリコン単結晶から切り出されている。これらの結晶成長方法においては、石英ルツボ内でシリコン原料を溶融して、そこからシリコン単結晶を育成するものであって、石英ルツボから溶出した酸素原子がシリコン単結晶中に過飽和な状態で含まれている。この酸素原子は、先に述べたイントリンシックゲッタリングのBMDとして有用である。つまりデバイス製造等の熱プロセスを通じて、シリコン単結晶中の過剰な酸素原子がSiと反応してSiO2の形でシリコン単結晶内に析出する。これがBMD(Bulk Micro Defect)と呼ばれるものである。

【0006】

またCZ法によるシリコン単結晶中には酸素原子のほかに、抵抗率を制御するためにドーパントが含まれている。3族のBや5族のP、As、Sbなどの原子が一般的である。さらに炭素をドープしたシリコン単結晶においては炭素原子も不純物として含まれている。これらのドーパントや酸素・炭素原子はシリコン単結晶中に偏析現象によって取り込まれていく。しかしシリコン溶融液内の不純物の濃度が完全に均一ではない点、成長速度が一定でなく炉内の温度変動や結晶の直径によって変動するため実効の偏析係数が成長速度に連動して変化する点などからシリコン単結晶中の不純物濃度は不均一になる。このときシリコン単結晶の成長界面が平らでなく一般的に上凸形状である点と、シリコン単結晶を回転させながら育成している点とから、同心円状の縞状濃淡分布を形成する。これがストリエーションまたは成長縞と呼ばれるものである。

【0007】

近年、撮像素子上にこの濃淡と一致するような不良が発生することが明らかになってきた。不良の内容としては、光が入ってない状態でもキャリアが発生してしまう暗電流や発生した電荷を井戸型ポテンシャル内で溜める際のエネルギー障壁高さ異常などである。従って単結晶育成中にストリエーション状の不純物分布を低減する必要がある。これに対する技術として特許文献8では成長速度を一定範囲内で抑制することが提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2001−102384号公報

【特許文献2】特開2001−237247号公報

【特許文献3】特開2009−212351号公報

【特許文献4】特開2009−212352号公報

【特許文献5】特開2011−82443号公報

【特許文献6】特開平6−163410号公報

【特許文献7】特開平10−41311号公報

【特許文献8】特開2009−274888号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、近年の更なる微細化・高感度化の流れの中ではこれだけでは充分でなくなってきており、暗電流やポテンシャル異常の問題が再度発生する場合があることがわかってきた。本発明者らがこの問題を解析していくと、シリコンウエーハ中に含まれていた酸素原子が撮像素子製造中にエピタキシャル層内に拡散してしまい、その酸素が例えばドナー化したりして、上述のような問題が引き起こされることが推定された。特許文献6、7のように厚いエピタキシャル層の例は少ないながら存在するが、これらの文献ではエピタキシャル層中の不純物に関しては触れられておらず充分とはいえない。

【0010】

本発明は上記問題点に鑑みてなされたものであり、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハ及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、上記課題を解決するためになされたものであって、CZ法によりシリコン単結晶を育成し、該シリコン単結晶からシリコンウエーハを作製し、該シリコンウエーハ上にエピタキシャル層を成長することで撮像素子製造用のエピタキシャルウエーハを製造する方法であって、

前記エピタキシャル層の成長前に、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、

前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法を提供する。

【0012】

このような製造方法であれば、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハを製造することができる。

【0013】

また、前記エピタキシャル層の成長前に、厚さXを下記式により計算することが好ましい。

4×1017=([Oi]ini+[Oi]sol(T))/2−([Oi]ini−[Oi]sol(T))/2×erf[X/{2√(D(T)t)}]

(式中、[Oi]iniは前記シリコンウエーハの初期酸素濃度、Tは前記撮像素子製造中の最も高温の熱プロセスの温度、[Oi]sol(T)は前記温度Tにおける酸素の固溶度、D(T)は前記温度Tにおける酸素の拡散係数、tは前記温度Tの熱プロセスの処理時間、erfはエラー関数を示す。)

【0014】

上記のように、撮像素子の製造の熱プロセスによってシリコンウエーハからエピタキシャル層中に拡散する酸素の濃度は厚さXの関数として表すことができる。酸素の拡散係数は熱処理温度が下がれば劇的に下がるので、上記式のように、撮像素子製造中の最も高温の熱プロセスについてのみ拡散する酸素濃度を計算することで、煩雑な計算が不要になり、また汎用性の高い計算方法となる。

【0015】

さらに、前記エピタキシャル層の成長において、エピタキシャル層として多層エピタキシャル層を成長することができる。

【0016】

このように抵抗率や導電型の異なるエピタキシャル層を多層成長させた場合であっても、本発明のエピタキシャルウエーハの製造方法であれば、シリコンウエーハ中の酸素等不純物の悪影響は撮像素子形成部分まで及ばない。

【0017】

また、前記エピタキシャル層の成長において、エピタキシャル層を、厚さXに加えて、更に撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さであって、該エピタキシャル層全体の厚さが9μm以上20μm以下となる厚さで成長することが好ましい。

【0018】

近年の撮像素子製造プロセスではゲート酸化膜が形成される熱処理がもっとも高温のプロセスであることが多く、このプロセス後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さは約3μm程度と見積もられる。そのため、エピタキシャル層を厚さ9μm以上に形成することが望ましく、また厚いほど好ましい。また、20μm以下であればコストパフォーマンスが良い。

【0019】

さらに、前記シリコン単結晶の育成において、炭素濃度が1.3×1016−22×1016atoms/cm3(ASTM’74)となるように炭素をドープし、酸素濃度が8×1017−16×1017atoms/cm3(ASTM’79)となるように制御してシリコン単結晶を育成することができる。

【0020】

このように、炭素をドープするシリコン単結晶の場合であれば、炭素濃度が1.3×1016atoms/cm3以上であればBMD向上効果が得られ、炭素濃度が22×1016atoms/cm3以下であればシリコン単結晶における炭素の固溶限界までは達しないので単結晶化しやすい。また、酸素濃度が8×1017atoms/cm3以上であればBMDを形成しやすく、酸素濃度が16×1017atoms/cm3以下であればBMDの個数、サイズともに良好でゲッタリング能力が向上する。

【0021】

また、前記シリコン単結晶の育成において、炭素をドープせず、酸素濃度が16×1017−24×1017atoms/cm3(ASTM’79)となるように制御してシリコン単結晶を育成することができる。

【0022】

このように、炭素をドープしないシリコン単結晶の場合でも、酸素濃度が16×1017atoms/cm3(ASTM’79)以上とすることでBMDが十分成長する。また、酸素濃度が24×1017atoms/cm3(ASTM’79)以下であれば酸素析出量が大きくなりすぎず、ウエーハの反りなど別の問題を引き起こす可能性を抑制できる。

【0023】

さらに、本発明は、CZ法により育成したシリコン単結晶から作製されたシリコンウエーハに、エピタキシャル層を成長させた撮像素子製造用のエピタキシャルウエーハであって、

前記エピタキシャル層は、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域と、前記撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域とが形成されるものであり、該酸素濃度が4×1017atoms/cm3未満の領域の厚さは6μm以上となるものであることを特徴とするエピタキシャルウエーハを提供する。

【0024】

このようなエピタキシャルウエーハであれば、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないものとなる。

【発明の効果】

【0025】

以上説明したように、本発明のエピタキシャルウエーハの製造方法であれば、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハを製造することができる。また、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXの算出も、煩雑な計算は不要であり、汎用性の高い方法で行うことができる。さらに、シリコンウエーハとして、適切な炭素濃度、酸素濃度を有するものを使用することで優れたゲッタリング能力を有するエピタキシャルウエーハを製造することができる。本発明により製造されたエピタキシャルウエーハはデジタルカメラや携帯電話などに用いられているCCDやCISといった固体撮像素子用に好適に用いることができる。

【図面の簡単な説明】

【0026】

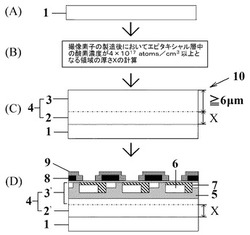

【図1】本発明のエピタキシャルウエーハの製造方法のフロー図である。

【図2】実施例1の条件におけるエピタキシャルウエーハに熱シュミレーションを施した場合の酸素濃度の分布を示した図である。

【図3】実施例2の条件におけるエピタキシャルウエーハに熱シュミレーションを施した場合の酸素濃度の分布を示した図である。

【発明を実施するための形態】

【0027】

以下、本発明を詳細に説明するが、本発明はこれに限定されるものではない。上述のように、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハの製造方法が望まれていた。

【0028】

本発明者らは、上記問題点について鋭意検討を重ねた結果、シリコンウエーハ中の酸素等不純物の悪影響が及ぶエピタキシャル層の領域の厚さを算出し、この厚さに加えて酸素等不純物の悪影響が及ばないエピタキシャル層の領域(撮像素子形成部分)の厚さが6μm以上となる厚さで、エピタキシャル層を成長することでシリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハとなることを見出して、本発明を完成させた。

【0029】

図1に本発明のエピタキシャルウエーハの製造方法のフロー図を示す。本発明の製造方法では、CZ法によりシリコン単結晶を育成し、該シリコン単結晶からシリコンウエーハ1を作製し(図1(A))、エピタキシャル層を成長する前に、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算する(図1(B))。その後、エピタキシャル層4を、厚さXに加えて、更に撮像素子の製造後におけるエピタキシャル層4中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長し、撮像素子製造用のエピタキシャルウエーハ10を製造する(図1(C))。

【0030】

図1(D)に示すように、撮像素子を製造するプロセス中では、その熱環境によりシリコンウエーハ1からエピタキシャル層4中に酸素が拡散していく。その結果、撮像素子の製造後には、エピタキシャル層4中に拡散した酸素濃度が高い領域と低い領域が形成される。本発明では、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)以上となるシリコンウエーハに近い領域を緩衝層2’、撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)未満となるシリコンウエーハから離れた領域を有効層3’と呼ぶこととする。緩衝層2’、有効層3’はどちらも撮像素子の製造前のエピタキシャル層4のことである。本発明では、成長するエピタキシャル層4全体の厚さは、撮像素子を製造後の緩衝層2’となる領域2の厚さと有効層3’となる領域3の厚さの和である。

【0031】

例えば図1(D)で行う撮像素子製造プロセスでは、エピタキシャル層4上にP型ウェル・ゲート酸化膜5を形成し、この内にn型不純物注入部6及びp型不純物注入部7を選択的にイオン注入し、転送部とフォトダイオードを形成する。また、その上にポリシリコン電極8、受光部を除く部分に遮光膜9を形成することで、撮像素子を形成できる。

【0032】

前述のように撮像素子製造中(図1(D))にシリコンウエーハから酸素が拡散し、デバイス特性に悪影響をもたらすことが判ってきたため、本発明ではシリコンウエーハ1からの影響を排除するための緩衝層2’となる領域2の厚さを予め算出し(図1(B))、これに加えて、更に撮像素子を作製するための有効層3’となる領域3の厚さが6μm以上となる厚さで、エピタキシャル層4を成長する(図1(C))。これにより、シリコンウエーハの影響を受けない高感度で高集積度な撮像素子製造用エピタキシャルウエーハを作製することができる。

【0033】

ここで、撮像素子製造後に有効層となる領域は、撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)未満となる領域とし、その厚さとしては6μm以上必要とした。有効層に撮像素子を形成する場合には、入射光を光電変換してキャリアを発生させそれを溜めておくフォトダイオード(撮像素子)部分とその下に不要となった電荷を排出する部分が形成される。他に転送部などフォトダイオードで感じた光の強さを読み取る部分も形成される。

【0034】

先に述べたように光の進入深さは波長によって異なり、例えば光の強度が半分になる深さは青色で約0.3μm、赤色であれば3μm程度である。赤色を効率よく受光するためにはフォトダイオードの厚さが最低でも3μm程度は必要である。従って不要電荷を放出する領域も含めた撮像素子製造に必要な厚さは少なくとも4μm以上である。必要な厚さは本来撮像素子設計に関わるものであり一概に決められるものではないが、昨今の撮像素子の高感度化を鑑み本発明では有効層となる領域に必要な厚さを6μm以上とした。

【0035】

また、撮像素子製造後に緩衝層となる領域は、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)以上となる領域とした。酸素濃度4×1017atoms/cm3(ASTM’79)で撮像素子製造後に緩衝層となる領域と有効層となる領域を分けたのは、撮像素子製造の後工程などで行われる配線やパッケージなどで低温の熱処理によって酸素ドナーが発生することが考えられるためである。酸素ドナーは酸素濃度が減れば激減する。本発明者らの実験データでは最も酸素ドナーが発生しやすい450℃で5時間の熱処理をした場合、酸素濃度が4×1017atoms/cm3(ASTM’79)の場合にはキャリアは約8×1011atoms/cm3発生し、酸素濃度8×1017atoms/cm3(ASTM’79)の場合にはキャリアは約5×1013atoms/cm3発生し、さらに酸素濃度が12×1017atoms/cm3(ASTM’79)の場合にはキャリアは約6×1014atoms/cm3発生した。これから分かるように、酸素濃度が2倍、3倍となるにつれて桁違いに酸素ドナー起因のキャリアが増加することがわかる。フォトダイオードを作製する近辺のもともとのドーパント濃度は1014〜1015程度であるから、酸素ドナー起因キャリアによる悪影響を防止するためにはこれより2桁程度酸素ドナー濃度が低いことが望まれる。従って、酸素濃度が4×1017atoms/cm3(ASTM’79)以上の部分を緩衝層となる領域とし、それを除いた部分はフォトダイオード等を作製する有効層となる領域とした。

【0036】

一般にエピタキシャル層の厚さが厚くなるとコストも高くなる。エピタキシャル層を成長させる工程ではウエーハのロード/アンドロードや前処理等の工程はあるが、最も工程の時間を律速するのはエピタキシャル層を成長させる工程である。それはエピタキシャル層の成長速度が非常に遅いためである。従ってエピタキシャル層を厚く成長させることはコストアップに直結するものである。このため必要な厚さ以上はエピタキシャル層の厚さを厚くしないのが普通である。しかし、本発明では従来必要とされてきたフォトダイオード等を作製するのに必要な厚さに加えて、シリコンウエーハからの影響を抑制するための緩衝層となる領域を設ける点が最大の特徴である。これにより、今後予想される微細化・高感度化の要求に対し、エピタキシャル層の厚さアップによるパフォーマンスの向上が期待でき、最終的にコストパフォーマンスの優れた製品を提供することが可能となる。

【0037】

また、緩衝層の厚さを以下のようにして決めることで、撮像素子製造後の酸素濃度を確認する作業を省くことができる。シリコンウエーハとエピタキシャル層との界面からエピタキシャル層側の距離、すなわち緩衝層となる領域の厚さをXとすると、熱プロセスによってシリコンウエーハからエピタキシャル層中に拡散する酸素の濃度Cは厚さXの関数として次式のように表される。なおここでerfはエラー関数(誤差関数)の略であり、拡散の濃度を求めるために一般的に用いられるものである。

C(X)=([Oi]ini+[Oi]sol(T))/2−([Oi]ini−[Oi]sol(T))/2×erf[X/{2√(D(T)t)}]

(式中、[Oi]iniはシリコンウエーハの初期酸素濃度、Tは撮像素子製造中の最も高温の熱プロセスの温度、[Oi]sol(T)は温度Tにおける酸素の固溶度、D(T)は温度Tにおける酸素の拡散係数、tは温度Tの熱プロセスの処理時間、erfはエラー関数を示す。)

【0038】

これにより求められた酸素濃度分布から、酸素濃度が4×1017atoms/cm3(ASTM’79)となる厚さ、すなわち緩衝層となる領域の厚さXとして定めることができる。

【0039】

なお、上記式では、拡散した酸素濃度を撮像素子製造中の最高温度の処理温度により計算しているが、エピタキシャル層成長時の熱処理や撮像素子製造中の他の熱処理など全ての熱処理において酸素の拡散を計算することもできる。しかしながら、それぞれの熱処理についての計算を行うと計算式が煩雑になる恐れがあり、また計算式の汎用性が損なわれる恐れがある。一方で、エピタキシャル成長は高温だが短時間であるし、撮像素子製造中の熱処理の詳細に関してはデバイスメーカーのノウハウに関わる問題であり、撮像素子を製造するに際し適宜変更されるものである。また、最近の撮像素子製造温度の全体的な低温化に伴って高温で熱処理される工程は減少してきている。さらに、酸素の拡散係数は熱処理温度が下がれば劇的に下がる。以上より、拡散した酸素濃度の算出式に、簡便性と汎用性を持たせるため、上記式では最も高温の撮像素子製造プロセスを代表して試算して、概算の緩衝層となる領域の厚さを決定することとした。

【0040】

また、本発明のエピタキシャルウエーハの製造方法においては、1層のエピタキシャル層を成長させる場合だけではなく、撮像素子構造の一部をエピタキシャル成長時に造り込む場合など2層以上の多層エピタキシャル層を成長することもできる。このような多層エピタキシャルウエーハにおいては、各々のエピタキシャル層の厚さを合計した全体のエピタキシャル層の厚さが、上述の緩衝層となる領域及び有効層となる領域の厚さを有するものであれば良い。

【0041】

多層エピタキシャル層を形成する場合は、抵抗率や導電型の異なるエピタキシャル層を多層成長させることができる。本発明はシリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層のフォトダイオード形成部分まで及ばないことを目的とするが、このように抵抗率が異なっていたとしてもエピタキシャル層中の酸素原子や炭素原子濃度はシリコンウエーハに比較すれば皆無といえるほどに低いので、どの抵抗率の層であっても緩衝層となる領域としての役割を果たすことが可能である。

【0042】

緩衝層となる領域の厚さは上述したように、撮像素子製造プロセスの設計に依存する数値ではあるが近年のプロセスではゲート酸化膜が形成される熱処理がもっとも高温のプロセスであることが多い。例えば、基板の初期酸素濃度を14.5×1017atoms/cm3(ASTM’79)、酸化膜を形成する温度と時間を1000℃、60分と想定すれば、酸素濃度が4×1017atoms/cm3以上となる深さは約2.6μmである。従って近年の撮像素子におけるおおよその緩衝層となる領域の厚さは3μm程度と見積もられる。有効層となる領域としては6μm以上必要であることから、撮像素子用のエピタキシャル層の全体の厚さの最低厚さは9μmと見積もられる。

【0043】

以上のことからエピタキシャル層の全体の厚さを9μm以上20μm以下とすることが望ましい。上限を20μmとしたのはコストがパフォーマンス以上に高くなるおそれがあるからである。将来、エピタキシャル成長技術が改善されコストが下がる方策が見つかれば、エピタキシャル層は厚ければ厚いほど良いといえる。

【0044】

本発明のエピタキシャルウエーハの製造方法では、白傷の対策もあるので従来用いられてきた炭素をドープしたシリコン単結晶の場合には、炭素濃度は1.3×1016−22×1016atoms/cm3(ASTM’74)であることが好ましい。炭素濃度が1.3×1016atoms/cm3以上であればBMD向上効果が得られ、22×1016atoms/cm3以下であればシリコン単結晶における炭素の固溶限界までは達しないので単結晶化しやすい。

【0045】

また、炭素をドープしたシリコン単結晶の酸素濃度は8×1017−16×1017atoms/cm3(ASTM’79)に制御されたものが好ましい。8×1017atoms/cm3以上であればBMDを形成しやすい。また、16×1017atoms/cm3以下であればBMDの個数、サイズともに良好でゲッタリング能力が向上する。

【0046】

さらに、炭素をドープしないシリコン単結晶の場合であれば、酸素濃度が16×1017atoms/cm3(ASTM’79)以上であればBMDが十分成長する。従って撮像素子の白傷対策用のシリコンウエーハとして、炭素をドープせずに酸素濃度16×1017atoms/cm3(ASTM’79)以上であるシリコンウエーハを用いることも有効である。また、24×1017atoms/cm3(ASTM’79)以下であれば酸素析出量が大きくなりすぎず、ウエーハの反りなど別の問題を引き起こす可能性を抑制できる。

【実施例】

【0047】

以下、本発明の実施例および比較例を挙げてさらに詳細に説明するが、本発明は下記の実施例に限定されるものではない。

【0048】

〔実施例1〕

磁場を印加したCZ法であるMCZ法を用いて、炭素濃度5.4×1016atoms/cm3(ASTM’74)、酸素濃度14.2×1017atoms/cm3(ASTM’79)の直径300mmのシリコン単結晶を育成し、これから切り出したウエーハを研磨してシリコンウエーハとした。

【0049】

このとき酸素の拡散に最も影響すると思われる熱処理がゲート酸化熱処理であり、具体的には1000℃、60分ドライ酸素雰囲気で行う予定であった。上記酸素濃度とこの熱処理条件から撮像素子製造後のエピタキシャル層の酸素濃度が4×1017atoms/cm3(ASTM’79)以上になる領域の厚さは上記式により図2に示すように2.3μmと計算される。フォトダイオード形成領域深さが6μmであったとすると、シリコンウエーハの影響を受けないために必要な厚さは8.3μmとなる。なお、ここで酸素の拡散係数D(T)はD(T)=Doexp(−Eo/kT)、Do=0.13(cm2/s)、Eo=2.53(eV)、酸素の固溶度[Oi]sol(T)は[Oi]sol(T)=[Oi]oexp(−Eoi/kT)、[Oi]o=9.00×1022(atoms/cm3)、Eoi=1.52(eV)として計算した。

【0050】

このため試算で求めた8.3μmより厚い9μmのエピタキシャル層をシリコンウエーハ上に成長し、撮像素子プロセスに投入した。エピタキシャル層はPドープn型の層を形成した。また撮像素子のプロセスの概略としては、n型エピタキシャル層にP型ウェル・ゲート酸化膜を形成し、このウェル内にn型及びp型の不純物を選択的にイオン注入し、転送部とフォトダイオードを形成する。その上にポリシリコン電極、受光部を除く部分に遮光膜を形成することで、撮像素子を形成した。

【0051】

その結果、実施例1では筋状の暗電流異常は検出されなかった。また、シリコンウエーハには光散乱法によって1×109/cm3以上の白傷の抑制には充分と思われるBMDが検出された。従って、上記の試算で求めたエピタキシャル層の厚さが8.3μm以上必要であるという結果が妥当であったことが証明されたと考えられる。

【0052】

〔比較例〕

次にシリコンウエーハは全く同じシリコン単結晶(結晶炭素濃度5.4×1016atoms/cm3(ASTM’74)、酸素濃度14.2×1017atoms/cm3(ASTM’79))から切り出したものを用い、エピタキシャル層の厚さを上記の試算で求めた8.3μmより薄い6μmとしたこと以外は実施例1と全く同じエピタキシャルウエーハを作製した。このウエーハを実施例1と同じ撮像素子プロセスに投入した。

【0053】

その結果、出来上がった撮像素子には実施例1では見られなかった筋状の暗電流異常が検出された。一方でシリコンウエーハには光散乱法によって1×109/cm3以上の白傷の抑制には充分と思われるBMDが検出された。これをX線トポグラフ及び光散乱法にてウエーハ面内観察すると、X線では回折強度の濃淡として、光散乱法ではBMD密度の多寡として、同心円状のストリエーションパターン(縞状の分)が観察された。これら縞状分布と筋状の暗電流不良パターンを比較すると類似性が高いことがわかった。従って、ストリエーション起因で不良を発生させてしまったことが考えられる。

【0054】

実施例1の試算結果からシリコンウエーハの影響を受けないために必要な厚さは8.3μmとなる。このため6μmのエピタキシャル層の厚さでは問題が発生したものと考えられる。

【0055】

また、比較例と実施例1で用いたエピタキシャルウエーハに撮像素子製造プロセスを模した熱シミュレーションを施した。それらのウエーハをSIMS(Secondary Ion−microprobe Mass Spectrometer)を用いて、表面から深さ方向に酸素濃度の分布を測定した。その結果、比較例で用いたウエーハでは表面から奥に行くにしたがって徐々に酸素濃度が高くなり、表面から3.7μm(シリコンウエーハ−エピタキシャル層界面から2.3μm)のところで酸素濃度4×1017atoms/cm3(ASTM’79)となった。一方で実施例1に用いたウエーハの場合、図2に示すように同様に表面から奥に行くにしたがって徐々に酸素濃度が高くなっていき、深さ約6.5μm(シリコンウエーハ−エピタキシャル層界面から2.5μm)のところで酸素濃度4×1017atoms/cm3(ASTM’79)となった。

【0056】

以上のことから、有効層として必要な深さがおおよそ6μmであること、充分な緩衝層を有するべきであること、有効層として機能するにはその酸素濃度が4×1017atoms/cm3(ASTM’79)以下であることが必要であることが確認できた。

【0057】

〔実施例2〕

比較例と実施例1で用いたシリコンウエーハとは異なり、炭素をドープせず、酸素濃度を17×1017atoms/cm3(ASTM’79)と高くして育成したシリコン単結晶からシリコンウエーハを形成した。この酸素濃度の異なるシリコンウエーハを用いて、撮像素子製造プロセスを模した熱シミュレーションを施した後に酸素濃度分布を測定し、有効層の厚さが充分取れるかの確認実験を行う。このとき撮像素子製造プロセスの条件変更を想定して、実施例1で用いた熱シミュレーションのうち酸化膜形成熱処理を1000℃、30分と半分の時間に設定した。

【0058】

この酸素濃度及び熱処理条件から計算されるエピタキシャル層中の酸素濃度は図3のようになり、酸素濃度4×1017atoms/cm3(ASTM’79)を満たす厚さは1.9μmと試算された。そこでこの炭素ドープしていない高酸素濃度シリコンウエーハに有効層として6μm以上が取れると予測される厚さ8μmのエピタキシャル層を成長させた。その後、酸化膜形成熱処理を1000℃、30分としたデバイスシミュレーション熱処理を施した。

【0059】

このウエーハをSIMS(Secondary Ion−microprobe Mass Spectrometer)を用いて、表面から深さ方向に酸素濃度の分布を測定した。表面から奥に行くにしたがって徐々に酸素濃度が高くなり、表面から6.2μm(シリコンウエーハ−エピタキシャル層界面から1.8μm)のところで酸素濃度4×1017atoms/cm3(ASTM’79)となった。つまり、計算した予想どおりフォトダイオード形成に必要な有効層の厚さ6μmを確保できていた。またシリコンウエーハ中には光散乱法によって1×109/cm3以上の白傷の抑制には充分と思われるBMDが検出された。

【0060】

以上のように、事前に撮像素子製造プロセスの熱処理条件とシリコンウエーハの酸素濃度とがわかっていれば、本発明の製造方法を用いて有効層の厚さを確保するためのエピタキシャル層の厚さを事前に予想してエピタキシャル層を成長させることができ、これによってシリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハを製造でき、不良率を低減することが可能である。

【0061】

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は、例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

【符号の説明】

【0062】

1…シリコンウエーハ、 2…緩衝層となる領域、 2’…緩衝層、 3…有効層となる領域、 3’…有効層、 4…エピタキシャル層、 5…P型ウェル・ゲート酸化膜、 6…n型不純物注入部、 7…p型不純物注入部、 8…ポリシリコン電極、 9…遮光膜、 10…エピタキシャルウエーハ

【技術分野】

【0001】

本発明は、撮像素子製造用のエピタキシャルウエーハ及びその製造方法に関する。

【背景技術】

【0002】

固体撮像素子に用いられるシリコンウエーハとしては、フォトダイオード(撮像素子)を形成する際に、光電効果によってキャリアを発生させたり、そのキャリアを井戸型ポテンシャルによって溜めておいたりする際の均一な動作を確保するため、面内およびウエーハ間の抵抗率を均一にすることが可能であるエピタキシャルウエーハが用いられる。フォトダイオードはこのエピタキシャル層内に形成されるが、フォトダイオードからの不要な電荷を流すためにフォトダイオードを形成する層よりも下側に抵抗率の低いエピタキシャル層を形成する2層エピタキシャル層や多層エピタキシャル層が用いられることもある。例えば、n型シリコンウエーハに、抵抗率の低いエピタキシャル層(n+層:ドーパントが多いので+を付けて表現することが多い)を成長させ、その上に通常抵抗率のエピタキシャル層を成長させたn/n+/nという構造などが比較的多く用いられている。

【0003】

撮像素子製造用のシリコンウエーハに関する特徴としては、ゲッタリング技術が挙げられる。撮像素子では白傷などと呼ばれる映像上の欠陥が発生することがあり、これは不純物などに起因することが知られている。この不純物を防止する手法としては、シリコンウエーハ内に酸素析出物(BMD)を形成したり(イントリンシックゲッタリング)、シリコンウエーハの下面側に機械的なダメージや歪を形成したり(イクストリンシックゲッタリング)して、撮像素子製造中の熱環境を利用して歪場に不純物を捕らえるゲッタリング技術が知られている。撮像素子製造用のシリコンウエーハではこのゲッタリング能力を更に向上させるために特許文献1、2などで開示されている炭素をドープしてBMDを向上(増加及び制御)させる方法が用いられてきている。

【0004】

次に、エピタキシャル層に関する特徴としては先にも述べた抵抗率の均一性はもちろんであるが、エピタキシャル層の厚さも特徴的である。エピタキシャル層にはフォトダイオードが形成されるが、この部分ではレンズで集光され色フィルタによって色分けされた光で光電効果を起こし、それによって発生したキャリア数を光の強度として感知する。光の進入深さは波長によって異なり、例えば光の強度が半分になる深さは青色で約0.3μm、赤色であれば3μm程度である。赤色を効率よく受光するためにはエピタキシャル層の厚さが最低でも3μm程度は必要であるため、その下部に形成されるキャリアを放出する領域を合わせると4μm以上は必要であり、メモリーやロジックなどに使われるエピタキシャル層の厚さよりは厚く成長させるのが一般的である。厚いエピタキシャル層の記載例として、特許文献3〜5では厚さに関する議論はほとんど行われていないが2−10μmまたは1−20μmなどと記載されている。更に特許文献6、7では実施例にて11μmまたは12μmのエピタキシャル層の厚さが記載されており、撮像素子用に厚いエピタキシャル層が用いられている例は過去にも存在する。しかしながらエピタキシャル層の厚さを厚く成長させるとその分コストアップになるため無制限に厚くすることはできず、従って実際に撮像素子に用いられる現実のエピタキシャル層の厚さは4−6μm程度が現実的な厚さである。

【0005】

しかしながら近年、シリコンウエーハに含まれている不純物分布が悪影響をもたらすことがわかってきた。シリコンウエーハは一般にCZ法(MCZ法を含む)により育成されたシリコン単結晶から切り出されている。これらの結晶成長方法においては、石英ルツボ内でシリコン原料を溶融して、そこからシリコン単結晶を育成するものであって、石英ルツボから溶出した酸素原子がシリコン単結晶中に過飽和な状態で含まれている。この酸素原子は、先に述べたイントリンシックゲッタリングのBMDとして有用である。つまりデバイス製造等の熱プロセスを通じて、シリコン単結晶中の過剰な酸素原子がSiと反応してSiO2の形でシリコン単結晶内に析出する。これがBMD(Bulk Micro Defect)と呼ばれるものである。

【0006】

またCZ法によるシリコン単結晶中には酸素原子のほかに、抵抗率を制御するためにドーパントが含まれている。3族のBや5族のP、As、Sbなどの原子が一般的である。さらに炭素をドープしたシリコン単結晶においては炭素原子も不純物として含まれている。これらのドーパントや酸素・炭素原子はシリコン単結晶中に偏析現象によって取り込まれていく。しかしシリコン溶融液内の不純物の濃度が完全に均一ではない点、成長速度が一定でなく炉内の温度変動や結晶の直径によって変動するため実効の偏析係数が成長速度に連動して変化する点などからシリコン単結晶中の不純物濃度は不均一になる。このときシリコン単結晶の成長界面が平らでなく一般的に上凸形状である点と、シリコン単結晶を回転させながら育成している点とから、同心円状の縞状濃淡分布を形成する。これがストリエーションまたは成長縞と呼ばれるものである。

【0007】

近年、撮像素子上にこの濃淡と一致するような不良が発生することが明らかになってきた。不良の内容としては、光が入ってない状態でもキャリアが発生してしまう暗電流や発生した電荷を井戸型ポテンシャル内で溜める際のエネルギー障壁高さ異常などである。従って単結晶育成中にストリエーション状の不純物分布を低減する必要がある。これに対する技術として特許文献8では成長速度を一定範囲内で抑制することが提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2001−102384号公報

【特許文献2】特開2001−237247号公報

【特許文献3】特開2009−212351号公報

【特許文献4】特開2009−212352号公報

【特許文献5】特開2011−82443号公報

【特許文献6】特開平6−163410号公報

【特許文献7】特開平10−41311号公報

【特許文献8】特開2009−274888号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、近年の更なる微細化・高感度化の流れの中ではこれだけでは充分でなくなってきており、暗電流やポテンシャル異常の問題が再度発生する場合があることがわかってきた。本発明者らがこの問題を解析していくと、シリコンウエーハ中に含まれていた酸素原子が撮像素子製造中にエピタキシャル層内に拡散してしまい、その酸素が例えばドナー化したりして、上述のような問題が引き起こされることが推定された。特許文献6、7のように厚いエピタキシャル層の例は少ないながら存在するが、これらの文献ではエピタキシャル層中の不純物に関しては触れられておらず充分とはいえない。

【0010】

本発明は上記問題点に鑑みてなされたものであり、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハ及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、上記課題を解決するためになされたものであって、CZ法によりシリコン単結晶を育成し、該シリコン単結晶からシリコンウエーハを作製し、該シリコンウエーハ上にエピタキシャル層を成長することで撮像素子製造用のエピタキシャルウエーハを製造する方法であって、

前記エピタキシャル層の成長前に、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、

前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法を提供する。

【0012】

このような製造方法であれば、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハを製造することができる。

【0013】

また、前記エピタキシャル層の成長前に、厚さXを下記式により計算することが好ましい。

4×1017=([Oi]ini+[Oi]sol(T))/2−([Oi]ini−[Oi]sol(T))/2×erf[X/{2√(D(T)t)}]

(式中、[Oi]iniは前記シリコンウエーハの初期酸素濃度、Tは前記撮像素子製造中の最も高温の熱プロセスの温度、[Oi]sol(T)は前記温度Tにおける酸素の固溶度、D(T)は前記温度Tにおける酸素の拡散係数、tは前記温度Tの熱プロセスの処理時間、erfはエラー関数を示す。)

【0014】

上記のように、撮像素子の製造の熱プロセスによってシリコンウエーハからエピタキシャル層中に拡散する酸素の濃度は厚さXの関数として表すことができる。酸素の拡散係数は熱処理温度が下がれば劇的に下がるので、上記式のように、撮像素子製造中の最も高温の熱プロセスについてのみ拡散する酸素濃度を計算することで、煩雑な計算が不要になり、また汎用性の高い計算方法となる。

【0015】

さらに、前記エピタキシャル層の成長において、エピタキシャル層として多層エピタキシャル層を成長することができる。

【0016】

このように抵抗率や導電型の異なるエピタキシャル層を多層成長させた場合であっても、本発明のエピタキシャルウエーハの製造方法であれば、シリコンウエーハ中の酸素等不純物の悪影響は撮像素子形成部分まで及ばない。

【0017】

また、前記エピタキシャル層の成長において、エピタキシャル層を、厚さXに加えて、更に撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さであって、該エピタキシャル層全体の厚さが9μm以上20μm以下となる厚さで成長することが好ましい。

【0018】

近年の撮像素子製造プロセスではゲート酸化膜が形成される熱処理がもっとも高温のプロセスであることが多く、このプロセス後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さは約3μm程度と見積もられる。そのため、エピタキシャル層を厚さ9μm以上に形成することが望ましく、また厚いほど好ましい。また、20μm以下であればコストパフォーマンスが良い。

【0019】

さらに、前記シリコン単結晶の育成において、炭素濃度が1.3×1016−22×1016atoms/cm3(ASTM’74)となるように炭素をドープし、酸素濃度が8×1017−16×1017atoms/cm3(ASTM’79)となるように制御してシリコン単結晶を育成することができる。

【0020】

このように、炭素をドープするシリコン単結晶の場合であれば、炭素濃度が1.3×1016atoms/cm3以上であればBMD向上効果が得られ、炭素濃度が22×1016atoms/cm3以下であればシリコン単結晶における炭素の固溶限界までは達しないので単結晶化しやすい。また、酸素濃度が8×1017atoms/cm3以上であればBMDを形成しやすく、酸素濃度が16×1017atoms/cm3以下であればBMDの個数、サイズともに良好でゲッタリング能力が向上する。

【0021】

また、前記シリコン単結晶の育成において、炭素をドープせず、酸素濃度が16×1017−24×1017atoms/cm3(ASTM’79)となるように制御してシリコン単結晶を育成することができる。

【0022】

このように、炭素をドープしないシリコン単結晶の場合でも、酸素濃度が16×1017atoms/cm3(ASTM’79)以上とすることでBMDが十分成長する。また、酸素濃度が24×1017atoms/cm3(ASTM’79)以下であれば酸素析出量が大きくなりすぎず、ウエーハの反りなど別の問題を引き起こす可能性を抑制できる。

【0023】

さらに、本発明は、CZ法により育成したシリコン単結晶から作製されたシリコンウエーハに、エピタキシャル層を成長させた撮像素子製造用のエピタキシャルウエーハであって、

前記エピタキシャル層は、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域と、前記撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域とが形成されるものであり、該酸素濃度が4×1017atoms/cm3未満の領域の厚さは6μm以上となるものであることを特徴とするエピタキシャルウエーハを提供する。

【0024】

このようなエピタキシャルウエーハであれば、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないものとなる。

【発明の効果】

【0025】

以上説明したように、本発明のエピタキシャルウエーハの製造方法であれば、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハを製造することができる。また、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXの算出も、煩雑な計算は不要であり、汎用性の高い方法で行うことができる。さらに、シリコンウエーハとして、適切な炭素濃度、酸素濃度を有するものを使用することで優れたゲッタリング能力を有するエピタキシャルウエーハを製造することができる。本発明により製造されたエピタキシャルウエーハはデジタルカメラや携帯電話などに用いられているCCDやCISといった固体撮像素子用に好適に用いることができる。

【図面の簡単な説明】

【0026】

【図1】本発明のエピタキシャルウエーハの製造方法のフロー図である。

【図2】実施例1の条件におけるエピタキシャルウエーハに熱シュミレーションを施した場合の酸素濃度の分布を示した図である。

【図3】実施例2の条件におけるエピタキシャルウエーハに熱シュミレーションを施した場合の酸素濃度の分布を示した図である。

【発明を実施するための形態】

【0027】

以下、本発明を詳細に説明するが、本発明はこれに限定されるものではない。上述のように、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハの製造方法が望まれていた。

【0028】

本発明者らは、上記問題点について鋭意検討を重ねた結果、シリコンウエーハ中の酸素等不純物の悪影響が及ぶエピタキシャル層の領域の厚さを算出し、この厚さに加えて酸素等不純物の悪影響が及ばないエピタキシャル層の領域(撮像素子形成部分)の厚さが6μm以上となる厚さで、エピタキシャル層を成長することでシリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハとなることを見出して、本発明を完成させた。

【0029】

図1に本発明のエピタキシャルウエーハの製造方法のフロー図を示す。本発明の製造方法では、CZ法によりシリコン単結晶を育成し、該シリコン単結晶からシリコンウエーハ1を作製し(図1(A))、エピタキシャル層を成長する前に、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算する(図1(B))。その後、エピタキシャル層4を、厚さXに加えて、更に撮像素子の製造後におけるエピタキシャル層4中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長し、撮像素子製造用のエピタキシャルウエーハ10を製造する(図1(C))。

【0030】

図1(D)に示すように、撮像素子を製造するプロセス中では、その熱環境によりシリコンウエーハ1からエピタキシャル層4中に酸素が拡散していく。その結果、撮像素子の製造後には、エピタキシャル層4中に拡散した酸素濃度が高い領域と低い領域が形成される。本発明では、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)以上となるシリコンウエーハに近い領域を緩衝層2’、撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)未満となるシリコンウエーハから離れた領域を有効層3’と呼ぶこととする。緩衝層2’、有効層3’はどちらも撮像素子の製造前のエピタキシャル層4のことである。本発明では、成長するエピタキシャル層4全体の厚さは、撮像素子を製造後の緩衝層2’となる領域2の厚さと有効層3’となる領域3の厚さの和である。

【0031】

例えば図1(D)で行う撮像素子製造プロセスでは、エピタキシャル層4上にP型ウェル・ゲート酸化膜5を形成し、この内にn型不純物注入部6及びp型不純物注入部7を選択的にイオン注入し、転送部とフォトダイオードを形成する。また、その上にポリシリコン電極8、受光部を除く部分に遮光膜9を形成することで、撮像素子を形成できる。

【0032】

前述のように撮像素子製造中(図1(D))にシリコンウエーハから酸素が拡散し、デバイス特性に悪影響をもたらすことが判ってきたため、本発明ではシリコンウエーハ1からの影響を排除するための緩衝層2’となる領域2の厚さを予め算出し(図1(B))、これに加えて、更に撮像素子を作製するための有効層3’となる領域3の厚さが6μm以上となる厚さで、エピタキシャル層4を成長する(図1(C))。これにより、シリコンウエーハの影響を受けない高感度で高集積度な撮像素子製造用エピタキシャルウエーハを作製することができる。

【0033】

ここで、撮像素子製造後に有効層となる領域は、撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)未満となる領域とし、その厚さとしては6μm以上必要とした。有効層に撮像素子を形成する場合には、入射光を光電変換してキャリアを発生させそれを溜めておくフォトダイオード(撮像素子)部分とその下に不要となった電荷を排出する部分が形成される。他に転送部などフォトダイオードで感じた光の強さを読み取る部分も形成される。

【0034】

先に述べたように光の進入深さは波長によって異なり、例えば光の強度が半分になる深さは青色で約0.3μm、赤色であれば3μm程度である。赤色を効率よく受光するためにはフォトダイオードの厚さが最低でも3μm程度は必要である。従って不要電荷を放出する領域も含めた撮像素子製造に必要な厚さは少なくとも4μm以上である。必要な厚さは本来撮像素子設計に関わるものであり一概に決められるものではないが、昨今の撮像素子の高感度化を鑑み本発明では有効層となる領域に必要な厚さを6μm以上とした。

【0035】

また、撮像素子製造後に緩衝層となる領域は、撮像素子の製造後においてエピタキシャル層中の酸素濃度が4×1017atoms/cm3(ASTM’79)以上となる領域とした。酸素濃度4×1017atoms/cm3(ASTM’79)で撮像素子製造後に緩衝層となる領域と有効層となる領域を分けたのは、撮像素子製造の後工程などで行われる配線やパッケージなどで低温の熱処理によって酸素ドナーが発生することが考えられるためである。酸素ドナーは酸素濃度が減れば激減する。本発明者らの実験データでは最も酸素ドナーが発生しやすい450℃で5時間の熱処理をした場合、酸素濃度が4×1017atoms/cm3(ASTM’79)の場合にはキャリアは約8×1011atoms/cm3発生し、酸素濃度8×1017atoms/cm3(ASTM’79)の場合にはキャリアは約5×1013atoms/cm3発生し、さらに酸素濃度が12×1017atoms/cm3(ASTM’79)の場合にはキャリアは約6×1014atoms/cm3発生した。これから分かるように、酸素濃度が2倍、3倍となるにつれて桁違いに酸素ドナー起因のキャリアが増加することがわかる。フォトダイオードを作製する近辺のもともとのドーパント濃度は1014〜1015程度であるから、酸素ドナー起因キャリアによる悪影響を防止するためにはこれより2桁程度酸素ドナー濃度が低いことが望まれる。従って、酸素濃度が4×1017atoms/cm3(ASTM’79)以上の部分を緩衝層となる領域とし、それを除いた部分はフォトダイオード等を作製する有効層となる領域とした。

【0036】

一般にエピタキシャル層の厚さが厚くなるとコストも高くなる。エピタキシャル層を成長させる工程ではウエーハのロード/アンドロードや前処理等の工程はあるが、最も工程の時間を律速するのはエピタキシャル層を成長させる工程である。それはエピタキシャル層の成長速度が非常に遅いためである。従ってエピタキシャル層を厚く成長させることはコストアップに直結するものである。このため必要な厚さ以上はエピタキシャル層の厚さを厚くしないのが普通である。しかし、本発明では従来必要とされてきたフォトダイオード等を作製するのに必要な厚さに加えて、シリコンウエーハからの影響を抑制するための緩衝層となる領域を設ける点が最大の特徴である。これにより、今後予想される微細化・高感度化の要求に対し、エピタキシャル層の厚さアップによるパフォーマンスの向上が期待でき、最終的にコストパフォーマンスの優れた製品を提供することが可能となる。

【0037】

また、緩衝層の厚さを以下のようにして決めることで、撮像素子製造後の酸素濃度を確認する作業を省くことができる。シリコンウエーハとエピタキシャル層との界面からエピタキシャル層側の距離、すなわち緩衝層となる領域の厚さをXとすると、熱プロセスによってシリコンウエーハからエピタキシャル層中に拡散する酸素の濃度Cは厚さXの関数として次式のように表される。なおここでerfはエラー関数(誤差関数)の略であり、拡散の濃度を求めるために一般的に用いられるものである。

C(X)=([Oi]ini+[Oi]sol(T))/2−([Oi]ini−[Oi]sol(T))/2×erf[X/{2√(D(T)t)}]

(式中、[Oi]iniはシリコンウエーハの初期酸素濃度、Tは撮像素子製造中の最も高温の熱プロセスの温度、[Oi]sol(T)は温度Tにおける酸素の固溶度、D(T)は温度Tにおける酸素の拡散係数、tは温度Tの熱プロセスの処理時間、erfはエラー関数を示す。)

【0038】

これにより求められた酸素濃度分布から、酸素濃度が4×1017atoms/cm3(ASTM’79)となる厚さ、すなわち緩衝層となる領域の厚さXとして定めることができる。

【0039】

なお、上記式では、拡散した酸素濃度を撮像素子製造中の最高温度の処理温度により計算しているが、エピタキシャル層成長時の熱処理や撮像素子製造中の他の熱処理など全ての熱処理において酸素の拡散を計算することもできる。しかしながら、それぞれの熱処理についての計算を行うと計算式が煩雑になる恐れがあり、また計算式の汎用性が損なわれる恐れがある。一方で、エピタキシャル成長は高温だが短時間であるし、撮像素子製造中の熱処理の詳細に関してはデバイスメーカーのノウハウに関わる問題であり、撮像素子を製造するに際し適宜変更されるものである。また、最近の撮像素子製造温度の全体的な低温化に伴って高温で熱処理される工程は減少してきている。さらに、酸素の拡散係数は熱処理温度が下がれば劇的に下がる。以上より、拡散した酸素濃度の算出式に、簡便性と汎用性を持たせるため、上記式では最も高温の撮像素子製造プロセスを代表して試算して、概算の緩衝層となる領域の厚さを決定することとした。

【0040】

また、本発明のエピタキシャルウエーハの製造方法においては、1層のエピタキシャル層を成長させる場合だけではなく、撮像素子構造の一部をエピタキシャル成長時に造り込む場合など2層以上の多層エピタキシャル層を成長することもできる。このような多層エピタキシャルウエーハにおいては、各々のエピタキシャル層の厚さを合計した全体のエピタキシャル層の厚さが、上述の緩衝層となる領域及び有効層となる領域の厚さを有するものであれば良い。

【0041】

多層エピタキシャル層を形成する場合は、抵抗率や導電型の異なるエピタキシャル層を多層成長させることができる。本発明はシリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層のフォトダイオード形成部分まで及ばないことを目的とするが、このように抵抗率が異なっていたとしてもエピタキシャル層中の酸素原子や炭素原子濃度はシリコンウエーハに比較すれば皆無といえるほどに低いので、どの抵抗率の層であっても緩衝層となる領域としての役割を果たすことが可能である。

【0042】

緩衝層となる領域の厚さは上述したように、撮像素子製造プロセスの設計に依存する数値ではあるが近年のプロセスではゲート酸化膜が形成される熱処理がもっとも高温のプロセスであることが多い。例えば、基板の初期酸素濃度を14.5×1017atoms/cm3(ASTM’79)、酸化膜を形成する温度と時間を1000℃、60分と想定すれば、酸素濃度が4×1017atoms/cm3以上となる深さは約2.6μmである。従って近年の撮像素子におけるおおよその緩衝層となる領域の厚さは3μm程度と見積もられる。有効層となる領域としては6μm以上必要であることから、撮像素子用のエピタキシャル層の全体の厚さの最低厚さは9μmと見積もられる。

【0043】

以上のことからエピタキシャル層の全体の厚さを9μm以上20μm以下とすることが望ましい。上限を20μmとしたのはコストがパフォーマンス以上に高くなるおそれがあるからである。将来、エピタキシャル成長技術が改善されコストが下がる方策が見つかれば、エピタキシャル層は厚ければ厚いほど良いといえる。

【0044】

本発明のエピタキシャルウエーハの製造方法では、白傷の対策もあるので従来用いられてきた炭素をドープしたシリコン単結晶の場合には、炭素濃度は1.3×1016−22×1016atoms/cm3(ASTM’74)であることが好ましい。炭素濃度が1.3×1016atoms/cm3以上であればBMD向上効果が得られ、22×1016atoms/cm3以下であればシリコン単結晶における炭素の固溶限界までは達しないので単結晶化しやすい。

【0045】

また、炭素をドープしたシリコン単結晶の酸素濃度は8×1017−16×1017atoms/cm3(ASTM’79)に制御されたものが好ましい。8×1017atoms/cm3以上であればBMDを形成しやすい。また、16×1017atoms/cm3以下であればBMDの個数、サイズともに良好でゲッタリング能力が向上する。

【0046】

さらに、炭素をドープしないシリコン単結晶の場合であれば、酸素濃度が16×1017atoms/cm3(ASTM’79)以上であればBMDが十分成長する。従って撮像素子の白傷対策用のシリコンウエーハとして、炭素をドープせずに酸素濃度16×1017atoms/cm3(ASTM’79)以上であるシリコンウエーハを用いることも有効である。また、24×1017atoms/cm3(ASTM’79)以下であれば酸素析出量が大きくなりすぎず、ウエーハの反りなど別の問題を引き起こす可能性を抑制できる。

【実施例】

【0047】

以下、本発明の実施例および比較例を挙げてさらに詳細に説明するが、本発明は下記の実施例に限定されるものではない。

【0048】

〔実施例1〕

磁場を印加したCZ法であるMCZ法を用いて、炭素濃度5.4×1016atoms/cm3(ASTM’74)、酸素濃度14.2×1017atoms/cm3(ASTM’79)の直径300mmのシリコン単結晶を育成し、これから切り出したウエーハを研磨してシリコンウエーハとした。

【0049】

このとき酸素の拡散に最も影響すると思われる熱処理がゲート酸化熱処理であり、具体的には1000℃、60分ドライ酸素雰囲気で行う予定であった。上記酸素濃度とこの熱処理条件から撮像素子製造後のエピタキシャル層の酸素濃度が4×1017atoms/cm3(ASTM’79)以上になる領域の厚さは上記式により図2に示すように2.3μmと計算される。フォトダイオード形成領域深さが6μmであったとすると、シリコンウエーハの影響を受けないために必要な厚さは8.3μmとなる。なお、ここで酸素の拡散係数D(T)はD(T)=Doexp(−Eo/kT)、Do=0.13(cm2/s)、Eo=2.53(eV)、酸素の固溶度[Oi]sol(T)は[Oi]sol(T)=[Oi]oexp(−Eoi/kT)、[Oi]o=9.00×1022(atoms/cm3)、Eoi=1.52(eV)として計算した。

【0050】

このため試算で求めた8.3μmより厚い9μmのエピタキシャル層をシリコンウエーハ上に成長し、撮像素子プロセスに投入した。エピタキシャル層はPドープn型の層を形成した。また撮像素子のプロセスの概略としては、n型エピタキシャル層にP型ウェル・ゲート酸化膜を形成し、このウェル内にn型及びp型の不純物を選択的にイオン注入し、転送部とフォトダイオードを形成する。その上にポリシリコン電極、受光部を除く部分に遮光膜を形成することで、撮像素子を形成した。

【0051】

その結果、実施例1では筋状の暗電流異常は検出されなかった。また、シリコンウエーハには光散乱法によって1×109/cm3以上の白傷の抑制には充分と思われるBMDが検出された。従って、上記の試算で求めたエピタキシャル層の厚さが8.3μm以上必要であるという結果が妥当であったことが証明されたと考えられる。

【0052】

〔比較例〕

次にシリコンウエーハは全く同じシリコン単結晶(結晶炭素濃度5.4×1016atoms/cm3(ASTM’74)、酸素濃度14.2×1017atoms/cm3(ASTM’79))から切り出したものを用い、エピタキシャル層の厚さを上記の試算で求めた8.3μmより薄い6μmとしたこと以外は実施例1と全く同じエピタキシャルウエーハを作製した。このウエーハを実施例1と同じ撮像素子プロセスに投入した。

【0053】

その結果、出来上がった撮像素子には実施例1では見られなかった筋状の暗電流異常が検出された。一方でシリコンウエーハには光散乱法によって1×109/cm3以上の白傷の抑制には充分と思われるBMDが検出された。これをX線トポグラフ及び光散乱法にてウエーハ面内観察すると、X線では回折強度の濃淡として、光散乱法ではBMD密度の多寡として、同心円状のストリエーションパターン(縞状の分)が観察された。これら縞状分布と筋状の暗電流不良パターンを比較すると類似性が高いことがわかった。従って、ストリエーション起因で不良を発生させてしまったことが考えられる。

【0054】

実施例1の試算結果からシリコンウエーハの影響を受けないために必要な厚さは8.3μmとなる。このため6μmのエピタキシャル層の厚さでは問題が発生したものと考えられる。

【0055】

また、比較例と実施例1で用いたエピタキシャルウエーハに撮像素子製造プロセスを模した熱シミュレーションを施した。それらのウエーハをSIMS(Secondary Ion−microprobe Mass Spectrometer)を用いて、表面から深さ方向に酸素濃度の分布を測定した。その結果、比較例で用いたウエーハでは表面から奥に行くにしたがって徐々に酸素濃度が高くなり、表面から3.7μm(シリコンウエーハ−エピタキシャル層界面から2.3μm)のところで酸素濃度4×1017atoms/cm3(ASTM’79)となった。一方で実施例1に用いたウエーハの場合、図2に示すように同様に表面から奥に行くにしたがって徐々に酸素濃度が高くなっていき、深さ約6.5μm(シリコンウエーハ−エピタキシャル層界面から2.5μm)のところで酸素濃度4×1017atoms/cm3(ASTM’79)となった。

【0056】

以上のことから、有効層として必要な深さがおおよそ6μmであること、充分な緩衝層を有するべきであること、有効層として機能するにはその酸素濃度が4×1017atoms/cm3(ASTM’79)以下であることが必要であることが確認できた。

【0057】

〔実施例2〕

比較例と実施例1で用いたシリコンウエーハとは異なり、炭素をドープせず、酸素濃度を17×1017atoms/cm3(ASTM’79)と高くして育成したシリコン単結晶からシリコンウエーハを形成した。この酸素濃度の異なるシリコンウエーハを用いて、撮像素子製造プロセスを模した熱シミュレーションを施した後に酸素濃度分布を測定し、有効層の厚さが充分取れるかの確認実験を行う。このとき撮像素子製造プロセスの条件変更を想定して、実施例1で用いた熱シミュレーションのうち酸化膜形成熱処理を1000℃、30分と半分の時間に設定した。

【0058】

この酸素濃度及び熱処理条件から計算されるエピタキシャル層中の酸素濃度は図3のようになり、酸素濃度4×1017atoms/cm3(ASTM’79)を満たす厚さは1.9μmと試算された。そこでこの炭素ドープしていない高酸素濃度シリコンウエーハに有効層として6μm以上が取れると予測される厚さ8μmのエピタキシャル層を成長させた。その後、酸化膜形成熱処理を1000℃、30分としたデバイスシミュレーション熱処理を施した。

【0059】

このウエーハをSIMS(Secondary Ion−microprobe Mass Spectrometer)を用いて、表面から深さ方向に酸素濃度の分布を測定した。表面から奥に行くにしたがって徐々に酸素濃度が高くなり、表面から6.2μm(シリコンウエーハ−エピタキシャル層界面から1.8μm)のところで酸素濃度4×1017atoms/cm3(ASTM’79)となった。つまり、計算した予想どおりフォトダイオード形成に必要な有効層の厚さ6μmを確保できていた。またシリコンウエーハ中には光散乱法によって1×109/cm3以上の白傷の抑制には充分と思われるBMDが検出された。

【0060】

以上のように、事前に撮像素子製造プロセスの熱処理条件とシリコンウエーハの酸素濃度とがわかっていれば、本発明の製造方法を用いて有効層の厚さを確保するためのエピタキシャル層の厚さを事前に予想してエピタキシャル層を成長させることができ、これによってシリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハを製造でき、不良率を低減することが可能である。

【0061】

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は、例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

【符号の説明】

【0062】

1…シリコンウエーハ、 2…緩衝層となる領域、 2’…緩衝層、 3…有効層となる領域、 3’…有効層、 4…エピタキシャル層、 5…P型ウェル・ゲート酸化膜、 6…n型不純物注入部、 7…p型不純物注入部、 8…ポリシリコン電極、 9…遮光膜、 10…エピタキシャルウエーハ

【特許請求の範囲】

【請求項1】

CZ法によりシリコン単結晶を育成し、該シリコン単結晶からシリコンウエーハを作製し、該シリコンウエーハ上にエピタキシャル層を成長することで撮像素子製造用のエピタキシャルウエーハを製造する方法であって、

前記エピタキシャル層の成長前に、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、

前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

【請求項2】

前記エピタキシャル層の成長前に、前記厚さXを下記式により計算することを特徴とする請求項1に記載のエピタキシャルウエーハの製造方法。

4×1017=([Oi]ini+[Oi]sol(T))/2−([Oi]ini−[Oi]sol(T))/2×erf[X/{2√(D(T)t)}]

(式中、[Oi]iniは前記シリコンウエーハの初期酸素濃度、Tは前記撮像素子製造中の最も高温の熱プロセスの温度、[Oi]sol(T)は前記温度Tにおける酸素の固溶度、D(T)は前記温度Tにおける酸素の拡散係数、tは前記温度Tの熱プロセスの処理時間、erfはエラー関数を示す。)

【請求項3】

前記エピタキシャル層の成長において、前記エピタキシャル層として多層エピタキシャル層を成長することを特徴とする請求項1又は請求項2に記載のエピタキシャルウエーハの製造方法。

【請求項4】

前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さであって、該エピタキシャル層全体の厚さが9μm以上20μm以下となる厚さで成長することを特徴とする請求項1乃至請求項3のいずれか1項に記載のエピタキシャルウエーハの製造方法。

【請求項5】

前記シリコン単結晶の育成において、炭素濃度が1.3×1016−22×1016atoms/cm3(ASTM’74)となるように炭素をドープし、酸素濃度が8×1017−16×1017atoms/cm3(ASTM’79)となるように制御して前記シリコン単結晶を育成することを特徴とする請求項1乃至請求項4のいずれか1項に記載のエピタキシャルウエーハの製造方法。

【請求項6】

前記シリコン単結晶の育成において、炭素をドープせず、酸素濃度が16×1017−24×1017atoms/cm3(ASTM’79)となるように制御して前記シリコン単結晶を育成することを特徴とする請求項1乃至請求項4のいずれか1項に記載のエピタキシャルウエーハの製造方法。

【請求項7】

CZ法により育成したシリコン単結晶から作製されたシリコンウエーハに、エピタキシャル層を成長させた撮像素子製造用のエピタキシャルウエーハであって、

前記エピタキシャル層は、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域と、前記撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域とが形成されるものであり、該酸素濃度が4×1017atoms/cm3未満の領域の厚さは6μm以上となるものであることを特徴とするエピタキシャルウエーハ。

【請求項1】

CZ法によりシリコン単結晶を育成し、該シリコン単結晶からシリコンウエーハを作製し、該シリコンウエーハ上にエピタキシャル層を成長することで撮像素子製造用のエピタキシャルウエーハを製造する方法であって、

前記エピタキシャル層の成長前に、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、

前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

【請求項2】

前記エピタキシャル層の成長前に、前記厚さXを下記式により計算することを特徴とする請求項1に記載のエピタキシャルウエーハの製造方法。

4×1017=([Oi]ini+[Oi]sol(T))/2−([Oi]ini−[Oi]sol(T))/2×erf[X/{2√(D(T)t)}]

(式中、[Oi]iniは前記シリコンウエーハの初期酸素濃度、Tは前記撮像素子製造中の最も高温の熱プロセスの温度、[Oi]sol(T)は前記温度Tにおける酸素の固溶度、D(T)は前記温度Tにおける酸素の拡散係数、tは前記温度Tの熱プロセスの処理時間、erfはエラー関数を示す。)

【請求項3】

前記エピタキシャル層の成長において、前記エピタキシャル層として多層エピタキシャル層を成長することを特徴とする請求項1又は請求項2に記載のエピタキシャルウエーハの製造方法。

【請求項4】

前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さであって、該エピタキシャル層全体の厚さが9μm以上20μm以下となる厚さで成長することを特徴とする請求項1乃至請求項3のいずれか1項に記載のエピタキシャルウエーハの製造方法。

【請求項5】

前記シリコン単結晶の育成において、炭素濃度が1.3×1016−22×1016atoms/cm3(ASTM’74)となるように炭素をドープし、酸素濃度が8×1017−16×1017atoms/cm3(ASTM’79)となるように制御して前記シリコン単結晶を育成することを特徴とする請求項1乃至請求項4のいずれか1項に記載のエピタキシャルウエーハの製造方法。

【請求項6】

前記シリコン単結晶の育成において、炭素をドープせず、酸素濃度が16×1017−24×1017atoms/cm3(ASTM’79)となるように制御して前記シリコン単結晶を育成することを特徴とする請求項1乃至請求項4のいずれか1項に記載のエピタキシャルウエーハの製造方法。

【請求項7】

CZ法により育成したシリコン単結晶から作製されたシリコンウエーハに、エピタキシャル層を成長させた撮像素子製造用のエピタキシャルウエーハであって、

前記エピタキシャル層は、前記撮像素子の製造において前記シリコンウエーハから前記エピタキシャル層に酸素が拡散することで、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域と、前記撮像素子の製造後にエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域とが形成されるものであり、該酸素濃度が4×1017atoms/cm3未満の領域の厚さは6μm以上となるものであることを特徴とするエピタキシャルウエーハ。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−89858(P2013−89858A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−230781(P2011−230781)

【出願日】平成23年10月20日(2011.10.20)

【出願人】(000190149)信越半導体株式会社 (867)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月20日(2011.10.20)

【出願人】(000190149)信越半導体株式会社 (867)

【Fターム(参考)】

[ Back to top ]