エンコーダ通信回路

【課題】平衡形ラインドライバ出力方式のシリアル信号を互いに送受信するエンコーダと制御装置とにおいて、該制御装置に好適なエンコーダ通信回路を提供する。

【解決手段】エンコーダ1および制御装置6が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、エンコーダ1は通信プロトコルとしての受信待ち状態が論理Hレベルで製作されていることから、先ず、MPU31の処理動作により、MPU31のOut1端子から論理Hを出力し、Out2端子から論理Lを出力し、その後は、MPU31のOut1端子は論理Hの状態、Out2端子は論理Lの状態をそれぞれ継続しつつ、エンコーダ1と制御装置6との間は通常の通信状態に入るようにする。

【解決手段】エンコーダ1および制御装置6が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、エンコーダ1は通信プロトコルとしての受信待ち状態が論理Hレベルで製作されていることから、先ず、MPU31の処理動作により、MPU31のOut1端子から論理Hを出力し、Out2端子から論理Lを出力し、その後は、MPU31のOut1端子は論理Hの状態、Out2端子は論理Lの状態をそれぞれ継続しつつ、エンコーダ1と制御装置6との間は通常の通信状態に入るようにする。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、平衡形ラインドライバ出力方式のシリアル信号を互いに送受信するエンコーダと制御装置とに関し、特に、前記制御装置に設けられた入力抵抗部と差動形バストランシーバとから形成されるエンコーダ通信回路に関する。

【背景技術】

【0002】

この種のエンコーダは、例えば、産業機械設備の動力源としての電動機の出力軸に連結され、この電動機の出力軸の位置情報を制御装置としての前記電動機の可変速駆動装置に伝達する用途に供されるものである。このとき、前記エンコーダを製作するメーカと前記電動機および制御装置を製作するメーカとは、互いに異なるメーカであることが多く、また、前記電動機および制御装置を製作するメーカと前記産業設備を製作するメーカとは、互いに異なるメーカであることが多い。

【0003】

このような用途のエンコーダに関しては、下記特許文献1,2などに記載されているように、エンコーダの出力信号は、エンコーダの客先回路である前記制御装置からの要求に従ったフォーマットでシリアル信号を出力することが行われていた。

【0004】

一方、前記電動機および制御装置を製作するメーカにおいては、客先としての前記産業設備を製作するメーカから、複数のメーカの異なった仕様のエンコーダに対応できるものが要求される場合があった。

【0005】

図6,7は、上述の場合の従来例としてのエンコーダおよび制御装置の部分回路構成図である。

【0006】

図6において、1はエンコーダ、4はサーボアンプ等の制御装置、3はエンコーダ1と制御装置4との間のシリアル信号を伝送するためのケーブルである。

【0007】

図6に示したエンコーダ1の部分回路構成図には、平衡形ラインドライバ出力方式のシリアル信号を送受信するための差動形バストランシーバ11と、この差動形バストランシーバ11の入力抵抗部を形成する抵抗12〜14とが示されており、抵抗12はプルアップ抵抗、抵抗13は終端抵抗、抵抗14はプルダウン抵抗と称されるものである。

【0008】

同様に、図6に示した制御装置4の部分回路構成図には、この制御装置4での制御動作を司るマイクロプロッセシングユニット21(以下、MPU21とも称する)と、MPU21からのパラレル信号とエンコーダ1からのシリアル信号とを互いに変換するSP変換機能とその周辺回路とを一体化した特定用途集積回路22(以下、ASIC22とも称する)と、平衡形ラインドライバ出力方式のシリアル信号を送受信するための差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗24〜26とが示されており、抵抗24はプルアップ抵抗、抵抗25は終端抵抗、抵抗26はプルダウン抵抗と称されるものである。

【0009】

また図7において、2はエンコーダ、5は制御装置、3はエンコーダ2と制御装置5との間のシリアル信号を伝送するためのケーブルであり、この図において、図6に示した回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0010】

すなわち図7に示したエンコーダ2の部分回路構成図には、差動形バストランシーバ11と、この差動形バストランシーバ11の入力抵抗部を形成する抵抗13,15,16とが示されており、抵抗15はプルアップ抵抗、抵抗16はプルダウン抵抗と称されるものである。

【0011】

同様に、図7に示した制御装置5の部分回路構成図には、この制御装置5での制御動作を司るMPU21と、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,27,28とが示されており、抵抗27はプルアップ抵抗、抵抗28はプルダウン抵抗と称されるものである。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開平11−304536号公報

【特許文献2】特開2008−40582号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

通信プロトコルの違いの中には、制御装置とエンコーダの通信停止状態のときの信号論理が異なるものがある。上述の図6に示した回路構成と図7の示した回路構成とが異なっているのは、エンコーダ1は通信プロトコルとしての受信待ち状態が論理Hレベルで製作され、また、エンコーダ2は通信プロトコルとしての受信待ち状態が論理Lレベルで製作されていることに対応するためである。

【0014】

すなわち、図6で示すエンコーダ1は、差動の通信信号の非反転信号がプルアップ抵抗12により電源Vccにプルアップされ、反転信号がプルダウン抵抗14によりGNDにプルダウンされている。この結果、エンコーダ1は、通信停止状態で終端抵抗13の両端電圧、すなわち、差動信号の通信信号線間には正の電圧が現れ、差動形バストランシーバ11のレシーバ出力は論理Hレベルとなる。また、図7で示すエンコーダ2は、差動の通信信号の反転信号がプルアップ抵抗15により電源Vccにプルアップされ、非反転信号がプルダウン抵抗16によりGNDにプルダウンされている。この結果、エンコーダ2は、通信停止状態で終端抵抗13の両端電圧、すなわち、差動信号の通信信号線間には負の電圧が現れ、差動形バストランシーバ11のレシーバ出力は論理Lレベルとなる。

【0015】

このように通信プロトコルの異なるエンコーダ1,2が存在することから、各々に対応した制御装置が必要となる。このため、図6に示した制御装置4と図7に示した制御装置5とにおいて、前記入力抵抗部の破線で示す未実装の抵抗は、制御装置4,5それぞれのプリント配線基板上に予め設置スペースとプリントパターンとが設けてあり、上述のエンコーダ1,2の通信プロトコルの違いに対応できるようにしている。

【0016】

しかしながら、上述の対応策では前記プリント配線基板上に余分な実装スペースが必要であり、このことが制御装置の小型化を阻害し、また、前記プリント配線基板上の部品配置の最適化を阻害する要因となっていた。さらに、上述のエンコーダの通信プロトコルが現地(客先)でしか確認できない場合には、前記入力抵抗部の抵抗のうち、少なくともプルアップ抵抗、プルダウン抵抗の実装作業を現地で行うことになり、この制御装置の動作信頼性を損なう恐れがあるという問題点もあった。

【0017】

この発明の目的は、上記問題点を解消したエンコーダ通信回路を提供することにある。

【課題を解決するための手段】

【0018】

この第1の発明は、平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、前記エンコーダおよび制御装置が互いに受信待ち状態、すなわち双方が送受信停止状態のときの前記エンコーダが出力する論理レベルに基づいて、前記入力抵抗部の両端に印加する直流電圧極性を決定するようにしたことを特徴とする。

【0019】

また、第2の発明は平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、前記エンコーダおよび制御装置が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、前記入力抵抗部の両端をそれぞれハイインピーダンス状態にしたときの前記エンコーダが出力している論理レベルを前記差動形バストランシーバの受信出力値から判別し、この判別した論理レベルにより前記入力抵抗部の両端の直流電圧極性を決定して印加するようにしたことを特徴とする。

【発明の効果】

【0020】

この第1の発明によれば、制御装置におけるエンコーダ通信回路は、そのハードウェア構成を同一にすることができ、さらに、第2の発明によれば、上記の効果に加えて、使用するエンコーダの受信待ち状態での論理値の違いも自動的に判別しつつ、そのエンコーダを用いることができる。

【図面の簡単な説明】

【0021】

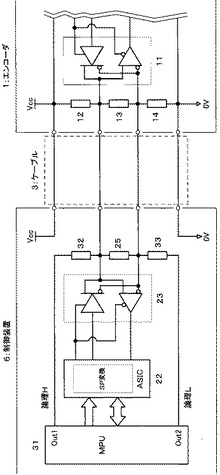

【図1】この発明の第1の実施例を示す回路構成図

【図2】この発明の第2の実施例を示す回路構成図

【図3】この発明の第3の実施例を示す回路構成図

【図4】この発明の第4の実施例を示す回路構成図

【図5】図3,4の動作を説明するフローチャート

【図6】従来例を示す回路構成図

【図7】図6とは別の従来例を示す回路構成図

【発明を実施するための形態】

【0022】

図1は、この発明の第1の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図6に示した従来例の回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0023】

すなわち図1に示した制御装置6の部分回路構成図には、この制御装置6での制御動作を司るMPU31と、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。サーボアンプ等の制御装置6は、シリアル通信によってエンコーダ1に対してデータ要求信号を送信し、このデータ要求信号によりエンコーダ1から送信された位置情報信号を受信することによって、受信した位置情報に基づいた制御動作を行っている。

【0024】

差動信号の通信信号線間に終端抵抗25が接続されるとともに、2本の通信信号線にはそれぞれ抵抗32および抵抗33の一方の端子が接続される。MPU31にはデジタル信号を出力するデジタル出力端子Out1,Out2が設けられ、デジタル出力端子Out1は抵抗32の他方の端子が接続されるとともに、デジタル出力端子Out2は抵抗33の他方の端子が接続される。MPU31のデジタル出力端子は、論理Hを出力することによって電源電圧Vccとほぼ等しい電圧を出力し、逆に、論理Lを出力することによってGNDとほぼ等しい電圧を出力することによって、入力抵抗部(抵抗25,32,33)の両端に印加する直流電圧極性を決定する。

【0025】

この制御装置6では、通信プロトコルとしての受信待ち状態が論理Hレベルで製作されていることが前以て確認されているエンコーダ1が接続された場合、エンコーダ1と制御装置6とに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち送受信停止状態のときに、先ず、MPU31の処理動作により、差動の非反転信号側の通信信号線に抵抗32を介して接続されているMPU31のOut1端子から論理Hを出力し、差動の反転信号の通信信号線に抵抗33を介して接続されているOut2端子から論理Lを出力する。その結果、抵抗32がプルアップ抵抗の機能を行い、抵抗33がプルダウン抵抗の機能を行うようにしている。

【0026】

その後は、MPU31のOut1端子は論理Hの状態、Out2端子は論理Lの状態をそれぞれ継続することにより、エンコーダ1と制御装置6との間は通常の通信状態に入ることができる。

【0027】

図2は、この発明の第2の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図1および図7に示した回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0028】

すなわち図2に示した制御装置6aの部分回路構成図には、この制御装置6aでの制御動作を司るMPU31aと、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。MPU31aにはデジタル出力端子Out1,Out2が設けられ、デジタル出力端子Out1は抵抗32を介して一方の通信信号線に接続されるとともに、デジタル出力端子Out2は抵抗33を介して他方の通信信号線に接続されている。

【0029】

この制御装置6aでは、通信プロトコルとしての受信待ち状態が論理Lレベルで製作されていることが前以て確認されているエンコーダ2が接続された場合、エンコーダ2と制御装置6aとに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち送受信停止状態のときに、先ず、MPU31aの処理動作により、差動の通信信号の非反転信号に抵抗32を介して接続されているMPU31aのOut1端子から論理Lを出力し、差動の通信信号の反転信号に抵抗33を介して接続されているOut2端子から論理Hを出力する。その結果、抵抗33がプルアップ抵抗の機能を行い、抵抗32がプルダウン抵抗の機能を行うようにしている。

【0030】

その後は、MPU31aのOut1端子は論理Lの状態、Out2端子は論理Hの状態をそれぞれ継続することにより、エンコーダ2と制御装置6aとの間は通常の通信状態に入ることができる。

【0031】

なお、この発明では平衡形ラインドライバ出力方式のシリアル信号であることから、抵抗32と抵抗33とは同一抵抗値に設定している。また、このプルアップ抵抗とプルダウン抵抗とは前記シリアル信号に重畳するノイズ成分を抑制するために設置される。

【0032】

また、図1と図2に示した回路構成図から明らかなように、この発明の制御装置6,6aにおけるエンコーダ通信回路は、そのハードウェア構成を同一にすることができ、さらに、客先(現地)でのプルアップ抵抗、プルダウン抵抗の実装作業が不要である。

【0033】

図3は、この発明の第3の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図1に示した実施例の回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0034】

すなわち図3に示した制御装置7の部分回路構成図には、この制御装置7での制御動作を司るMPU34と、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。制御装置7は、シリアル通信によってエンコーダ1に対してデータ要求信号を送信し、このデータ要求信号によりエンコーダ1から送信された位置情報信号を受信することによって、受信した位置情報に基づいた制御動作を行っている。図1に示したものとは、MPU34の出力端子をスリーステート出力としてハイインピーダンス状態を取りうるようにした点と、差動形バストランシーバ23の受信出力をMPU34の入力端子In1に入力している点で相違している。

【0035】

この制御装置7での動作を、図5に示したフローチャートを参照しつつ、以下に説明する。なお、このフローチャートでは、エンコーダ1の通信プロトコルとしての受信待ち状態での論理状態は不明として、処理動作を行っている。

【0036】

先ず、エンコーダ1と制御装置7とに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、MPU34の処理動作により、該MPUのOut1端子とOut2端子とをハイインピーダンス状態に設定する(図5、ステップS1)。

【0037】

この状態でのMPU34のIn1端子の状態、すなわち、差動形バストランシーバ23の受信出力値をMPU34が読込み(図5、ステップS2)、その論理値を判別する(図5、ステップS3)。

【0038】

その結果、エンコーダ1はその通信プロトコルとしての受信待ち状態が論理Hレベルで製作されていることが確認されたので、図5のステップS4に移る。

【0039】

このステップS4では、MPU34のOut1端子とOut2端子とをハイインピーダンス状態から、MPU34の処理動作により、MPU34のOut1端子を論理Hに、Out2端子を論理Lに設定する。

【0040】

その結果、抵抗32がプルアップ抵抗の機能をし、抵抗33がプルダウン抵抗の機能をするので、その後は、MPU34のOut1端子は論理Hの状態、Out2端子は論理Lの状態をそれぞれ継続することにより、エンコーダ1と制御装置7との間は通常の通信状態に入ることができる。

【0041】

図4は、この発明の第4の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図2に示した実施例の回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0042】

すなわち図4に示した制御装置7aの部分回路構成図には、この制御装置7aでの制御動作を司るMPU34aと、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。図3と同様に、図2に示したものとは、MPU34aの出力端子をスリーステート出力としてハイインピーダンス状態を取りうるようにした点と、差動形バストランシーバ23の受信出力をMPU34aの入力端子In1に入力している点で相違している。

【0043】

この制御装置7aでの動作を、図5に示したフローチャートを参照しつつ、以下に説明する。なお、このフローチャートでは、エンコーダ2の通信プロトコルとしての受信待ち状態での論理状態は不明として、処理動作を行っている。

【0044】

先ず、エンコーダ1と制御装置7aとに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、MPU34aの処理動作により、MPU34aのOut1端子とOut2端子とをハイインピーダンス状態に設定する(図5、ステップS1)。

【0045】

この状態でのMPU34aのIn1端子の状態、すなわち、差動形バストランシーバ23の受信出力値をMPU34aが読込み(図5、ステップS2)、その論理値を判別する(図5、ステップS3)。

【0046】

その結果、エンコーダ2はその通信プロトコルとしての受信待ち状態が論理Lレベルで製作されていることが確認されたので、図5のステップS5に移る。

【0047】

このステップS5では、MPU34aのOut1端子とOut2端子とをハイインピーダンス状態から、MPU34aの処理動作により、MPU34aのOut1端子を論理Lに、Out2端子を論理Hに設定する。

【0048】

その結果、抵抗33がプルアップ抵抗の機能をし、抵抗32がプルダウン抵抗の機能をするので、その後は、MPU34aのOut1端子は論理Lの状態、Out2端子は論理Hの状態をそれぞれ継続することにより、エンコーダ2と制御装置7aとの間は通常の通信状態に入ることができる。

【0049】

図3と図4に示した回路構成図から明らかなように、この発明の制御装置7,7aにおけるエンコーダ通信回路は、そのハードウェア構成を同一にすることができ、さらに、使用するエンコーダの受信待ち状態での論理値の違いも自動的に判別しつつ、そのエンコーダを用いることができる。

【0050】

なお、図1〜4に示したMPU31,31a、34,34aそれぞれのOut1端子およびOut2端子の駆動能力が小さい場合、若しくは上記それぞれのMPUの電源電圧が通常5ボルトに設定される図示のVccの電圧値より低い場合には、それぞれのMPUのOut1端子と抵抗32との接続径路およびOut2端子と抵抗33との接続径路に市販のバッファ素子を挿設することにより、プルアップ抵抗およびプルダウン抵抗の機能を確実に行わせることができる。

【符号の説明】

【0051】

1,2…エンコーダ、3…ケーブル、4〜7,6a,7a…制御装置、11…差動形バストランシーバ、12〜16…抵抗、21,31,31a,34,34a…MPU、22…ASIC,23…差動形バストランシーバ、24〜28,32,33…抵抗。

【技術分野】

【0001】

この発明は、平衡形ラインドライバ出力方式のシリアル信号を互いに送受信するエンコーダと制御装置とに関し、特に、前記制御装置に設けられた入力抵抗部と差動形バストランシーバとから形成されるエンコーダ通信回路に関する。

【背景技術】

【0002】

この種のエンコーダは、例えば、産業機械設備の動力源としての電動機の出力軸に連結され、この電動機の出力軸の位置情報を制御装置としての前記電動機の可変速駆動装置に伝達する用途に供されるものである。このとき、前記エンコーダを製作するメーカと前記電動機および制御装置を製作するメーカとは、互いに異なるメーカであることが多く、また、前記電動機および制御装置を製作するメーカと前記産業設備を製作するメーカとは、互いに異なるメーカであることが多い。

【0003】

このような用途のエンコーダに関しては、下記特許文献1,2などに記載されているように、エンコーダの出力信号は、エンコーダの客先回路である前記制御装置からの要求に従ったフォーマットでシリアル信号を出力することが行われていた。

【0004】

一方、前記電動機および制御装置を製作するメーカにおいては、客先としての前記産業設備を製作するメーカから、複数のメーカの異なった仕様のエンコーダに対応できるものが要求される場合があった。

【0005】

図6,7は、上述の場合の従来例としてのエンコーダおよび制御装置の部分回路構成図である。

【0006】

図6において、1はエンコーダ、4はサーボアンプ等の制御装置、3はエンコーダ1と制御装置4との間のシリアル信号を伝送するためのケーブルである。

【0007】

図6に示したエンコーダ1の部分回路構成図には、平衡形ラインドライバ出力方式のシリアル信号を送受信するための差動形バストランシーバ11と、この差動形バストランシーバ11の入力抵抗部を形成する抵抗12〜14とが示されており、抵抗12はプルアップ抵抗、抵抗13は終端抵抗、抵抗14はプルダウン抵抗と称されるものである。

【0008】

同様に、図6に示した制御装置4の部分回路構成図には、この制御装置4での制御動作を司るマイクロプロッセシングユニット21(以下、MPU21とも称する)と、MPU21からのパラレル信号とエンコーダ1からのシリアル信号とを互いに変換するSP変換機能とその周辺回路とを一体化した特定用途集積回路22(以下、ASIC22とも称する)と、平衡形ラインドライバ出力方式のシリアル信号を送受信するための差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗24〜26とが示されており、抵抗24はプルアップ抵抗、抵抗25は終端抵抗、抵抗26はプルダウン抵抗と称されるものである。

【0009】

また図7において、2はエンコーダ、5は制御装置、3はエンコーダ2と制御装置5との間のシリアル信号を伝送するためのケーブルであり、この図において、図6に示した回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0010】

すなわち図7に示したエンコーダ2の部分回路構成図には、差動形バストランシーバ11と、この差動形バストランシーバ11の入力抵抗部を形成する抵抗13,15,16とが示されており、抵抗15はプルアップ抵抗、抵抗16はプルダウン抵抗と称されるものである。

【0011】

同様に、図7に示した制御装置5の部分回路構成図には、この制御装置5での制御動作を司るMPU21と、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,27,28とが示されており、抵抗27はプルアップ抵抗、抵抗28はプルダウン抵抗と称されるものである。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開平11−304536号公報

【特許文献2】特開2008−40582号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

通信プロトコルの違いの中には、制御装置とエンコーダの通信停止状態のときの信号論理が異なるものがある。上述の図6に示した回路構成と図7の示した回路構成とが異なっているのは、エンコーダ1は通信プロトコルとしての受信待ち状態が論理Hレベルで製作され、また、エンコーダ2は通信プロトコルとしての受信待ち状態が論理Lレベルで製作されていることに対応するためである。

【0014】

すなわち、図6で示すエンコーダ1は、差動の通信信号の非反転信号がプルアップ抵抗12により電源Vccにプルアップされ、反転信号がプルダウン抵抗14によりGNDにプルダウンされている。この結果、エンコーダ1は、通信停止状態で終端抵抗13の両端電圧、すなわち、差動信号の通信信号線間には正の電圧が現れ、差動形バストランシーバ11のレシーバ出力は論理Hレベルとなる。また、図7で示すエンコーダ2は、差動の通信信号の反転信号がプルアップ抵抗15により電源Vccにプルアップされ、非反転信号がプルダウン抵抗16によりGNDにプルダウンされている。この結果、エンコーダ2は、通信停止状態で終端抵抗13の両端電圧、すなわち、差動信号の通信信号線間には負の電圧が現れ、差動形バストランシーバ11のレシーバ出力は論理Lレベルとなる。

【0015】

このように通信プロトコルの異なるエンコーダ1,2が存在することから、各々に対応した制御装置が必要となる。このため、図6に示した制御装置4と図7に示した制御装置5とにおいて、前記入力抵抗部の破線で示す未実装の抵抗は、制御装置4,5それぞれのプリント配線基板上に予め設置スペースとプリントパターンとが設けてあり、上述のエンコーダ1,2の通信プロトコルの違いに対応できるようにしている。

【0016】

しかしながら、上述の対応策では前記プリント配線基板上に余分な実装スペースが必要であり、このことが制御装置の小型化を阻害し、また、前記プリント配線基板上の部品配置の最適化を阻害する要因となっていた。さらに、上述のエンコーダの通信プロトコルが現地(客先)でしか確認できない場合には、前記入力抵抗部の抵抗のうち、少なくともプルアップ抵抗、プルダウン抵抗の実装作業を現地で行うことになり、この制御装置の動作信頼性を損なう恐れがあるという問題点もあった。

【0017】

この発明の目的は、上記問題点を解消したエンコーダ通信回路を提供することにある。

【課題を解決するための手段】

【0018】

この第1の発明は、平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、前記エンコーダおよび制御装置が互いに受信待ち状態、すなわち双方が送受信停止状態のときの前記エンコーダが出力する論理レベルに基づいて、前記入力抵抗部の両端に印加する直流電圧極性を決定するようにしたことを特徴とする。

【0019】

また、第2の発明は平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、前記エンコーダおよび制御装置が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、前記入力抵抗部の両端をそれぞれハイインピーダンス状態にしたときの前記エンコーダが出力している論理レベルを前記差動形バストランシーバの受信出力値から判別し、この判別した論理レベルにより前記入力抵抗部の両端の直流電圧極性を決定して印加するようにしたことを特徴とする。

【発明の効果】

【0020】

この第1の発明によれば、制御装置におけるエンコーダ通信回路は、そのハードウェア構成を同一にすることができ、さらに、第2の発明によれば、上記の効果に加えて、使用するエンコーダの受信待ち状態での論理値の違いも自動的に判別しつつ、そのエンコーダを用いることができる。

【図面の簡単な説明】

【0021】

【図1】この発明の第1の実施例を示す回路構成図

【図2】この発明の第2の実施例を示す回路構成図

【図3】この発明の第3の実施例を示す回路構成図

【図4】この発明の第4の実施例を示す回路構成図

【図5】図3,4の動作を説明するフローチャート

【図6】従来例を示す回路構成図

【図7】図6とは別の従来例を示す回路構成図

【発明を実施するための形態】

【0022】

図1は、この発明の第1の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図6に示した従来例の回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0023】

すなわち図1に示した制御装置6の部分回路構成図には、この制御装置6での制御動作を司るMPU31と、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。サーボアンプ等の制御装置6は、シリアル通信によってエンコーダ1に対してデータ要求信号を送信し、このデータ要求信号によりエンコーダ1から送信された位置情報信号を受信することによって、受信した位置情報に基づいた制御動作を行っている。

【0024】

差動信号の通信信号線間に終端抵抗25が接続されるとともに、2本の通信信号線にはそれぞれ抵抗32および抵抗33の一方の端子が接続される。MPU31にはデジタル信号を出力するデジタル出力端子Out1,Out2が設けられ、デジタル出力端子Out1は抵抗32の他方の端子が接続されるとともに、デジタル出力端子Out2は抵抗33の他方の端子が接続される。MPU31のデジタル出力端子は、論理Hを出力することによって電源電圧Vccとほぼ等しい電圧を出力し、逆に、論理Lを出力することによってGNDとほぼ等しい電圧を出力することによって、入力抵抗部(抵抗25,32,33)の両端に印加する直流電圧極性を決定する。

【0025】

この制御装置6では、通信プロトコルとしての受信待ち状態が論理Hレベルで製作されていることが前以て確認されているエンコーダ1が接続された場合、エンコーダ1と制御装置6とに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち送受信停止状態のときに、先ず、MPU31の処理動作により、差動の非反転信号側の通信信号線に抵抗32を介して接続されているMPU31のOut1端子から論理Hを出力し、差動の反転信号の通信信号線に抵抗33を介して接続されているOut2端子から論理Lを出力する。その結果、抵抗32がプルアップ抵抗の機能を行い、抵抗33がプルダウン抵抗の機能を行うようにしている。

【0026】

その後は、MPU31のOut1端子は論理Hの状態、Out2端子は論理Lの状態をそれぞれ継続することにより、エンコーダ1と制御装置6との間は通常の通信状態に入ることができる。

【0027】

図2は、この発明の第2の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図1および図7に示した回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0028】

すなわち図2に示した制御装置6aの部分回路構成図には、この制御装置6aでの制御動作を司るMPU31aと、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。MPU31aにはデジタル出力端子Out1,Out2が設けられ、デジタル出力端子Out1は抵抗32を介して一方の通信信号線に接続されるとともに、デジタル出力端子Out2は抵抗33を介して他方の通信信号線に接続されている。

【0029】

この制御装置6aでは、通信プロトコルとしての受信待ち状態が論理Lレベルで製作されていることが前以て確認されているエンコーダ2が接続された場合、エンコーダ2と制御装置6aとに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち送受信停止状態のときに、先ず、MPU31aの処理動作により、差動の通信信号の非反転信号に抵抗32を介して接続されているMPU31aのOut1端子から論理Lを出力し、差動の通信信号の反転信号に抵抗33を介して接続されているOut2端子から論理Hを出力する。その結果、抵抗33がプルアップ抵抗の機能を行い、抵抗32がプルダウン抵抗の機能を行うようにしている。

【0030】

その後は、MPU31aのOut1端子は論理Lの状態、Out2端子は論理Hの状態をそれぞれ継続することにより、エンコーダ2と制御装置6aとの間は通常の通信状態に入ることができる。

【0031】

なお、この発明では平衡形ラインドライバ出力方式のシリアル信号であることから、抵抗32と抵抗33とは同一抵抗値に設定している。また、このプルアップ抵抗とプルダウン抵抗とは前記シリアル信号に重畳するノイズ成分を抑制するために設置される。

【0032】

また、図1と図2に示した回路構成図から明らかなように、この発明の制御装置6,6aにおけるエンコーダ通信回路は、そのハードウェア構成を同一にすることができ、さらに、客先(現地)でのプルアップ抵抗、プルダウン抵抗の実装作業が不要である。

【0033】

図3は、この発明の第3の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図1に示した実施例の回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0034】

すなわち図3に示した制御装置7の部分回路構成図には、この制御装置7での制御動作を司るMPU34と、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。制御装置7は、シリアル通信によってエンコーダ1に対してデータ要求信号を送信し、このデータ要求信号によりエンコーダ1から送信された位置情報信号を受信することによって、受信した位置情報に基づいた制御動作を行っている。図1に示したものとは、MPU34の出力端子をスリーステート出力としてハイインピーダンス状態を取りうるようにした点と、差動形バストランシーバ23の受信出力をMPU34の入力端子In1に入力している点で相違している。

【0035】

この制御装置7での動作を、図5に示したフローチャートを参照しつつ、以下に説明する。なお、このフローチャートでは、エンコーダ1の通信プロトコルとしての受信待ち状態での論理状態は不明として、処理動作を行っている。

【0036】

先ず、エンコーダ1と制御装置7とに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、MPU34の処理動作により、該MPUのOut1端子とOut2端子とをハイインピーダンス状態に設定する(図5、ステップS1)。

【0037】

この状態でのMPU34のIn1端子の状態、すなわち、差動形バストランシーバ23の受信出力値をMPU34が読込み(図5、ステップS2)、その論理値を判別する(図5、ステップS3)。

【0038】

その結果、エンコーダ1はその通信プロトコルとしての受信待ち状態が論理Hレベルで製作されていることが確認されたので、図5のステップS4に移る。

【0039】

このステップS4では、MPU34のOut1端子とOut2端子とをハイインピーダンス状態から、MPU34の処理動作により、MPU34のOut1端子を論理Hに、Out2端子を論理Lに設定する。

【0040】

その結果、抵抗32がプルアップ抵抗の機能をし、抵抗33がプルダウン抵抗の機能をするので、その後は、MPU34のOut1端子は論理Hの状態、Out2端子は論理Lの状態をそれぞれ継続することにより、エンコーダ1と制御装置7との間は通常の通信状態に入ることができる。

【0041】

図4は、この発明の第4の実施例としてのエンコーダおよび制御装置の部分回路構成図であり、この図において、図2に示した実施例の回路構成と同一機能を有するものには同一符号を付して、ここではその説明を省略する。

【0042】

すなわち図4に示した制御装置7aの部分回路構成図には、この制御装置7aでの制御動作を司るMPU34aと、ASIC22と、差動形バストランシーバ23と、この差動形バストランシーバ23の入力抵抗部を形成する抵抗25,32,33とが示されている。図3と同様に、図2に示したものとは、MPU34aの出力端子をスリーステート出力としてハイインピーダンス状態を取りうるようにした点と、差動形バストランシーバ23の受信出力をMPU34aの入力端子In1に入力している点で相違している。

【0043】

この制御装置7aでの動作を、図5に示したフローチャートを参照しつつ、以下に説明する。なお、このフローチャートでは、エンコーダ2の通信プロトコルとしての受信待ち状態での論理状態は不明として、処理動作を行っている。

【0044】

先ず、エンコーダ1と制御装置7aとに電源電圧が印加された後の初期状態として、双方が互いに受信待ち状態、すなわち双方が送受信停止状態のときに、MPU34aの処理動作により、MPU34aのOut1端子とOut2端子とをハイインピーダンス状態に設定する(図5、ステップS1)。

【0045】

この状態でのMPU34aのIn1端子の状態、すなわち、差動形バストランシーバ23の受信出力値をMPU34aが読込み(図5、ステップS2)、その論理値を判別する(図5、ステップS3)。

【0046】

その結果、エンコーダ2はその通信プロトコルとしての受信待ち状態が論理Lレベルで製作されていることが確認されたので、図5のステップS5に移る。

【0047】

このステップS5では、MPU34aのOut1端子とOut2端子とをハイインピーダンス状態から、MPU34aの処理動作により、MPU34aのOut1端子を論理Lに、Out2端子を論理Hに設定する。

【0048】

その結果、抵抗33がプルアップ抵抗の機能をし、抵抗32がプルダウン抵抗の機能をするので、その後は、MPU34aのOut1端子は論理Lの状態、Out2端子は論理Hの状態をそれぞれ継続することにより、エンコーダ2と制御装置7aとの間は通常の通信状態に入ることができる。

【0049】

図3と図4に示した回路構成図から明らかなように、この発明の制御装置7,7aにおけるエンコーダ通信回路は、そのハードウェア構成を同一にすることができ、さらに、使用するエンコーダの受信待ち状態での論理値の違いも自動的に判別しつつ、そのエンコーダを用いることができる。

【0050】

なお、図1〜4に示したMPU31,31a、34,34aそれぞれのOut1端子およびOut2端子の駆動能力が小さい場合、若しくは上記それぞれのMPUの電源電圧が通常5ボルトに設定される図示のVccの電圧値より低い場合には、それぞれのMPUのOut1端子と抵抗32との接続径路およびOut2端子と抵抗33との接続径路に市販のバッファ素子を挿設することにより、プルアップ抵抗およびプルダウン抵抗の機能を確実に行わせることができる。

【符号の説明】

【0051】

1,2…エンコーダ、3…ケーブル、4〜7,6a,7a…制御装置、11…差動形バストランシーバ、12〜16…抵抗、21,31,31a,34,34a…MPU、22…ASIC,23…差動形バストランシーバ、24〜28,32,33…抵抗。

【特許請求の範囲】

【請求項1】

平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、

前記エンコーダおよび制御装置が互いに送受信停止状態のときの前記エンコーダが出力する論理レベルに基づいて、前記入力抵抗部の両端に印加する直流電圧極性を決定するようにしたことを特徴とするエンコーダ通信回路。

【請求項2】

平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、

前記エンコーダおよび制御装置が互いに送受信停止状態のときに、前記入力抵抗部の両端をそれぞれハイインピーダンス状態にしたときの前記エンコーダが出力している論理レベルを前記差動形バストランシーバの受信出力値から判別し、

この判別した論理レベルにより前記入力抵抗部の両端の直流電圧極性を決定して印加するようにしたことを特徴とするエンコーダ通信回路。

【請求項1】

平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、

前記エンコーダおよび制御装置が互いに送受信停止状態のときの前記エンコーダが出力する論理レベルに基づいて、前記入力抵抗部の両端に印加する直流電圧極性を決定するようにしたことを特徴とするエンコーダ通信回路。

【請求項2】

平衡形ラインドライバ出力方式のシリアル信号を互いに通信信号線を介して送受信するエンコーダと制御装置とからなり、前記制御装置が入力抵抗部と差動形バストランシーバとを有するエンコーダ通信回路において、

前記エンコーダおよび制御装置が互いに送受信停止状態のときに、前記入力抵抗部の両端をそれぞれハイインピーダンス状態にしたときの前記エンコーダが出力している論理レベルを前記差動形バストランシーバの受信出力値から判別し、

この判別した論理レベルにより前記入力抵抗部の両端の直流電圧極性を決定して印加するようにしたことを特徴とするエンコーダ通信回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−168787(P2012−168787A)

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願番号】特願2011−29811(P2011−29811)

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

[ Back to top ]