オフセット補正回路、オフセット補正方法及び記録再生装置

【課題】ダイナミックに発生するオフセットをキャンセルすることが可能な、オフセット補正回路、オフセット補正方法及び記録再生装置を提供すること。

【解決手段】入力信号の振幅を調整するVGA106と、VGA106からの出力信号をフィルタリングするHPF108と、オフセットの調整時に、VGA106のゲインを変化させるゲイン変化回路と、ゲイン変化回路によりゲインを変化させた状態でHPF108の後段に出力された信号の振幅を検出する振幅検出回路118と、振幅検出回路118で検出された振幅に応じて、VGA106へ入力される入力信号のオフセットを調整するオフセット調整回路と、を備える。

【解決手段】入力信号の振幅を調整するVGA106と、VGA106からの出力信号をフィルタリングするHPF108と、オフセットの調整時に、VGA106のゲインを変化させるゲイン変化回路と、ゲイン変化回路によりゲインを変化させた状態でHPF108の後段に出力された信号の振幅を検出する振幅検出回路118と、振幅検出回路118で検出された振幅に応じて、VGA106へ入力される入力信号のオフセットを調整するオフセット調整回路と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、オフセット補正回路、オフセット補正方法及び記録再生装置に関する。

【背景技術】

【0002】

従来、例えば下記の特許文献1に記載されているように、入力信号や回路において発生するオフセットをハイパスフィルタ(HPF)により除去する方法が知られている。

【0003】

【特許文献1】特開2003−229780号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、入力信号や回路において発生するオフセットをハイパスフィルタで除去する際に、HPFのカットオフ周波数により、ダイナミックに変化するオフセットを十分に除去することができないという問題があった。

【0005】

例えば、光ディスク装置においては、AGCループを動作させることにより、入力信号の振幅を一定に制御した後に、入力信号を後段のフィルタやADCに入力する。この際、AGCループの動作に伴いVGAの出力オフセットが変動する。この場合において、AGCループの動作速度がHPFのカットオフ周波数よりも高いと、出力オフセットの変化分はそのまま後段の回路に伝達されてしまい、信号歪や回路の飽和などの原因となってしまう。このオフセットを吸収するためには、HPFの時定数で信号が収束するまで待つ必要があり、その間の入力信号を正常に読み出すことができなくなるという問題が発生する。

【0006】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、ダイナミックに発生するオフセットをキャンセルすることが可能な、新規かつ改良されたオフセット補正回路、オフセット補正方法及び記録再生装置を提供することにある。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明のある観点によれば、入力信号の振幅を調整する振幅調整回路と、前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと、オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と、前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と、前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するオフセット調整回路と、を備える、オフセット補正回路が提供される。

【0008】

上記構成によれば、振幅調整回路により入力信号の振幅が調整され、振幅調整回路からの出力信号がハイパスフィルタによりフィルタリングされる。また、オフセットの調整時に、ゲイン変化回路により振幅調整回路のゲインが変化され、ゲイン変化回路によりゲインを変化させた状態で、ハイパスフィルタの後段に出力された信号の振幅が検出される。そして、振幅検出回路で検出された振幅に応じて、振幅調整回路へ入力される入力信号のオフセットが調整される。従って、振幅調整回路による振幅調整時に発生するダイナミックなオフセットの変化を抑えることが可能となる。

【0009】

また、前記ゲイン変化回路は、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させるものであってもよい。

【0010】

また、前記ゲイン変化回路は、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させるものであってもよい。

【0011】

また、前記オフセット調整回路は、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整するものであってもよい。

【0012】

また、前記振幅調整回路は、後段の回路に出力した信号の振幅を用いたAGCループにより前記入力信号の振幅を調整するものであってもよい。

【0013】

また、上記課題を解決するために、本発明の別の観点によれば、振幅調整回路により入力信号の振幅を調整するステップと、ハイパスフィルタにより前記振幅調整回路からの出力信号をフィルタリングするステップと、オフセットの調整時に、ゲイン変化回路により前記振幅調整回路のゲインを変化させるステップと、前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出するステップと、検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するステップと、を備える、オフセット補正方法が提供される。

【0014】

上記構成によれば、振幅調整回路により入力信号の振幅が調整され、振幅調整回路からの出力信号がハイパスフィルタによりフィルタリングされる。また、オフセットの調整時に、ゲイン変化回路により振幅調整回路のゲインが変化され、ゲインを変化させた状態で、ハイパスフィルタの後段に出力された信号の振幅が検出される。そして、検出された振幅に応じて、振幅調整回路へ入力される入力信号のオフセットが調整される。従って、振幅調整回路による振幅調整時に発生するダイナミックなオフセットの変化を抑えることが可能となる。

【0015】

また、前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させるものであってもよい。

【0016】

また、前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させるものであってもよい。

【0017】

また、前記入力信号のオフセットを調整するステップにおいて、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整するものであってもよい。

【0018】

また、前記入力信号の振幅を調整するステップにおいて、前記振幅検出回路から後段の回路に出力した出力信号の振幅を用いたAGCループにより前記入力信号の振幅を調整するものであってもよい。

【0019】

また、上記課題を解決するために、本発明の別の観点によれば、光記録媒体に光を照射し、前記光記録媒体からの反射光を受光する光ピックアップと、前記光ピックアップから出力されたRF信号の振幅を調整する振幅調整回路と、前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと、オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と、前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と、前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記RF信号のオフセットを調整するオフセット調整回路と、を備える、記録再生装置が提供される。

【0020】

上記構成によれば、光ピックアップにより光記録媒体に光が照射され、光記録媒体からの反射光が受光される。光ピックアップから出力されたRF信号の振幅は、振幅調整回路により調整され、振幅調整回路からの出力信号がハイパスフィルタによりフィルタリングされる。また、オフセットの調整時に、ゲイン変化回路により振幅調整回路のゲインが変化され、ゲインを変化させた状態で、ハイパスフィルタの後段に出力された信号の振幅が検出される。そして、検出された振幅に応じて、振幅調整回路へ入力されるRF信号のオフセットが調整される。従って、振幅調整回路による振幅調整時に発生するダイナミックなオフセットの変化を抑えることが可能となる。

【発明の効果】

【0021】

本発明によれば、ダイナミックに発生するオフセットをキャンセルすることが可能な、新規かつ改良されたオフセット補正回路、オフセット補正方法及び記録再生装置を提供することが可能となる。

【発明を実施するための最良の形態】

【0022】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0023】

図1は、本発明の一実施形態に係る光ディスク装置100の構成を示す模式図である。図1は、光ディスクのRF系信号処理の全体構成を示している。図1に示すように、光ディスク装置100は、ディスク状記録媒体200のトラックを読み出す光学ヘッド(光ピックアップ)102、プリアンプ104、VGA(Variable Gain Amp)回路106、ハイパスフィルタ(HPF)108、アナログフィルタ110、HPF112、AD変換回路(ADC)114、デジタルフィルタ116、振幅検出回路118、ゲイン制御部120、ゲイン制御用DA変換回路(DAC)122、ビタビデコーダ124、復号器126、コントローラ128を有して構成されている。

【0024】

図1において、光学ヘッド102から出力されてプリアンプ104で増幅されたRF信号は、VGA回路(振幅調整回路)106で後段回路のダイナミックレンジに合わせて振幅調整され、HPF108でフィルタリングされてDCオフセット成分を除去され、アナログフィルタ110に入力される。アナログフィルタ110により不要な信号成分を除去された再生信号は、HPF112を経由して、ADC114に入力される。

【0025】

ADC114からの出力信号は、デジタルフィルタ116に入力される。デジタルフィルタ116の出力は、ビタビデコーダ124、復号器126を経由して再生データの復号が行われ、コントローラ128に出力される。

【0026】

また、AGCループとしては、デジタルフィルタ116の出力信号の振幅が振幅検出回路118により検出される。そして、検出された振幅は、ゲイン制御回路120によりターゲット振幅と比較され、比較の結果に基づいてゲイン制御信号が出力される。ゲイン制御信号は、ゲイン制御用DAC122に入力され、アナログ変換された制御信号によりVGA106のゲインが制御される。

【0027】

ここで、AGC(Auto Gain Control)ループの動作において、AGCループの制御時定数とオフセット除去用のHPF108のカットオフ周波数の関係により、AGCループが高速でゲイン制御動作を行うと、VGA106の出力のオフセットがダイナミックに変動する場合がある。この場合、HPF108ではオフセットを除去することができず、オフセットの変動がHPF108を経由して後段の回路に伝播する場合がある。なお、以下の説明では、AGCループのゲイン制御時に発生するオフセット変動を、ダイナミックオフセットと称することとする。

【0028】

特に、VGA106への入力信号の周波数成分が、AGCの動作速度に対して比較的低い場合、オフセット除去用のHPF108のカットオフ周波数を十分に高くすることが出来ない。HPF108のカットオフ周波数に対して、高い時定数でAGCが動作した場合、VGA106のオフセット変動は、HPF108の時定数で収束するまでの間は、そのまま後段の回路に伝達されてしまう。そして、後段の回路でダイナミックレンジが不足すると、波形歪や波形のクランプなどが発生し、信号処理上問題となる。この種のオフセットはDC的には内蔵HPFにより除去されるので、HPF108の後段では静的に観測することができず、キャンセルが難しい。

【0029】

一例として、BD−REやDVD−RAMではセクター先頭のVFO領域でAGCを静定させる必要があるが、この期間はBD−REで1500チャネルビット(以下cbsとする)、DVD−RAMで500cbs程度である。この期間を1倍速時の時間に換算すると、BD−REで22us、DVD−RAMで17us程度である。更に、この区間ではPLLを引き込む必要があり、実際にAGCの引き込みに使用出来るのは、この区間の半分以下である。これに対して、HPF108のカットオフ周波数fcは1KHz程度であり、時定数は160usである。このため、AGC引き込み応答で発生するダイナミックオフセットをHPF108で吸収する時間は全く無い。

【0030】

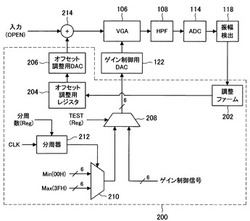

このため、本実施形態では、ダイナミックオフセットをキャンセルするためのダイナミックオフセットキャンセル回路を設けている。図2は、本実施形態に係るダイナミックオフセットキャンセル回路200の構成を示す模式図である。ダイナミックオフセットキャンセル回路200は、調整ファーム(オフセット調整回路)202、オフセット調整用レジスタ204、オフセット調整用DAC206、スイッチ(SW)208、スイッチ(SW)210、分周器212、加算器214を有して構成されている。

【0031】

ダイナミックオフセットキャンセル回路200は、光ディスク装置100のダイナミックオフセット調整工程において、HPF108の時定数より十分高い周波数でVGA106(AGC)のゲインをダイナミックに変化させる。ダイナミックオフセット調整工程は、例えば光ディスク装置100の製造時に行われる。また、光ディスク装置100において、所定のタイミングで行われる自動調整によりダイナミックオフセット調整工程を行うようにしても良い。

【0032】

より詳細には、図2に示すように、VGA106のゲインをダイナミックに変化させるため、スイッチ210には、00H(MIN;最小値)と3F(MAX;最大値)の2つの値が入力される。また、分周器212にはクロックパルスCLKが入力され、分周器212からはクロックパルスCLKと分周数に応じた周波数が出力されて、スイッチ210へ入力される。スイッチ210は、分周器212から出力された周波数により、00H、3Fの2つの値を交互に切り換えてスイッチ208へ出力する。

【0033】

スイッチ208には、ゲイン制御回路120から出力されたゲイン制御信号と、スイッチ210からの出力が入力される。通常時には、スイッチ208は、ゲイン制御回路120から出力されたゲイン制御信号をゲイン制御用DAC122へ出力する。一方、ダイナミックオフセット調整工程では、スイッチ208にテスト信号(TEST(Reg))が入力されて、スイッチ210の出力がゲイン制御用DAC122へ入力されるようにスイッチ208が動作する。このようにして、ダイナミックオフセット調整工程では、分周器212から出力された周波数により00Hと3Fの2つの値が交互に切り換えられてゲイン制御用DAC122に入力される。そして、ゲイン制御用DAC122は入力された信号をアナログ信号に変換し、VGA106はゲイン制御用DAC122から入力された値に基づいてゲインを変化させる。このように、分周器212及びスイッチ210は、ダイナミックオフセット調整時にVGA106のゲインを変化させるゲイン変化回路として機能する。

【0034】

これにより、VGA106の出力にダイナミックオフセットが発生する。そして、本実施形態では、発生したダイナミックオフセットを、HPF108を経由して後段のロジック回路で計測し、ダイナミックオフセットの変動の振幅が最小になる様にVGA106の入力段に設けたオフセットキャンセル用DAC206の設定を調整する。

【0035】

なお、この時発生するダイナミックオフセットの周波数は、ゲイン制御用DAC122におけるゲイン切り換えの周波数、すなわち分周器212からの出力信号の周波数と同じである。この周波数をHPF108のカットオフ周波数よりも十分高くした状態で、HPF108の後段の振幅計測回路によりオフセットの変動量を振幅として計測する。本実施形態において、振幅計測回路は、AGCループを構成する回路の一部(振幅検出回路118)で構成され、特に専用回路を設ける必要はない。

【0036】

なお、VGA106の制御にゲイン制御用DAC122は必須の構成ではなく、また、ゲイン制御値の切り換えにスイッチ208,210は必須ではない。ゲイン制御値をHPF108の時定数に対して十分高速で変化させるため、他の構成を用いても良く、例えば、ゲイン制御値を連続的かつ周期的に変化させても良い。また、VGA106のゲインの切り換えは2値に限定されるものではなく、より多くの値の間で相互に切り換え、このときのダイナミックオフセットを検出しても良い。

【0037】

図3は、ダイナミックオフセット調整工程におけるダイナミックオフセット調整の処理を示すフローチャートである。また、図4は、オフセット調整時の各部の波形を示す特性図である。ここで、図4(A)はゲイン制御用DAC122への入力波形、図4(B)はVGA106のゲイン、図4(C)はオフセット調整前のVGA106の出力波形、図4(D)はオフセット調整後のVGA106の出力波形、をそれぞれ示している。

【0038】

図3に示すように、先ず、ステップS1では、VGA106をオフセット調整モードに設定する。オフセット調整モードでは、スイッチ208にテスト信号が入力される。また、スイッチ210により、信号00H、3Fが分周器212の周波数で切り換えられて、スイッチ208を経由してゲイン制御用DAC122へ入力される。これにより、図4(A)に示すように、CLKを分周した周期で、ゲイン制御用DAC122への入力は、00H(MIN;最小値)→3F(MAX;最大値)→00H(MIN;最小値)→3F(MAX;最大値)の値が交互に繰り返されるように設定される。これにより、図4(B)に示すように、VGA106のゲインは、最大値と最小値の間で交互に切り換えられる。

【0039】

そして、次のステップS2では、VGA106の出力のダイナミックオフセットを調整するため、オフセット調整用DAC206の設定を変更する。この際、振幅検出回路118にてダイナミックオフセットの振幅が検出され、振幅を最小にするため、調整ファーム202からオフセット調整用レジスタ204へ制御値が出力される。調整ファーム202は、VGA106への入力信号のオフセットを調整するためのコントローラとして機能する。オフセット調整用レジスタ204は、振幅検出回路118から入力された制御値に基づいて、オフセット調整用DAC206への入力値を設定するレジスタである。オフセット調整用DAC206は、オフセット調整用レジスタ204からの入力値をアナログ信号に変換する。オフセット調整用DAC206の出力は、加算器214によりVGA106の入力信号に対して加算され、入力信号のオフセットが変更される。

【0040】

次のステップS3では、振幅検出回路118により、ダイナミックオフセットの変動成分の振幅を計測する。次のステップS4では、ステップS3で計測した振幅に基づいて、振幅が最小となるオフセット調整用DAC206の調整値を判定可能であるか否かを判定し、判定可能の場合は、調整を終了する。一方、振幅が最小となる調整値を判定可能でない場合は、ステップS2に戻り、オフセット調整用DAC206によるオフセット調整を再度行う。なお、調整工程において取得された振幅の値は、光ディスク装置100が備えるメモリ(不図示)等に格納されることができる。

【0041】

ダイナミックオフセットが変化している場合、図4(C)に示すように、ゲイン制御用DAC122によりゲインを切り換えるタイミングで、VGA106の出力にパルスが発生する。図3の処理によりダイナミックオフセット調整が行われると、図4(D)に示すように、オフセット調整後のVGA106の出力波形において、VGA106の出力波形の振幅が減少する。従って、ダイナミックオフセットが最小となるように調整することができる。

【0042】

以上説明したように本実施形態によれば、予め用意された2つの制御値を特定の周波数で切り換えることによりVGA106のゲインを制御し、このときに発生するダイナミックオフセットが最小となるようにVGA106の入力信号のオフセットが調整される。従って、簡素な回路構成および調整方法で、VGA106のダイナミックオフセットを除去することが可能となる。そして、ダイナミックオフセットを除去することにより、オフセット除去用のHPF108のカットオフ周波数に影響を受けることなく、AGCループの動作速度を高めることが可能となり、高速AGCを実現することが可能となる。また、オフセット調整により、回路のダイナミックレンジを有効に活用することが可能となり、回路規模や電力消費量を低減することができる。

【0043】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

【図面の簡単な説明】

【0044】

【図1】本発明の一実施形態に係る光ディスク装置の構成を示す模式図である。

【図2】本発明の一実施形態に係るダイナミックオフセットキャンセル回路の構成を示す模式図である。

【図3】ダイナミックオフセット調整工程におけるダイナミックオフセット調整の処理を示すフローチャートである。

【図4】オフセット調整時の各部の波形を示す特性図である。

【符号の説明】

【0045】

100 光ディスク装置

106 VGA

108 HPF

118 振幅検出回路

202 調整ファーム

204 オフセット調整用レジスタ

206 オフセット調整用DAC

208,210 スイッチ

212 分周器

【技術分野】

【0001】

本発明は、オフセット補正回路、オフセット補正方法及び記録再生装置に関する。

【背景技術】

【0002】

従来、例えば下記の特許文献1に記載されているように、入力信号や回路において発生するオフセットをハイパスフィルタ(HPF)により除去する方法が知られている。

【0003】

【特許文献1】特開2003−229780号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、入力信号や回路において発生するオフセットをハイパスフィルタで除去する際に、HPFのカットオフ周波数により、ダイナミックに変化するオフセットを十分に除去することができないという問題があった。

【0005】

例えば、光ディスク装置においては、AGCループを動作させることにより、入力信号の振幅を一定に制御した後に、入力信号を後段のフィルタやADCに入力する。この際、AGCループの動作に伴いVGAの出力オフセットが変動する。この場合において、AGCループの動作速度がHPFのカットオフ周波数よりも高いと、出力オフセットの変化分はそのまま後段の回路に伝達されてしまい、信号歪や回路の飽和などの原因となってしまう。このオフセットを吸収するためには、HPFの時定数で信号が収束するまで待つ必要があり、その間の入力信号を正常に読み出すことができなくなるという問題が発生する。

【0006】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、ダイナミックに発生するオフセットをキャンセルすることが可能な、新規かつ改良されたオフセット補正回路、オフセット補正方法及び記録再生装置を提供することにある。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明のある観点によれば、入力信号の振幅を調整する振幅調整回路と、前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと、オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と、前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と、前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するオフセット調整回路と、を備える、オフセット補正回路が提供される。

【0008】

上記構成によれば、振幅調整回路により入力信号の振幅が調整され、振幅調整回路からの出力信号がハイパスフィルタによりフィルタリングされる。また、オフセットの調整時に、ゲイン変化回路により振幅調整回路のゲインが変化され、ゲイン変化回路によりゲインを変化させた状態で、ハイパスフィルタの後段に出力された信号の振幅が検出される。そして、振幅検出回路で検出された振幅に応じて、振幅調整回路へ入力される入力信号のオフセットが調整される。従って、振幅調整回路による振幅調整時に発生するダイナミックなオフセットの変化を抑えることが可能となる。

【0009】

また、前記ゲイン変化回路は、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させるものであってもよい。

【0010】

また、前記ゲイン変化回路は、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させるものであってもよい。

【0011】

また、前記オフセット調整回路は、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整するものであってもよい。

【0012】

また、前記振幅調整回路は、後段の回路に出力した信号の振幅を用いたAGCループにより前記入力信号の振幅を調整するものであってもよい。

【0013】

また、上記課題を解決するために、本発明の別の観点によれば、振幅調整回路により入力信号の振幅を調整するステップと、ハイパスフィルタにより前記振幅調整回路からの出力信号をフィルタリングするステップと、オフセットの調整時に、ゲイン変化回路により前記振幅調整回路のゲインを変化させるステップと、前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出するステップと、検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するステップと、を備える、オフセット補正方法が提供される。

【0014】

上記構成によれば、振幅調整回路により入力信号の振幅が調整され、振幅調整回路からの出力信号がハイパスフィルタによりフィルタリングされる。また、オフセットの調整時に、ゲイン変化回路により振幅調整回路のゲインが変化され、ゲインを変化させた状態で、ハイパスフィルタの後段に出力された信号の振幅が検出される。そして、検出された振幅に応じて、振幅調整回路へ入力される入力信号のオフセットが調整される。従って、振幅調整回路による振幅調整時に発生するダイナミックなオフセットの変化を抑えることが可能となる。

【0015】

また、前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させるものであってもよい。

【0016】

また、前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させるものであってもよい。

【0017】

また、前記入力信号のオフセットを調整するステップにおいて、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整するものであってもよい。

【0018】

また、前記入力信号の振幅を調整するステップにおいて、前記振幅検出回路から後段の回路に出力した出力信号の振幅を用いたAGCループにより前記入力信号の振幅を調整するものであってもよい。

【0019】

また、上記課題を解決するために、本発明の別の観点によれば、光記録媒体に光を照射し、前記光記録媒体からの反射光を受光する光ピックアップと、前記光ピックアップから出力されたRF信号の振幅を調整する振幅調整回路と、前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと、オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と、前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と、前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記RF信号のオフセットを調整するオフセット調整回路と、を備える、記録再生装置が提供される。

【0020】

上記構成によれば、光ピックアップにより光記録媒体に光が照射され、光記録媒体からの反射光が受光される。光ピックアップから出力されたRF信号の振幅は、振幅調整回路により調整され、振幅調整回路からの出力信号がハイパスフィルタによりフィルタリングされる。また、オフセットの調整時に、ゲイン変化回路により振幅調整回路のゲインが変化され、ゲインを変化させた状態で、ハイパスフィルタの後段に出力された信号の振幅が検出される。そして、検出された振幅に応じて、振幅調整回路へ入力されるRF信号のオフセットが調整される。従って、振幅調整回路による振幅調整時に発生するダイナミックなオフセットの変化を抑えることが可能となる。

【発明の効果】

【0021】

本発明によれば、ダイナミックに発生するオフセットをキャンセルすることが可能な、新規かつ改良されたオフセット補正回路、オフセット補正方法及び記録再生装置を提供することが可能となる。

【発明を実施するための最良の形態】

【0022】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0023】

図1は、本発明の一実施形態に係る光ディスク装置100の構成を示す模式図である。図1は、光ディスクのRF系信号処理の全体構成を示している。図1に示すように、光ディスク装置100は、ディスク状記録媒体200のトラックを読み出す光学ヘッド(光ピックアップ)102、プリアンプ104、VGA(Variable Gain Amp)回路106、ハイパスフィルタ(HPF)108、アナログフィルタ110、HPF112、AD変換回路(ADC)114、デジタルフィルタ116、振幅検出回路118、ゲイン制御部120、ゲイン制御用DA変換回路(DAC)122、ビタビデコーダ124、復号器126、コントローラ128を有して構成されている。

【0024】

図1において、光学ヘッド102から出力されてプリアンプ104で増幅されたRF信号は、VGA回路(振幅調整回路)106で後段回路のダイナミックレンジに合わせて振幅調整され、HPF108でフィルタリングされてDCオフセット成分を除去され、アナログフィルタ110に入力される。アナログフィルタ110により不要な信号成分を除去された再生信号は、HPF112を経由して、ADC114に入力される。

【0025】

ADC114からの出力信号は、デジタルフィルタ116に入力される。デジタルフィルタ116の出力は、ビタビデコーダ124、復号器126を経由して再生データの復号が行われ、コントローラ128に出力される。

【0026】

また、AGCループとしては、デジタルフィルタ116の出力信号の振幅が振幅検出回路118により検出される。そして、検出された振幅は、ゲイン制御回路120によりターゲット振幅と比較され、比較の結果に基づいてゲイン制御信号が出力される。ゲイン制御信号は、ゲイン制御用DAC122に入力され、アナログ変換された制御信号によりVGA106のゲインが制御される。

【0027】

ここで、AGC(Auto Gain Control)ループの動作において、AGCループの制御時定数とオフセット除去用のHPF108のカットオフ周波数の関係により、AGCループが高速でゲイン制御動作を行うと、VGA106の出力のオフセットがダイナミックに変動する場合がある。この場合、HPF108ではオフセットを除去することができず、オフセットの変動がHPF108を経由して後段の回路に伝播する場合がある。なお、以下の説明では、AGCループのゲイン制御時に発生するオフセット変動を、ダイナミックオフセットと称することとする。

【0028】

特に、VGA106への入力信号の周波数成分が、AGCの動作速度に対して比較的低い場合、オフセット除去用のHPF108のカットオフ周波数を十分に高くすることが出来ない。HPF108のカットオフ周波数に対して、高い時定数でAGCが動作した場合、VGA106のオフセット変動は、HPF108の時定数で収束するまでの間は、そのまま後段の回路に伝達されてしまう。そして、後段の回路でダイナミックレンジが不足すると、波形歪や波形のクランプなどが発生し、信号処理上問題となる。この種のオフセットはDC的には内蔵HPFにより除去されるので、HPF108の後段では静的に観測することができず、キャンセルが難しい。

【0029】

一例として、BD−REやDVD−RAMではセクター先頭のVFO領域でAGCを静定させる必要があるが、この期間はBD−REで1500チャネルビット(以下cbsとする)、DVD−RAMで500cbs程度である。この期間を1倍速時の時間に換算すると、BD−REで22us、DVD−RAMで17us程度である。更に、この区間ではPLLを引き込む必要があり、実際にAGCの引き込みに使用出来るのは、この区間の半分以下である。これに対して、HPF108のカットオフ周波数fcは1KHz程度であり、時定数は160usである。このため、AGC引き込み応答で発生するダイナミックオフセットをHPF108で吸収する時間は全く無い。

【0030】

このため、本実施形態では、ダイナミックオフセットをキャンセルするためのダイナミックオフセットキャンセル回路を設けている。図2は、本実施形態に係るダイナミックオフセットキャンセル回路200の構成を示す模式図である。ダイナミックオフセットキャンセル回路200は、調整ファーム(オフセット調整回路)202、オフセット調整用レジスタ204、オフセット調整用DAC206、スイッチ(SW)208、スイッチ(SW)210、分周器212、加算器214を有して構成されている。

【0031】

ダイナミックオフセットキャンセル回路200は、光ディスク装置100のダイナミックオフセット調整工程において、HPF108の時定数より十分高い周波数でVGA106(AGC)のゲインをダイナミックに変化させる。ダイナミックオフセット調整工程は、例えば光ディスク装置100の製造時に行われる。また、光ディスク装置100において、所定のタイミングで行われる自動調整によりダイナミックオフセット調整工程を行うようにしても良い。

【0032】

より詳細には、図2に示すように、VGA106のゲインをダイナミックに変化させるため、スイッチ210には、00H(MIN;最小値)と3F(MAX;最大値)の2つの値が入力される。また、分周器212にはクロックパルスCLKが入力され、分周器212からはクロックパルスCLKと分周数に応じた周波数が出力されて、スイッチ210へ入力される。スイッチ210は、分周器212から出力された周波数により、00H、3Fの2つの値を交互に切り換えてスイッチ208へ出力する。

【0033】

スイッチ208には、ゲイン制御回路120から出力されたゲイン制御信号と、スイッチ210からの出力が入力される。通常時には、スイッチ208は、ゲイン制御回路120から出力されたゲイン制御信号をゲイン制御用DAC122へ出力する。一方、ダイナミックオフセット調整工程では、スイッチ208にテスト信号(TEST(Reg))が入力されて、スイッチ210の出力がゲイン制御用DAC122へ入力されるようにスイッチ208が動作する。このようにして、ダイナミックオフセット調整工程では、分周器212から出力された周波数により00Hと3Fの2つの値が交互に切り換えられてゲイン制御用DAC122に入力される。そして、ゲイン制御用DAC122は入力された信号をアナログ信号に変換し、VGA106はゲイン制御用DAC122から入力された値に基づいてゲインを変化させる。このように、分周器212及びスイッチ210は、ダイナミックオフセット調整時にVGA106のゲインを変化させるゲイン変化回路として機能する。

【0034】

これにより、VGA106の出力にダイナミックオフセットが発生する。そして、本実施形態では、発生したダイナミックオフセットを、HPF108を経由して後段のロジック回路で計測し、ダイナミックオフセットの変動の振幅が最小になる様にVGA106の入力段に設けたオフセットキャンセル用DAC206の設定を調整する。

【0035】

なお、この時発生するダイナミックオフセットの周波数は、ゲイン制御用DAC122におけるゲイン切り換えの周波数、すなわち分周器212からの出力信号の周波数と同じである。この周波数をHPF108のカットオフ周波数よりも十分高くした状態で、HPF108の後段の振幅計測回路によりオフセットの変動量を振幅として計測する。本実施形態において、振幅計測回路は、AGCループを構成する回路の一部(振幅検出回路118)で構成され、特に専用回路を設ける必要はない。

【0036】

なお、VGA106の制御にゲイン制御用DAC122は必須の構成ではなく、また、ゲイン制御値の切り換えにスイッチ208,210は必須ではない。ゲイン制御値をHPF108の時定数に対して十分高速で変化させるため、他の構成を用いても良く、例えば、ゲイン制御値を連続的かつ周期的に変化させても良い。また、VGA106のゲインの切り換えは2値に限定されるものではなく、より多くの値の間で相互に切り換え、このときのダイナミックオフセットを検出しても良い。

【0037】

図3は、ダイナミックオフセット調整工程におけるダイナミックオフセット調整の処理を示すフローチャートである。また、図4は、オフセット調整時の各部の波形を示す特性図である。ここで、図4(A)はゲイン制御用DAC122への入力波形、図4(B)はVGA106のゲイン、図4(C)はオフセット調整前のVGA106の出力波形、図4(D)はオフセット調整後のVGA106の出力波形、をそれぞれ示している。

【0038】

図3に示すように、先ず、ステップS1では、VGA106をオフセット調整モードに設定する。オフセット調整モードでは、スイッチ208にテスト信号が入力される。また、スイッチ210により、信号00H、3Fが分周器212の周波数で切り換えられて、スイッチ208を経由してゲイン制御用DAC122へ入力される。これにより、図4(A)に示すように、CLKを分周した周期で、ゲイン制御用DAC122への入力は、00H(MIN;最小値)→3F(MAX;最大値)→00H(MIN;最小値)→3F(MAX;最大値)の値が交互に繰り返されるように設定される。これにより、図4(B)に示すように、VGA106のゲインは、最大値と最小値の間で交互に切り換えられる。

【0039】

そして、次のステップS2では、VGA106の出力のダイナミックオフセットを調整するため、オフセット調整用DAC206の設定を変更する。この際、振幅検出回路118にてダイナミックオフセットの振幅が検出され、振幅を最小にするため、調整ファーム202からオフセット調整用レジスタ204へ制御値が出力される。調整ファーム202は、VGA106への入力信号のオフセットを調整するためのコントローラとして機能する。オフセット調整用レジスタ204は、振幅検出回路118から入力された制御値に基づいて、オフセット調整用DAC206への入力値を設定するレジスタである。オフセット調整用DAC206は、オフセット調整用レジスタ204からの入力値をアナログ信号に変換する。オフセット調整用DAC206の出力は、加算器214によりVGA106の入力信号に対して加算され、入力信号のオフセットが変更される。

【0040】

次のステップS3では、振幅検出回路118により、ダイナミックオフセットの変動成分の振幅を計測する。次のステップS4では、ステップS3で計測した振幅に基づいて、振幅が最小となるオフセット調整用DAC206の調整値を判定可能であるか否かを判定し、判定可能の場合は、調整を終了する。一方、振幅が最小となる調整値を判定可能でない場合は、ステップS2に戻り、オフセット調整用DAC206によるオフセット調整を再度行う。なお、調整工程において取得された振幅の値は、光ディスク装置100が備えるメモリ(不図示)等に格納されることができる。

【0041】

ダイナミックオフセットが変化している場合、図4(C)に示すように、ゲイン制御用DAC122によりゲインを切り換えるタイミングで、VGA106の出力にパルスが発生する。図3の処理によりダイナミックオフセット調整が行われると、図4(D)に示すように、オフセット調整後のVGA106の出力波形において、VGA106の出力波形の振幅が減少する。従って、ダイナミックオフセットが最小となるように調整することができる。

【0042】

以上説明したように本実施形態によれば、予め用意された2つの制御値を特定の周波数で切り換えることによりVGA106のゲインを制御し、このときに発生するダイナミックオフセットが最小となるようにVGA106の入力信号のオフセットが調整される。従って、簡素な回路構成および調整方法で、VGA106のダイナミックオフセットを除去することが可能となる。そして、ダイナミックオフセットを除去することにより、オフセット除去用のHPF108のカットオフ周波数に影響を受けることなく、AGCループの動作速度を高めることが可能となり、高速AGCを実現することが可能となる。また、オフセット調整により、回路のダイナミックレンジを有効に活用することが可能となり、回路規模や電力消費量を低減することができる。

【0043】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

【図面の簡単な説明】

【0044】

【図1】本発明の一実施形態に係る光ディスク装置の構成を示す模式図である。

【図2】本発明の一実施形態に係るダイナミックオフセットキャンセル回路の構成を示す模式図である。

【図3】ダイナミックオフセット調整工程におけるダイナミックオフセット調整の処理を示すフローチャートである。

【図4】オフセット調整時の各部の波形を示す特性図である。

【符号の説明】

【0045】

100 光ディスク装置

106 VGA

108 HPF

118 振幅検出回路

202 調整ファーム

204 オフセット調整用レジスタ

206 オフセット調整用DAC

208,210 スイッチ

212 分周器

【特許請求の範囲】

【請求項1】

入力信号の振幅を調整する振幅調整回路と;

前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと;

オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と;

前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と;

前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するオフセット調整回路と;

を備える、オフセット補正回路。

【請求項2】

前記ゲイン変化回路は、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させる、請求項1に記載のオフセット補正回路。

【請求項3】

前記ゲイン変化回路は、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させる、請求項1に記載のオフセット補正回路。

【請求項4】

前記オフセット調整回路は、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整する、請求項1に記載のオフセット補正回路。

【請求項5】

前記振幅調整回路は、後段の回路に出力した信号の振幅を用いたAGCループにより前記入力信号の振幅を調整する、請求項1に記載のオフセット補正回路。

【請求項6】

振幅調整回路により入力信号の振幅を調整するステップと;

ハイパスフィルタにより前記振幅調整回路からの出力信号をフィルタリングするステップと;

オフセットの調整時に、ゲイン変化回路により前記振幅調整回路のゲインを変化させるステップと;

前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出するステップと;

検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するステップと;

を備える、オフセット補正方法。

【請求項7】

前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させる、請求項6に記載のオフセット補正方法。

【請求項8】

前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させる、請求項6に記載のオフセット補正方法。

【請求項9】

前記入力信号のオフセットを調整するステップにおいて、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整する、請求項6に記載のオフセット補正方法。

【請求項10】

前記入力信号の振幅を調整するステップにおいて、前記振幅検出回路から後段の回路に出力した出力信号の振幅を用いたAGCループにより前記入力信号の振幅を調整する、請求項6に記載のオフセット補正方法。

【請求項11】

光記録媒体に光を照射し、前記光記録媒体からの反射光を受光する光ピックアップと;

前記光ピックアップから出力されたRF信号の振幅を調整する振幅調整回路と;

前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと;

オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と;

前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と;

前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記RF信号のオフセットを調整するオフセット調整回路と;

を備える、記録再生装置。

【請求項1】

入力信号の振幅を調整する振幅調整回路と;

前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと;

オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と;

前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と;

前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するオフセット調整回路と;

を備える、オフセット補正回路。

【請求項2】

前記ゲイン変化回路は、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させる、請求項1に記載のオフセット補正回路。

【請求項3】

前記ゲイン変化回路は、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させる、請求項1に記載のオフセット補正回路。

【請求項4】

前記オフセット調整回路は、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整する、請求項1に記載のオフセット補正回路。

【請求項5】

前記振幅調整回路は、後段の回路に出力した信号の振幅を用いたAGCループにより前記入力信号の振幅を調整する、請求項1に記載のオフセット補正回路。

【請求項6】

振幅調整回路により入力信号の振幅を調整するステップと;

ハイパスフィルタにより前記振幅調整回路からの出力信号をフィルタリングするステップと;

オフセットの調整時に、ゲイン変化回路により前記振幅調整回路のゲインを変化させるステップと;

前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出するステップと;

検出された前記振幅に応じて、前記振幅調整回路へ入力される前記入力信号のオフセットを調整するステップと;

を備える、オフセット補正方法。

【請求項7】

前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを前記ハイパスフィルタのカットオフ周波数よりも高い周波数で変化させる、請求項6に記載のオフセット補正方法。

【請求項8】

前記ゲインを変化させるステップにおいて、前記振幅調整回路のゲインを予め定められた2値の間で交互に変化させる、請求項6に記載のオフセット補正方法。

【請求項9】

前記入力信号のオフセットを調整するステップにおいて、前記振幅検出回路で検出された前記振幅が最小となるように前記入力信号のオフセットを調整する、請求項6に記載のオフセット補正方法。

【請求項10】

前記入力信号の振幅を調整するステップにおいて、前記振幅検出回路から後段の回路に出力した出力信号の振幅を用いたAGCループにより前記入力信号の振幅を調整する、請求項6に記載のオフセット補正方法。

【請求項11】

光記録媒体に光を照射し、前記光記録媒体からの反射光を受光する光ピックアップと;

前記光ピックアップから出力されたRF信号の振幅を調整する振幅調整回路と;

前記振幅調整回路からの出力信号をフィルタリングするハイパスフィルタと;

オフセットの調整時に、前記振幅調整回路のゲインを変化させるゲイン変化回路と;

前記ゲイン変化回路によりゲインを変化させた状態で、前記ハイパスフィルタの後段に出力された信号の振幅を検出する振幅検出回路と;

前記振幅検出回路で検出された前記振幅に応じて、前記振幅調整回路へ入力される前記RF信号のオフセットを調整するオフセット調整回路と;

を備える、記録再生装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2009−295253(P2009−295253A)

【公開日】平成21年12月17日(2009.12.17)

【国際特許分類】

【出願番号】特願2008−149822(P2008−149822)

【出願日】平成20年6月6日(2008.6.6)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成21年12月17日(2009.12.17)

【国際特許分類】

【出願日】平成20年6月6日(2008.6.6)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]