オペアンプ補償回路

【課題】出力バッファを有するオペアンプA1であつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供する。

【解決手段】バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタT1を有し、あるいは、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続し、それぞれ入力信号と反転された入力信号が入力されている構成を有し、オフセット電位が接地となることを特徴とする。

【解決手段】バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタT1を有し、あるいは、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続し、それぞれ入力信号と反転された入力信号が入力されている構成を有し、オフセット電位が接地となることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、オフセット電位の補償されたオペアンプ補償回路に関する。

【背景技術】

【0002】

オペアンプは、電子回路の基本となる増幅器で、応用範囲も広く、多用されている。近年、技術の開発、応用が進む中で、オペアンプのオフセットの問題が極めて重要な問題となっている。現在、一般に使用されているICでは、オフセット電圧の値は1mV程度であるが、1mVでも許容出来ない状況も発生する。これを、減算回路を例として説明する。

【0003】

減算回路は、ある信号の中から不要な信号を取り除き有効な信号のみを出力させたい場合に使用する。オペアンプと抵抗の組み合せにより実現可能なアナログ回路としては、加算回路と並んで重要な回路構成となる。

【0004】

図1は、従来の減算回路の例を示した説明図であり、図1のような回路構成となっている。減算回路は、“Vin”、“Vref”電圧が入力される。“Vref”端子の電圧は基準電圧となる為、固定電圧となる。Vinは0VからVDD電圧の幅で入力される。R1、R2、R3、R4の抵抗値はR2/R1=R4/R3を満たすように決定する。本例の回路では、R1:R2:R3:R4=1:1:1:1の抵抗値に設定するとする。その場合、オペアンプA1の入力ノード”A”の電位は、A=Vin/2[V](A=Vin*R4/(R3+R4)より)、ノード”B”の電位は、仮想短絡(フィードバックをかけたオペアンプの二つの入力はいつも同電位となる)によりB=Aとなる。図2は、本例の減算回路の動作を示した説明図であり、横軸、縦軸ともに電圧値を示している。また、Vrefを固定電圧とし、Vinを0[V]より増加した場合の動作を示している。図で、減算回路の出力電圧“Ampout”は、“Vin>Vref”の場合(図2(1)の区間)、“Ampout=Vin−Vref”となり、“Vin”端子と“Vref端子”の電位差が出力される。“Vref>=Vin”の電圧が入力された場合(図2(2)の区間)は、Vin−Vref<=0となる為、0[V]が出力される。

【0005】

Vref>=Vinの場合、理想上は0[V]が出力されるが、実際にはオペアンプA1の回路構成上、0[V]にはならず数mV程度の電位浮きが発生する。図3は、このような減算回路のオフセット発生の不具合現象を示した説明図である。(2)Vref>=Vinの部分を拡大している。図4は、オフセット発生に係る電流経路を示した説明図である。図4に示すように、減算回路の特性上、0V出力時、R1、R2、オペアンプA1の出力バッファ部M1の経路で電流が流れる。M1素子のON抵抗を小さくしなければ、“Ampout”の出力電圧の電位浮きが発生する。しかし、オペアンプA1の出力バッファのゲート電圧はA級、AB級出力バッファ(すなわち、それぞれA級増幅回路、AB級増幅回路)を用いても、ゲート電圧を印加する各A〜Cのノードの電位をVDDにすることは出来ない。このため、M1素子のWサイズを大きくする以外に、ON抵抗を十分小さくすることは困難となる。

【0006】

“Vin>Vref”の場合は、“Ampout”の出力電圧は“Vin−Vref”となり、この1mV程度の電位の浮きはそれほど問題にならない。しかし、“Vref>=Vin”の場合は、出力電圧は“0”Vを期待しているため、1mV程度の浮きですら問題となる場合が多い。

【0007】

図5に出力電圧浮きにより不具合が発生する回路構成例を示す。これは減算回路で、電

流発生回路を駆動する例である。電流発生回路は、電流発生回路アンプA2と、電源と接地間に直列接続されたMOSトランジスタと抵抗RSINKを接続した構成である。電流発生回路アンプA2の出力がMOSトランジスタに入力し、MOSトランジスタと抵抗RSINK間の出力電圧FBoutが電流発生回路アンプA2の入力にフィードバックされる。この回路構成では、減算回路により“Ampout”に、“Vin”端子と“Vref”端子の電圧差“Vin−Vref”電圧が出力される。“Ampout”電圧が後段の電流発生回路アンプA2の仮想短絡により、“FBout=Ampout”となる。FBout電圧とRSINK抵抗により、MOSトランジスタ端のIsinkout端子に“FBout[V]/RSINK[Ω]”のシンク電流が流れる。RSINK抵抗値は数百Ω程度である。このようすを図6に示す。

“Vin>Vref”の場合((1)の区間)では、“Ampout=FBout>0V”となり、シンク電流“Isink=FBout/RSINK”が流れる。RSINK抵抗値は数Ω程度の為、“Isinkout”の電流は数mA程度となる。“Vref>=Vin”の場合((2)区間)では、“Ampout=FBout=0V”の為、Isinkout端子シンクの電流は0[μA]となるはずである。しかし、減算回路のオフセットが1[mV]発生すると仮定し、RSINK抵抗値を100Ωに設定したとすると、“Isinkout”端子シンクの電流は10μA流れることになる(Vref>=Vin条件で、Isinkout端子に流れるシンク電流をリーク電流と呼ぶ)。一般的に(2)の区間のシンク電流のSPECは、±1μA程度である。SPEC±1μAに抑えるためには、2つの手法が考えられる。

(1)RSINK抵抗値を数百Ω程度から数kΩ(10倍にする)。

ただし、この方法では図7のように(2)区間のリーク電流を制限する事が可能だが、(1)区間のシンク電流も1/10となる為、実用的ではない。

(2)オフセット電圧を数mVから数百μV(1/10)にする。

【0008】

減算回路のオフセットをなくすことにより、図6の(2)区間の“Ampout”端子の電位浮きを抑えることが可能となる。さらに、図5の(2)のオペアンプの仮想短絡により、“Ampout=FBout”となるため、“Ampout”端子の電位を抑えることになり、結果的にIsinkout端子のリーク電流を抑える事が可能となる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2001−244759号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

以上のような問題点から本願発明は、出力バッファを有するオペアンプであつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供することを課題とする。

【課題を解決するための手段】

【0011】

本発明は係る課題に鑑みなされたものであり、請求項1の発明は、出力バッファを有するオペアンプであつて、バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタを有し、オフセット電位が接地となることを特徴とするオペアンプ補償回路としたものである。

【0012】

本発明の請求項2の発明は、MOSトランジスタが、Nチャンネルトランジスタと、Pチャンネルトランジスタとを並列接続した構成で、それぞれ入力信号と反転された入力信号が入力されていることを特徴とする請求項1に記載のオペアンプ補償回路としたものである。

【0013】

本発明の請求項3の発明は、入力信号が、オペアンプの入力と同じ信号が入力している

比較回路の出力信号であることを特徴とする請求項1または請求項2に記載のオペアンプ補償回路としたものである。

【発明の効果】

【0014】

本発明のオペアンプ補償回路は以上のような構成であるので、出力バッファを有するオペアンプであつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路とすることができる。

【図面の簡単な説明】

【0015】

【図1】従来の減算回路の例を示した説明図である。

【図2】図1の例の減算回路の動作を示した説明図である。

【図3】減算回路のオフセット発生の不具合現象を示した説明図である。

【図4】減算回路のオフセット発生の不具合現象を示した他の説明図である。

【図5】出力電圧浮きにより不具合が発生する回路構成例を示す。

【図6】図5の回路構成のRSINK電流による電圧変化を示す説明図である。

【図7】図5のRSINK抵抗をパラメタとした電圧変化を示す説明図である。

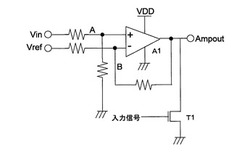

【図8】本発明のオペアンプ補償回路の第一実施形態を示す説明図である。

【図9】本発明のオペアンプ補償回路の第二の実施形態を示す説明図である。

【図10】本発明のオペアンプ補償回路の第三の実施形態を示す説明図である。

【図11】本発明のオペアンプ補償回路の第三の実施形態の動作を説明する図である。

【図12】本発明に使用できるヒステリシスの有るコンパレータの説明図である。

【図13】図10の回路構成で、ヒステリシスの有るコンパレータを使用した場合の説明図である。

【図14】本発明のオペアンプ補償回路を用い、減算回路、コンパレータ、ボルテージフォロワの回路構成とした例の説明図である。

【図15】本発明のオペアンプ補償回路を用い、減算回路、コンパレータ、VI変換回路の構成とした説明図である。

【発明を実施するための形態】

【0016】

以下本発明を実施するための形態につき説明する。図8は、本発明のオペアンプ補償回路の第一実施形態を示す説明図である。本オペアンプ補償回路は、出力バッファを有するオペアンプA1であつて、バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるNMOSトランジスタを有している。入力信号が電源電圧の大きさで入力することによってオフセット電位が接地となる。図8は、出力バッファを有するオペアンプ回路A1に抵抗R1、R2、R3、R4を接続した減算回路を構成している。そしてこのオ

ペアンプの出力と接地間にNMOSトランジスタT1が接続されている。NMOSトランジスタT1には接地から電源電圧まで変化する入力信号が入力する。減算回路の入力Vrefは、図1と同様に、通常は、“Vref”端子の電圧は基準電圧となる為、固定電圧となる。Vinは0VからVDD電圧の幅で入力される。

【0017】

Vref>=Vin時にNMOSトランジスタT1をON、Vref<=Vin時にOFFさせる。このNMOSトランジスタT1のゲート電圧は0V〜VDD電圧幅で振幅する為、NMOSのゲート電圧を高く取ることが出来、ON抵抗を小さくすることができる。そして、ノード“Ampout”を0[V]までダウンさせる。NMOSトランジスタT1のサイズは、Wはレイアウト面積に問題ないように可能な限り大きくし、Lはプロセスの最小で設計するとよい。

【0018】

図9は、本発明のオペアンプ補償回路の第二の実施形態を示す説明図である。図で示すように、第一の実施形態のNMOSトランジスタT1を、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続したものとしている。そして、それぞれ入力信号と、インバータINV1を介して反転された入力信号とが入力されている。NMOS素子単体ではなく、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続したSW構成にすることにより、レイアウト面積は大きくなるが、オフセット電圧をNMOS単体の場合より抑えることが可能となる。

【0019】

図10は、本発明のオペアンプ補償回路の第三の実施形態を示す説明図である。図で示すように、本実施形態は、第二の実施形態の入力信号を、オペアンプA1の入力と同じ信号Vref、Vinが入力している比較回路A2の出力信号Compoutとしている。NMOSトランジスタTN1のゲートに、“Vin”と“Vref”のコンパレータの出力“Compout”を接続することにより、Vin>Vref時、コンパレータの出力“Compout”は“L”、Vref>=Vin時、“H”を出力する。コンパレータの出力は0V⇔VDDの電圧幅を確保出来るため、Vref>=Vin時、オペアンプ単体の場合より、Ampoutを0Vに近づけることが可能となる。Vin>Vref時、NMOSトランジスタTN1はオフしているため、影響しない。

【0020】

図11に本第三の実施形態の動作を示す。オペアンプA1の出力は、AB級バッファを例示している。Vref>=Vinの場合、“Compout”電圧は“H”となり、CMOS

SWはONとなる。これにより、“Ampout”を“L”とする経路が、図11の抵抗とバッファトランジスタを経由して接地する経路(1)と、抵抗とCMOS SWを経由して接地する経路(2)との2つとなる。経路(2)の効果により、“Ampout”の電位浮きが改善される。

【0021】

本実施の形態例のコンパレータを追加することにより、図3の(2)の区間で発生するオフセット電圧をキャンセルすることが可能となる。(1)の区間では図9のCMOS SWは“OFF”している為、影響を与えない。

【0022】

図10で本発明の実施の形態例を示しているように、コンパレータの追加により減算回路部のオフセットをなくすことにより、後段に接続される回路にオフセットが伝搬しない点が有効である。

【0023】

なお以上の動作は、図8の第一の実施の形態でも、コンパレータの出力をNMOSトランジスタTN1に入力することにより同様の動作が得られる。

【0024】

コンパレータにはヒステリシスを有する回路があるが、本実施形態に利用するコンパレータには使用できない。図13は、本実施形態でヒステリシスを有するコンパレータを用い、入力Vref電圧は固定電圧とし、Vinを0VからVDD電圧の幅で入力した場合の各電圧変化を示している。このとき、入力Vinの印加の仕方(Vin=VDD⇒0V、またはVin=0V⇒VDD)によって出力Ampoutが、コンパレータのヒステリシスのため図のように変化する。

(Vin=VDD⇒0V)の印加の場合、

コンパレータのヒステリシス幅の影響によりCMOS SWが”OFF”している為、数mVのオフセットが発生してしまう。本回路の特徴である オフセットキャンセルが出来ていない区間が発生してしまう。

(Vin=0V⇒VDD)の印加の場合、

Vin電圧がコンパレータのヒステリシス分の電圧を超えないと、CMOS SWが”OFF”しない。その為、CMOS SWが”ON”しており、Ampoutの電圧を”0”Vまで引っぱってしまう。

このように、コンパレータはヒステリシス有りを使用出来ない為、図12に示すように容量Cを追加する。容量Cを追加することにより、コンパレータの応答特性を下げ、高周波のノイズをキャンセルすることが出来る。容量Cの大きさは、キャンセルするノイズの周波により調整する。

【0025】

図14は、オペアンプ補償回路の一構成例の説明図で、減算回路とボルテージフォロワの回路構成に本発明のオペアンプ補償回路とコンパレータを接続した回路構成である。減算回路のオフセットをキャンセルすることにより、ボルテージフォロワの出力にオフセットが出力されないようにしている。

【0026】

図15は、本発明のオペアンプ補償回路の他の構成例の説明図で、減算回路とVI変換回路の回路構成に本発明のオペアンプ補償回路とコンパレータを接続した回路構成である。減算回路のオフセットをキャンセルすることにより、VI変換回路の出力にオフセットが出力されないようにしている。

【技術分野】

【0001】

本発明は、オフセット電位の補償されたオペアンプ補償回路に関する。

【背景技術】

【0002】

オペアンプは、電子回路の基本となる増幅器で、応用範囲も広く、多用されている。近年、技術の開発、応用が進む中で、オペアンプのオフセットの問題が極めて重要な問題となっている。現在、一般に使用されているICでは、オフセット電圧の値は1mV程度であるが、1mVでも許容出来ない状況も発生する。これを、減算回路を例として説明する。

【0003】

減算回路は、ある信号の中から不要な信号を取り除き有効な信号のみを出力させたい場合に使用する。オペアンプと抵抗の組み合せにより実現可能なアナログ回路としては、加算回路と並んで重要な回路構成となる。

【0004】

図1は、従来の減算回路の例を示した説明図であり、図1のような回路構成となっている。減算回路は、“Vin”、“Vref”電圧が入力される。“Vref”端子の電圧は基準電圧となる為、固定電圧となる。Vinは0VからVDD電圧の幅で入力される。R1、R2、R3、R4の抵抗値はR2/R1=R4/R3を満たすように決定する。本例の回路では、R1:R2:R3:R4=1:1:1:1の抵抗値に設定するとする。その場合、オペアンプA1の入力ノード”A”の電位は、A=Vin/2[V](A=Vin*R4/(R3+R4)より)、ノード”B”の電位は、仮想短絡(フィードバックをかけたオペアンプの二つの入力はいつも同電位となる)によりB=Aとなる。図2は、本例の減算回路の動作を示した説明図であり、横軸、縦軸ともに電圧値を示している。また、Vrefを固定電圧とし、Vinを0[V]より増加した場合の動作を示している。図で、減算回路の出力電圧“Ampout”は、“Vin>Vref”の場合(図2(1)の区間)、“Ampout=Vin−Vref”となり、“Vin”端子と“Vref端子”の電位差が出力される。“Vref>=Vin”の電圧が入力された場合(図2(2)の区間)は、Vin−Vref<=0となる為、0[V]が出力される。

【0005】

Vref>=Vinの場合、理想上は0[V]が出力されるが、実際にはオペアンプA1の回路構成上、0[V]にはならず数mV程度の電位浮きが発生する。図3は、このような減算回路のオフセット発生の不具合現象を示した説明図である。(2)Vref>=Vinの部分を拡大している。図4は、オフセット発生に係る電流経路を示した説明図である。図4に示すように、減算回路の特性上、0V出力時、R1、R2、オペアンプA1の出力バッファ部M1の経路で電流が流れる。M1素子のON抵抗を小さくしなければ、“Ampout”の出力電圧の電位浮きが発生する。しかし、オペアンプA1の出力バッファのゲート電圧はA級、AB級出力バッファ(すなわち、それぞれA級増幅回路、AB級増幅回路)を用いても、ゲート電圧を印加する各A〜Cのノードの電位をVDDにすることは出来ない。このため、M1素子のWサイズを大きくする以外に、ON抵抗を十分小さくすることは困難となる。

【0006】

“Vin>Vref”の場合は、“Ampout”の出力電圧は“Vin−Vref”となり、この1mV程度の電位の浮きはそれほど問題にならない。しかし、“Vref>=Vin”の場合は、出力電圧は“0”Vを期待しているため、1mV程度の浮きですら問題となる場合が多い。

【0007】

図5に出力電圧浮きにより不具合が発生する回路構成例を示す。これは減算回路で、電

流発生回路を駆動する例である。電流発生回路は、電流発生回路アンプA2と、電源と接地間に直列接続されたMOSトランジスタと抵抗RSINKを接続した構成である。電流発生回路アンプA2の出力がMOSトランジスタに入力し、MOSトランジスタと抵抗RSINK間の出力電圧FBoutが電流発生回路アンプA2の入力にフィードバックされる。この回路構成では、減算回路により“Ampout”に、“Vin”端子と“Vref”端子の電圧差“Vin−Vref”電圧が出力される。“Ampout”電圧が後段の電流発生回路アンプA2の仮想短絡により、“FBout=Ampout”となる。FBout電圧とRSINK抵抗により、MOSトランジスタ端のIsinkout端子に“FBout[V]/RSINK[Ω]”のシンク電流が流れる。RSINK抵抗値は数百Ω程度である。このようすを図6に示す。

“Vin>Vref”の場合((1)の区間)では、“Ampout=FBout>0V”となり、シンク電流“Isink=FBout/RSINK”が流れる。RSINK抵抗値は数Ω程度の為、“Isinkout”の電流は数mA程度となる。“Vref>=Vin”の場合((2)区間)では、“Ampout=FBout=0V”の為、Isinkout端子シンクの電流は0[μA]となるはずである。しかし、減算回路のオフセットが1[mV]発生すると仮定し、RSINK抵抗値を100Ωに設定したとすると、“Isinkout”端子シンクの電流は10μA流れることになる(Vref>=Vin条件で、Isinkout端子に流れるシンク電流をリーク電流と呼ぶ)。一般的に(2)の区間のシンク電流のSPECは、±1μA程度である。SPEC±1μAに抑えるためには、2つの手法が考えられる。

(1)RSINK抵抗値を数百Ω程度から数kΩ(10倍にする)。

ただし、この方法では図7のように(2)区間のリーク電流を制限する事が可能だが、(1)区間のシンク電流も1/10となる為、実用的ではない。

(2)オフセット電圧を数mVから数百μV(1/10)にする。

【0008】

減算回路のオフセットをなくすことにより、図6の(2)区間の“Ampout”端子の電位浮きを抑えることが可能となる。さらに、図5の(2)のオペアンプの仮想短絡により、“Ampout=FBout”となるため、“Ampout”端子の電位を抑えることになり、結果的にIsinkout端子のリーク電流を抑える事が可能となる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2001−244759号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

以上のような問題点から本願発明は、出力バッファを有するオペアンプであつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供することを課題とする。

【課題を解決するための手段】

【0011】

本発明は係る課題に鑑みなされたものであり、請求項1の発明は、出力バッファを有するオペアンプであつて、バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタを有し、オフセット電位が接地となることを特徴とするオペアンプ補償回路としたものである。

【0012】

本発明の請求項2の発明は、MOSトランジスタが、Nチャンネルトランジスタと、Pチャンネルトランジスタとを並列接続した構成で、それぞれ入力信号と反転された入力信号が入力されていることを特徴とする請求項1に記載のオペアンプ補償回路としたものである。

【0013】

本発明の請求項3の発明は、入力信号が、オペアンプの入力と同じ信号が入力している

比較回路の出力信号であることを特徴とする請求項1または請求項2に記載のオペアンプ補償回路としたものである。

【発明の効果】

【0014】

本発明のオペアンプ補償回路は以上のような構成であるので、出力バッファを有するオペアンプであつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路とすることができる。

【図面の簡単な説明】

【0015】

【図1】従来の減算回路の例を示した説明図である。

【図2】図1の例の減算回路の動作を示した説明図である。

【図3】減算回路のオフセット発生の不具合現象を示した説明図である。

【図4】減算回路のオフセット発生の不具合現象を示した他の説明図である。

【図5】出力電圧浮きにより不具合が発生する回路構成例を示す。

【図6】図5の回路構成のRSINK電流による電圧変化を示す説明図である。

【図7】図5のRSINK抵抗をパラメタとした電圧変化を示す説明図である。

【図8】本発明のオペアンプ補償回路の第一実施形態を示す説明図である。

【図9】本発明のオペアンプ補償回路の第二の実施形態を示す説明図である。

【図10】本発明のオペアンプ補償回路の第三の実施形態を示す説明図である。

【図11】本発明のオペアンプ補償回路の第三の実施形態の動作を説明する図である。

【図12】本発明に使用できるヒステリシスの有るコンパレータの説明図である。

【図13】図10の回路構成で、ヒステリシスの有るコンパレータを使用した場合の説明図である。

【図14】本発明のオペアンプ補償回路を用い、減算回路、コンパレータ、ボルテージフォロワの回路構成とした例の説明図である。

【図15】本発明のオペアンプ補償回路を用い、減算回路、コンパレータ、VI変換回路の構成とした説明図である。

【発明を実施するための形態】

【0016】

以下本発明を実施するための形態につき説明する。図8は、本発明のオペアンプ補償回路の第一実施形態を示す説明図である。本オペアンプ補償回路は、出力バッファを有するオペアンプA1であつて、バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるNMOSトランジスタを有している。入力信号が電源電圧の大きさで入力することによってオフセット電位が接地となる。図8は、出力バッファを有するオペアンプ回路A1に抵抗R1、R2、R3、R4を接続した減算回路を構成している。そしてこのオ

ペアンプの出力と接地間にNMOSトランジスタT1が接続されている。NMOSトランジスタT1には接地から電源電圧まで変化する入力信号が入力する。減算回路の入力Vrefは、図1と同様に、通常は、“Vref”端子の電圧は基準電圧となる為、固定電圧となる。Vinは0VからVDD電圧の幅で入力される。

【0017】

Vref>=Vin時にNMOSトランジスタT1をON、Vref<=Vin時にOFFさせる。このNMOSトランジスタT1のゲート電圧は0V〜VDD電圧幅で振幅する為、NMOSのゲート電圧を高く取ることが出来、ON抵抗を小さくすることができる。そして、ノード“Ampout”を0[V]までダウンさせる。NMOSトランジスタT1のサイズは、Wはレイアウト面積に問題ないように可能な限り大きくし、Lはプロセスの最小で設計するとよい。

【0018】

図9は、本発明のオペアンプ補償回路の第二の実施形態を示す説明図である。図で示すように、第一の実施形態のNMOSトランジスタT1を、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続したものとしている。そして、それぞれ入力信号と、インバータINV1を介して反転された入力信号とが入力されている。NMOS素子単体ではなく、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続したSW構成にすることにより、レイアウト面積は大きくなるが、オフセット電圧をNMOS単体の場合より抑えることが可能となる。

【0019】

図10は、本発明のオペアンプ補償回路の第三の実施形態を示す説明図である。図で示すように、本実施形態は、第二の実施形態の入力信号を、オペアンプA1の入力と同じ信号Vref、Vinが入力している比較回路A2の出力信号Compoutとしている。NMOSトランジスタTN1のゲートに、“Vin”と“Vref”のコンパレータの出力“Compout”を接続することにより、Vin>Vref時、コンパレータの出力“Compout”は“L”、Vref>=Vin時、“H”を出力する。コンパレータの出力は0V⇔VDDの電圧幅を確保出来るため、Vref>=Vin時、オペアンプ単体の場合より、Ampoutを0Vに近づけることが可能となる。Vin>Vref時、NMOSトランジスタTN1はオフしているため、影響しない。

【0020】

図11に本第三の実施形態の動作を示す。オペアンプA1の出力は、AB級バッファを例示している。Vref>=Vinの場合、“Compout”電圧は“H”となり、CMOS

SWはONとなる。これにより、“Ampout”を“L”とする経路が、図11の抵抗とバッファトランジスタを経由して接地する経路(1)と、抵抗とCMOS SWを経由して接地する経路(2)との2つとなる。経路(2)の効果により、“Ampout”の電位浮きが改善される。

【0021】

本実施の形態例のコンパレータを追加することにより、図3の(2)の区間で発生するオフセット電圧をキャンセルすることが可能となる。(1)の区間では図9のCMOS SWは“OFF”している為、影響を与えない。

【0022】

図10で本発明の実施の形態例を示しているように、コンパレータの追加により減算回路部のオフセットをなくすことにより、後段に接続される回路にオフセットが伝搬しない点が有効である。

【0023】

なお以上の動作は、図8の第一の実施の形態でも、コンパレータの出力をNMOSトランジスタTN1に入力することにより同様の動作が得られる。

【0024】

コンパレータにはヒステリシスを有する回路があるが、本実施形態に利用するコンパレータには使用できない。図13は、本実施形態でヒステリシスを有するコンパレータを用い、入力Vref電圧は固定電圧とし、Vinを0VからVDD電圧の幅で入力した場合の各電圧変化を示している。このとき、入力Vinの印加の仕方(Vin=VDD⇒0V、またはVin=0V⇒VDD)によって出力Ampoutが、コンパレータのヒステリシスのため図のように変化する。

(Vin=VDD⇒0V)の印加の場合、

コンパレータのヒステリシス幅の影響によりCMOS SWが”OFF”している為、数mVのオフセットが発生してしまう。本回路の特徴である オフセットキャンセルが出来ていない区間が発生してしまう。

(Vin=0V⇒VDD)の印加の場合、

Vin電圧がコンパレータのヒステリシス分の電圧を超えないと、CMOS SWが”OFF”しない。その為、CMOS SWが”ON”しており、Ampoutの電圧を”0”Vまで引っぱってしまう。

このように、コンパレータはヒステリシス有りを使用出来ない為、図12に示すように容量Cを追加する。容量Cを追加することにより、コンパレータの応答特性を下げ、高周波のノイズをキャンセルすることが出来る。容量Cの大きさは、キャンセルするノイズの周波により調整する。

【0025】

図14は、オペアンプ補償回路の一構成例の説明図で、減算回路とボルテージフォロワの回路構成に本発明のオペアンプ補償回路とコンパレータを接続した回路構成である。減算回路のオフセットをキャンセルすることにより、ボルテージフォロワの出力にオフセットが出力されないようにしている。

【0026】

図15は、本発明のオペアンプ補償回路の他の構成例の説明図で、減算回路とVI変換回路の回路構成に本発明のオペアンプ補償回路とコンパレータを接続した回路構成である。減算回路のオフセットをキャンセルすることにより、VI変換回路の出力にオフセットが出力されないようにしている。

【特許請求の範囲】

【請求項1】

出力バッファを有するオペアンプであつて、

バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタを有し、オフセット電位が接地となることを特徴とするオペアンプ補償回路。

【請求項2】

MOSトランジスタが、Nチャンネルトランジスタと、Pチャンネルトランジスタとを並列接続した構成で、それぞれ入力信号と反転された入力信号が入力されていることを特徴とする請求項1に記載のオペアンプ補償回路。

【請求項3】

入力信号が、オペアンプの入力と同じ信号が入力している比較回路の出力信号であることを特徴とする請求項1または請求項2に記載のオペアンプ補償回路。

【請求項1】

出力バッファを有するオペアンプであつて、

バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタを有し、オフセット電位が接地となることを特徴とするオペアンプ補償回路。

【請求項2】

MOSトランジスタが、Nチャンネルトランジスタと、Pチャンネルトランジスタとを並列接続した構成で、それぞれ入力信号と反転された入力信号が入力されていることを特徴とする請求項1に記載のオペアンプ補償回路。

【請求項3】

入力信号が、オペアンプの入力と同じ信号が入力している比較回路の出力信号であることを特徴とする請求項1または請求項2に記載のオペアンプ補償回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−106178(P2013−106178A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−248580(P2011−248580)

【出願日】平成23年11月14日(2011.11.14)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月14日(2011.11.14)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

[ Back to top ]