オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】第1バッファ10の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第2バッファ12の電源端子には、第1電源からの第1電源電圧VCC1が供給される。非反転アンプ14の電源端子には、第2電源電圧VCC2が供給される。起動電圧源16は、その電源端子に第2電源電圧VCC2を受け、起動電圧VSTARTを生成する。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW1をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW1をオフする。

【解決手段】第1バッファ10の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第2バッファ12の電源端子には、第1電源からの第1電源電圧VCC1が供給される。非反転アンプ14の電源端子には、第2電源電圧VCC2が供給される。起動電圧源16は、その電源端子に第2電源電圧VCC2を受け、起動電圧VSTARTを生成する。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW1をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW1をオフする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、オーディオ信号を処理するオーディオ信号処理回路に関する。

【背景技術】

【0002】

スピーカやヘッドホン端子を備える電子機器には、オーディオ信号を増幅するオーディオ信号処理回路が搭載される。一般に、オーディオ信号処理回路は、直列に接続された複数のステージのアンプあるいはバッファを備える。

【0003】

オーディオ信号の振幅は、後段のステージほど大きくなる。したがって効率の観点からは、複数のステージのアンプに対して、異なる電源電圧を供給することが好ましい。具体的には、前段のアンプには低い電源電圧を供給し、後段のアンプには高い電源電圧を供給することにより、低歪化、高効率化を両立できる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−117489号公報

【特許文献2】特開2005−217710号公報

【特許文献3】特開2004−222077号公報

【特許文献4】特開平11−340759号公報

【特許文献5】特開2003−283262号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明者は、マルチステージのアンプについて検討した結果、以下の課題を認識するに至った。

図1は、本発明者が検討した2段のアンプを含むオーディオ信号処理回路の構成を示すブロック図である。前段の第1アンプAMP1は、利得1のバッファ(ボルテージフォロア)であり、その電源端子には第1電源電圧VCC1が供給される。後段の第2アンプAMP2は、利得g2を有する非反転増幅器であり、その電源端子には第1電源電圧VCC1よりも高い第2電源電圧VCC2が供給される。

【0006】

第2アンプAMP2の出力は、直流防止キャパシタC1を介してパワーアンプPAに供給される。パワーアンプPAは、第2アンプAMP2の出力信号を増幅し、スピーカやヘッドホンなどの電気音響変換素子(以下、スピーカという)SPKへと供給する。

【0007】

通常の動作状態(非ミュート状態)において、第1アンプAMP1の入力電圧および出力電圧Vaの直流レベルは、所定のバイアス電圧VBIAS1に保たれている。好ましくはバイアス電圧VBIAS1は、第1アンプAMP1に対する電源電圧VCC1の中点電圧VCC1/2である。オーディオ信号S1の交流信号成分をVsigと書くとき、第1アンプAMP1の出力Vaは、式(1)で与えられる。

Va=Vsig+VBIAS1 …(1)

【0008】

第1アンプAMP1には、ミュート機能が設けられる。第1アンプAMP1は、ミュート状態において所定のバイアス電圧VBIAS1を出力する。第1アンプAMP1は、ミュート状態と非ミュート状態がシームレスに切りかえ可能に構成され、アンプAMP1と一体に構成される場合もある。オーディオ信号処理回路100rの起動時には、第1アンプAMP1はミュート状態に設定される。

【0009】

一方、第2アンプAMP2の出力電圧Vbは、その入力電圧Vaとバイアス電圧VBIAS3を用いて式(1)で与えられる。

Vb=(1+R1/R2)×Va−R1/R2×VBIAS3 …(2)

(1+R1/R2)は、第2アンプAMP2の利得g2である。

【0010】

式(2)に式(1)を代入すると、式(3)を得る。

Vb=g2×Vsig+VBIAS2 …(3)

VBIAS2={(1+R1/R2)×VBIAS1−R1/R2×VBIAS3}

つまり、第2アンプAMP2の出力電圧Vbは、直流レベルVBIAS2に、利得g2で増幅された信号Vsigが重畳された波形となる。

【0011】

第2アンプAMP2の出力電圧Vbの直流レベルVBIAS2は、第2アンプAMP2に対する電源電圧VCC2の中点電圧VCC2/2であることが望ましい。バイアス電圧VBIAS3は、VBIAS2=VCC2/2が成り立つように設定される。

【0012】

バイアス電圧VBIAS2が一定であれば、直流阻止用キャパシタC1によって除去され、パワーアンプPAには、オーディオ信号Vb’=g2×Vsigが供給される。パワーアンプPAは、第2アンプAMP2の出力信号を増幅し、スピーカやヘッドホンなどの電気音響変換素子(以下、スピーカという)SPKへと供給する。

【0013】

いま、第2電源電圧VCC2が第1電源電圧VCC1よりも先に立ち上がる状況について検討する。図2は、図1のオーディオ信号処理回路100rの動作を示す波形図である。第2電源電圧VCC2が十分に高い状況では、第2アンプAMP2が正常に動作し、第2アンプAMP2の出力電圧Vbは、入力電圧Vaに応じたレベルとなる。ところが、第2電源電圧VCC2が低い状態では、第2アンプAMP2が正常に動作しない。本明細書において、電源電圧が高くアンプが正常動作する領域を「安定領域」、電源電圧が低くアンプが正常動作しない領域を「不安定領域」と称し、そのしきい値電圧を、「安定動作しきい値」と称する。また、起動直後に、第2アンプAMP2が不安定領域で動作する期間を「遷移期間」と称する。

【0014】

一方、第1電源電圧VCC1が低いと、第1アンプAMP1が不安定領域で動作するため、第1アンプAMP1の出力はハイインピーダンスとなり、その出力電圧Vaは不定となる。図2に示すように、第2アンプAMP2が不安定領域で動作するときに、その入力電圧Vaが不定であると、その出力電圧Vbは、電源電圧VCC2に向けて急激に増大し、その後、電源電圧VCC2に張り付いて遷移する。

【0015】

その後、第1アンプAMP1に対する第1電源電圧VCC1が増大すると、第1アンプAMP1が正常に動作するようになり、第1アンプAMP1の出力電圧のレベルが確定する。その結果、第2アンプAMP2の出力電圧Vbは、第1アンプAMP1の出力電圧に応じたレベルに向かって急峻に変化する。

【0016】

このようにして第2アンプAMP2の出力に生ずる電圧変化がスピーカSPKに入力されるとノイズ(ショック音)が出力される。電圧変化幅が小さい場合、ミュートトランジスタTr1によって除去することが可能であるが、変化幅が1V以上になると、ミュートトランジスタTr1では除去することが難しくなる。

【0017】

このようにアンプごとに異なる電源電圧を供給する場合、オーディオ信号処理回路の出力電圧は、各電源電圧を生成する電源回路の立ち上げシーケンスの影響を受ける。

2つの電源電圧VCC1、VCC2の起動シーケンスを、ノイズが発生しないように最適化することにより、ノイズを抑制することは可能であるが、この手法では、システムの設計が複雑となる。

【0018】

本発明は係る課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、ノイズを抑制したオーディオ信号処理回路の提供にある。

【課題を解決するための手段】

【0019】

本発明のある態様は、オーディオ信号処理回路に関する。オーディオ信号処理回路は、第1バッファと、第2バッファと、非反転アンプと、起動電圧源と、スイッチと、制御回路と、を備える。第1バッファは、その電源端子に第1電源からの第1電源電圧を受け、その非反転入力端子にオーディオ信号を受け、その反転入力端子がその出力端子と接続された第1演算増幅器を含む。第2バッファは、その非反転入力端子に所定のバイアス電圧を受け、その反転入力端子がその出力端子と接続された第2演算増幅器を含む。非反転アンプは、その電源端子に第1電源と異なる第2電源からの第2電源電圧を受け、その非反転入力端子に第1演算増幅器の出力電圧が入力された第3演算増幅器と、第2演算増幅器の出力電圧と第3演算増幅器の出力電圧を分圧し、第3演算増幅器の反転入力端子に印加する第1分圧回路と、を含む。起動電圧源は、その電源端子に第2電源電圧を受け、起動電圧を生成する。スイッチは、起動電圧源の出力端子と第3演算増幅器の非反転入力端子の間に設けられる。制御回路は、第2電源電圧が所定のしきい値電圧より低いときにスイッチをオンし、第2電源電圧がしきい値電圧より高いときにスイッチをオフする。

【0020】

第1電源電圧が第2電源電圧より遅れて起動する場合に、第1バッファの出力はハイインピーダンス状態となる。一方、起動電圧源は、第2電源電圧を受けて動作するため、起動電圧は、第1バッファよりも早い時刻に確定する。第2アンプの遷移期間において、スイッチをオンすることにより、非反転アンプには、起動電圧源からの起動電圧が入力される。その結果、遷移期間における非反転アンプの出力電圧は、第2電源電圧には張り付かずに、起動電圧に応じた値をとり、第2アンプの出力電圧に発生する電圧変化を抑制でき、ノイズを低減できる。

【0021】

起動電圧源は、第2電源電圧を受けて、バイアス電圧を生成する電圧源と、その電源端子に第2電源電圧を受け、その非反転入力端子に電圧源からのバイアス電圧を受け、その反転入力端子がその出力端子と接続された第4演算増幅器を含み、起動電圧を生成する第4バッファと、を備えてもよい。

電圧源は、第2電源電圧を分圧する第2分圧回路を含んでもよい。

【0022】

ある態様のオーディオ信号処理回路は、第1演算増幅器、第2演算増幅器、第3演算増幅器、起動電圧源およびスイッチのセットを複数チャンネル備えてもよい。単一の起動電圧源および単一の制御回路が、複数チャンネルで共有されてもよい。

【0023】

本発明の別の態様は、電子機器に関する。この電子機器は、上述のいずれかの態様のオーディオ信号処理回路と、オーディオ信号処理回路の非反転アンプの出力信号を直流防止キャパシタを介して受け、それを増幅するパワーアンプと、パワーアンプにより駆動される電気音響変換素子と、を備える。

【0024】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0025】

本発明に係るオーディオ信号処理回路によれば、ノイズを抑制できる。

【図面の簡単な説明】

【0026】

【図1】本発明者が検討した2段のアンプを含むオーディオ信号処理回路の構成を示すブロック図である。

【図2】図1のオーディオ信号処理回路の動作を示す波形図である。

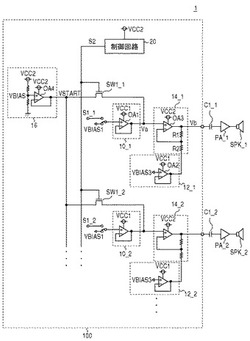

【図3】実施の形態に係るオーディオ信号処理回路を備える電子機器の構成を示す回路図である。

【図4】図3の制御回路の構成例を示す回路図である。

【図5】図4の制御回路の動作を示す波形図である。

【図6】図3のオーディオ信号処理回路の動作を示すシミュレーション波形図である。

【発明を実施するための形態】

【0027】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0028】

本明細書において、「部材Aと部材Bが接続」された状態とは、部材Aと部材Bが物理的に直接的に接続される場合や、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0029】

図3は、実施の形態に係るオーディオ信号処理回路100を備える電子機器1の構成を示す回路図である。電子機器1は、マルチチャンネルのオーディオ信号を再生する。電子機器1は、オーディオ信号処理回路100と、チャンネルごとに設けられたパワーアンプPAと、チャンネルごとに設けられたスピーカやヘッドホンなどの電気音響変換素子(以下、スピーカと総称する)SPKと、を備える。

【0030】

オーディオ信号処理回路100の各チャンネルは同様に構成される。i番目(iは自然数)のチャンネルに関して、オーディオ信号処理回路100は、第1バッファ10_i、第2バッファ12_i、非反転アンプ14_i、スイッチSW1_i、起動電圧源16、制御回路20を備え、ひとつの半導体基板上に一体集積化される。「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。起動電圧源16および制御回路20は、複数のチャンネルで共有される。

【0031】

オーディオ信号処理回路100は、図示しない第1電源から第1電源電圧VCC1を受け、それとは別の図示しない第2電源から第2電源電圧VCC2を受ける。

【0032】

第1バッファ10_iは、第1演算増幅器OA1を含む。第1演算増幅器OA1の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第1演算増幅器OA1の非反転入力端子(+)には、対応するチャンネルのオーディオ信号S1_iが入力され、その反転入力端子(−)は、その出力端子と接続される。第1バッファ10_iは、利得1倍(0dB)のボルテージフォロアである。

【0033】

第2バッファ12_iは、第2演算増幅器OA2を含む。第2演算増幅器OA2の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第2演算増幅器OA2の非反転入力端子(+)には、所定のバイアス電圧VBIAS3が入力され、その反転入力端子(−)はその出力端子と接続される。バイアス電圧VBIAS3は、非反転アンプ14_1の出力電圧Vbの直流レベルVBIAS2が、VCC2/2となるように定めることが望ましい。

【0034】

第2演算増幅器OA2に第1電源電圧VCC1を供給することにより、第2電源電圧VCC2を供給する場合に比べて、第2演算増幅器OA2を低耐圧素子で構成できるため、回路面積を小さくできる。

【0035】

なお、回路面積が問題とならない場合、第2演算増幅器OA2に第2電源電圧VCC2を供給することが好ましい。これにより、第2電源電圧VCC2が立ち上がる際に、起動電圧源16の出力VSTARTと第2バッファ12の出力電圧VBIASを、一致して上昇させることができる。

【0036】

非反転アンプ14_iは、第3演算増幅器OA3、第1分圧回路R1、R2を含む。第3演算増幅器OA3の電源端子には、第2電源からの第2電源電圧VCC2が供給される。第3演算増幅器OA3の非反転入力端子(+)には、第1演算増幅器OA1の出力電圧が入力される。分圧回路R1、R2は、第2演算増幅器OA2の出力電圧と第3演算増幅器OA3の出力電圧を分圧し、第3演算増幅器OA3の反転入力端子(−)に印加する。非反転アンプ14_iは、(1+R1/R2)で与えられる利得g2を有する。

【0037】

起動電圧源16の電源端子には、第2電源電圧VCC2が供給される。起動電圧源16は、第2電源電圧VCC2が供給されると、起動電圧VSTARTを生成する。たとえば起動電圧源16は、第2分圧回路R3、R4と、第4演算増幅器OA4を含んでもよい。第2分圧回路R3、R4は、第2電源電圧VCC2を1/2分圧し、バイアス電圧VBIAS=VCC2/2を生成する。第4演算増幅器OA4の電源端子には、第2電源電圧VCC2が供給される。第4演算増幅器OA4の非反転入力端子(+)には、第2分圧回路R3、R4の出力電圧VBIASが入力され、その反転入力端子(−)はその出力端子と接続される。第4演算増幅器OA4からは、起動電圧VSTARTが出力される。

なお起動電圧源16は、第2電源電圧VCC2にもとづいて、起動電圧VSTARTを生成できればよく、その構成は特に限定されない。たとえば抵抗R3、R4とは別の形式の電圧源によって、バイアス電圧VBIASを生成してもよい。

【0038】

スイッチSW1_iは、起動電圧源16の出力端子と、対応する非反転アンプ14_iの第3演算増幅器OA3の非反転入力端子(+)の間に設けられる。たとえばスイッチSW1_iは、NチャンネルMOSFETで構成され、そのゲートに印加される制御信号S2がハイレベル電圧のときオン、ローレベル電圧のときオフする。

【0039】

制御回路20は、第2電源電圧VCC2を受け、第2電源電圧VCC2が所定のしきい値電圧Vth1より低いときに、各チャンネルのスイッチSW1をオンし、第2電源電圧VCC2がしきい値電圧Vth1より高いときに各チャンネルのスイッチSW1をオフする。

【0040】

図4は、図3の制御回路20の構成例を示す回路図である。制御回路20は、第1抵抗Ra1〜第3抵抗Ra3、トランジスタM1、キャパシタC2を有する。第1抵抗Ra1および第2抵抗Ra2は、第2電源電圧VCC2が印加される電源ラインと、接地電圧VSSが供給される接地ラインの間に順に直列に設けられる。第3抵抗Ra3およびトランジスタM1は、電源ラインと接地ラインの間に順に直列に設けられる。トランジスタM1の制御端子(ゲート)には、式(4)で与えられる第1抵抗Ra1と第2抵抗Ra2の接続点N1の電位VN1が印加される。

VN1=VCC2×Ra2/(Ra1+Ra2) …(4)

トランジスタM1と第3抵抗Ra3の接続点N2の電圧VN2が、キャパシタC2によって平滑化され、制御信号S2が生成される。

【0041】

制御信号S2は、ノードN1の電圧VN1がトランジスタM1のゲートソース間しきい値電圧VTHより小さいときにハイレベル、大きいときにローレベルとなる。そして制御信号S2は、VCC2<Vth1のときにハイレベル(VCC2)、VCC2>Vth1のときにローレベル(VSS=0)となる。しきい値電圧Vth1は、式(5)で与えられる。

Vth1=VTH×(Ra1+Ra2)/Ra2 …(5)

【0042】

制御回路20は、しきい値電圧Vth1が非反転アンプ14の不安定領域と安定領域の境界のしきい値電圧と一致するように設計される。図5は、図4の制御回路20の動作を示す波形図である。第2電源が起動すると、第2電源電圧VCC2が時間とともに上昇する。第2電源電圧VCC2がしきい値電圧Vth1より低い領域では、S2=VCC2となる。第2電源電圧VCC2がしきい値電圧Vth1より高くなると、制御信号S2はローレベルとなる。上述のようにしきい値電圧Vth1は、非反転アンプ14の安定動作しきい値と等しく設定されるため、制御信号S2は、遷移期間τにおいてハイレベル、その後の安定動作期間においてローレベルをとる。

【0043】

以上がオーディオ信号処理回路100の構成である。続いてその動作を説明する。図6は、図3のオーディオ信号処理回路100の動作を示すシミュレーション波形図である。図6には、第1電源電圧VCC1、第2電源電圧VCC2、制御信号S2および非反転アンプ14の出力電圧Vbが示される。併せて、図1において生成される出力電圧Vb’を一点鎖線で示す。

【0044】

はじめに、実施の形態に係るオーディオ信号処理回路100の効果を明確とするため、図1のオーディオ信号処理回路100rの動作を再度説明する。

起動時に、第1バッファ10はミュート状態に設定され、オーディオ信号S1が遮断される。第1電源電圧VCC1に先立ち、第2電源電圧VCC2が立ち上がり始める。起動直後において、第1電源電圧VCC1が低いため、第1バッファ10が動作せず、したがって第1バッファ10の出力はハイインピーダンスとなり、その出力電圧Vaは不定となる。

【0045】

起動直後の遷移期間τにおいて、非反転アンプ14は不安定領域で動作する。このときにその入力電圧Vaが不定であると、その出力電圧Vbは第2電源電圧VCC2に向けて急峻に上昇する(時刻t1)。続いて第1電源電圧VCC1が立ち上がると、第1バッファ10の出力が低インピーダンスとなり、非反転アンプ14の入力電圧Vaが確定する。そうすると、非反転アンプ14の出力電圧Vbは、入力電圧Vaに応じた電圧レベルへと急峻に変化する(時刻t2)。

【0046】

このように、図1のオーディオ信号処理回路100rでは、第1電源電圧VCC1が第2電源電圧VCC2に遅れて立ち上がると、非反転アンプ14の出力電圧が変動する。

【0047】

続いて、図3のオーディオ信号処理回路100の動作を説明する。

起動電圧源16の第4演算増幅器OA4には、第1電源電圧VCC1ではなく第2電源電圧VCC2が供給される。したがって、起動電圧源16の出力は、第1バッファ10よりも早い時刻に、ハイインピーダンスから低インピーダンスとなり、起動電圧源16からは、起動電圧VSTARTが出力される。

【0048】

第2電源電圧VCC2の上昇とともに制御信号S2が上昇し、スイッチSW1がオンすると、起動電圧VSTARTが非反転アンプ14に入力される(時刻t3)。その結果、非反転アンプ14の出力電圧Vbは、起動電圧VSTARTに応じたレベルへと遷移するが、このときの変化量は、時刻t1における出力電圧Vb’の変化量にくらべて十分に小さい。

【0049】

このように、図3のオーディオ信号処理回路100によれば、図1のオーディオ信号処理回路100rに比べて、遷移期間τにおける、出力電圧Vbの変動を抑制することができる。出力電圧Vbの変化量が小さければ、ミュートトランジスタによって除去することが可能であり、あるいはミュートトランジスタそのものを省略することができる場合もある。

【0050】

さらに、複数チャンネルで、起動電圧源16および制御回路20が共有されるため、図1のオーディオ信号処理回路100rに比べて、消費電力や回路面積もそれほど大きくならない。なお、消費電力や回路面積の増大が許容される場合には、チャンネルごとに起動電圧源16よび制御回路20を設けてもよい。

【0051】

実施の形態では、マルチチャンネルのオーディオ信号処理回路100について説明したが、本発明はシングルチャンネルにおいても有効である。

【0052】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0053】

1…電子機器、100…オーディオ信号処理回路、10…第1バッファ、12…第2バッファ、14…非反転アンプ、16…起動電圧源、SW1…スイッチ、20…制御回路、OA1…第1演算増幅器、OA2…第2演算増幅器、OA3…第3演算増幅器、OA4…第4演算増幅器、VCC1…第1電源電圧、VCC2…第2電源電圧。

【技術分野】

【0001】

本発明は、オーディオ信号を処理するオーディオ信号処理回路に関する。

【背景技術】

【0002】

スピーカやヘッドホン端子を備える電子機器には、オーディオ信号を増幅するオーディオ信号処理回路が搭載される。一般に、オーディオ信号処理回路は、直列に接続された複数のステージのアンプあるいはバッファを備える。

【0003】

オーディオ信号の振幅は、後段のステージほど大きくなる。したがって効率の観点からは、複数のステージのアンプに対して、異なる電源電圧を供給することが好ましい。具体的には、前段のアンプには低い電源電圧を供給し、後段のアンプには高い電源電圧を供給することにより、低歪化、高効率化を両立できる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−117489号公報

【特許文献2】特開2005−217710号公報

【特許文献3】特開2004−222077号公報

【特許文献4】特開平11−340759号公報

【特許文献5】特開2003−283262号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明者は、マルチステージのアンプについて検討した結果、以下の課題を認識するに至った。

図1は、本発明者が検討した2段のアンプを含むオーディオ信号処理回路の構成を示すブロック図である。前段の第1アンプAMP1は、利得1のバッファ(ボルテージフォロア)であり、その電源端子には第1電源電圧VCC1が供給される。後段の第2アンプAMP2は、利得g2を有する非反転増幅器であり、その電源端子には第1電源電圧VCC1よりも高い第2電源電圧VCC2が供給される。

【0006】

第2アンプAMP2の出力は、直流防止キャパシタC1を介してパワーアンプPAに供給される。パワーアンプPAは、第2アンプAMP2の出力信号を増幅し、スピーカやヘッドホンなどの電気音響変換素子(以下、スピーカという)SPKへと供給する。

【0007】

通常の動作状態(非ミュート状態)において、第1アンプAMP1の入力電圧および出力電圧Vaの直流レベルは、所定のバイアス電圧VBIAS1に保たれている。好ましくはバイアス電圧VBIAS1は、第1アンプAMP1に対する電源電圧VCC1の中点電圧VCC1/2である。オーディオ信号S1の交流信号成分をVsigと書くとき、第1アンプAMP1の出力Vaは、式(1)で与えられる。

Va=Vsig+VBIAS1 …(1)

【0008】

第1アンプAMP1には、ミュート機能が設けられる。第1アンプAMP1は、ミュート状態において所定のバイアス電圧VBIAS1を出力する。第1アンプAMP1は、ミュート状態と非ミュート状態がシームレスに切りかえ可能に構成され、アンプAMP1と一体に構成される場合もある。オーディオ信号処理回路100rの起動時には、第1アンプAMP1はミュート状態に設定される。

【0009】

一方、第2アンプAMP2の出力電圧Vbは、その入力電圧Vaとバイアス電圧VBIAS3を用いて式(1)で与えられる。

Vb=(1+R1/R2)×Va−R1/R2×VBIAS3 …(2)

(1+R1/R2)は、第2アンプAMP2の利得g2である。

【0010】

式(2)に式(1)を代入すると、式(3)を得る。

Vb=g2×Vsig+VBIAS2 …(3)

VBIAS2={(1+R1/R2)×VBIAS1−R1/R2×VBIAS3}

つまり、第2アンプAMP2の出力電圧Vbは、直流レベルVBIAS2に、利得g2で増幅された信号Vsigが重畳された波形となる。

【0011】

第2アンプAMP2の出力電圧Vbの直流レベルVBIAS2は、第2アンプAMP2に対する電源電圧VCC2の中点電圧VCC2/2であることが望ましい。バイアス電圧VBIAS3は、VBIAS2=VCC2/2が成り立つように設定される。

【0012】

バイアス電圧VBIAS2が一定であれば、直流阻止用キャパシタC1によって除去され、パワーアンプPAには、オーディオ信号Vb’=g2×Vsigが供給される。パワーアンプPAは、第2アンプAMP2の出力信号を増幅し、スピーカやヘッドホンなどの電気音響変換素子(以下、スピーカという)SPKへと供給する。

【0013】

いま、第2電源電圧VCC2が第1電源電圧VCC1よりも先に立ち上がる状況について検討する。図2は、図1のオーディオ信号処理回路100rの動作を示す波形図である。第2電源電圧VCC2が十分に高い状況では、第2アンプAMP2が正常に動作し、第2アンプAMP2の出力電圧Vbは、入力電圧Vaに応じたレベルとなる。ところが、第2電源電圧VCC2が低い状態では、第2アンプAMP2が正常に動作しない。本明細書において、電源電圧が高くアンプが正常動作する領域を「安定領域」、電源電圧が低くアンプが正常動作しない領域を「不安定領域」と称し、そのしきい値電圧を、「安定動作しきい値」と称する。また、起動直後に、第2アンプAMP2が不安定領域で動作する期間を「遷移期間」と称する。

【0014】

一方、第1電源電圧VCC1が低いと、第1アンプAMP1が不安定領域で動作するため、第1アンプAMP1の出力はハイインピーダンスとなり、その出力電圧Vaは不定となる。図2に示すように、第2アンプAMP2が不安定領域で動作するときに、その入力電圧Vaが不定であると、その出力電圧Vbは、電源電圧VCC2に向けて急激に増大し、その後、電源電圧VCC2に張り付いて遷移する。

【0015】

その後、第1アンプAMP1に対する第1電源電圧VCC1が増大すると、第1アンプAMP1が正常に動作するようになり、第1アンプAMP1の出力電圧のレベルが確定する。その結果、第2アンプAMP2の出力電圧Vbは、第1アンプAMP1の出力電圧に応じたレベルに向かって急峻に変化する。

【0016】

このようにして第2アンプAMP2の出力に生ずる電圧変化がスピーカSPKに入力されるとノイズ(ショック音)が出力される。電圧変化幅が小さい場合、ミュートトランジスタTr1によって除去することが可能であるが、変化幅が1V以上になると、ミュートトランジスタTr1では除去することが難しくなる。

【0017】

このようにアンプごとに異なる電源電圧を供給する場合、オーディオ信号処理回路の出力電圧は、各電源電圧を生成する電源回路の立ち上げシーケンスの影響を受ける。

2つの電源電圧VCC1、VCC2の起動シーケンスを、ノイズが発生しないように最適化することにより、ノイズを抑制することは可能であるが、この手法では、システムの設計が複雑となる。

【0018】

本発明は係る課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、ノイズを抑制したオーディオ信号処理回路の提供にある。

【課題を解決するための手段】

【0019】

本発明のある態様は、オーディオ信号処理回路に関する。オーディオ信号処理回路は、第1バッファと、第2バッファと、非反転アンプと、起動電圧源と、スイッチと、制御回路と、を備える。第1バッファは、その電源端子に第1電源からの第1電源電圧を受け、その非反転入力端子にオーディオ信号を受け、その反転入力端子がその出力端子と接続された第1演算増幅器を含む。第2バッファは、その非反転入力端子に所定のバイアス電圧を受け、その反転入力端子がその出力端子と接続された第2演算増幅器を含む。非反転アンプは、その電源端子に第1電源と異なる第2電源からの第2電源電圧を受け、その非反転入力端子に第1演算増幅器の出力電圧が入力された第3演算増幅器と、第2演算増幅器の出力電圧と第3演算増幅器の出力電圧を分圧し、第3演算増幅器の反転入力端子に印加する第1分圧回路と、を含む。起動電圧源は、その電源端子に第2電源電圧を受け、起動電圧を生成する。スイッチは、起動電圧源の出力端子と第3演算増幅器の非反転入力端子の間に設けられる。制御回路は、第2電源電圧が所定のしきい値電圧より低いときにスイッチをオンし、第2電源電圧がしきい値電圧より高いときにスイッチをオフする。

【0020】

第1電源電圧が第2電源電圧より遅れて起動する場合に、第1バッファの出力はハイインピーダンス状態となる。一方、起動電圧源は、第2電源電圧を受けて動作するため、起動電圧は、第1バッファよりも早い時刻に確定する。第2アンプの遷移期間において、スイッチをオンすることにより、非反転アンプには、起動電圧源からの起動電圧が入力される。その結果、遷移期間における非反転アンプの出力電圧は、第2電源電圧には張り付かずに、起動電圧に応じた値をとり、第2アンプの出力電圧に発生する電圧変化を抑制でき、ノイズを低減できる。

【0021】

起動電圧源は、第2電源電圧を受けて、バイアス電圧を生成する電圧源と、その電源端子に第2電源電圧を受け、その非反転入力端子に電圧源からのバイアス電圧を受け、その反転入力端子がその出力端子と接続された第4演算増幅器を含み、起動電圧を生成する第4バッファと、を備えてもよい。

電圧源は、第2電源電圧を分圧する第2分圧回路を含んでもよい。

【0022】

ある態様のオーディオ信号処理回路は、第1演算増幅器、第2演算増幅器、第3演算増幅器、起動電圧源およびスイッチのセットを複数チャンネル備えてもよい。単一の起動電圧源および単一の制御回路が、複数チャンネルで共有されてもよい。

【0023】

本発明の別の態様は、電子機器に関する。この電子機器は、上述のいずれかの態様のオーディオ信号処理回路と、オーディオ信号処理回路の非反転アンプの出力信号を直流防止キャパシタを介して受け、それを増幅するパワーアンプと、パワーアンプにより駆動される電気音響変換素子と、を備える。

【0024】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0025】

本発明に係るオーディオ信号処理回路によれば、ノイズを抑制できる。

【図面の簡単な説明】

【0026】

【図1】本発明者が検討した2段のアンプを含むオーディオ信号処理回路の構成を示すブロック図である。

【図2】図1のオーディオ信号処理回路の動作を示す波形図である。

【図3】実施の形態に係るオーディオ信号処理回路を備える電子機器の構成を示す回路図である。

【図4】図3の制御回路の構成例を示す回路図である。

【図5】図4の制御回路の動作を示す波形図である。

【図6】図3のオーディオ信号処理回路の動作を示すシミュレーション波形図である。

【発明を実施するための形態】

【0027】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0028】

本明細書において、「部材Aと部材Bが接続」された状態とは、部材Aと部材Bが物理的に直接的に接続される場合や、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0029】

図3は、実施の形態に係るオーディオ信号処理回路100を備える電子機器1の構成を示す回路図である。電子機器1は、マルチチャンネルのオーディオ信号を再生する。電子機器1は、オーディオ信号処理回路100と、チャンネルごとに設けられたパワーアンプPAと、チャンネルごとに設けられたスピーカやヘッドホンなどの電気音響変換素子(以下、スピーカと総称する)SPKと、を備える。

【0030】

オーディオ信号処理回路100の各チャンネルは同様に構成される。i番目(iは自然数)のチャンネルに関して、オーディオ信号処理回路100は、第1バッファ10_i、第2バッファ12_i、非反転アンプ14_i、スイッチSW1_i、起動電圧源16、制御回路20を備え、ひとつの半導体基板上に一体集積化される。「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。起動電圧源16および制御回路20は、複数のチャンネルで共有される。

【0031】

オーディオ信号処理回路100は、図示しない第1電源から第1電源電圧VCC1を受け、それとは別の図示しない第2電源から第2電源電圧VCC2を受ける。

【0032】

第1バッファ10_iは、第1演算増幅器OA1を含む。第1演算増幅器OA1の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第1演算増幅器OA1の非反転入力端子(+)には、対応するチャンネルのオーディオ信号S1_iが入力され、その反転入力端子(−)は、その出力端子と接続される。第1バッファ10_iは、利得1倍(0dB)のボルテージフォロアである。

【0033】

第2バッファ12_iは、第2演算増幅器OA2を含む。第2演算増幅器OA2の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第2演算増幅器OA2の非反転入力端子(+)には、所定のバイアス電圧VBIAS3が入力され、その反転入力端子(−)はその出力端子と接続される。バイアス電圧VBIAS3は、非反転アンプ14_1の出力電圧Vbの直流レベルVBIAS2が、VCC2/2となるように定めることが望ましい。

【0034】

第2演算増幅器OA2に第1電源電圧VCC1を供給することにより、第2電源電圧VCC2を供給する場合に比べて、第2演算増幅器OA2を低耐圧素子で構成できるため、回路面積を小さくできる。

【0035】

なお、回路面積が問題とならない場合、第2演算増幅器OA2に第2電源電圧VCC2を供給することが好ましい。これにより、第2電源電圧VCC2が立ち上がる際に、起動電圧源16の出力VSTARTと第2バッファ12の出力電圧VBIASを、一致して上昇させることができる。

【0036】

非反転アンプ14_iは、第3演算増幅器OA3、第1分圧回路R1、R2を含む。第3演算増幅器OA3の電源端子には、第2電源からの第2電源電圧VCC2が供給される。第3演算増幅器OA3の非反転入力端子(+)には、第1演算増幅器OA1の出力電圧が入力される。分圧回路R1、R2は、第2演算増幅器OA2の出力電圧と第3演算増幅器OA3の出力電圧を分圧し、第3演算増幅器OA3の反転入力端子(−)に印加する。非反転アンプ14_iは、(1+R1/R2)で与えられる利得g2を有する。

【0037】

起動電圧源16の電源端子には、第2電源電圧VCC2が供給される。起動電圧源16は、第2電源電圧VCC2が供給されると、起動電圧VSTARTを生成する。たとえば起動電圧源16は、第2分圧回路R3、R4と、第4演算増幅器OA4を含んでもよい。第2分圧回路R3、R4は、第2電源電圧VCC2を1/2分圧し、バイアス電圧VBIAS=VCC2/2を生成する。第4演算増幅器OA4の電源端子には、第2電源電圧VCC2が供給される。第4演算増幅器OA4の非反転入力端子(+)には、第2分圧回路R3、R4の出力電圧VBIASが入力され、その反転入力端子(−)はその出力端子と接続される。第4演算増幅器OA4からは、起動電圧VSTARTが出力される。

なお起動電圧源16は、第2電源電圧VCC2にもとづいて、起動電圧VSTARTを生成できればよく、その構成は特に限定されない。たとえば抵抗R3、R4とは別の形式の電圧源によって、バイアス電圧VBIASを生成してもよい。

【0038】

スイッチSW1_iは、起動電圧源16の出力端子と、対応する非反転アンプ14_iの第3演算増幅器OA3の非反転入力端子(+)の間に設けられる。たとえばスイッチSW1_iは、NチャンネルMOSFETで構成され、そのゲートに印加される制御信号S2がハイレベル電圧のときオン、ローレベル電圧のときオフする。

【0039】

制御回路20は、第2電源電圧VCC2を受け、第2電源電圧VCC2が所定のしきい値電圧Vth1より低いときに、各チャンネルのスイッチSW1をオンし、第2電源電圧VCC2がしきい値電圧Vth1より高いときに各チャンネルのスイッチSW1をオフする。

【0040】

図4は、図3の制御回路20の構成例を示す回路図である。制御回路20は、第1抵抗Ra1〜第3抵抗Ra3、トランジスタM1、キャパシタC2を有する。第1抵抗Ra1および第2抵抗Ra2は、第2電源電圧VCC2が印加される電源ラインと、接地電圧VSSが供給される接地ラインの間に順に直列に設けられる。第3抵抗Ra3およびトランジスタM1は、電源ラインと接地ラインの間に順に直列に設けられる。トランジスタM1の制御端子(ゲート)には、式(4)で与えられる第1抵抗Ra1と第2抵抗Ra2の接続点N1の電位VN1が印加される。

VN1=VCC2×Ra2/(Ra1+Ra2) …(4)

トランジスタM1と第3抵抗Ra3の接続点N2の電圧VN2が、キャパシタC2によって平滑化され、制御信号S2が生成される。

【0041】

制御信号S2は、ノードN1の電圧VN1がトランジスタM1のゲートソース間しきい値電圧VTHより小さいときにハイレベル、大きいときにローレベルとなる。そして制御信号S2は、VCC2<Vth1のときにハイレベル(VCC2)、VCC2>Vth1のときにローレベル(VSS=0)となる。しきい値電圧Vth1は、式(5)で与えられる。

Vth1=VTH×(Ra1+Ra2)/Ra2 …(5)

【0042】

制御回路20は、しきい値電圧Vth1が非反転アンプ14の不安定領域と安定領域の境界のしきい値電圧と一致するように設計される。図5は、図4の制御回路20の動作を示す波形図である。第2電源が起動すると、第2電源電圧VCC2が時間とともに上昇する。第2電源電圧VCC2がしきい値電圧Vth1より低い領域では、S2=VCC2となる。第2電源電圧VCC2がしきい値電圧Vth1より高くなると、制御信号S2はローレベルとなる。上述のようにしきい値電圧Vth1は、非反転アンプ14の安定動作しきい値と等しく設定されるため、制御信号S2は、遷移期間τにおいてハイレベル、その後の安定動作期間においてローレベルをとる。

【0043】

以上がオーディオ信号処理回路100の構成である。続いてその動作を説明する。図6は、図3のオーディオ信号処理回路100の動作を示すシミュレーション波形図である。図6には、第1電源電圧VCC1、第2電源電圧VCC2、制御信号S2および非反転アンプ14の出力電圧Vbが示される。併せて、図1において生成される出力電圧Vb’を一点鎖線で示す。

【0044】

はじめに、実施の形態に係るオーディオ信号処理回路100の効果を明確とするため、図1のオーディオ信号処理回路100rの動作を再度説明する。

起動時に、第1バッファ10はミュート状態に設定され、オーディオ信号S1が遮断される。第1電源電圧VCC1に先立ち、第2電源電圧VCC2が立ち上がり始める。起動直後において、第1電源電圧VCC1が低いため、第1バッファ10が動作せず、したがって第1バッファ10の出力はハイインピーダンスとなり、その出力電圧Vaは不定となる。

【0045】

起動直後の遷移期間τにおいて、非反転アンプ14は不安定領域で動作する。このときにその入力電圧Vaが不定であると、その出力電圧Vbは第2電源電圧VCC2に向けて急峻に上昇する(時刻t1)。続いて第1電源電圧VCC1が立ち上がると、第1バッファ10の出力が低インピーダンスとなり、非反転アンプ14の入力電圧Vaが確定する。そうすると、非反転アンプ14の出力電圧Vbは、入力電圧Vaに応じた電圧レベルへと急峻に変化する(時刻t2)。

【0046】

このように、図1のオーディオ信号処理回路100rでは、第1電源電圧VCC1が第2電源電圧VCC2に遅れて立ち上がると、非反転アンプ14の出力電圧が変動する。

【0047】

続いて、図3のオーディオ信号処理回路100の動作を説明する。

起動電圧源16の第4演算増幅器OA4には、第1電源電圧VCC1ではなく第2電源電圧VCC2が供給される。したがって、起動電圧源16の出力は、第1バッファ10よりも早い時刻に、ハイインピーダンスから低インピーダンスとなり、起動電圧源16からは、起動電圧VSTARTが出力される。

【0048】

第2電源電圧VCC2の上昇とともに制御信号S2が上昇し、スイッチSW1がオンすると、起動電圧VSTARTが非反転アンプ14に入力される(時刻t3)。その結果、非反転アンプ14の出力電圧Vbは、起動電圧VSTARTに応じたレベルへと遷移するが、このときの変化量は、時刻t1における出力電圧Vb’の変化量にくらべて十分に小さい。

【0049】

このように、図3のオーディオ信号処理回路100によれば、図1のオーディオ信号処理回路100rに比べて、遷移期間τにおける、出力電圧Vbの変動を抑制することができる。出力電圧Vbの変化量が小さければ、ミュートトランジスタによって除去することが可能であり、あるいはミュートトランジスタそのものを省略することができる場合もある。

【0050】

さらに、複数チャンネルで、起動電圧源16および制御回路20が共有されるため、図1のオーディオ信号処理回路100rに比べて、消費電力や回路面積もそれほど大きくならない。なお、消費電力や回路面積の増大が許容される場合には、チャンネルごとに起動電圧源16よび制御回路20を設けてもよい。

【0051】

実施の形態では、マルチチャンネルのオーディオ信号処理回路100について説明したが、本発明はシングルチャンネルにおいても有効である。

【0052】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0053】

1…電子機器、100…オーディオ信号処理回路、10…第1バッファ、12…第2バッファ、14…非反転アンプ、16…起動電圧源、SW1…スイッチ、20…制御回路、OA1…第1演算増幅器、OA2…第2演算増幅器、OA3…第3演算増幅器、OA4…第4演算増幅器、VCC1…第1電源電圧、VCC2…第2電源電圧。

【特許請求の範囲】

【請求項1】

その電源端子に第1電源からの第1電源電圧を受け、その非反転入力端子にオーディオ信号を受け、その反転入力端子がその出力端子と接続された第1演算増幅器を含む第1バッファと、

その非反転入力端子に所定のバイアス電圧を受け、その反転入力端子がその出力端子と接続された第2演算増幅器を含む第2バッファと、

その電源端子に第1電源と異なる第2電源からの第2電源電圧を受け、その非反転入力端子に前記第1演算増幅器の出力電圧が入力された第3演算増幅器と、前記第2演算増幅器の出力電圧と前記第3演算増幅器の出力電圧を分圧し、前記第3演算増幅器の反転入力端子に印加する第1分圧回路と、を含む非反転アンプと、

その電源端子に前記第2電源電圧を受け、起動電圧を生成する起動電圧源と、

前記起動電圧源の出力端子と前記第3演算増幅器の非反転入力端子の間に設けられたスイッチと、

前記第2電源電圧が所定のしきい値電圧より低いときに前記スイッチをオンし、前記第2電源電圧が前記しきい値電圧より高いときに前記スイッチをオフする制御回路と、

を備えることを特徴とするオーディオ信号処理回路。

【請求項2】

前記起動電圧源は、

前記第2電源電圧を受けて、バイアス電圧を生成する電圧源と、

その電源端子に前記第2電源電圧を受け、その非反転入力端子に前記電圧源からのバイアス電圧を受け、その反転入力端子がその出力端子と接続された第4演算増幅器を含み、前記起動電圧を生成する第4バッファと、

を備えることを特徴とする請求項1に記載のオーディオ信号処理回路。

【請求項3】

前記電圧源は、前記第2電源電圧を分圧する第2分圧回路を含むことを特徴とする請求項2に記載のオーディオ信号処理回路。

【請求項4】

前記制御回路は、

前記第2電源電圧が印加される電源ラインと接地ラインの間に順に直列に設けられた第1抵抗および第2抵抗と、

前記電源ラインと接地ラインの間に順に直列に設けられた第3抵抗およびトランジスタと、

を含み、

前記トランジスタの制御端子には、前記第1抵抗と前記第2抵抗の接続点の電位が印加され、前記トランジスタと前記第3抵抗の接続点の電圧を、前記スイッチに対する制御信号として出力することを特徴とする請求項1から3のいずれかに記載のオーディオ信号処理回路。

【請求項5】

前記第1演算増幅器、前記第2演算増幅器、前記第3演算増幅器、前記起動電圧源および前記スイッチのセットを複数チャンネル備え、

単一の前記起動電圧源および単一の前記制御回路が、複数チャンネルで共有されることを特徴とする請求項1から4のいずれかに記載のオーディオ信号処理回路。

【請求項6】

ひとつの半導体基板上に一体集積化されることを特徴とする請求項1から5のいずれかに記載のオーディオ信号処理回路。

【請求項7】

請求項1から6のいずれかに記載のオーディオ信号処理回路と、

前記オーディオ信号処理回路に第1電源電圧、第2電源電圧を供給する電源と、

前記オーディオ信号処理回路の前記非反転アンプの出力信号を直流防止キャパシタを介して受け、それを増幅するパワーアンプと、

前記パワーアンプにより駆動される電気音響変換素子と、

を備えることを特徴とする電子機器。

【請求項1】

その電源端子に第1電源からの第1電源電圧を受け、その非反転入力端子にオーディオ信号を受け、その反転入力端子がその出力端子と接続された第1演算増幅器を含む第1バッファと、

その非反転入力端子に所定のバイアス電圧を受け、その反転入力端子がその出力端子と接続された第2演算増幅器を含む第2バッファと、

その電源端子に第1電源と異なる第2電源からの第2電源電圧を受け、その非反転入力端子に前記第1演算増幅器の出力電圧が入力された第3演算増幅器と、前記第2演算増幅器の出力電圧と前記第3演算増幅器の出力電圧を分圧し、前記第3演算増幅器の反転入力端子に印加する第1分圧回路と、を含む非反転アンプと、

その電源端子に前記第2電源電圧を受け、起動電圧を生成する起動電圧源と、

前記起動電圧源の出力端子と前記第3演算増幅器の非反転入力端子の間に設けられたスイッチと、

前記第2電源電圧が所定のしきい値電圧より低いときに前記スイッチをオンし、前記第2電源電圧が前記しきい値電圧より高いときに前記スイッチをオフする制御回路と、

を備えることを特徴とするオーディオ信号処理回路。

【請求項2】

前記起動電圧源は、

前記第2電源電圧を受けて、バイアス電圧を生成する電圧源と、

その電源端子に前記第2電源電圧を受け、その非反転入力端子に前記電圧源からのバイアス電圧を受け、その反転入力端子がその出力端子と接続された第4演算増幅器を含み、前記起動電圧を生成する第4バッファと、

を備えることを特徴とする請求項1に記載のオーディオ信号処理回路。

【請求項3】

前記電圧源は、前記第2電源電圧を分圧する第2分圧回路を含むことを特徴とする請求項2に記載のオーディオ信号処理回路。

【請求項4】

前記制御回路は、

前記第2電源電圧が印加される電源ラインと接地ラインの間に順に直列に設けられた第1抵抗および第2抵抗と、

前記電源ラインと接地ラインの間に順に直列に設けられた第3抵抗およびトランジスタと、

を含み、

前記トランジスタの制御端子には、前記第1抵抗と前記第2抵抗の接続点の電位が印加され、前記トランジスタと前記第3抵抗の接続点の電圧を、前記スイッチに対する制御信号として出力することを特徴とする請求項1から3のいずれかに記載のオーディオ信号処理回路。

【請求項5】

前記第1演算増幅器、前記第2演算増幅器、前記第3演算増幅器、前記起動電圧源および前記スイッチのセットを複数チャンネル備え、

単一の前記起動電圧源および単一の前記制御回路が、複数チャンネルで共有されることを特徴とする請求項1から4のいずれかに記載のオーディオ信号処理回路。

【請求項6】

ひとつの半導体基板上に一体集積化されることを特徴とする請求項1から5のいずれかに記載のオーディオ信号処理回路。

【請求項7】

請求項1から6のいずれかに記載のオーディオ信号処理回路と、

前記オーディオ信号処理回路に第1電源電圧、第2電源電圧を供給する電源と、

前記オーディオ信号処理回路の前記非反転アンプの出力信号を直流防止キャパシタを介して受け、それを増幅するパワーアンプと、

前記パワーアンプにより駆動される電気音響変換素子と、

を備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−93666(P2013−93666A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−233093(P2011−233093)

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]