カスタムLSI開発プラットフォーム、命令セット・アーキテクチャ及び論理回路構成情報の生成方法、並びにプログラム

【課題】

ユーザの所望するカスタムLSIを高級プログラミング言語により、作成可能なカスタムLSI開発プラットフォームを提供することにある。

【解決手段】

動的論理回路再構成可能プロセッサとソフトウェアプログラムとから成るカスタムLSI開発プラットフォームであり、前記ソフトウェアプログラムは、高級言語で記述されたプログラムから動的論理回路構成可能プロセッサの命令セットと論理素子接続情報とを含む命令セット・アーキテクチャ(以下、ISA)を生成するISAジェネレータと、前記論理素子接続情報と、前記動的論理回路構成可能プロセッサのプログラマブル・エレメント(以下、PE)の機能及び配置配列情報とから前記PEの配置配線情報を生成する論理回路構成・ジェネレータとを備えたカスタムLSI開発プラットフォーム。

ユーザの所望するカスタムLSIを高級プログラミング言語により、作成可能なカスタムLSI開発プラットフォームを提供することにある。

【解決手段】

動的論理回路再構成可能プロセッサとソフトウェアプログラムとから成るカスタムLSI開発プラットフォームであり、前記ソフトウェアプログラムは、高級言語で記述されたプログラムから動的論理回路構成可能プロセッサの命令セットと論理素子接続情報とを含む命令セット・アーキテクチャ(以下、ISA)を生成するISAジェネレータと、前記論理素子接続情報と、前記動的論理回路構成可能プロセッサのプログラマブル・エレメント(以下、PE)の機能及び配置配列情報とから前記PEの配置配線情報を生成する論理回路構成・ジェネレータとを備えたカスタムLSI開発プラットフォーム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、特定用途向けのカスタムLSIを設計、開発及び製造する技術に関し、特に、高級言語で記述されたアプリケーション・プログラムから命令セット・アーキテクチャ(Instruction Set Architecture、以下、ISAという。)と、かかるアプリケーション・プログラムを実行するプロセッサの一連の論理回路構成情報を生成する技術に関する。また、生成したISAと論理回路構成情報とを動的に再構成可能プロセッサに適用することにより、短期間に特定用途向けカスタムLSIを設計、開発及び製造可能ならしめるカスタムLSI開発プラットフォーム技術に関する。

【背景技術】

【0002】

特定用途向け集積回路(Application Specific Integrated Circuit:ASIC)を含むカスタムLSIを使用する分野においては、仕様変更や製品の開発期間を短縮するため、プロセッサ内部の論理回路の構成を自由に変更できる、フィールド・プログラマブル・ゲート・アレイ(Field Programmable Gate Array:FPGA)や、プログラマブル・ロジック・デバイス(Programmable Logic Device:PLD)などのプログラマブル論理回路が広く用いられている。

【0003】

しかし、カスタムLSIに要求される論理回路構成は複雑となり、規模も増大しているため、多数の算術論理ユニット(Arithmetic and Logic Unit:ALU)をFPGAやPLDに組み込まなくてはならないという問題がある。

【0004】

規模が増大した論理回路においても、その全てが常に動作している訳ではないことに着目し、動的にプロセッサの論理回路を再構成する、動的再構成可能プロセッサが、例えば下記の特許文献1、特許文献2において提案されている。

【0005】

カスタムLSIのシステム設計・開発を行う際、どこまでをハードウェアで実現し、どこまでをソフトウェアで実現するかという機能分割は大きな問題である。アプリケーションの全てをハードウェアで実現できれば、動作速度、低消費電力性を実現できる。しかし、設計・開発にかかる、1)チップ製造費、2)設計期間、3)ハードウェア設計者の確保等のコストは大きくなる。

【0006】

逆に全てを汎用プロセッサ上で動作するソフトウェアで実現すると、要求されるシステム性能を満たすことは難しいが、設計・開発コストは小さくて済むという利点がある。

【0007】

ソフトウェア開発者がカスタムLSIを開発する上での課題として、カスタムLSIの仕様を記述するのに「Verilog-HDL」や「VHDL」といったソフトウェア開発者にはなじみ

の薄いハードウェア記述言語(HDL)を利用しなければならないという問題がある。かかるHDLのコードは記述量が多いことから作成に時間がかかる上、コンパイルやシミュレーションにかかる時間も長いという問題がある。

【0008】

LSIに実装するアルゴリズムの検討には、C言語のように抽象度の高い高級言語や、モデリング・ツールを使うことが多い。しかし、高級言語で作成したアルゴリズムを使って論理回路を作成するには、検討したアルゴリズムをHDLで書き直す必要があり、これには多くの時間がかかるという問題がある。しかも、いったんHDLで論理回路構成を記述するとアルゴリズムを変更しにくいという問題もある。

【0009】

更に、動作合成の段階でハードウェア特有の制限を考慮しなければならないことも、ソフトウェア開発者にとっては大きな障壁となっている。

【特許文献1】特開2003−198362号公報

【特許文献2】特開2003−029969号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

そこで、本発明の課題は、ソフトウェア開発者が高級記述言語、例えばC言語でアプリケーション・プログラムを作成すれば、これに基づいてISA及び論理回路構成情報が自動的に生成され、生成されたISA及び論理回路構成情報が再構成可能プロセッサに自動的に反映され、これにより準汎用的に製造する再構成可能プロセッサをカスタムLSIとして作成可能なカスタムLSI開発プラットフォームを提供することにある。

【0011】

また、本発明の他の課題は、高級記述言語、例えばC言語で作成されたアプリケーション・プログラムから、ISA及び論理回路構成情報を生成するソフトウェアプログラム、及び生成されたISAと論理回路構成情報とが自動的に反映される再構成可能プロセッサを提供することにある。

【0012】

また、本発明の他の課題は、高級記述言語、例えばC言語で作成されたアプリケーション・プログラムから、ISA及び論理回路構成情報を生成するプログラムを提供することにある。

【課題を解決するための手段】

【0013】

(1)本発明は、高級言語で記述されたプログラム(以下、ソースプログラム)から命令セット・アーキテクチャ(以下、ISA)を自動生成する手段(以下、ISAジェネレータ)を含むソフトウェアプログラムと、前記生成されたISAに対応して論理回路を再構成する手段を含む再構成可能プロセッサとを備えたカスタムLSI開発プラットフォームであって、前記ISAジェネレータは、ソースプログラムの命令のパターンを抽出する手段と、前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換する手段とを備えたことを特徴とする。

【0014】

(2)前記ソフトウェアプログラムが、前記再構成可能プロセッサの論理回路を構成するプログラマブル・エレメント(以下、PE)の配置配列情報と前記生成されたISAとから前記プロセッサの論理回路構成情報を生成する論理回路構成ジェネレータを備えることは好ましい。

【0015】

(3)前記ソフトウェアプログラムが、前記生成されたISAを前記再構成可能プロセッサの実行可能可能なコード(以下、プログラム・オブジェクトコード)に変換する手段と、前記論理回路構成情報を前記再構成可能プロセッサの実行可能可能なコード(以下、論理回路構成・オブジェクトコード)に変換する手段とを備えることは好ましい。

【0016】

(4)前記再構成可能プロセッサが、前記プログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとに基づいて、PEを再配置し論理回路を再構成する手段を備えることは好ましい。

【0017】

(5)前記ISAジェネレータが、ライブラリに格納されているカスタム命令を呼び出すファンクションコール手段と、前記プロセッサの制御命令とを含む中間コードを生成する手段とを備えることは好ましい。

【0018】

(6)前記プログラム・オブジェクトコードと前記論理回路再構成・オブジェクトコードに基づいて、前記再構成可能プロセッサが前記ソースプログラムを実行するパフォーマンスをシミュレートする手段を備えることは好ましい。

【0019】

(7)前記抽出した命令をカスタム命令に置換するプロセスにおいて、カスタム命令に置き換えられなかった命令を新たなカスタム命令として生成する手段を備えることは好ましい。

【0020】

(8)本発明は、再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)の生成方法であって、高級言語で記述されたプログラム(以下、ソースプログラム)の命令のパターンを抽出し、前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換し、前記再構成可能プロセッサ用のISAを生成することを特徴とする。

【0021】

(9)置換されたカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報を抽出し、該論理素子接続情報を含んでISAを生成することは好ましい。

【0022】

(10)前記プロセッサが動的再構成可能プロセッサであることは好ましい。

【0023】

(11)前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換するプロセスにおいて、前記ソースプログラムの命令中、カスタム命令に置換できなかった命令を、新たなカスタム命令として定義するとともに前記ライブラリに追加し、カスタム命令の再抽出を行うことは好ましい。

【0024】

(12)本発明は、再構成可能プロセッサの論理回路構成情報の生成方法であって、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出し、前記抽出された命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換し、前記抽出したカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と、前記プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成することを特徴とする。

【0025】

(13)前記再構成可能プロセッサが、動的再構成可能プロセッサであることは好ましい。

【0026】

(14)本発明は、(3)に記載のプログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとを実行する手段を備えたことを特徴とする再構成可能プロセッサである。

【0027】

(15)(14)に記載の再構成可能プロセッサは、動的再構成可能論理回路と、前記動的再構成可能論理回路を構成するプログラマブル・エレメント(以下、PE)の命令毎の配置配列情報を記憶するコンフィギュレーション・メモリと、命令の実行の中間結果を一時的に保持するレジスタ・ファイルと、命令を保持するメモリと、命令の実行順序を含むプロセッサの管理を行うコントローラとを備えることは好ましい。

【0028】

(16)前記コントローラは、前記メモリにアクセスするときのインデックスを記憶するインデックス・レジスタを備えることは好ましい。

【0029】

(17)前記インデックス・レジスタの値を記憶するスタックを更に備えることは好ましい。

【0030】

(18)本発明は、コンピュータに実行させ再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)を生成するコンピュータ・プログラムであって、前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、前記抽出した命令パターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップとをコンピュータに実行させるISAを生成することを特徴とするコンピュータ・プログラムである。

【0031】

(19)本発明は、コンピュータに実行させ動的再構成可能プロセッサの論理回路構成情報を生成するコンピュータ・プログラムであって、前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップと、前記命令セットに含まれるカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と前記再構成可能プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成するステップとをコンピュータに実行させ論理回路構成情報を生成することを特徴とするコンピュータ・プログラムである。

【発明の効果】

【0032】

本発明によれば、ソフトウェア開発者は、ハードウェアの特徴に関する部分を意識することなく、アプリケーション(コンピュータプログラム)を開発できる。その結果、開発に要する全体的な実行サイクル数を減らすことができ、所望の用途に特化したLSIを短期間に開発できる。

【0033】

また、カスタムLSIを開発する資産の共通化(プラットフォーム化)が可能となり、設計・開発資産の標準化を図ることができる。

【発明を実施するための最良の形態】

【0034】

[用語の定義]

本明細書において、動的論理回路再構成可能プロセッサとは、動的にプロセッサ内部の論理回路を命令に従い、再構成しながら処理を行う機能を備えたプロセッサをいう。

【0035】

カスタムLSIとは、ニーズに合わせて設計、製造された特定用途向け集積回路(Application Specific Integrated Circuit:ASIC)を含むLSIをいう。

【0036】

カスタム命令とは、プロセッサが実行する命令であって、ユーザが定義した命令である。

【0037】

命令セットとは、インストラクションセット (Instruction Set:IS)ともいい、プロセッサが備えるカスタム命令の集合である。

【0038】

命令セット・アーキテクチャ (Instruction Set Architecture:ISA)は、命令セットとプロセッサの論理回路構成情報を生成するのに必要な論理素子接続情報とからなる。

【0039】

論理素子接続情報とは、例えば、AND回路の次にOR回路、その次にXOR回路といった情報が定義されている情報である。従って、再構成可能プロセッサの論理回路上で、AND回路をどこに配置し、OR回路やXOR回路をどこに配置し、それらをどの配線を使って接続するのかという情報は含まれない。

【0040】

カスタム論理回路とは、カスタム命令を実現する論理回路をいい、汎用プロセッサ上では性能上の理由等で実現しない、あるいは実現することができない回路や機能のことである。

【0041】

プラットフォームとは、異なるカスタム論理回路を実現するために利用可能な共通のハードウェア(再構成可能プロセッサ)とソフトウェアプログラムとで構成されるシステムである。

【0042】

データ・パスとは、カスタム命令を実行するプロセッサの論理回路である。

【0043】

プログラマブル・エレメント(Programmable Element)とは、AND回路、OR回路、XOR回路、あるいはALU等の論理回路を構成する素子である。

【0044】

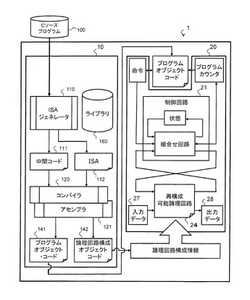

図1は本発明のカスタムLSI開発プラットフォーム1の全体構成ブロック図を示したものである。カスタムLSI開発プラットフォーム1は、再構成可能プロセッサ20と、ソフトウェアプログラム10とで構成される。

【0045】

ソフトウェアプログラム10は、再構成可能プロセッサ20のISA、及び再構成可能プロセッサ20内の再構成可能論理回路24(リコンフィギュラブル・データ・パス)をカスタム命令毎に動的に変更させるための論理回路構成情報等を生成する一連のプログラムから構成されている。

【0046】

ソフトウェア開発者がC言語でソースプログラム100を記述すると、ISAジェネレータ110は、中間コード111とISA112とを生成し、これらをコンパイル等することにより、プログラム・オブジェクトコード141と論理回路構成・オブジェクトコード142とを生成する。

【0047】

再構成可能プロセッサ20は、プログラム・オブジェクトコード141及び論理回路構成・オブジェクトコード142に基づいて、再構成可能論理回路24をカスタム命令毎に変化させながら入力データ27を演算処理し、最終的な結果としてデータ28を出力する。

【0048】

図2は、ソフトウェアプログラム10の詳細ブロック図を示したものである。Cソースプログラム100が与えられると、ISAジェネレータ110が起動し、Cソースプログラム100の命令構造を解析する。なお、ライブラリ160には、事前に定義された複数のカスタム命令が格納されている。

【0049】

ISAジェネレータ110は、Cソースプログラム100中で使われている命令のパターン、あるいは繰り返し使われている命令のパターンを抽出し、ライブラリ160内のカスタム命令のパターンと比較し、Cソースプログラム100内の命令をカスタム命令に置換し、中間コード111とISA112とを生成する。

【0050】

中間コード111は、カスタム命令のファンクションコールと制御命令とから成り、ISA112は、カスタム命令と論理素子接続情報とから成る。

【0051】

中間コード111は、コンパイラ120によりアセンブラコード121にコンパイルされた後、アセンブラ140によりプログラム・オブジェクトコード141となる。なお、コンパイラ120は、中間コード111と、ISA112のカスタム命令、例えば乗算は“×”で定義されているといったカスタム命令を、アセンブラコード121にコンパイルするものである。

【0052】

ISA112のカスタム命令は、コンパイラ120により中間コード111とともにアセンブラコード121に変換された後、アセンブラ140によりプログラム・オブジェクトコード141となる。

【0053】

論理回路構成ジェネレータ130は、ISA112の論理素子接続情報と、再構成可能論理回路24のプログラマブル・エレメント(PE)の配置配列情報1310とから、論理回路構成情報1311を生成し、これをアセンブラ140により論理回路構成・オブジェクトコード142に変換する。

【0054】

図3はISAジェネレータ110の詳細ブロック図を示したものである。図3に示すパターニング・モジュール1110は、ライブラリ160を参照しながら、Cソースプログラム100中に使われている命令、あるいは繰り返し使われている命令を抽出し、抽出した命令のパターンとライブラリ160に格納されているカスタム命令のパターンとを比較し、一致する命令をカスタム命令で置換する。

【0055】

パターニング・モジュール1110によりカスタム命令として抽出されなかった(事前にカスタム命令として用意されていなかった)雑多な命令は、クリエータ150により新たに定義し作成するか、既存のカスタム命令に合成可能であれば合成し、新たなカスタム命令として定義する。ライブラリ160中のカスタム命令は、カスタム命令の追加、合成により常に更新される。

【0056】

パターンニング・モジュール1110は、Cソースプログラム全体が実行可能になるまで、Cソースプログラムの命令をカスタム命令に置き換える。また、パターンニング・モジュール1110は論理素子接続情報(カスタム命令と関連付けられてライブラリ160に格納されている。)と、PEの配置配列情報とを参照して、カスタム命令毎に再構成可能論理回路24の論理回路構成情報を生成する。

【0057】

図4は本発明の一実施の形態である再構成可能プロセッサ20のブロック図を示したものである。動的再構成可能プロセッサ20は、リコンフィギュラブル・データ・パス(再構成可能論理回路)24を備え、順序制御によりプログラムを実行するプロセッサである。この再構成可能プロセッサ20は、1ステップ毎に論理回路構成の再設定を行いながら、Cソースプログラム100の処理内容を実行する。なお、ステップとは、論理回路構成の設定と演算の実行を合わせた、一命令の実行にかかる期間である。また、論理回路構成情報とは、カスタム命令を実行するための再構成可能な論理回路の構成情報である。

【0058】

再構成可能プロセッサ20は、コントローラ21、スタック22、コンフィギュレーション・メモリ23、リコンフィギュラブル・データ・パス24、レジスタ・ファイル25、及びメモリ26を備える。

【0059】

コントローラ21は、コンフィギュレーション・データのロード、メモリ26内のデータのロードなど、再構成可能プロセッサ20の全体管理を行う。内部には22ビットのインデックス・レジスタ211を7つ備え、インデックス・レジスタ211内の値を用いてメモリ26にアクセスすることができる。また、インデックス・レジスタ211内の値を格納するスタック22と接続している。

【0060】

メモリ26は、再構成可能プロセッサ20の命令を保持する記憶装置である。

【0061】

図5は、メモリ26が保持する命令フォーマットの構成を示した図である。

【0062】

図5中、Exe_Non欄では、命令をリコンフィギュラブル・データ・パス24により演算

を行う場合、あるいはリコンフィギュラブル・データ・パス24によらずにインデックス・レジスタ211内の値の操作のみを行う場合のどちらを選択するかを指示するものである。

【0063】

リコンフィギュラブル・データ・パス24で演算を行う命令の場合は、適切なコンフィギュレーション・データが格納されているコンフィギュレーション・メモリ23のアドレスと演算に用いるレジスタ・ファイル25とを指定する。インデックス・レジスタ211内の値を操作する命令の場合は、操作内容と操作に用いるインデックス・レジスタ211とを指定する。

【0064】

Dt_Adr欄に例えばメモリアドレスを指定すれば、メモリ26とインデックス・レジスタ211間のデータのやり取りを行わせることができる。

【0065】

Flow_Code欄では、プログラムの実行順序制御を指定することができ、ここで、分岐条

件の指定を行えば、リコンフィギュラブル・データ・パス24での演算結果を用いて処理を分岐させることも可能である。

【0066】

Dt_Adrは絶対アドレスの指定に用い、Rel_Adr欄は相対アドレスの指定に用いる。

【0067】

Work_Rateは、リコンフィギュラブル・データ・パス24での処理を行う際のクロック

・サイクル数を処理内容によって、1,2,4,8クロック・サイクルに指定することに用いることができる。

【0068】

コンフィギュレーション・メモリ23は、コンフィギュレーション・データを格納するメモリである。カスタム命令のコンフィギュレーションを128個まで保持することができる。

【0069】

レジスタ・ファイル25は、リコンフィギュラブル・データ・パス24の各PEでの演算結果を保存し、異なるファンクションに引き渡すレジスタである。1ワードは256ビット幅である。レジスタ・ファイル25は、リコンフィギュラブル・データ・パス24のPEに接続されており、データが出力されるPEの位置によって、格納されるレジスタ・ファイル25中のビット位置が決定される。

【0070】

図6は、リコンフィギュラブル・データ・パス24の構成の一実施形態を示したものである。リコンフィギュラブル・データ・パス24は、PEが16行8列で配置されている。PEは6入力2出力であり、入力に対して任意の論理関数を割り当てることができる。各PE間は、垂直ライン(VL:Vertical Line)と水平ライン(HL:Horizontal Line)で接続されている。

【0071】

VLが一列の各PEに接続しており、各VLはHLで接続されている。VLからHL、あるいはHLからVLへの信号受け渡しはスイッチ部(SW)が制御している。VLは64ビット幅で8本、HLは64ビット幅で7本である。また、メモリからコンフィギュラブル・データ・パス24へは一度に64ビットのデータをロードすることができる。

【0072】

この再構成可能プロセッサ20は、まずコントローラ21がメモリ26からプログラムを読み出し、リコンフィギュラブル・データ・パス24を使う命令か、それともインデックス・レジスタ211内の値のみを操作する命令かの判断をする。

【0073】

リコンフィギュラブル・データ・パス24を使う場合、コントローラ21がプログラム中に指定されたコンフィギュレーション・メモリ23のアドレスから適切なコンフィギュレーション・データを読み出し、このデータをリコンフィギュラブル・データ・パス24にロードする。

【0074】

リコンフィギュラブル・データ・パス24は、コンフィギュレーション(論理回路構成)が確定すると、入力データに対して処理を行う。各PEで実行された演算結果はVLに出力されるとともにレジスタ・ファイル25に書き込むことができる。中間結果として別のファンクションにデータを引き渡して使うことができる。レジスタ・ファイル25を用いることで大きな処理を複数ファンクションに分割して実行することができる。

【0075】

インデックス・レジスタ211内の値を用いる場合は、インデックス・レジスタ211内に演算回路が用意されているので、プログラム中に指定された操作を演算回路で行い、次の命令に遷移する。

【実施例1】

【0076】

本発明の一実施の形態であるソフトウェアプログラム10と、再構成可能プロセッサ20とを用いて、AES(Advanced Encryption Standard)の暗号化用カスタムLSIを開発した。

【0077】

AESはDES(Data Encryption Standard)に代わる標準暗号化方式として選定されているものである。C言語で作成したAESのプログラムからISAを生成するとともに、AES暗号化処理を再構成可能プロセッサ20に実装し性能評価を行った。

【0078】

AESでは、平文のビット数や鍵のビット数を選択可能であるが、この実施例では両者とも128ビットとした。

【0079】

図7にAES暗号化の処理の流れを示す。先ず、Stateと呼ばれる、2次元配列のデータ形式平文を配置する。ラウンド鍵を生成し(S1)、Stateとラウンド鍵とで排他的論理和をとる(S2)。ラウンド関数を規定回数実行する。この実施例においては次の条件で9回実行した。ラウンド関数は次の4つの変換で実行する。まず、8ビット入力8ビット出力のいわゆるs-box変換処理(バイト・サブ(Byte-Sub))を実行する(S3)。

【0080】

次に、行に対してバイト単位の周期的シフトを施すシフト・ロウ(Shift-Row)を実行する(S4)。次に、列ごとの行列演算の実行であるミックス・コラム(Mix-Column)を行う(S5)。そして、そのStateとラウンド鍵とで排他的論理(Add-Round-key)を実行する(S6)。S3からS6のステップを9回繰り返し実行する。

【0081】

そして、最後にバイト・サブ(Byte-Sub)(S7)、シフト・ロウ(Shift-Row)(S8)、ラウンド鍵処理(Add-Round-Key)(S9)を実行し、暗号文(Encrypted)を得る(S10)。

【0082】

暗号化処理の中心となるのは、バイト・サブ(Byte-sub)やシフト・ロウ(Shift-Row)、ミックス・コラム(Mix-Column)、ラウンド鍵処理(Add-Round-Key)の4つの変換処理である。これら4つの変換処理を実現するにあたり、各変換処理を実現するためのカスタム命令を作成した。

【0083】

この実施例においては、バイト・サブ(Byte-Sub)は32ビット、シフト・ロウ(Shift-Row)は128ビット、ミックス・コラム(Mix-Column)は64ビット、ラウンド鍵処理(Add-Round-Key)は128ビットずつの単位に分けて処理を行う実装をした。このため、それらの前後でデータの分割、結合などを行うための命令も追加した。

【0084】

図8、図9はバイト・サブ(Byte-sub)、シフト・ロウ(Shift-Row)、ミックス・コラム(Mix-Column)、ラウンド鍵処理(Add-Round-Key)を含むC言語で記述したAESの暗号化処理の中間コード111の記述例である。

【0085】

図8、図9に示すように、AES暗号化のメインルーチンは、「Encrypt」関数である。図8の中間コード中、カスタム命令は、先頭に「vu1_」がつている箇所である。

【0086】

これにより、全体処理で309サイクル、暗号化の処理部分で79サイクルの結果が得られた。

【実施例2】

【0087】

DESは米国商務省標準局で標準化されている暗号規格である。暗号化と復号化に同じ鍵を使用する共通鍵暗号で、64ビットの平文と56ビットの鍵を入力することによって、暗号文64ビットを出力する。

【0088】

DESの暗号化処理では、まず64ビットのビット列を入力し、それに対して、転置表を元に初期転置を行う。転置したビット列を32ビットずつ分割する。分割したビット列をそれぞれ鍵と暗号化関数Fで暗号化する。鍵は入力した56ビット鍵から生成された48ビットのラウンド鍵を使用する。

【0089】

この処理を16回行い、作成した左右ビット列を結合して最終転置を行い、その結果が暗号文として出力される。

【0090】

図10はDES暗号化処理のフローチャートを示したものである。動的論理回路再構成可能プロセッサ20上でのDES暗号化処理には、カスタム命令を6つ必要とした。

【0091】

表1は、DES暗号化処理に用いたカスタム命令とその内容を示したものである。

【0092】

【表1】

【0093】

先ず、命令0で鍵56ビットをメモリからリコンフィギュラブル・データ・パス24に入力し同時に転置を行う。同様に命令1で平文64ビットを入力し、同時に初期転置を行う。次にラウンド回数によって、命令2、あるいは命令3で鍵の循環シフトを行う。命令4では鍵の縮約転置および暗号化F関数を一命令で行う。

【0094】

各命令間のデータの授受は全てレジスタ・ファイル25を介して行っている。このラウンドを16回繰り返す。図10では繰り返しが条件分岐処理になっているが、本実施例では繰り返しは展開して逐次処理を行った。これは条件分岐処理で実行するにはラウンド回数を判定するための回路を余分につくる必要があり、設計する回路規模を縮小するためである。最後に初期転置の逆の転置を行い、暗号文64ビットをメモリに出力する。

【0095】

表2は、再構成可能プロセッサ20でDES暗号化処理を行った際の動作周波数とスループットを示したものである。

【0096】

【表2】

【0097】

この実施例ではDES暗号化処理の動作周波数は6.25MHZであった。比較対象として、Intel Pentium(登録商標)4上でDES暗号化処理を行った際の結果も表2に示す。Intel Pentium(登録商標)4上へのDES暗号化処理の実装は、C言語によってDES暗号

化処理の仕様を忠実に記述したものをコンパイルすることによって行った。コンパイルオプションには−O2を用いた。

【0098】

表2から再構成可能プロセッサ20上でのDES暗号化処理は、Intel Pentium(登録商標)4上でのDES暗号化処理よりも3.8倍高い性能を示した。これは、動的再構成可能プロセッサ20の構成要素であるPEが入力に対して1ビット単位で任意の論理関数を割り当てることが可能であるとう特徴をDES暗号化処理に生かすことができたためである。

【0099】

DES暗号化処理では、1ビット単位での転置や換字を繰り返す。Intel Pentium(登録商標)4などの32ビットマイクロプロセッサでは、1ビット単位で処理を行う際には、1ビットを取り出す処理が必要となる。動的再構成可能プロセッサ20のPEは1ビット単位の転置処理では、データをレジスタ・ファイル25からリコンフィギュラブル・データ・パス24に取り込み、指定のビット位置に移動させて再びレジスタ・ファイル25に格納する。これによって、大量のデータの転置処理が一命令で可能となった。

【0100】

また、PEでは入力に対して任意の論理関数を割り当てることができるので、データ依存関係のある複数の処理を合成し、一命令で実行することによって、実行クロック・サイクル数を削減することが可能であった。リコンフィギュラブル・データ・パス24上でのDES暗号化処理において、平文64ビットの暗号化に要したクロック・サイクル数は70サイクルであった。

【産業上の利用可能性】

【0101】

本発明は、カスタムLSIの設計及び開発を行う場合のプラットフォームとして利用することができる。また、アプリケーションに特化したカスタムLSIの製造に利用することもでき、産業上の利用可能性がある。

【図面の簡単な説明】

【0102】

【図1】本発明のカスタムLSI開発プラットフォーム1の全体構成ブロック図である。

【図2】ソフトウェアプログラム10の詳細ブロック図を示したものである。

【図3】ISAジェネレータ110の詳細ブロック図を示したものである。

【図4】本発明の一実施の形態である再構成可能プロセッサ20のブロック図を示したものである。

【図5】命令フォーマットの構成を示した図である。

【図6】リコンフィギュラブル・データ・パス24の構成の一実施形態を示したものである。

【図7】AES暗号化の処理の流れを示した図である。

【図8】AESの暗号化処理の中間コードの記述例である。

【図9】AESの暗号化処理の中間コードの記述例である。

【図10】DES暗号化処理のフローチャートを示したものである。

【符号の説明】

【0103】

1 カスタムLSI開発プラットフォーム

10 ソフトウェアプログラム

20 再構成可能プロセッサ

21 コントローラ

22 スタック

23 コンフィギュレーション・メモリ

24 再構成可能論理回路(リコンフィギュラブル・データ・パス)

25 レジスタ・ファイル

26 メモリ

100 Cソースプログラム

110 ISAジェネレータ

111 中間コード

112 命令セット・アーキテクチャ(ISA)

130 論理回路構成ジェネレータ

131 論理回路構成情報

141 プログラム・オブジェクトコード

142 論理回路構成・オブジェクトコード

160 ライブラリ

【技術分野】

【0001】

本発明は、特定用途向けのカスタムLSIを設計、開発及び製造する技術に関し、特に、高級言語で記述されたアプリケーション・プログラムから命令セット・アーキテクチャ(Instruction Set Architecture、以下、ISAという。)と、かかるアプリケーション・プログラムを実行するプロセッサの一連の論理回路構成情報を生成する技術に関する。また、生成したISAと論理回路構成情報とを動的に再構成可能プロセッサに適用することにより、短期間に特定用途向けカスタムLSIを設計、開発及び製造可能ならしめるカスタムLSI開発プラットフォーム技術に関する。

【背景技術】

【0002】

特定用途向け集積回路(Application Specific Integrated Circuit:ASIC)を含むカスタムLSIを使用する分野においては、仕様変更や製品の開発期間を短縮するため、プロセッサ内部の論理回路の構成を自由に変更できる、フィールド・プログラマブル・ゲート・アレイ(Field Programmable Gate Array:FPGA)や、プログラマブル・ロジック・デバイス(Programmable Logic Device:PLD)などのプログラマブル論理回路が広く用いられている。

【0003】

しかし、カスタムLSIに要求される論理回路構成は複雑となり、規模も増大しているため、多数の算術論理ユニット(Arithmetic and Logic Unit:ALU)をFPGAやPLDに組み込まなくてはならないという問題がある。

【0004】

規模が増大した論理回路においても、その全てが常に動作している訳ではないことに着目し、動的にプロセッサの論理回路を再構成する、動的再構成可能プロセッサが、例えば下記の特許文献1、特許文献2において提案されている。

【0005】

カスタムLSIのシステム設計・開発を行う際、どこまでをハードウェアで実現し、どこまでをソフトウェアで実現するかという機能分割は大きな問題である。アプリケーションの全てをハードウェアで実現できれば、動作速度、低消費電力性を実現できる。しかし、設計・開発にかかる、1)チップ製造費、2)設計期間、3)ハードウェア設計者の確保等のコストは大きくなる。

【0006】

逆に全てを汎用プロセッサ上で動作するソフトウェアで実現すると、要求されるシステム性能を満たすことは難しいが、設計・開発コストは小さくて済むという利点がある。

【0007】

ソフトウェア開発者がカスタムLSIを開発する上での課題として、カスタムLSIの仕様を記述するのに「Verilog-HDL」や「VHDL」といったソフトウェア開発者にはなじみ

の薄いハードウェア記述言語(HDL)を利用しなければならないという問題がある。かかるHDLのコードは記述量が多いことから作成に時間がかかる上、コンパイルやシミュレーションにかかる時間も長いという問題がある。

【0008】

LSIに実装するアルゴリズムの検討には、C言語のように抽象度の高い高級言語や、モデリング・ツールを使うことが多い。しかし、高級言語で作成したアルゴリズムを使って論理回路を作成するには、検討したアルゴリズムをHDLで書き直す必要があり、これには多くの時間がかかるという問題がある。しかも、いったんHDLで論理回路構成を記述するとアルゴリズムを変更しにくいという問題もある。

【0009】

更に、動作合成の段階でハードウェア特有の制限を考慮しなければならないことも、ソフトウェア開発者にとっては大きな障壁となっている。

【特許文献1】特開2003−198362号公報

【特許文献2】特開2003−029969号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

そこで、本発明の課題は、ソフトウェア開発者が高級記述言語、例えばC言語でアプリケーション・プログラムを作成すれば、これに基づいてISA及び論理回路構成情報が自動的に生成され、生成されたISA及び論理回路構成情報が再構成可能プロセッサに自動的に反映され、これにより準汎用的に製造する再構成可能プロセッサをカスタムLSIとして作成可能なカスタムLSI開発プラットフォームを提供することにある。

【0011】

また、本発明の他の課題は、高級記述言語、例えばC言語で作成されたアプリケーション・プログラムから、ISA及び論理回路構成情報を生成するソフトウェアプログラム、及び生成されたISAと論理回路構成情報とが自動的に反映される再構成可能プロセッサを提供することにある。

【0012】

また、本発明の他の課題は、高級記述言語、例えばC言語で作成されたアプリケーション・プログラムから、ISA及び論理回路構成情報を生成するプログラムを提供することにある。

【課題を解決するための手段】

【0013】

(1)本発明は、高級言語で記述されたプログラム(以下、ソースプログラム)から命令セット・アーキテクチャ(以下、ISA)を自動生成する手段(以下、ISAジェネレータ)を含むソフトウェアプログラムと、前記生成されたISAに対応して論理回路を再構成する手段を含む再構成可能プロセッサとを備えたカスタムLSI開発プラットフォームであって、前記ISAジェネレータは、ソースプログラムの命令のパターンを抽出する手段と、前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換する手段とを備えたことを特徴とする。

【0014】

(2)前記ソフトウェアプログラムが、前記再構成可能プロセッサの論理回路を構成するプログラマブル・エレメント(以下、PE)の配置配列情報と前記生成されたISAとから前記プロセッサの論理回路構成情報を生成する論理回路構成ジェネレータを備えることは好ましい。

【0015】

(3)前記ソフトウェアプログラムが、前記生成されたISAを前記再構成可能プロセッサの実行可能可能なコード(以下、プログラム・オブジェクトコード)に変換する手段と、前記論理回路構成情報を前記再構成可能プロセッサの実行可能可能なコード(以下、論理回路構成・オブジェクトコード)に変換する手段とを備えることは好ましい。

【0016】

(4)前記再構成可能プロセッサが、前記プログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとに基づいて、PEを再配置し論理回路を再構成する手段を備えることは好ましい。

【0017】

(5)前記ISAジェネレータが、ライブラリに格納されているカスタム命令を呼び出すファンクションコール手段と、前記プロセッサの制御命令とを含む中間コードを生成する手段とを備えることは好ましい。

【0018】

(6)前記プログラム・オブジェクトコードと前記論理回路再構成・オブジェクトコードに基づいて、前記再構成可能プロセッサが前記ソースプログラムを実行するパフォーマンスをシミュレートする手段を備えることは好ましい。

【0019】

(7)前記抽出した命令をカスタム命令に置換するプロセスにおいて、カスタム命令に置き換えられなかった命令を新たなカスタム命令として生成する手段を備えることは好ましい。

【0020】

(8)本発明は、再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)の生成方法であって、高級言語で記述されたプログラム(以下、ソースプログラム)の命令のパターンを抽出し、前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換し、前記再構成可能プロセッサ用のISAを生成することを特徴とする。

【0021】

(9)置換されたカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報を抽出し、該論理素子接続情報を含んでISAを生成することは好ましい。

【0022】

(10)前記プロセッサが動的再構成可能プロセッサであることは好ましい。

【0023】

(11)前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換するプロセスにおいて、前記ソースプログラムの命令中、カスタム命令に置換できなかった命令を、新たなカスタム命令として定義するとともに前記ライブラリに追加し、カスタム命令の再抽出を行うことは好ましい。

【0024】

(12)本発明は、再構成可能プロセッサの論理回路構成情報の生成方法であって、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出し、前記抽出された命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換し、前記抽出したカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と、前記プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成することを特徴とする。

【0025】

(13)前記再構成可能プロセッサが、動的再構成可能プロセッサであることは好ましい。

【0026】

(14)本発明は、(3)に記載のプログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとを実行する手段を備えたことを特徴とする再構成可能プロセッサである。

【0027】

(15)(14)に記載の再構成可能プロセッサは、動的再構成可能論理回路と、前記動的再構成可能論理回路を構成するプログラマブル・エレメント(以下、PE)の命令毎の配置配列情報を記憶するコンフィギュレーション・メモリと、命令の実行の中間結果を一時的に保持するレジスタ・ファイルと、命令を保持するメモリと、命令の実行順序を含むプロセッサの管理を行うコントローラとを備えることは好ましい。

【0028】

(16)前記コントローラは、前記メモリにアクセスするときのインデックスを記憶するインデックス・レジスタを備えることは好ましい。

【0029】

(17)前記インデックス・レジスタの値を記憶するスタックを更に備えることは好ましい。

【0030】

(18)本発明は、コンピュータに実行させ再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)を生成するコンピュータ・プログラムであって、前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、前記抽出した命令パターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップとをコンピュータに実行させるISAを生成することを特徴とするコンピュータ・プログラムである。

【0031】

(19)本発明は、コンピュータに実行させ動的再構成可能プロセッサの論理回路構成情報を生成するコンピュータ・プログラムであって、前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップと、前記命令セットに含まれるカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と前記再構成可能プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成するステップとをコンピュータに実行させ論理回路構成情報を生成することを特徴とするコンピュータ・プログラムである。

【発明の効果】

【0032】

本発明によれば、ソフトウェア開発者は、ハードウェアの特徴に関する部分を意識することなく、アプリケーション(コンピュータプログラム)を開発できる。その結果、開発に要する全体的な実行サイクル数を減らすことができ、所望の用途に特化したLSIを短期間に開発できる。

【0033】

また、カスタムLSIを開発する資産の共通化(プラットフォーム化)が可能となり、設計・開発資産の標準化を図ることができる。

【発明を実施するための最良の形態】

【0034】

[用語の定義]

本明細書において、動的論理回路再構成可能プロセッサとは、動的にプロセッサ内部の論理回路を命令に従い、再構成しながら処理を行う機能を備えたプロセッサをいう。

【0035】

カスタムLSIとは、ニーズに合わせて設計、製造された特定用途向け集積回路(Application Specific Integrated Circuit:ASIC)を含むLSIをいう。

【0036】

カスタム命令とは、プロセッサが実行する命令であって、ユーザが定義した命令である。

【0037】

命令セットとは、インストラクションセット (Instruction Set:IS)ともいい、プロセッサが備えるカスタム命令の集合である。

【0038】

命令セット・アーキテクチャ (Instruction Set Architecture:ISA)は、命令セットとプロセッサの論理回路構成情報を生成するのに必要な論理素子接続情報とからなる。

【0039】

論理素子接続情報とは、例えば、AND回路の次にOR回路、その次にXOR回路といった情報が定義されている情報である。従って、再構成可能プロセッサの論理回路上で、AND回路をどこに配置し、OR回路やXOR回路をどこに配置し、それらをどの配線を使って接続するのかという情報は含まれない。

【0040】

カスタム論理回路とは、カスタム命令を実現する論理回路をいい、汎用プロセッサ上では性能上の理由等で実現しない、あるいは実現することができない回路や機能のことである。

【0041】

プラットフォームとは、異なるカスタム論理回路を実現するために利用可能な共通のハードウェア(再構成可能プロセッサ)とソフトウェアプログラムとで構成されるシステムである。

【0042】

データ・パスとは、カスタム命令を実行するプロセッサの論理回路である。

【0043】

プログラマブル・エレメント(Programmable Element)とは、AND回路、OR回路、XOR回路、あるいはALU等の論理回路を構成する素子である。

【0044】

図1は本発明のカスタムLSI開発プラットフォーム1の全体構成ブロック図を示したものである。カスタムLSI開発プラットフォーム1は、再構成可能プロセッサ20と、ソフトウェアプログラム10とで構成される。

【0045】

ソフトウェアプログラム10は、再構成可能プロセッサ20のISA、及び再構成可能プロセッサ20内の再構成可能論理回路24(リコンフィギュラブル・データ・パス)をカスタム命令毎に動的に変更させるための論理回路構成情報等を生成する一連のプログラムから構成されている。

【0046】

ソフトウェア開発者がC言語でソースプログラム100を記述すると、ISAジェネレータ110は、中間コード111とISA112とを生成し、これらをコンパイル等することにより、プログラム・オブジェクトコード141と論理回路構成・オブジェクトコード142とを生成する。

【0047】

再構成可能プロセッサ20は、プログラム・オブジェクトコード141及び論理回路構成・オブジェクトコード142に基づいて、再構成可能論理回路24をカスタム命令毎に変化させながら入力データ27を演算処理し、最終的な結果としてデータ28を出力する。

【0048】

図2は、ソフトウェアプログラム10の詳細ブロック図を示したものである。Cソースプログラム100が与えられると、ISAジェネレータ110が起動し、Cソースプログラム100の命令構造を解析する。なお、ライブラリ160には、事前に定義された複数のカスタム命令が格納されている。

【0049】

ISAジェネレータ110は、Cソースプログラム100中で使われている命令のパターン、あるいは繰り返し使われている命令のパターンを抽出し、ライブラリ160内のカスタム命令のパターンと比較し、Cソースプログラム100内の命令をカスタム命令に置換し、中間コード111とISA112とを生成する。

【0050】

中間コード111は、カスタム命令のファンクションコールと制御命令とから成り、ISA112は、カスタム命令と論理素子接続情報とから成る。

【0051】

中間コード111は、コンパイラ120によりアセンブラコード121にコンパイルされた後、アセンブラ140によりプログラム・オブジェクトコード141となる。なお、コンパイラ120は、中間コード111と、ISA112のカスタム命令、例えば乗算は“×”で定義されているといったカスタム命令を、アセンブラコード121にコンパイルするものである。

【0052】

ISA112のカスタム命令は、コンパイラ120により中間コード111とともにアセンブラコード121に変換された後、アセンブラ140によりプログラム・オブジェクトコード141となる。

【0053】

論理回路構成ジェネレータ130は、ISA112の論理素子接続情報と、再構成可能論理回路24のプログラマブル・エレメント(PE)の配置配列情報1310とから、論理回路構成情報1311を生成し、これをアセンブラ140により論理回路構成・オブジェクトコード142に変換する。

【0054】

図3はISAジェネレータ110の詳細ブロック図を示したものである。図3に示すパターニング・モジュール1110は、ライブラリ160を参照しながら、Cソースプログラム100中に使われている命令、あるいは繰り返し使われている命令を抽出し、抽出した命令のパターンとライブラリ160に格納されているカスタム命令のパターンとを比較し、一致する命令をカスタム命令で置換する。

【0055】

パターニング・モジュール1110によりカスタム命令として抽出されなかった(事前にカスタム命令として用意されていなかった)雑多な命令は、クリエータ150により新たに定義し作成するか、既存のカスタム命令に合成可能であれば合成し、新たなカスタム命令として定義する。ライブラリ160中のカスタム命令は、カスタム命令の追加、合成により常に更新される。

【0056】

パターンニング・モジュール1110は、Cソースプログラム全体が実行可能になるまで、Cソースプログラムの命令をカスタム命令に置き換える。また、パターンニング・モジュール1110は論理素子接続情報(カスタム命令と関連付けられてライブラリ160に格納されている。)と、PEの配置配列情報とを参照して、カスタム命令毎に再構成可能論理回路24の論理回路構成情報を生成する。

【0057】

図4は本発明の一実施の形態である再構成可能プロセッサ20のブロック図を示したものである。動的再構成可能プロセッサ20は、リコンフィギュラブル・データ・パス(再構成可能論理回路)24を備え、順序制御によりプログラムを実行するプロセッサである。この再構成可能プロセッサ20は、1ステップ毎に論理回路構成の再設定を行いながら、Cソースプログラム100の処理内容を実行する。なお、ステップとは、論理回路構成の設定と演算の実行を合わせた、一命令の実行にかかる期間である。また、論理回路構成情報とは、カスタム命令を実行するための再構成可能な論理回路の構成情報である。

【0058】

再構成可能プロセッサ20は、コントローラ21、スタック22、コンフィギュレーション・メモリ23、リコンフィギュラブル・データ・パス24、レジスタ・ファイル25、及びメモリ26を備える。

【0059】

コントローラ21は、コンフィギュレーション・データのロード、メモリ26内のデータのロードなど、再構成可能プロセッサ20の全体管理を行う。内部には22ビットのインデックス・レジスタ211を7つ備え、インデックス・レジスタ211内の値を用いてメモリ26にアクセスすることができる。また、インデックス・レジスタ211内の値を格納するスタック22と接続している。

【0060】

メモリ26は、再構成可能プロセッサ20の命令を保持する記憶装置である。

【0061】

図5は、メモリ26が保持する命令フォーマットの構成を示した図である。

【0062】

図5中、Exe_Non欄では、命令をリコンフィギュラブル・データ・パス24により演算

を行う場合、あるいはリコンフィギュラブル・データ・パス24によらずにインデックス・レジスタ211内の値の操作のみを行う場合のどちらを選択するかを指示するものである。

【0063】

リコンフィギュラブル・データ・パス24で演算を行う命令の場合は、適切なコンフィギュレーション・データが格納されているコンフィギュレーション・メモリ23のアドレスと演算に用いるレジスタ・ファイル25とを指定する。インデックス・レジスタ211内の値を操作する命令の場合は、操作内容と操作に用いるインデックス・レジスタ211とを指定する。

【0064】

Dt_Adr欄に例えばメモリアドレスを指定すれば、メモリ26とインデックス・レジスタ211間のデータのやり取りを行わせることができる。

【0065】

Flow_Code欄では、プログラムの実行順序制御を指定することができ、ここで、分岐条

件の指定を行えば、リコンフィギュラブル・データ・パス24での演算結果を用いて処理を分岐させることも可能である。

【0066】

Dt_Adrは絶対アドレスの指定に用い、Rel_Adr欄は相対アドレスの指定に用いる。

【0067】

Work_Rateは、リコンフィギュラブル・データ・パス24での処理を行う際のクロック

・サイクル数を処理内容によって、1,2,4,8クロック・サイクルに指定することに用いることができる。

【0068】

コンフィギュレーション・メモリ23は、コンフィギュレーション・データを格納するメモリである。カスタム命令のコンフィギュレーションを128個まで保持することができる。

【0069】

レジスタ・ファイル25は、リコンフィギュラブル・データ・パス24の各PEでの演算結果を保存し、異なるファンクションに引き渡すレジスタである。1ワードは256ビット幅である。レジスタ・ファイル25は、リコンフィギュラブル・データ・パス24のPEに接続されており、データが出力されるPEの位置によって、格納されるレジスタ・ファイル25中のビット位置が決定される。

【0070】

図6は、リコンフィギュラブル・データ・パス24の構成の一実施形態を示したものである。リコンフィギュラブル・データ・パス24は、PEが16行8列で配置されている。PEは6入力2出力であり、入力に対して任意の論理関数を割り当てることができる。各PE間は、垂直ライン(VL:Vertical Line)と水平ライン(HL:Horizontal Line)で接続されている。

【0071】

VLが一列の各PEに接続しており、各VLはHLで接続されている。VLからHL、あるいはHLからVLへの信号受け渡しはスイッチ部(SW)が制御している。VLは64ビット幅で8本、HLは64ビット幅で7本である。また、メモリからコンフィギュラブル・データ・パス24へは一度に64ビットのデータをロードすることができる。

【0072】

この再構成可能プロセッサ20は、まずコントローラ21がメモリ26からプログラムを読み出し、リコンフィギュラブル・データ・パス24を使う命令か、それともインデックス・レジスタ211内の値のみを操作する命令かの判断をする。

【0073】

リコンフィギュラブル・データ・パス24を使う場合、コントローラ21がプログラム中に指定されたコンフィギュレーション・メモリ23のアドレスから適切なコンフィギュレーション・データを読み出し、このデータをリコンフィギュラブル・データ・パス24にロードする。

【0074】

リコンフィギュラブル・データ・パス24は、コンフィギュレーション(論理回路構成)が確定すると、入力データに対して処理を行う。各PEで実行された演算結果はVLに出力されるとともにレジスタ・ファイル25に書き込むことができる。中間結果として別のファンクションにデータを引き渡して使うことができる。レジスタ・ファイル25を用いることで大きな処理を複数ファンクションに分割して実行することができる。

【0075】

インデックス・レジスタ211内の値を用いる場合は、インデックス・レジスタ211内に演算回路が用意されているので、プログラム中に指定された操作を演算回路で行い、次の命令に遷移する。

【実施例1】

【0076】

本発明の一実施の形態であるソフトウェアプログラム10と、再構成可能プロセッサ20とを用いて、AES(Advanced Encryption Standard)の暗号化用カスタムLSIを開発した。

【0077】

AESはDES(Data Encryption Standard)に代わる標準暗号化方式として選定されているものである。C言語で作成したAESのプログラムからISAを生成するとともに、AES暗号化処理を再構成可能プロセッサ20に実装し性能評価を行った。

【0078】

AESでは、平文のビット数や鍵のビット数を選択可能であるが、この実施例では両者とも128ビットとした。

【0079】

図7にAES暗号化の処理の流れを示す。先ず、Stateと呼ばれる、2次元配列のデータ形式平文を配置する。ラウンド鍵を生成し(S1)、Stateとラウンド鍵とで排他的論理和をとる(S2)。ラウンド関数を規定回数実行する。この実施例においては次の条件で9回実行した。ラウンド関数は次の4つの変換で実行する。まず、8ビット入力8ビット出力のいわゆるs-box変換処理(バイト・サブ(Byte-Sub))を実行する(S3)。

【0080】

次に、行に対してバイト単位の周期的シフトを施すシフト・ロウ(Shift-Row)を実行する(S4)。次に、列ごとの行列演算の実行であるミックス・コラム(Mix-Column)を行う(S5)。そして、そのStateとラウンド鍵とで排他的論理(Add-Round-key)を実行する(S6)。S3からS6のステップを9回繰り返し実行する。

【0081】

そして、最後にバイト・サブ(Byte-Sub)(S7)、シフト・ロウ(Shift-Row)(S8)、ラウンド鍵処理(Add-Round-Key)(S9)を実行し、暗号文(Encrypted)を得る(S10)。

【0082】

暗号化処理の中心となるのは、バイト・サブ(Byte-sub)やシフト・ロウ(Shift-Row)、ミックス・コラム(Mix-Column)、ラウンド鍵処理(Add-Round-Key)の4つの変換処理である。これら4つの変換処理を実現するにあたり、各変換処理を実現するためのカスタム命令を作成した。

【0083】

この実施例においては、バイト・サブ(Byte-Sub)は32ビット、シフト・ロウ(Shift-Row)は128ビット、ミックス・コラム(Mix-Column)は64ビット、ラウンド鍵処理(Add-Round-Key)は128ビットずつの単位に分けて処理を行う実装をした。このため、それらの前後でデータの分割、結合などを行うための命令も追加した。

【0084】

図8、図9はバイト・サブ(Byte-sub)、シフト・ロウ(Shift-Row)、ミックス・コラム(Mix-Column)、ラウンド鍵処理(Add-Round-Key)を含むC言語で記述したAESの暗号化処理の中間コード111の記述例である。

【0085】

図8、図9に示すように、AES暗号化のメインルーチンは、「Encrypt」関数である。図8の中間コード中、カスタム命令は、先頭に「vu1_」がつている箇所である。

【0086】

これにより、全体処理で309サイクル、暗号化の処理部分で79サイクルの結果が得られた。

【実施例2】

【0087】

DESは米国商務省標準局で標準化されている暗号規格である。暗号化と復号化に同じ鍵を使用する共通鍵暗号で、64ビットの平文と56ビットの鍵を入力することによって、暗号文64ビットを出力する。

【0088】

DESの暗号化処理では、まず64ビットのビット列を入力し、それに対して、転置表を元に初期転置を行う。転置したビット列を32ビットずつ分割する。分割したビット列をそれぞれ鍵と暗号化関数Fで暗号化する。鍵は入力した56ビット鍵から生成された48ビットのラウンド鍵を使用する。

【0089】

この処理を16回行い、作成した左右ビット列を結合して最終転置を行い、その結果が暗号文として出力される。

【0090】

図10はDES暗号化処理のフローチャートを示したものである。動的論理回路再構成可能プロセッサ20上でのDES暗号化処理には、カスタム命令を6つ必要とした。

【0091】

表1は、DES暗号化処理に用いたカスタム命令とその内容を示したものである。

【0092】

【表1】

【0093】

先ず、命令0で鍵56ビットをメモリからリコンフィギュラブル・データ・パス24に入力し同時に転置を行う。同様に命令1で平文64ビットを入力し、同時に初期転置を行う。次にラウンド回数によって、命令2、あるいは命令3で鍵の循環シフトを行う。命令4では鍵の縮約転置および暗号化F関数を一命令で行う。

【0094】

各命令間のデータの授受は全てレジスタ・ファイル25を介して行っている。このラウンドを16回繰り返す。図10では繰り返しが条件分岐処理になっているが、本実施例では繰り返しは展開して逐次処理を行った。これは条件分岐処理で実行するにはラウンド回数を判定するための回路を余分につくる必要があり、設計する回路規模を縮小するためである。最後に初期転置の逆の転置を行い、暗号文64ビットをメモリに出力する。

【0095】

表2は、再構成可能プロセッサ20でDES暗号化処理を行った際の動作周波数とスループットを示したものである。

【0096】

【表2】

【0097】

この実施例ではDES暗号化処理の動作周波数は6.25MHZであった。比較対象として、Intel Pentium(登録商標)4上でDES暗号化処理を行った際の結果も表2に示す。Intel Pentium(登録商標)4上へのDES暗号化処理の実装は、C言語によってDES暗号

化処理の仕様を忠実に記述したものをコンパイルすることによって行った。コンパイルオプションには−O2を用いた。

【0098】

表2から再構成可能プロセッサ20上でのDES暗号化処理は、Intel Pentium(登録商標)4上でのDES暗号化処理よりも3.8倍高い性能を示した。これは、動的再構成可能プロセッサ20の構成要素であるPEが入力に対して1ビット単位で任意の論理関数を割り当てることが可能であるとう特徴をDES暗号化処理に生かすことができたためである。

【0099】

DES暗号化処理では、1ビット単位での転置や換字を繰り返す。Intel Pentium(登録商標)4などの32ビットマイクロプロセッサでは、1ビット単位で処理を行う際には、1ビットを取り出す処理が必要となる。動的再構成可能プロセッサ20のPEは1ビット単位の転置処理では、データをレジスタ・ファイル25からリコンフィギュラブル・データ・パス24に取り込み、指定のビット位置に移動させて再びレジスタ・ファイル25に格納する。これによって、大量のデータの転置処理が一命令で可能となった。

【0100】

また、PEでは入力に対して任意の論理関数を割り当てることができるので、データ依存関係のある複数の処理を合成し、一命令で実行することによって、実行クロック・サイクル数を削減することが可能であった。リコンフィギュラブル・データ・パス24上でのDES暗号化処理において、平文64ビットの暗号化に要したクロック・サイクル数は70サイクルであった。

【産業上の利用可能性】

【0101】

本発明は、カスタムLSIの設計及び開発を行う場合のプラットフォームとして利用することができる。また、アプリケーションに特化したカスタムLSIの製造に利用することもでき、産業上の利用可能性がある。

【図面の簡単な説明】

【0102】

【図1】本発明のカスタムLSI開発プラットフォーム1の全体構成ブロック図である。

【図2】ソフトウェアプログラム10の詳細ブロック図を示したものである。

【図3】ISAジェネレータ110の詳細ブロック図を示したものである。

【図4】本発明の一実施の形態である再構成可能プロセッサ20のブロック図を示したものである。

【図5】命令フォーマットの構成を示した図である。

【図6】リコンフィギュラブル・データ・パス24の構成の一実施形態を示したものである。

【図7】AES暗号化の処理の流れを示した図である。

【図8】AESの暗号化処理の中間コードの記述例である。

【図9】AESの暗号化処理の中間コードの記述例である。

【図10】DES暗号化処理のフローチャートを示したものである。

【符号の説明】

【0103】

1 カスタムLSI開発プラットフォーム

10 ソフトウェアプログラム

20 再構成可能プロセッサ

21 コントローラ

22 スタック

23 コンフィギュレーション・メモリ

24 再構成可能論理回路(リコンフィギュラブル・データ・パス)

25 レジスタ・ファイル

26 メモリ

100 Cソースプログラム

110 ISAジェネレータ

111 中間コード

112 命令セット・アーキテクチャ(ISA)

130 論理回路構成ジェネレータ

131 論理回路構成情報

141 プログラム・オブジェクトコード

142 論理回路構成・オブジェクトコード

160 ライブラリ

【特許請求の範囲】

【請求項1】

高級言語で記述されたプログラム(以下、ソースプログラム)から命令セット・アーキテクチャ(以下、ISA)を自動生成する手段(以下、ISAジェネレータ)を含むソフトウェアプログラムと、前記生成されたISAに対応して論理回路を再構成する手段を含む再構成可能プロセッサとを備えたカスタムLSI開発プラットフォームであって、

前記ISAジェネレータは、

ソースプログラムの命令のパターンを抽出する手段と、

前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換する手段と

を備えたことを特徴とするカスタムLSI開発プラットフォーム。

【請求項2】

前記ソフトウェアプログラムは、前記再構成可能プロセッサの論理回路を構成するプログラマブル・エレメント(以下、PE)の配置配列情報と前記生成されたISAとから前記プロセッサの論理回路構成情報を生成する論理回路構成ジェネレータを備えたことを特徴とする請求項1に記載のカスタムLSI開発プラットフォーム。

【請求項3】

前記ソフトウェアプログラムは、

前記生成されたISAを前記再構成可能プロセッサの実行可能可能なコード(以下、プログラム・オブジェクトコード)に変換する手段と、

前記論理回路構成情報を前記再構成可能プロセッサの実行可能可能なコード(以下、論理回路構成・オブジェクトコード)に変換する手段と

を備えたことを特徴とする請求項1または2に記載のカスタムLSI開発プラットフォーム。

【請求項4】

前記再構成可能プロセッサは、前記プログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとに基づいて、PEを再配置し論理回路を再構成する手段を備えたことを特徴とする請求項1から3のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項5】

前記ISAジェネレータは、

ライブラリに格納されているカスタム命令を呼び出すファンクションコール手段と、

前記プロセッサの制御命令を含む中間コードを生成する手段と

を備えたことを特徴とする請求項1から4のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項6】

前記プログラム・オブジェクトコードと前記論理回路再構成・オブジェクトコードに基づいて、前記再構成可能プロセッサが前記ソースプログラムを実行するパフォーマンスをシミュレートする手段を備えたことを特徴とする請求項1から5のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項7】

前記抽出した命令をカスタム命令に置換するプロセスにおいて、カスタム命令に置き換えられなかった命令を新たなカスタム命令として生成する手段を備えたことを特徴とする請求項1から6のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項8】

再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)の生成方法であって、

高級言語で記述されたプログラム(以下、ソースプログラム)の命令のパターンを抽出し、

前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、

前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換し、前記再構成可能プロセッサ用のISAを生成することを特徴とするISAの生成方法。

【請求項9】

置換されたカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報を抽出し、該論理素子接続情報を含んでISAを生成することを特徴とする請求項8に記載のISAの生成方法。

【請求項10】

前記プロセッサが動的再構成可能プロセッサであることを特徴とする請求項8又は9に記載のISAの生成方法。

【請求項11】

前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換するプロセスにおいて、前記ソースプログラムの命令中、カスタム命令に置換できなかった命令を、新たなカスタム命令として定義するとともに前記ライブラリに追加し、カスタム命令の再抽出を行うことを特徴とする請求項8から10のいずれかに記載のISAの生成方法。

【請求項12】

再構成可能プロセッサの論理回路構成情報の生成方法であって、

高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出し、

前記抽出された命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、

前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換し、

前記抽出したカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と、前記プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成することを特徴とする論理回路構成情報の生成方法。

【請求項13】

前記再構成可能プロセッサが、動的再構成可能プロセッサであることを特徴とする請求項12に記載の論理回路構成情報の生成方法。

【請求項14】

請求項3に記載のプログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとを実行する手段を備えた再構成可能プロセッサ。

【請求項15】

動的再構成可能論理回路と、

前記動的再構成可能論理回路を構成するプログラマブル・エレメント(以下、PE)の命令毎の配置配列情報を記憶するコンフィギュレーション・メモリと、

命令の実行の中間結果を一時的に保持するレジスタ・ファイルと、

命令を保持するメモリと、

命令の実行順序を含むプロセッサの管理を行うコントローラと

を備えたことを特徴とする請求項14に記載の再構成可能プロセッサ。

【請求項16】

前記コントローラは、前記メモリにアクセスするときのインデックスを記憶するインデックス・レジスタを備えたことを特徴とする請求項14又は15に記載の再構成可能プロセッサ。

【請求項17】

前記インデックス・レジスタの値を記憶するスタックを更に備えたことを特徴とする請求項14から16のいずれかに記載の再構成可能プロセッサ。

【請求項18】

コンピュータに実行させ再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)を生成するコンピュータ・プログラムであって、

前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、

前記抽出した命令パターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、

前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップと

をコンピュータに実行させるISAを生成するコンピュータ・プログラム。

【請求項19】

コンピュータに実行させ動的再構成可能プロセッサの論理回路構成情報を生成するコンピュータ・プログラムであって、

前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、

前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、

前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップと、

前記命令セットに含まれるカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と前記再構成可能プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成するステップと

をコンピュータに実行させる論理回路構成情報を生成するコンピュータ・プログラム。

【請求項1】

高級言語で記述されたプログラム(以下、ソースプログラム)から命令セット・アーキテクチャ(以下、ISA)を自動生成する手段(以下、ISAジェネレータ)を含むソフトウェアプログラムと、前記生成されたISAに対応して論理回路を再構成する手段を含む再構成可能プロセッサとを備えたカスタムLSI開発プラットフォームであって、

前記ISAジェネレータは、

ソースプログラムの命令のパターンを抽出する手段と、

前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換する手段と

を備えたことを特徴とするカスタムLSI開発プラットフォーム。

【請求項2】

前記ソフトウェアプログラムは、前記再構成可能プロセッサの論理回路を構成するプログラマブル・エレメント(以下、PE)の配置配列情報と前記生成されたISAとから前記プロセッサの論理回路構成情報を生成する論理回路構成ジェネレータを備えたことを特徴とする請求項1に記載のカスタムLSI開発プラットフォーム。

【請求項3】

前記ソフトウェアプログラムは、

前記生成されたISAを前記再構成可能プロセッサの実行可能可能なコード(以下、プログラム・オブジェクトコード)に変換する手段と、

前記論理回路構成情報を前記再構成可能プロセッサの実行可能可能なコード(以下、論理回路構成・オブジェクトコード)に変換する手段と

を備えたことを特徴とする請求項1または2に記載のカスタムLSI開発プラットフォーム。

【請求項4】

前記再構成可能プロセッサは、前記プログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとに基づいて、PEを再配置し論理回路を再構成する手段を備えたことを特徴とする請求項1から3のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項5】

前記ISAジェネレータは、

ライブラリに格納されているカスタム命令を呼び出すファンクションコール手段と、

前記プロセッサの制御命令を含む中間コードを生成する手段と

を備えたことを特徴とする請求項1から4のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項6】

前記プログラム・オブジェクトコードと前記論理回路再構成・オブジェクトコードに基づいて、前記再構成可能プロセッサが前記ソースプログラムを実行するパフォーマンスをシミュレートする手段を備えたことを特徴とする請求項1から5のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項7】

前記抽出した命令をカスタム命令に置換するプロセスにおいて、カスタム命令に置き換えられなかった命令を新たなカスタム命令として生成する手段を備えたことを特徴とする請求項1から6のいずれかに記載のカスタムLSI開発プラットフォーム。

【請求項8】

再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)の生成方法であって、

高級言語で記述されたプログラム(以下、ソースプログラム)の命令のパターンを抽出し、

前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、

前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換し、前記再構成可能プロセッサ用のISAを生成することを特徴とするISAの生成方法。

【請求項9】

置換されたカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報を抽出し、該論理素子接続情報を含んでISAを生成することを特徴とする請求項8に記載のISAの生成方法。

【請求項10】

前記プロセッサが動的再構成可能プロセッサであることを特徴とする請求項8又は9に記載のISAの生成方法。

【請求項11】

前記抽出した命令をカスタム命令、及び/又はカスタム命令の組み合わせで置換するプロセスにおいて、前記ソースプログラムの命令中、カスタム命令に置換できなかった命令を、新たなカスタム命令として定義するとともに前記ライブラリに追加し、カスタム命令の再抽出を行うことを特徴とする請求項8から10のいずれかに記載のISAの生成方法。

【請求項12】

再構成可能プロセッサの論理回路構成情報の生成方法であって、

高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出し、

前記抽出された命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較し、

前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換し、

前記抽出したカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と、前記プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成することを特徴とする論理回路構成情報の生成方法。

【請求項13】

前記再構成可能プロセッサが、動的再構成可能プロセッサであることを特徴とする請求項12に記載の論理回路構成情報の生成方法。

【請求項14】

請求項3に記載のプログラム・オブジェクトコードと前記論理回路構成・オブジェクトコードとを実行する手段を備えた再構成可能プロセッサ。

【請求項15】

動的再構成可能論理回路と、

前記動的再構成可能論理回路を構成するプログラマブル・エレメント(以下、PE)の命令毎の配置配列情報を記憶するコンフィギュレーション・メモリと、

命令の実行の中間結果を一時的に保持するレジスタ・ファイルと、

命令を保持するメモリと、

命令の実行順序を含むプロセッサの管理を行うコントローラと

を備えたことを特徴とする請求項14に記載の再構成可能プロセッサ。

【請求項16】

前記コントローラは、前記メモリにアクセスするときのインデックスを記憶するインデックス・レジスタを備えたことを特徴とする請求項14又は15に記載の再構成可能プロセッサ。

【請求項17】

前記インデックス・レジスタの値を記憶するスタックを更に備えたことを特徴とする請求項14から16のいずれかに記載の再構成可能プロセッサ。

【請求項18】

コンピュータに実行させ再構成可能プロセッサの命令セット・アーキテクチャ(以下、ISA)を生成するコンピュータ・プログラムであって、

前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、

前記抽出した命令パターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、

前記抽出した命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップと

をコンピュータに実行させるISAを生成するコンピュータ・プログラム。

【請求項19】

コンピュータに実行させ動的再構成可能プロセッサの論理回路構成情報を生成するコンピュータ・プログラムであって、

前記コンピュータ・プログラムは、高級言語で記述されたプログラム(以下、ソースプログラム)の命令パターンを抽出するステップと、

前記抽出した命令のパターンとライブラリに格納されているカスタム命令のパターンとを比較するステップと、

前記抽出された命令を前記カスタム命令、及び/又はカスタム命令の組み合わせで置換するステップと、

前記命令セットに含まれるカスタム命令と関連付けられてライブラリに格納されている論理素子接続情報と前記再構成可能プロセッサのプログラマブル・エレメント(以下、PE)の配置配列情報とから、論理回路構成情報を生成するステップと

をコンピュータに実行させる論理回路構成情報を生成するコンピュータ・プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2006−185423(P2006−185423A)

【公開日】平成18年7月13日(2006.7.13)

【国際特許分類】

【出願番号】特願2005−338457(P2005−338457)

【出願日】平成17年11月24日(2005.11.24)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成16年11月5日 財団法人福岡県産業・科学技術振興財団他5者主催の「福岡システムLSI総合開発センターオープン記念等合同フォーラム」において文書をもって発表

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【出願人】(504145342)国立大学法人九州大学 (960)

【出願人】(391043332)財団法人福岡県産業・科学技術振興財団 (53)

【出願人】(596134367)財団法人九州システム情報技術研究所 (12)

【Fターム(参考)】

【公開日】平成18年7月13日(2006.7.13)

【国際特許分類】

【出願日】平成17年11月24日(2005.11.24)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成16年11月5日 財団法人福岡県産業・科学技術振興財団他5者主催の「福岡システムLSI総合開発センターオープン記念等合同フォーラム」において文書をもって発表

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【出願人】(504145342)国立大学法人九州大学 (960)

【出願人】(391043332)財団法人福岡県産業・科学技術振興財団 (53)

【出願人】(596134367)財団法人九州システム情報技術研究所 (12)

【Fターム(参考)】

[ Back to top ]