ガロア体の逆元演算回路

【課題】ダイナミックハザードに起因する消費電力の増加を一様に抑えて、DPA攻撃を困難にする。

【解決手段】8ビットの入力データは4つのデコーダ111乃至114によって2ビットずつデコードされ、それぞれ4ビットずつ計16ビットのデコードデータとなる。演算部120はデコードデータに対してGF(((22)2)2)逆元演算を行う。演算結果は4つのエンコーダ131乃至124によって4ビットずつエンコードされ、それぞれ2ビットずつ計8ビットの出力データとなる。デコーダ111乃至114は共通の制御信号PCdlyに同期して演算開始前に固定値「0000」を一旦出力した後に、入力データに応じて何れか1ビットのみを「1」に変化させる。演算部120は固定値が入力されると固定値を出力し、固定値以外が入力されると演算結果を出力する。これにより、中間値への遷移を抑止する。

【解決手段】8ビットの入力データは4つのデコーダ111乃至114によって2ビットずつデコードされ、それぞれ4ビットずつ計16ビットのデコードデータとなる。演算部120はデコードデータに対してGF(((22)2)2)逆元演算を行う。演算結果は4つのエンコーダ131乃至124によって4ビットずつエンコードされ、それぞれ2ビットずつ計8ビットの出力データとなる。デコーダ111乃至114は共通の制御信号PCdlyに同期して演算開始前に固定値「0000」を一旦出力した後に、入力データに応じて何れか1ビットのみを「1」に変化させる。演算部120は固定値が入力されると固定値を出力し、固定値以外が入力されると演算結果を出力する。これにより、中間値への遷移を抑止する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ガロア体の逆元演算回路に関し、特にメッセージの暗号化または復号化の際に利用されるガロア体の逆元演算回路に関する。

【背景技術】

【0002】

2001年、米国国立標準技術研究所(NIST)はRijndealを次期米国標準の128ビット共通鍵ブロック暗号AES(Advanced Encryption Standard)として選出した。AESの回路実装においては、演算速度の高速化や回路規模削減手法が学会等で報告されてきているが、それに加えて、低消費電力化やサイドチャンネル攻撃に対する耐性をもつ構成も近年報告されている。特に、従来の共通鍵ブロック暗号のDES(Data Encryption Standard)の置換えとして用いる場合、電池動作の組込み機器への搭載や、非接触動作するICカードへの搭載に際しては、消費電力に対する仕様は著しく制限される。

【0003】

AES暗号の入力データは128ビットであるが、8ビットを単位とした4×4のマトリクスとして定義され、演算処理は8ビット単位で行われる。暗号化の際の演算処理としては、SubBytes、ShiftRows、MixColumns、AddRoundKeyが行われる。SubBytesは、8ビットデータに対して逆元を計算し、アフィン変換を行うものである。ShiftRowsは、4×4のマトリクスの横方向(各行)に対して回転処理を行うものである。MixColumnsは、4×4のマトリクスの縦方向(各列)に対して処理を行うものである。AddRoundKeyは、ラウンド鍵との排他的論理和(XOR)演算を行うものである。この中で、回路規模および消費電力が最も大きいのがSubBytesである。このSubBytesでは、8ビット入力8ビット出力のテーブル(Sbox)が定義され、このテーブルに従った変換が行われる。このテーブルSboxは、16個必要とされる。

【0004】

Sboxの主要な構成方法としては、(1)テーブルをランダムロジックにて構成する方法、(2)二分決定グラフにより構成する方法、(3)合成体上で逆元演算を行う数値演算回路により構成する方法が考えられる。これらを比較すると、一般的にゲート規模は(1)、(2)、(3)の順に小さくなり、ゲート規模の観点からは(3)の逆元演算が有利である。(3)の逆元演算では、AESの仕様書に公開されているように、入力値を以下の既約多項式でのガロア体GF(28)の要素とみなして演算する。

x8+x4+x3+x+1

【0005】

Sboxの暗号化時の演算式は、暗号化演算時の8ビット入力を(b7 b6 b5 b4 b3 b2 b1 b0)、8ビット出力を(b7' b6' b5' b4' b3' b2' b1' b0')としたとき、出力は以下の演算式により生成される。

【数1】

【0006】

復号化演算時の8ビット入力を(b7' b6' b5' b4' b3' b2' b1' b0')、8ビット出力を(b7 b6 b5 b4 b3 b2 b1 b0)としたとき、出力は以下の演算式により生成される。

【数2】

【0007】

ガロア体上の演算では、基底が異なれば異なる演算になる。SubBytesで用いる既約多項式とは異なる体に合成体がある。ここで、合成体とは、素体から複数回の拡大により得られた体をいう。合成体上の乗算はさらに小さい合成体を用いて構成することができ、これにより、回路規模を削減することができる(例えば、非特許文献1参照。)。以下の既約多項式(式1)を使って得られる合成体GF(((22)2)2)上の逆元演算回路は、GF(28)と同形な体上の逆元演算回路として得られる。

GF(2)→GF(22): x2+x+1

GF(22)→GF((22)2): x2+x+φ ・・・(式1)

GF((22)2)→GF(((22)2)2): x2+x+λ

ただし、φ={10}2、λ={1100}2である。

【0008】

逆元の演算は、もとの体Aの元を同形写像δで合成体Bへマップし、合成体B上で逆元演算を実行した後、同形写像δ-1でもとの体Aへマップするという手順で行われる。合成体GF(((22)2)2)上の逆元演算において、入力データを(PH,PL)、出力データを(PH-1, PL-1)としたとき、2つのデータの積は次式のようになる。

(PH・x+PL)・(PH-1・x+PL-1)

=PH・PH-1・x2+(PH・PL-1+PL・PH-1)x+PL・PL-1

=PH・PH-1・(x+λ)+(PH・PL-1+PL・PH-1)・x+PL・PL-1

=(PH・PH-1+PH・PL-1+PL・PH-1)・x+PH・PH-1・λ+PL・PL-1

=1

これにより、次式が得られる。

PH・PH-1+PH・PL-1+PL・PH-1=0

PH・PH-1・λ+PL・PL-1=1

上式をPH-1およびPL-1について解くと、以下の式が得られる。

【数3】

【0009】

この合成体上での8ビットの逆元演算を用いた(3)の構成では、回路規模は、他の2つの構成に比べて半分以下になるが、消費電流に関してはゲート規模の比率ほどは小さくならない。原因としては、乗算回路や逆元演算回路の2つの入力の遅延差に起因するダイナミックハザードが考えられる。このダイナミックハザードは後段に行くほど累積され、余分な電力消費が増加する。8ビットの逆元演算回路の最終段には、2つの4ビット乗算器が配置されるが、逆元演算回路への信号入力を起点とした時、上位側の乗算器の一方の入力は遅延ゼロでデータが入力されるのに対して、他方の入力は十数乃至三十数ゲートの遅延でデータが入力される。この間、出力は一旦中間値に遷移してから演算結果に遷移する。そして、遅延はビット毎に異なり、さらに、各ビット値が「0」か「1」かにより遅延は異なってくる。また、この逆元演算回路の入力信号も、ビット毎に異なるタイミングで入ってくる。これらにより、最終的な値に到達するまでに、8ビットの逆元演算回路は様々な中間値に遷移し、その度に演算回路での貫通電流および負荷で充放電電流を消費する。そして、この充放電電流は、消費電流を測定して、それに統計処理を施すことにより鍵を取り出すDPA(Difference Power Analysis)攻撃の対象となる。このようなDPA攻撃への対策の1つとして、遅延調整のための遅延回路を配置して、2入力演算回路の信号遅延差を調整する方法が提案されている(例えば、非特許文献1参照。)。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】Sumio Morioka and Akashi Satoh : "An Optimized S-box circuit architecture for low power AES design", Workshop on Cryptographic Hardware and Embedded Systems 2002(CHES 2002),第172乃至186頁,2002年8月

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述のDPA攻撃に対処するために、遅延調整のための遅延回路を配置して、2入力演算回路の信号遅延差を調整する方法が提案されている。しかしながら、入力の遅延差は入力データ値によっても異なるため、すべてのデータに対して一様に消費電力を削減することは困難である。そして、削減できなかったハザード電流により、DPA攻撃に対する脅威は依然残ってしまう。

【0012】

本発明はこのような状況に鑑みてなされたものであり、ダイナミックハザードに起因する消費電力の増加を一様に抑えて、DPA攻撃に対して耐性のある回路構成を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明は、上記課題を解決するためになされたものであり、その第1の側面は、ガロア体の入力データよりもビット幅が広い所定の固定値を一旦出力した後に、上記入力データに応じて上記固定値から所定ビット数だけ異なる値を示すデコードデータを出力するデコーダと、上記デコードデータに対してガロア体の逆元演算を実行して上記デコードデータの逆元データを出力する演算部と、上記逆元データを上記入力データと等しいビット幅の出力データにエンコードするエンコーダとを具備するガロア体の逆元演算回路である。これにより、固定値から所定ビット数だけ異なるデコードデータを演算対象として、中間値への遷移を抑止するという作用をもたらす。

【0014】

また、この第1の側面において、上記デコーダは、制御信号に同期して上記固定値の出力を行うようにしてもよい。これにより、入力データの各ビットの遷移にばらつきがある場合であっても一斉に演算を駆動するという作用をもたらす。

【0015】

また、この第1の側面において、上記制御信号は、上記入力データが上記デコーダに入力されるタイミングを示すものであってもよい。これにより、デコーダに入力されるタイミングに合わせて一斉に演算を駆動するという作用をもたらす。

【0016】

また、この第1の側面において、上記演算部は、上記デコーダから上記固定値が出力されている間は上記固定値を出力するようにしてもよい。これにより、演算結果の遷移する期間を制限するという作用をもたらす。

【0017】

また、本発明の第2の側面は、ガロア体の8ビットの入力データを2ビットずつに区切った4組の部分データに対してそれぞれ4ビット幅の固定値を一旦出力した後に、上記部分データに応じて上記固定値から1ビットだけ異なる4ビット幅のデコードデータをそれぞれ出力する4つのデコーダと、上記4組のデコードデータからなる16ビットデータに対して逆元演算を実行して上記16ビットデータの逆元データを出力する演算部と、上記逆元データを4ビットずつに区切ってそれぞれ2ビット幅の出力データにエンコードする4つのエンコーダとを具備するガロア体の逆元演算回路である。これにより、固定値から4ビット中1ビットだけ異なるデコードデータを演算対象として、中間値への遷移を抑止するという作用をもたらす。

【0018】

また、この第2の側面において、上記4つのデコーダは、共通の制御信号に同期して上記固定値の出力を行うようにしてもよい。これにより、8ビットの入力データの各ビットの遷移にばらつきがある場合であっても一斉に演算を駆動するという作用をもたらす。

【0019】

また、この第2の側面において、上記制御信号は、上記入力データが上記デコーダに入力されるタイミングを示すものであってもよい。これにより、デコーダに入力されるタイミングに合わせて一斉に演算を駆動するという作用をもたらす。

【0020】

また、この第2の側面において、上記演算部は、上記4つのデコーダの全てが上記固定値を出力している間は4組の上記固定値からなる16ビット幅のデータを出力するようにしてもよい。これにより、演算結果の遷移する期間を制限するという作用をもたらす。

【発明の効果】

【0021】

本発明によれば、ダイナミックハザードに起因する消費電力の増加を一様に抑えて、DPA攻撃を困難にすることができるという優れた効果を奏し得る。

【図面の簡単な説明】

【0022】

【図1】本発明において想定する暗号化および復号化の処理手順例を示す図である。

【図2】本発明において想定する暗号化および復号化の共通化した処理手順例を示す図である。

【図3】本発明において想定するSubBytes/Inv_SubBytes(931)の処理内容を示す図である。

【図4】既約多項式を用いた逆元演算回路の基本原理を示す図である。

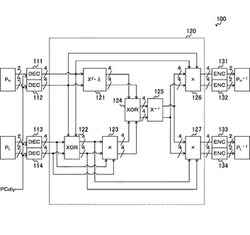

【図5】本発明の実施の形態におけるGF(((22)2)2)逆元演算回路100の構成例を示す図である。

【図6】本発明の実施の形態におけるデコーダ111乃至114およびエンコーダ131乃至134の構成例を示す図である。

【図7】本発明の実施の形態におけるデコーダ111乃至114の各々の動作の真理値表を示す図である。

【図8】本発明の実施の形態におけるエンコーダ131乃至134の各々の動作の真理値表を示す図である。

【図9】本発明の実施の形態におけるx2・λ演算回路121の構成例を示す図である。

【図10】本発明の実施の形態におけるx2・λ演算回路121の動作の真理値表である。

【図11】本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例を示す図である。

【図12】本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例による動作の真理値表である。

【図13】本発明の第1の実施の形態における排他的論理和演算回路122および124の動作タイミング例を示す図である。

【図14】本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例を示す図である。

【図15】本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例による動作の真理値表である。

【図16】本発明の実施の形態における乗算回路123、126および127の構成例を示す図である。

【図17】本発明の実施の形態におけるインバータ236の構成例を示す図である。

【図18】本発明の実施の形態における否定排他的論理和演算回路231および232の構成例を示す図である。

【図19】本発明の実施の形態における乗算回路233の構成例を示す図である。

【図20】本発明の実施の形態における乗算回路233の構成例による動作の真理値表である。

【図21】本発明の実施の形態における乗算φ演算回路234の構成例を示す図である。

【図22】本発明の実施の形態における乗算φ演算回路234の構成例による動作の真理値表である。

【図23】本発明の実施の形態における負論理乗算回路235の構成例を示す図である。

【図24】本発明の実施の形態における負論理乗算回路235の構成例による動作の真理値表である。

【図25】本発明の実施の形態における負論理入力排他的論理和演算回路237の構成例を示す図である。

【図26】本発明の実施の形態における乗算回路123、126および127の動作タイミング例を示す図である。

【図27】本発明の実施の形態によるGF(((22)2)2)逆元演算回路100の構成例における遅延量を示す図である。

【図28】本発明の第1の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。

【図29】本発明の第2の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。

【発明を実施するための形態】

【0023】

以下、本発明を実施するための形態(以下、実施の形態と称する)について説明する。説明は以下の順序により行う。

1.第1の実施の形態(1ラウンドの処理を2相に分けて実行する例)

2.第2の実施の形態(1ラウンドの処理を1クロックサイクルで実行する例)

3.変形例

【0024】

<1.第1の実施の形態>

[暗号化装置または復号化装置の構成]

図1は、本発明において想定する暗号化および復号化の処理手順例を示す図である。図1(a)は、メッセージを暗号化するための処理手順であり、SubBytes(911)、ShiftRows(912)、MixColumns(915)、AddRoundKey(916)の各手順を含む。AES暗号の入力データは128ビットであるが、8ビットを単位とした4×4のマトリクスとして定義され、演算処理は8ビット単位で行われる。この128ビットの入力データは、ラウンド演算の開始前(Rd0)に入力され、AddRoundKey(916)を経てレジスタ910に保持される。

【0025】

SubBytes(911)は、8ビットデータに対して逆元を計算し、アフィン変換を行うものである。ShiftRows(912)は、4×4のマトリクスの横方向(各行)に対して回転処理を行うものである。MixColumns(915)は、4×4のマトリクスの縦方向(各列)に対して演算処理を行うものである。AddRoundKey(916)は、ラウンド鍵(919)との排他的論理和(XOR)演算を行うものである。レジスタ910には、各手順を1ラウンド行う度に(Rd1乃至10)中間値が更新される。

【0026】

この暗号化処理では、各手順を10ラウンド繰り返した後にレジスタ910に保持された値が暗号として出力される。なお、最終ラウンド(Rd10)では、MixColumns(915)の処理は行われない。

【0027】

図1(b)は、暗号化されたメッセージを復号化するための処理手順であり、Inv_SubBytes(921)、Inv_ShiftRows(922)、AddRoundKey(923)、Inv_MixColumns(925)の各手順を含む。暗号化されたメッセージは、ラウンド演算の開始前(Rd10)に入力され、AddRoundKey(923)を経てレジスタ920に保持される。

【0028】

Inv_SubBytes(921)は、SubBytes(911)の逆の処理を行うものである。Inv_ShiftRows(922)は、ShiftRows(912)の逆の処理を行うものである。AddRoundKey(923)は、ラウンド鍵(928)との排他的論理和演算を行うものである。Inv_MixColumns(925)は、MixColumns(915)の逆の処理を行うものである。レジスタ920には、各手順を1ラウンド行う度に(Rd9乃至0)中間値が更新される。

【0029】

この復号化処理では、各手順を10ラウンド繰り返した後にレジスタ920に保持された値が復号化されたメッセージとして出力される。なお、最終ラウンド(Rd0)では、Inv_MixColumns(925)の処理は行われない。

【0030】

ここで、SubBytes(911)およびShiftRows(912)とInv_SubBytes(921)およびInv_ShiftRows(922)とは対になる処理であるため、暗号化処理と復号化処理との間で共通化することができる。MixColumns(915)とInv_MixColumns(925)との間も同様である。そこで、次のように両者を共通化した処理手順として実現した場合のイメージを示す。

【0031】

図2は、本発明において想定する暗号化および復号化の共通化した処理手順例を示す図である。SubBytes/Inv_SubBytes(931)は、SubBytes(911)とInv_SubBytes(921)とを共通化したものである。ShiftRows/Inv_ShiftRows(932)は、ShiftRows(912)とInv_ShiftRows(922)とを共通化したものである。AddRoundKey(933)は、AddRoundKey(923)と同様に、ラウンド鍵(928)との排他的論理和演算を行うものである。選択手順934は、暗号化時にAddRoundKey(933)を経ない値を選択し、復号化時にAddRoundKey(933)の出力を選択するものである。MixColumns/Inv_MixColumns(935)は、MixColumns(915)とInv_MixColumns(925)とを共通化したものである。AddRoundKey(936)は、AddRoundKey(916)と同様に、ラウンド鍵(919)との排他的論理和演算を行うものである。選択手順937は、暗号化時にAddRoundKey(936)の出力を選択し、復号化時にAddRoundKey(936)を経ない値を選択するものである。レジスタ930は、レジスタ910とレジスタ920とを共通化したものであり、暗号化または復号化の中間値を保持するものである。

【0032】

図3は、本発明において想定するSubBytes/Inv_SubBytes(931)の処理内容を示す図である。このSubBytes/Inv_SubBytes(931)を、以下ではSboxと呼称する。上述のレジスタ930の出力は、別の演算回路に入力されることなく、このSboxに入力される。このSboxは、暗号化時と復号化時とで共通化されているため、両者を切り換えるスイッチ34および38を備えている。

【0033】

Sboxにおいて、暗号化時には、同形写像変換回路12において写像変換δを行い、逆元演算回路100においてGF(((22)2)2)上の逆元演算を行う。そして、逆同形写像変換・アフィン変換回路16において逆写像変換δ-1とアフィン変換を行った後に排他的論理和(XOR)演算回路17により排他的論理和演算を行う。

【0034】

一方、復号化時には、排他的論理和演算回路21により排他的論理和演算を行った後に逆アフィン変換・同形写像回路22において逆アフィン変換と写像変換δを行う。そして、逆元演算回路100においてGF(((22)2)2)上の逆元演算を行う。その後、逆同形写像回路26において逆写像変換δ-1を行う。

【0035】

[逆元演算回路の構成]

図4は、既約多項式を用いた逆元演算回路の基本原理を示す図である。図4(a)は、8ビットのGF(((22)2)2)逆元演算回路である。ここでは、入力データの上位4ビットをPH、下位4ビットをPLにより表し、出力データの上位4ビットをPH-1、下位4ビットをPL-1により表している。逆元演算回路は階層的な構造を有し、合成体GF(((22)2)2)上の逆元演算は、以下の部分体GF((22)2)の演算回路を組み合わせることにより実現される。すなわち、このGF(((22)2)2)逆元演算回路は、x2・λ演算回路811と、排他的論理和演算回路812および814と、乗算回路813、816および817と、逆元演算回路820とを備える。

【0036】

図4(b)は、4ビットのGF((22)2)逆元演算回路820である。合成体GF((22)2)上の逆元演算は、以下の部分体GF(22)の演算を組み合わせることにより実現される。すなわち、このGF((22)2)逆元演算回路820は、x2・φ演算回路821と、排他的論理和演算回路822および824と、乗算回路823、826および827と、逆元演算回路830とを備える。

【0037】

上述のとおり、この逆元演算回路の基本原理をそのまま利用した場合、ダイナミックハザードによる中間値への遷移のため、DPA攻撃の対象とされるおそれが生じる。そこで、本発明の実施の形態では、逆元演算回路の前段にデコーダを配置して、逆元演算回路をデコードデータによるテーブル回路で構成することにより、演算によるゲート遅延を削減する。そして、それとともに、演算回路の入力が全て確定するまで固定値を出力する構成を採ることにより、中間値への遷移を抑止するように制御を行う。

【0038】

図5は、本発明の実施の形態におけるGF(((22)2)2)逆元演算回路100の構成例を示す図である。このGF(((22)2)2)逆元演算回路100は、4つのデコーダ111乃至114と、演算部120と、4つのエンコーダ131乃至134とを備えている。

【0039】

デコーダ111乃至114は、8ビットの入力データのうちそれぞれ2ビットずつをデコードして、それぞれ4ビットのデコードデータを出力するものである。デコーダ111乃至114は、共通する制御信号PCdly(Phase Control delay)によって動作タイミングを制御される。なお、ここでは4つのデコーダ111乃至114を用いた例について説明するが、これらは一体化したものでもよく、また、任意の数に分割したものでもよい。

【0040】

演算部120は、デコーダ111乃至114から出力された16ビットのデコードデータに対してGF(((22)2)2)逆元演算を行うものである。部分体で使用する規約多項式が決まっている場合、合成体上での演算で、1つまたは2つの4ビット入力が決まれば、出力の4ビットは自動的に決まる。そして、ここでは、2ビット単位でデコードしたデータで演算がなされるものとしている。この演算部120は、図4(a)の基本原理に準じた構成を備えており、x2・λ演算回路121と、排他的論理和演算回路122および124と、乗算回路123、126および127と、GF((22)2)逆元演算回路125とを備える。各回路の構成についてはさらに後述する。

【0041】

エンコーダ131乃至134は、演算部120から出力された16ビットのデコードデータのうちそれぞれ4ビットずつをエンコードして、それぞれ2ビットのバイナリデータを出力するものである。なお、ここでは4つのエンコーダ131乃至134を用いた例について説明するが、これらは一体化したものでもよく、また、任意の数に分割したものでもよい。

【0042】

図6は、本発明の実施の形態におけるデコーダ111乃至114およびエンコーダ131乃至134の構成例を示す図である。

【0043】

図6(a)は、デコーダ111乃至114の構成例である。ここでは、デコーダ111の内部を代表として示しているが、デコーダ112乃至114についても同様の構成を備える。デコーダ111は、8ビットの入力データのうち上位の2ビットb6およびb7を入力として、b6およびb7ならびにこれらの反転信号を組み合わせて4ビットのデコードデータを生成する。このデコーダ111は、インバータと否定論理和(NOR)演算回路の2ゲート遅延を有する。また、否定論理和演算回路には制御信号PCdlyが入力され、この制御信号PCdlyが「1」を示す間は、デコードデータは所定の固定値になる。本発明の実施の形態では、所定の固定値としてデコードデータを全ビット「0」にすることを想定している。

【0044】

図6(b)は、エンコーダ131乃至134の構成例である。ここでは、エンコーダ131の内部を代表として示しているが、エンコーダ132乃至134についても同様の構成を備える。エンコーダ131は、16ビットのデコードデータのうち上位の4ビットを入力として、d0乃至d3を組み合わせて2ビットのエンコードデータを生成する。このエンコーダ131は、否定論理和演算回路とインバータの2ゲート遅延を有する。

【0045】

図7は、本発明の実施の形態におけるデコーダ111乃至114の各々の動作の真理値表を示す図である。上述のようにデコーダ111乃至114の各々には2ビットの入力データと制御信号PCdlyが入力される。制御信号PCdlyが「1」の場合、入力データにかかわらず、デコードデータは「0000」になる。制御信号PCdlyが「0」の場合、入力データに応じて、4ビットのデコードデータのうち1ビットだけが「1」となり、他のビットは「0」になる。

【0046】

これにより、制御信号PCdlyのタイミングに合わせてデコードデータを「0000」にリセットして、その後、入力データに応じてデコードデータの4ビットのうち1ビットだけを「1」にするという遷移を実現することができる。

【0047】

図8は、本発明の実施の形態におけるエンコーダ131乃至134の各々の動作の真理値表を示す図である。デコードデータが「1」を示すビット位置に応じて、出力データが決定される。ここで、出力データが定義されるのは、4ビットのデコードデータのうち1ビットだけが「1」となり、他のビットが「0」となっている場合、および、4ビットのデコードデータが全て「0」となっている場合である。これ以外の場合は未定義である。図6(b)の構成例では、この性質を利用して、4ビットのうち下位1ビットを参照することなくバイナリデータを生成している。

【0048】

図9は、本発明の実施の形態におけるx2・λ演算回路121の構成例を示す図である。また、図10は、本発明の実施の形態におけるx2・λ演算回路121の動作の真理値表である。デコード前の2進数データによりx2・λ演算の真理値表を作成すると、図10(a)に示すようになる。図7の関係を利用してデコードデータによるx2・λ演算の真理値表を作成すると、図10(b)に示すようになる。図9は図10(b)の関係を組合せ回路により実現したものである。

【0049】

このx2・λ演算回路121では、下位4ビットの出力については、インバータ211または否定論理和演算回路212と否定論理和演算回路213との2ゲート遅延により演算が行われる。また、上位4ビットの出力については、論理積−否定論理和演算回路214とインバータ215との2ゲート遅延により演算が行われる。したがって、上位および下位の演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、このx2・λ演算回路121に、2進数データでは定義されないデコードデータとして「0000_0000」が入力された場合、「0000_0000」を出力する。

【0050】

図11は、本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例を示す図である。また、図12は、本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例による動作の真理値表である。排他的論理和演算回路では、各ビットは独立して動作するため、半分の規模の排他的論理和演算回路を並列配置することにより回路を構成することができる。したがって、ここでは、デコード後の8ビット幅の排他的論理和演算回路122および124を、4ビット幅の排他的論理和演算回路の並列配置により実現する構成例について説明する。

【0051】

デコード前の2進数データにより排他的論理和演算の真理値表を作成すると、図12(a)に示すようになる。図7の関係を利用してデコードデータによる排他的論理和演算の真理値表を作成すると、図12(b)に示すようになる。図11は図12(b)の関係を組合せ回路により実現したものである。この排他的論理和演算回路では、論理積−否定論理和演算回路221とインバータ222との2ゲート遅延により演算が行われる。また、この排他的論理和演算回路の2つのデコード入力のうち、少なくとも一方のデコード入力に「0000」が入力された場合、入力信号は論理積−否定論理和演算回路221により受けているため、排他的論理和演算回路122または124は「0000」を出力する。

【0052】

図13は、本発明の第1の実施の形態における排他的論理和演算回路122および124の動作タイミング例を示す図である。本発明の第1の実施の形態では、1ラウンドの動作をプリチャージ相とエバリュエーション相の2相に分けて交互に行うようにフェーズ制御(PC:Phase Control)を行う。プリチャージ相では、出力は一旦「0000」にリセットされる。そして、エバリュエーション相では2つの入力が何れも「0000」以外になった後、さらに演算遅延が経過した後に排他的論理和演算結果が出力される。この排他的論理和演算結果は、デコードデータであるため、1ビットだけが「1」であり、それ以外のビットは「0」を示す。したがって、プリチャージ相でリセットされた「0000」から1ビットだけが、エバリュエーション相において「1」に遷移する。また、2つの入力の変化タイミングに遅延差がある場合、両方のデータが確定するまで「0000」が出力される。そして、両方のデータが確定した後に排他的論理和演算を実行して、演算結果に遷移する。このとき、中間値への遷移は起こらない。

【0053】

図14は、本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例を示す図である。また、図15は、本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例による動作の真理値表である。デコード前の2進数データによりGF((22)2)逆元演算の真理値表を作成すると、図15(a)に示すようになる。図7の関係を利用してデコードデータによるGF((22)2)逆元演算の真理値表を作成すると、図15(b)に示すようになる。図14は図15(b)の関係を組合せ回路により実現したものである。

【0054】

このGF((22)2)逆元演算回路125では、論理積−否定論理和演算回路251とインバータ252との2ゲート遅延により演算が行われる。したがって、このGF((22)2)逆元演算回路125における演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、このGF((22)2)逆元演算回路125に、2進数データでは定義されないデコードデータとして「0000_0000」が入力された場合、「0000_0000」を出力する。

【0055】

図16は、本発明の実施の形態における乗算回路123、126および127の構成例を示す図である。4ビットの2進数データ(デコードデータでは8ビット)を入力とする乗算回路では、入力の組み合わせは24×24=256通りになる。これをテーブルで構成すると、回路規模は他のテーブルを用いた4ビット演算回路(例えば逆元演算回路)の16倍となり、回路規模が各段に大きくなる。ここでは、回路規模を削減するため、部分体GF((22)2)での乗算器を用いて構成する例を示す。

【0056】

部分体GF((22)2)での乗算器は、図16に示すように4ビットのデコードデータの排他的論理和演算回路および4ビットのデコードデータの乗算回路により構成される。また、遅延時間を考慮して一部の回路の入力または出力は負論理になっている。すなわち、この回路は、否定排他的論理和(XNOR)演算回路231および232と、乗算回路233と、乗算φ演算回路234と、負論理乗算回路235と、インバータ236と、負論理入力排他的論理和演算回路237と、排他的論理和演算回路238とを備える。そして、演算器231乃至238は、デコードデータの演算をする演算器である。なお、排他的論理和演算回路238は図11に示した回路をそのまま利用することができる。また、インバータ236は、入力がデコードデータの場合、図17に示すように、配線のみで実現でき、乗算器の演算遅延に影響を与えない。

【0057】

図18は、本発明の実施の形態における否定排他的論理和演算回路231および232の構成例を示す図である。この回路は、図11の排他的論理和演算回路において最終段のインバータを取り除いたものになっている。したがって、この否定排他的論理和演算回路231および232では、論理積−否定論理和演算回路311による1ゲート遅延により演算が行われる。

【0058】

図19は、本発明の実施の形態における乗算回路233の構成例を示す図である。また、図20は、本発明の実施の形態における乗算回路233の構成例による動作の真理値表である。デコード前の2進数データにより乗算の真理値表を作成すると、図20(a)に示すようになる。図7の関係を利用してデコードデータによる乗算の真理値表を作成すると、図20(b)に示すようになる。図19は図20(b)の関係を組合せ回路により実現したものである。

【0059】

この乗算回路233では、最下位ビットd0を出力するために、否定論理和(NOR)演算回路331と否定論理和演算回路332との2ゲート遅延により演算が行われる。上位3ビットを出力するために、論理積−否定論理和演算回路333と、インバータ334との2ゲート遅延により演算が行われる。したがって、この乗算回路233における演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、この乗算回路233の2つの入力のうちの少なくとも一方の入力に、2進数データでは定義されないデコードデータとして「0000」が入力された場合、「0000」を出力する。

【0060】

図21は、本発明の実施の形態における乗算φ演算回路234の構成例を示す図である。また、図22は、本発明の実施の形態における乗算φ演算回路234の構成例による動作の真理値表である。デコード前の2進数データにより乗算φ演算の真理値表を作成すると、図22(a)に示すようになる。図7の関係を利用してデコードデータによる乗算の真理値表を作成すると、図22(b)に示すようになる。図21は図22(b)の関係を組合せ回路により実現したものである。

【0061】

この乗算φ演算回路234は、乗算結果にφ(=10)を乗じた値を出力するものであるが、φが固定値であるため、図19の乗算回路233の出力のビット順序を変更することにより実現可能である。したがって、この乗算φ演算回路234における演算結果は、乗算回路233と同様に、データにかかわらず等しく2ゲート遅延により出力される。また、この乗算φ演算回路234の2つの入力のうちの少なくとも一方の入力に、2進数データでは定義されないデコードデータとして「0000」が入力された場合、「0000」を出力する。

【0062】

図23は、本発明の実施の形態における負論理乗算回路235の構成例を示す図である。また、図24は、本発明の実施の形態における負論理乗算回路235の構成例による動作の真理値表である。この負論理乗算回路235は、入力および出力ともに負論理となっている。

【0063】

この負論理乗算回路235では、最下位ビット/d0を出力するために、否定論理積(NAND)演算回路351と否定論理積演算回路352との2ゲート遅延により演算が行われる。上位3ビットを出力するために、論理和−否定論理積演算回路353と、インバータ354との2ゲート遅延により演算が行われる。したがって、この負論理乗算回路235における演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、この負論理乗算回路235の少なくとも何れか一方の入力に、2進数データでは定義されないデコードデータ「0000」の負論理の値「1111」が入力された場合、負論理の値「1111」を出力する。

【0064】

図25は、本発明の実施の形態における負論理入力排他的論理和演算回路237の構成例を示す図である。この負論理入力排他的論理和演算回路237は、入力のみが負論理となっている。

【0065】

この負論理入力排他的論理和演算回路237では、各ビットを出力するために、論理和−否定論理積演算回路371の1ゲート遅延により演算が行われる。したがって、この負論理入力排他的論理和演算回路237における演算結果は、データにかかわらず等しく1ゲート遅延により出力される。また、この負論理入力排他的論理和演算回路237の何れか一方の入力に、2進数データでは定義されないデコードデータ「0000」の負論理の値「1111」が入力された場合、「0000」を出力する。

【0066】

これらの回路構成により、4ビット乗算回路123、126および127は、上位2ビットおよび下位2ビットともに、遅延時間は4ゲート遅延となる。また、4ビット乗算回路としてみた場合、入力も出力も正論理の動作となる。

【0067】

図26は、本発明の実施の形態における乗算回路123、126および127の動作タイミング例を示す図である。本発明の第1の実施の形態では、上述のように、1ラウンドの動作をプリチャージ相とエバリュエーション相の2相に分けて交互に行うようにフェーズ制御を行う。プリチャージ相では、出力は一旦「0000」にリセットされる。そして、エバリュエーション相では2つの入力が何れも「0000」以外になった後、さらに演算遅延が経過した後に乗算演算結果が出力される。この乗算演算結果は、デコードデータであるため、1ビットだけが「1」であり、それ以外のビットは「0」を示す。したがって、プリチャージ相でリセットされた「0000」から1ビットだけが、エバリュエーション相において「1」に遷移する。また、2つの入力の変化タイミングに遅延差がある場合、両方のデータが確定するまで「0000」が出力される。そして、両方のデータが確定した後に乗算動作を実行して、実行結果に遷移する。このとき、中間値への遷移は起こらず、したがって、中間値遷移による電流も発生しない。

【0068】

[逆元演算回路の遅延量]

図27は、本発明の実施の形態によるGF(((22)2)2)逆元演算回路100の構成例における演算データの信号経路を示す図である。

【0069】

上述のように、x2・λ演算回路121では2ゲート遅延を要し、排他的論理和演算回路122または124では2ゲート遅延を要し、乗算回路123、126または127では4ゲート遅延を要し、GF((22)2)逆元演算回路125では2ゲート遅延を要する。そして、これらの演算回路を通る演算データの信号経路は、経路A乃至Eの5つの信号経路が存在する。この中で、最も回路動作による遅延が大きいのは経路Bで、その遅延は14ゲート遅延ある。他の経路での、通過する演算回路による遅延の積算は、経路Aで10ゲート遅延、経路Cで12ゲート遅延、経路Dで4ゲート遅延、そして、経路Eで6ゲート遅延である。しかし、2つの入力データから演算結果を生成する「排他的論理和演算回路」および「乗算回路」は、2つの入力のうち少なくとも一方が固定値の場合は固定値を出力し、2つの入力が共にデコード値になってから演算動作を開始する。そして、その出力は、排他的論理和演算回路では2ゲート遅延後、乗算回路では4ゲート遅延後、固定値から演算結果に遷移する。5つの演算経路には、「排他的論理和演算回路」および「乗算回路」の2入力演算器の少なくとも1つが配置されている。そして、2入力演算器の2つの入力が有効値になるタイミングは異なる場合が多いが、2入力演算器は2つの入力の少なくとも一方が固定値の場合は固定値を出力し、両方の入力が有効値になってから所定時間経過後に出力は固定値から演算結果に遷移する。したがって、異なる遅延で入力された2つの経路の信号は、2入力演算器を通過した後は遅い方の経路の遅延タイミングに一致して以降の回路に入力される。例えば、GF((22)2)逆元演算回路125の出力となる経路A乃至Cは、全て最も回路遅延の積算の大きい経路Bの遅延と一致して乗算器126および127に入力される。経路Dのデータは、遅延なく乗算器126に入力されるが、他方の入力遅延が経路Bのタイミングとなるため、乗算器126を経た経路Dのタイミングも経路Bのタイミングと一致する。同様に、乗算器127を経た経路Eのタイミングも経路Bのタイミングと一致する。これらより、全ての演算経路においてデータが確定するのは、経路Bの遅延である14ゲート遅延後となる。

【0070】

このデコードデータによる逆元演算回路では、入力部にはデコーダ111乃至114のデコード回路が、出力部にはエンコーダ131乃至134がそれぞれ配置され、各々2ゲート遅延を要する。これは全ての信号パスに共通に付加される遅延時間で、結局、GF(((22)2)2)逆元演算回路100の演算遅延時間は、演算パスに関わらず18ゲート遅延となる。また、この演算回路では、2入力の演算回路の場合、両方の入力が確定してから演算が開始され、その演算器の演算遅延後に出力が固定値から演算結果に遷移する構成となっているため、各演算経路で中間値への遷移は起こらない。そして、各演算器の出力が固定値からデコード値に変化した時、変化する信号線は出力値にかかわらずデコード単位で1本であるため、DPA攻撃で鍵が取り出される可能性は低くなる。また、遅延時間が短縮されたことにより、動作周波数を高く設定することができる。

【0071】

[逆元演算回路の動作]

図28は、本発明の第1の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。この第1の実施の形態では、1ラウンドの動作をプリチャージ相とエバリュエーション相の2相に分けて交互に行うようにフェーズ制御の制御信号PCが変化する。プリチャージ相ではレジスタ930の出力が一旦「0000」にリセットされ、エバリュエーション相ではレジスタ930に保持された値が出力される。

【0072】

図2および図3により説明したように、レジスタ930からGF(((22)2)2)逆元演算回路100への入力はある程度の遅延を伴う。そこで、この遅延タイミングにあわせた制御信号PCdly(Phase Control delay)が利用される。この制御信号PCdlyは、制御信号PCと同じタイミングで立ち上がり、制御信号PCの立下り後、レジスタ930からGF(((22)2)2)逆元演算回路100までの回路動作による遅延時間に若干のマージンを見込んだ時間経過後に立ち下がる。すなわち、図6により説明したように、この制御信号PCdlyは、デコーダ111乃至114からデコードデータが演算部120へ出力されるタイミングを示す。この制御信号PCdlyはデコーダ111乃至114に入力され、制御信号PCdlyが「1」を示している間、デコードデータは入力データにかかわらず「0000」になる。一方、制御信号PCdlyが「0」を示している間、デコーダ111乃至114から入力データに応じたデコードデータが出力される。

【0073】

プリチャージ相では、クロックの立上りに同期して制御信号PCが「1」になり、レジスタからの信号は全て「0」に制御される。これが伝播して、各回路ブロックのノードは順次プリチャージレベルに遷移していく。そして、制御信号PCの立上りに同期して制御信号PCdlyも「1」に遷移し、デコード回路111乃至114からのデコード出力は全て「0000」に制御されて、GF(((22)2)2)のデコードデータによる逆元演算回路120へ入力される。これにより、4ゲート遅延後に乗算回路126のデコード出力が、6ゲート遅延後に乗算回路127のデコード出力がそれぞれ「0000_0000」となる。

【0074】

エバリュエーション相では、制御信号PCが「0」になり、レジスタ930に保持された値が出力されるようになる。これにより、各回路ブロックで演算が開始され、演算結果が次の回路に供給されていく。そして、所定時間経過後、GF(((22)2)2)逆元演算回路100に演算結果が供給される。制御信号PCdlyは、レジスタ930の出力からGF(((22)2)2)逆元演算回路100の入力までの演算時間に若干のマージンを見込んだ時間を発生させる遅延回路によって発生されるタイミングで「0」に遷移する。これにより、制御信号PCdlyが「0」になった時点で、GF(((22)2)2)逆元演算回路100の入力信号のデコードデータがGF(((22)2)2)逆元演算回路100に入力されて演算が実行される。そして、14ゲート遅延経過後、乗算器126および127の出力は各々ほぼ同時に「0000_0000」から演算結果に遷移する。

【0075】

このとき、演算結果の出力端に、DPA攻撃の対象となる演算の中間値が現れることはない。そして、エバリュエーション相で、GF(((22)2)2)逆元演算回路100の入力PHおよびPLならびに出力PH-1およびPL-1は、「0000_0000」からデコードデータに変化するだけである。すなわち、デコードデータは4本の信号線毎に1本だけ「1」に変化するだけであるため、配線容量に差異がないと仮定した場合、入力値および出力値に関係なく信号変化に伴う配線の充放電電流は一定である。そのため、GF(((22)2)2)逆元演算回路100に対するDPA攻撃は困難となる。また、GF(((22)2)2)逆元演算回路100の内部動作においても、各演算ブロックの出力信号は、プリチャージ相で設定された固定値「0000」からデコードデータに変化するだけで、変化は4本の信号線で1本だけとなる。したがって、GF(((22)2)2)逆元演算回路100の内部動作電流に対するDPA攻撃も困難となる。

【0076】

このように、本発明の第1の実施の形態では、デコードデータで動作する演算回路を用いて、プリチャージ相において各演算回路出力のデコードデータを「0000」にリセットし、エバリュエーション相で1ビットだけ「1」に変化させる。これにより、逆元演算時の中間値への遷移を抑止することができる。

【0077】

<2.第2の実施の形態>

上述の第1の実施の形態では1ラウンドの処理をプリチャージ相およびエバリュエーション相の2相に分けて実行したが、この第2の実施の形態では1ラウンドの処理を1クロックサイクルで実行することを想定する。

【0078】

本発明の第2の実施の形態におけるGF(((22)2)2)逆元演算回路の回路構成は、上述の第1の実施の形態において説明したものと同様である。したがって、ゲート遅延も第1の実施の形態の場合と同様であり、少ないゲート遅延による逆元演算が可能となる。ただし、制御信号PCdlyのタイミングが第1の実施の形態の場合とは異なる。

【0079】

[逆元演算回路の動作]

図29は、本発明の第2の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。この第2の実施の形態では、レジスタ930の出力からGF(((22)2)2)逆元演算回路100までの演算パスの遅延時間にマージンを加えた時間が経過した後に、制御信号PCdlyが「1」から「0」に変化するように制御される。すなわち、この制御信号PCdlyは、演算部120への入力データがデコーダ111乃至114から出力されるタイミングを示すことになる。

【0080】

クロックの立上りで、レジスタ930の出力は更新され、更新データによるラウンド演算が開始される。これと同時に制御信号PCdlyも「1」になり、GF(((22)2)2)逆元演算回路100の入力信号はデコーダ111乃至114によって「0000_0000」に制御され、この入力を受けてGF(((22)2)2)逆元演算回路100が動作する。そして、エンコーダ131乃至134の入力も「0000_0000」になる。このときの出力変化は、直前のデコードデータに関わらず、4本の信号線で1本だけ「0」に変化する。

【0081】

レジスタ930の出力からGF(((22)2)2)逆元演算回路100までの演算パスの遅延時間にマージンを加えた時間が経過した後、制御信号PCdlyは「0」となり、GF(((22)2)2)逆元演算回路100に到達している演算データがデコードされる。これにより、GF(((22)2)2)逆元演算回路100が動作を開始する。

【0082】

そして、14ゲート遅延後に乗算回路126および127の出力も「0000_0000」から演算結果に遷移する。このときの出力変化も、4本の信号線で1本だけ「1」に変化する。

【0083】

このように、本発明の第2の実施の形態によれば、レジスタ930の出力からの遅延時間にマージンを加えたタイミングで制御信号PCdlyを制御することにより、逆元演算時の中間値への遷移を抑止することができる。

【0084】

<3.変形例>

上述の実施の形態ではRijndealへの適用例について説明したが、数値演算でSbox値を生成する他の暗号にも本発明は適用可能である。例えば、AESと同様な構成をとる次世代暗号として、Camellia、Hierocrypt等にも適用することができる。

【0085】

このように、本発明の実施の形態によれば、GF(((22)2)2)逆元演算回路100において入力データを制御信号PCdlyにより固定値とデコード値の切り替えを制御し、逆元演算後に演算結果をエンコードすることにより、中間値への遷移を抑止することができる。また、逆元演算サイクル数が少ないため、中間値への遷移の確率およびその遷移時間も短く、中間値遷移による消費電流の増加を抑えることができる。そして、それと同時に、高い周波数での動作が可能となる。また、逆元演算回路において、2入力回路での入力遅延の差による中間値への遷移がほとんど発生しないため、その遷移に伴う電流に対するDPA攻撃が困難になる。また、逆元演算回路の入出力信号の変化は、固定値(例えば「0000_0000」)から演算結果のデコード値への変化またはその逆であるため、変化する信号線は例えば4本に付き常に1本であり、これは入出力データに依存しない。そのため、入出力信号の変化に対するDPA攻撃は困難になる。

【0086】

なお、本発明の実施の形態は本発明を具現化するための一例を示したものであり、本発明の実施の形態において明示したように、本発明の実施の形態における事項と、特許請求の範囲における発明特定事項とはそれぞれ対応関係を有する。同様に、特許請求の範囲における発明特定事項と、これと同一名称を付した本発明の実施の形態における事項とはそれぞれ対応関係を有する。ただし、本発明は実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において実施の形態に種々の変形を施すことにより具現化することができる。

【符号の説明】

【0087】

12 同形写像変換回路

16 逆同形写像・アフィン変換回路

22 逆アフィン変換・同形写像変換回路

26 逆同形写像変換回路

17、21 排他的論理和(XOR)演算回路

34、38 スイッチ

100 GF(((22)2)2)逆元演算回路

111〜114 デコーダ

120 デコードデータによる逆元演算部

121 x2・λ演算回路

122、124 排他的論理和(XOR)演算回路

123、126、127 乗算回路

125 GF((22)2)逆元演算回路

131〜134 エンコーダ

231、232 否定排他的論理和(XNOR)演算回路

233 乗算回路

234 乗算φ演算回路

235 負論理乗算回路

236 インバータ

237 負論理入力排他的論理和演算回路

238 排他的論理和(XOR)演算回路

910、920、930 レジスタ

【技術分野】

【0001】

本発明は、ガロア体の逆元演算回路に関し、特にメッセージの暗号化または復号化の際に利用されるガロア体の逆元演算回路に関する。

【背景技術】

【0002】

2001年、米国国立標準技術研究所(NIST)はRijndealを次期米国標準の128ビット共通鍵ブロック暗号AES(Advanced Encryption Standard)として選出した。AESの回路実装においては、演算速度の高速化や回路規模削減手法が学会等で報告されてきているが、それに加えて、低消費電力化やサイドチャンネル攻撃に対する耐性をもつ構成も近年報告されている。特に、従来の共通鍵ブロック暗号のDES(Data Encryption Standard)の置換えとして用いる場合、電池動作の組込み機器への搭載や、非接触動作するICカードへの搭載に際しては、消費電力に対する仕様は著しく制限される。

【0003】

AES暗号の入力データは128ビットであるが、8ビットを単位とした4×4のマトリクスとして定義され、演算処理は8ビット単位で行われる。暗号化の際の演算処理としては、SubBytes、ShiftRows、MixColumns、AddRoundKeyが行われる。SubBytesは、8ビットデータに対して逆元を計算し、アフィン変換を行うものである。ShiftRowsは、4×4のマトリクスの横方向(各行)に対して回転処理を行うものである。MixColumnsは、4×4のマトリクスの縦方向(各列)に対して処理を行うものである。AddRoundKeyは、ラウンド鍵との排他的論理和(XOR)演算を行うものである。この中で、回路規模および消費電力が最も大きいのがSubBytesである。このSubBytesでは、8ビット入力8ビット出力のテーブル(Sbox)が定義され、このテーブルに従った変換が行われる。このテーブルSboxは、16個必要とされる。

【0004】

Sboxの主要な構成方法としては、(1)テーブルをランダムロジックにて構成する方法、(2)二分決定グラフにより構成する方法、(3)合成体上で逆元演算を行う数値演算回路により構成する方法が考えられる。これらを比較すると、一般的にゲート規模は(1)、(2)、(3)の順に小さくなり、ゲート規模の観点からは(3)の逆元演算が有利である。(3)の逆元演算では、AESの仕様書に公開されているように、入力値を以下の既約多項式でのガロア体GF(28)の要素とみなして演算する。

x8+x4+x3+x+1

【0005】

Sboxの暗号化時の演算式は、暗号化演算時の8ビット入力を(b7 b6 b5 b4 b3 b2 b1 b0)、8ビット出力を(b7' b6' b5' b4' b3' b2' b1' b0')としたとき、出力は以下の演算式により生成される。

【数1】

【0006】

復号化演算時の8ビット入力を(b7' b6' b5' b4' b3' b2' b1' b0')、8ビット出力を(b7 b6 b5 b4 b3 b2 b1 b0)としたとき、出力は以下の演算式により生成される。

【数2】

【0007】

ガロア体上の演算では、基底が異なれば異なる演算になる。SubBytesで用いる既約多項式とは異なる体に合成体がある。ここで、合成体とは、素体から複数回の拡大により得られた体をいう。合成体上の乗算はさらに小さい合成体を用いて構成することができ、これにより、回路規模を削減することができる(例えば、非特許文献1参照。)。以下の既約多項式(式1)を使って得られる合成体GF(((22)2)2)上の逆元演算回路は、GF(28)と同形な体上の逆元演算回路として得られる。

GF(2)→GF(22): x2+x+1

GF(22)→GF((22)2): x2+x+φ ・・・(式1)

GF((22)2)→GF(((22)2)2): x2+x+λ

ただし、φ={10}2、λ={1100}2である。

【0008】

逆元の演算は、もとの体Aの元を同形写像δで合成体Bへマップし、合成体B上で逆元演算を実行した後、同形写像δ-1でもとの体Aへマップするという手順で行われる。合成体GF(((22)2)2)上の逆元演算において、入力データを(PH,PL)、出力データを(PH-1, PL-1)としたとき、2つのデータの積は次式のようになる。

(PH・x+PL)・(PH-1・x+PL-1)

=PH・PH-1・x2+(PH・PL-1+PL・PH-1)x+PL・PL-1

=PH・PH-1・(x+λ)+(PH・PL-1+PL・PH-1)・x+PL・PL-1

=(PH・PH-1+PH・PL-1+PL・PH-1)・x+PH・PH-1・λ+PL・PL-1

=1

これにより、次式が得られる。

PH・PH-1+PH・PL-1+PL・PH-1=0

PH・PH-1・λ+PL・PL-1=1

上式をPH-1およびPL-1について解くと、以下の式が得られる。

【数3】

【0009】

この合成体上での8ビットの逆元演算を用いた(3)の構成では、回路規模は、他の2つの構成に比べて半分以下になるが、消費電流に関してはゲート規模の比率ほどは小さくならない。原因としては、乗算回路や逆元演算回路の2つの入力の遅延差に起因するダイナミックハザードが考えられる。このダイナミックハザードは後段に行くほど累積され、余分な電力消費が増加する。8ビットの逆元演算回路の最終段には、2つの4ビット乗算器が配置されるが、逆元演算回路への信号入力を起点とした時、上位側の乗算器の一方の入力は遅延ゼロでデータが入力されるのに対して、他方の入力は十数乃至三十数ゲートの遅延でデータが入力される。この間、出力は一旦中間値に遷移してから演算結果に遷移する。そして、遅延はビット毎に異なり、さらに、各ビット値が「0」か「1」かにより遅延は異なってくる。また、この逆元演算回路の入力信号も、ビット毎に異なるタイミングで入ってくる。これらにより、最終的な値に到達するまでに、8ビットの逆元演算回路は様々な中間値に遷移し、その度に演算回路での貫通電流および負荷で充放電電流を消費する。そして、この充放電電流は、消費電流を測定して、それに統計処理を施すことにより鍵を取り出すDPA(Difference Power Analysis)攻撃の対象となる。このようなDPA攻撃への対策の1つとして、遅延調整のための遅延回路を配置して、2入力演算回路の信号遅延差を調整する方法が提案されている(例えば、非特許文献1参照。)。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】Sumio Morioka and Akashi Satoh : "An Optimized S-box circuit architecture for low power AES design", Workshop on Cryptographic Hardware and Embedded Systems 2002(CHES 2002),第172乃至186頁,2002年8月

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述のDPA攻撃に対処するために、遅延調整のための遅延回路を配置して、2入力演算回路の信号遅延差を調整する方法が提案されている。しかしながら、入力の遅延差は入力データ値によっても異なるため、すべてのデータに対して一様に消費電力を削減することは困難である。そして、削減できなかったハザード電流により、DPA攻撃に対する脅威は依然残ってしまう。

【0012】

本発明はこのような状況に鑑みてなされたものであり、ダイナミックハザードに起因する消費電力の増加を一様に抑えて、DPA攻撃に対して耐性のある回路構成を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明は、上記課題を解決するためになされたものであり、その第1の側面は、ガロア体の入力データよりもビット幅が広い所定の固定値を一旦出力した後に、上記入力データに応じて上記固定値から所定ビット数だけ異なる値を示すデコードデータを出力するデコーダと、上記デコードデータに対してガロア体の逆元演算を実行して上記デコードデータの逆元データを出力する演算部と、上記逆元データを上記入力データと等しいビット幅の出力データにエンコードするエンコーダとを具備するガロア体の逆元演算回路である。これにより、固定値から所定ビット数だけ異なるデコードデータを演算対象として、中間値への遷移を抑止するという作用をもたらす。

【0014】

また、この第1の側面において、上記デコーダは、制御信号に同期して上記固定値の出力を行うようにしてもよい。これにより、入力データの各ビットの遷移にばらつきがある場合であっても一斉に演算を駆動するという作用をもたらす。

【0015】

また、この第1の側面において、上記制御信号は、上記入力データが上記デコーダに入力されるタイミングを示すものであってもよい。これにより、デコーダに入力されるタイミングに合わせて一斉に演算を駆動するという作用をもたらす。

【0016】

また、この第1の側面において、上記演算部は、上記デコーダから上記固定値が出力されている間は上記固定値を出力するようにしてもよい。これにより、演算結果の遷移する期間を制限するという作用をもたらす。

【0017】

また、本発明の第2の側面は、ガロア体の8ビットの入力データを2ビットずつに区切った4組の部分データに対してそれぞれ4ビット幅の固定値を一旦出力した後に、上記部分データに応じて上記固定値から1ビットだけ異なる4ビット幅のデコードデータをそれぞれ出力する4つのデコーダと、上記4組のデコードデータからなる16ビットデータに対して逆元演算を実行して上記16ビットデータの逆元データを出力する演算部と、上記逆元データを4ビットずつに区切ってそれぞれ2ビット幅の出力データにエンコードする4つのエンコーダとを具備するガロア体の逆元演算回路である。これにより、固定値から4ビット中1ビットだけ異なるデコードデータを演算対象として、中間値への遷移を抑止するという作用をもたらす。

【0018】

また、この第2の側面において、上記4つのデコーダは、共通の制御信号に同期して上記固定値の出力を行うようにしてもよい。これにより、8ビットの入力データの各ビットの遷移にばらつきがある場合であっても一斉に演算を駆動するという作用をもたらす。

【0019】

また、この第2の側面において、上記制御信号は、上記入力データが上記デコーダに入力されるタイミングを示すものであってもよい。これにより、デコーダに入力されるタイミングに合わせて一斉に演算を駆動するという作用をもたらす。

【0020】

また、この第2の側面において、上記演算部は、上記4つのデコーダの全てが上記固定値を出力している間は4組の上記固定値からなる16ビット幅のデータを出力するようにしてもよい。これにより、演算結果の遷移する期間を制限するという作用をもたらす。

【発明の効果】

【0021】

本発明によれば、ダイナミックハザードに起因する消費電力の増加を一様に抑えて、DPA攻撃を困難にすることができるという優れた効果を奏し得る。

【図面の簡単な説明】

【0022】

【図1】本発明において想定する暗号化および復号化の処理手順例を示す図である。

【図2】本発明において想定する暗号化および復号化の共通化した処理手順例を示す図である。

【図3】本発明において想定するSubBytes/Inv_SubBytes(931)の処理内容を示す図である。

【図4】既約多項式を用いた逆元演算回路の基本原理を示す図である。

【図5】本発明の実施の形態におけるGF(((22)2)2)逆元演算回路100の構成例を示す図である。

【図6】本発明の実施の形態におけるデコーダ111乃至114およびエンコーダ131乃至134の構成例を示す図である。

【図7】本発明の実施の形態におけるデコーダ111乃至114の各々の動作の真理値表を示す図である。

【図8】本発明の実施の形態におけるエンコーダ131乃至134の各々の動作の真理値表を示す図である。

【図9】本発明の実施の形態におけるx2・λ演算回路121の構成例を示す図である。

【図10】本発明の実施の形態におけるx2・λ演算回路121の動作の真理値表である。

【図11】本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例を示す図である。

【図12】本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例による動作の真理値表である。

【図13】本発明の第1の実施の形態における排他的論理和演算回路122および124の動作タイミング例を示す図である。

【図14】本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例を示す図である。

【図15】本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例による動作の真理値表である。

【図16】本発明の実施の形態における乗算回路123、126および127の構成例を示す図である。

【図17】本発明の実施の形態におけるインバータ236の構成例を示す図である。

【図18】本発明の実施の形態における否定排他的論理和演算回路231および232の構成例を示す図である。

【図19】本発明の実施の形態における乗算回路233の構成例を示す図である。

【図20】本発明の実施の形態における乗算回路233の構成例による動作の真理値表である。

【図21】本発明の実施の形態における乗算φ演算回路234の構成例を示す図である。

【図22】本発明の実施の形態における乗算φ演算回路234の構成例による動作の真理値表である。

【図23】本発明の実施の形態における負論理乗算回路235の構成例を示す図である。

【図24】本発明の実施の形態における負論理乗算回路235の構成例による動作の真理値表である。

【図25】本発明の実施の形態における負論理入力排他的論理和演算回路237の構成例を示す図である。

【図26】本発明の実施の形態における乗算回路123、126および127の動作タイミング例を示す図である。

【図27】本発明の実施の形態によるGF(((22)2)2)逆元演算回路100の構成例における遅延量を示す図である。

【図28】本発明の第1の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。

【図29】本発明の第2の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。

【発明を実施するための形態】

【0023】

以下、本発明を実施するための形態(以下、実施の形態と称する)について説明する。説明は以下の順序により行う。

1.第1の実施の形態(1ラウンドの処理を2相に分けて実行する例)

2.第2の実施の形態(1ラウンドの処理を1クロックサイクルで実行する例)

3.変形例

【0024】

<1.第1の実施の形態>

[暗号化装置または復号化装置の構成]

図1は、本発明において想定する暗号化および復号化の処理手順例を示す図である。図1(a)は、メッセージを暗号化するための処理手順であり、SubBytes(911)、ShiftRows(912)、MixColumns(915)、AddRoundKey(916)の各手順を含む。AES暗号の入力データは128ビットであるが、8ビットを単位とした4×4のマトリクスとして定義され、演算処理は8ビット単位で行われる。この128ビットの入力データは、ラウンド演算の開始前(Rd0)に入力され、AddRoundKey(916)を経てレジスタ910に保持される。

【0025】

SubBytes(911)は、8ビットデータに対して逆元を計算し、アフィン変換を行うものである。ShiftRows(912)は、4×4のマトリクスの横方向(各行)に対して回転処理を行うものである。MixColumns(915)は、4×4のマトリクスの縦方向(各列)に対して演算処理を行うものである。AddRoundKey(916)は、ラウンド鍵(919)との排他的論理和(XOR)演算を行うものである。レジスタ910には、各手順を1ラウンド行う度に(Rd1乃至10)中間値が更新される。

【0026】

この暗号化処理では、各手順を10ラウンド繰り返した後にレジスタ910に保持された値が暗号として出力される。なお、最終ラウンド(Rd10)では、MixColumns(915)の処理は行われない。

【0027】

図1(b)は、暗号化されたメッセージを復号化するための処理手順であり、Inv_SubBytes(921)、Inv_ShiftRows(922)、AddRoundKey(923)、Inv_MixColumns(925)の各手順を含む。暗号化されたメッセージは、ラウンド演算の開始前(Rd10)に入力され、AddRoundKey(923)を経てレジスタ920に保持される。

【0028】

Inv_SubBytes(921)は、SubBytes(911)の逆の処理を行うものである。Inv_ShiftRows(922)は、ShiftRows(912)の逆の処理を行うものである。AddRoundKey(923)は、ラウンド鍵(928)との排他的論理和演算を行うものである。Inv_MixColumns(925)は、MixColumns(915)の逆の処理を行うものである。レジスタ920には、各手順を1ラウンド行う度に(Rd9乃至0)中間値が更新される。

【0029】

この復号化処理では、各手順を10ラウンド繰り返した後にレジスタ920に保持された値が復号化されたメッセージとして出力される。なお、最終ラウンド(Rd0)では、Inv_MixColumns(925)の処理は行われない。

【0030】

ここで、SubBytes(911)およびShiftRows(912)とInv_SubBytes(921)およびInv_ShiftRows(922)とは対になる処理であるため、暗号化処理と復号化処理との間で共通化することができる。MixColumns(915)とInv_MixColumns(925)との間も同様である。そこで、次のように両者を共通化した処理手順として実現した場合のイメージを示す。

【0031】

図2は、本発明において想定する暗号化および復号化の共通化した処理手順例を示す図である。SubBytes/Inv_SubBytes(931)は、SubBytes(911)とInv_SubBytes(921)とを共通化したものである。ShiftRows/Inv_ShiftRows(932)は、ShiftRows(912)とInv_ShiftRows(922)とを共通化したものである。AddRoundKey(933)は、AddRoundKey(923)と同様に、ラウンド鍵(928)との排他的論理和演算を行うものである。選択手順934は、暗号化時にAddRoundKey(933)を経ない値を選択し、復号化時にAddRoundKey(933)の出力を選択するものである。MixColumns/Inv_MixColumns(935)は、MixColumns(915)とInv_MixColumns(925)とを共通化したものである。AddRoundKey(936)は、AddRoundKey(916)と同様に、ラウンド鍵(919)との排他的論理和演算を行うものである。選択手順937は、暗号化時にAddRoundKey(936)の出力を選択し、復号化時にAddRoundKey(936)を経ない値を選択するものである。レジスタ930は、レジスタ910とレジスタ920とを共通化したものであり、暗号化または復号化の中間値を保持するものである。

【0032】

図3は、本発明において想定するSubBytes/Inv_SubBytes(931)の処理内容を示す図である。このSubBytes/Inv_SubBytes(931)を、以下ではSboxと呼称する。上述のレジスタ930の出力は、別の演算回路に入力されることなく、このSboxに入力される。このSboxは、暗号化時と復号化時とで共通化されているため、両者を切り換えるスイッチ34および38を備えている。

【0033】

Sboxにおいて、暗号化時には、同形写像変換回路12において写像変換δを行い、逆元演算回路100においてGF(((22)2)2)上の逆元演算を行う。そして、逆同形写像変換・アフィン変換回路16において逆写像変換δ-1とアフィン変換を行った後に排他的論理和(XOR)演算回路17により排他的論理和演算を行う。

【0034】

一方、復号化時には、排他的論理和演算回路21により排他的論理和演算を行った後に逆アフィン変換・同形写像回路22において逆アフィン変換と写像変換δを行う。そして、逆元演算回路100においてGF(((22)2)2)上の逆元演算を行う。その後、逆同形写像回路26において逆写像変換δ-1を行う。

【0035】

[逆元演算回路の構成]

図4は、既約多項式を用いた逆元演算回路の基本原理を示す図である。図4(a)は、8ビットのGF(((22)2)2)逆元演算回路である。ここでは、入力データの上位4ビットをPH、下位4ビットをPLにより表し、出力データの上位4ビットをPH-1、下位4ビットをPL-1により表している。逆元演算回路は階層的な構造を有し、合成体GF(((22)2)2)上の逆元演算は、以下の部分体GF((22)2)の演算回路を組み合わせることにより実現される。すなわち、このGF(((22)2)2)逆元演算回路は、x2・λ演算回路811と、排他的論理和演算回路812および814と、乗算回路813、816および817と、逆元演算回路820とを備える。

【0036】

図4(b)は、4ビットのGF((22)2)逆元演算回路820である。合成体GF((22)2)上の逆元演算は、以下の部分体GF(22)の演算を組み合わせることにより実現される。すなわち、このGF((22)2)逆元演算回路820は、x2・φ演算回路821と、排他的論理和演算回路822および824と、乗算回路823、826および827と、逆元演算回路830とを備える。

【0037】

上述のとおり、この逆元演算回路の基本原理をそのまま利用した場合、ダイナミックハザードによる中間値への遷移のため、DPA攻撃の対象とされるおそれが生じる。そこで、本発明の実施の形態では、逆元演算回路の前段にデコーダを配置して、逆元演算回路をデコードデータによるテーブル回路で構成することにより、演算によるゲート遅延を削減する。そして、それとともに、演算回路の入力が全て確定するまで固定値を出力する構成を採ることにより、中間値への遷移を抑止するように制御を行う。

【0038】

図5は、本発明の実施の形態におけるGF(((22)2)2)逆元演算回路100の構成例を示す図である。このGF(((22)2)2)逆元演算回路100は、4つのデコーダ111乃至114と、演算部120と、4つのエンコーダ131乃至134とを備えている。

【0039】

デコーダ111乃至114は、8ビットの入力データのうちそれぞれ2ビットずつをデコードして、それぞれ4ビットのデコードデータを出力するものである。デコーダ111乃至114は、共通する制御信号PCdly(Phase Control delay)によって動作タイミングを制御される。なお、ここでは4つのデコーダ111乃至114を用いた例について説明するが、これらは一体化したものでもよく、また、任意の数に分割したものでもよい。

【0040】

演算部120は、デコーダ111乃至114から出力された16ビットのデコードデータに対してGF(((22)2)2)逆元演算を行うものである。部分体で使用する規約多項式が決まっている場合、合成体上での演算で、1つまたは2つの4ビット入力が決まれば、出力の4ビットは自動的に決まる。そして、ここでは、2ビット単位でデコードしたデータで演算がなされるものとしている。この演算部120は、図4(a)の基本原理に準じた構成を備えており、x2・λ演算回路121と、排他的論理和演算回路122および124と、乗算回路123、126および127と、GF((22)2)逆元演算回路125とを備える。各回路の構成についてはさらに後述する。

【0041】

エンコーダ131乃至134は、演算部120から出力された16ビットのデコードデータのうちそれぞれ4ビットずつをエンコードして、それぞれ2ビットのバイナリデータを出力するものである。なお、ここでは4つのエンコーダ131乃至134を用いた例について説明するが、これらは一体化したものでもよく、また、任意の数に分割したものでもよい。

【0042】

図6は、本発明の実施の形態におけるデコーダ111乃至114およびエンコーダ131乃至134の構成例を示す図である。

【0043】

図6(a)は、デコーダ111乃至114の構成例である。ここでは、デコーダ111の内部を代表として示しているが、デコーダ112乃至114についても同様の構成を備える。デコーダ111は、8ビットの入力データのうち上位の2ビットb6およびb7を入力として、b6およびb7ならびにこれらの反転信号を組み合わせて4ビットのデコードデータを生成する。このデコーダ111は、インバータと否定論理和(NOR)演算回路の2ゲート遅延を有する。また、否定論理和演算回路には制御信号PCdlyが入力され、この制御信号PCdlyが「1」を示す間は、デコードデータは所定の固定値になる。本発明の実施の形態では、所定の固定値としてデコードデータを全ビット「0」にすることを想定している。

【0044】

図6(b)は、エンコーダ131乃至134の構成例である。ここでは、エンコーダ131の内部を代表として示しているが、エンコーダ132乃至134についても同様の構成を備える。エンコーダ131は、16ビットのデコードデータのうち上位の4ビットを入力として、d0乃至d3を組み合わせて2ビットのエンコードデータを生成する。このエンコーダ131は、否定論理和演算回路とインバータの2ゲート遅延を有する。

【0045】

図7は、本発明の実施の形態におけるデコーダ111乃至114の各々の動作の真理値表を示す図である。上述のようにデコーダ111乃至114の各々には2ビットの入力データと制御信号PCdlyが入力される。制御信号PCdlyが「1」の場合、入力データにかかわらず、デコードデータは「0000」になる。制御信号PCdlyが「0」の場合、入力データに応じて、4ビットのデコードデータのうち1ビットだけが「1」となり、他のビットは「0」になる。

【0046】

これにより、制御信号PCdlyのタイミングに合わせてデコードデータを「0000」にリセットして、その後、入力データに応じてデコードデータの4ビットのうち1ビットだけを「1」にするという遷移を実現することができる。

【0047】

図8は、本発明の実施の形態におけるエンコーダ131乃至134の各々の動作の真理値表を示す図である。デコードデータが「1」を示すビット位置に応じて、出力データが決定される。ここで、出力データが定義されるのは、4ビットのデコードデータのうち1ビットだけが「1」となり、他のビットが「0」となっている場合、および、4ビットのデコードデータが全て「0」となっている場合である。これ以外の場合は未定義である。図6(b)の構成例では、この性質を利用して、4ビットのうち下位1ビットを参照することなくバイナリデータを生成している。

【0048】

図9は、本発明の実施の形態におけるx2・λ演算回路121の構成例を示す図である。また、図10は、本発明の実施の形態におけるx2・λ演算回路121の動作の真理値表である。デコード前の2進数データによりx2・λ演算の真理値表を作成すると、図10(a)に示すようになる。図7の関係を利用してデコードデータによるx2・λ演算の真理値表を作成すると、図10(b)に示すようになる。図9は図10(b)の関係を組合せ回路により実現したものである。

【0049】

このx2・λ演算回路121では、下位4ビットの出力については、インバータ211または否定論理和演算回路212と否定論理和演算回路213との2ゲート遅延により演算が行われる。また、上位4ビットの出力については、論理積−否定論理和演算回路214とインバータ215との2ゲート遅延により演算が行われる。したがって、上位および下位の演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、このx2・λ演算回路121に、2進数データでは定義されないデコードデータとして「0000_0000」が入力された場合、「0000_0000」を出力する。

【0050】

図11は、本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例を示す図である。また、図12は、本発明の実施の形態における排他的論理和演算回路122および124の半分の構成例による動作の真理値表である。排他的論理和演算回路では、各ビットは独立して動作するため、半分の規模の排他的論理和演算回路を並列配置することにより回路を構成することができる。したがって、ここでは、デコード後の8ビット幅の排他的論理和演算回路122および124を、4ビット幅の排他的論理和演算回路の並列配置により実現する構成例について説明する。

【0051】

デコード前の2進数データにより排他的論理和演算の真理値表を作成すると、図12(a)に示すようになる。図7の関係を利用してデコードデータによる排他的論理和演算の真理値表を作成すると、図12(b)に示すようになる。図11は図12(b)の関係を組合せ回路により実現したものである。この排他的論理和演算回路では、論理積−否定論理和演算回路221とインバータ222との2ゲート遅延により演算が行われる。また、この排他的論理和演算回路の2つのデコード入力のうち、少なくとも一方のデコード入力に「0000」が入力された場合、入力信号は論理積−否定論理和演算回路221により受けているため、排他的論理和演算回路122または124は「0000」を出力する。

【0052】

図13は、本発明の第1の実施の形態における排他的論理和演算回路122および124の動作タイミング例を示す図である。本発明の第1の実施の形態では、1ラウンドの動作をプリチャージ相とエバリュエーション相の2相に分けて交互に行うようにフェーズ制御(PC:Phase Control)を行う。プリチャージ相では、出力は一旦「0000」にリセットされる。そして、エバリュエーション相では2つの入力が何れも「0000」以外になった後、さらに演算遅延が経過した後に排他的論理和演算結果が出力される。この排他的論理和演算結果は、デコードデータであるため、1ビットだけが「1」であり、それ以外のビットは「0」を示す。したがって、プリチャージ相でリセットされた「0000」から1ビットだけが、エバリュエーション相において「1」に遷移する。また、2つの入力の変化タイミングに遅延差がある場合、両方のデータが確定するまで「0000」が出力される。そして、両方のデータが確定した後に排他的論理和演算を実行して、演算結果に遷移する。このとき、中間値への遷移は起こらない。

【0053】

図14は、本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例を示す図である。また、図15は、本発明の実施の形態におけるGF((22)2)逆元演算回路125の構成例による動作の真理値表である。デコード前の2進数データによりGF((22)2)逆元演算の真理値表を作成すると、図15(a)に示すようになる。図7の関係を利用してデコードデータによるGF((22)2)逆元演算の真理値表を作成すると、図15(b)に示すようになる。図14は図15(b)の関係を組合せ回路により実現したものである。

【0054】

このGF((22)2)逆元演算回路125では、論理積−否定論理和演算回路251とインバータ252との2ゲート遅延により演算が行われる。したがって、このGF((22)2)逆元演算回路125における演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、このGF((22)2)逆元演算回路125に、2進数データでは定義されないデコードデータとして「0000_0000」が入力された場合、「0000_0000」を出力する。

【0055】

図16は、本発明の実施の形態における乗算回路123、126および127の構成例を示す図である。4ビットの2進数データ(デコードデータでは8ビット)を入力とする乗算回路では、入力の組み合わせは24×24=256通りになる。これをテーブルで構成すると、回路規模は他のテーブルを用いた4ビット演算回路(例えば逆元演算回路)の16倍となり、回路規模が各段に大きくなる。ここでは、回路規模を削減するため、部分体GF((22)2)での乗算器を用いて構成する例を示す。

【0056】

部分体GF((22)2)での乗算器は、図16に示すように4ビットのデコードデータの排他的論理和演算回路および4ビットのデコードデータの乗算回路により構成される。また、遅延時間を考慮して一部の回路の入力または出力は負論理になっている。すなわち、この回路は、否定排他的論理和(XNOR)演算回路231および232と、乗算回路233と、乗算φ演算回路234と、負論理乗算回路235と、インバータ236と、負論理入力排他的論理和演算回路237と、排他的論理和演算回路238とを備える。そして、演算器231乃至238は、デコードデータの演算をする演算器である。なお、排他的論理和演算回路238は図11に示した回路をそのまま利用することができる。また、インバータ236は、入力がデコードデータの場合、図17に示すように、配線のみで実現でき、乗算器の演算遅延に影響を与えない。

【0057】

図18は、本発明の実施の形態における否定排他的論理和演算回路231および232の構成例を示す図である。この回路は、図11の排他的論理和演算回路において最終段のインバータを取り除いたものになっている。したがって、この否定排他的論理和演算回路231および232では、論理積−否定論理和演算回路311による1ゲート遅延により演算が行われる。

【0058】

図19は、本発明の実施の形態における乗算回路233の構成例を示す図である。また、図20は、本発明の実施の形態における乗算回路233の構成例による動作の真理値表である。デコード前の2進数データにより乗算の真理値表を作成すると、図20(a)に示すようになる。図7の関係を利用してデコードデータによる乗算の真理値表を作成すると、図20(b)に示すようになる。図19は図20(b)の関係を組合せ回路により実現したものである。

【0059】

この乗算回路233では、最下位ビットd0を出力するために、否定論理和(NOR)演算回路331と否定論理和演算回路332との2ゲート遅延により演算が行われる。上位3ビットを出力するために、論理積−否定論理和演算回路333と、インバータ334との2ゲート遅延により演算が行われる。したがって、この乗算回路233における演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、この乗算回路233の2つの入力のうちの少なくとも一方の入力に、2進数データでは定義されないデコードデータとして「0000」が入力された場合、「0000」を出力する。

【0060】

図21は、本発明の実施の形態における乗算φ演算回路234の構成例を示す図である。また、図22は、本発明の実施の形態における乗算φ演算回路234の構成例による動作の真理値表である。デコード前の2進数データにより乗算φ演算の真理値表を作成すると、図22(a)に示すようになる。図7の関係を利用してデコードデータによる乗算の真理値表を作成すると、図22(b)に示すようになる。図21は図22(b)の関係を組合せ回路により実現したものである。

【0061】

この乗算φ演算回路234は、乗算結果にφ(=10)を乗じた値を出力するものであるが、φが固定値であるため、図19の乗算回路233の出力のビット順序を変更することにより実現可能である。したがって、この乗算φ演算回路234における演算結果は、乗算回路233と同様に、データにかかわらず等しく2ゲート遅延により出力される。また、この乗算φ演算回路234の2つの入力のうちの少なくとも一方の入力に、2進数データでは定義されないデコードデータとして「0000」が入力された場合、「0000」を出力する。

【0062】

図23は、本発明の実施の形態における負論理乗算回路235の構成例を示す図である。また、図24は、本発明の実施の形態における負論理乗算回路235の構成例による動作の真理値表である。この負論理乗算回路235は、入力および出力ともに負論理となっている。

【0063】

この負論理乗算回路235では、最下位ビット/d0を出力するために、否定論理積(NAND)演算回路351と否定論理積演算回路352との2ゲート遅延により演算が行われる。上位3ビットを出力するために、論理和−否定論理積演算回路353と、インバータ354との2ゲート遅延により演算が行われる。したがって、この負論理乗算回路235における演算結果は、データにかかわらず等しく2ゲート遅延により出力される。また、この負論理乗算回路235の少なくとも何れか一方の入力に、2進数データでは定義されないデコードデータ「0000」の負論理の値「1111」が入力された場合、負論理の値「1111」を出力する。

【0064】

図25は、本発明の実施の形態における負論理入力排他的論理和演算回路237の構成例を示す図である。この負論理入力排他的論理和演算回路237は、入力のみが負論理となっている。

【0065】

この負論理入力排他的論理和演算回路237では、各ビットを出力するために、論理和−否定論理積演算回路371の1ゲート遅延により演算が行われる。したがって、この負論理入力排他的論理和演算回路237における演算結果は、データにかかわらず等しく1ゲート遅延により出力される。また、この負論理入力排他的論理和演算回路237の何れか一方の入力に、2進数データでは定義されないデコードデータ「0000」の負論理の値「1111」が入力された場合、「0000」を出力する。

【0066】

これらの回路構成により、4ビット乗算回路123、126および127は、上位2ビットおよび下位2ビットともに、遅延時間は4ゲート遅延となる。また、4ビット乗算回路としてみた場合、入力も出力も正論理の動作となる。

【0067】

図26は、本発明の実施の形態における乗算回路123、126および127の動作タイミング例を示す図である。本発明の第1の実施の形態では、上述のように、1ラウンドの動作をプリチャージ相とエバリュエーション相の2相に分けて交互に行うようにフェーズ制御を行う。プリチャージ相では、出力は一旦「0000」にリセットされる。そして、エバリュエーション相では2つの入力が何れも「0000」以外になった後、さらに演算遅延が経過した後に乗算演算結果が出力される。この乗算演算結果は、デコードデータであるため、1ビットだけが「1」であり、それ以外のビットは「0」を示す。したがって、プリチャージ相でリセットされた「0000」から1ビットだけが、エバリュエーション相において「1」に遷移する。また、2つの入力の変化タイミングに遅延差がある場合、両方のデータが確定するまで「0000」が出力される。そして、両方のデータが確定した後に乗算動作を実行して、実行結果に遷移する。このとき、中間値への遷移は起こらず、したがって、中間値遷移による電流も発生しない。

【0068】

[逆元演算回路の遅延量]

図27は、本発明の実施の形態によるGF(((22)2)2)逆元演算回路100の構成例における演算データの信号経路を示す図である。

【0069】

上述のように、x2・λ演算回路121では2ゲート遅延を要し、排他的論理和演算回路122または124では2ゲート遅延を要し、乗算回路123、126または127では4ゲート遅延を要し、GF((22)2)逆元演算回路125では2ゲート遅延を要する。そして、これらの演算回路を通る演算データの信号経路は、経路A乃至Eの5つの信号経路が存在する。この中で、最も回路動作による遅延が大きいのは経路Bで、その遅延は14ゲート遅延ある。他の経路での、通過する演算回路による遅延の積算は、経路Aで10ゲート遅延、経路Cで12ゲート遅延、経路Dで4ゲート遅延、そして、経路Eで6ゲート遅延である。しかし、2つの入力データから演算結果を生成する「排他的論理和演算回路」および「乗算回路」は、2つの入力のうち少なくとも一方が固定値の場合は固定値を出力し、2つの入力が共にデコード値になってから演算動作を開始する。そして、その出力は、排他的論理和演算回路では2ゲート遅延後、乗算回路では4ゲート遅延後、固定値から演算結果に遷移する。5つの演算経路には、「排他的論理和演算回路」および「乗算回路」の2入力演算器の少なくとも1つが配置されている。そして、2入力演算器の2つの入力が有効値になるタイミングは異なる場合が多いが、2入力演算器は2つの入力の少なくとも一方が固定値の場合は固定値を出力し、両方の入力が有効値になってから所定時間経過後に出力は固定値から演算結果に遷移する。したがって、異なる遅延で入力された2つの経路の信号は、2入力演算器を通過した後は遅い方の経路の遅延タイミングに一致して以降の回路に入力される。例えば、GF((22)2)逆元演算回路125の出力となる経路A乃至Cは、全て最も回路遅延の積算の大きい経路Bの遅延と一致して乗算器126および127に入力される。経路Dのデータは、遅延なく乗算器126に入力されるが、他方の入力遅延が経路Bのタイミングとなるため、乗算器126を経た経路Dのタイミングも経路Bのタイミングと一致する。同様に、乗算器127を経た経路Eのタイミングも経路Bのタイミングと一致する。これらより、全ての演算経路においてデータが確定するのは、経路Bの遅延である14ゲート遅延後となる。

【0070】

このデコードデータによる逆元演算回路では、入力部にはデコーダ111乃至114のデコード回路が、出力部にはエンコーダ131乃至134がそれぞれ配置され、各々2ゲート遅延を要する。これは全ての信号パスに共通に付加される遅延時間で、結局、GF(((22)2)2)逆元演算回路100の演算遅延時間は、演算パスに関わらず18ゲート遅延となる。また、この演算回路では、2入力の演算回路の場合、両方の入力が確定してから演算が開始され、その演算器の演算遅延後に出力が固定値から演算結果に遷移する構成となっているため、各演算経路で中間値への遷移は起こらない。そして、各演算器の出力が固定値からデコード値に変化した時、変化する信号線は出力値にかかわらずデコード単位で1本であるため、DPA攻撃で鍵が取り出される可能性は低くなる。また、遅延時間が短縮されたことにより、動作周波数を高く設定することができる。

【0071】

[逆元演算回路の動作]

図28は、本発明の第1の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。この第1の実施の形態では、1ラウンドの動作をプリチャージ相とエバリュエーション相の2相に分けて交互に行うようにフェーズ制御の制御信号PCが変化する。プリチャージ相ではレジスタ930の出力が一旦「0000」にリセットされ、エバリュエーション相ではレジスタ930に保持された値が出力される。

【0072】

図2および図3により説明したように、レジスタ930からGF(((22)2)2)逆元演算回路100への入力はある程度の遅延を伴う。そこで、この遅延タイミングにあわせた制御信号PCdly(Phase Control delay)が利用される。この制御信号PCdlyは、制御信号PCと同じタイミングで立ち上がり、制御信号PCの立下り後、レジスタ930からGF(((22)2)2)逆元演算回路100までの回路動作による遅延時間に若干のマージンを見込んだ時間経過後に立ち下がる。すなわち、図6により説明したように、この制御信号PCdlyは、デコーダ111乃至114からデコードデータが演算部120へ出力されるタイミングを示す。この制御信号PCdlyはデコーダ111乃至114に入力され、制御信号PCdlyが「1」を示している間、デコードデータは入力データにかかわらず「0000」になる。一方、制御信号PCdlyが「0」を示している間、デコーダ111乃至114から入力データに応じたデコードデータが出力される。

【0073】

プリチャージ相では、クロックの立上りに同期して制御信号PCが「1」になり、レジスタからの信号は全て「0」に制御される。これが伝播して、各回路ブロックのノードは順次プリチャージレベルに遷移していく。そして、制御信号PCの立上りに同期して制御信号PCdlyも「1」に遷移し、デコード回路111乃至114からのデコード出力は全て「0000」に制御されて、GF(((22)2)2)のデコードデータによる逆元演算回路120へ入力される。これにより、4ゲート遅延後に乗算回路126のデコード出力が、6ゲート遅延後に乗算回路127のデコード出力がそれぞれ「0000_0000」となる。

【0074】

エバリュエーション相では、制御信号PCが「0」になり、レジスタ930に保持された値が出力されるようになる。これにより、各回路ブロックで演算が開始され、演算結果が次の回路に供給されていく。そして、所定時間経過後、GF(((22)2)2)逆元演算回路100に演算結果が供給される。制御信号PCdlyは、レジスタ930の出力からGF(((22)2)2)逆元演算回路100の入力までの演算時間に若干のマージンを見込んだ時間を発生させる遅延回路によって発生されるタイミングで「0」に遷移する。これにより、制御信号PCdlyが「0」になった時点で、GF(((22)2)2)逆元演算回路100の入力信号のデコードデータがGF(((22)2)2)逆元演算回路100に入力されて演算が実行される。そして、14ゲート遅延経過後、乗算器126および127の出力は各々ほぼ同時に「0000_0000」から演算結果に遷移する。

【0075】

このとき、演算結果の出力端に、DPA攻撃の対象となる演算の中間値が現れることはない。そして、エバリュエーション相で、GF(((22)2)2)逆元演算回路100の入力PHおよびPLならびに出力PH-1およびPL-1は、「0000_0000」からデコードデータに変化するだけである。すなわち、デコードデータは4本の信号線毎に1本だけ「1」に変化するだけであるため、配線容量に差異がないと仮定した場合、入力値および出力値に関係なく信号変化に伴う配線の充放電電流は一定である。そのため、GF(((22)2)2)逆元演算回路100に対するDPA攻撃は困難となる。また、GF(((22)2)2)逆元演算回路100の内部動作においても、各演算ブロックの出力信号は、プリチャージ相で設定された固定値「0000」からデコードデータに変化するだけで、変化は4本の信号線で1本だけとなる。したがって、GF(((22)2)2)逆元演算回路100の内部動作電流に対するDPA攻撃も困難となる。

【0076】

このように、本発明の第1の実施の形態では、デコードデータで動作する演算回路を用いて、プリチャージ相において各演算回路出力のデコードデータを「0000」にリセットし、エバリュエーション相で1ビットだけ「1」に変化させる。これにより、逆元演算時の中間値への遷移を抑止することができる。

【0077】

<2.第2の実施の形態>

上述の第1の実施の形態では1ラウンドの処理をプリチャージ相およびエバリュエーション相の2相に分けて実行したが、この第2の実施の形態では1ラウンドの処理を1クロックサイクルで実行することを想定する。

【0078】

本発明の第2の実施の形態におけるGF(((22)2)2)逆元演算回路の回路構成は、上述の第1の実施の形態において説明したものと同様である。したがって、ゲート遅延も第1の実施の形態の場合と同様であり、少ないゲート遅延による逆元演算が可能となる。ただし、制御信号PCdlyのタイミングが第1の実施の形態の場合とは異なる。

【0079】

[逆元演算回路の動作]

図29は、本発明の第2の実施の形態におけるGF(((22)2)2)逆元演算回路100の動作タイミング例を示す図である。この第2の実施の形態では、レジスタ930の出力からGF(((22)2)2)逆元演算回路100までの演算パスの遅延時間にマージンを加えた時間が経過した後に、制御信号PCdlyが「1」から「0」に変化するように制御される。すなわち、この制御信号PCdlyは、演算部120への入力データがデコーダ111乃至114から出力されるタイミングを示すことになる。

【0080】

クロックの立上りで、レジスタ930の出力は更新され、更新データによるラウンド演算が開始される。これと同時に制御信号PCdlyも「1」になり、GF(((22)2)2)逆元演算回路100の入力信号はデコーダ111乃至114によって「0000_0000」に制御され、この入力を受けてGF(((22)2)2)逆元演算回路100が動作する。そして、エンコーダ131乃至134の入力も「0000_0000」になる。このときの出力変化は、直前のデコードデータに関わらず、4本の信号線で1本だけ「0」に変化する。

【0081】

レジスタ930の出力からGF(((22)2)2)逆元演算回路100までの演算パスの遅延時間にマージンを加えた時間が経過した後、制御信号PCdlyは「0」となり、GF(((22)2)2)逆元演算回路100に到達している演算データがデコードされる。これにより、GF(((22)2)2)逆元演算回路100が動作を開始する。

【0082】

そして、14ゲート遅延後に乗算回路126および127の出力も「0000_0000」から演算結果に遷移する。このときの出力変化も、4本の信号線で1本だけ「1」に変化する。

【0083】

このように、本発明の第2の実施の形態によれば、レジスタ930の出力からの遅延時間にマージンを加えたタイミングで制御信号PCdlyを制御することにより、逆元演算時の中間値への遷移を抑止することができる。

【0084】

<3.変形例>

上述の実施の形態ではRijndealへの適用例について説明したが、数値演算でSbox値を生成する他の暗号にも本発明は適用可能である。例えば、AESと同様な構成をとる次世代暗号として、Camellia、Hierocrypt等にも適用することができる。

【0085】

このように、本発明の実施の形態によれば、GF(((22)2)2)逆元演算回路100において入力データを制御信号PCdlyにより固定値とデコード値の切り替えを制御し、逆元演算後に演算結果をエンコードすることにより、中間値への遷移を抑止することができる。また、逆元演算サイクル数が少ないため、中間値への遷移の確率およびその遷移時間も短く、中間値遷移による消費電流の増加を抑えることができる。そして、それと同時に、高い周波数での動作が可能となる。また、逆元演算回路において、2入力回路での入力遅延の差による中間値への遷移がほとんど発生しないため、その遷移に伴う電流に対するDPA攻撃が困難になる。また、逆元演算回路の入出力信号の変化は、固定値(例えば「0000_0000」)から演算結果のデコード値への変化またはその逆であるため、変化する信号線は例えば4本に付き常に1本であり、これは入出力データに依存しない。そのため、入出力信号の変化に対するDPA攻撃は困難になる。

【0086】

なお、本発明の実施の形態は本発明を具現化するための一例を示したものであり、本発明の実施の形態において明示したように、本発明の実施の形態における事項と、特許請求の範囲における発明特定事項とはそれぞれ対応関係を有する。同様に、特許請求の範囲における発明特定事項と、これと同一名称を付した本発明の実施の形態における事項とはそれぞれ対応関係を有する。ただし、本発明は実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において実施の形態に種々の変形を施すことにより具現化することができる。

【符号の説明】

【0087】

12 同形写像変換回路

16 逆同形写像・アフィン変換回路

22 逆アフィン変換・同形写像変換回路

26 逆同形写像変換回路

17、21 排他的論理和(XOR)演算回路

34、38 スイッチ

100 GF(((22)2)2)逆元演算回路

111〜114 デコーダ

120 デコードデータによる逆元演算部

121 x2・λ演算回路

122、124 排他的論理和(XOR)演算回路

123、126、127 乗算回路

125 GF((22)2)逆元演算回路

131〜134 エンコーダ

231、232 否定排他的論理和(XNOR)演算回路

233 乗算回路

234 乗算φ演算回路

235 負論理乗算回路

236 インバータ

237 負論理入力排他的論理和演算回路

238 排他的論理和(XOR)演算回路

910、920、930 レジスタ

【特許請求の範囲】

【請求項1】

ガロア体の入力データよりもビット幅が広い所定の固定値を一旦出力した後に、前記入力データに応じて前記固定値から所定ビット数だけ異なる値を示すデコードデータを出力するデコーダと、

前記デコードデータに対してガロア体の逆元演算を実行して前記デコードデータの逆元データを出力する演算部と、

前記逆元データを前記入力データと等しいビット幅の出力データにエンコードするエンコーダと

を具備するガロア体の逆元演算回路。

【請求項2】

前記デコーダは、制御信号に同期して前記固定値の出力を行う請求項1記載のガロア体の逆元演算回路。

【請求項3】

前記制御信号は、前記入力データが前記デコーダに入力されるタイミングを示す請求項2記載のガロア体の逆元演算回路。

【請求項4】

前記演算部は、前記デコーダから前記固定値が出力されている間は前記固定値を出力する請求項1記載のガロア体の逆元演算回路。

【請求項5】

ガロア体の8ビットの入力データを2ビットずつに区切った4組の部分データに対してそれぞれ4ビット幅の固定値を一旦出力した後に、前記部分データに応じて前記固定値から1ビットだけ異なる4ビット幅のデコードデータをそれぞれ出力する4つのデコーダと、

前記4組のデコードデータからなる16ビットデータに対して逆元演算を実行して前記16ビットデータの逆元データを出力する演算部と、

前記逆元データを4ビットずつに区切ってそれぞれ2ビット幅の出力データにエンコードする4つのエンコーダと

を具備するガロア体の逆元演算回路。

【請求項6】

前記4つのデコーダは、共通の制御信号に同期して前記固定値の出力を行う請求項5記載のガロア体の逆元演算回路。

【請求項7】

前記制御信号は、前記入力データが前記デコーダに入力されるタイミングを示す請求項6記載のガロア体の逆元演算回路。

【請求項8】

前記演算部は、前記4つのデコーダの全てが前記固定値を出力している間は4組の前記固定値からなる16ビット幅のデータを出力する請求項5記載のガロア体の逆元演算回路。

【請求項1】

ガロア体の入力データよりもビット幅が広い所定の固定値を一旦出力した後に、前記入力データに応じて前記固定値から所定ビット数だけ異なる値を示すデコードデータを出力するデコーダと、

前記デコードデータに対してガロア体の逆元演算を実行して前記デコードデータの逆元データを出力する演算部と、

前記逆元データを前記入力データと等しいビット幅の出力データにエンコードするエンコーダと

を具備するガロア体の逆元演算回路。

【請求項2】

前記デコーダは、制御信号に同期して前記固定値の出力を行う請求項1記載のガロア体の逆元演算回路。

【請求項3】

前記制御信号は、前記入力データが前記デコーダに入力されるタイミングを示す請求項2記載のガロア体の逆元演算回路。

【請求項4】

前記演算部は、前記デコーダから前記固定値が出力されている間は前記固定値を出力する請求項1記載のガロア体の逆元演算回路。

【請求項5】

ガロア体の8ビットの入力データを2ビットずつに区切った4組の部分データに対してそれぞれ4ビット幅の固定値を一旦出力した後に、前記部分データに応じて前記固定値から1ビットだけ異なる4ビット幅のデコードデータをそれぞれ出力する4つのデコーダと、

前記4組のデコードデータからなる16ビットデータに対して逆元演算を実行して前記16ビットデータの逆元データを出力する演算部と、

前記逆元データを4ビットずつに区切ってそれぞれ2ビット幅の出力データにエンコードする4つのエンコーダと

を具備するガロア体の逆元演算回路。

【請求項6】

前記4つのデコーダは、共通の制御信号に同期して前記固定値の出力を行う請求項5記載のガロア体の逆元演算回路。

【請求項7】

前記制御信号は、前記入力データが前記デコーダに入力されるタイミングを示す請求項6記載のガロア体の逆元演算回路。

【請求項8】

前記演算部は、前記4つのデコーダの全てが前記固定値を出力している間は4組の前記固定値からなる16ビット幅のデータを出力する請求項5記載のガロア体の逆元演算回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【公開番号】特開2012−22218(P2012−22218A)

【公開日】平成24年2月2日(2012.2.2)

【国際特許分類】

【出願番号】特願2010−161223(P2010−161223)

【出願日】平成22年7月16日(2010.7.16)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年2月2日(2012.2.2)

【国際特許分類】

【出願日】平成22年7月16日(2010.7.16)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]