キャッシュメモリ、及びキャッシュメモリの駆動方法

【課題】低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供する。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、キャッシュメモリとその駆動方法に関する。

【背景技術】

【0002】

多くのCPU(Central Processing Unit:中央演算装置)には、一時的にデータを格納するキャッシュメモリが搭載される。キャッシュメモリは低速なメインメモリのデータの内容の一部をコピーして格納する、高速動作が可能なメモリである。キャッシュメモリにCPUが要求するデータが格納されていると、CPUは高速に演算処理を実行することができる。

【0003】

ここで、キャッシュメモリにCPUの要求するデータが格納されていることをキャッシュヒットといい、当該データが格納されていない場合をキャッシュミスという。キャッシュミスの場合は、低速なメインメモリにデータを要求する。

【0004】

キャッシュメモリの代表的な構成としては、フル連想方式、ダイレクトマップ方式、セット連想方式などがある。

【0005】

nウェイセット連想方式のキャッシュメモリは、n個のメモリセットを用いる。各メモリセットは一つの比較回路と、メインメモリのアドレスの下位ビットに対応してあらかじめ割り当てられたm行のラインを備える。各ラインは、メインメモリのアドレスの上位ビットを格納するタグフィールドと、当該アドレスに対応したデータが格納されるデータフィールドとを備える。またラインは、メモリセットにおいてデータを管理する単位とも呼ばれる。

【0006】

また、キャッシュメモリ内には当該キャッシュメモリの動作を制御する制御部が設けられる。当該制御部は、キャッシュメモリ内の特定のセットの特定のラインを選択し、当該ラインに格納されたデータを読み出す、又は当該ラインにデータを格納することができる。

【0007】

アドレスで特定される一のデータをキャッシュメモリに格納する方法を説明する。制御部はアドレスの下位ビットを参照し、それぞれのメモリセット毎に1つ割り当てられたライン(合計n行)のいずれかを、データの格納先の候補として選定する。

【0008】

キャッシュメモリの書き換えアルゴリズムとして、LRU(Least Recently Used)方式を用いる場合、上記n行のラインのうち、最も過去に使用されたラインを格納先として確定し、当該ラインに上記一のデータを上書きする。具体的には、タグフィールドにアドレスの上位ビットを格納し、データフィールドにメインメモリのコピーデータを格納する。

【0009】

次に、キャッシュメモリがデータを出力する方法を説明する。CPU(中央演算装置)がアドレスで特定されるデータをキャッシュメモリに設けられる制御部に要求すると、当該制御部によって、n個のメモリセットのそれぞれについて、当該アドレスの下位ビットに割り当てられたラインが選択される。次いで、それぞれのメモリセットに設けられた比較回路が、当該アドレスの上位ビットとタグフィールドに格納された上位ビットを比較し、一致する場合(キャッシュヒット)に、そのラインのデータフィールドに格納されたデータをCPUに出力する。一方、アドレスの上位ビットとタグフィールドに格納された上位ビットが、n行のライン全てにおいて一致しない場合(キャッシュミス)は、CPUはメインメモリにデータを要求する。

【0010】

また近年、トランジスタの構成材料として、高移動度と、均一な素子特性とを兼ね備えた酸化物半導体と呼ばれる、半導体特性を示す金属酸化物に注目が集まっている。金属酸化物は様々な用途に用いられている。例えば、酸化インジウムは、液晶表示装置において画素電極の材料として用いられている。半導体特性を示す金属酸化物としては、例えば、酸化タングステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物によってチャネルが形成されるトランジスタが、既に知られている(特許文献1及び特許文献2)。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2007−123861号公報

【特許文献2】特開2007−96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

上述のnウェイセット連想方式のキャッシュメモリは、キャッシュメモリの備えるメモリセットの数を大きくするほどキャッシュヒットする確率が高まり、CPUの処理速度を向上させることができる。一方、一度の読み出し動作でn個のセットの全てにおいて読み出し動作を行うところ、そのうちキャッシュヒットするセットは多くても1個であるため、残りのn−1個のセットの読み出しに要する電力は無駄になってしまう。

【0013】

また、1つのメモリセットには、必ず一つの比較回路が必要となるため、キャッシュメモリの備えるメモリセットの数を大きくすると、回路規模の増大を招いてしまう。

【0014】

本発明は、このような技術的背景でなされたものである。したがって本発明は、低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供することを課題とする。

【課題を解決するための手段】

【0015】

上記課題を達成するために、本発明はメモリセルの構成に着眼した。1ビットのデータを格納可能な1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つ外部へデータを出力可能な構成とする。

【0016】

より具体的には、第1格納部は、1ビットのデータを格納することができると共に、当該データを読み出しデータとして出力することができる。さらに第1格納部には、外部(例えばCPU)から入力されるデータを格納することができる。データ転送部は、第1格納部に格納されているデータを一時的に格納することができる。さらにデータ転送部は、格納したデータを第2格納部に転送することができる。第2格納部は、1ビットのデータを格納することができると共に、第1格納部にデータを転送することができる。

【0017】

このような構成とすることにより、本発明の一態様のメモリセルは、2種類のデータを格納可能で、且ついずれかのデータを第1格納部に格納することにより、当該データを読み出しデータとして出力することができる。

【0018】

すなわち、本発明の一態様のキャッシュメモリは、複数のメモリセルから構成されるラインを複数有するメモリセットと、メモリセットと対に設けられた比較回路と、制御部と、を有する。また、メモリセルのそれぞれは、第1格納部と、第2格納部と、データ転送部と、を有し、第1格納部は、制御部から入力される1ビットのデータを格納可能で、且つ、格納された1ビットのデータを比較回路に出力可能で、且つ、格納された1ビットのデータをデータ転送部に転送可能であり、またデータ転送部は、第1格納部から転送された1ビットのデータを格納可能で、且つ、格納された1ビットのデータを第2格納部に転送可能であり、第2格納部は、データ転送部から転送された1ビットのデータを格納可能で、且つ、格納された1ビットのデータを第1格納部に転送可能である。さらに、メモリセットは、制御部によって指定されるラインのいずれか1つを選択し、当該ラインを構成するメモリセルの第1格納部のそれぞれに制御部から入力される1ビットのデータを格納可能で、且つ、制御部によって指定されるラインのいずれか1つを選択し、当該ラインを構成するメモリセルの第1格納部のそれぞれから出力されるデータ群を比較回路に出力可能である。また、比較回路は、上記メモリセットから出力されたデータ群に含まれるアドレスデータと、CPUから入力されたアドレスデータとが一致するか否かを比較し、一致しない場合において、データ群を出力したラインを構成するメモリセルのそれぞれは、第2格納部に格納された1ビットのデータを第1格納部に転送すると共に、メモリセットはデータの転送が行われたメモリセルの第1格納部のそれぞれから出力されるデータ群を比較回路に出力する、キャッシュメモリである。

【0019】

本発明の一態様の上記キャッシュメモリは、1つの比較回路と対となるメモリセット内に、上述の2種類のデータを格納可能なメモリセルを有する。したがって、当該メモリセルから出力可能な2種類のデータは、1つの比較回路に送信される。そのため、比較回路を増やすことなく格納できるデータ容量を増大させることができる。

【0020】

また、最初に第1格納部に格納されていた第1のデータが読み出され、当該第1のデータが要求されるデータと一致しない場合に限り、第2格納部に格納されている第2のデータを第1格納部に転送し、再度読み出しを行う。したがって、最初に読み出される第1のデータが要求されるデータと一致した場合には読み出し動作を行わないため、従来のキャッシュメモリの構成に比べて読み出し動作を行う頻度を低減することが可能となり、結果として低消費電力動作が実現される。

【0021】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおいて、第1格納部とデータ転送部とは、第1トランジスタを介して接続され、データ転送部と第2格納部とは、第2トランジスタを介して接続され、第2格納部と第1格納部とは、第3トランジスタを介して接続される。さらに、第1トランジスタが、オン状態のときに第1格納部からデータ転送部へ1ビットのデータが転送され、オフ状態のときにデータ転送部は当該データを保持する。また、第2トランジスタが、オン状態のときにデータ転送部から第2格納部へ1ビットのデータが転送され、オフ状態のときに第2格納部は当該データを保持する。また、第3トランジスタが、オン状態のときに第2格納部から第1格納部へ1ビットのデータが転送されることを特徴とする。

【0022】

このように、キャッシュメモリ内のメモリセルの有する第1格納部と第2格納部とデータ転送部を、それぞれ1つのトランジスタを介して接続することにより、データの転送動作を簡便に行えるだけでなく、極めて単純な回路構成とすることができる。

【0023】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおいて、第1格納部は、2つのインバータが環状に接続されたインバータループを有し、データ転送部は、一方の電極が接地された第1容量素子を有し、第2格納部は、一方の電極が接地された第2容量素子を有する。また、第1格納部とデータ転送部とは、インバータループの一方のノードと、第1容量素子の他方の電極との間に、直列に接続される第1トランジスタを介して接続されている。またデータ転送部と第2格納部とは、第1容量素子の他方の電極と、第2容量素子の他方の電極との間に、直列に接続される第2トランジスタを介して接続されている。さらに、第2格納部と第1格納部とは、第2容量素子の他方の電極と、インバータループの他方のノードとの間に、直列に接続されるインバータと第3トランジスタを介して接続されている。ここで、第1トランジスタが、オン状態のときに第1格納部からデータ転送部へ1ビットのデータが転送され、オフ状態のときにデータ転送部は当該データを保持する。また、第2トランジスタが、オン状態のときにデータ転送部から第2格納部へ1ビットのデータが転送され、オフ状態のときに第2格納部は当該データを保持する。さらに、第3トランジスタが、オン状態のときに第2格納部から第1格納部へ1ビットのデータが転送されることを特徴とする。

【0024】

またこのように、第1格納部には2つのインバータで構成されるインバータループを適用することにより、データの入出力を行う第1格納部の動作を高速に行うことが出来るため、データの読み出し及び書き込みを高速に行えるキャッシュメモリとすることが出来る。また、第2格納部とデータ転送部をそれぞれ容量素子1つで構成することにより、メモリセルの回路構成を極めて簡略化することができる。

【0025】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおける、第1トランジスタ及び第2トランジスタは、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−18A以下であることを特徴とする。

【0026】

このように容量素子で構成されるデータ転送部と第2格納部とに直接接続されるトランジスタに、オフ状態におけるリーク電流が極めて低減されたトランジスタを用いることにより、データ転送部及び第2格納部に格納するデータを長い期間に渡って保持することが可能となる。

【0027】

このようなオフ状態におけるリーク電流が極めて低いトランジスタとしては、シリコンよりもバンドギャップの広い半導体をチャネルが形成される半導体層に用いた電界効果型のトランジスタが挙げられる。

【0028】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおける、第1トランジスタ及び第2トランジスタは、チャネルが形成される半導体層に酸化物半導体を含んで構成されることを特徴とする。

【0029】

このように、上記トランジスタを構成する半導体として酸化物半導体を用いることが好ましい。より好ましくは、真性キャリア密度が極めて低い酸化物半導体を用いる。チャネルが形成される半導体層の真性キャリア密度が極めて低いため、トランジスタのオフ状態におけるリーク電流は極めて小さいものとなる。このような特徴は、他の半導体(例えばシリコン)にはない酸化物半導体に特有の特徴である。

【0030】

また、本発明の一態様のキャッシュメモリの駆動方法は、まず、第1格納部と第2格納部とを有する複数のメモリセルから構成されるラインを複数有するメモリセットが、制御部によって指定されるラインのいずれか1つを選択し、当該ラインを構成するメモリセルの第1格納部のそれぞれから出力される第1データ群を比較回路に出力する。その後、比較回路は、メモリセットから出力された第1データ群に含まれるアドレスデータと、CPUから入力されたアドレスデータとが一致するか否かを比較し、一致する場合には、比較回路はCPUにキャッシュヒット信号及びメモリセットから出力された第1データ群に含まれるメインデータを出力する。一方、一致しない場合には、第1データ群を出力したラインを構成するメモリセルのそれぞれは、第2格納部に格納されたデータを第1格納部に転送すると共に、メモリセットは、データの転送が行われたメモリセルの第1格納部のそれぞれから出力される第2データ群を比較回路に出力する、キャッシュメモリの駆動方法である。

【0031】

このような駆動方法を用いることにより、従来のキャッシュメモリに比べて読み出し動作を行う頻度を低減することができるため、結果として低消費電力駆動が可能なキャッシュメモリとすることができる。

【0032】

以下では例を挙げて、本発明の一態様のキャッシュメモリとその駆動方法を用いることにより、従来のキャッシュメモリと比較して消費電力を低減可能であることを説明する。

【0033】

一例として、8個のメモリセットを有する従来のキャッシュメモリと、4個のメモリセットを有する本発明の一態様のキャッシュメモリについて、そのキャッシュヒット率と消費電力の期待値について説明する。なお上述のように、本発明の一態様のキャッシュメモリのメモリセルは、従来構成に比べて2倍のデータを格納可能であるため、これら2つのキャッシュメモリは、等しいデータ量を格納することができるとする。

【0034】

ここで、キャッシュメモリの1度の読み出し動作でキャッシュヒットする確率をキャッシュヒット率Pとし、キャッシュメモリの読み出しに要する全消費電力をWとし、それぞれのメモリセットが一度の読み出し動作で消費する消費電力を消費電力Wsとする。

【0035】

また、それぞれのキャッシュメモリにおいて、いずれか1つのメモリセット内の1つのラインに要求するデータが格納されているとする。したがって、8個のメモリセットを有する従来のキャッシュメモリでは、いずれか1つのセットに要求するデータが格納されている。一方、4個のメモリセットを有する本発明の一態様のキャッシュメモリでは、いずれか1つのメモリセット内の1つのラインを構成するメモリセル群における、いずれかの格納部(第1格納部または第2格納部)に要求するデータが格納されているとする。

【0036】

8個のメモリセットを有する従来のキャッシュメモリにおいては、いずれかのセットに要求するデータが格納されているため、1度の読み出し動作でのキャッシュヒット率Pの期待値は1となる。また、一度の読み出し動作で8個のメモリセット全ての読み出しを実行するため、消費される全消費電力Wは8Wsとなる。

【0037】

一方、本発明の一態様のキャッシュメモリにおいて、1度目の読み出し動作では、それぞれのメモリセット内のメモリセルの第1格納部に格納されているデータを読み出す。さらに1度目の読み出し動作でキャッシュヒットしなかった場合には、該当するメモリセルの第2格納部に格納されたデータを第1格納部に転送し、2度目の読み出し動作を行う。したがって、1度目の読み出し動作でのキャッシュヒット率P1は0.5であり、2度目の読み出し動作でのキャッシュヒット率(1度目の読み出し動作でキャッシュヒットせず、且つ2度目の読み出し動作でキャッシュヒットする確率)P2も同様に0.5であるため、結果としてキャッシュヒット率Pは1となる。

【0038】

また、読み出し動作で消費する消費電力Wの期待値は、1度目の読み出し動作でキャッシュヒットする場合の消費電力W1と、1度目の読み出し動作でキャッシュヒットせず、且つ2度目の読み出し動作でキャッシュヒットする場合の消費電力W2を足したものとなる。すなわち、消費電力W1はP1×4Ws=2Wsであり、消費電力W2はP2×8Ws=4Wsとなるため、結果としてキャッシュメモリの読み出し動作における全消費電力Wは6Wsとなる。

【0039】

このように、本発明の一態様のキャッシュメモリと、その駆動方法を用いることで、メモリセットの数を増やした場合と同等のキャッシュヒット率の向上を実現しつつ、読み出し動作における消費電力を低減することができる。

【発明の効果】

【0040】

本発明によれば、低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供できる。

【図面の簡単な説明】

【0041】

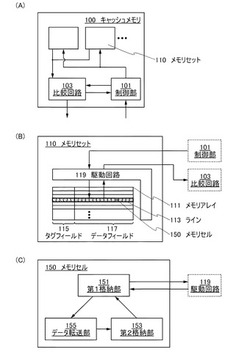

【図1】本発明の一態様の、キャッシュメモリを説明する図。

【図2】本発明の一態様の、キャッシュメモリの接続構成を説明する図。

【図3】本発明の一態様の、キャッシュメモリの動作を説明する図。

【図4】本発明の一態様の、キャッシュメモリのメモリセルを説明する図。

【図5】本発明の一態様の、キャッシュメモリのメモリセルの動作を説明する図。

【図6】本発明の一態様の、トランジスタを説明する図。

【図7】本発明の一態様の、トランジスタの作製方法を説明する図。

【図8】本発明の一態様の、キャッシュメモリのメモリセルを説明する図。

【図9】酸化物材料の結晶構造を説明する図。

【図10】酸化物材料の結晶構造を説明する図。

【図11】酸化物材料の結晶構造を説明する図。

【図12】酸化物材料の結晶構造を説明する図。

【図13】本発明の一態様の、電子機器を説明する図。

【発明を実施するための形態】

【0042】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0043】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0044】

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書におけるトランジスタは、IGFET(Insulated Gate Field Effect Transistor)や薄膜トランジスタ(TFT:Thin Film Transistor)を含む。

【0045】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0046】

また、本明細書等において、トランジスタのソース、又はドレインのどちらか一方のことを「第1電極」と呼び、ソース、又はドレインの他方を「第2電極」とも呼ぶことがある。なお、この際、ゲートについては「ゲート」又は「ゲート電極」とも呼ぶ。

【0047】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、コイル、容量素子、その他の各種機能を有する素子などが含まれる。

【0048】

なお、本明細書等においてノードとは、回路を構成する素子の電気的な接続を可能とする素子(例えば、配線など)のことをいう。したがって、”Aが接続されたノード”とは、Aと電気的に接続され、且つAと同電位と見なせる配線のことをいう。なお、配線の途中に電気的な接続を可能とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオードなど)が1個以上配置されていても、Aと同電位と見なせれば同じノードであるとする。

【0049】

なお、本明細書で説明する回路図においては、チャネルが形成される半導体に酸化物半導体などを用いたトランジスタが適用されることを示すために、回路図内のトランジスタにOSの符号を併せて付す場合がある。

【0050】

(実施の形態1)

本実施の形態では、本発明の一態様のキャッシュメモリの構成と、その駆動方法について図1乃至図3を用いて説明する。

【0051】

<構成例>

図1(A)は、本実施の形態で例示するキャッシュメモリの構成を示すブロック図である。キャッシュメモリ100は、1または複数のメモリセット110と、制御部101と、比較回路103と、を有する。各メモリセット110は比較回路103及び制御部101と電気的に接続し、また比較回路103及び制御部101はお互いに電気的に接続している。

【0052】

制御部101は、比較回路103からの入力信号や外部(例えばCPU)からの命令信号に応じて、各メモリセット110の動作を制御する。例えばメモリセット110の読み出し動作や、メモリセット110へのデータの書き換え動作、または後に説明するメモリセット110内のメモリセルのデータ転送動作などを制御する。

【0053】

制御部101には、外部から要求されるアドレスデータが入力される。制御部101は、当該アドレスデータを上位ビットから構成される第1のアドレスデータと下位ビットから構成される第2のアドレスデータとに分割し、第1のアドレスデータを比較回路103に、また第2のアドレスデータをそれぞれのメモリセット110に出力する。

【0054】

また、制御部101は外部からの命令信号に応じて、指定されるメモリセット110内のデータの書き換えを行うことができる。例えば外部から書き換えの命令信号に加えてアドレスデータとメインデータとが入力されると、書き換えを行う対象のメモリセット110を選択し、当該メモリセット110内に対して、アドレスデータの下位ビット(第2のアドレスデータ)に対応するラインに、アドレスデータの上位ビット(第1のアドレスデータ)とメインデータを格納するよう要求する。

【0055】

比較回路103には、それぞれのメモリセット110から、後に説明する当該それぞれのメモリセット110内の特定のラインのタグフィールドに格納されたアドレスデータと、データフィールドに格納されたメインデータが入力される。比較回路103は、制御部101から入力された第1のアドレスデータとメモリセット110から入力されたアドレスデータとを比較し、一致する場合には、キャッシュヒット信号に加えてメインデータを外部に出力する。一方、全てのメモリセット110においてこれらが一致しない場合には、キャッシュミス信号のみを制御部101に出力する。

【0056】

なお具体的には、比較回路103は、キャッシュメモリ100が有するメモリセット110と等しい数のタグ比較回路と、1つのデータ比較回路を備える。1つのメモリセット110には1つのタグ比較回路が接続され、当該メモリセットから出力されるアドレスデータと、第1のアドレスデータとの比較を行い、その結果をキャッシュヒット信号又はキャッシュミス信号として、データ比較回路に出力する。データ比較回路には各々のタグ比較回路から入力される上記信号と、それぞれのメモリセット110からのメインデータが入力され、各々のタグ比較回路から入力される信号に応じて、キャッシュヒット信号及びメインデータを外部に出力するか、キャッシュミス信号のみを制御部101に出力するかのいずれかを行う。

【0057】

なお、読み出し動作や上記比較動作は、全てのメモリセット110に対して並行して行われる。このように並行して動作を行うことにより、より高速動作が実現できる。

【0058】

ここで、制御部101は、比較回路103から1度目のキャッシュミス信号が入力された場合、それぞれのメモリセット110に対して、後に説明するデータ転送動作と読み出し動作を行うよう、命令信号を送信する。また、制御部101に2度目のキャッシュミス信号が入力された場合には、比較回路103に対して、キャッシュミス信号を外部に出力するように要求する命令信号を出力する。比較回路103は、当該信号が入力されると、キャッシュミス信号を外部に出力する。

【0059】

続いて、メモリセット110の構成について説明する。図1(B)は、メモリセット110の構成を示すブロック図である。メモリセット110は、メモリアレイ111と、駆動回路119とを有する。また、メモリアレイ111は、m本のライン113から構成され、それぞれのライン113は複数のメモリセル150を有する。

【0060】

m本のライン113のそれぞれは、アドレスデータの下位ビットに対応して設けられている。したがって、制御部101から入力される第2のアドレスデータによって、選択されるライン113が一義的に決定される。例えば当該第2のアドレスデータとして8ビット分のデータを用いる場合には、メモリセット110は256本のライン113を有する。

【0061】

また、ライン113は少なくともタグフィールド115とデータフィールド117の2つの領域を有している。タグフィールド115には、第1のアドレスデータが格納され、データフィールド117にはアドレスデータに対応したメインデータが格納される。

【0062】

駆動回路119は、制御部101からの要求に応じて、メモリアレイ111内のライン113を選択し、データを格納する(書き換える)、またはデータを読み出して比較回路に出力することができる。また、任意のライン113内のメモリセル150に対して、後述するデータ転送動作を行うことができる。

【0063】

データを読み出す際、駆動回路119は制御部101から入力される第2のアドレスデータによって一義的に決定されるメモリアレイ111内の1つのライン113を選択し、当該ライン113に格納されるデータ(データ群とも呼ぶ)を読み出すと共に当該データを比較回路103に出力する。

【0064】

データ転送動作を行う際、駆動回路119は制御部101からの命令信号に応じて、指定する1つのライン113を構成する全てのメモリセル150に対して、後述するデータ転送動作を行い、次いで当該ライン113に格納されるデータの読み出しを行うと共に比較回路103に出力する。

【0065】

また、駆動回路119は、制御部101からの命令信号に応じて、特定のラインに対してデータの書き換えを行うことができる。制御部101からは書き換え命令信号に加えて、第1のアドレスデータと第2のアドレスデータとメインデータが入力される。駆動回路119は、第2のアドレスデータで一義的に決定されるメモリアレイ111内の1つのライン113を選択し、当該ライン113のタグフィールド115に第1のアドレスデータを、またデータフィールド117にメインデータをそれぞれ格納する。

【0066】

続いて、メモリセル150について説明する。図1(C)は、メモリセル150の構成を示すブロック図である。

【0067】

メモリセル150は、第1格納部151と、第2格納部153と、データ転送部155を有する。第1格納部151、第2格納部153、及びデータ転送部155は、それぞれ1ビットのデータを格納することができる。

【0068】

第1格納部151は、当該第1格納部151に格納された1ビットのデータを駆動回路119に出力することができる。また駆動回路119により、当該第1格納部151に格納されるデータを書き換えることができる。さらに、当該第1格納部151に格納された1ビットのデータをデータ転送部155に転送することが出来る。

【0069】

データ転送部155は、第1格納部151から転送された1ビットのデータを格納しておくことができる。さらにデータ転送部155は、当該データ転送部155に格納された1ビットのデータを第2格納部153に転送し、当該第2格納部153内のデータを書き換えることができる。

【0070】

第2格納部153は、データ転送部155から転送された1ビットのデータを格納しておくことが出来る。さらに、当該第2格納部153に格納された1ビットのデータを第1格納部151に転送し、当該第1格納部151内のデータを書き換えることができる。

【0071】

ここで本明細書等において、メモリセル内でのデータの転送は、転送元に格納されたデータのコピーを、転送先に格納するものとする。したがって、データの転送後には、転送元と転送先とに同一のデータが格納された状態となる。

【0072】

ここで、データ転送動作を行う場合について説明する。まず初期状態として、第1格納部151には第1のデータが、また第2格納部153には第2のデータが格納されているとする。

【0073】

データ転送動作は主に3つの動作からなる。まず第1の動作として、第1格納部151に格納された第1のデータを、データ転送部155にコピーして格納(転送)する。次いで、第2の動作として、第2格納部153に格納された第2のデータを、第1格納部151に転送する。この段階で、第1格納部151及び第2格納部153のそれぞれには、第2のデータが格納され、データ転送部155には第1のデータが格納されている状態となる。最後に、第3の動作として、データ転送部155から第2格納部153に第1のデータを転送することによりデータ転送動作が終了する。最終的に、第1格納部151には第2のデータが、また第2格納部153には第1のデータが格納されている状態となり、初期状態における第1格納部151と第2格納部153に格納されていたデータが置換された状態となる。

【0074】

以上がキャッシュメモリ100の構成についての説明である。

【0075】

<接続構成例>

ここで、本発明の一態様のキャッシュメモリ100は、少なくとも演算部と、制御部を有するCPUに接続することができる。図2は、キャッシュメモリ100が接続され、制御部161及び演算部162を有するCPU160の構成を示すブロック図である。

【0076】

演算部162は、論理演算、アドレス演算などの演算処理を行う。また、演算部162は、制御部161に対して演算に必要なメインデータを要求するため、制御部161に対して要求するメインデータに対応するアドレスデータを制御部161に出力する。

【0077】

制御部161は、演算部162からアドレスデータが入力されると、キャッシュメモリ100に当該アドレスデータを出力してデータを要求する。このとき、キャッシュメモリ100からキャッシュヒット信号と要求したメインデータを受信した場合は、演算部162に当該データを出力する。一方、キャッシュメモリ100からキャッシュミス信号を受信した場合は、メインメモリ170に対してデータを要求する。

【0078】

また、制御部161は、メインメモリ170からメインデータを取得した際、演算部162に当該メインデータを出力すると共に、キャッシュメモリ100に当該メインデータを格納するように命令する。このとき、制御部161は、キャッシュメモリ100に対し、書き込み命令信号と、メインデータと、当該メインデータに対応するアドレスデータを送信する。キャッシュメモリ100は、当該書き込み命令信号にしたがって、指定されるセットの特定のラインに当該メインデータとアドレスデータを格納する。なお、制御部161は、メインメモリ170からメインデータを取得した後、まずキャッシュメモリ100に当該メインデータとアドレスデータを格納し、キャッシュメモリ100に格納された当該メインデータを読み出して演算部162に送信してもよい。

【0079】

メインメモリ170としては、例えば、SRAMやDRAMから構成される揮発性の記憶装置をはじめ、光磁気ディスクやフラッシュメモリなどの不揮発性の記憶装置を用いることができる。ここで以降では、キャッシュメモリとメインメモリとの違いとして、CPUが最初にデータを要求する記憶装置のことをキャッシュメモリといい、2番目以降にデータを要求する記憶装置のことをメインメモリということとする。

【0080】

<動作例>

続いて、キャッシュメモリ100の動作例について図3を参照して説明する。図3は、キャッシュメモリ100の動作の一例に係るフローチャートである。

【0081】

ここで、初期状態として、各々のメモリセル150内の第1格納部151には第1のデータが、また第2格納部153には第2のデータが格納されているとする。

【0082】

まず、ステップ201(第1の読み出し)では、制御部101に要求されるアドレスデータが入力され、制御部101から各メモリセット110に第2のアドレスデータが、また比較回路103に第1のアドレスデータが出力される。それぞれのメモリセット110は、第2のアドレスデータで一義的に決定されるライン113内に格納されているアドレスデータとメインデータの読み出しを行うと共に、これらを比較回路103に出力する。ここで読み出されるデータは、各々のメモリセル150内の第1格納部151に格納されている第1のデータである。

【0083】

ステップ202(第1の比較)において、比較回路103は第1のアドレスデータと、各メモリセット110から入力されるアドレスデータとの比較を行う。

【0084】

ここで、いずれかのメモリセット110から入力されるアドレスデータと、第1のアドレスデータが一致した(キャッシュヒットした)場合、ステップ203(出力)として、比較回路103はキャッシュヒット信号と、当該メモリセットから入力されたメインデータを合わせて外部に出力する。

【0085】

また、ステップ202において、それぞれのメモリセット110から入力されるアドレスデータが第1のアドレスデータといずれも一致しない(キャッシュミスした)場合、比較回路103は制御部101にキャッシュミス信号を出力する。

【0086】

制御部101はステップ202において比較回路103からキャッシュミス信号を受けると、それぞれのメモリセット110に対してデータ転送動作の命令信号を送信する。

【0087】

ステップ204(データ転送動作)では、各々のメモリセット110の上記第2のアドレスデータに対応したライン113内の全てのメモリセル150において、上述したデータ転送動作を行う。具体的には、メモリセル150内の第1格納部151に格納されている第1のデータをデータ転送部155に転送して格納する第1の動作と、第2格納部153に格納されている第2のデータを第1格納部151に転送して書き換える第2の動作と、データ転送部155に格納されている第1のデータを第2格納部153に転送して書き換える第3の動作と、を順に行う。

【0088】

続いて、ステップ205(第2の読み出し)では、それぞれのメモリセット110においてステップ204でデータ転送動作を行ったライン113に対して再度読み出し動作を行うと共に、比較回路103に読み出されたデータが出力される。ここで読み出されるデータは、各々のメモリセル150内の第1格納部151に格納されている第2のデータとなる。

【0089】

なお、ステップ205の読み出し動作は、ステップ204の第3の動作と並行して行うことが好ましい。これらの動作を並行して行うことで、より高速動作が実現できる。

【0090】

続いて、ステップ206(第2の比較)において、比較回路103は第1のアドレスデータと、各メモリセット110から入力されるアドレスデータとの比較を行う。

【0091】

ステップ206でいずれかのメモリセット110でキャッシュヒットした場合、ステップ203として、比較回路103はキャッシュヒット信号と、当該メモリセットから入力されたメインデータを合わせて外部に出力する。

【0092】

ここで、キャッシュヒットしたメモリセット110については、そのままの状態が維持され、キャッシュヒットしなかった他のメモリセット110については、ステップ207に移行する。

【0093】

一方、ステップ206において、いずれのメモリセット110でもキャッシュヒットしなかった(キャッシュミスした)場合は、比較回路103はキャッシュミス信号を制御部101に送信する。続いて、制御部101からの命令により、比較回路103は外部にキャッシュミス信号を出力し、各メモリセット110はステップ207に移行する。

【0094】

ステップ207(書き換え判定)では、それぞれのメモリセット110について、データの書き換えを行うかどうかの判定を行う。ステップ206において、比較回路103が外部にキャッシュミス信号を送信した場合は、いずれかのメモリセット110を選択し、メインメモリ170から取得した新たなデータ(第3のデータ)に書き換える。データを書き換えるメモリセット110の選択方法としては、上述のLRU方式や、最も使用頻度が少ないメモリセットを選択するLFU(Least Frequency Used)方式、又は最初にデータが格納されたメモリセットを選択するFIFO(First In First Out)方式などの書き換えアルゴリズムを用いることができる。

【0095】

ステップ207でデータの書き換えを行わないと判定されたメモリセット110については、ステップ208において再度データ転送動作を行う。また、データの書き換えを行うと判定されたメモリセット110については、ステップ209に移行する。

【0096】

ステップ208(データ転送動作)では、上述したデータ転送動作を再度行う。その結果、該当するメモリセル150においては、第1格納部151に第1のデータが、また第2格納部153に第2のデータが格納された状態、すなわち初期状態と同じ状態に戻る。

【0097】

ステップ209(データ書き込み動作)では、制御部101に、アドレスデータと書き換え命令信号と、各々のメモリセルに入力する第3のデータからなるデータ群が入力される。続いて、ステップ207で書き換えを行うと判定されたメモリセット110の、該当するライン113内の全てのメモリセル150に対し、第3のデータの書き込みを行う。各メモリセル150では、第1格納部151に第3のデータが書込まれる。したがって、書き込みが行われたメモリセル150では、第1格納部151には第3のデータが、また第2格納部153には第1のデータが格納された状態となる。

【0098】

以上が、本発明の一態様のキャッシュメモリ100の動作についての説明である。

【0099】

このように、キャッシュメモリ100内のメモリセル150には2種類のデータを格納することが出来るため、メモリセットの数を2倍にした場合と同等のキャッシュヒット率を得ることが出来る。さらに、メモリセットの数を増やす場合に比べて、比較回路の数を増やすことが無いため、回路規模の増大が抑制できる。また、このようなメモリセル150を有するキャッシュメモリ100を上述のように動作させることにより、メモリセットの数を2倍にした場合に比べて読み出しに要する消費電力を低減することができる。

【0100】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0101】

(実施の形態2)

本実施の形態では、実施の形態1で例示したメモリセル150の具体的な構成例と、その動作について、図4及び図5を用いて説明する。

【0102】

<構成例>

図4に、本実施の形態で例示するメモリセル150の構成例を示す。メモリセル150は、トランジスタ261、トランジスタ262、トランジスタ263、トランジスタ271、トランジスタ272、インバータ273、インバータ274、容量素子281、容量素子291、及びインバータ292を有する。またメモリセル150には、第1ゲート線251、第2ゲート線252、第3ゲート線253、第4ゲート線254、第1ビット線255、及び第2ビット線256が接続されている。

【0103】

ここで、トランジスタ261、トランジスタ262、トランジスタ263、トランジスタ271、トランジスタ272は全てnチャネル型のトランジスタである。また、インバータ273、インバータ274、及びインバータ292は、入力された電位の位相を反転させて出力する機能を有する回路素子であればどのような構成を用いても良い。例えばnチャネル型のトランジスタとpチャネル型のトランジスタの2種類のトランジスタを組み合わせて構成されていてもよいし、nチャネル型のトランジスタ又はpチャネル型のトランジスタのいずれか一方を含んで構成されていても良い。

【0104】

トランジスタ271は、ゲートが第1ゲート線251と接続され、第1電極が第1ビット線255と接続され、第2電極がインバータ273の入力端子、インバータ274の出力端子、及びトランジスタ261の第1電極に接続される。またトランジスタ272は、ゲートが第1ゲート線251と接続され、第1電極がインバータ273の出力端子、インバータ274の入力端子、及びトランジスタ263の第1電極と接続され、第2電極が第2ビット線256と接続される。インバータ273とインバータ274はそれぞれが環状に接続されたインバータループを構成している。ここで、当該インバータループが実施の形態1で例示した第1格納部151に相当する。なお、トランジスタ271の第2電極が接続されるノードをノード265、またトランジスタ272の第1電極が接続されるノードをノード266とする。

【0105】

トランジスタ261は、ゲートが第2ゲート線252に接続され、第2電極が容量素子281の一方の電極、及びトランジスタ262の第1電極に接続される。また容量素子281の他方の電極は接地されている。ここで、トランジスタ261の第2電極と容量素子281の一方の電極との間のノード267と、容量素子281を含む領域が、実施の形態1で例示したデータ転送部155に相当する。データ転送部155は、容量素子281に電位が保持されることによりデータを格納する。

【0106】

トランジスタ262は、ゲートが第3ゲート線253と接続され、第2電極が容量素子291の一方の電極、及びインバータ292の入力端子と接続される。容量素子291の他方の電極は接地されている。また、インバータ292の出力端子は、トランジスタ263の第2電極と接続される。トランジスタ263のゲートは、第4ゲート線254と接続される。ここで、容量素子291とインバータ292の間のノード268と、容量素子291とを含む領域が、実施の形態1で例示した第2格納部153に相当する。第2格納部153は、容量素子291に電位が保持されることによりデータを格納する。

【0107】

メモリセル150は、第1ビット線255及び第2ビット線256を介して第1格納部151に格納されるデータを出力することができると共に、第1格納部151のデータを書き換えることが出来る。また、第1格納部151に格納されたデータは、トランジスタ261を介してデータ転送部155にコピーして格納することが出来る。また、データ転送部155に格納されたデータを、トランジスタ262を介して第2格納部153に格納することにより、書き換えることが出来る。さらに、第2格納部153に格納されたデータは、トランジスタ263を介して第1格納部151に格納することにより、書き換えることが出来る。

【0108】

ここで、データ転送部155に格納されているデータを第2格納部153に転送する場合、具体的にはトランジスタ262をオン状態にして、ノード267とノード268を導通状態とし、ノード268の電位を、トランジスタ262をオン状態とする直前のノード267の電位に近い電位にまで変化させる。そのため、データ転送部155内の容量素子281は、第2格納部153内の容量素子291よりも十分大きい容量とする。例えば、容量素子281の容量を容量素子291の少なくとも2倍以上の容量とすることが好ましい。

【0109】

また、トランジスタ271及びトランジスタ272、並びにインバータ273、インバータ274及びインバータ292を構成するトランジスタには、チャネルが形成される半導体として結晶性シリコンなどを用いた、高速動作可能なトランジスタを適用することが出来る。このような高速動作可能なトランジスタを用いることにより、メモリセル150への読み出しや書き込み動作を高速に行うことが出来る。

【0110】

またトランジスタ261とトランジスタ262には、オフ状態におけるリーク電流が極めて低減されたトランジスタを適用することが好ましい。例えば、シリコンよりもバンドギャップの広い半導体をチャネルが形成される半導体層に用いた電界効果型のトランジスタを適用することができる。例えば2eV以上、好ましくは2.5eV以上、より好ましくは3.0eV以上のバンドギャップを有する半導体を用いることができる。このようなトランジスタは、オフ状態におけるリーク電流が小さい特徴を有する。またこのような半導体として酸化物半導体を用いることが好ましい。

【0111】

また、上記トランジスタを構成する半導体は、真性キャリア密度が極めて低い酸化物半導体を用いることが好ましい。チャネルが形成される半導体層の真性キャリア密度が極めて低いため、トランジスタのオフ状態におけるリーク電流は極めて小さいものとなる。このような特徴は、他の半導体(例えばシリコン)にはない酸化物半導体に特有の特徴である。

【0112】

さらに、上記酸化物半導体を含むトランジスタは、オフ状態におけるリーク電流(以下オフ電流とも呼ぶ)が低く、チャネル幅1μmあたり10aA(1×10−17A)以下、好ましくはチャネル幅1μmあたり1aA(1×10−18A)以下、より好ましくはチャネル幅1μmあたり10zA(1×10−20A)以下、さらに好ましくはチャネル幅1μmあたり1zA(1×10−21A)以下、さらに好ましくはチャネル幅1μmあたり100yA(1×10−22A)以下である。

【0113】

なお、トランジスタ263には、トランジスタ271などと同様の高速動作可能なトランジスタを適用しても良いし、トランジスタ261などと同様の、オフ状態におけるリーク電流が極めて低減されたトランジスタを適用することも出来る。

【0114】

なお、本実施の形態ではデータ転送部155及び第2格納部153の構成として、容量素子に電荷を蓄積することによりデータを格納する構成としたが、メモリセル150の構成はこれに限られない。例えば、データ転送部155と第2格納部153とを、インバータループを用いた構成とし、それぞれに格納されたデータを、トランジスタやアナログスイッチなどのスイッチング素子を介して転送可能な構成としても良い。しかし、本実施の形態で例示したメモリセル150の構成とすることにより、メモリセルを構成するトランジスタ数が極めて低減され、より簡略化された構成とすることが出来る。また、後の実施の形態で例示するように、トランジスタ271などに適用される高速動作可能なトランジスタと、トランジスタ261などに適用されるオフ状態におけるリーク電流が極めて低減されたトランジスタとを積層して形成することにより、さらにメモリセル150の占有面積を低減することが出来る。

【0115】

<回路動作例>

以下では、本実施の形態で例示するメモリセル150の回路動作の一例について、図5を用いて説明する。図5は、メモリセル150の回路動作に係るタイミングチャートである。

【0116】

図5に示すタイミングチャートでは、上から順に第1ゲート線251、第1ビット線255、第2ビット線256、第2ゲート線252、第3ゲート線253、第4ゲート線254、ノード265、ノード266、ノード267、及びノード268における、電位の時間推移を示している。

【0117】

期間T0は、初期状態を示している。ここで初期状態として、第1格納部151内のノード265にハイレベル電位が、ノード266にローレベル電位が与えられているものとする。また、初期状態では、データ転送部155内のノード267と、第2格納部153内のノード268にはローレベル電位が与えられている。また、第1ビット線255及び第2ビット線256には、中間電位を与えることによりプリチャージされている。

【0118】

期間T1は、第1の読み出し動作を示す。読み出しを行う場合、第1ゲート線251のみにハイレベル電位を与える。このとき、第1ゲート線251にゲートが接続されたトランジスタ271及びトランジスタ272がオン状態となるため、ノード265と第1ビット線255、及びノード266と第2ビット線256がそれぞれ導通状態となる。したがって、第1ビット線255にはハイレベル電位が、また第2ビット線256にはローレベル電位が出力される。これらの電位の変化を、駆動回路119内のセンスアンプ等で検知することにより読み出しを行うことが出来る。

【0119】

期間T2は、第1格納部151からデータ転送部155へのデータの転送動作を示す。このとき、第2ゲート線252にハイレベル電位を与えることにより、トランジスタ261がオン状態となり、ノード265とノード267とが導通状態となる。さらに、容量素子281にノード267の電位に応じた電荷が蓄積されることにより、データ転送部155にハイレベル電位が格納される。

【0120】

期間T2の後、第2ゲート線252にローレベル電位を与えることによりトランジスタ261がオフ状態となる。さらにこのとき、トランジスタ262もオフ状態が維持されている。ここで、トランジスタ261及びトランジスタ262は上述のようにオフ状態におけるリーク電流が極めて低いため、容量素子281に蓄積された電荷の流出が極めて抑制され、ノード267の電位を極めて長い期間保持することが出来る。

【0121】

期間T3は、第2格納部153から第1格納部151へのデータ書き換え動作を示す。このとき、第4ゲート線254にハイレベル電位を与えることにより、トランジスタ263をオン状態とする。したがって、ノード268の電位がインバータ292によって反転された電位が、ノード266に与えられる。ここでは、ノード268がローレベル電位であるため、ノード266にはこの反転した電位であるハイレベル電位が与えられる。これに応じて、ノード265の電位は、ハイレベル電位からローレベル電位に反転する。このようにして、第2格納部153から第1格納部151へデータを書き換えることができる。

【0122】

期間T4は、第2の読み出し動作を示す。期間T1と同様に、第1ゲート線251にハイレベル電位を与えることにより読み出しを行う。ここでは、第1ビット線255にローレベル電位が、第2ビット線256にハイレベル電位が出力される。

【0123】

期間T5は、データ転送部155から第2格納部153へのデータの転送動作を示す。このとき、第3ゲート線253にハイレベル電位を与えることにより、トランジスタ262をオン状態とし、ノード267とノード268とを導通状態とする。ここで、上述のように、容量素子291に比べて容量素子281の容量が十分大きいため、ノード268の電位は、トランジスタ262をオン状態とする直前のノード267の電位に近い値にまで変化する。このようにして、データ転送部155から第2格納部153へデータを転送することが出来る。なお、実際は容量素子291と容量素子281との間で電荷のやり取りが行われるため、容量素子291の電位も変動することがあるが、図5には明瞭化のためこの電位の変動は図示していない。

【0124】

期間T5の後、第3ゲート線253にローレベル電位を与えることにより、トランジスタ262がオフ状態となる。上述のようにトランジスタ262はオフ状態におけるリーク電流が極めて低いため、容量素子291に蓄積された電荷の流出が極めて抑制され、ノード268の電位を極めて長い期間保持することが出来る。

【0125】

期間T6は、第1格納部151へのデータ書き込み動作を示す。ここでは、第1格納部151内のノード265にハイレベル電位を、ノード266にローレベル電位を書込む場合について説明する。このとき、第1ゲート線251にハイレベル電位を与えると共に、第1ビット線255にはハイレベル電位を、また第2ビット線256にはローレベル電位を与える。したがって、ノード265にはトランジスタ271を介して第1ビット線255からハイレベル電位が与えられ、ノード266にはトランジスタ272を介して第2ビット線256からローレベル電位が与えられる。このようにして、第1格納部151へデータを書込むことができる。

【0126】

期間T7は、第3の読み出し動作を示す。期間T1と同様に、第1ゲート線251にハイレベル電位を与えることにより読み出しを行う。ここでは、第1ビット線255にハイレベル電位が、第2ビット線256にローレベル電位が出力される。

【0127】

以上がメモリセル150の動作についての説明である。

【0128】

このようなメモリセル150を実施の形態1のキャッシュメモリ100に適用することにより、メモリセットを増やした場合と同等のキャッシュヒット率を実現しつつ、低消費電力動作が可能なキャッシュメモリを実現できる。

【0129】

また、メモリセル150内の第1格納部151とデータ転送部155、及びデータ転送部155と第2格納部153のそれぞれを接続するトランジスタに、オフ状態におけるリーク電流が極めて低減されたトランジスタを適用することにより、データ転送部155と第2格納部153に格納されるデータを極めて長い期間に渡って保持することが出来る。

【0130】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0131】

(実施の形態3)

本実施の形態では、本発明の一態様のキャッシュメモリに適用可能な酸化物半導体層を含むトランジスタの例について説明する。

【0132】

上記酸化物半導体層を含むトランジスタの構造例について、図6を用いて説明する。図6は、本実施の形態におけるトランジスタの構造例を示す断面模式図である。

【0133】

図6(A)に示すトランジスタは、導電層601(a)と、絶縁層602(a)と、半導体層603(a)と、導電層605a(a)と、導電層605b(a)と、絶縁層606(a)と、導電層608(a)と、を含む。

【0134】

導電層601(a)は、被素子形成層600(a)の上に設けられる。

【0135】

絶縁層602(a)は、導電層601(a)の上に設けられる。

【0136】

半導体層603(a)は、絶縁層602(a)を介して導電層601(a)に重畳する。

【0137】

導電層605a(a)及び導電層605b(a)のそれぞれは、半導体層603(a)の上に設けられ、半導体層603(a)に電気的に接続される。

【0138】

絶縁層606(a)は、半導体層603(a)、導電層605a(a)、及び導電層605b(a)の上に設けられる。

【0139】

導電層608(a)は、絶縁層606(a)を介して半導体層603(a)に重畳する。

【0140】

なお、必ずしも導電層601(a)及び導電層608(a)の一方を設けなくてもよい。また、導電層608(a)を設けない場合には、絶縁層606(a)を設けなくてもよい。

【0141】

図6(B)に示すトランジスタは、導電層601(b)と、絶縁層602(b)と、半導体層603(b)と、導電層605a(b)と、導電層605b(b)と、絶縁層606(b)と、導電層608(b)と、を含む。

【0142】

導電層601(b)は、被素子形成層600(b)の上に設けられる。

【0143】

絶縁層602(b)は、導電層601(b)の上に設けられる。

【0144】

導電層605a(b)及び導電層605b(b)のそれぞれは、絶縁層602(b)の一部の上に設けられる。

【0145】

半導体層603(b)は、導電層605a(b)及び導電層605b(b)の上に設けられ、導電層605a(b)及び導電層605b(b)に電気的に接続される。また、半導体層603(b)は、絶縁層602(b)を介して導電層601(b)に重畳する。

【0146】

絶縁層606(b)は、半導体層603(b)、導電層605a(b)、及び導電層605b(b)の上に設けられる。

【0147】

導電層608(b)は、絶縁層606(b)を介して半導体層603(b)に重畳する。

【0148】

なお、必ずしも導電層601(b)及び導電層608(b)の一方を設けなくてもよい。導電層608(b)を設けない場合には、絶縁層606(b)を設けなくてもよい。

【0149】

図6(C)に示すトランジスタは、導電層601(c)と、絶縁層602(c)と、半導体層603(c)と、導電層605a(c)と、導電層605b(c)と、を含む。

【0150】

半導体層603(c)は、領域604a(c)及び領域604b(c)を含む。領域604a(c)及び領域604b(c)は、互いに離間し、それぞれドーパントが添加された領域である。なお、領域604a(c)及び領域604b(c)の間の領域がチャネル形成領域になる。半導体層603(c)は、被素子形成層600(c)の上に設けられる。なお、必ずしも領域604a(c)及び領域604b(c)を設けなくてもよい。

【0151】

導電層605a(c)及び導電層605b(c)は、半導体層603(c)の上に設けられ、半導体層603(c)に電気的に接続される。また、導電層605a(c)及び導電層605b(c)の側面は、テーパ状である。

【0152】

また、導電層605a(c)は、領域604a(c)の一部に重畳するが、必ずしもこれに限定されない。導電層605a(c)を領域604a(c)の一部に重畳させることにより、導電層605a(c)及び領域604a(c)の間の抵抗値を小さくすることができる。また、導電層605a(c)に重畳する半導体層603(c)の領域の全てが領域604a(c)でもよい。

【0153】

また、導電層605b(c)は、領域604b(c)の一部に重畳するが、必ずしもこれに限定されない。導電層605b(c)を領域604b(c)の一部に重畳させることにより、導電層605b(c)及び領域604b(c)の間の抵抗を小さくすることができる。また、導電層605b(c)に重畳する半導体層603(c)の領域の全てが領域604b(c)でもよい。

【0154】

絶縁層602(c)は、半導体層603(c)、導電層605a(c)、及び導電層605b(c)の上に設けられる。

【0155】

導電層601(c)は、絶縁層602(c)を介して半導体層603(c)に重畳する。絶縁層602(c)を介して導電層601(c)と重畳する半導体層603(c)の領域がチャネル形成領域になる。

【0156】

また、図6(D)に示すトランジスタは、導電層601(d)と、絶縁層602(d)と、半導体層603(d)と、導電層605a(d)と、導電層605b(d)と、を含む。

【0157】

導電層605a(d)及び導電層605b(d)は、被素子形成層600(d)の上に設けられる。また、導電層605a(d)及び導電層605b(d)の側面は、テーパ状である。

【0158】

半導体層603(d)は、領域604a(d)及び領域604b(d)と、を含む。領域604a(d)及び領域604b(d)は、互いに離間し、それぞれドーパントが添加された領域である。また、領域604a(d)及び領域604b(d)の間の領域がチャネル形成領域になる。半導体層603(d)は、例えば導電層605a(d)、導電層605b(d)、及び被素子形成層600(d)の上に設けられ、導電層605a(d)及び導電層605b(d)に電気的に接続される。なお、必ずしも領域604a(d)及び領域604b(d)を設けなくてもよい。

【0159】

領域604a(d)は、導電層605a(d)に電気的に接続される。

【0160】

領域604b(d)は、導電層605b(d)に電気的に接続される。

【0161】

絶縁層602(d)は、半導体層603(d)の上に設けられる。

【0162】

導電層601(d)は、絶縁層602(d)を介して半導体層603(d)に重畳する。絶縁層602(d)を介して導電層601(d)と重畳する半導体層603(d)の領域がチャネル形成領域になる。

【0163】

以下では、図6(A)乃至図6(D)に示す各構成要素について説明する。

【0164】

被素子形成層600(a)乃至被素子形成層600(d)としては、例えば絶縁層、又は絶縁表面を有する基板などを用いることができる。また、予め素子が形成された層を被素子形成層600(a)乃至被素子形成層600(d)として用いることもできる。

【0165】

導電層601(a)乃至導電層601(d)のそれぞれは、トランジスタのゲートとしての機能を有する。なお、トランジスタのゲートとしての機能を有する層をゲート電極又はゲート配線ともいう。

【0166】

導電層601(a)乃至導電層601(d)としては、例えばモリブデン、マグネシウム、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、導電層601(a)乃至導電層601(d)の形成に適用可能な材料の層の積層により、導電層601(a)乃至導電層601(d)を構成することもできる。

【0167】

絶縁層602(a)乃至絶縁層602(d)のそれぞれは、トランジスタのゲート絶縁層としての機能を有する。

【0168】

絶縁層602(a)乃至絶縁層602(d)としては、例えば酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、酸化ハフニウム層、又は酸化ランタン層を用いることができる。また、絶縁層602(a)乃至絶縁層602(d)に適用可能な材料の層の積層により絶縁層602(a)乃至絶縁層602(d)を構成することもできる。

【0169】

また、絶縁層602(a)乃至絶縁層602(d)としては、例えば元素周期表における第13族元素及び酸素元素を含む材料の絶縁層を用いることもできる。例えば、半導体層603(a)乃至半導体層603(d)が第13族元素を含む場合に、半導体層603(a)乃至半導体層603(d)に接する絶縁層として第13族元素を含む絶縁層を用いることにより、該絶縁層と酸化物半導体層との界面の状態を良好にすることができる。

【0170】

第13族元素及び酸素元素を含む材料としては、例えば酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどが挙げられる。なお、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多い物質のことをいい、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)がアルミニウムの含有量(原子%)以上の物質のことをいう。例えば、Al2Ox(x=3+α、αは0より大きく1より小さい値)、Ga2Ox(x=3+α、αは0より大きく1より小さい値)、又はGaxAl2−xO3+α(xは0より大きく2より小さい値、αは0より大きく1より小さい値)で表記される材料を用いることもできる。

【0171】

また、絶縁層602(a)乃至絶縁層602(d)に適用可能な材料の層の積層により絶縁層602(a)乃至絶縁層602(d)を構成することもできる。例えば、複数のGa2Oxで表記される酸化ガリウムを含む層の積層により絶縁層602(a)乃至絶縁層602(d)を構成してもよい。また、Ga2Oxで表記される酸化ガリウムを含む絶縁層及びAl2Oxで表記される酸化アルミニウムを含む絶縁層の積層により絶縁層602(a)乃至絶縁層602(d)を構成してもよい。

【0172】

半導体層603(a)乃至半導体層603(d)のそれぞれは、トランジスタのチャネルが形成される層としての機能を有する。半導体層603(a)乃至半導体層603(d)に適用可能な酸化物半導体としては、例えば四元系金属酸化物、三元系金属酸化物、又は二元系金属酸化物などを含む金属酸化物を用いることができる。

【0173】

用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0174】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0175】

四元系金属酸化物としては、例えばIn−Sn−Ga−Zn−O系酸化物、In−Sn−Al−Zn―O系酸化物、In−Sn−Hf−Zn―O系酸化物、またはIn−Hf−Al−Zn―O系酸化物などを用いることができる。

【0176】

三元系金属酸化物としては、例えばIn−Ga−Zn−O系酸化物、In−Sn−Zn−O系酸化物、In−Al−Zn−O系酸化物、Sn−Ga−Zn−O系酸化物、Al−Ga−Zn−O系酸化物、Sn−Al−Zn−O系酸化物、In−Hf−Zn−O系酸化物、In−La−Zn−O系酸化物、In−Ce−Zn−O系酸化物、In−Pr−Zn−O系酸化物、In−Nd−Zn−O系酸化物、In−Sm−Zn−O系酸化物、In−Eu−Zn−O系酸化物、In−Gd−Zn−O系酸化物、In−Tb−Zn−O系酸化物、In−Dy−Zn−O系酸化物、In−Ho−Zn−O系酸化物、In−Er−Zn−O系酸化物、In−Tm−Zn−O系酸化物、In−Yb−Zn−O系酸化物、又はIn−Lu−Zn−O系酸化物などを用いることができる。

【0177】

二元系金属酸化物としては、例えばIn−Zn−O系酸化物、Sn−Zn−O系酸化物、Al−Zn−O系酸化物、Zn−Mg−O系酸化物、Sn−Mg−O系酸化物、In−Mg−O系酸化物、In−Sn−O系酸化物、又はIn−Ga−O系酸化物などを用いることができる。

【0178】

また、酸化物半導体としては、例えばIn−O系酸化物、Sn−O系酸化物、又はZn−O系酸化物などを用いることもできる。また、上記酸化物半導体として適用可能な金属酸化物は、酸化シリコンを含んでいてもよい。

【0179】

酸化物半導体層には、例えば、In:Ga:Zn=1:1:1あるいはIn:Ga:Zn=2:2:1の原子比のIn−Ga−Zn−O系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1、In:Sn:Zn=2:1:3あるいはIn:Sn:Zn=2:1:5の原子比のIn−Sn−Zn−O系酸化物やその組成の近傍の酸化物を用いるとよい。

【0180】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0181】

また、酸化物半導体としては、InLO3(ZnO)m(mは0より大きい数)で表記される材料を用いることもできる。InLO3(ZnO)mのLは、Ga、Al、Mn、及びCoから選ばれた一つ又は複数の金属元素を示す。

【0182】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0183】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0184】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0185】

また、半導体層603(a)乃至半導体層603(d)の少なくともチャネルが形成される領域は、結晶性を有し、非単結晶であって、ab面に垂直な方向から見て、三角形、六角形、正三角形、又は正六角形の原子配列を有し、且つ、c軸方向に垂直な方向から見て金属原子が層状に配列した相、又はc軸方向に垂直な方向から見て金属原子と酸素原子が層状に配列した相を有してもよい。上記相を有する材料をCAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)ともいう。

【0186】

また、結晶性を有する酸化物半導体を用いたトランジスタは、トランジスタのストレス劣化(ゲートバイアスストレスなどによる劣化)や、可視光や紫外光の照射よるトランジスタの電気的特性変化が抑制され、信頼性の高いトランジスタとすることができる。

【0187】

また、トランジスタのチャネル長を30nmとしたとき、半導体層603(a)乃至半導体層603(d)の厚さを例えば5nm程度にしてもよい。このとき、半導体層603(a)乃至半導体層603(d)がCAAC−OS膜からなる酸化物半導体層であれば、トランジスタにおける短チャネル効果を抑制することができる。

【0188】

なお、CAAC−OS膜については、実施の形態5で詳細に説明する。

【0189】

領域604a(c)、領域604b(c)、領域604a(d)、及び領域604b(d)は、n型又はp型の導電型を付与するドーパントが添加され、トランジスタのソース又はドレインとしての機能を有する。ドーパントとしては、例えば元素周期表における13族の元素(例えば硼素など)、元素周期表における15族の元素(例えば窒素、リン、又は砒素など)の一つ又は複数を用いることができる。なお、トランジスタのソースとしての機能を有する領域をソース領域ともいい、トランジスタのドレインとしての機能を有する領域をドレイン領域ともいう。領域604a(c)、領域604b(c)、領域604a(d)、及び領域604b(d)にドーパントを添加することにより導電層との接続抵抗を小さくすることができるため、トランジスタを微細化することができる。

【0190】

導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)のそれぞれは、トランジスタのソース又はドレインとしての機能を有する。なお、トランジスタのソースとしての機能を有する層をソース電極又はソース配線ともいい、トランジスタのドレインとしての機能を有する層をドレイン電極又はドレイン配線ともいう。

【0191】

導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)としては、例えばアルミニウム、マグネシウム、クロム、銅、タンタル、チタン、モリブデン、若しくはタングステンなどの金属材料、又はこれらの金属材料を主成分とする合金材料の層を用いることができる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層により、導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)を構成することができる。また、導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)に適用可能な材料の層の積層により、導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)を構成することもできる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層と銅を含む層の積層により、導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)を構成することができる。

【0192】

また、導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)としては、導電性の金属酸化物を含む層を用いることもできる。導電性の金属酸化物としては、例えば酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ、又は酸化インジウム酸化亜鉛を用いることができる。なお、導電層605a(a)乃至導電層605a(d)、及び導電層605b(a)乃至導電層605b(d)に適用可能な導電性の金属酸化物は、酸化シリコンを含んでいてもよい。

【0193】

絶縁層606(a)及び絶縁層606(b)としては、絶縁層602(a)乃至絶縁層602(d)に適用可能な材料の層を用いることができる。また、絶縁層606(a)及び絶縁層606(b)に適用可能な材料の積層により、絶縁層606(a)及び絶縁層606(b)を構成してもよい。例えば、酸化シリコン層、酸化アルミニウム層などにより絶縁層606(a)及び絶縁層606(b)を構成してもよい。例えば、酸化アルミニウム層を用いることにより、半導体層603(a)及び半導体層603(b)への不純物の侵入抑制効果をより高めることができ、また、半導体層603(a)及び半導体層603(b)中の酸素の脱離抑制効果を高めることができる。

【0194】

導電層608(a)及び導電層608(b)のそれぞれは、トランジスタのゲートとしての機能を有する。なお、トランジスタが導電層601(a)及び導電層608(a)の両方、又は導電層601(b)及び導電層608(b)の両方を含む構造である場合、導電層601(a)及び導電層608(a)の一方、又は導電層601(b)及び導電層608(b)の一方を、バックゲート、バックゲート電極、又はバックゲート配線ともいう。ゲートとしての機能を有する導電層を、チャネル形成層を介して複数設けることにより、トランジスタの閾値電圧を制御しやすくすることができる。

【0195】

導電層608(a)及び導電層608(b)としては、例えば導電層601(a)乃至導電層601(d)に適用可能な材料の層を用いることができる。また、導電層608(a)及び導電層608(b)に適用可能な材料の層の積層により導電層608(a)及び導電層608(b)を構成してもよい。

【0196】

なお、本実施の形態のトランジスタを、チャネル形成層としての機能を有する酸化物半導体層の一部の上に絶縁層を含み、該絶縁層を介して酸化物半導体層に重畳するように、ソース又はドレインとしての機能を有する導電層を含む構造としてもよい。上記構造である場合、絶縁層は、トランジスタのチャネル形成層を保護する層(チャネル保護層ともいう)としての機能を有する。チャネル保護層としての機能を有する絶縁層としては、例えば絶縁層602(a)乃至絶縁層602(d)に適用可能な材料の層を用いることができる。また、絶縁層602(a)乃至絶縁層602(d)に適用可能な材料の積層によりチャネル保護層としての機能を有する絶縁層を構成してもよい。

【0197】

また、被素子形成層600(a)乃至被素子形成層600(d)の上に下地層を形成し、該下地層の上にトランジスタを形成してもよい。このとき、下地層としては、例えば絶縁層602(a)乃至絶縁層602(d)に適用可能な材料の層を用いることができる。また、絶縁層602(a)乃至絶縁層602(d)に適用可能な材料の積層により下地層を構成してもよい。例えば、酸化アルミニウム層及び酸化シリコン層の積層により下地層を構成することにより、下地層に含まれる酸素が半導体層603(a)乃至半導体層603(d)を介して脱離するのを抑制することができる。

【0198】

続いて、以下では本実施の形態におけるトランジスタの作製方法例として、図6(A)に示すトランジスタの作製方法例について、図7を用いて説明する。図7は、図6(A)に示すトランジスタの作製方法例を説明するための断面模式図である。

【0199】

まず、図7(A)に示すように、被素子形成層600(a)を準備し、被素子形成層600(a)の上に第1の導電膜を形成し、第1の導電膜の一部をエッチングすることにより導電層601(a)を形成する。

【0200】

例えば、スパッタリング法を用いて導電層601(a)に適用可能な材料の膜を形成することにより第1の導電膜を形成することができる。また、第1の導電膜に適用可能な材料の膜を積層させ、第1の導電膜を形成することもできる。

【0201】

なお、スパッタリングガスとして、例えば水素、水、水酸基、又は水素化物などの不純物が除去された高純度ガスを用いることにより、形成される膜の上記不純物濃度を低減することができる。

【0202】

なお、スパッタリング法を用いて膜を形成する前に、スパッタリング装置の予備加熱室において予備加熱処理を行ってもよい。上記予備加熱処理を行うことにより、水素、水分などの不純物を脱離することができる。

【0203】

また、スパッタリング法を用いて膜を形成する前に、例えばアルゴン、窒素、ヘリウム、又は酸素雰囲気下で、ターゲット側に電圧を印加せずに、基板側にRF電源を用いて電圧を印加し、プラズマを形成して被形成面を改質する処理(逆スパッタともいう)を行ってもよい。逆スパッタを行うことにより、被形成面に付着している粉状物質(パーティクル、ごみともいう)を除去することができる。

【0204】

また、スパッタリング法を用いて膜を形成する場合、吸着型の真空ポンプなどを用いて、膜を形成する成膜室内の残留水分を除去することができる。吸着型の真空ポンプとしては、例えばクライオポンプ、イオンポンプ、又はチタンサブリメーションポンプなどを用いることができる。また、コールドトラップを設けたターボ分子ポンプを用いて成膜室内の残留水分を除去することもできる。上記真空ポンプを用いることにより、不純物を含む排気の逆流を低減することができる。

【0205】

また、上記導電層601(a)の形成方法のように、本実施の形態におけるトランジスタの作製方法例において、膜の一部をエッチングして層を形成する場合、例えば、フォトリソグラフィ工程により膜の一部の上にレジストマスクを形成し、レジストマスクを用いて膜をエッチングすることにより、層を形成することができる。なお、この場合、層の形成後にレジストマスクを除去する。

【0206】

また、インクジェット法を用いてレジストマスクを形成してもよい。インクジェット法を用いることにより、フォトマスクが不要になるため、製造コストを低減することができる。また、透過率の異なる複数の領域を有する露光マスク(多階調マスクともいう)を用いてレジストマスクを形成してもよい。多階調マスクを用いることにより、異なる厚さの領域を有するレジストマスクを形成することができ、トランジスタの作製に使用するレジストマスクの数を低減することができる。

【0207】

次に、図7(B)に示すように、導電層601(a)の上に第1の絶縁膜を形成することにより絶縁層602(a)を形成する。

【0208】

例えば、スパッタリング法やプラズマCVD法などを用いて絶縁層602(a)に適用可能な材料の膜を形成することにより第1の絶縁膜を形成することができる。また、絶縁層602(a)に適用可能な材料の膜を積層させることにより第1の絶縁膜を形成することもできる。また、高密度プラズマCVD法(例えばμ波(例えば、周波数2.45GHzのμ波)を用いた高密度プラズマCVD法)を用いて絶縁層602(a)に適用可能な材料の膜を形成することにより、絶縁層602(a)を緻密にすることができ、絶縁層602(a)の絶縁耐圧を向上させることができる。

【0209】

次に、図7(C)に示すように、絶縁層602(a)の上に酸化物半導体膜を形成し、その後酸化物半導体膜の一部をエッチングすることにより半導体層603(a)を形成する。酸化物半導体膜はスパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて形成する。

【0210】

例えば、スパッタリング法を用いて半導体層603(a)に適用可能な酸化物半導体材料の膜を形成することにより酸化物半導体膜を形成することができる。なお、希ガス雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で酸化物半導体膜を形成してもよく、好ましくは酸素ガス雰囲気下で形成する。また、形成時の基板加熱温度を100℃以上600℃以下、好ましくは150℃以上550℃以下、さらに好ましくは200℃以上500℃以下とし、酸化物半導体膜の厚さは、1nm以上40nm以下、好ましくは3nm以上20nm以下とする。このとき、スパッタリング装置内の水素又は水などの不純物の濃度が極めて低いことが好ましい。例えば、酸化物半導体膜の形成前に熱処理を行うことにより、スパッタリング装置内の水素又は水などの不純物の濃度を低くすることができる。また、形成時の基板加熱温度が高いほど、得られる酸化物半導体膜の不純物濃度は低くなる。さらに、形成時の基板加熱温度によって酸化物半導体膜中の原子配列が整い、高密度化され、多結晶またはCAAC−OSが膜表面だけではなく膜全体に形成されやすくなる。また、酸素ガス雰囲気で成膜することでも、希ガスなどの余分な原子が含まれないため、多結晶またはCAAC−OSが形成されやすくなる。ただし、酸素ガスと希ガスの混合雰囲気とする場合は酸素ガスの割合は30体積%以上、好ましくは50体積%以上、さらに好ましくは80体積%以上とする。なお、酸化物半導体膜は薄いほど、トランジスタの短チャネル効果が低減される。ただし、薄くしすぎると界面散乱の影響が強くなり、電界効果移動度の低下が起こることがある。

【0211】

また、酸化物半導体膜をスパッタリング法により形成する際、絶縁層602(a)は平坦であることが好ましい。例えば、絶縁層602(a)の平均面粗さは、0.5nm未満、さらには0.1nm以下であることが好ましい。

【0212】

また、スパッタリングターゲットとして、例えば、ターゲット中の金属元素の原子数比がIn:Zn=50:1乃至In:Zn=1:2(モル数比に換算するとIn2O3:ZnO=25:1乃至In2O3:ZnO=1:4)、好ましくはIn:Zn=20:1乃至In:Zn=1:1(モル数比に換算するとIn2O3:ZnO=10:1乃至In2O3:ZnO=1:2)、さらに好ましくはIn:Zn=15:1乃至In:Zn=1.5:1(モル数比に換算するとIn2O3:ZnO=15:2乃至In2O3:ZnO=3:4)である酸化物ターゲットを用いて酸化物半導体膜を形成することができる。例えば、In−Zn−O系酸化物半導体の形成に用いるターゲットは、原子数比がIn:Zn:O=S:U:Rのとき、R>1.5S+Uとする。Inの量を多くすることにより、トランジスタの移動度を向上させることができる。

【0213】

また、In−Sn−Zn−O系の材料膜を、スパッタリング法によって形成する場合に用いる酸化物半導体のターゲット中の金属元素の原子数比は、In:Sn:Znが1:1:1、2:1:3、1:2:2、または4:9:7などを用いることができる。前述の原子数比を有するIn−Sn−Zn−Oターゲットを用いて酸化物半導体膜を形成することで、多結晶またはCAAC−OSが形成されやすくなる。

【0214】

また、In−Ga−Zn−O系の材料膜を、スパッタリング法によって形成する場合に用いる酸化物半導体のターゲット中の金属元素の原子数比は、In:Ga:Znが1:1:1、4:2:3、3:1:2、1:1:2、2:1:3、または3:1:4などを用いることができる。前述の原子数比を有するIn−Ga−Zn−Oターゲットを用いて酸化物半導体膜を形成することで、多結晶またはCAAC−OSが形成されやすくなる。

【0215】

次に、図7(D)に示すように、絶縁層602(a)及び半導体層603(a)の上に第2の導電膜を形成し、第2の導電膜の一部をエッチングすることにより導電層605a(a)及び導電層605b(a)を形成する。

【0216】

例えば、スパッタリング法などを用いて導電層605a(a)及び導電層605b(a)に適用可能な材料の膜を形成することにより第2の導電膜を形成することができる。また、導電層605a(a)及び導電層605b(a)に適用可能な材料の膜を積層させることにより第2の導電膜を形成することもできる。

【0217】

次に、図7(E)に示すように、半導体層603(a)に接するように絶縁層606(a)を形成する。

【0218】

例えば、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で、スパッタリング法を用いて絶縁層606(a)に適用可能な膜を形成することにより、絶縁層606(a)を形成することができる。スパッタリング法を用いて絶縁層606(a)を形成することにより、トランジスタのバックチャネルとしての機能を有する半導体層603(a)の部分における抵抗の低下を抑制することができる。また、絶縁層606(a)を形成する際の基板温度は、室温以上300℃以下であることが好ましい。

【0219】

また、絶縁層606(a)を形成する前にN2O、N2、又はArなどのガスを用いたプラズマ処理を行い、露出している半導体層603(a)の表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、その後、大気に触れることなく、絶縁層606(a)を形成することが好ましい。

【0220】

さらに、図6(A)に示すトランジスタの作製方法の一例では、例えば600℃以上750℃以下、又は600℃以上基板の歪み点未満の温度で加熱処理を行う。例えば、酸化物半導体膜を形成した後、酸化物半導体膜の一部をエッチングした後、第2の導電膜を形成した後、第2の導電膜の一部をエッチングした後、又は絶縁層606(a)を形成した後に上記加熱処理を行う。加熱処理は、減圧雰囲気、不活性雰囲気または酸化性雰囲気で行う。酸化物半導体膜が露出した状態で加熱処理を行う場合は特に、酸化物半導体膜中の不純物濃度を低減することができる。

【0221】

また上述した加熱処理は、減圧雰囲気または不活性雰囲気で加熱処理を行った後、温度を保持しつつ酸化性雰囲気に切り替えてさらに加熱処理を行うと好ましい。これは、減圧雰囲気または不活性雰囲気にて加熱処理を行うと、酸化物半導体膜中の不純物濃度を低減することができるが、同時に酸素欠損も生じてしまうためであり、このとき生じた酸素欠損を、酸化性雰囲気での加熱処理により低減することができる。

【0222】

酸化物半導体膜は、成膜時の基板加熱に加え、加熱処理を行うことで、膜中の不純物準位を極めて小さくすることが可能となる。その結果、トランジスタの電界効果移動度を後述する理想的な電界効果移動度近くまで高めることが可能となる。

【0223】

なお、上記加熱処理を行う加熱処理装置としては、電気炉、又は抵抗発熱体などの発熱体からの熱伝導又は熱輻射により被処理物を加熱する装置を用いることができ、例えばGRTA(Gas Rapid Thermal Anneal)装置又はLRTA(Lamp Rapid Thermal Anneal)装置などのRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、例えばハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、又は高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。また、GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスとしては、例えば希ガス、又は加熱処理によって被処理物と反応しない不活性気体(例えば窒素)を用いることができる。

【0224】

また、上記加熱処理を行った後、該加熱処理を行った炉と同じ炉に高純度の酸素ガス、高純度のN2Oガス、又は超乾燥エア(露点が−40℃以下、好ましくは−60℃以下の雰囲気)を導入してもよい。このとき、酸素ガス又はN2Oガスは、水、水素などを含まないことが好ましい。また、加熱処理装置に導入する酸素ガス又はN2Oガスの純度を、6N以上、好ましくは7N以上、すなわち、酸素ガス又はN2Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下とすることが好ましい。酸素ガス又はN2Oガスの作用により、半導体層603(a)に酸素が供給され、半導体層603(a)中の酸素欠乏に起因する欠陥を低減することができる。なお、上記高純度の酸素ガス、高純度のN2Oガス、又は超乾燥エアの導入は、上記加熱処理時に行ってもよい。

【0225】

また、絶縁層602(a)形成後、酸化物半導体膜形成後、ソース電極又はドレイン電極となる導電層形成後、ソース電極又はドレイン電極となる導電層の上の絶縁層形成後、又は加熱処理後に酸素プラズマによる酸素ドーピング処理を行ってもよい。例えば2.45GHzの高密度プラズマにより酸素ドーピング処理を行ってもよい。また、イオン注入法を用いて酸素ドーピング処理を行ってもよい。酸素ドーピング処理を行うことにより、作製されるトランジスタの電気特性のばらつきを低減することができる。例えば、酸素ドーピング処理を行い、絶縁層602(a)及び絶縁層606(a)の一方又は両方を、化学量論的組成比より酸素が多い状態にする。

【0226】

半導体層603(a)に接する絶縁層中の酸素を過剰にすることにより、半導体層603(a)に供給されやすくなる。よって、半導体層603(a)中、又は絶縁層602(a)及び絶縁層606(a)の一方又は両方と、半導体層603(a)との界面における酸素欠陥を低減することができるため、半導体層603(a)のキャリア濃度をより低減することができる。また、これに限定されず、製造過程により半導体層603(a)に含まれる酸素を過剰にした場合であっても、半導体層603(a)に接する上記絶縁層により、半導体層603(a)からの酸素の脱離を抑制することができる。

【0227】

例えば、絶縁層602(a)及び絶縁層606(a)の一方又は両方として、酸化ガリウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化ガリウムの組成をGa2Oxにすることができる。

【0228】

また、絶縁層602(a)及び絶縁層606(a)の一方又は両方として、酸化アルミニウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化アルミニウムの組成をAl2Oxにすることができる。

【0229】

また、絶縁層602(a)及び絶縁層606(a)の一方又は両方として、酸化ガリウムアルミニウム又は酸化アルミニウムガリウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化ガリウムアルミニウム又は酸化アルミニウムガリウムの組成をGaxAl2−xO3+αとすることができる。

【0230】

以上の工程により、半導体層603(a)から、水素、水、水酸基、又は水素化物(水素化合物ともいう)などの不純物を排除し、且つ半導体層603(a)に酸素を供給することにより、酸化物半導体層を高純度化させることができる。

【0231】

さらに、上記加熱処理とは別に、絶縁層606(a)を形成した後に、不活性ガス雰囲気下、又は酸素ガス雰囲気下で加熱処理(好ましくは200℃以上600℃以下、例えば250℃以上350℃以下)を行ってもよい。

【0232】

さらに、図7(E)に示すように、絶縁層606(a)の上に第3の導電膜を形成し、第3の導電膜の一部をエッチングすることにより導電層608(a)を形成する。

【0233】

例えば、スパッタリング法を用いて導電層608(a)に適用可能な材料の膜を形成することにより第3の導電膜を形成することができる。また、第3の導電膜に適用可能な材料の膜を積層させ、第3の導電膜を形成することもできる。

【0234】

なお、図6(A)に示すトランジスタの作製方法例を示したが、これに限定されず、例えば図6(B)乃至図6(D)に示す各構成要素において、名称が図6(A)に示す各構成要素と同じであり且つ機能の少なくとも一部が図6(A)に示す各構成要素と同じであれば、図6(A)に示すトランジスタの作製方法例の説明を適宜援用することができる。

【0235】

また、図6(C)及び図6(D)に示すように、領域604a(c)及び領域604a(d)、又は領域604b(c)乃至領域604b(d)を形成する場合には、ゲートとしての機能を有する導電層が形成される側から半導体層にドーパントを添加することにより、ゲート絶縁層としての機能を有する絶縁層を介して自己整合で領域604a(c)及び領域604a(d)、及び領域604b(c)及び領域604b(d)を形成する。

【0236】

例えば、イオンドーピング装置又はイオン注入装置を用いてドーパントを添加することができる。

【0237】

図6及び図7を用いて説明したように、本実施の形態におけるトランジスタの一例は、ゲートとしての機能を有する導電層と、ゲート絶縁層としての機能を有する絶縁層と、ゲート絶縁層としての機能を有する絶縁層を介してゲートとしての機能を有する導電層に重畳し、チャネルが形成される酸化物半導体層と、酸化物半導体層に電気的に接続され、ソース及びドレインの一方としての機能を有する導電層と、酸化物半導体層に電気的に接続され、ソース及びドレインの他方としての機能を有する導電層と、を含む構造である。

【0238】

なお、酸化物半導体膜の形成後において、脱水化処理(脱水素化処理)を行い酸化物半導体膜から、水素、または水分を除去して不純物が極力含まれないように高純度化し、加酸素化処理によって同時に減少してしまった酸素を酸化物半導体に加える、または過剰な酸素を供給し酸化物半導体膜の酸素欠損を補填することが好ましい。また、本明細書等において、酸化物半導体膜に酸素を供給する場合を、加酸素化処理、または過酸素化処理と記す場合がある。

【0239】

このように、酸化物半導体膜は、脱水化処理(脱水素化処理)により、水素または水分が除去され、加酸素化処理により酸素欠損を補填することによって、電気的にi型(真性)化またはi型に限りなく近い酸化物半導体膜とすることができる。

【0240】

上記チャネルが形成される酸化物半導体層は、高純度化させることによりI型又は実質的にI型となった酸化物半導体層である。酸化物半導体層を高純度化させることにより、酸化物半導体層のキャリア濃度を1×1014/cm3未満、好ましくは1×1012/cm3未満、さらに好ましくは1×1011/cm3未満にすることができる。

【0241】

またこのように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層を備えるトランジスタは、極めて優れたオフ電流特性を実現できる。例えば、室温(25℃)でのチャネル幅1μmあたりのオフ電流を10aA/μm(1×10−17A/μm)以下にすること、さらにはチャネル幅1μmあたりのオフ電流を1aA/μm(1×10−18A/μm)以下、さらにはチャネル幅1μmあたりのオフ電流を10zA/μm(1×10−20A/μm)以下、さらにはチャネル幅1μmあたりのオフ電流を1zA/μm(1×10−21A/μm)以下、さらにはチャネル幅1μmあたりのオフ電流を100yA/μm(1×10−22A/μm)以下にすることができる。トランジスタのオフ電流は、低ければ低いほどよいが、本実施の形態におけるトランジスタのオフ電流の下限値は、約10−30A/μmであると見積もられる。

【0242】

本実施の形態の酸化物半導体層を含むトランジスタを、例えば上記実施の形態におけるメモリセル内のトランジスタに適用することにより、トランジスタのオフ状態におけるリーク電流を極めて低減することができ、データの保持期間を極めて長いものとすることができる。

【0243】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0244】

(実施の形態4)

本実施の形態では、上記実施の形態におけるメモリセルの構造例について説明する。

【0245】

本実施の形態におけるメモリセルは、チャネルが形成され、元素周期表における第14族の半導体(シリコンなど)を含有する半導体層を含むトランジスタと、チャネルが形成される酸化物半導体層を含むトランジスタを用いて構成される。このとき、チャネルが形成される酸化物半導体層を含むトランジスタは、元素周期表における第14族の半導体(シリコンなど)を含有する半導体層を含むトランジスタの上に積層させることができる。元素周期表における第14族の半導体(シリコンなど)を含有する半導体層を含むトランジスタは、例えば図4におけるトランジスタ271やインバータ273を構成するトランジスタに適用される。

【0246】

元素周期表における第14族の半導体(シリコンなど)を含有する半導体層を含むトランジスタの上にチャネルが形成される酸化物半導体層を含むトランジスタを積層する例について、図8に示す。なお、図8では、実際の寸法と異なる構成要素を含む。

【0247】

図8では、半導体層780と、絶縁層784aと、絶縁層784bと、導電層785aと、導電層785bと、絶縁層786aと、絶縁層786bと、絶縁層786cと、絶縁層786dと、絶縁層788と、半導体層753と、導電層754aと、導電層754bと、絶縁層755と、導電層756と、絶縁層757aと、絶縁層757bと、絶縁層758と、絶縁層759と、導電層760aと、導電層760bと、により元素周期表における第14族の半導体(シリコンなど)を含有する半導体層を含むpチャネル型トランジスタ及びnチャネル型トランジスタ(例えば図4に示すインバータ273などを構成するトランジスタに相当)とチャネルが形成される酸化物半導体層を含むトランジスタ(例えば図4に示すトランジスタ261に相当)が構成される。

【0248】

さらに、半導体層780は、領域782a、領域782b、領域782c、及び領域782dを有する。また、半導体層780は、絶縁領域781a乃至絶縁領域781cにより、各トランジスタが電気的に分離されている。

【0249】

半導体層780としては、例えば半導体基板を用いることができる。また、別の基板の上に設けられた半導体層を半導体層780として用いることもできる。

【0250】

領域782a及び領域782bは、互いに離間して設けられ、p型の導電型を付与するドーパントが添加された領域である。領域782a及び領域782bは、上記pチャネル型トランジスタのソース領域又はドレイン領域としての機能を有する。例えば、領域782a及び領域782bのそれぞれは、別途設けられた導電層に電気的に接続されてもよい。

【0251】

領域782c及び領域782dは、互いに離間して設けられ、n型の導電型を付与するドーパントが添加された領域である。領域782c及び領域782dは、上記nチャネル型トランジスタのソース領域又はドレイン領域としての機能を有する。例えば、領域782c及び領域782dのそれぞれは、別途設けられた導電層に電気的に接続されてもよい。

【0252】

なお、領域782a乃至領域782dの一部に低濃度領域を設けてもよい。このとき低濃度領域の深さは、それ以外の領域782a乃至領域782dの領域の深さより小さくてもよいが、これに限定されない。

【0253】

絶縁層784aは、絶縁領域781a及び絶縁領域781bに挟まれた半導体層780の領域の上に設けられる。絶縁層784aは、上記pチャネル型トランジスタのゲート絶縁層としての機能を有する。

【0254】

絶縁層784bは、絶縁領域781b及び絶縁領域781cに挟まれた半導体層780の領域の上に設けられる。絶縁層784bは、上記nチャネル型トランジスタのゲート絶縁層としての機能を有する。

【0255】

絶縁層784a及び絶縁層784bとしては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化ハフニウム、有機絶縁材料(例えばポリイミド又はアクリルなど)などの材料の層を用いることができる。また、絶縁層784a及び絶縁層784bに適用可能な材料の積層により絶縁層784a及び絶縁層784bを構成してもよい。

【0256】

導電層785aは、絶縁層784aを介して半導体層780に重畳する。導電層785aに重畳する半導体層780の領域が上記pチャネル型トランジスタのチャネル形成領域になる。導電層785aは、上記pチャネル型トランジスタのゲートとしての機能を有する。

【0257】

導電層785bは、絶縁層784bを介して半導体層780に重畳する。導電層785bに重畳する半導体層780の領域が上記nチャネル型トランジスタのチャネル形成領域になる。導電層785bは、上記nチャネル型トランジスタのゲートとしての機能を有する。

【0258】

導電層785a及び導電層785bとしては、例えばモリブデン、マグネシウム、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、導電層785a及び導電層785bに適用可能な材料の積層により、導電層785a及び導電層785bを構成することもできる。

【0259】

絶縁層786aは、絶縁層784aの上に設けられ、導電層785aにおける、互いに対向する一対の側面の一方に接する。

【0260】

絶縁層786bは、絶縁層784aの上に設けられ、導電層785aにおける、互いに対向する上記一対の側面の他方に接する。

【0261】

絶縁層786cは、絶縁層784bの上に設けられ、導電層785bにおける、互いに対向する一対の側面の一方に接する。

【0262】

絶縁層786dは、絶縁層784bの上に設けられ、導電層785bにおける、互いに対向する上記一対の側面の他方に接する。

【0263】

絶縁層788は、絶縁層786a、絶縁層786b、絶縁層786c、及び絶縁層786dの上に設けられる。

【0264】

絶縁層786a乃至絶縁層786d、及び絶縁層788としては、絶縁層784a及び絶縁層784bに適用可能な材料のうち、絶縁層784a及び絶縁層784bに適用した材料と同じ材料の層又は異なる材料の層を用いることができる。また、絶縁層786a乃至絶縁層786d、及び絶縁層788に適用可能な材料の積層により、絶縁層786a乃至絶縁層786d、及び絶縁層788を構成することもできる。

【0265】

半導体層753は、絶縁層788の上に設けられる。半導体層753は、領域752a及び領域752bを含む。領域752a及び領域752bはドーパントが添加された領域であり、ソース領域又はドレイン領域としての機能を有する。ドーパントとしては、上記実施の形態における酸化物半導体層を含むトランジスタに適用可能なドーパントを適宜用いることができる。なお、領域752a及び領域752bは必ずしも設けなくともよい。

【0266】

半導体層753としては、例えば図6(A)に示す半導体層603(a)に適用可能な材料の層を用いることができる。

【0267】

絶縁層755は、半導体層753の上に設けられる。また絶縁層755は、トランジスタのゲート絶縁層としての機能を有する。

【0268】

絶縁層755としては、例えば図6(A)に示す絶縁層602(a)に適用可能な材料の層を用いることができる。また、絶縁層755に適用可能な材料の積層により絶縁層755を構成してもよい。

【0269】

導電層756は、絶縁層755を介して半導体層753に重畳する。導電層756は、トランジスタのゲートとしての機能を有する。

【0270】

導電層756としては、例えば図6(A)に示す導電層601(a)に適用可能な材料の層を用いることができる。また、導電層756に適用可能な材料の積層により導電層756を構成してもよい。

【0271】

絶縁層757a及び絶縁層757bは、導電層756の側面に接して絶縁層755の上に設けられる。なお、絶縁層757a及び絶縁層757bは必ずしも設けなくてもよい。

【0272】

導電層754aは、半導体層753に接して電気的に接続される。また、導電層754aは、導電層785aに電気的に接続される。導電層754aは、上記酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

【0273】

導電層754bは、半導体層753に接して電気的に接続される。導電層754bは、上記酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

【0274】

導電層754a及び導電層754bとしては、例えば図6(A)に示す導電層605a(a)及び導電層605b(a)に適用可能な材料の層を用いることができる。また、導電層754a及び導電層754bに適用可能な材料の積層により導電層754a及び導電層754bを構成してもよい。

【0275】

絶縁層758は、導電層756、絶縁層757a、絶縁層757b、導電層754a、及び導電層754bの上に設けられる。

【0276】

絶縁層758としては、例えば図6(A)に示す絶縁層602(a)に適用可能な材料の層を用いることができる。また、絶縁層758に適用可能な材料の積層により絶縁層758を構成してもよい。絶縁層758は、不純物の侵入を抑制する保護層としての機能を有する。

【0277】

絶縁層759は、絶縁層758の上に設けられる。

【0278】

絶縁層759としては、例えば図6(A)に示す絶縁層602(a)に適用可能な材料の層を用いることができる。また、絶縁層759に適用可能な材料の積層により絶縁層759を構成してもよい。

【0279】

導電層760aは、絶縁層758及び絶縁層759に設けられた開口部を介して導電層754aに電気的に接続される。導電層760aは、酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

【0280】

導電層760bは、絶縁層758及び絶縁層759に設けられた開口部を介して導電層754bに電気的に接続される。導電層760bは、酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

【0281】

導電層760a及び導電層760bとしては、例えば図6(A)に示す導電層605a(a)及び導電層605b(a)に適用可能な材料の層を用いることができる。また、導電層760a及び導電層760bに適用可能な材料の積層により導電層760a及び導電層760bを構成してもよい。

【0282】

なお、ここでは容量素子281及び容量素子291については明瞭化のため図示していないが、上記nチャネル型のトランジスタ、pチャネル型のトランジスタ、及び酸化物半導体層を含むトランジスタを構成する導電層又はドーパントが添加された半導体層のいずれか2つと、その間に挟持されるいずれかの絶縁層によって形成すればよい。また、酸化物半導体層を含むトランジスタの上方に積層して形成してもよい。

【0283】

以上が図8に示すメモリセルの構造例の説明である。

【0284】

図8を用いて説明したように、本実施の形態におけるメモリセルの構造例では、異なる材料の半導体層を用いたトランジスタを積層させてメモリセルを構成することにより、回路面積を小さくすることができる。

【0285】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0286】

(実施の形態5)

本実施の形態では、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶を含む酸化物半導体(CAAC−OS:C Axis Aligned Crystalline Oxide Semiconductorともいう。)について説明する。

【0287】

CAAC−OSとは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

【0288】

CAAC−OSは単結晶ではないが、非晶質のみから形成されているものでもない。CAAC−OS膜は、非晶質相に結晶部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0289】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0290】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0291】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0292】

CAAC−OSを構成する酸素の一部は窒素で置換されてもよい。また、CAAC−OSを構成する個々の結晶部分のc軸は一定の方向(例えば、CAAC−OSが形成される基板面、CAAC−OSの表面などに垂直な方向)に揃っていてもよい。または、CAAC−OSを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAAC−OSが形成される基板面、CAAC−OSの表面などに垂直な方向)を向いていてもよい。

【0293】

CAAC−OSは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0294】

このようなCAAC−OSの例として、膜状に形成され、膜表面または形成される基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子(または窒素原子)の層状配列が認められる酸化物を挙げることもできる。

【0295】

CAAC−OSに含まれる結晶構造の一例について図9乃至図12を用いて詳細に説明する。なお、特に断りがない限り、図9乃至図12は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図9において丸で囲まれたOは4配位のOを示し、二重丸は3配位のOを示す。

【0296】

図9(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図9(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図9(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図9(A)に示す小グループは電荷が0である。

【0297】

図9(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図9(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図9(B)に示す構造をとりうる。図9(B)に示す小グループは電荷が0である。

【0298】

図9(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図9(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図9(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあってもよい。図9(C)に示す小グループは電荷が0である。

【0299】

図9(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図9(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図9(D)に示す小グループは電荷が+1となる。

【0300】

図9(E)に、2個のZnを含む小グループを示す。図9(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図9(E)に示す小グループは電荷が−1となる。

【0301】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0302】

ここで、これらの小グループ同士が結合する規則について説明する。図9(A)に示す6配位のInの上半分の3個のOは、下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。図9(B)に示す5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。図9(C)に示す4配位のZnの上半分の1個のOは、下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)、4配位の金属原子(Zn)のいずれかと結合することになる。

【0303】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0304】

図10(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図10(B)に、3つの中グループで構成される大グループを示す。なお、図10(C)は、図10(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0305】

図10(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図10(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図10(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0306】

図10(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0307】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図9(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0308】

具体的には、図10(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0309】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物(IGZOとも表記する。)、In−Al−Zn−O系酸化物、Sn−Ga−Zn−O系酸化物、Al−Ga−Zn−O系酸化物、Sn−Al−Zn−O系酸化物や、In−Hf−Zn−O系酸化物、In−La−Zn−O系酸化物、In−Ce−Zn−O系酸化物、In−Pr−Zn−O系酸化物、In−Nd−Zn−O系酸化物、In−Sm−Zn−O系酸化物、In−Eu−Zn−O系酸化物、In−Gd−Zn−O系酸化物、In−Tb−Zn−O系酸化物、In−Dy−Zn−O系酸化物、In−Ho−Zn−O系酸化物、In−Er−Zn−O系酸化物、In−Tm−Zn−O系酸化物、In−Yb−Zn−O系酸化物、In−Lu−Zn−O系酸化物や、二元系金属の酸化物であるIn−Zn−O系酸化物、Sn−Zn−O系酸化物、Al−Zn−O系酸化物、Zn−Mg−O系酸化物、Sn−Mg−O系酸化物、In−Mg−O系酸化物や、In−Ga−O系の材料などを用いた場合も同様である。

【0310】

例えば、図11(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0311】

図11(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0312】

図11(B)に3つの中グループで構成される大グループを示す。なお、図11(C)は、図11(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0313】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0314】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図11(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0315】

具体的には、図11(B)に示した大グループが繰り返されることで、In−Ga−Zn−O系の結晶を得ることができる。なお、得られるIn−Ga−Zn−O系の層構造は、InGaO3(ZnO)n(nは自然数。)とする組成式で表すことができる。

【0316】

n=1(InGaZnO4)の場合は、例えば、図12(A)に示す結晶構造を取りうる。なお、図12(A)に示す結晶構造において、図9(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0317】

また、n=2(InGaZn2O5)の場合は、例えば、図12(B)に示す結晶構造を取りうる。なお、図12(B)に示す結晶構造において、図9(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0318】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0319】

(実施の形態6)

本実施の形態では、上記実施の形態におけるキャッシュメモリを備えた電子機器の例について説明する。

【0320】

本実施の形態における電子機器の構成例について、図13(A)乃至図13(D)を用いて説明する。

【0321】

図13(A)に示す電子機器は、携帯型情報端末の例である。図13(A)に示す情報端末は、筐体1001aと、筐体1001aに設けられた表示部1002aと、を具備する。

【0322】

なお、筐体1001aの側面1003aに外部機器に接続させるための接続端子、及び図13(A)に示す携帯型情報端末を操作するためのボタンの一つ又は複数を設けてもよい。

【0323】

図13(A)に示す携帯型情報端末は、筐体1001aの中に、CPUと、記憶回路と、外部機器とCPU及び記憶回路との信号の送受信を行うインターフェースと、外部機器との信号の送受信を行うアンテナと、を備える。

【0324】

図13(A)に示す携帯型情報端末は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊技機の一つ又は複数としての機能を有する。

【0325】

図13(B)に示す電子機器は、折り畳み式の携帯型情報端末の例である。図13(B)に示す携帯型情報端末は、筐体1001bと、筐体1001bに設けられた表示部1002bと、筐体1004と、筐体1004に設けられた表示部1005と、筐体1001b及び筐体1004を接続する軸部1006と、を具備する。

【0326】

また、図13(B)に示す携帯型情報端末では、軸部1006により筐体1001b又は筐体1004を動かすことにより、筐体1001bを筐体1004に重畳させることができる。

【0327】

なお、筐体1001bの側面1003b又は筐体1004の側面1007に外部機器に接続させるための接続端子、及び図13(B)に示す携帯型情報端末を操作するためのボタンの一つ又は複数を設けてもよい。

【0328】

また、表示部1002b及び表示部1005に、互いに異なる画像又は一続きの画像を表示させてもよい。なお、表示部1005を必ずしも設けなくてもよく、表示部1005の代わりに、入力装置であるキーボードを設けてもよい。

【0329】

図13(B)に示す携帯型情報端末は、筐体1001b又は筐体1004の中に、CPUと、記憶回路と、外部機器とCPU及び記憶回路との信号の送受信を行うインターフェースと、を備える。なお、図13(B)に示す携帯型情報端末に、外部との信号の送受信を行うアンテナを設けてもよい。

【0330】

図13(B)に示す携帯型情報端末は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊技機の一つ又は複数としての機能を有する。

【0331】

図13(C)に示す電子機器は、設置型情報端末の例である。図13(C)に示す設置型情報端末は、筐体1001cと、筐体1001cに設けられた表示部1002cと、を具備する。

【0332】

なお、表示部1002cを、筐体1001cにおける甲板部1008に設けることもできる。

【0333】

また、図13(C)に示す設置型情報端末は、筐体1001cの中に、CPUと、記憶回路と、外部機器とCPU及び記憶回路との信号の送受信を行うインターフェースと、を備える。なお、図13(C)に示す設置型情報端末に、外部との信号の送受信を行うアンテナを設けてもよい。

【0334】

さらに、図13(C)に示す設置型情報端末における筐体1001cの側面1003cに券などを出力する券出力部、硬貨投入部、及び紙幣挿入部の一つ又は複数を設けてもよい。

【0335】

図13(C)に示す設置型情報端末は、例えば現金自動預け払い機、券などの注文をするための情報通信端末(マルチメディアステーションともいう)、又は遊技機としての機能を有する。

【0336】

図13(D)は、設置型情報端末の例である。図13(D)に示す設置型情報端末は、筐体1001dと、筐体1001dに設けられた表示部1002dと、を具備する。なお、筐体1001dを支持する支持台を設けてもよい。

【0337】

なお、筐体1001dの側面1003dに外部機器に接続させるための接続端子、及び図13(D)に示す設置型情報端末を操作するためのボタンの一つ又は複数を設けてもよい。

【0338】

また、図13(D)に示す設置型情報端末は、筐体1001dの中に、CPUと、記憶回路と、外部機器とCPU及び記憶回路との信号の送受信を行うインターフェースと、を備えてもよい。なお、図13(D)に示す設置型情報端末に、外部との信号の送受信を行うアンテナを設けてもよい。

【0339】

図13(D)に示す設置型情報端末は、例えばデジタルフォトフレーム、モニタ、又はテレビジョン装置としての機能を有する。

【0340】

上記実施の形態のキャッシュメモリは、図13(A)乃至図13(D)に示す電子機器のCPUに接続して用いられる。

【0341】

図13を用いて説明したように、本実施の形態における電子機器の一例は、キャッシュメモリとして上記実施の形態におけるキャッシュメモリを具備する構成である。

【0342】

上記構成にすることにより、低消費電力化が実現され、且つキャッシュヒット率が向上することによりCPUの動作速度が改善された電子機器とすることができる。

【0343】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0344】

100 キャッシュメモリ

101 制御部

103 比較回路

110 メモリセット

111 メモリアレイ

113 ライン

115 タグフィールド

117 データフィールド

119 駆動回路

150 メモリセル

151 第1格納部

153 第2格納部

155 データ転送部

160 CPU

161 制御部

162 演算部

170 メインメモリ

251 第1ゲート線

252 第2ゲート線

253 第3ゲート線

254 第4ゲート線

255 第1ビット線

256 第2ビット線

261 トランジスタ

262 トランジスタ

263 トランジスタ

265 ノード

266 ノード

267 ノード

268 ノード

271 トランジスタ

272 トランジスタ

273 インバータ

274 インバータ

281 容量素子

291 容量素子

292 インバータ

600 被素子形成層

601 導電層

602 絶縁層

603 半導体層

604a 領域

604b 領域

605a 導電層

605b 導電層

606 絶縁層

608 導電層

752a 領域

752b 領域

753 半導体層

754a 導電層

754b 導電層

755 絶縁層

756 導電層

757a 絶縁層

757b 絶縁層

758 絶縁層

759 絶縁層

760a 導電層

760b 導電層

780 半導体層

781a 絶縁領域

781b 絶縁領域

781c 絶縁領域

782a 領域

782b 領域

782c 領域

782d 領域

784a 絶縁層

784b 絶縁層

785a 導電層

785b 導電層

786a 絶縁層

786b 絶縁層

786c 絶縁層

786d 絶縁層

788 絶縁層

1001a 筐体

1001b 筐体

1001c 筐体

1001d 筐体

1002a 表示部

1002b 表示部

1002c 表示部

1002d 表示部

1003a 側面

1003b 側面

1003c 側面

1003d 側面

1004 筐体

1005 表示部

1006 軸部

1007 側面

1008 甲板部

【技術分野】

【0001】

本発明は、キャッシュメモリとその駆動方法に関する。

【背景技術】

【0002】

多くのCPU(Central Processing Unit:中央演算装置)には、一時的にデータを格納するキャッシュメモリが搭載される。キャッシュメモリは低速なメインメモリのデータの内容の一部をコピーして格納する、高速動作が可能なメモリである。キャッシュメモリにCPUが要求するデータが格納されていると、CPUは高速に演算処理を実行することができる。

【0003】

ここで、キャッシュメモリにCPUの要求するデータが格納されていることをキャッシュヒットといい、当該データが格納されていない場合をキャッシュミスという。キャッシュミスの場合は、低速なメインメモリにデータを要求する。

【0004】

キャッシュメモリの代表的な構成としては、フル連想方式、ダイレクトマップ方式、セット連想方式などがある。

【0005】

nウェイセット連想方式のキャッシュメモリは、n個のメモリセットを用いる。各メモリセットは一つの比較回路と、メインメモリのアドレスの下位ビットに対応してあらかじめ割り当てられたm行のラインを備える。各ラインは、メインメモリのアドレスの上位ビットを格納するタグフィールドと、当該アドレスに対応したデータが格納されるデータフィールドとを備える。またラインは、メモリセットにおいてデータを管理する単位とも呼ばれる。

【0006】

また、キャッシュメモリ内には当該キャッシュメモリの動作を制御する制御部が設けられる。当該制御部は、キャッシュメモリ内の特定のセットの特定のラインを選択し、当該ラインに格納されたデータを読み出す、又は当該ラインにデータを格納することができる。

【0007】

アドレスで特定される一のデータをキャッシュメモリに格納する方法を説明する。制御部はアドレスの下位ビットを参照し、それぞれのメモリセット毎に1つ割り当てられたライン(合計n行)のいずれかを、データの格納先の候補として選定する。

【0008】

キャッシュメモリの書き換えアルゴリズムとして、LRU(Least Recently Used)方式を用いる場合、上記n行のラインのうち、最も過去に使用されたラインを格納先として確定し、当該ラインに上記一のデータを上書きする。具体的には、タグフィールドにアドレスの上位ビットを格納し、データフィールドにメインメモリのコピーデータを格納する。

【0009】

次に、キャッシュメモリがデータを出力する方法を説明する。CPU(中央演算装置)がアドレスで特定されるデータをキャッシュメモリに設けられる制御部に要求すると、当該制御部によって、n個のメモリセットのそれぞれについて、当該アドレスの下位ビットに割り当てられたラインが選択される。次いで、それぞれのメモリセットに設けられた比較回路が、当該アドレスの上位ビットとタグフィールドに格納された上位ビットを比較し、一致する場合(キャッシュヒット)に、そのラインのデータフィールドに格納されたデータをCPUに出力する。一方、アドレスの上位ビットとタグフィールドに格納された上位ビットが、n行のライン全てにおいて一致しない場合(キャッシュミス)は、CPUはメインメモリにデータを要求する。

【0010】

また近年、トランジスタの構成材料として、高移動度と、均一な素子特性とを兼ね備えた酸化物半導体と呼ばれる、半導体特性を示す金属酸化物に注目が集まっている。金属酸化物は様々な用途に用いられている。例えば、酸化インジウムは、液晶表示装置において画素電極の材料として用いられている。半導体特性を示す金属酸化物としては、例えば、酸化タングステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物によってチャネルが形成されるトランジスタが、既に知られている(特許文献1及び特許文献2)。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2007−123861号公報

【特許文献2】特開2007−96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

上述のnウェイセット連想方式のキャッシュメモリは、キャッシュメモリの備えるメモリセットの数を大きくするほどキャッシュヒットする確率が高まり、CPUの処理速度を向上させることができる。一方、一度の読み出し動作でn個のセットの全てにおいて読み出し動作を行うところ、そのうちキャッシュヒットするセットは多くても1個であるため、残りのn−1個のセットの読み出しに要する電力は無駄になってしまう。

【0013】

また、1つのメモリセットには、必ず一つの比較回路が必要となるため、キャッシュメモリの備えるメモリセットの数を大きくすると、回路規模の増大を招いてしまう。

【0014】

本発明は、このような技術的背景でなされたものである。したがって本発明は、低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供することを課題とする。

【課題を解決するための手段】

【0015】

上記課題を達成するために、本発明はメモリセルの構成に着眼した。1ビットのデータを格納可能な1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つ外部へデータを出力可能な構成とする。

【0016】

より具体的には、第1格納部は、1ビットのデータを格納することができると共に、当該データを読み出しデータとして出力することができる。さらに第1格納部には、外部(例えばCPU)から入力されるデータを格納することができる。データ転送部は、第1格納部に格納されているデータを一時的に格納することができる。さらにデータ転送部は、格納したデータを第2格納部に転送することができる。第2格納部は、1ビットのデータを格納することができると共に、第1格納部にデータを転送することができる。

【0017】

このような構成とすることにより、本発明の一態様のメモリセルは、2種類のデータを格納可能で、且ついずれかのデータを第1格納部に格納することにより、当該データを読み出しデータとして出力することができる。

【0018】

すなわち、本発明の一態様のキャッシュメモリは、複数のメモリセルから構成されるラインを複数有するメモリセットと、メモリセットと対に設けられた比較回路と、制御部と、を有する。また、メモリセルのそれぞれは、第1格納部と、第2格納部と、データ転送部と、を有し、第1格納部は、制御部から入力される1ビットのデータを格納可能で、且つ、格納された1ビットのデータを比較回路に出力可能で、且つ、格納された1ビットのデータをデータ転送部に転送可能であり、またデータ転送部は、第1格納部から転送された1ビットのデータを格納可能で、且つ、格納された1ビットのデータを第2格納部に転送可能であり、第2格納部は、データ転送部から転送された1ビットのデータを格納可能で、且つ、格納された1ビットのデータを第1格納部に転送可能である。さらに、メモリセットは、制御部によって指定されるラインのいずれか1つを選択し、当該ラインを構成するメモリセルの第1格納部のそれぞれに制御部から入力される1ビットのデータを格納可能で、且つ、制御部によって指定されるラインのいずれか1つを選択し、当該ラインを構成するメモリセルの第1格納部のそれぞれから出力されるデータ群を比較回路に出力可能である。また、比較回路は、上記メモリセットから出力されたデータ群に含まれるアドレスデータと、CPUから入力されたアドレスデータとが一致するか否かを比較し、一致しない場合において、データ群を出力したラインを構成するメモリセルのそれぞれは、第2格納部に格納された1ビットのデータを第1格納部に転送すると共に、メモリセットはデータの転送が行われたメモリセルの第1格納部のそれぞれから出力されるデータ群を比較回路に出力する、キャッシュメモリである。

【0019】

本発明の一態様の上記キャッシュメモリは、1つの比較回路と対となるメモリセット内に、上述の2種類のデータを格納可能なメモリセルを有する。したがって、当該メモリセルから出力可能な2種類のデータは、1つの比較回路に送信される。そのため、比較回路を増やすことなく格納できるデータ容量を増大させることができる。

【0020】

また、最初に第1格納部に格納されていた第1のデータが読み出され、当該第1のデータが要求されるデータと一致しない場合に限り、第2格納部に格納されている第2のデータを第1格納部に転送し、再度読み出しを行う。したがって、最初に読み出される第1のデータが要求されるデータと一致した場合には読み出し動作を行わないため、従来のキャッシュメモリの構成に比べて読み出し動作を行う頻度を低減することが可能となり、結果として低消費電力動作が実現される。

【0021】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおいて、第1格納部とデータ転送部とは、第1トランジスタを介して接続され、データ転送部と第2格納部とは、第2トランジスタを介して接続され、第2格納部と第1格納部とは、第3トランジスタを介して接続される。さらに、第1トランジスタが、オン状態のときに第1格納部からデータ転送部へ1ビットのデータが転送され、オフ状態のときにデータ転送部は当該データを保持する。また、第2トランジスタが、オン状態のときにデータ転送部から第2格納部へ1ビットのデータが転送され、オフ状態のときに第2格納部は当該データを保持する。また、第3トランジスタが、オン状態のときに第2格納部から第1格納部へ1ビットのデータが転送されることを特徴とする。

【0022】

このように、キャッシュメモリ内のメモリセルの有する第1格納部と第2格納部とデータ転送部を、それぞれ1つのトランジスタを介して接続することにより、データの転送動作を簡便に行えるだけでなく、極めて単純な回路構成とすることができる。

【0023】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおいて、第1格納部は、2つのインバータが環状に接続されたインバータループを有し、データ転送部は、一方の電極が接地された第1容量素子を有し、第2格納部は、一方の電極が接地された第2容量素子を有する。また、第1格納部とデータ転送部とは、インバータループの一方のノードと、第1容量素子の他方の電極との間に、直列に接続される第1トランジスタを介して接続されている。またデータ転送部と第2格納部とは、第1容量素子の他方の電極と、第2容量素子の他方の電極との間に、直列に接続される第2トランジスタを介して接続されている。さらに、第2格納部と第1格納部とは、第2容量素子の他方の電極と、インバータループの他方のノードとの間に、直列に接続されるインバータと第3トランジスタを介して接続されている。ここで、第1トランジスタが、オン状態のときに第1格納部からデータ転送部へ1ビットのデータが転送され、オフ状態のときにデータ転送部は当該データを保持する。また、第2トランジスタが、オン状態のときにデータ転送部から第2格納部へ1ビットのデータが転送され、オフ状態のときに第2格納部は当該データを保持する。さらに、第3トランジスタが、オン状態のときに第2格納部から第1格納部へ1ビットのデータが転送されることを特徴とする。

【0024】

またこのように、第1格納部には2つのインバータで構成されるインバータループを適用することにより、データの入出力を行う第1格納部の動作を高速に行うことが出来るため、データの読み出し及び書き込みを高速に行えるキャッシュメモリとすることが出来る。また、第2格納部とデータ転送部をそれぞれ容量素子1つで構成することにより、メモリセルの回路構成を極めて簡略化することができる。

【0025】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおける、第1トランジスタ及び第2トランジスタは、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−18A以下であることを特徴とする。

【0026】

このように容量素子で構成されるデータ転送部と第2格納部とに直接接続されるトランジスタに、オフ状態におけるリーク電流が極めて低減されたトランジスタを用いることにより、データ転送部及び第2格納部に格納するデータを長い期間に渡って保持することが可能となる。

【0027】

このようなオフ状態におけるリーク電流が極めて低いトランジスタとしては、シリコンよりもバンドギャップの広い半導体をチャネルが形成される半導体層に用いた電界効果型のトランジスタが挙げられる。

【0028】

また、本発明の他の一態様のキャッシュメモリは、上記キャッシュメモリにおける、第1トランジスタ及び第2トランジスタは、チャネルが形成される半導体層に酸化物半導体を含んで構成されることを特徴とする。

【0029】

このように、上記トランジスタを構成する半導体として酸化物半導体を用いることが好ましい。より好ましくは、真性キャリア密度が極めて低い酸化物半導体を用いる。チャネルが形成される半導体層の真性キャリア密度が極めて低いため、トランジスタのオフ状態におけるリーク電流は極めて小さいものとなる。このような特徴は、他の半導体(例えばシリコン)にはない酸化物半導体に特有の特徴である。

【0030】

また、本発明の一態様のキャッシュメモリの駆動方法は、まず、第1格納部と第2格納部とを有する複数のメモリセルから構成されるラインを複数有するメモリセットが、制御部によって指定されるラインのいずれか1つを選択し、当該ラインを構成するメモリセルの第1格納部のそれぞれから出力される第1データ群を比較回路に出力する。その後、比較回路は、メモリセットから出力された第1データ群に含まれるアドレスデータと、CPUから入力されたアドレスデータとが一致するか否かを比較し、一致する場合には、比較回路はCPUにキャッシュヒット信号及びメモリセットから出力された第1データ群に含まれるメインデータを出力する。一方、一致しない場合には、第1データ群を出力したラインを構成するメモリセルのそれぞれは、第2格納部に格納されたデータを第1格納部に転送すると共に、メモリセットは、データの転送が行われたメモリセルの第1格納部のそれぞれから出力される第2データ群を比較回路に出力する、キャッシュメモリの駆動方法である。

【0031】

このような駆動方法を用いることにより、従来のキャッシュメモリに比べて読み出し動作を行う頻度を低減することができるため、結果として低消費電力駆動が可能なキャッシュメモリとすることができる。

【0032】

以下では例を挙げて、本発明の一態様のキャッシュメモリとその駆動方法を用いることにより、従来のキャッシュメモリと比較して消費電力を低減可能であることを説明する。

【0033】

一例として、8個のメモリセットを有する従来のキャッシュメモリと、4個のメモリセットを有する本発明の一態様のキャッシュメモリについて、そのキャッシュヒット率と消費電力の期待値について説明する。なお上述のように、本発明の一態様のキャッシュメモリのメモリセルは、従来構成に比べて2倍のデータを格納可能であるため、これら2つのキャッシュメモリは、等しいデータ量を格納することができるとする。

【0034】

ここで、キャッシュメモリの1度の読み出し動作でキャッシュヒットする確率をキャッシュヒット率Pとし、キャッシュメモリの読み出しに要する全消費電力をWとし、それぞれのメモリセットが一度の読み出し動作で消費する消費電力を消費電力Wsとする。

【0035】

また、それぞれのキャッシュメモリにおいて、いずれか1つのメモリセット内の1つのラインに要求するデータが格納されているとする。したがって、8個のメモリセットを有する従来のキャッシュメモリでは、いずれか1つのセットに要求するデータが格納されている。一方、4個のメモリセットを有する本発明の一態様のキャッシュメモリでは、いずれか1つのメモリセット内の1つのラインを構成するメモリセル群における、いずれかの格納部(第1格納部または第2格納部)に要求するデータが格納されているとする。

【0036】

8個のメモリセットを有する従来のキャッシュメモリにおいては、いずれかのセットに要求するデータが格納されているため、1度の読み出し動作でのキャッシュヒット率Pの期待値は1となる。また、一度の読み出し動作で8個のメモリセット全ての読み出しを実行するため、消費される全消費電力Wは8Wsとなる。

【0037】

一方、本発明の一態様のキャッシュメモリにおいて、1度目の読み出し動作では、それぞれのメモリセット内のメモリセルの第1格納部に格納されているデータを読み出す。さらに1度目の読み出し動作でキャッシュヒットしなかった場合には、該当するメモリセルの第2格納部に格納されたデータを第1格納部に転送し、2度目の読み出し動作を行う。したがって、1度目の読み出し動作でのキャッシュヒット率P1は0.5であり、2度目の読み出し動作でのキャッシュヒット率(1度目の読み出し動作でキャッシュヒットせず、且つ2度目の読み出し動作でキャッシュヒットする確率)P2も同様に0.5であるため、結果としてキャッシュヒット率Pは1となる。

【0038】

また、読み出し動作で消費する消費電力Wの期待値は、1度目の読み出し動作でキャッシュヒットする場合の消費電力W1と、1度目の読み出し動作でキャッシュヒットせず、且つ2度目の読み出し動作でキャッシュヒットする場合の消費電力W2を足したものとなる。すなわち、消費電力W1はP1×4Ws=2Wsであり、消費電力W2はP2×8Ws=4Wsとなるため、結果としてキャッシュメモリの読み出し動作における全消費電力Wは6Wsとなる。

【0039】

このように、本発明の一態様のキャッシュメモリと、その駆動方法を用いることで、メモリセットの数を増やした場合と同等のキャッシュヒット率の向上を実現しつつ、読み出し動作における消費電力を低減することができる。

【発明の効果】

【0040】

本発明によれば、低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供できる。

【図面の簡単な説明】

【0041】

【図1】本発明の一態様の、キャッシュメモリを説明する図。

【図2】本発明の一態様の、キャッシュメモリの接続構成を説明する図。

【図3】本発明の一態様の、キャッシュメモリの動作を説明する図。

【図4】本発明の一態様の、キャッシュメモリのメモリセルを説明する図。

【図5】本発明の一態様の、キャッシュメモリのメモリセルの動作を説明する図。

【図6】本発明の一態様の、トランジスタを説明する図。

【図7】本発明の一態様の、トランジスタの作製方法を説明する図。

【図8】本発明の一態様の、キャッシュメモリのメモリセルを説明する図。

【図9】酸化物材料の結晶構造を説明する図。

【図10】酸化物材料の結晶構造を説明する図。

【図11】酸化物材料の結晶構造を説明する図。

【図12】酸化物材料の結晶構造を説明する図。

【図13】本発明の一態様の、電子機器を説明する図。

【発明を実施するための形態】

【0042】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0043】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0044】

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書におけるトランジスタは、IGFET(Insulated Gate Field Effect Transistor)や薄膜トランジスタ(TFT:Thin Film Transistor)を含む。

【0045】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0046】

また、本明細書等において、トランジスタのソース、又はドレインのどちらか一方のことを「第1電極」と呼び、ソース、又はドレインの他方を「第2電極」とも呼ぶことがある。なお、この際、ゲートについては「ゲート」又は「ゲート電極」とも呼ぶ。

【0047】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、コイル、容量素子、その他の各種機能を有する素子などが含まれる。

【0048】

なお、本明細書等においてノードとは、回路を構成する素子の電気的な接続を可能とする素子(例えば、配線など)のことをいう。したがって、”Aが接続されたノード”とは、Aと電気的に接続され、且つAと同電位と見なせる配線のことをいう。なお、配線の途中に電気的な接続を可能とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオードなど)が1個以上配置されていても、Aと同電位と見なせれば同じノードであるとする。

【0049】

なお、本明細書で説明する回路図においては、チャネルが形成される半導体に酸化物半導体などを用いたトランジスタが適用されることを示すために、回路図内のトランジスタにOSの符号を併せて付す場合がある。

【0050】

(実施の形態1)

本実施の形態では、本発明の一態様のキャッシュメモリの構成と、その駆動方法について図1乃至図3を用いて説明する。

【0051】

<構成例>

図1(A)は、本実施の形態で例示するキャッシュメモリの構成を示すブロック図である。キャッシュメモリ100は、1または複数のメモリセット110と、制御部101と、比較回路103と、を有する。各メモリセット110は比較回路103及び制御部101と電気的に接続し、また比較回路103及び制御部101はお互いに電気的に接続している。

【0052】

制御部101は、比較回路103からの入力信号や外部(例えばCPU)からの命令信号に応じて、各メモリセット110の動作を制御する。例えばメモリセット110の読み出し動作や、メモリセット110へのデータの書き換え動作、または後に説明するメモリセット110内のメモリセルのデータ転送動作などを制御する。

【0053】

制御部101には、外部から要求されるアドレスデータが入力される。制御部101は、当該アドレスデータを上位ビットから構成される第1のアドレスデータと下位ビットから構成される第2のアドレスデータとに分割し、第1のアドレスデータを比較回路103に、また第2のアドレスデータをそれぞれのメモリセット110に出力する。

【0054】

また、制御部101は外部からの命令信号に応じて、指定されるメモリセット110内のデータの書き換えを行うことができる。例えば外部から書き換えの命令信号に加えてアドレスデータとメインデータとが入力されると、書き換えを行う対象のメモリセット110を選択し、当該メモリセット110内に対して、アドレスデータの下位ビット(第2のアドレスデータ)に対応するラインに、アドレスデータの上位ビット(第1のアドレスデータ)とメインデータを格納するよう要求する。

【0055】

比較回路103には、それぞれのメモリセット110から、後に説明する当該それぞれのメモリセット110内の特定のラインのタグフィールドに格納されたアドレスデータと、データフィールドに格納されたメインデータが入力される。比較回路103は、制御部101から入力された第1のアドレスデータとメモリセット110から入力されたアドレスデータとを比較し、一致する場合には、キャッシュヒット信号に加えてメインデータを外部に出力する。一方、全てのメモリセット110においてこれらが一致しない場合には、キャッシュミス信号のみを制御部101に出力する。

【0056】

なお具体的には、比較回路103は、キャッシュメモリ100が有するメモリセット110と等しい数のタグ比較回路と、1つのデータ比較回路を備える。1つのメモリセット110には1つのタグ比較回路が接続され、当該メモリセットから出力されるアドレスデータと、第1のアドレスデータとの比較を行い、その結果をキャッシュヒット信号又はキャッシュミス信号として、データ比較回路に出力する。データ比較回路には各々のタグ比較回路から入力される上記信号と、それぞれのメモリセット110からのメインデータが入力され、各々のタグ比較回路から入力される信号に応じて、キャッシュヒット信号及びメインデータを外部に出力するか、キャッシュミス信号のみを制御部101に出力するかのいずれかを行う。

【0057】

なお、読み出し動作や上記比較動作は、全てのメモリセット110に対して並行して行われる。このように並行して動作を行うことにより、より高速動作が実現できる。

【0058】

ここで、制御部101は、比較回路103から1度目のキャッシュミス信号が入力された場合、それぞれのメモリセット110に対して、後に説明するデータ転送動作と読み出し動作を行うよう、命令信号を送信する。また、制御部101に2度目のキャッシュミス信号が入力された場合には、比較回路103に対して、キャッシュミス信号を外部に出力するように要求する命令信号を出力する。比較回路103は、当該信号が入力されると、キャッシュミス信号を外部に出力する。

【0059】

続いて、メモリセット110の構成について説明する。図1(B)は、メモリセット110の構成を示すブロック図である。メモリセット110は、メモリアレイ111と、駆動回路119とを有する。また、メモリアレイ111は、m本のライン113から構成され、それぞれのライン113は複数のメモリセル150を有する。

【0060】

m本のライン113のそれぞれは、アドレスデータの下位ビットに対応して設けられている。したがって、制御部101から入力される第2のアドレスデータによって、選択されるライン113が一義的に決定される。例えば当該第2のアドレスデータとして8ビット分のデータを用いる場合には、メモリセット110は256本のライン113を有する。

【0061】

また、ライン113は少なくともタグフィールド115とデータフィールド117の2つの領域を有している。タグフィールド115には、第1のアドレスデータが格納され、データフィールド117にはアドレスデータに対応したメインデータが格納される。

【0062】

駆動回路119は、制御部101からの要求に応じて、メモリアレイ111内のライン113を選択し、データを格納する(書き換える)、またはデータを読み出して比較回路に出力することができる。また、任意のライン113内のメモリセル150に対して、後述するデータ転送動作を行うことができる。

【0063】

データを読み出す際、駆動回路119は制御部101から入力される第2のアドレスデータによって一義的に決定されるメモリアレイ111内の1つのライン113を選択し、当該ライン113に格納されるデータ(データ群とも呼ぶ)を読み出すと共に当該データを比較回路103に出力する。

【0064】

データ転送動作を行う際、駆動回路119は制御部101からの命令信号に応じて、指定する1つのライン113を構成する全てのメモリセル150に対して、後述するデータ転送動作を行い、次いで当該ライン113に格納されるデータの読み出しを行うと共に比較回路103に出力する。

【0065】

また、駆動回路119は、制御部101からの命令信号に応じて、特定のラインに対してデータの書き換えを行うことができる。制御部101からは書き換え命令信号に加えて、第1のアドレスデータと第2のアドレスデータとメインデータが入力される。駆動回路119は、第2のアドレスデータで一義的に決定されるメモリアレイ111内の1つのライン113を選択し、当該ライン113のタグフィールド115に第1のアドレスデータを、またデータフィールド117にメインデータをそれぞれ格納する。

【0066】

続いて、メモリセル150について説明する。図1(C)は、メモリセル150の構成を示すブロック図である。

【0067】

メモリセル150は、第1格納部151と、第2格納部153と、データ転送部155を有する。第1格納部151、第2格納部153、及びデータ転送部155は、それぞれ1ビットのデータを格納することができる。

【0068】

第1格納部151は、当該第1格納部151に格納された1ビットのデータを駆動回路119に出力することができる。また駆動回路119により、当該第1格納部151に格納されるデータを書き換えることができる。さらに、当該第1格納部151に格納された1ビットのデータをデータ転送部155に転送することが出来る。

【0069】

データ転送部155は、第1格納部151から転送された1ビットのデータを格納しておくことができる。さらにデータ転送部155は、当該データ転送部155に格納された1ビットのデータを第2格納部153に転送し、当該第2格納部153内のデータを書き換えることができる。

【0070】

第2格納部153は、データ転送部155から転送された1ビットのデータを格納しておくことが出来る。さらに、当該第2格納部153に格納された1ビットのデータを第1格納部151に転送し、当該第1格納部151内のデータを書き換えることができる。

【0071】

ここで本明細書等において、メモリセル内でのデータの転送は、転送元に格納されたデータのコピーを、転送先に格納するものとする。したがって、データの転送後には、転送元と転送先とに同一のデータが格納された状態となる。

【0072】

ここで、データ転送動作を行う場合について説明する。まず初期状態として、第1格納部151には第1のデータが、また第2格納部153には第2のデータが格納されているとする。

【0073】

データ転送動作は主に3つの動作からなる。まず第1の動作として、第1格納部151に格納された第1のデータを、データ転送部155にコピーして格納(転送)する。次いで、第2の動作として、第2格納部153に格納された第2のデータを、第1格納部151に転送する。この段階で、第1格納部151及び第2格納部153のそれぞれには、第2のデータが格納され、データ転送部155には第1のデータが格納されている状態となる。最後に、第3の動作として、データ転送部155から第2格納部153に第1のデータを転送することによりデータ転送動作が終了する。最終的に、第1格納部151には第2のデータが、また第2格納部153には第1のデータが格納されている状態となり、初期状態における第1格納部151と第2格納部153に格納されていたデータが置換された状態となる。

【0074】

以上がキャッシュメモリ100の構成についての説明である。

【0075】

<接続構成例>

ここで、本発明の一態様のキャッシュメモリ100は、少なくとも演算部と、制御部を有するCPUに接続することができる。図2は、キャッシュメモリ100が接続され、制御部161及び演算部162を有するCPU160の構成を示すブロック図である。

【0076】

演算部162は、論理演算、アドレス演算などの演算処理を行う。また、演算部162は、制御部161に対して演算に必要なメインデータを要求するため、制御部161に対して要求するメインデータに対応するアドレスデータを制御部161に出力する。

【0077】

制御部161は、演算部162からアドレスデータが入力されると、キャッシュメモリ100に当該アドレスデータを出力してデータを要求する。このとき、キャッシュメモリ100からキャッシュヒット信号と要求したメインデータを受信した場合は、演算部162に当該データを出力する。一方、キャッシュメモリ100からキャッシュミス信号を受信した場合は、メインメモリ170に対してデータを要求する。

【0078】

また、制御部161は、メインメモリ170からメインデータを取得した際、演算部162に当該メインデータを出力すると共に、キャッシュメモリ100に当該メインデータを格納するように命令する。このとき、制御部161は、キャッシュメモリ100に対し、書き込み命令信号と、メインデータと、当該メインデータに対応するアドレスデータを送信する。キャッシュメモリ100は、当該書き込み命令信号にしたがって、指定されるセットの特定のラインに当該メインデータとアドレスデータを格納する。なお、制御部161は、メインメモリ170からメインデータを取得した後、まずキャッシュメモリ100に当該メインデータとアドレスデータを格納し、キャッシュメモリ100に格納された当該メインデータを読み出して演算部162に送信してもよい。

【0079】

メインメモリ170としては、例えば、SRAMやDRAMから構成される揮発性の記憶装置をはじめ、光磁気ディスクやフラッシュメモリなどの不揮発性の記憶装置を用いることができる。ここで以降では、キャッシュメモリとメインメモリとの違いとして、CPUが最初にデータを要求する記憶装置のことをキャッシュメモリといい、2番目以降にデータを要求する記憶装置のことをメインメモリということとする。

【0080】

<動作例>

続いて、キャッシュメモリ100の動作例について図3を参照して説明する。図3は、キャッシュメモリ100の動作の一例に係るフローチャートである。

【0081】

ここで、初期状態として、各々のメモリセル150内の第1格納部151には第1のデータが、また第2格納部153には第2のデータが格納されているとする。

【0082】

まず、ステップ201(第1の読み出し)では、制御部101に要求されるアドレスデータが入力され、制御部101から各メモリセット110に第2のアドレスデータが、また比較回路103に第1のアドレスデータが出力される。それぞれのメモリセット110は、第2のアドレスデータで一義的に決定されるライン113内に格納されているアドレスデータとメインデータの読み出しを行うと共に、これらを比較回路103に出力する。ここで読み出されるデータは、各々のメモリセル150内の第1格納部151に格納されている第1のデータである。

【0083】

ステップ202(第1の比較)において、比較回路103は第1のアドレスデータと、各メモリセット110から入力されるアドレスデータとの比較を行う。

【0084】

ここで、いずれかのメモリセット110から入力されるアドレスデータと、第1のアドレスデータが一致した(キャッシュヒットした)場合、ステップ203(出力)として、比較回路103はキャッシュヒット信号と、当該メモリセットから入力されたメインデータを合わせて外部に出力する。

【0085】

また、ステップ202において、それぞれのメモリセット110から入力されるアドレスデータが第1のアドレスデータといずれも一致しない(キャッシュミスした)場合、比較回路103は制御部101にキャッシュミス信号を出力する。

【0086】

制御部101はステップ202において比較回路103からキャッシュミス信号を受けると、それぞれのメモリセット110に対してデータ転送動作の命令信号を送信する。

【0087】

ステップ204(データ転送動作)では、各々のメモリセット110の上記第2のアドレスデータに対応したライン113内の全てのメモリセル150において、上述したデータ転送動作を行う。具体的には、メモリセル150内の第1格納部151に格納されている第1のデータをデータ転送部155に転送して格納する第1の動作と、第2格納部153に格納されている第2のデータを第1格納部151に転送して書き換える第2の動作と、データ転送部155に格納されている第1のデータを第2格納部153に転送して書き換える第3の動作と、を順に行う。

【0088】

続いて、ステップ205(第2の読み出し)では、それぞれのメモリセット110においてステップ204でデータ転送動作を行ったライン113に対して再度読み出し動作を行うと共に、比較回路103に読み出されたデータが出力される。ここで読み出されるデータは、各々のメモリセル150内の第1格納部151に格納されている第2のデータとなる。

【0089】

なお、ステップ205の読み出し動作は、ステップ204の第3の動作と並行して行うことが好ましい。これらの動作を並行して行うことで、より高速動作が実現できる。

【0090】

続いて、ステップ206(第2の比較)において、比較回路103は第1のアドレスデータと、各メモリセット110から入力されるアドレスデータとの比較を行う。

【0091】

ステップ206でいずれかのメモリセット110でキャッシュヒットした場合、ステップ203として、比較回路103はキャッシュヒット信号と、当該メモリセットから入力されたメインデータを合わせて外部に出力する。

【0092】

ここで、キャッシュヒットしたメモリセット110については、そのままの状態が維持され、キャッシュヒットしなかった他のメモリセット110については、ステップ207に移行する。

【0093】

一方、ステップ206において、いずれのメモリセット110でもキャッシュヒットしなかった(キャッシュミスした)場合は、比較回路103はキャッシュミス信号を制御部101に送信する。続いて、制御部101からの命令により、比較回路103は外部にキャッシュミス信号を出力し、各メモリセット110はステップ207に移行する。

【0094】

ステップ207(書き換え判定)では、それぞれのメモリセット110について、データの書き換えを行うかどうかの判定を行う。ステップ206において、比較回路103が外部にキャッシュミス信号を送信した場合は、いずれかのメモリセット110を選択し、メインメモリ170から取得した新たなデータ(第3のデータ)に書き換える。データを書き換えるメモリセット110の選択方法としては、上述のLRU方式や、最も使用頻度が少ないメモリセットを選択するLFU(Least Frequency Used)方式、又は最初にデータが格納されたメモリセットを選択するFIFO(First In First Out)方式などの書き換えアルゴリズムを用いることができる。

【0095】

ステップ207でデータの書き換えを行わないと判定されたメモリセット110については、ステップ208において再度データ転送動作を行う。また、データの書き換えを行うと判定されたメモリセット110については、ステップ209に移行する。

【0096】

ステップ208(データ転送動作)では、上述したデータ転送動作を再度行う。その結果、該当するメモリセル150においては、第1格納部151に第1のデータが、また第2格納部153に第2のデータが格納された状態、すなわち初期状態と同じ状態に戻る。

【0097】