キャッシュメモリ装置及び制御方法

【課題】キャッシュメモリに記憶されたピクセルデータの利用率向上を可能とするキャッシュメモリ装置を提供する。

【解決手段】本発明は、表示する画像データの幅がWピクセルであり、2次元方形領域の幅がaピクセル及び縦がbピクセルの場合、横方向のエントリ数がW/aである数pであり、縦方向のエントリ数が[a×2(1/2)/b]の整数値に2を加えた数qであるエントリマトリクスのキャッシュメモリと、表示画面の座標系の表示アドレスを、表示メモリの画像データの座標系へ角度θで座標変換が行われた、2次元方形領域のメモリアドレスから、エントリアドレスを生成するエントリアドレス生成部と、表示メモリからメモリアドレスを用いた角度θのラスタースキャンで分割画像データを読み出し、キャッシュメモリに書き込む書込制御部と、表示される画像データの全走査線に対応するピクセルデータを順次読み出す読出制御部とを有する。

【解決手段】本発明は、表示する画像データの幅がWピクセルであり、2次元方形領域の幅がaピクセル及び縦がbピクセルの場合、横方向のエントリ数がW/aである数pであり、縦方向のエントリ数が[a×2(1/2)/b]の整数値に2を加えた数qであるエントリマトリクスのキャッシュメモリと、表示画面の座標系の表示アドレスを、表示メモリの画像データの座標系へ角度θで座標変換が行われた、2次元方形領域のメモリアドレスから、エントリアドレスを生成するエントリアドレス生成部と、表示メモリからメモリアドレスを用いた角度θのラスタースキャンで分割画像データを読み出し、キャッシュメモリに書き込む書込制御部と、表示される画像データの全走査線に対応するピクセルデータを順次読み出す読出制御部とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、キャッシュメモリ装置及び制御方法に関するものである。

【背景技術】

【0002】

船舶用レーダあるいはナビゲーションシステム等の表示装置の表示画面において、自身を原点とした自身の進行をy軸とし、このy軸に対して垂直な軸をx軸とした2次元座標系(以下、表示2次元座標系)に海図あるいは地図などを表示させる画像表示方式がある。

例えば、船舶用レーダの場合においては、船舶自身の進行方向を画面の上部、すなわち進行方向に平行な軸をY軸として、海図画像を表示画面に表示するヘッドアップ表示モードがある。

【0003】

しかし、一般的に、海図画像は、海図画像の画像データを蓄積する表示メモリにおいて、北の方向に平行な軸をY軸とする場合など、船の進行方向と異なる方向の2次元座標系(メモリ2次元座標系)で記憶されている。

したがって、ノースアップ表示モードの表示から、船の進行方向をY軸として表示画面に海図画像を表示する表示モードに変更した場合、すなわち海図画像を船の進行方向を上部として表示するヘッドアップ表示モードに変更した場合、表示メモリに記憶されている海図画像を船の進行方向が上部となるように再描画する必要がある。

この表示メモリに対して再描画を行う構成の場合、船首方位が更新される度に表示が行われるまでに時間がかかってしまう。

そのため、表示メモリの海図画像の再描画を行う一般的な構成ではなく、船首方位が更新されたとしても、表示メモリに記憶される海図画像の再描画を行なわず、表示モード変更後の海図画像の表示を高速に行うため、以下の方法が用いられる場合がある。

すなわち、表示2次元座標系の表示画面に対して表示メモリの画像データを表示させる際、表示2次元座標系の座標点(表示2次元座標系の表示画面におけるピクセルの位置を示す点)の座標を、表示メモリにおけるメモリ2次元座標系の座標点(メモリ2次元座標系で記憶された画像データにおけるピクセルの位置を示す点)の座標に、メモリ2次元座標系における自身の位置を中心として表示2次元座標系を回転させた座標変換を行う。

【0004】

この座標変換の結果得られた座標により、メモリ2次元座標系における表示メモリから、表示2次元座標系における座標を読み出し、すなわち、メモリ2次元座標系の画像データから、表示2次元座標系の表示画面に表示する表示画像データを切り出して表示させることになる。

図4はメモリ2次元座標系における画像データと表示2次元座標系における表示画像データとの関係を説明する図である。図4において、図4(a)はメモリ2次元座標系に対して表示2次元座標系が回転されておらず平行移動している場合であり、図4(b)はメモリ2次元系に対して表示2次元座標系回転及び平行移動している場合を示している。

【0005】

次に、図4(a)の場合におけるメモリ2次元座標系の表示メモリの画像データから、表示2次元座標系による表示領域の表示画像データにおけるピクセルのデータ(以下、ピクセルデータ)の読み出しについて説明する。

表示メモリからの表示画像データの読み出しは、表示領域を表示画面に表示する走査線方向にデータを読み出すラスタースキャン方式により行われる。

このため、表示メモリが図4(a)に示されるように、X軸方向がNドット、Y軸方向がMドットであり、表示2次元座標系のx軸及びy軸の各々が、それぞれメモリ2次元座標系のX軸、Y軸と平行である場合において、表示メモリの画像データから表示画面(X軸方向にnドット、Y軸方向にmドット)に対応する表示領域の表示画像データピクセルデータの読み出しを以下の様に行う。

【0006】

ピクセルデータの読み出しの際、図4(a)の場合、メモリ2次元座標系に対して表示2次元座標系が回転しておらず、表示領域内のピクセルデータのアドレスを、ラスタースキャン方向の行毎に順次、表示2次元座標系からメモリ2次元座標系に行平行移動のみの座標変換を行う。

そして、表示領域のピクセルのデータを、表示領域の左上端から開始し、X軸方向(ラスタースキャン方向)へ直線的にnピクセル分移動し、表示領域の右端に達すると順次Y軸方向に隣接する下部のピクセルデータの行へ移動させ、X軸方向を表示領域の左端へ戻した後、X軸方向に直線移動を行いつつピクセルデータを読み出す。また、表示領域における最後のピクセルのデータ、すなわち表示領域の右下の位置にあるピクセルのデータを読み出した後、表示領域のピクセルのデータの読み出しの始点である左上端に戻り、上述した読み出し動作を繰り返す。

【0007】

一方、図4(b)に示されるように、表示2次元座標系がメモリ2次元座標系に対して、回転角度θで回転し、平行移動している場合、すなわち船舶の進行方向が北の方向(Y軸)に対して、自船位置を原点として回転角度θで回転し、かつ平行移動している場合において、表示メモリの画像データから、表示画面に対応する表示領域の表示画像データにおけるピクセルデータの読み出しを以下の様に行う。

すでに述べたように、表示2次元座標系における座標を、メモリ2次元座標系の座標に座標変換し(回転及び平行移動の処理を行い)、得られた表示画像データのメモリ2次元座標系におけるアドレスを用いて、表示領域の左上の座標点から、図4(a)のスキャン方向に対して、回転角度θ傾いたスキャン方向に順次ピクセルのデータを読み出す処理を行う。表示領域内におけるピクセルデータの読み出しは、図4(a)と同様なラスタースキャン方式で行われるが、読み出しに際して、上述した回転を含む座標変換が行われることになる。

【0008】

一方、ある方向を基準として、例えば図4(b)に示すように、北方向に平行な軸をY軸として表示メモリに格納されたメモリ2次元座標系の画像データから、高速に任意の回転角度θの表示画像データを読み出す場合、実装として最も簡易な構成としてはランダムアクセスが可能なSRAM(Static Random Access Memory)を用いることになる。

しかしながら、表示メモリには表示装置の画素数に比較し、より多くの画像数のピクセルのデータが記憶されており、大きな容量が必要となるため、SRAMを用いると製造コストが非常にかかってしまう。

このため、表示装置に表示する画像データを蓄積する表示メモリとしては、データ量に対して価格の安いSDRAM(Synchronous Dynamic Random Access Memory)が多用されている。

【0009】

このSDRAMは、SRAMのように、ピクセルデータを単位とした高速なランダムアクセスを、そのデータを読み出す構成により行うことができない。

すなわち、SDRAMは、記憶領域におけるメモリセルのアクセスにおいて、ロウアドレスが選択されている場合、ページ単位読み出しとして、カラムアドレスを変化させることで、小単位(例えば、ピクセルデータ単位)のデータを、同一のロウアドレスにおける連続したアドレス範囲においてのみ高速にアクセスできる。

しかしながら、メモリアクセスを行う際にロウアドレスを変更する場合、ロウアドレスを活性化させるためのオーバーヘッドが乗じるため、ロウアドレスを変更するアドレス変化を伴うランダムアクセスを高速に実行することができない。

したがって、SDRAMから複数のピクセルデータをブロック単位に読み出し、ランダムアクセスが可能なSRAMにより構成したキャッシュメモリに対し、ブロック単位に読み出したピクセルデータを一旦記憶させ、キャッシュメモリからラスタースキャン方式によりピクセルデータを読み出し、表示画面に表示させている(例えば、特許文献1参照)。

【0010】

ここで、図5を用いてさらに説明する。図5は、表示メモリにおけるピクセルデータの記憶形式を示す図である。

例えば、特許文献1においては、図5(a)に示すように、表示メモリは、X軸方向にNドット、Y軸方向にMドットで構成され、全体としてN×Mピクセルのピクセルデータからなる画像データが記憶されている。ここで、各メモリアクセス1サイクルでアクセスされる1アドレスには、例えば、2次元方形領域8ドット×8ピクセルデータの64ピクセルデータが配置されるように、N×Mピクセルの各ピクセルデータが表示メモリに記憶されている。この2次元方形領域は例として示す同図(b)に示されるように、ピクセルデータD0からピクセルデータD63の64個のピクセルデータにより構成されている。

したがって、表示メモリからは各2次元方形領域A0、…、AN/K−1、…、Anが指定されると、その方形領域に含まれる64ピクセルデータが連続してブロックとして読み出され、キャッシュのエントリに対して書き込まれる。この2次元方形領域としては、8×8ピクセルデータとして説明したが、4×4ピクセルデータ、あるいは2×2ピクセルデータ等の正方領域でよく、また正方領域に限らず、長方領域とすることも出来る。ここで、kは2次元方形領域を正方形とした場合の各辺のピクセル数を示している(1ピクセルデータは、例えばピクセルの階調度を示すデータであり複数のビットから構成されている)。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2002−181919号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

しかしながら、特許文献1に示すレーダ装置における画像表示においては、表示画面に表示させる画像の解像度を上げるにつれ、表示するピクセルデータの量が増加するため、より大きな帯域幅が必要となる。したがって、SDRAMのアクセスタイムあるいは回転角度θによっては、メモリのデータ読み出しの帯域幅が不足する虞がある。また、回転角度θにおいては45°付近において、ロウアドレスの変更を伴うアクセス回数が増加することにより、データ読み出しの時間が増加することにより、データ読出の帯域幅が不足することになる。

この結果、表示画面に表示する全ての画像データを、表示メモリから読み出すことができず、表示画面の一部が直前に表示された画像データのままとなってしまう。

【0013】

また、特許文献1においては、キャッシュメモリに記憶されている2次元方形領域のピクセルのデータから、ラスタースキャンにおいてスキャン方向に配置されているピクセルのデータを読み出した後に、新たな2次元方形領域のピクセルデータを、SDRAMから読み出して、キャッシュメモリに上書きする処理を行っている。

【0014】

このため、2次元方形領域に複数の走査線に対応するピクセルデータが記憶されていたとしても、その一部しか利用していないことになる。例えば、図5(b)における矢印で示したスキャン方向に読み出されるピクセルデータは8ピクセル分である。すなわち、読み出した64ピクセルのデータ中において、実際に用いられるのは8ピクセル分のみであり、12.5%の利用率しかないことになる。

したがって、SDRAMからのデータ読出における限られた帯域幅を有効に使う必要があるが、引用文献1に記載された方法では、キャッシュメモリに記憶された2次元方形領域のピクセルのデータの利用率が不十分な状態において、キャッシュメモリの使用が行われている。

【0015】

本発明は、上記の課題を考慮してなされたものであって、記憶された2次元方形領域のピクセルのデータの利用率を上げ、表示メモリからの読み出すデータの帯域幅が同一であっても、より解像度の高い画像を表示することを可能とするキャッシュメモリ装置、制御方法を提供することを目的とする。

【課題を解決するための手段】

【0016】

本発明のキャッシュメモリ装置は、表示メモリから読み出され、画像表示に用いられる画像データを、キャッシュするメモリであり、画像データを分割した2次元方形領域毎の分割画像データ毎に、メモリを構成するエントリに書き込まれ、表示する画像データの横幅がWピクセルである場合、2次元方形領域の横幅がaピクセル及び縦幅がbピクセルの場合、横方向のエントリ数がW/aで求められた数pであり、縦方向のエントリ数が[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されたキャッシュメモリと、表示メモリから指定された角度θでラスタースキャンにより分割画像データを読み出すための、表示画面の座標系におけるピクセルデータの表示アドレスを、表示メモリに記憶された画像データの座標系へ角度θによる座標変換が行われた、表示メモリにおける2次元方形領域のメモリアドレスが入力され、メモリアドレスからエントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成するエントリアドレス生成部と、メモリアクセス1サイクルの動作で、記憶している表示画像データにおける2次元方形領域毎の分割画像データの一括した書き込み及び読み出しが可能な表示メモリから、指定されたメモリアドレスを用いた角度θのラスタースキャンにより、分割画像データを読み出し、エントリアドレスを用いてキャッシュメモリのエントリに書き込むキャッシメモリ書込制御部と、エントリから指定された角度θのラスタースキャンにより、分割画像データに含まれた、表示される画像データの走査線全てに対応するピクセルデータを順次読み出すキャッシュメモリ制御部とを有することを特徴とする。

【0017】

本発明のキャッシュメモリ装置は、エントリアドレス生成部が、メモリアドレスからエントリアドレスを生成する際、角度θが、(7π/4)から(π/4)までの間及び(3π/4)から(5π/4)までの間の場合、メモリアドレスのX軸方向の座標をエントリマトリクスの横方向の列アドレスに対応させ、Y軸方向の座標をエントリマトリクスの縦方向の行アドレスに対応させてエントリアドレスを生成し、角度θが、(π/4)から(3π/4)まで間及び(5π/4)から(7π/4)までの間の場合、メモリアドレスのX軸方向の座標をエントリマトリクスの縦方向の行アドレスに対応させ、Y軸方向の座標をエントリマトリクスの横方向の列アドレスに対応させてエントリアドレスを生成することを特徴とする。

【0018】

本発明のキャッシュメモリ装置は、エントリマトリクスにおけるエントリ各々に対応した記憶領域を有する番号記憶部と、表示画面への表示開始から、当該表示画面に表示される走査線の数を走査線番号としてカウントし、エントリに記憶されているピクセルデータを読み出す毎に、その時点の走査線番号を番号記憶部に書き込む番号記憶制御部と、2次元方形領域が記憶されたエントリをラスタースキャンによりアクセスする際、当該エントリに記憶されている走査線番号と、現在の走査線番号とが同一または連続しているかのいずれであるか否かの判定を行い、同一でなくかつ連続していない場合をキャッシュミスとして検出するキャッシュミス検出部とをさらに有し、キャッシュミス検出部がキャッシュミスを検出した場合、キャッシメモリ書込制御部が現在の走査線番号に対応するピクセルデータの含まれる2次元方形領域のピクセルデータを表示メモリから読み出し、エントリマトリクスにおけるキャッシュミスとして検出されたエントリに上書きすることを特徴とする。

【0019】

本発明のキャッシュメモリ装置は、2次元方形領域が2の倍数のa=bの正方形であることを特徴とする。

【発明の効果】

【0020】

この発明によれば、キャッシュメモリの各エントリに記憶された分割画像データから、表示される画像の全ての走査線に対応するピクセルデータを読み出すため、従来の様に、各エントリの分割画像データから1走査線分のピクセルデータしか使用しない場合に比較し、分割画像データにおけるピクセルデータの利用率を向上させることができ、表示メモリからの読み出しの帯域幅が同一であっても、より解像度の高い画像を表示することが可能となる。

【図面の簡単な説明】

【0021】

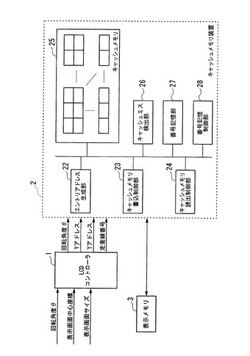

【図1】この発明の一実施形態によるキャッシュメモリ装置を用いた表示制御装置の構成例を示す概略ブロック図である。

【図2】回転角度θの走査線と、2次元方形領域におけるピクセルとの関係を説明する図である。

【図3】2次元方形領域がa×aの場合の回転角度θ=45°の場合における、走査線と2次元平行形領域との対応を示す図である。

【図4】メモリ2次元座標系における画像データと表示2次元座標系における表示画像データとの関係を説明する図である。

【図5】表示メモリにおけるピクセルデータの記憶形式を示す図である。

【発明を実施するための形態】

【0022】

以下、図面を参照して、本発明の実施の形態について説明する。図1は、この発明の一実施形態によるキャッシュメモリ装置を用いた表示制御装置の構成例を示す概略ブロック図である。本実施形態において、表示制御装置の制御対象はLCD(Liquid Crystal Display)表示装置である。例えば、本発明は、例えば、船舶、車などのレーダ装置の画像表示に用いられる。以下、船舶のレーダ装置のヘッドアップ表示(自身の進行方向を表示画面の上部とする表示)モードにおける画像表示の処理として説明する。

【0023】

図1における表示制御装置は、LCDコントローラ1、キャッシュメモリ装置2及び表示メモリ3を備えている。表示メモリ3には、記憶容量が大きく、一回のメモリアクセスにより複数のビットデータの読出が可能なSDRAMなどが用いられている。表示メモリ3は、例えば、レーダ装置の表示装置に表示する画像データが一定の向きで、例えばY軸方向が南北軸に平行となり、X軸方向が東西軸に平行となるように記憶されている。表示メモリ3は、図4に示すように、表示装置に表示される表示画像データの画像領域より大きい画像領域のピクセルデータを有している。また、表示メモリ3は、画像データを複数に分割した2次元平行形領域毎の分割画像データを、連続したメモリアドレスにより記憶している。表示メモリ3は、例えば、図5(b)に示すような2次元平行形領域毎の分割として、SDRAMのROW(ワード線)毎に、画像データの32×32ピクセルの矩形領域のデータが格納されている。後述するように、キャッシュメモリ装置2は、表示メモリ3から4×4ピクセルの2次元平行形領域毎の分割画像データを単位として、表示メモリ3から読み出すため、同一の32×32ピクセル範囲内からの2次元平行形領域の読み出しを高速化することができる。

【0024】

LCDコントローラ1は、図示しないCPU(Central Processing Unit)から南北方向を基準として回転した角度である回転角度θと、表示装置に表示される表示画像の中心にあるピクセルの表示メモリ3におけるメモリアドレスとが入力される。ここで、LCDコントローラ1は、内部記憶部に表示装置の表示画面の横のピクセル数W及び縦のピクセル数Hが予め設定されている。そして、LCDコントローラ1は、記憶されている表示画面の大きさ(W×Hピクセル)と、供給される表示画面の中心のメモリアドレスと、回転角度θとから、図4(b)に示すように、走査線に位置するピクセルデータを読み出すためのラスタースキャン読み出しを行うメモリアドレスを算出する。

【0025】

LCDコントローラ1は、ラスタースキャン読み出しのため、走査線に対応するピクセルのメモリアドレス(Xアドレス、Yアドレス)を、回転角度θ(指定された角度)に応じて以下の式を用いて算出する。

X=XC+Rsinθ

Y=YC+Rcosθ

XCは、表示画像の中心にあるピクセルの表示メモリ3におけるメモリアドレスのXアドレスである。YCは、表示画像の中心にあるピクセルの表示メモリ3におけるメモリアドレスのYアドレスである。Rは表示画像における表示アドレスから表示メモリのメモリアドレスに変換するピクセルの画像中心のピクセルからの距離(ピクセル数)である。すなわち、LCDコントローラ1は、図4の説明と同様に、表示2次元座標系における座標を、メモリ2次元座標系の座標に座標変換し、メモリアドレスを求めている。

また、LCDコントローラ1は、求めたメモリアドレスから、2次元方形領域を示す領域メモリアドレス(メモリアドレスの先頭アドレス)を生成し、メモリアドレスとともにこの領域メモリアドレスをキャッシュメモリ装置2へ出力する。

【0026】

キャッシュメモリ装置2は、LCDコントローラ1から供給される回転角度θ、表示メモリ3におけるピクセルデータのアドレス(Xアドレス、Yアドレス)、現在アクセスしているピクセルデータの存在する走査線番号により、表示メモリ3から表示画像データをキャッシュ(使用頻度の高いデータを高速なメモリに蓄えておく処理)する。

このキャッシュメモリ装置2は、エントリアドレス生成部22、キャッシュメモリ書込制御部23、キャッシュメモリ読出制御部24、キャッシュメモリ25、キャッシュミス検出部26、番号記憶部27、番号記憶制御部28とを備えている。

【0027】

キャッシュメモリ25は、表示メモリ3から読み出され、画像表示に用いられる画像データを、一旦キャッシュするメモリであり、高速にランダムアクセスが可能なSRAMなどで構成されている。

また、キャッシュメモリ25は、画像データを分割した2次元方形領域毎の分割画像データを、メモリを構成するエントリ毎に記憶する。このキャッシュメモリ25は、表示する画像データの横幅がWピクセルである場合、2次元方形領域の横幅がaピクセル及び縦幅がbピクセルとすると、横方向のエントリ数がW/aで求められた数pであり、縦方向の[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されている。本実施形態においては、2次元方形領域をa=b=2として各エントリを形成している(理由は後述)。また、2次元方形領域は、a≠bの長方形でも良い。

【0028】

キャッシュメモリ書込制御部23は、図4の説明と同様の表示メモリ3からの読み出し処理により、LCDコントローラ1から供給される領域メモリアドレスが示す2次元方形領域のピクセルデータ(分割画像データ)を、表示メモリ3から読み出す。そして、キャッシュメモリ書込制御部23、キャッシュメモリ25に対し、エントリアドレス生成部22の生成するエントリアドレス(後述)の示すエントリに、読み出したピクセルデータを書き込む。

キャッシュメモリ読出制御部24は、エントリアドレス生成部22がLCDコントローラ1から供給されるメモリアドレス(Xアドレス、Yアドレス)から変換したエントリアドレスの示すエントリにより、このエントリに記憶されている2次元方形領域におけるメモリアドレス(Xアドレス、Yアドレス)示すピクセルデータを読み出し、LCDコントローラ1へ出力する。

【0029】

エントリアドレス生成部22は、メモリアドレスと領域メモリアドレスから、キャッシュメモリ25におけるエントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成する。以下の場合、4×4ピクセルのデータ(2次元方形領域)が1エントリに格納され、エントリマトリクスは横2048×縦4となっている。

このエントリアドレスCadは、

Cad={y[3:2],x[10:2]} …(1)

、または

Cad={x[3:2],y[10:2]} …(2)

として生成される(後述)。

(1)及び(2)式のいずれの場合においても、それぞれ下位2ビットは2次元方形領域内の4つのピクセルのいずれかの位置を示し、x[s1,r1]における下位2ビット(ピクセルデータの横方向の並び、x座標)以外の上位ビットはエントリマトリクスにおけるエントリの列(横方向の並び、x座標)の位置を示し、y[s2,r2]における下位2ビット(ピクセルデータの縦方向の並び、y座標)以外の上位ビットはエントリマトリクスにおけるエントリの行(縦方向の並び、y座標)の位置を示している。

【0030】

次に、キャッシュメモリ25のエントリマトリクスを、表示する画像データの横幅がWピクセルである場合、2次元方形領域の横幅がaピクセル及び縦幅がbピクセルとすると、横方向のエントリ数がW/aで求められた数pであり、縦方向のエントリ数がb×2(1/2)を四捨五入して整数とし1を加算した数qとした根拠を説明する。キャッシュメモリ25のアクセスにおいて、画像データをラスタースキャンにより読み出す際に事実として、以下の状態が存在する。図2は、回転角度θの走査線と、2次元方形領域におけるピクセルとの関係を説明する図である。図2(a)は、回転角度θが45°未満の場合における走査線が通過する2次元方形領域との対応を示す図である。図2(b)は、回転角度θが45°以上の場合における走査線が通過する2次元方形領域との対応を示す図である。

(事実1)走査線単位にラスタースキャン方式の読み出しを行うため、常に走査線に沿った一方向にアドレスが進む特性を有している。表示画面における走査線毎のピクセルデータの読み出しが終了すると、表示画面の上端から下端に向かって走査線を移動し、順次ピクセルデータを読み出す。途中で前の走査線のピクセルデータを読み出すことはなく、一度読み出したピクセルデータは2度と使用しない。

(事実2)表示メモリ3の画像データにおけるピクセルデータを図2(a)に示すように、回転角度θ=45°でキャッシュする場合を考えると、4×4の2次元方形領域(矩形領域)は、ピクセルデータの読み出しにおいて、最大で6本の走査線を描画する際に用いられる。すなわち、「4×(2)1/2=5.7≒6」であり、6走査線以内のシノニム(他の2次元方形領域のデータへの置き換え)を許容すると意図しない画像の崩れ(乱れ)が生じる。

(事実3)6走査線にわたって用いられたキャッシュエントリは、次の走査線を表示する際には用いられない。このキャッシュエントリには新たな2次元方形領域のピクセルデータを書き込むことが許容される。

(事実4)ヘッドアップ表示モードにおいて、回転角度θは同一フレーム(表示画面に表示される画像)内で変更されることはない。

(事実5)図2に示すように、回転角度θが45°以内の場合(図2(a))、同一走査線において、2次元方形領域の縦方向の連続数は2以下である。一方、回転角度θが45°以上の場合(図2(b))、同一走査線において、2次元方形領域の縦方向の連続数は3以上である。

(事実6)隣接した走査線間でラスタースキャン読み出しを行う回転角度θが45°以内とすると、事実5に記載したように、隣接する2次元方形領域の縦方向の連続数は2以下である。また、回転角度θが45°以上の場合、隣接する2次元方形領域の縦方向の連続数は4以上となる場合がある(図2(b))。

上記において、45°以内とは後述する角度範囲R1の場合を指し、45°以上とは角度範囲R2の場合を指している。

【0031】

次に、図3は、2次元方形領域がa×aの場合の回転角度θ=45°の場合における、走査線と2次元平行形領域との対応を示す図である。

上述した事実により、図3に示すように、2次元方形領域がa×aの場合、すなわち2次元方形領域が4×4の場合、回転角度θが45°であり、2次元方形領域600のピクセルが走査線に使用されると、走査線は隣接する2次元方形領域の列において、2次元方形領域601、602及び603のピクセルのいずれかが使用されるのが判る。

事実2、事実5及び事実6より、回転角度θが45°未満の場合、キャッシュメモリ25に6本分の走査線に対応するピクセルデータしか保存できないとすると、走査線7本目のピクセルデータを保存するため、キャッシュの入れ替えが必要となる。しかしながら、図2(a)で示すように、走査線間で共有する2次元方形領域が存在するため、例えば、2次元方形領域600において走査線6本分のピクセルデータが使用された場合でも、隣接する列の2次元方形領域603が2次元方形領域600における6本目の走査線と共通に使用された場合でも、2次元方形領域602及び603はまだ使用される可能性があるため、ピクセルデータの入れ替えはできない。

【0032】

ここで、キャッシュのエントリマトリクスは、1走査線のアクセスでシノニムが発生しない構成が必要となる。角度範囲R1の場合、1エントリにかかる走査線の本数(最大の再利用回数)は、

q=INT[(a×2(1/2))/b]+1 …(3)

により求まる。ここで、INTは[]内を整数化するため、小数点以下を切り捨てているため、1を加算している。

例えば、2次元方形領域が幅4(a)×縦4(b)の場合、エントリマトリクスは、横のエントリ数p(=W/4)縦のエントリ数qは2となる。これにより、1走査線の間にシノニム(異なる走査線の間で使用するピクセルデータが同一のエントリに格納されている状態)が発生しないエントリマトリクスが得られる。

ここで、a=b=4であり、q=2の場合、図3(a)に示すように、走査線NによりエントリAに含まれるピクセルデータpaを参照した際、走査線NはエントリB’も参照される。走査線N+1ではピクセルデータpaに隣接するピクセルデータpbが必要であるが、エントリマトリクスの構成において、q=2としているため、エントリB’とエントリBとはシノニムの関係にある。ここで、エントリB’の最終アクセスは走査線Nで行われている。走査線N+1においてエントリB’を参照する際、前回の最終アクセスが走査線Nであったため、後述するキャッシュミス検出部26によるキャッシュミス検出処理が誤判定することになる。誤判定であるが、ヒットしたとして新たに表示メモリ3からの2次元方形領域の画像データの読み出しが行われず、そのままエントリB’のピクセルデータがエントリBのピクセルデータとして読み出され、表示される画像が乱れてしまう

そのため、エントリマトリクスの縦のエントリ数q=3とすることにより、図3(b)に示すように、エントリC’とエントリBとはシノニムの関係とはならないため、キャッシュミス検出部26によるキャッシュミス検出処理が正常に行われることなる。したがって、上記(3)式の結果に1を加算する必要があり、エントリマトリクスの縦のエントリ数qを算出する際に用いる式は、(4)式となる。

q=INT[(a×2(1/2))/b]+2

エントリマトリクスの縦のエントリの配列数は「3」とすることになる。この結果、7本の走査線の保存が可能となる。したがって、表示画面の画面幅を2048とし、2次元方形領域をピクセルデータ4×4とした場合、エントリマトリクスは横幅512(=2048/4)個のエントリであり、縦幅3個のエントリである1536個のエントリから形成される。すでに述べたように、エントリには2次元方形領域毎の4×4個のピクセルデータ(階調度に依ってそのビット数は変化する)が格納される。

【0033】

また 上述した事実6により、横方向に隣接する縦方向の2次元方形領域の連続数と、縦方向に隣接する横方向の2次元方形領域の連続数との関係が逆転するため、回転角度θが以下に示す角度範囲に応じて、エントリアドレスの作成ルールを変更し、キャッシュメモリ25におけるエントリマトリクスを有効に使用する。すなわち、45°以内と45°以上とでは、走査線のラスタースキャンによる2次元方形領域毎の並びが変化するため、この変化に対応させてエントリマトリクスのアドレスを変換する。

・角度範囲R1として、回転角度θが、(7π/4)から(π/4)までの間及び(3π/4)から(5π/4)までの間、

すなわち(7π/4)<θ<(π/4)、(3π/4)<θ<(5π/4)までの間において、(1)式によりエントリアドレスを生成し、

・角度範囲R2として、回転角度θが、(π/4)から(3π/4)まで間及び(5π/4)から(7π/4)までの間、

すなわち、(π/4)≦θ≦(3π/4)、(5π/4)≦θ≦(7π/4)までの間において、(2)式によりエントリアドレスを生成する。

【0034】

すなわち、エントリアドレス生成部22は、供給される回転角度θの値が、角度範囲R1にあるか角度範囲R2にあるかの検出を行う。そして、エントリアドレス生成部22は、回転角度θの値が角度範囲R1の場合、Cad={y[3:2],x[10:2]}としてエントリアドレスを生成し、一方、回転角度θの値が角度範囲R2の場合、Cad={x[3:2],y[10:2]}としてエントリアドレスを生成する。これにより、いずれの回転角度θにおいても、エントリマトリクスに対して7本以上の走査線のピクセルデータを記憶させることができる。結果として、少ないエントリマトリクスにより、シノニムを発生させずに、回転角度θがいずれの値であっても、高速にピクセルデータをLCDコントローラ1へ供給することができる。

【0035】

次に図1を参照して、本実施形態におけるキャッシュメモリ装置におけるキャッシュメモリ25に対する行う制御について説明する。本実施形態においては、キャッシュメモリ25のエントリ各々に対するピクセルデータの入れ替えは、走査線の連続性により行う。

本実施形態においては、すでに説明した構成の他に、番号記憶部27及び番号記憶制御部28を備えている。

番号記憶部27は、キャッシュメモリ25におけるエントリマトリクスのエントリ各々に対応した記憶領域を有している。

番号記憶制御部28は、LCDコントローラ1が表示アドレスから求めた走査線番号を入力し、エントリに記憶されているピクセルデータが読み出される毎に、その時点の走査線番号を番号記憶部27における読み出したピクセルデータが記憶されたエントリに対応した記憶領域に書き込む。この走査線番号は、画像表示における垂直ブランク期間中に、LCDコントローラ1から供給される垂直同期信号により初期値(「0」)に設定され、1本目の走査線のピクセルデータが含まれる2次元方形領域のピクセルデータを、表示メモリ3から読み出す。ここで、番号記憶制御部28は、番号記憶部27に記憶された走査線番号と比較する番号として、表示画面への表示開始から、表示画面に表示する走査線の数を走査線番号としてカウントしたものを用いても良い。

【0036】

キャッシュミス検出部26は、2次元方形領域のピクセルデータが記憶されたエントリがラスタースキャンによりアクセスされた際、アクセスされたエントリに対応して番号記憶部27に記憶されている走査線番号と、現在のラスタースキャンを行っている(LCDコントローラ1から供給される)走査線番号とが同一または連続しているかのいずれであるか否かの判定を行い、同一でなくかつ連続もしていない場合をキャッシュミスとして検出する。

また、キャッシュミス検出部26は、キャッシュミスを検出した場合、キャッシュメモリ書込制御部23に対して、エントリのピクセルデータの上書きを要求する制御信号を出力する。

これにより、キャッシュメモリ書込制御部23は、現在の走査線番号に対応するピクセルデータの含まれる2次元方形領域のピクセルデータを、読み出そうとしてキャッシュミスとなったメモリアドレス(領域メモリアドレス)により、表示メモリ3から読み出し、エントリマトリクスにおけるキャッシュミスとして検出されたエントリアドレスの示すエントリに上書きする。

【0037】

上述したように、キャッシュメモリ読出制御部24は、Xアドレス及びYアドレスが供給されると、エントリアドレス生成部22がXアドレス及びYアドレスから求めたエントリからピクセルデータを読み出す処理を行う。

このとき、キャッシュミス検出部26は、LCDコントローラ1から供給されている走査線番号と、読み出そうとしているエントリに対応して番号記憶部27に記憶されている走査線番号との比較を行い、同一か連続している走査線番号である場合、キャッシュメモリ読み出し制御部24に対して、読み出して良いことを示す制御情報を出力する。また、番号記憶制御部28は、表示アドレスに対応した現在の走査線番号を、ピクセルデータを読み出したエントリに対応した、番号記憶部27の記憶領域に対して書き込む。

これにより、キャッシュメモリ読出制御部24は、キャッシュメモリ25からエントリアドレスにより読み出したピクセルデータをLCDコントローラ1に対して出力する。

【0038】

一方、キャッシュミス検出部26は、LCDコントローラ1から供給されている走査線番号と、読み出そうとしているエントリに対応して番号記憶部27に記憶されている走査線番号との比較を行い、同一かつ連続してもいない走査線番号である場合、キャッシュメモリ読み出し制御部24に対して、読み出しを停止することを示す制御情報を出力する。また、キャッシュミス検出部26は、キャッシュミスしたエントリをアクセスしたメモリアドレスにより、表示メモリ3から2次元方形領域のピクセルデータの読み出し処理を要求する制御信号を、キャッシュメモリ書込制御部23に対して出力する。

読み出し処理を要求する制御信号が供給されることにより、キャッシュメモリ書込制御部23は、LCDコントローラ1から供給される、ピクセルの表示アドレスから変換した表示メモリの2次元方形領域を示す領域メモリアドレスにより表示メモリ3をアクセスし、表示メモリ3から領域メモリアドレスの示す2次元方形領域のピクセルデータを読み出す。また、番号記憶制御部28は、表示アドレスに対応した現在の走査線番号を、ピクセルデータを読み出したエントリに対応した、番号記憶部27の記憶領域に対して書き込む。

【0039】

そして、キャッシュメモリ書込制御部23は、読み出した2次元方形領域のピクセルデータを、エントリアドレス生成部22がメモリアドレスから生成したエントリアドレスの示すエントリに書き込む。

これにより、LCDコントローラ1が要求したメモリアドレスに対応する2次元方形領域のピクセルデータがキャッシュメモリ25のエントリに書き込まれる。

次に、キャッシュメモリ書込制御部23は、キャッシュミスしたエントリに対し、走査線に対応した新たなピクセルデータの書き込みが終了したことを示す終了信号を、キャッシュメモリ読出制御部24に対して出力する。

終了信号が供給されると、キャッシュメモリ読出制御部24は、エントリアドレス生成部22が出力するエントリアドレスの示すエントリに記憶されているピクセルデータを読み出し、LCDコントローラ1に対して出力する。

そして、LCDコントローラ1は、キャッシュメモリ装置2から供給されたピクセルデータを表示装置に表示させる。

【0040】

また、図1におけるキャッシュメモリ装置におけるキャッシュメモリ25を制御する機能を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、この記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することによりキャッシュメモリ25の制御を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものとする。

【0041】

また、「コンピュータシステム」は、WWWシステムを利用している場合であれば、ホームページ提供環境(あるいは表示環境)も含むものとする。

また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムを送信する場合の通信線のように、短時間の間、動的にプログラムを保持するもの、その場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリのように、一定時間プログラムを保持しているものも含むものとする。また上記プログラムは、前述した機能の一部を実現するためのものであっても良く、さらに前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるものであっても良い。

【0042】

以上、この発明の実施形態を図面を参照して詳述してきたが、具体的な構成はこの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計等も含まれる。

【産業上の利用可能性】

【0043】

本実施形態においては、レーダ装置におけるレーダ画像のヘッドアップ表示モードにおける動作として説明したが、車などのナビゲーションシステムのように、ヘッドアップ表示が行われるような、画像メモリの座標系に対し、表示画面の座標系が回転されるなどして異なっている場合には、画像表示を高速に行うことが可能となる。

【符号の説明】

【0044】

1…LCDコントローラ 2…キャッシュメモリ装置 3…表示メモリ 22…エントリアドレス生成部 23…キャッシュメモリ書込制御部 24…キャッシュメモリ読出制御部 25…キャッシュメモリ 26…キャッシュミス検出部 27…番号記憶部 28…番号記憶制御部

【技術分野】

【0001】

本発明は、キャッシュメモリ装置及び制御方法に関するものである。

【背景技術】

【0002】

船舶用レーダあるいはナビゲーションシステム等の表示装置の表示画面において、自身を原点とした自身の進行をy軸とし、このy軸に対して垂直な軸をx軸とした2次元座標系(以下、表示2次元座標系)に海図あるいは地図などを表示させる画像表示方式がある。

例えば、船舶用レーダの場合においては、船舶自身の進行方向を画面の上部、すなわち進行方向に平行な軸をY軸として、海図画像を表示画面に表示するヘッドアップ表示モードがある。

【0003】

しかし、一般的に、海図画像は、海図画像の画像データを蓄積する表示メモリにおいて、北の方向に平行な軸をY軸とする場合など、船の進行方向と異なる方向の2次元座標系(メモリ2次元座標系)で記憶されている。

したがって、ノースアップ表示モードの表示から、船の進行方向をY軸として表示画面に海図画像を表示する表示モードに変更した場合、すなわち海図画像を船の進行方向を上部として表示するヘッドアップ表示モードに変更した場合、表示メモリに記憶されている海図画像を船の進行方向が上部となるように再描画する必要がある。

この表示メモリに対して再描画を行う構成の場合、船首方位が更新される度に表示が行われるまでに時間がかかってしまう。

そのため、表示メモリの海図画像の再描画を行う一般的な構成ではなく、船首方位が更新されたとしても、表示メモリに記憶される海図画像の再描画を行なわず、表示モード変更後の海図画像の表示を高速に行うため、以下の方法が用いられる場合がある。

すなわち、表示2次元座標系の表示画面に対して表示メモリの画像データを表示させる際、表示2次元座標系の座標点(表示2次元座標系の表示画面におけるピクセルの位置を示す点)の座標を、表示メモリにおけるメモリ2次元座標系の座標点(メモリ2次元座標系で記憶された画像データにおけるピクセルの位置を示す点)の座標に、メモリ2次元座標系における自身の位置を中心として表示2次元座標系を回転させた座標変換を行う。

【0004】

この座標変換の結果得られた座標により、メモリ2次元座標系における表示メモリから、表示2次元座標系における座標を読み出し、すなわち、メモリ2次元座標系の画像データから、表示2次元座標系の表示画面に表示する表示画像データを切り出して表示させることになる。

図4はメモリ2次元座標系における画像データと表示2次元座標系における表示画像データとの関係を説明する図である。図4において、図4(a)はメモリ2次元座標系に対して表示2次元座標系が回転されておらず平行移動している場合であり、図4(b)はメモリ2次元系に対して表示2次元座標系回転及び平行移動している場合を示している。

【0005】

次に、図4(a)の場合におけるメモリ2次元座標系の表示メモリの画像データから、表示2次元座標系による表示領域の表示画像データにおけるピクセルのデータ(以下、ピクセルデータ)の読み出しについて説明する。

表示メモリからの表示画像データの読み出しは、表示領域を表示画面に表示する走査線方向にデータを読み出すラスタースキャン方式により行われる。

このため、表示メモリが図4(a)に示されるように、X軸方向がNドット、Y軸方向がMドットであり、表示2次元座標系のx軸及びy軸の各々が、それぞれメモリ2次元座標系のX軸、Y軸と平行である場合において、表示メモリの画像データから表示画面(X軸方向にnドット、Y軸方向にmドット)に対応する表示領域の表示画像データピクセルデータの読み出しを以下の様に行う。

【0006】

ピクセルデータの読み出しの際、図4(a)の場合、メモリ2次元座標系に対して表示2次元座標系が回転しておらず、表示領域内のピクセルデータのアドレスを、ラスタースキャン方向の行毎に順次、表示2次元座標系からメモリ2次元座標系に行平行移動のみの座標変換を行う。

そして、表示領域のピクセルのデータを、表示領域の左上端から開始し、X軸方向(ラスタースキャン方向)へ直線的にnピクセル分移動し、表示領域の右端に達すると順次Y軸方向に隣接する下部のピクセルデータの行へ移動させ、X軸方向を表示領域の左端へ戻した後、X軸方向に直線移動を行いつつピクセルデータを読み出す。また、表示領域における最後のピクセルのデータ、すなわち表示領域の右下の位置にあるピクセルのデータを読み出した後、表示領域のピクセルのデータの読み出しの始点である左上端に戻り、上述した読み出し動作を繰り返す。

【0007】

一方、図4(b)に示されるように、表示2次元座標系がメモリ2次元座標系に対して、回転角度θで回転し、平行移動している場合、すなわち船舶の進行方向が北の方向(Y軸)に対して、自船位置を原点として回転角度θで回転し、かつ平行移動している場合において、表示メモリの画像データから、表示画面に対応する表示領域の表示画像データにおけるピクセルデータの読み出しを以下の様に行う。

すでに述べたように、表示2次元座標系における座標を、メモリ2次元座標系の座標に座標変換し(回転及び平行移動の処理を行い)、得られた表示画像データのメモリ2次元座標系におけるアドレスを用いて、表示領域の左上の座標点から、図4(a)のスキャン方向に対して、回転角度θ傾いたスキャン方向に順次ピクセルのデータを読み出す処理を行う。表示領域内におけるピクセルデータの読み出しは、図4(a)と同様なラスタースキャン方式で行われるが、読み出しに際して、上述した回転を含む座標変換が行われることになる。

【0008】

一方、ある方向を基準として、例えば図4(b)に示すように、北方向に平行な軸をY軸として表示メモリに格納されたメモリ2次元座標系の画像データから、高速に任意の回転角度θの表示画像データを読み出す場合、実装として最も簡易な構成としてはランダムアクセスが可能なSRAM(Static Random Access Memory)を用いることになる。

しかしながら、表示メモリには表示装置の画素数に比較し、より多くの画像数のピクセルのデータが記憶されており、大きな容量が必要となるため、SRAMを用いると製造コストが非常にかかってしまう。

このため、表示装置に表示する画像データを蓄積する表示メモリとしては、データ量に対して価格の安いSDRAM(Synchronous Dynamic Random Access Memory)が多用されている。

【0009】

このSDRAMは、SRAMのように、ピクセルデータを単位とした高速なランダムアクセスを、そのデータを読み出す構成により行うことができない。

すなわち、SDRAMは、記憶領域におけるメモリセルのアクセスにおいて、ロウアドレスが選択されている場合、ページ単位読み出しとして、カラムアドレスを変化させることで、小単位(例えば、ピクセルデータ単位)のデータを、同一のロウアドレスにおける連続したアドレス範囲においてのみ高速にアクセスできる。

しかしながら、メモリアクセスを行う際にロウアドレスを変更する場合、ロウアドレスを活性化させるためのオーバーヘッドが乗じるため、ロウアドレスを変更するアドレス変化を伴うランダムアクセスを高速に実行することができない。

したがって、SDRAMから複数のピクセルデータをブロック単位に読み出し、ランダムアクセスが可能なSRAMにより構成したキャッシュメモリに対し、ブロック単位に読み出したピクセルデータを一旦記憶させ、キャッシュメモリからラスタースキャン方式によりピクセルデータを読み出し、表示画面に表示させている(例えば、特許文献1参照)。

【0010】

ここで、図5を用いてさらに説明する。図5は、表示メモリにおけるピクセルデータの記憶形式を示す図である。

例えば、特許文献1においては、図5(a)に示すように、表示メモリは、X軸方向にNドット、Y軸方向にMドットで構成され、全体としてN×Mピクセルのピクセルデータからなる画像データが記憶されている。ここで、各メモリアクセス1サイクルでアクセスされる1アドレスには、例えば、2次元方形領域8ドット×8ピクセルデータの64ピクセルデータが配置されるように、N×Mピクセルの各ピクセルデータが表示メモリに記憶されている。この2次元方形領域は例として示す同図(b)に示されるように、ピクセルデータD0からピクセルデータD63の64個のピクセルデータにより構成されている。

したがって、表示メモリからは各2次元方形領域A0、…、AN/K−1、…、Anが指定されると、その方形領域に含まれる64ピクセルデータが連続してブロックとして読み出され、キャッシュのエントリに対して書き込まれる。この2次元方形領域としては、8×8ピクセルデータとして説明したが、4×4ピクセルデータ、あるいは2×2ピクセルデータ等の正方領域でよく、また正方領域に限らず、長方領域とすることも出来る。ここで、kは2次元方形領域を正方形とした場合の各辺のピクセル数を示している(1ピクセルデータは、例えばピクセルの階調度を示すデータであり複数のビットから構成されている)。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2002−181919号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

しかしながら、特許文献1に示すレーダ装置における画像表示においては、表示画面に表示させる画像の解像度を上げるにつれ、表示するピクセルデータの量が増加するため、より大きな帯域幅が必要となる。したがって、SDRAMのアクセスタイムあるいは回転角度θによっては、メモリのデータ読み出しの帯域幅が不足する虞がある。また、回転角度θにおいては45°付近において、ロウアドレスの変更を伴うアクセス回数が増加することにより、データ読み出しの時間が増加することにより、データ読出の帯域幅が不足することになる。

この結果、表示画面に表示する全ての画像データを、表示メモリから読み出すことができず、表示画面の一部が直前に表示された画像データのままとなってしまう。

【0013】

また、特許文献1においては、キャッシュメモリに記憶されている2次元方形領域のピクセルのデータから、ラスタースキャンにおいてスキャン方向に配置されているピクセルのデータを読み出した後に、新たな2次元方形領域のピクセルデータを、SDRAMから読み出して、キャッシュメモリに上書きする処理を行っている。

【0014】

このため、2次元方形領域に複数の走査線に対応するピクセルデータが記憶されていたとしても、その一部しか利用していないことになる。例えば、図5(b)における矢印で示したスキャン方向に読み出されるピクセルデータは8ピクセル分である。すなわち、読み出した64ピクセルのデータ中において、実際に用いられるのは8ピクセル分のみであり、12.5%の利用率しかないことになる。

したがって、SDRAMからのデータ読出における限られた帯域幅を有効に使う必要があるが、引用文献1に記載された方法では、キャッシュメモリに記憶された2次元方形領域のピクセルのデータの利用率が不十分な状態において、キャッシュメモリの使用が行われている。

【0015】

本発明は、上記の課題を考慮してなされたものであって、記憶された2次元方形領域のピクセルのデータの利用率を上げ、表示メモリからの読み出すデータの帯域幅が同一であっても、より解像度の高い画像を表示することを可能とするキャッシュメモリ装置、制御方法を提供することを目的とする。

【課題を解決するための手段】

【0016】

本発明のキャッシュメモリ装置は、表示メモリから読み出され、画像表示に用いられる画像データを、キャッシュするメモリであり、画像データを分割した2次元方形領域毎の分割画像データ毎に、メモリを構成するエントリに書き込まれ、表示する画像データの横幅がWピクセルである場合、2次元方形領域の横幅がaピクセル及び縦幅がbピクセルの場合、横方向のエントリ数がW/aで求められた数pであり、縦方向のエントリ数が[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されたキャッシュメモリと、表示メモリから指定された角度θでラスタースキャンにより分割画像データを読み出すための、表示画面の座標系におけるピクセルデータの表示アドレスを、表示メモリに記憶された画像データの座標系へ角度θによる座標変換が行われた、表示メモリにおける2次元方形領域のメモリアドレスが入力され、メモリアドレスからエントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成するエントリアドレス生成部と、メモリアクセス1サイクルの動作で、記憶している表示画像データにおける2次元方形領域毎の分割画像データの一括した書き込み及び読み出しが可能な表示メモリから、指定されたメモリアドレスを用いた角度θのラスタースキャンにより、分割画像データを読み出し、エントリアドレスを用いてキャッシュメモリのエントリに書き込むキャッシメモリ書込制御部と、エントリから指定された角度θのラスタースキャンにより、分割画像データに含まれた、表示される画像データの走査線全てに対応するピクセルデータを順次読み出すキャッシュメモリ制御部とを有することを特徴とする。

【0017】

本発明のキャッシュメモリ装置は、エントリアドレス生成部が、メモリアドレスからエントリアドレスを生成する際、角度θが、(7π/4)から(π/4)までの間及び(3π/4)から(5π/4)までの間の場合、メモリアドレスのX軸方向の座標をエントリマトリクスの横方向の列アドレスに対応させ、Y軸方向の座標をエントリマトリクスの縦方向の行アドレスに対応させてエントリアドレスを生成し、角度θが、(π/4)から(3π/4)まで間及び(5π/4)から(7π/4)までの間の場合、メモリアドレスのX軸方向の座標をエントリマトリクスの縦方向の行アドレスに対応させ、Y軸方向の座標をエントリマトリクスの横方向の列アドレスに対応させてエントリアドレスを生成することを特徴とする。

【0018】

本発明のキャッシュメモリ装置は、エントリマトリクスにおけるエントリ各々に対応した記憶領域を有する番号記憶部と、表示画面への表示開始から、当該表示画面に表示される走査線の数を走査線番号としてカウントし、エントリに記憶されているピクセルデータを読み出す毎に、その時点の走査線番号を番号記憶部に書き込む番号記憶制御部と、2次元方形領域が記憶されたエントリをラスタースキャンによりアクセスする際、当該エントリに記憶されている走査線番号と、現在の走査線番号とが同一または連続しているかのいずれであるか否かの判定を行い、同一でなくかつ連続していない場合をキャッシュミスとして検出するキャッシュミス検出部とをさらに有し、キャッシュミス検出部がキャッシュミスを検出した場合、キャッシメモリ書込制御部が現在の走査線番号に対応するピクセルデータの含まれる2次元方形領域のピクセルデータを表示メモリから読み出し、エントリマトリクスにおけるキャッシュミスとして検出されたエントリに上書きすることを特徴とする。

【0019】

本発明のキャッシュメモリ装置は、2次元方形領域が2の倍数のa=bの正方形であることを特徴とする。

【発明の効果】

【0020】

この発明によれば、キャッシュメモリの各エントリに記憶された分割画像データから、表示される画像の全ての走査線に対応するピクセルデータを読み出すため、従来の様に、各エントリの分割画像データから1走査線分のピクセルデータしか使用しない場合に比較し、分割画像データにおけるピクセルデータの利用率を向上させることができ、表示メモリからの読み出しの帯域幅が同一であっても、より解像度の高い画像を表示することが可能となる。

【図面の簡単な説明】

【0021】

【図1】この発明の一実施形態によるキャッシュメモリ装置を用いた表示制御装置の構成例を示す概略ブロック図である。

【図2】回転角度θの走査線と、2次元方形領域におけるピクセルとの関係を説明する図である。

【図3】2次元方形領域がa×aの場合の回転角度θ=45°の場合における、走査線と2次元平行形領域との対応を示す図である。

【図4】メモリ2次元座標系における画像データと表示2次元座標系における表示画像データとの関係を説明する図である。

【図5】表示メモリにおけるピクセルデータの記憶形式を示す図である。

【発明を実施するための形態】

【0022】

以下、図面を参照して、本発明の実施の形態について説明する。図1は、この発明の一実施形態によるキャッシュメモリ装置を用いた表示制御装置の構成例を示す概略ブロック図である。本実施形態において、表示制御装置の制御対象はLCD(Liquid Crystal Display)表示装置である。例えば、本発明は、例えば、船舶、車などのレーダ装置の画像表示に用いられる。以下、船舶のレーダ装置のヘッドアップ表示(自身の進行方向を表示画面の上部とする表示)モードにおける画像表示の処理として説明する。

【0023】

図1における表示制御装置は、LCDコントローラ1、キャッシュメモリ装置2及び表示メモリ3を備えている。表示メモリ3には、記憶容量が大きく、一回のメモリアクセスにより複数のビットデータの読出が可能なSDRAMなどが用いられている。表示メモリ3は、例えば、レーダ装置の表示装置に表示する画像データが一定の向きで、例えばY軸方向が南北軸に平行となり、X軸方向が東西軸に平行となるように記憶されている。表示メモリ3は、図4に示すように、表示装置に表示される表示画像データの画像領域より大きい画像領域のピクセルデータを有している。また、表示メモリ3は、画像データを複数に分割した2次元平行形領域毎の分割画像データを、連続したメモリアドレスにより記憶している。表示メモリ3は、例えば、図5(b)に示すような2次元平行形領域毎の分割として、SDRAMのROW(ワード線)毎に、画像データの32×32ピクセルの矩形領域のデータが格納されている。後述するように、キャッシュメモリ装置2は、表示メモリ3から4×4ピクセルの2次元平行形領域毎の分割画像データを単位として、表示メモリ3から読み出すため、同一の32×32ピクセル範囲内からの2次元平行形領域の読み出しを高速化することができる。

【0024】

LCDコントローラ1は、図示しないCPU(Central Processing Unit)から南北方向を基準として回転した角度である回転角度θと、表示装置に表示される表示画像の中心にあるピクセルの表示メモリ3におけるメモリアドレスとが入力される。ここで、LCDコントローラ1は、内部記憶部に表示装置の表示画面の横のピクセル数W及び縦のピクセル数Hが予め設定されている。そして、LCDコントローラ1は、記憶されている表示画面の大きさ(W×Hピクセル)と、供給される表示画面の中心のメモリアドレスと、回転角度θとから、図4(b)に示すように、走査線に位置するピクセルデータを読み出すためのラスタースキャン読み出しを行うメモリアドレスを算出する。

【0025】

LCDコントローラ1は、ラスタースキャン読み出しのため、走査線に対応するピクセルのメモリアドレス(Xアドレス、Yアドレス)を、回転角度θ(指定された角度)に応じて以下の式を用いて算出する。

X=XC+Rsinθ

Y=YC+Rcosθ

XCは、表示画像の中心にあるピクセルの表示メモリ3におけるメモリアドレスのXアドレスである。YCは、表示画像の中心にあるピクセルの表示メモリ3におけるメモリアドレスのYアドレスである。Rは表示画像における表示アドレスから表示メモリのメモリアドレスに変換するピクセルの画像中心のピクセルからの距離(ピクセル数)である。すなわち、LCDコントローラ1は、図4の説明と同様に、表示2次元座標系における座標を、メモリ2次元座標系の座標に座標変換し、メモリアドレスを求めている。

また、LCDコントローラ1は、求めたメモリアドレスから、2次元方形領域を示す領域メモリアドレス(メモリアドレスの先頭アドレス)を生成し、メモリアドレスとともにこの領域メモリアドレスをキャッシュメモリ装置2へ出力する。

【0026】

キャッシュメモリ装置2は、LCDコントローラ1から供給される回転角度θ、表示メモリ3におけるピクセルデータのアドレス(Xアドレス、Yアドレス)、現在アクセスしているピクセルデータの存在する走査線番号により、表示メモリ3から表示画像データをキャッシュ(使用頻度の高いデータを高速なメモリに蓄えておく処理)する。

このキャッシュメモリ装置2は、エントリアドレス生成部22、キャッシュメモリ書込制御部23、キャッシュメモリ読出制御部24、キャッシュメモリ25、キャッシュミス検出部26、番号記憶部27、番号記憶制御部28とを備えている。

【0027】

キャッシュメモリ25は、表示メモリ3から読み出され、画像表示に用いられる画像データを、一旦キャッシュするメモリであり、高速にランダムアクセスが可能なSRAMなどで構成されている。

また、キャッシュメモリ25は、画像データを分割した2次元方形領域毎の分割画像データを、メモリを構成するエントリ毎に記憶する。このキャッシュメモリ25は、表示する画像データの横幅がWピクセルである場合、2次元方形領域の横幅がaピクセル及び縦幅がbピクセルとすると、横方向のエントリ数がW/aで求められた数pであり、縦方向の[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されている。本実施形態においては、2次元方形領域をa=b=2として各エントリを形成している(理由は後述)。また、2次元方形領域は、a≠bの長方形でも良い。

【0028】

キャッシュメモリ書込制御部23は、図4の説明と同様の表示メモリ3からの読み出し処理により、LCDコントローラ1から供給される領域メモリアドレスが示す2次元方形領域のピクセルデータ(分割画像データ)を、表示メモリ3から読み出す。そして、キャッシュメモリ書込制御部23、キャッシュメモリ25に対し、エントリアドレス生成部22の生成するエントリアドレス(後述)の示すエントリに、読み出したピクセルデータを書き込む。

キャッシュメモリ読出制御部24は、エントリアドレス生成部22がLCDコントローラ1から供給されるメモリアドレス(Xアドレス、Yアドレス)から変換したエントリアドレスの示すエントリにより、このエントリに記憶されている2次元方形領域におけるメモリアドレス(Xアドレス、Yアドレス)示すピクセルデータを読み出し、LCDコントローラ1へ出力する。

【0029】

エントリアドレス生成部22は、メモリアドレスと領域メモリアドレスから、キャッシュメモリ25におけるエントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成する。以下の場合、4×4ピクセルのデータ(2次元方形領域)が1エントリに格納され、エントリマトリクスは横2048×縦4となっている。

このエントリアドレスCadは、

Cad={y[3:2],x[10:2]} …(1)

、または

Cad={x[3:2],y[10:2]} …(2)

として生成される(後述)。

(1)及び(2)式のいずれの場合においても、それぞれ下位2ビットは2次元方形領域内の4つのピクセルのいずれかの位置を示し、x[s1,r1]における下位2ビット(ピクセルデータの横方向の並び、x座標)以外の上位ビットはエントリマトリクスにおけるエントリの列(横方向の並び、x座標)の位置を示し、y[s2,r2]における下位2ビット(ピクセルデータの縦方向の並び、y座標)以外の上位ビットはエントリマトリクスにおけるエントリの行(縦方向の並び、y座標)の位置を示している。

【0030】

次に、キャッシュメモリ25のエントリマトリクスを、表示する画像データの横幅がWピクセルである場合、2次元方形領域の横幅がaピクセル及び縦幅がbピクセルとすると、横方向のエントリ数がW/aで求められた数pであり、縦方向のエントリ数がb×2(1/2)を四捨五入して整数とし1を加算した数qとした根拠を説明する。キャッシュメモリ25のアクセスにおいて、画像データをラスタースキャンにより読み出す際に事実として、以下の状態が存在する。図2は、回転角度θの走査線と、2次元方形領域におけるピクセルとの関係を説明する図である。図2(a)は、回転角度θが45°未満の場合における走査線が通過する2次元方形領域との対応を示す図である。図2(b)は、回転角度θが45°以上の場合における走査線が通過する2次元方形領域との対応を示す図である。

(事実1)走査線単位にラスタースキャン方式の読み出しを行うため、常に走査線に沿った一方向にアドレスが進む特性を有している。表示画面における走査線毎のピクセルデータの読み出しが終了すると、表示画面の上端から下端に向かって走査線を移動し、順次ピクセルデータを読み出す。途中で前の走査線のピクセルデータを読み出すことはなく、一度読み出したピクセルデータは2度と使用しない。

(事実2)表示メモリ3の画像データにおけるピクセルデータを図2(a)に示すように、回転角度θ=45°でキャッシュする場合を考えると、4×4の2次元方形領域(矩形領域)は、ピクセルデータの読み出しにおいて、最大で6本の走査線を描画する際に用いられる。すなわち、「4×(2)1/2=5.7≒6」であり、6走査線以内のシノニム(他の2次元方形領域のデータへの置き換え)を許容すると意図しない画像の崩れ(乱れ)が生じる。

(事実3)6走査線にわたって用いられたキャッシュエントリは、次の走査線を表示する際には用いられない。このキャッシュエントリには新たな2次元方形領域のピクセルデータを書き込むことが許容される。

(事実4)ヘッドアップ表示モードにおいて、回転角度θは同一フレーム(表示画面に表示される画像)内で変更されることはない。

(事実5)図2に示すように、回転角度θが45°以内の場合(図2(a))、同一走査線において、2次元方形領域の縦方向の連続数は2以下である。一方、回転角度θが45°以上の場合(図2(b))、同一走査線において、2次元方形領域の縦方向の連続数は3以上である。

(事実6)隣接した走査線間でラスタースキャン読み出しを行う回転角度θが45°以内とすると、事実5に記載したように、隣接する2次元方形領域の縦方向の連続数は2以下である。また、回転角度θが45°以上の場合、隣接する2次元方形領域の縦方向の連続数は4以上となる場合がある(図2(b))。

上記において、45°以内とは後述する角度範囲R1の場合を指し、45°以上とは角度範囲R2の場合を指している。

【0031】

次に、図3は、2次元方形領域がa×aの場合の回転角度θ=45°の場合における、走査線と2次元平行形領域との対応を示す図である。

上述した事実により、図3に示すように、2次元方形領域がa×aの場合、すなわち2次元方形領域が4×4の場合、回転角度θが45°であり、2次元方形領域600のピクセルが走査線に使用されると、走査線は隣接する2次元方形領域の列において、2次元方形領域601、602及び603のピクセルのいずれかが使用されるのが判る。

事実2、事実5及び事実6より、回転角度θが45°未満の場合、キャッシュメモリ25に6本分の走査線に対応するピクセルデータしか保存できないとすると、走査線7本目のピクセルデータを保存するため、キャッシュの入れ替えが必要となる。しかしながら、図2(a)で示すように、走査線間で共有する2次元方形領域が存在するため、例えば、2次元方形領域600において走査線6本分のピクセルデータが使用された場合でも、隣接する列の2次元方形領域603が2次元方形領域600における6本目の走査線と共通に使用された場合でも、2次元方形領域602及び603はまだ使用される可能性があるため、ピクセルデータの入れ替えはできない。

【0032】

ここで、キャッシュのエントリマトリクスは、1走査線のアクセスでシノニムが発生しない構成が必要となる。角度範囲R1の場合、1エントリにかかる走査線の本数(最大の再利用回数)は、

q=INT[(a×2(1/2))/b]+1 …(3)

により求まる。ここで、INTは[]内を整数化するため、小数点以下を切り捨てているため、1を加算している。

例えば、2次元方形領域が幅4(a)×縦4(b)の場合、エントリマトリクスは、横のエントリ数p(=W/4)縦のエントリ数qは2となる。これにより、1走査線の間にシノニム(異なる走査線の間で使用するピクセルデータが同一のエントリに格納されている状態)が発生しないエントリマトリクスが得られる。

ここで、a=b=4であり、q=2の場合、図3(a)に示すように、走査線NによりエントリAに含まれるピクセルデータpaを参照した際、走査線NはエントリB’も参照される。走査線N+1ではピクセルデータpaに隣接するピクセルデータpbが必要であるが、エントリマトリクスの構成において、q=2としているため、エントリB’とエントリBとはシノニムの関係にある。ここで、エントリB’の最終アクセスは走査線Nで行われている。走査線N+1においてエントリB’を参照する際、前回の最終アクセスが走査線Nであったため、後述するキャッシュミス検出部26によるキャッシュミス検出処理が誤判定することになる。誤判定であるが、ヒットしたとして新たに表示メモリ3からの2次元方形領域の画像データの読み出しが行われず、そのままエントリB’のピクセルデータがエントリBのピクセルデータとして読み出され、表示される画像が乱れてしまう

そのため、エントリマトリクスの縦のエントリ数q=3とすることにより、図3(b)に示すように、エントリC’とエントリBとはシノニムの関係とはならないため、キャッシュミス検出部26によるキャッシュミス検出処理が正常に行われることなる。したがって、上記(3)式の結果に1を加算する必要があり、エントリマトリクスの縦のエントリ数qを算出する際に用いる式は、(4)式となる。

q=INT[(a×2(1/2))/b]+2

エントリマトリクスの縦のエントリの配列数は「3」とすることになる。この結果、7本の走査線の保存が可能となる。したがって、表示画面の画面幅を2048とし、2次元方形領域をピクセルデータ4×4とした場合、エントリマトリクスは横幅512(=2048/4)個のエントリであり、縦幅3個のエントリである1536個のエントリから形成される。すでに述べたように、エントリには2次元方形領域毎の4×4個のピクセルデータ(階調度に依ってそのビット数は変化する)が格納される。

【0033】

また 上述した事実6により、横方向に隣接する縦方向の2次元方形領域の連続数と、縦方向に隣接する横方向の2次元方形領域の連続数との関係が逆転するため、回転角度θが以下に示す角度範囲に応じて、エントリアドレスの作成ルールを変更し、キャッシュメモリ25におけるエントリマトリクスを有効に使用する。すなわち、45°以内と45°以上とでは、走査線のラスタースキャンによる2次元方形領域毎の並びが変化するため、この変化に対応させてエントリマトリクスのアドレスを変換する。

・角度範囲R1として、回転角度θが、(7π/4)から(π/4)までの間及び(3π/4)から(5π/4)までの間、

すなわち(7π/4)<θ<(π/4)、(3π/4)<θ<(5π/4)までの間において、(1)式によりエントリアドレスを生成し、

・角度範囲R2として、回転角度θが、(π/4)から(3π/4)まで間及び(5π/4)から(7π/4)までの間、

すなわち、(π/4)≦θ≦(3π/4)、(5π/4)≦θ≦(7π/4)までの間において、(2)式によりエントリアドレスを生成する。

【0034】

すなわち、エントリアドレス生成部22は、供給される回転角度θの値が、角度範囲R1にあるか角度範囲R2にあるかの検出を行う。そして、エントリアドレス生成部22は、回転角度θの値が角度範囲R1の場合、Cad={y[3:2],x[10:2]}としてエントリアドレスを生成し、一方、回転角度θの値が角度範囲R2の場合、Cad={x[3:2],y[10:2]}としてエントリアドレスを生成する。これにより、いずれの回転角度θにおいても、エントリマトリクスに対して7本以上の走査線のピクセルデータを記憶させることができる。結果として、少ないエントリマトリクスにより、シノニムを発生させずに、回転角度θがいずれの値であっても、高速にピクセルデータをLCDコントローラ1へ供給することができる。

【0035】

次に図1を参照して、本実施形態におけるキャッシュメモリ装置におけるキャッシュメモリ25に対する行う制御について説明する。本実施形態においては、キャッシュメモリ25のエントリ各々に対するピクセルデータの入れ替えは、走査線の連続性により行う。

本実施形態においては、すでに説明した構成の他に、番号記憶部27及び番号記憶制御部28を備えている。

番号記憶部27は、キャッシュメモリ25におけるエントリマトリクスのエントリ各々に対応した記憶領域を有している。

番号記憶制御部28は、LCDコントローラ1が表示アドレスから求めた走査線番号を入力し、エントリに記憶されているピクセルデータが読み出される毎に、その時点の走査線番号を番号記憶部27における読み出したピクセルデータが記憶されたエントリに対応した記憶領域に書き込む。この走査線番号は、画像表示における垂直ブランク期間中に、LCDコントローラ1から供給される垂直同期信号により初期値(「0」)に設定され、1本目の走査線のピクセルデータが含まれる2次元方形領域のピクセルデータを、表示メモリ3から読み出す。ここで、番号記憶制御部28は、番号記憶部27に記憶された走査線番号と比較する番号として、表示画面への表示開始から、表示画面に表示する走査線の数を走査線番号としてカウントしたものを用いても良い。

【0036】

キャッシュミス検出部26は、2次元方形領域のピクセルデータが記憶されたエントリがラスタースキャンによりアクセスされた際、アクセスされたエントリに対応して番号記憶部27に記憶されている走査線番号と、現在のラスタースキャンを行っている(LCDコントローラ1から供給される)走査線番号とが同一または連続しているかのいずれであるか否かの判定を行い、同一でなくかつ連続もしていない場合をキャッシュミスとして検出する。

また、キャッシュミス検出部26は、キャッシュミスを検出した場合、キャッシュメモリ書込制御部23に対して、エントリのピクセルデータの上書きを要求する制御信号を出力する。

これにより、キャッシュメモリ書込制御部23は、現在の走査線番号に対応するピクセルデータの含まれる2次元方形領域のピクセルデータを、読み出そうとしてキャッシュミスとなったメモリアドレス(領域メモリアドレス)により、表示メモリ3から読み出し、エントリマトリクスにおけるキャッシュミスとして検出されたエントリアドレスの示すエントリに上書きする。

【0037】

上述したように、キャッシュメモリ読出制御部24は、Xアドレス及びYアドレスが供給されると、エントリアドレス生成部22がXアドレス及びYアドレスから求めたエントリからピクセルデータを読み出す処理を行う。

このとき、キャッシュミス検出部26は、LCDコントローラ1から供給されている走査線番号と、読み出そうとしているエントリに対応して番号記憶部27に記憶されている走査線番号との比較を行い、同一か連続している走査線番号である場合、キャッシュメモリ読み出し制御部24に対して、読み出して良いことを示す制御情報を出力する。また、番号記憶制御部28は、表示アドレスに対応した現在の走査線番号を、ピクセルデータを読み出したエントリに対応した、番号記憶部27の記憶領域に対して書き込む。

これにより、キャッシュメモリ読出制御部24は、キャッシュメモリ25からエントリアドレスにより読み出したピクセルデータをLCDコントローラ1に対して出力する。

【0038】

一方、キャッシュミス検出部26は、LCDコントローラ1から供給されている走査線番号と、読み出そうとしているエントリに対応して番号記憶部27に記憶されている走査線番号との比較を行い、同一かつ連続してもいない走査線番号である場合、キャッシュメモリ読み出し制御部24に対して、読み出しを停止することを示す制御情報を出力する。また、キャッシュミス検出部26は、キャッシュミスしたエントリをアクセスしたメモリアドレスにより、表示メモリ3から2次元方形領域のピクセルデータの読み出し処理を要求する制御信号を、キャッシュメモリ書込制御部23に対して出力する。

読み出し処理を要求する制御信号が供給されることにより、キャッシュメモリ書込制御部23は、LCDコントローラ1から供給される、ピクセルの表示アドレスから変換した表示メモリの2次元方形領域を示す領域メモリアドレスにより表示メモリ3をアクセスし、表示メモリ3から領域メモリアドレスの示す2次元方形領域のピクセルデータを読み出す。また、番号記憶制御部28は、表示アドレスに対応した現在の走査線番号を、ピクセルデータを読み出したエントリに対応した、番号記憶部27の記憶領域に対して書き込む。

【0039】

そして、キャッシュメモリ書込制御部23は、読み出した2次元方形領域のピクセルデータを、エントリアドレス生成部22がメモリアドレスから生成したエントリアドレスの示すエントリに書き込む。

これにより、LCDコントローラ1が要求したメモリアドレスに対応する2次元方形領域のピクセルデータがキャッシュメモリ25のエントリに書き込まれる。

次に、キャッシュメモリ書込制御部23は、キャッシュミスしたエントリに対し、走査線に対応した新たなピクセルデータの書き込みが終了したことを示す終了信号を、キャッシュメモリ読出制御部24に対して出力する。

終了信号が供給されると、キャッシュメモリ読出制御部24は、エントリアドレス生成部22が出力するエントリアドレスの示すエントリに記憶されているピクセルデータを読み出し、LCDコントローラ1に対して出力する。

そして、LCDコントローラ1は、キャッシュメモリ装置2から供給されたピクセルデータを表示装置に表示させる。

【0040】

また、図1におけるキャッシュメモリ装置におけるキャッシュメモリ25を制御する機能を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、この記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することによりキャッシュメモリ25の制御を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものとする。

【0041】

また、「コンピュータシステム」は、WWWシステムを利用している場合であれば、ホームページ提供環境(あるいは表示環境)も含むものとする。

また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムを送信する場合の通信線のように、短時間の間、動的にプログラムを保持するもの、その場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリのように、一定時間プログラムを保持しているものも含むものとする。また上記プログラムは、前述した機能の一部を実現するためのものであっても良く、さらに前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるものであっても良い。

【0042】

以上、この発明の実施形態を図面を参照して詳述してきたが、具体的な構成はこの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計等も含まれる。

【産業上の利用可能性】

【0043】

本実施形態においては、レーダ装置におけるレーダ画像のヘッドアップ表示モードにおける動作として説明したが、車などのナビゲーションシステムのように、ヘッドアップ表示が行われるような、画像メモリの座標系に対し、表示画面の座標系が回転されるなどして異なっている場合には、画像表示を高速に行うことが可能となる。

【符号の説明】

【0044】

1…LCDコントローラ 2…キャッシュメモリ装置 3…表示メモリ 22…エントリアドレス生成部 23…キャッシュメモリ書込制御部 24…キャッシュメモリ読出制御部 25…キャッシュメモリ 26…キャッシュミス検出部 27…番号記憶部 28…番号記憶制御部

【特許請求の範囲】

【請求項1】

表示メモリから読み出され、画像表示に用いられる画像データを、キャッシュするメモリであり、前記画像データを分割した2次元方形領域毎の分割画像データ毎に、メモリを構成するエントリに書き込まれ、表示する画像データの横幅がWピクセルである場合、前記2次元方形領域の横幅がaピクセル及び縦幅がbピクセルの場合、横方向の前記エントリ数がW/aで求められた数pであり、縦方向の前記エントリ数が[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されたキャッシュメモリと、

前記表示メモリから指定された角度θでラスタースキャンにより前記分割画像データを読み出すための、表示画面の座標系におけるピクセルデータの表示アドレスを、前記表示メモリに記憶された画像データの座標系へ前記角度θによる座標変換が行われた、前記表示メモリにおける2次元方形領域のメモリアドレスが入力され、前記メモリアドレスから前記エントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成するエントリアドレス生成部と、

メモリアクセス1サイクルの動作で、記憶している表示画像データにおける前記2次元方形領域毎の分割画像データの一括した書き込み及び読み出しが可能な表示メモリから、指定された前記メモリアドレスを用いた前記角度θのラスタースキャンにより、前記分割画像データを読み出し、前記エントリアドレスを用いて前記キャッシュメモリのエントリに書き込むキャッシメモリ書込制御部と、

前記エントリから指定された前記角度θのラスタースキャンにより、分割画像データに含まれた、表示される画像データの走査線全てに対応するピクセルデータを順次読み出すキャッシュメモリ制御部と

を有することを特徴とするキャッシュメモリ装置。

【請求項2】

前記エントリアドレス生成部が、

前記メモリアドレスから前記エントリアドレスを生成する際、

前記角度θが、(7π/4)から(π/4)までの間及び(3π/4)から(5π/4)までの間の場合、前記メモリアドレスのX軸方向の座標を前記エントリマトリクスの横方向の列アドレスに対応させ、Y軸方向の座標を前記エントリマトリクスの縦方向の行アドレスに対応させて前記エントリアドレスを生成し、

前記角度θが、(π/4)から(3π/4)まで間及び(5π/4)から(7π/4)までの間の場合、前記メモリアドレスのX軸方向の座標を前記エントリマトリクスの縦方向の行アドレスに対応させ、Y軸方向の座標を前記エントリマトリクスの横方向の列アドレスに対応させて前記エントリアドレスを生成することを特徴とする請求項1に記載のキャッシュメモリ装置。

【請求項3】

前記エントリマトリクスにおける前記エントリ各々に対応した記憶領域を有する番号記憶部と、

前記表示画面への表示開始から、当該表示画面に表示される走査線の数を走査線番号としてカウントし、前記エントリに記憶されている前記ピクセルデータを読み出す毎に、その時点の走査線番号を前記番号記憶部に書き込む番号記憶制御部と、

前記2次元方形領域が記憶された前記エントリをラスタースキャンによりアクセスする際、当該エントリに記憶されている走査線番号と、現在の走査線番号とが同一または連続しているかのいずれであるか否かの判定を行い、同一でなくかつ連続していない場合をキャッシュミスとして検出するキャッシュミス検出部と

をさらに有し、

前記キャッシュミス検出部がキャッシュミスを検出した場合、

前記キャッシメモリ書込制御部が現在の走査線番号に対応するピクセルデータの含まれる前記2次元方形領域のピクセルデータを前記表示メモリから読み出し、前記エントリマトリクスにおけるキャッシュミスとして検出されたエントリに上書きする

ことを特徴とする請求項1または請求項2に記載のキャッシュメモリ装置。

【請求項4】

前記2次元方形領域が2の倍数のa=bの正方形であることを特徴とする請求項1から請求項3のいずれか一項に記載のキャッシュメモリ装置。

【請求項5】

表示メモリから読み出され、画像表示に用いられる画像データをキャッシュするメモリであり、前記画像データを分割した2次元方形領域毎の分割画像データ毎に、メモリを構成するエントリに書き込まれ、表示する画像データの横幅がWピクセルである場合、前記2次元方形領域の横幅がaピクセル及び縦幅がbピクセルの場合、横方向の前記エントリ数がW/aで求められた数pであり、縦方向の前記エントリ数が[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されたキャッシュメモリに対し、前記表示メモリから指定された角度θでラスタースキャンにより前記分割画像データを読み出すため、表示画面の座標系におけるピクセルデータの表示アドレスを、前記表示メモリに記憶された画像データの座標系へ前記角度θによる座標変換を行い、前記表示メモリにおける2次元方形領域のメモリアドレスが入力され、入力された前記「メモリアドレスにより、分割画像データの読み出し及び書き込みを制御するキャッシュメモリ制御方法であり、

エントリアドレス生成部が、前記メモリアドレスから前記エントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成するエントリアドレス生成過程と、

キャッシメモリ書込制御部が、メモリアクセス1サイクルの動作で、記憶している表示画像データにおける前記2次元方形領域毎の分割画像データの一括した書き込み及び読み出しが可能な表示メモリから、指定された前記メモリアドレスを用いた角度θのラスタースキャンにより、前記分割画像データを読み出し、前記エントリアドレスを用いて前記キャッシュメモリのエントリに書き込むキャッシメモリ書込制御過程と、

キャッシュメモリ読出制御部が、前記エントリから指定された角度θのラスタースキャンにより、分割画像データに含まれた、表示される画像データの走査線全てに対応するピクセルデータを順次読み出すキャッシュメモリ読出制御過程と

を有することを特徴とするキャッシュメモリの制御方法。

【請求項1】

表示メモリから読み出され、画像表示に用いられる画像データを、キャッシュするメモリであり、前記画像データを分割した2次元方形領域毎の分割画像データ毎に、メモリを構成するエントリに書き込まれ、表示する画像データの横幅がWピクセルである場合、前記2次元方形領域の横幅がaピクセル及び縦幅がbピクセルの場合、横方向の前記エントリ数がW/aで求められた数pであり、縦方向の前記エントリ数が[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されたキャッシュメモリと、

前記表示メモリから指定された角度θでラスタースキャンにより前記分割画像データを読み出すための、表示画面の座標系におけるピクセルデータの表示アドレスを、前記表示メモリに記憶された画像データの座標系へ前記角度θによる座標変換が行われた、前記表示メモリにおける2次元方形領域のメモリアドレスが入力され、前記メモリアドレスから前記エントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成するエントリアドレス生成部と、

メモリアクセス1サイクルの動作で、記憶している表示画像データにおける前記2次元方形領域毎の分割画像データの一括した書き込み及び読み出しが可能な表示メモリから、指定された前記メモリアドレスを用いた前記角度θのラスタースキャンにより、前記分割画像データを読み出し、前記エントリアドレスを用いて前記キャッシュメモリのエントリに書き込むキャッシメモリ書込制御部と、

前記エントリから指定された前記角度θのラスタースキャンにより、分割画像データに含まれた、表示される画像データの走査線全てに対応するピクセルデータを順次読み出すキャッシュメモリ制御部と

を有することを特徴とするキャッシュメモリ装置。

【請求項2】

前記エントリアドレス生成部が、

前記メモリアドレスから前記エントリアドレスを生成する際、

前記角度θが、(7π/4)から(π/4)までの間及び(3π/4)から(5π/4)までの間の場合、前記メモリアドレスのX軸方向の座標を前記エントリマトリクスの横方向の列アドレスに対応させ、Y軸方向の座標を前記エントリマトリクスの縦方向の行アドレスに対応させて前記エントリアドレスを生成し、

前記角度θが、(π/4)から(3π/4)まで間及び(5π/4)から(7π/4)までの間の場合、前記メモリアドレスのX軸方向の座標を前記エントリマトリクスの縦方向の行アドレスに対応させ、Y軸方向の座標を前記エントリマトリクスの横方向の列アドレスに対応させて前記エントリアドレスを生成することを特徴とする請求項1に記載のキャッシュメモリ装置。

【請求項3】

前記エントリマトリクスにおける前記エントリ各々に対応した記憶領域を有する番号記憶部と、

前記表示画面への表示開始から、当該表示画面に表示される走査線の数を走査線番号としてカウントし、前記エントリに記憶されている前記ピクセルデータを読み出す毎に、その時点の走査線番号を前記番号記憶部に書き込む番号記憶制御部と、

前記2次元方形領域が記憶された前記エントリをラスタースキャンによりアクセスする際、当該エントリに記憶されている走査線番号と、現在の走査線番号とが同一または連続しているかのいずれであるか否かの判定を行い、同一でなくかつ連続していない場合をキャッシュミスとして検出するキャッシュミス検出部と

をさらに有し、

前記キャッシュミス検出部がキャッシュミスを検出した場合、

前記キャッシメモリ書込制御部が現在の走査線番号に対応するピクセルデータの含まれる前記2次元方形領域のピクセルデータを前記表示メモリから読み出し、前記エントリマトリクスにおけるキャッシュミスとして検出されたエントリに上書きする

ことを特徴とする請求項1または請求項2に記載のキャッシュメモリ装置。

【請求項4】

前記2次元方形領域が2の倍数のa=bの正方形であることを特徴とする請求項1から請求項3のいずれか一項に記載のキャッシュメモリ装置。

【請求項5】

表示メモリから読み出され、画像表示に用いられる画像データをキャッシュするメモリであり、前記画像データを分割した2次元方形領域毎の分割画像データ毎に、メモリを構成するエントリに書き込まれ、表示する画像データの横幅がWピクセルである場合、前記2次元方形領域の横幅がaピクセル及び縦幅がbピクセルの場合、横方向の前記エントリ数がW/aで求められた数pであり、縦方向の前記エントリ数が[a×2(1/2)/b]を整数とした数値に2を加えた数qであるエントリマトリクスで構成されたキャッシュメモリに対し、前記表示メモリから指定された角度θでラスタースキャンにより前記分割画像データを読み出すため、表示画面の座標系におけるピクセルデータの表示アドレスを、前記表示メモリに記憶された画像データの座標系へ前記角度θによる座標変換を行い、前記表示メモリにおける2次元方形領域のメモリアドレスが入力され、入力された前記「メモリアドレスにより、分割画像データの読み出し及び書き込みを制御するキャッシュメモリ制御方法であり、

エントリアドレス生成部が、前記メモリアドレスから前記エントリマトリクスのエントリ各々の位置及び当該エントリの中のピクセルデータの各々の位置を示すエントリアドレスを生成するエントリアドレス生成過程と、

キャッシメモリ書込制御部が、メモリアクセス1サイクルの動作で、記憶している表示画像データにおける前記2次元方形領域毎の分割画像データの一括した書き込み及び読み出しが可能な表示メモリから、指定された前記メモリアドレスを用いた角度θのラスタースキャンにより、前記分割画像データを読み出し、前記エントリアドレスを用いて前記キャッシュメモリのエントリに書き込むキャッシメモリ書込制御過程と、

キャッシュメモリ読出制御部が、前記エントリから指定された角度θのラスタースキャンにより、分割画像データに含まれた、表示される画像データの走査線全てに対応するピクセルデータを順次読み出すキャッシュメモリ読出制御過程と

を有することを特徴とするキャッシュメモリの制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−203363(P2012−203363A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−70879(P2011−70879)

【出願日】平成23年3月28日(2011.3.28)

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月28日(2011.3.28)

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

[ Back to top ]