キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に用いられるキャパシタおよびキャパシタを用いた半導体装置に関する。

【背景技術】

【0002】

半導体集積回路等に用いられるキャパシタは従来、金属や導電性の高いシリコン等の半導体によって形成される電極の間に酸化シリコン等の誘電体を挟む構造のものが用いられてきた。しかしながら、回路が微細化されると酸化シリコン(比誘電率4程度)よりも誘電率の高い材料(high−k材料)を用いることが検討されるようになった。

【0003】

このようなhigh−k材料を用いる際の問題点は、一般にhigh−k材料の電子親和力(真空準位と伝導帯下端とのエネルギー差)が大きいということである。例えば、非特許文献1によると、酸化シリコンの電子親和力は0.9電子ボルトであるのに対し、high−k材料のひとつである酸化ハフニウムの電子親和力は2.5電子ボルトである。

【0004】

このため、例えば、n型シリコンと酸化シリコンの接合では、ポテンシャル障壁が3.5電子ボルトであったのに、n型シリコンと酸化ハフニウムの接合では、ポテンシャル障壁が1.5電子ボルト(接合での分極のため、ポテンシャル障壁は必ずしもn型シリコンの仕事関数と誘電体の電子親和力の差と等しくならないことに注意が必要である)まで低下してしまう。

【0005】

1.5電子ボルト程度の障壁でも誘電体の厚さが5nm以上であれば、絶縁特性に顕著な問題は生じないが、回路の微細化と共に誘電体の厚さも3nm以下となることが要求されると量子効果によるトンネル電流が大きくなり、キャパシタとしての機能が十分に果たせないことが問題となっている。

【0006】

また、より誘電率の大きな酸化タンタルやチタン酸バリウムストロンチウム、チタン酸鉛、ジルコン酸鉛、ジルコン酸バリウム等ではn型シリコンとの接合のポテンシャル障壁が0.5電子ボルト以下であり、誘電体の厚さが10nm以上であっても十分な絶縁性を示すことは難しい。

【0007】

一般にポテンシャル障壁が1電子ボルト以上であれば、熱的な励起が無視できるので、誘電体が相応の厚さを有する限り、キャパシタとして実用的であると考えられる(非特許文献1参照)。逆にポテンシャル障壁が1電子ボルト未満であるとキャパシタの誘電体として相応しくないと考えられる。

【0008】

このような問題点に関しては、用いる金属を金(仕事関数5.1電子ボルト)、パラジウム(仕事関数5.2電子ボルト)、白金(仕事関数5.4電子ボルト)のようにn型シリコン(仕事関数4.0電子ボルト)よりも仕事関数の高い材料とすることで、解決することが考えられる。すなわち、仕事関数がn型シリコンより1電子ボルト高い金属と誘電体との間では、誘電体のポテンシャル障壁の高さはn型シリコンの場合より1電子ボルト高くなるためである。

【0009】

しかしながら、このような仕事関数の高い金属は高価であり、その薄膜はスパッタリング法のように物理的な方法で形成する以外に実用的な作製方法はない。物理的な成膜方法では、例えば、DRAMで用いられるようなトレンチ型キャパシタあるいはスタック型キャパシタのような特殊な形状の物体に被覆性よく形成することは困難である。

【0010】

また、このような仕事関数の高い金属はhigh−k材料とも反応しやすいことが報告されている。さらには、例えば、白金は酸化物からの酸素の脱離を促進することから、high−k材料との間に、別途、バリヤ層を別の材料で形成することが必要とされている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】米国特許第5764562号

【特許文献2】米国特許第5877522号

【特許文献3】米国特許第5802000号

【特許文献4】米国特許第7772053号

【特許文献5】米国特許公開2011/0227074号

【非特許文献】

【0012】

【非特許文献1】John Robertson, ”Band offsets of wide−band−gap oxides and implications for future electronic devices” Journal of Vacuum Science and Technology B, 18 p. 1785 (2000).

【非特許文献2】R. E. Jones et al. ”Evidence for p−Type Doping of InN”, Phys. Rev. Lett. 96, p. 125505 (2006).

【非特許文献3】M. Nakamura et al., ”The Phase Relations in the In2O3−Ga2ZnO4−ZnO System at 1350℃”、J. Solid State Chem.,Vol.93, p. 298−315 (1991).

【発明の概要】

【発明が解決しようとする課題】

【0013】

本発明は、安価な材料で、high−k材料を用いたキャパシタを提供することを課題の一とする。また、本発明は、特殊な形状の表面にも被服性よく形成されたhigh−k材料を用いたキャパシタを提供することを課題の一とする。また、本発明は、十分に微細化された場合に適したキャパシタを提供することを課題とする。

【0014】

また、本発明はキャパシタを有する半導体装置を提供することを課題とする。また、本発明は、上記キャパシタあるいは半導体装置の一の製造方法を提供することを課題とする。本発明では以上の課題の少なくとも1つを解決する。

【課題を解決するための手段】

【0015】

本発明の一態様は、誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体を有するキャパシタである。また、本発明の一態様は、誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体と、該n型半導体に対向するように誘電体の他の面に設けられた導電性を有する材料とを有する半導体装置である。また、本発明の一態様は、絶縁物の側面に形成された、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上の膜状のn型半導体と、前記n型半導体上に形成された膜状の誘電体とを有する半導体装置である。

【0016】

上記において、誘電体はチタン酸ストロンチウム、チタン酸鉛、チタン酸バリウムストロンチウム、ジルコン酸鉛、ジルコン酸バリウム、酸化タンタル、ビスマスチタン酸ストロンチウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化アルミニウム、酸化イットリウム、酸化ランタン、珪酸ジルコニウム、珪酸ハフニウムから選ばれた1つ以上の材料を含んでもよい。

【0017】

上記において、誘電体は、ストロンチウム、チタン、バリウム、ジルコニウム、鉛、タンタル、ビスマス、ハフニウム、アルミニウム、イットリウム、ランタンから選ばれた1つ以上の元素が、誘電体を構成する金属元素のうちの50%以上である酸化物であってもよい。

【0018】

上記において、誘電体は酸化インジウム、酸化亜鉛、酸化インジウムガリウム、酸化インジウム亜鉛、酸化インジウムガリウム亜鉛から選ばれた1つ以上の材料を含んでもよい。あるいは、誘電体において、インジウム、亜鉛、ガリウムのいずれかが、誘電体を構成する金属元素に占める比率が20%以上であってもよい。

【0019】

酸化インジウム、酸化亜鉛等はバンドギャップが2.5電子ボルト以上の酸化物半導体として知られているが、それらのうち電子親和力が4.6電子ボルト以下であるものは、本発明の一態様において、n型半導体とのポテンシャル障壁の高さが1電子ボルト以上となる。バンドギャップが上記のように大きいので、熱励起キャリアが少なく、真性であるものは極めて抵抗が高い。

【0020】

また、これらの酸化物半導体が相当量のドナーを有していたとしても、本発明の一態様のn型半導体との接触によって、ドナーにより生じる電子はn型半導体に吸収され、酸化物半導体は空乏化して極めて高抵抗となる。本発明の一態様のn型半導体を構成する元素のいくつかはこれらの酸化物半導体を構成する元素でもあるので、製造工程を簡略化することもできる。

【0021】

同様に窒化ガリウム、窒化ガリウムアルミニウム等も誘電体として用いることができる。

【0022】

なお、本明細書で金属元素とは、希ガス元素、水素、ホウ素、炭素、窒素、16族元素(酸素等)、17族元素(フッ素等)、シリコン、燐、ゲルマニウム、砒素、アンチモン以外の全ての元素のことである。また、酸化物とは、それを構成する元素のうち、金属元素以外の元素に占める酸素の比率が50原子%以上の化合物のことである。

【0023】

上記において、n型半導体の仕事関数は5.5電子ボルト以上であることが好ましい。また、上記において、n型半導体の厚さは4nm以上10nm以下であることが好ましい。上記において、n型半導体は、ALD(原子層堆積;Atomic Layer Deposition)法によって形成されることが好ましい。

【0024】

上記のキャパシタあるいは半導体装置はダイナミック・ランダム・アクセス・メモリ(DRAM)に用いられてもよい。その他、半導体集積回路に用いられてもよい。また、上記のキャパシタあるいは半導体装置は、トレンチ型キャパシタあるいはスタック型キャパシタの一部もしくは全部を構成してもよい。

【0025】

ここで、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する高仕事関数のn型半導体(以下、高仕事関数化合物半導体ともいう)は、5原子%以上50原子%以下の濃度の窒素を有することが好ましい。また、高仕事関数化合物半導体は、5原子%以上66.7原子%以下の濃度の亜鉛を有することが好ましい。あるいは、5原子%以上50原子%以下の濃度のインジウムを有することが好ましい。あるいは、5原子%以上57.1原子%以下の濃度の錫を有することが好ましい。

【0026】

また、高仕事関数化合物半導体では、原子番号が20以下の金属元素の濃度を1%以下、好ましくは0.01%以下とするとよい。また、高仕事関数化合物半導体は、酸素や他の原子番号21以上の金属元素を有していてもよい。また、高仕事関数化合物半導体は水素を0.01原子%乃至10原子%含有していてもよい。また、高仕事関数化合物半導体に含まれる酸素の比率を、高仕事関数化合物半導体を構成する金属元素以外の元素(酸素も含む)に対して20原子%乃至90原子%としてもよい。

【0027】

高仕事関数化合物半導体の一例として化学式InNとして知られる窒化インジウムがある。窒化インジウムはバンドギャップが0.7電子ボルト以下の半導体であるが、その電子親和力は5.6電子ボルトである。窒化インジウムはウルツ鉱型構造であることが知られている。

【0028】

なお、窒化インジウムのインジウムの一部をガリウムあるいはアルミニウムで置き換えると、バンドギャップを大きくできることが知られており、その程度は、置き換える比率や置き換える元素に依存する。同様に、電子親和力も置き換える比率や置き換える元素に応じて変化させることができる。

【0029】

例えば、In0.9Ga0.1Nという組成式で表される物質の電子親和力は約5.4電子ボルトとなる。一般にIn1−aGaaNという組成式で表される物質の電子親和力はおおよそ、(5.6−2a)[電子ボルト](ただし、a≦0.3)となる。

【0030】

他の例として化学式Zn3N2として知られる窒化亜鉛がある。窒化亜鉛についてはその物性値についての詳細は知られていないが、電子親和力は5.5電子ボルト程度である。窒化亜鉛は立方晶型構造であることが知られている。

【0031】

このような高仕事関数化合物半導体の作製には、公知のスパッタリング法、真空蒸着法、イオンプレーティング法、MBE(molecular beam epitaxy)法、CVD法(MOCVD(metal organic CVD)法やALD法)等を用いればよい。

【0032】

例えば、窒化ガリウムインジウム(In1−aGaaN)をMOCVD法で作製するのであれば、原料ガスとして、トリメチルインジウム((CH3)3In)とトリメチルガリウム((CH3)3Ga)とアンモニアを用い、基板温度は350℃乃至550℃とすればよい。

【0033】

また、このような高仕事関数化合物半導体の薄膜を、10nm以下の厚さに形成する場合や、アスペクト比が50を超えるような孔の内部に形成する場合には、上記の原料ガス等を用いて、原子層を1層ずつ堆積するALD法が効果的である。

【発明の効果】

【0034】

上述の高仕事関数化合物半導体の仕事関数は5.0電子ボルト以上である。そのため、真空準位から4電子ボルト乃至5電子ボルト下の準位(典型的には真空準位から4.9電子ボルト下の準位、非特許文献2参照)に形成される多くの欠陥準位がドナーとなり、特にドーピング処理を施さずとも、1×1019cm−3以上、好ましくは1×1020cm−3以上の電子濃度を有するn型の半導体となる。

【0035】

そして、上述のように仕事関数がn型シリコンよりも1.0電子ボルト以上高いために、誘電体との接合でのポテンシャル障壁がn型シリコンの場合よりも1.0電子ボルト以上高くなる。さらに、これらの高仕事関数化合物半導体は貴金属を使用せずに合成できるものである。また、これらの高仕事関数化合物半導体の極めて薄い膜を均一に堆積することも、特殊な形状の表面にこれらの高仕事関数化合物半導体の薄膜を形成することもできる。

【0036】

なお、これらの高仕事関数化合物半導体をキャパシタの双方の電極とすることがもっとも効果的であるが、何らかの事情により一方の電極のみに、これらの高仕事関数化合物半導体を用い、他方をより仕事関数の低い材料で作製したとしても、十分な効果が得られる。その場合には、十分な絶縁性を得るためには、これらの高仕事関数化合物半導体を用いた電極(電極A)の電位が、他方の電極(電極B)の電位と同じか低いことが好ましい。

【0037】

例えば、電極Aの仕事関数を5.5電子ボルト、電極Bの仕事関数を4電子ボルト、誘電体を酸化タンタル(電子親和力3.2電子ボルト)とする。非特許文献1によると、電極Bと誘電体の接合のポテンシャル障壁は0.36電子ボルトとなる。同様に、電極Aと誘電体の接合のポテンシャル障壁は1.86電子ボルトとなる。

【0038】

電極Aの電位が電極Bよりも低ければ、電子は、電極Aから電極Bに移動することが考えられる。しかし、上述のように電極Aと誘電体との接合のポテンシャル障壁が1.86電子ボルトもあるためトンネル確率は極めて低い。

【0039】

逆に、電極Aの電位が電極Bよりも高ければ、電子は、電極Bから電極Aに移動することが考えられる。この場合、電極Bと誘電体との接合のポテンシャル障壁は0.36電子ボルトと低くなる。さらに、電極Aの電位が電極Bよりも1.5ボルト以上高ければ、その高さのポテンシャル障壁を越えれば、電子は電極Bから電極Aへ移動できる。このため、電極Aの電位が電極Bよりも1.5ボルト以上高くなると、急激にトンネル確率が上昇する。したがって、上記の構成の電極を有するキャパシタでは極性や電位差にも留意する必要がある。

【0040】

なお、多くのhigh−k材料は酸化物であるため、高仕事関数化合物半導体を構成する金属元素以外の元素に占める酸素の比率が20原子%乃至90原子%であると、high−k材料との密着性が良好である。また、界面で酸化還元反応がおこりにくく、界面が化学的に安定である。

【0041】

特に高仕事関数化合物半導体を構成する金属元素のうちインジウム原子と酸素の結合力は、high−k材料で用いられる多くの金属(例えば、ストロンチウム、チタン、バリウム、ジルコニウム、タンタル、ビスマス、鉛、ハフニウム、アルミニウム、イットリウム、ランタン)の原子と酸素の結合力と同等か弱いため、high−k材料から酸素を引き抜くことがなく、high−k材料を安定化させる上で効果的である。

【図面の簡単な説明】

【0042】

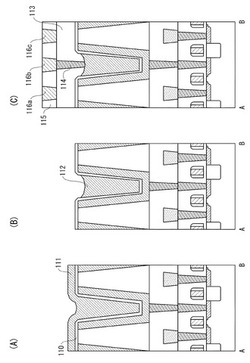

【図1】本発明の半導体装置の作製方法の例を説明する断面図である。

【図2】本発明の半導体装置の作製方法の例を説明する断面図である。

【図3】本発明の半導体装置の作製方法の例を説明する断面図である。

【図4】本発明の半導体装置の作製方法の例を説明する上面図である。

【図5】本発明の半導体装置の作製方法の例を説明する断面図である。

【図6】本発明の半導体装置の回路を説明する図である。

【図7】本発明の半導体装置の作製方法の例を説明する断面図である。

【発明を実施するための形態】

【0043】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0044】

(実施の形態1)

図1(A)乃至図1(C)、図2(A)乃至図2(C)及び図4(A)乃至図4(D)に、本実施の形態の半導体装置(スタック型キャパシタを有するDRAM)を作製する工程例を図示する。なお、特に断らない限り、用いる材料、方法等は公知の半導体集積回路作製技術を参照すればよい。

【0045】

図1(A)乃至図1(C)及び図2(A)乃至図2(C)は本実施の形態の半導体装置の作製工程の断面図であり、図4(A)乃至図4(D)は、本実施の形態の半導体装置の作製工程を上面より見た場合の模式図である。図4(A)乃至図4(D)には、主要な配線等のみを描いている。図4(A)乃至図4(D)の一点鎖線A−Bの断面が、図1(A)乃至図1(C)及び図2(A)乃至図2(C)に相当する。

【0046】

本実施の形態では、いわゆるFolded(折り返し)ビット方式のDRAMを作製する場合について説明する。Foldedビット方式では、メモリセルの面積は最小で8F2(Fは最小加工寸法(Feature Size))となる。Fが20nm以下となると、DRAMは物理的な限界に差しかかる。DRAMでは、キャパシタの容量は常にビット線の寄生容量の1割以上であることが求められる。すなわち、デザインルールが縮小しても、ビット線の長さが変わらない場合にはキャパシタの容量は一定であることが必要となる。

【0047】

最小加工寸法Fが20nm以下においては、スタック型キャパシタを採用するにしてもトレンチ型キャパシタを採用するにしても、それらは一辺20nm乃至40nmの孔に形成される。スタック型キャパシタは外側と内側の2つの電極と誘電体によって構成されるが、電極が薄いと電気抵抗が高まるので好ましくない。一方、誘電体(以下では、電極との間に2電子ボルト以上のポテンシャル障壁があると仮定する)も厚さが2nm未満となるとトンネル電流によって電荷の保持特性が悪化するので好ましくない。

【0048】

一般に誘電体の厚さtは、2nm以上、かつ、(F−4[nm])以下が必要とされる。これによると、最小加工寸法Fが20nmの場合には、tは2nm以上16nm以下、Fが10nmの場合には、tは2nm以上6nm以下となる。誘電体は可能な限り薄い方が好ましいので、最小加工寸法Fが10nm乃至20nmでは、4nm乃至6nmとすることが好ましい。一方、上記の条件からFが6nm未満では、tが2nm未満となり、実用的なキャパシタを作製できないということとなる。

【0049】

また、限られた断面積の孔を用いて一定の容量を確保するには、孔を深くするか、誘電体をhigh−k材料で構成するか、いずれかの方法を採用することになる。前者に関しては、アスペクト比200以上の孔を形成することは多くの技術的困難が伴う。そのため、後者の方法が主として検討されている。

【0050】

しかしながら、アスペクト比50乃至200の孔にhigh−k材料を用いたキャパシタを形成することは多くの困難がある。半導体集積回路に用いられている多くの導電性材料では、そのような穴の内面に十分に薄い薄膜を形成することは可能ではあるが、そのような材料は仕事関数が高くないため、high−k材料との間に十分なポテンシャル障壁を形成できず、誘電体の厚さが10nm以上必要となり、上記の関係式からはFが14nm未満では使用できない。

【0051】

一方、白金族元素は仕事関数が高いため、high−k材料との間に十分なポテンシャル障壁を形成できるが、これらの材料は、半導体集積回路に用いられることがあまりなく、現在の技術では、その薄膜を上記のような孔の内面に均一に形成する方法が知られていない。

【0052】

しかしながら、高仕事関数化合物半導体は、例えば、窒化インジウムの場合であれば、インジウムは砒化インジウム等の化合物半導体で用いられている元素であるので、既存の半導体集積回路作製技術を改良することで、必要な厚さの膜を上記の孔の内面に均一に形成できる。以下、図面にしたがって説明する。

【0053】

<図1(A)>

公知の半導体集積回路作製技術により、単結晶シリコン等の基板101上に、第1の絶縁物102、ワード線103aおよび103b、第1コンタクトプラグ104、ビット線105、第2コンタクトプラグ106を形成する。第1の絶縁物は素子分離絶縁物として機能する。

【0054】

なお、この工程は図4(A)乃至図4(C)を参照できる。すなわち、基板101上に第1の絶縁物102(素子分離絶縁物)を形成して、トランジスタを形成するための複数の長方形の領域を千鳥状に形成する(図4(A))。次に、それらの長方形の領域の中央を横切るように複数のワード線103a、103bを形成する。また、長方形の領域には2つずつ第1コンタクトプラグ104を設ける(図4(B))。さらに、各長方形の領域の第1コンタクトプラグ104の1つを結ぶように、ビット線105をジグザグに形成する(図4(C))。残された第1コンタクトプラグ104には、この後、キャパシタが形成される。

【0055】

<図1(B)>

酸化シリコンの第2の絶縁物107を形成して、これにキャパシタを形成するための孔108を設ける。なお、孔108の内面に厚さ2nm乃至5nmの酸化窒化シリコン膜(酸素/窒素=0.2〜0.8)を形成すると、後述する第1の高仕事関数化合物半導体層109との密着性を向上できる。

【0056】

<図1(C)>

孔108の内面に厚さ2nm乃至5nmの第1の高仕事関数化合物半導体層109を形成する。第1の高仕事関数化合物半導体層109は厚さが2nm未満では、導電性が不十分であるため好ましくない。また、第1の高仕事関数化合物半導体層109の厚さの上限は最小加工寸法Fに応じて決定すればよい。例えば、Fが20nmであれば、5nm以下とすることが好ましく、Fが10nmであれば、2.5nm以下とすることが好ましい。

【0057】

本実施の形態では、高仕事関数化合物半導体として、密着性を高めるため酸化窒化インジウムを用いる。酸化窒化インジウムを構成する元素のうち、酸素と窒素の比率、酸素/窒素は0.2乃至0.8とすればよい。なお、孔108の内面に窒素濃度の高い絶縁膜が設けられている場合には、窒化インジウムを用いてもよい。

【0058】

なお、高仕事関数化合物半導体の抵抗率は1×10−2Ωcm以下、好ましくは1×10−4Ωcm以下とするとよい。特に、酸化窒化インジウムに限らず多くの高仕事関数化合物半導体は、水素を1原子%乃至10原子%含有していると、キャリアが増加して導電率が向上するため好ましい。

【0059】

<図2(A)>

厚さ2nm乃至5nmの第3の絶縁物110を形成する。第3の絶縁物110としては各種のhigh−k材料を用いることができるが、酸化ハフニウム、酸化ジルコニウム、酸化タンタル等が好ましい。さらに、再び、酸化窒化インジウムによって、第2の高仕事関数化合物半導体層111を形成する。この際、孔108が酸化窒化インジウムによって埋められるように、第2の高仕事関数化合物半導体層111を形成するとよい。

【0060】

<図2(B)>

第2の高仕事関数化合物半導体層111をエッチングすることにより、孔108以外の部分の第3の絶縁物110を露出させ、対向電極112を形成する。この工程は、孔108の入り口付近での、電極間のショートを防止するためにおこなう。

【0061】

<図2(C)>

その後、第4の絶縁物113、第3コンタクトプラグ114を形成し、さらに第5の絶縁物115を形成し、キャパシタ線116a、116b、116cを形成する。本実施の形態では、図4(D)に示すように、キャパシタ線116a、116b、116cをワード線103a、103bと平行に形成する。しかし、キャパシタ線をビット線105と平行に形成してもよい。

【0062】

このようにして、Foldedビット方式のDRAMのメモリセルを作製できる。なお、キャパシタ線116a、116b、116cはそれぞれ、独立に電位を制御できるが、常に同じ電位を与える共通電位線として用いてもよい。

【0063】

(実施の形態2)

図3(A)乃至図3(C)、図4(E)および図4(F)に本実施の形態を示す。本実施の形態は薄膜トランジスタを用いて、オープンビット型のDRAMを作製するものである。オープンビット型のDRAMのメモリセルの面積は理想的には、実施の形態1で説明したFoldedビット線型DRAMよりも小さい6F2(Fは最小加工寸法)まで小さくできる。以下図面にしたがって説明する。

【0064】

<図3(A)>

第1の絶縁物201の上にビット線202を形成する。さらに、第2の絶縁物203を形成し、これにビット線202に接続する第1コンタクトプラグ204を形成する。さらに、適切な厚さおよび大きさの半導体層205、半導体層205を覆う第3の絶縁物206、ワード線207a、207bを形成する。第3の絶縁物206は薄膜トランジスタのゲート絶縁膜としても機能する。

【0065】

半導体層205は特に限定されず、単結晶、多結晶、非晶質いずれでもよく、シリコン、ゲルマニウム等の14族元素、砒化ガリウム、酸化インジウム、硫化亜鉛、窒化ガリウム等の化合物でもよい。また、純物質に限らず、何らかの添加物を含有してもよい。また、半導体層205は必要に応じて、n型の領域やp型の領域あるいは真性の領域、あるいはそれらの中間の導電性を示す領域を有してもよい。

【0066】

以上の工程は、図4(E)および図4(F)を参照することもできる。すなわち、第1の絶縁物201上にビット線202と、これに接続する第1コンタクトプラグ204を形成する(図4(E))。さらに、ビット線202と重なるように、半導体層205を形成する。また、ワード線207a、207bを形成する(図4(F))。

【0067】

一般に、第1の絶縁物201の下には、何らかの半導体集積回路が設けられていることが多い。その場合には、それらによって発生するノイズが上層の薄膜トランジスタの動作に支障をもたらすことがある。この問題に対しては、薄膜トランジスタの下に何らかのシールド層を設けて、ノイズを吸収させるとよいが、図4(F)に見られるように、ビット線202と半導体層205が重なるように配置すると、ビット線202がシールド層となり、ノイズを吸収する。

【0068】

<図3(B)>

第4の絶縁物208を形成し、第2コンタクトプラグ209a、209bを形成する。さらにキャパシタを形成するための孔を有する第5の絶縁物210を形成し、高仕事関数化合物半導体層211a、211bとそれらを覆う第6の絶縁物212を形成する。第6の絶縁物212としてはhigh−k材料を用いるとよい。高仕事関数化合物半導体層211a、211bと第6の絶縁物212の作製方法については実施の形態1を参照すればよい。

【0069】

<図3(C)>

対向電極213a、213bを形成した後、第7の絶縁物214と対向電極213a、213bに接続する第3コンタクトプラグ215a、215b、キャパシタ線216を形成する。以上で、オープンビット型DRAMのメモリセルを作製できる。

【0070】

本実施の形態では、キャパシタ線216は、ビット線202と平行に配置される。キャパシタ線216には、常に同じ電位を与えてもよいが、ビット線202に同期した電位としてもよい。例えば、特許文献1に記載されているように、ビット線とは逆の位相の相補的な電位を与えてもよい。

【0071】

本実施の形態で示したオープンビット型DRAMのメモリセルは、ビット線202がトランジスタの下に配置されているため、スタック型キャパシタを有しながらも設計の自由度が高い。スタック型キャパシタを有するオープンビット型DRAMとしては、例えば、特許文献2や特許文献3に記載されているが、例えば、特許文献2では、トランジスタとビット線を接続するため補助配線が必要であり、また、特許文献3では、ビット線がワード線と直角でない角度で交差する(その結果、メモリセルが平行四辺形となる)ことが求められる。

【0072】

いずれも、余計なプロセスや余分な面積が生じる。これらは、ビット線とキャパシタが共にトランジスタの上に存在するためであり、ビット線がキャパシタを避けるように配置することが求められる。これに対し、本実施の形態のようにビット線をトランジスタの下、キャパシタをトランジスタの上とすると、キャパシタの位置に関係なくビット線を配置できるため、極めて効率的なレイアウトとなる。

【0073】

(実施の形態3)

図5及び図6に本実施の形態を示す。本実施の形態は2つのトランジスタを用いて、信号増幅型のメモリセル(特許文献4参照)を作製するものである。

【0074】

図6(A)は実施の形態1および実施の形態2でも説明した通常の1トランジスタ1キャパシタ型のDRAMのメモリセルの回路図である。このDRAMでは、ワード線WLの電位に応じて書き込みトランジスタWTがオンオフし、ビット線BLとキャパシタCSの間で電荷を移動させる。そのため、ビット線BLの寄生容量に応じて、キャパシタCSの容量を決定する必要があり、デザインルールが縮小しても同程度の容量が必要である。そのため、トレンチ型キャパシタやスタック型キャパシタ、あるいはhigh−k材料の採用等が必須となっている。

【0075】

これに対し、図6(B)に示されるメモリセルは2トランジスタ1キャパシタ型であり、セルに蓄えられた電荷を読み出しトランジスタRTで増幅するため、キャパシタの容量は理想的には読み出しトランジスタRTと同じ速度で縮小することができる。

【0076】

しかしながら、現実には書き込みトランジスタWTのソースとドレイン間はオフ状態であっても有限の抵抗状態(通常、1×1013Ω〜1×1014Ω)である。キャパシタの電荷がなくなるまでの時間は、この抵抗とキャパシタCSの容量の積である。したがって、キャパシタCSの容量が減少すると、電荷の減少も早くなる。

【0077】

図6(A)の1トランジスタ1キャパシタ型のDRAMのメモリセルのキャパシタCSの容量は1×10−14F程度であるため、電荷がなくなるのに要する時間は0.1秒程度である。そのため、このタイプのメモリセルでは1秒に数十回電荷を再注入(リフレッシュ)する必要がある。

【0078】

このことは、図6(B)のメモリセルでも同様で、キャパシタCSの容量が1×10−14F程度であれば1秒に数十回のリフレッシュで済む。しかし、そのような大きな容量を有するのであれば余分なトランジスタを設ける意味はない。トランジスタを余分に設けるからには、容量をさらに小さくすることが望ましい。

【0079】

しかし、容量がさらに10分の1、100分の1となれば、電荷がなくなる時間も10分の1、100分の1となるので、リフレッシュの回数も1秒に数百回、数千回となり、およそ現実的でなくなる。すなわち、図6(B)に示されるメモリセルは、トランジスタのオフ状態の抵抗が1×1015Ω以下では実用的ではない。

【0080】

図6(B)に示される回路を用いて、実用的なメモリセルを構成するには、書き込みトランジスタWTのオフ抵抗が1×1018Ω以上、好ましくは1×1021Ω以上であることが必須である。例えば、キャパシタCSの容量を通常のDRAMの千分の1の1×10−17Fとすると、書き込みトランジスタWTのオフ抵抗が1×1018Ωのときは、1秒間に数回、オフ抵抗が1×1021Ωのときは、数分に1回のリフレッシュでよく、通常のDRAMと比較しても消費電力が低減できる。オフ抵抗がさらに大きければよりリフレッシュの頻度を低下させることができる。

【0081】

このような非常に高いオフ抵抗を得るためには、極めて薄いシリコン(特許文献4参照)、あるいは、バンドギャップが2.5電子ボルト以上4電子ボルト以下、好ましくは3電子ボルト以上3.8電子ボルト以下のワイドバンドギャップ半導体を使用すること(特許文献5参照)が必要となる。後者としては、例えば、酸化インジウム、酸化亜鉛等の酸化物半導体、窒化ガリウム等の窒化物半導体、硫化亜鉛等の硫化物半導体等を用いればよい。

【0082】

オフ抵抗は、熱的に励起するキャリアの濃度に比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、バルクのシリコンの場合にはバンドギャップが1.1電子ボルトなので、室温(300K)での熱励起キャリアの濃度は1×1011cm−3程度である。

【0083】

なお、特許文献4では、極めて薄いシリコンでは、量子効果によりバンドギャップが拡大するため、熱励起キャリアはバルクのシリコンより3桁程度少ないと報告されている。

【0084】

一方、バンドギャップ3.2電子ボルトの半導体では熱励起キャリアの濃度は1×10−7cm−3程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2電子ボルトの半導体の抵抗率は、シリコンより18桁も大きい。

【0085】

なお、ドナーやアクセプタによるキャリアは極力、低濃度であることが好ましく、その濃度は、1×1012cm−3以下とすることが好ましい。これらのキャリア濃度によりトランジスタのしきい値が決定される。

【0086】

このように、図6(B)に示される回路をメモリセルとして用いる場合には、トランジスタに用いる半導体の種類や物性が重要である。なお、上記の議論はキャパシタの誘電体の抵抗を無限大としたものであるが、誘電体の厚さやポテンシャル障壁の高さによっては有限の抵抗が生じることがある。その結果、トランジスタのオフ抵抗よりもキャパシタの寄生抵抗が小さくなると、リフレッシュ間隔が想定よりも短くなることがある。

【0087】

可能な限りキャパシタの寄生抵抗を大きくするには、実質的な誘電体の厚さを5nm以上、好ましくは10nm以上、ポテンシャル障壁を1.5電子ボルト以上、好ましくは2.5電子ボルト以上とするとよい。以下図面にしたがって説明する。

【0088】

<図5(A)>

単結晶シリコン等の基板301に導電性領域302a、302b、フローティングゲート303を形成する。このうち、導電性領域302aは図6(B)に共通電位線CLで示される配線となり、書き込みワード線WWL、読み出しワード線RWLと平行に形成する。また、第1の絶縁物304を形成する。

【0089】

<図5(B)>

第1の絶縁物304をエッチングして、フローティングゲート303の表面を露出させ、また、コンタクトホールを形成して、導電性領域302bに接続する第1コンタクトプラグ305を埋め込む。さらに、厚さ2nm乃至10nm、好ましくは2nm乃至5nmの適切な形状、面積の半導体層306と、それを覆う第2の絶縁物307を形成する。半導体層306の材料は上記した条件を満たすものを選択するとよい。

【0090】

第2の絶縁物307は、半導体層306を用いて形成される薄膜トランジスタのゲート絶縁膜として、また、キャパシタの誘電体としても機能する。さらに、第2の絶縁物307はhigh−k材料を用いて構成し、厚さは2nm乃至10nm、好ましくは2nm乃至5nmとする。

【0091】

<図5(C)>

反応性スパッタリング法で酸窒化亜鉛もしくは酸窒化インジウム、酸窒化錫、酸窒化インジウム亜鉛、酸窒化インジウム亜鉛ガリウム(組成式はInaGabZncOdNe、(0≦a≦1、0≦b≦1、0≦c≦1、0≦d≦1、0≦e≦1))等の仕事関数の高い酸窒化物膜(以下、高仕事関数酸窒化物膜308という)を成膜する。

【0092】

例えば、酸窒化亜鉛を成膜するには、酸化亜鉛をターゲットにして、窒素濃度が50%以上かつ酸素濃度が5%以下の雰囲気という条件を採用すればよい。同様に、酸窒化インジウム、酸窒化錫、酸窒化インジウム亜鉛、酸窒化インジウム亜鉛ガリウムを成膜するには、窒素濃度が50%以上かつ酸素濃度が5%以下の雰囲気で、それぞれ、酸化インジウム、酸化錫、酸化インジウム亜鉛、酸化インジウム亜鉛ガリウムをターゲットとして用いればよい。

【0093】

また、その際には、基板温度は100℃乃至600℃、好ましくは150℃乃至450℃とするとよい。また、成膜後、100℃乃至600℃、好ましくは150℃乃至450℃の非酸化性雰囲気で熱処理してもよい。

【0094】

なお、スパッタリング法以外にも、ALD法やCVD法(MOCVD法等)を採用してもよい。特に、第2の絶縁物307の厚さが5nm以下の場合には、第2の絶縁物307へのダメージの少ないALD法やCVD法を用いることが好ましい。

【0095】

酸化インジウム亜鉛ガリウムの例として、組成式InGaZnO4で表されるものは、YbFe2O4構造と呼ばれる結晶構造を取ることが知られている(非特許文献3参照)。しかしながら、例えば、5原子%以上の窒素が添加されるとウルツ鉱型構造が安定相となり、それにともなって電子状態も劇的に変化する。また、YbFe2O4構造に比べるとウルツ鉱型構造は結晶化が容易であるため、比較的低温で結晶化する。

【0096】

電子状態に関しては、例えば、バンドギャップはYbFe2O4構造のものが3.2電子ボルト程度であるが、ウルツ鉱型構造のものでは2.2電子ボルト以下となり、また、電子親和力も、前者が4.3電子ボルト程度のものが、後者では5.5電子ボルト以上となる。電子親和力が4.9電子ボルト以上となるため、欠陥準位によりn型の導電性を呈することとなる。なお、水素はドナーとして機能するため、水素を添加することによってもキャリア濃度を高めることもできる。

【0097】

なお、高仕事関数酸窒化物膜308は、窒素や亜鉛、錫、インジウム以外に酸素を窒素の2乃至5倍含有していると、ゲート絶縁膜との界面でのトラップ準位の発生を抑制する上で好ましい。また、高仕事関数酸窒化物膜308は、水素を1原子%乃至10原子%含有していると、界面の状況が改善され、かつ、キャリアが増加して導電率が向上するため好ましい。

【0098】

なお、酸化インジウム亜鉛ガリウム(In−Ga−Zn−O)の代わりに、二元系金属酸化物である、In−Sn−O、Sn−Zn−O、Al−Zn−O、In−Ga−Oや、三元系金属酸化物であるIn−Sn−Zn−O、In−Al−Zn−O、Sn−Ga−Zn−O、Al−Ga−Zn−O、Sn−Al−Zn−Oや、四元系金属酸化物であるIn−Sn−Ga−Zn−Oなどを用いてもよい。ここで、例えば、In−Ga−Zn−Oとは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物という意味である。

【0099】

その後、導電性の高い金属や金属化合物よりなる導電性膜309を適切な厚さだけ形成する。金属膜としてはアルミニウム、チタン、タンタル、タングステン等やそれらを50%以上有する合金を用いることができ、金属化合物膜としては、それらの窒化物膜を用いることができる。

【0100】

<図5(D)>

高仕事関数酸窒化物膜308と導電性膜309をエッチングして、これらの積層した膜よりなる書き込みワード線310と読み出しワード線311を形成する。また、書き込みワード線310と読み出しワード線311をマスクとして、アルゴンのような希ガス元素、燐やアルミニウム、ガリウム等の酸化されやすい元素等を照射して半導体層306に酸素欠損等を導入し、n型領域312を形成する。窒素イオンを照射しても同様にn型領域を作製できる。

【0101】

<図5(E)>

第3の絶縁物313と、第1コンタクトプラグ305に接続する第2コンタクトプラグ314、およびビット線315を形成する。ビット線315は図6(B)のビット線BLに相当し、書き込みワード線WWLと直交する。

【0102】

このようにして作製されるメモリセルの面積は8F2乃至12F2となる。また、このメモリセルでは、フローティングゲート303と読み出しワード線311の間にキャパシタ316(図6(B)のキャパシタCSに相当)が形成される。薄膜トランジスタはnチャネル型であるため、電荷を保存するためには、キャパシタ側の電位はビット線電位と同じかより高いことが好ましい。

【0103】

同様に、読み出しワード線311の電位は、フローティングゲート303の電位と同じかより低いことが好ましい。その条件が満たされるなら、フローティングゲート303の材料の仕事関数に関して特段の条件はなく、むしろ、仕事関数が半導体層を構成する半導体の電子親和力以下であると半導体層306との接合の抵抗を下げることができて好ましい。

【0104】

読み出しワード線311の電位が、フローティングゲート303の電位より低い場合(すなわち、フローティングゲート303に正の電荷が蓄積されている場合)、これらの間にある半導体層306が空乏化し、誘電体となることがある。その場合、キャパシタ316の誘電体は、第2の絶縁物307と半導体層306の積層であるとみなされる。

【0105】

したがって、キャパシタ316の誘電体の実質的な厚さは第2の絶縁物307の電気的な厚さと半導体層306の電気的な厚さの和となる。例えば、半導体層306と第2の絶縁物307の誘電率が同じであれば、第2の絶縁物307の厚さが2nmであったとしても、半導体層306の厚さが4nmであれば、キャパシタ316の誘電体の実質的な厚さは6nmであるため、トンネル電流は十分に小さくできる。

【0106】

この条件下では電子は、読み出しワード線311から、第2の絶縁物307と半導体層306を経て、フローティングゲート303へ移動しようとするが、読み出しワード線311と第2の絶縁物307の接合部は高仕事関数酸窒化物が用いられているため、ポテンシャル障壁が1.5電子ボルト以上となるためトンネル確率が極めて低く、十分な絶縁性が保たれる。

【0107】

一方、データの書き込みの際には、読み出しワード線311の電位を半導体層306よりも高くすることにより、半導体層に反転層(チャネル)を形成させてもよい。反転層は導電性が高く、よって、ビット線315の電位が、フローティングゲート303に伝わりやすくなる。

【0108】

なお、書き込みワード線310と半導体層306とのトンネル電流を低減させる目的からは、書き込みワード線310の電位を調整して、近傍(少なくとも書き込みワード線310から6nm以内)の半導体層306を空乏化させることが好ましい。

【0109】

(実施の形態4)

図7に本実施の形態を示す。本実施の形態では実施の形態3と同様に図6(B)に示すメモリセルの作製工程について説明する。以下図面にしたがって説明する。なお、詳細は実施の形態3を参照すればよい。

【0110】

<図7(A)>

実施の形態3で説明した方法等により、基板401上に、導電性領域402a、402b、フローティングゲート403、第1の絶縁物404、第1コンタクトプラグ405、半導体層406、第2の絶縁物407、書き込みワード線408、第3の絶縁物409を形成する。なお、ここで、書き込みワード線には特に高仕事関数化合物半導体を用いる必要はない。

【0111】

<図7(B)>

フローティングゲート403、あるいは第1コンタクトプラグ405に接続する第2コンタクトプラグ410を形成する。さらに、高仕事関数酸窒化物膜411をいくつかの第2コンタクトプラグ410と接するように形成する。高仕事関数酸窒化物膜411の作製方法は実施の形態3を参照すればよい。

【0112】

また、高仕事関数酸窒化物膜411を覆って、high−k材料を用いて、第4の絶縁物412を形成する。第4の絶縁物412は、キャパシタ414の誘電体として機能する。厚さは5nm以上10nm以下とすればよい。作製方法等は実施の形態1乃至実施の形態3を参照すればよい。

【0113】

さらに、実施の形態3の書き込みワード線310、読み出しワード線311と同様に高仕事関数酸窒化物膜と導電成膜の積層である読み出しワード線413を第4の絶縁物412上に形成する。この結果、読み出しワード線413と高仕事関数酸窒化物膜411、第4の絶縁物412からなるキャパシタ414が形成される。

【0114】

<図7(C)>

第5の絶縁物415と、第2コンタクトプラグ410のうち、高仕事関数酸窒化物膜411が設けられていないものに接続する第3コンタクトプラグ416、および第3コンタクトプラグ416に接続するビット線417を形成する。このようにして作製されるメモリセルの面積は6F2乃至9F2(Fは最小加工寸法)となる。

【符号の説明】

【0115】

101 基板

102 第1の絶縁物

103a ワード線

103b ワード線

104 第1コンタクトプラグ

105 ビット線

106 第2コンタクトプラグ

107 第2の絶縁物

108 孔

109 第1の高仕事関数化合物半導体層

110 第3の絶縁物

111 第2の高仕事関数化合物半導体層

112 対向電極

113 第4の絶縁物

114 第3コンタクトプラグ

115 第5の絶縁物

116a キャパシタ線

116b キャパシタ線

116c キャパシタ線

201 第1の絶縁物

202 ビット線

203 第2の絶縁物

204 第1コンタクトプラグ

205 半導体層

206 第3の絶縁物

207a ワード線

207b ワード線

208 第4の絶縁物

209a 第2コンタクトプラグ

209b 第2コンタクトプラグ

210 第5の絶縁物

211a 高仕事関数化合物半導体層

211b 高仕事関数化合物半導体層

212 第6の絶縁物

213a 対向電極

213b 対向電極

214 第7の絶縁物

215a 第3コンタクトプラグ

215b 第3コンタクトプラグ

216 キャパシタ線

301 基板

302a 導電性領域

302b 導電性領域

303 フローティングゲート

304 第1の絶縁物

305 第1コンタクトプラグ

306 半導体層

307 第2の絶縁物

308 高仕事関数酸窒化物膜

309 導電性膜

310 書き込みワード線

311 読み出しワード線

312 n型領域

313 第3の絶縁物

314 第2コンタクトプラグ

315 ビット線

316 キャパシタ

401 基板

402a 導電性領域

402b 導電性領域

403 フローティングゲート

404 第1の絶縁物

405 第1コンタクトプラグ

406 半導体層

407 第2の絶縁物

408 書き込みワード線

409 第3の絶縁物

410 第2コンタクトプラグ

411 高仕事関数酸窒化物膜

412 第4の絶縁物

413 読み出しワード線

414 キャパシタ

415 第5の絶縁物

416 第3コンタクトプラグ

417 ビット線

WL ワード線

BL ビット線

CL 共通電位線

CS キャパシタ

WT 書き込みトランジスタ

RT 読み出しトランジスタ

WWL 書き込みワード線

RWL 読み出しワード線

【技術分野】

【0001】

本発明は、半導体装置に用いられるキャパシタおよびキャパシタを用いた半導体装置に関する。

【背景技術】

【0002】

半導体集積回路等に用いられるキャパシタは従来、金属や導電性の高いシリコン等の半導体によって形成される電極の間に酸化シリコン等の誘電体を挟む構造のものが用いられてきた。しかしながら、回路が微細化されると酸化シリコン(比誘電率4程度)よりも誘電率の高い材料(high−k材料)を用いることが検討されるようになった。

【0003】

このようなhigh−k材料を用いる際の問題点は、一般にhigh−k材料の電子親和力(真空準位と伝導帯下端とのエネルギー差)が大きいということである。例えば、非特許文献1によると、酸化シリコンの電子親和力は0.9電子ボルトであるのに対し、high−k材料のひとつである酸化ハフニウムの電子親和力は2.5電子ボルトである。

【0004】

このため、例えば、n型シリコンと酸化シリコンの接合では、ポテンシャル障壁が3.5電子ボルトであったのに、n型シリコンと酸化ハフニウムの接合では、ポテンシャル障壁が1.5電子ボルト(接合での分極のため、ポテンシャル障壁は必ずしもn型シリコンの仕事関数と誘電体の電子親和力の差と等しくならないことに注意が必要である)まで低下してしまう。

【0005】

1.5電子ボルト程度の障壁でも誘電体の厚さが5nm以上であれば、絶縁特性に顕著な問題は生じないが、回路の微細化と共に誘電体の厚さも3nm以下となることが要求されると量子効果によるトンネル電流が大きくなり、キャパシタとしての機能が十分に果たせないことが問題となっている。

【0006】

また、より誘電率の大きな酸化タンタルやチタン酸バリウムストロンチウム、チタン酸鉛、ジルコン酸鉛、ジルコン酸バリウム等ではn型シリコンとの接合のポテンシャル障壁が0.5電子ボルト以下であり、誘電体の厚さが10nm以上であっても十分な絶縁性を示すことは難しい。

【0007】

一般にポテンシャル障壁が1電子ボルト以上であれば、熱的な励起が無視できるので、誘電体が相応の厚さを有する限り、キャパシタとして実用的であると考えられる(非特許文献1参照)。逆にポテンシャル障壁が1電子ボルト未満であるとキャパシタの誘電体として相応しくないと考えられる。

【0008】

このような問題点に関しては、用いる金属を金(仕事関数5.1電子ボルト)、パラジウム(仕事関数5.2電子ボルト)、白金(仕事関数5.4電子ボルト)のようにn型シリコン(仕事関数4.0電子ボルト)よりも仕事関数の高い材料とすることで、解決することが考えられる。すなわち、仕事関数がn型シリコンより1電子ボルト高い金属と誘電体との間では、誘電体のポテンシャル障壁の高さはn型シリコンの場合より1電子ボルト高くなるためである。

【0009】

しかしながら、このような仕事関数の高い金属は高価であり、その薄膜はスパッタリング法のように物理的な方法で形成する以外に実用的な作製方法はない。物理的な成膜方法では、例えば、DRAMで用いられるようなトレンチ型キャパシタあるいはスタック型キャパシタのような特殊な形状の物体に被覆性よく形成することは困難である。

【0010】

また、このような仕事関数の高い金属はhigh−k材料とも反応しやすいことが報告されている。さらには、例えば、白金は酸化物からの酸素の脱離を促進することから、high−k材料との間に、別途、バリヤ層を別の材料で形成することが必要とされている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】米国特許第5764562号

【特許文献2】米国特許第5877522号

【特許文献3】米国特許第5802000号

【特許文献4】米国特許第7772053号

【特許文献5】米国特許公開2011/0227074号

【非特許文献】

【0012】

【非特許文献1】John Robertson, ”Band offsets of wide−band−gap oxides and implications for future electronic devices” Journal of Vacuum Science and Technology B, 18 p. 1785 (2000).

【非特許文献2】R. E. Jones et al. ”Evidence for p−Type Doping of InN”, Phys. Rev. Lett. 96, p. 125505 (2006).

【非特許文献3】M. Nakamura et al., ”The Phase Relations in the In2O3−Ga2ZnO4−ZnO System at 1350℃”、J. Solid State Chem.,Vol.93, p. 298−315 (1991).

【発明の概要】

【発明が解決しようとする課題】

【0013】

本発明は、安価な材料で、high−k材料を用いたキャパシタを提供することを課題の一とする。また、本発明は、特殊な形状の表面にも被服性よく形成されたhigh−k材料を用いたキャパシタを提供することを課題の一とする。また、本発明は、十分に微細化された場合に適したキャパシタを提供することを課題とする。

【0014】

また、本発明はキャパシタを有する半導体装置を提供することを課題とする。また、本発明は、上記キャパシタあるいは半導体装置の一の製造方法を提供することを課題とする。本発明では以上の課題の少なくとも1つを解決する。

【課題を解決するための手段】

【0015】

本発明の一態様は、誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体を有するキャパシタである。また、本発明の一態様は、誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体と、該n型半導体に対向するように誘電体の他の面に設けられた導電性を有する材料とを有する半導体装置である。また、本発明の一態様は、絶縁物の側面に形成された、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上の膜状のn型半導体と、前記n型半導体上に形成された膜状の誘電体とを有する半導体装置である。

【0016】

上記において、誘電体はチタン酸ストロンチウム、チタン酸鉛、チタン酸バリウムストロンチウム、ジルコン酸鉛、ジルコン酸バリウム、酸化タンタル、ビスマスチタン酸ストロンチウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化アルミニウム、酸化イットリウム、酸化ランタン、珪酸ジルコニウム、珪酸ハフニウムから選ばれた1つ以上の材料を含んでもよい。

【0017】

上記において、誘電体は、ストロンチウム、チタン、バリウム、ジルコニウム、鉛、タンタル、ビスマス、ハフニウム、アルミニウム、イットリウム、ランタンから選ばれた1つ以上の元素が、誘電体を構成する金属元素のうちの50%以上である酸化物であってもよい。

【0018】

上記において、誘電体は酸化インジウム、酸化亜鉛、酸化インジウムガリウム、酸化インジウム亜鉛、酸化インジウムガリウム亜鉛から選ばれた1つ以上の材料を含んでもよい。あるいは、誘電体において、インジウム、亜鉛、ガリウムのいずれかが、誘電体を構成する金属元素に占める比率が20%以上であってもよい。

【0019】

酸化インジウム、酸化亜鉛等はバンドギャップが2.5電子ボルト以上の酸化物半導体として知られているが、それらのうち電子親和力が4.6電子ボルト以下であるものは、本発明の一態様において、n型半導体とのポテンシャル障壁の高さが1電子ボルト以上となる。バンドギャップが上記のように大きいので、熱励起キャリアが少なく、真性であるものは極めて抵抗が高い。

【0020】

また、これらの酸化物半導体が相当量のドナーを有していたとしても、本発明の一態様のn型半導体との接触によって、ドナーにより生じる電子はn型半導体に吸収され、酸化物半導体は空乏化して極めて高抵抗となる。本発明の一態様のn型半導体を構成する元素のいくつかはこれらの酸化物半導体を構成する元素でもあるので、製造工程を簡略化することもできる。

【0021】

同様に窒化ガリウム、窒化ガリウムアルミニウム等も誘電体として用いることができる。

【0022】

なお、本明細書で金属元素とは、希ガス元素、水素、ホウ素、炭素、窒素、16族元素(酸素等)、17族元素(フッ素等)、シリコン、燐、ゲルマニウム、砒素、アンチモン以外の全ての元素のことである。また、酸化物とは、それを構成する元素のうち、金属元素以外の元素に占める酸素の比率が50原子%以上の化合物のことである。

【0023】

上記において、n型半導体の仕事関数は5.5電子ボルト以上であることが好ましい。また、上記において、n型半導体の厚さは4nm以上10nm以下であることが好ましい。上記において、n型半導体は、ALD(原子層堆積;Atomic Layer Deposition)法によって形成されることが好ましい。

【0024】

上記のキャパシタあるいは半導体装置はダイナミック・ランダム・アクセス・メモリ(DRAM)に用いられてもよい。その他、半導体集積回路に用いられてもよい。また、上記のキャパシタあるいは半導体装置は、トレンチ型キャパシタあるいはスタック型キャパシタの一部もしくは全部を構成してもよい。

【0025】

ここで、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する高仕事関数のn型半導体(以下、高仕事関数化合物半導体ともいう)は、5原子%以上50原子%以下の濃度の窒素を有することが好ましい。また、高仕事関数化合物半導体は、5原子%以上66.7原子%以下の濃度の亜鉛を有することが好ましい。あるいは、5原子%以上50原子%以下の濃度のインジウムを有することが好ましい。あるいは、5原子%以上57.1原子%以下の濃度の錫を有することが好ましい。

【0026】

また、高仕事関数化合物半導体では、原子番号が20以下の金属元素の濃度を1%以下、好ましくは0.01%以下とするとよい。また、高仕事関数化合物半導体は、酸素や他の原子番号21以上の金属元素を有していてもよい。また、高仕事関数化合物半導体は水素を0.01原子%乃至10原子%含有していてもよい。また、高仕事関数化合物半導体に含まれる酸素の比率を、高仕事関数化合物半導体を構成する金属元素以外の元素(酸素も含む)に対して20原子%乃至90原子%としてもよい。

【0027】

高仕事関数化合物半導体の一例として化学式InNとして知られる窒化インジウムがある。窒化インジウムはバンドギャップが0.7電子ボルト以下の半導体であるが、その電子親和力は5.6電子ボルトである。窒化インジウムはウルツ鉱型構造であることが知られている。

【0028】

なお、窒化インジウムのインジウムの一部をガリウムあるいはアルミニウムで置き換えると、バンドギャップを大きくできることが知られており、その程度は、置き換える比率や置き換える元素に依存する。同様に、電子親和力も置き換える比率や置き換える元素に応じて変化させることができる。

【0029】

例えば、In0.9Ga0.1Nという組成式で表される物質の電子親和力は約5.4電子ボルトとなる。一般にIn1−aGaaNという組成式で表される物質の電子親和力はおおよそ、(5.6−2a)[電子ボルト](ただし、a≦0.3)となる。

【0030】

他の例として化学式Zn3N2として知られる窒化亜鉛がある。窒化亜鉛についてはその物性値についての詳細は知られていないが、電子親和力は5.5電子ボルト程度である。窒化亜鉛は立方晶型構造であることが知られている。

【0031】

このような高仕事関数化合物半導体の作製には、公知のスパッタリング法、真空蒸着法、イオンプレーティング法、MBE(molecular beam epitaxy)法、CVD法(MOCVD(metal organic CVD)法やALD法)等を用いればよい。

【0032】

例えば、窒化ガリウムインジウム(In1−aGaaN)をMOCVD法で作製するのであれば、原料ガスとして、トリメチルインジウム((CH3)3In)とトリメチルガリウム((CH3)3Ga)とアンモニアを用い、基板温度は350℃乃至550℃とすればよい。

【0033】

また、このような高仕事関数化合物半導体の薄膜を、10nm以下の厚さに形成する場合や、アスペクト比が50を超えるような孔の内部に形成する場合には、上記の原料ガス等を用いて、原子層を1層ずつ堆積するALD法が効果的である。

【発明の効果】

【0034】

上述の高仕事関数化合物半導体の仕事関数は5.0電子ボルト以上である。そのため、真空準位から4電子ボルト乃至5電子ボルト下の準位(典型的には真空準位から4.9電子ボルト下の準位、非特許文献2参照)に形成される多くの欠陥準位がドナーとなり、特にドーピング処理を施さずとも、1×1019cm−3以上、好ましくは1×1020cm−3以上の電子濃度を有するn型の半導体となる。

【0035】

そして、上述のように仕事関数がn型シリコンよりも1.0電子ボルト以上高いために、誘電体との接合でのポテンシャル障壁がn型シリコンの場合よりも1.0電子ボルト以上高くなる。さらに、これらの高仕事関数化合物半導体は貴金属を使用せずに合成できるものである。また、これらの高仕事関数化合物半導体の極めて薄い膜を均一に堆積することも、特殊な形状の表面にこれらの高仕事関数化合物半導体の薄膜を形成することもできる。

【0036】

なお、これらの高仕事関数化合物半導体をキャパシタの双方の電極とすることがもっとも効果的であるが、何らかの事情により一方の電極のみに、これらの高仕事関数化合物半導体を用い、他方をより仕事関数の低い材料で作製したとしても、十分な効果が得られる。その場合には、十分な絶縁性を得るためには、これらの高仕事関数化合物半導体を用いた電極(電極A)の電位が、他方の電極(電極B)の電位と同じか低いことが好ましい。

【0037】

例えば、電極Aの仕事関数を5.5電子ボルト、電極Bの仕事関数を4電子ボルト、誘電体を酸化タンタル(電子親和力3.2電子ボルト)とする。非特許文献1によると、電極Bと誘電体の接合のポテンシャル障壁は0.36電子ボルトとなる。同様に、電極Aと誘電体の接合のポテンシャル障壁は1.86電子ボルトとなる。

【0038】

電極Aの電位が電極Bよりも低ければ、電子は、電極Aから電極Bに移動することが考えられる。しかし、上述のように電極Aと誘電体との接合のポテンシャル障壁が1.86電子ボルトもあるためトンネル確率は極めて低い。

【0039】

逆に、電極Aの電位が電極Bよりも高ければ、電子は、電極Bから電極Aに移動することが考えられる。この場合、電極Bと誘電体との接合のポテンシャル障壁は0.36電子ボルトと低くなる。さらに、電極Aの電位が電極Bよりも1.5ボルト以上高ければ、その高さのポテンシャル障壁を越えれば、電子は電極Bから電極Aへ移動できる。このため、電極Aの電位が電極Bよりも1.5ボルト以上高くなると、急激にトンネル確率が上昇する。したがって、上記の構成の電極を有するキャパシタでは極性や電位差にも留意する必要がある。

【0040】

なお、多くのhigh−k材料は酸化物であるため、高仕事関数化合物半導体を構成する金属元素以外の元素に占める酸素の比率が20原子%乃至90原子%であると、high−k材料との密着性が良好である。また、界面で酸化還元反応がおこりにくく、界面が化学的に安定である。

【0041】

特に高仕事関数化合物半導体を構成する金属元素のうちインジウム原子と酸素の結合力は、high−k材料で用いられる多くの金属(例えば、ストロンチウム、チタン、バリウム、ジルコニウム、タンタル、ビスマス、鉛、ハフニウム、アルミニウム、イットリウム、ランタン)の原子と酸素の結合力と同等か弱いため、high−k材料から酸素を引き抜くことがなく、high−k材料を安定化させる上で効果的である。

【図面の簡単な説明】

【0042】

【図1】本発明の半導体装置の作製方法の例を説明する断面図である。

【図2】本発明の半導体装置の作製方法の例を説明する断面図である。

【図3】本発明の半導体装置の作製方法の例を説明する断面図である。

【図4】本発明の半導体装置の作製方法の例を説明する上面図である。

【図5】本発明の半導体装置の作製方法の例を説明する断面図である。

【図6】本発明の半導体装置の回路を説明する図である。

【図7】本発明の半導体装置の作製方法の例を説明する断面図である。

【発明を実施するための形態】

【0043】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0044】

(実施の形態1)

図1(A)乃至図1(C)、図2(A)乃至図2(C)及び図4(A)乃至図4(D)に、本実施の形態の半導体装置(スタック型キャパシタを有するDRAM)を作製する工程例を図示する。なお、特に断らない限り、用いる材料、方法等は公知の半導体集積回路作製技術を参照すればよい。

【0045】

図1(A)乃至図1(C)及び図2(A)乃至図2(C)は本実施の形態の半導体装置の作製工程の断面図であり、図4(A)乃至図4(D)は、本実施の形態の半導体装置の作製工程を上面より見た場合の模式図である。図4(A)乃至図4(D)には、主要な配線等のみを描いている。図4(A)乃至図4(D)の一点鎖線A−Bの断面が、図1(A)乃至図1(C)及び図2(A)乃至図2(C)に相当する。

【0046】

本実施の形態では、いわゆるFolded(折り返し)ビット方式のDRAMを作製する場合について説明する。Foldedビット方式では、メモリセルの面積は最小で8F2(Fは最小加工寸法(Feature Size))となる。Fが20nm以下となると、DRAMは物理的な限界に差しかかる。DRAMでは、キャパシタの容量は常にビット線の寄生容量の1割以上であることが求められる。すなわち、デザインルールが縮小しても、ビット線の長さが変わらない場合にはキャパシタの容量は一定であることが必要となる。

【0047】

最小加工寸法Fが20nm以下においては、スタック型キャパシタを採用するにしてもトレンチ型キャパシタを採用するにしても、それらは一辺20nm乃至40nmの孔に形成される。スタック型キャパシタは外側と内側の2つの電極と誘電体によって構成されるが、電極が薄いと電気抵抗が高まるので好ましくない。一方、誘電体(以下では、電極との間に2電子ボルト以上のポテンシャル障壁があると仮定する)も厚さが2nm未満となるとトンネル電流によって電荷の保持特性が悪化するので好ましくない。

【0048】

一般に誘電体の厚さtは、2nm以上、かつ、(F−4[nm])以下が必要とされる。これによると、最小加工寸法Fが20nmの場合には、tは2nm以上16nm以下、Fが10nmの場合には、tは2nm以上6nm以下となる。誘電体は可能な限り薄い方が好ましいので、最小加工寸法Fが10nm乃至20nmでは、4nm乃至6nmとすることが好ましい。一方、上記の条件からFが6nm未満では、tが2nm未満となり、実用的なキャパシタを作製できないということとなる。

【0049】

また、限られた断面積の孔を用いて一定の容量を確保するには、孔を深くするか、誘電体をhigh−k材料で構成するか、いずれかの方法を採用することになる。前者に関しては、アスペクト比200以上の孔を形成することは多くの技術的困難が伴う。そのため、後者の方法が主として検討されている。

【0050】

しかしながら、アスペクト比50乃至200の孔にhigh−k材料を用いたキャパシタを形成することは多くの困難がある。半導体集積回路に用いられている多くの導電性材料では、そのような穴の内面に十分に薄い薄膜を形成することは可能ではあるが、そのような材料は仕事関数が高くないため、high−k材料との間に十分なポテンシャル障壁を形成できず、誘電体の厚さが10nm以上必要となり、上記の関係式からはFが14nm未満では使用できない。

【0051】

一方、白金族元素は仕事関数が高いため、high−k材料との間に十分なポテンシャル障壁を形成できるが、これらの材料は、半導体集積回路に用いられることがあまりなく、現在の技術では、その薄膜を上記のような孔の内面に均一に形成する方法が知られていない。

【0052】

しかしながら、高仕事関数化合物半導体は、例えば、窒化インジウムの場合であれば、インジウムは砒化インジウム等の化合物半導体で用いられている元素であるので、既存の半導体集積回路作製技術を改良することで、必要な厚さの膜を上記の孔の内面に均一に形成できる。以下、図面にしたがって説明する。

【0053】

<図1(A)>

公知の半導体集積回路作製技術により、単結晶シリコン等の基板101上に、第1の絶縁物102、ワード線103aおよび103b、第1コンタクトプラグ104、ビット線105、第2コンタクトプラグ106を形成する。第1の絶縁物は素子分離絶縁物として機能する。

【0054】

なお、この工程は図4(A)乃至図4(C)を参照できる。すなわち、基板101上に第1の絶縁物102(素子分離絶縁物)を形成して、トランジスタを形成するための複数の長方形の領域を千鳥状に形成する(図4(A))。次に、それらの長方形の領域の中央を横切るように複数のワード線103a、103bを形成する。また、長方形の領域には2つずつ第1コンタクトプラグ104を設ける(図4(B))。さらに、各長方形の領域の第1コンタクトプラグ104の1つを結ぶように、ビット線105をジグザグに形成する(図4(C))。残された第1コンタクトプラグ104には、この後、キャパシタが形成される。

【0055】

<図1(B)>

酸化シリコンの第2の絶縁物107を形成して、これにキャパシタを形成するための孔108を設ける。なお、孔108の内面に厚さ2nm乃至5nmの酸化窒化シリコン膜(酸素/窒素=0.2〜0.8)を形成すると、後述する第1の高仕事関数化合物半導体層109との密着性を向上できる。

【0056】

<図1(C)>

孔108の内面に厚さ2nm乃至5nmの第1の高仕事関数化合物半導体層109を形成する。第1の高仕事関数化合物半導体層109は厚さが2nm未満では、導電性が不十分であるため好ましくない。また、第1の高仕事関数化合物半導体層109の厚さの上限は最小加工寸法Fに応じて決定すればよい。例えば、Fが20nmであれば、5nm以下とすることが好ましく、Fが10nmであれば、2.5nm以下とすることが好ましい。

【0057】

本実施の形態では、高仕事関数化合物半導体として、密着性を高めるため酸化窒化インジウムを用いる。酸化窒化インジウムを構成する元素のうち、酸素と窒素の比率、酸素/窒素は0.2乃至0.8とすればよい。なお、孔108の内面に窒素濃度の高い絶縁膜が設けられている場合には、窒化インジウムを用いてもよい。

【0058】

なお、高仕事関数化合物半導体の抵抗率は1×10−2Ωcm以下、好ましくは1×10−4Ωcm以下とするとよい。特に、酸化窒化インジウムに限らず多くの高仕事関数化合物半導体は、水素を1原子%乃至10原子%含有していると、キャリアが増加して導電率が向上するため好ましい。

【0059】

<図2(A)>

厚さ2nm乃至5nmの第3の絶縁物110を形成する。第3の絶縁物110としては各種のhigh−k材料を用いることができるが、酸化ハフニウム、酸化ジルコニウム、酸化タンタル等が好ましい。さらに、再び、酸化窒化インジウムによって、第2の高仕事関数化合物半導体層111を形成する。この際、孔108が酸化窒化インジウムによって埋められるように、第2の高仕事関数化合物半導体層111を形成するとよい。

【0060】

<図2(B)>

第2の高仕事関数化合物半導体層111をエッチングすることにより、孔108以外の部分の第3の絶縁物110を露出させ、対向電極112を形成する。この工程は、孔108の入り口付近での、電極間のショートを防止するためにおこなう。

【0061】

<図2(C)>

その後、第4の絶縁物113、第3コンタクトプラグ114を形成し、さらに第5の絶縁物115を形成し、キャパシタ線116a、116b、116cを形成する。本実施の形態では、図4(D)に示すように、キャパシタ線116a、116b、116cをワード線103a、103bと平行に形成する。しかし、キャパシタ線をビット線105と平行に形成してもよい。

【0062】

このようにして、Foldedビット方式のDRAMのメモリセルを作製できる。なお、キャパシタ線116a、116b、116cはそれぞれ、独立に電位を制御できるが、常に同じ電位を与える共通電位線として用いてもよい。

【0063】

(実施の形態2)

図3(A)乃至図3(C)、図4(E)および図4(F)に本実施の形態を示す。本実施の形態は薄膜トランジスタを用いて、オープンビット型のDRAMを作製するものである。オープンビット型のDRAMのメモリセルの面積は理想的には、実施の形態1で説明したFoldedビット線型DRAMよりも小さい6F2(Fは最小加工寸法)まで小さくできる。以下図面にしたがって説明する。

【0064】

<図3(A)>

第1の絶縁物201の上にビット線202を形成する。さらに、第2の絶縁物203を形成し、これにビット線202に接続する第1コンタクトプラグ204を形成する。さらに、適切な厚さおよび大きさの半導体層205、半導体層205を覆う第3の絶縁物206、ワード線207a、207bを形成する。第3の絶縁物206は薄膜トランジスタのゲート絶縁膜としても機能する。

【0065】

半導体層205は特に限定されず、単結晶、多結晶、非晶質いずれでもよく、シリコン、ゲルマニウム等の14族元素、砒化ガリウム、酸化インジウム、硫化亜鉛、窒化ガリウム等の化合物でもよい。また、純物質に限らず、何らかの添加物を含有してもよい。また、半導体層205は必要に応じて、n型の領域やp型の領域あるいは真性の領域、あるいはそれらの中間の導電性を示す領域を有してもよい。

【0066】

以上の工程は、図4(E)および図4(F)を参照することもできる。すなわち、第1の絶縁物201上にビット線202と、これに接続する第1コンタクトプラグ204を形成する(図4(E))。さらに、ビット線202と重なるように、半導体層205を形成する。また、ワード線207a、207bを形成する(図4(F))。

【0067】

一般に、第1の絶縁物201の下には、何らかの半導体集積回路が設けられていることが多い。その場合には、それらによって発生するノイズが上層の薄膜トランジスタの動作に支障をもたらすことがある。この問題に対しては、薄膜トランジスタの下に何らかのシールド層を設けて、ノイズを吸収させるとよいが、図4(F)に見られるように、ビット線202と半導体層205が重なるように配置すると、ビット線202がシールド層となり、ノイズを吸収する。

【0068】

<図3(B)>

第4の絶縁物208を形成し、第2コンタクトプラグ209a、209bを形成する。さらにキャパシタを形成するための孔を有する第5の絶縁物210を形成し、高仕事関数化合物半導体層211a、211bとそれらを覆う第6の絶縁物212を形成する。第6の絶縁物212としてはhigh−k材料を用いるとよい。高仕事関数化合物半導体層211a、211bと第6の絶縁物212の作製方法については実施の形態1を参照すればよい。

【0069】

<図3(C)>

対向電極213a、213bを形成した後、第7の絶縁物214と対向電極213a、213bに接続する第3コンタクトプラグ215a、215b、キャパシタ線216を形成する。以上で、オープンビット型DRAMのメモリセルを作製できる。

【0070】

本実施の形態では、キャパシタ線216は、ビット線202と平行に配置される。キャパシタ線216には、常に同じ電位を与えてもよいが、ビット線202に同期した電位としてもよい。例えば、特許文献1に記載されているように、ビット線とは逆の位相の相補的な電位を与えてもよい。

【0071】

本実施の形態で示したオープンビット型DRAMのメモリセルは、ビット線202がトランジスタの下に配置されているため、スタック型キャパシタを有しながらも設計の自由度が高い。スタック型キャパシタを有するオープンビット型DRAMとしては、例えば、特許文献2や特許文献3に記載されているが、例えば、特許文献2では、トランジスタとビット線を接続するため補助配線が必要であり、また、特許文献3では、ビット線がワード線と直角でない角度で交差する(その結果、メモリセルが平行四辺形となる)ことが求められる。

【0072】

いずれも、余計なプロセスや余分な面積が生じる。これらは、ビット線とキャパシタが共にトランジスタの上に存在するためであり、ビット線がキャパシタを避けるように配置することが求められる。これに対し、本実施の形態のようにビット線をトランジスタの下、キャパシタをトランジスタの上とすると、キャパシタの位置に関係なくビット線を配置できるため、極めて効率的なレイアウトとなる。

【0073】

(実施の形態3)

図5及び図6に本実施の形態を示す。本実施の形態は2つのトランジスタを用いて、信号増幅型のメモリセル(特許文献4参照)を作製するものである。

【0074】

図6(A)は実施の形態1および実施の形態2でも説明した通常の1トランジスタ1キャパシタ型のDRAMのメモリセルの回路図である。このDRAMでは、ワード線WLの電位に応じて書き込みトランジスタWTがオンオフし、ビット線BLとキャパシタCSの間で電荷を移動させる。そのため、ビット線BLの寄生容量に応じて、キャパシタCSの容量を決定する必要があり、デザインルールが縮小しても同程度の容量が必要である。そのため、トレンチ型キャパシタやスタック型キャパシタ、あるいはhigh−k材料の採用等が必須となっている。

【0075】

これに対し、図6(B)に示されるメモリセルは2トランジスタ1キャパシタ型であり、セルに蓄えられた電荷を読み出しトランジスタRTで増幅するため、キャパシタの容量は理想的には読み出しトランジスタRTと同じ速度で縮小することができる。

【0076】

しかしながら、現実には書き込みトランジスタWTのソースとドレイン間はオフ状態であっても有限の抵抗状態(通常、1×1013Ω〜1×1014Ω)である。キャパシタの電荷がなくなるまでの時間は、この抵抗とキャパシタCSの容量の積である。したがって、キャパシタCSの容量が減少すると、電荷の減少も早くなる。

【0077】

図6(A)の1トランジスタ1キャパシタ型のDRAMのメモリセルのキャパシタCSの容量は1×10−14F程度であるため、電荷がなくなるのに要する時間は0.1秒程度である。そのため、このタイプのメモリセルでは1秒に数十回電荷を再注入(リフレッシュ)する必要がある。

【0078】

このことは、図6(B)のメモリセルでも同様で、キャパシタCSの容量が1×10−14F程度であれば1秒に数十回のリフレッシュで済む。しかし、そのような大きな容量を有するのであれば余分なトランジスタを設ける意味はない。トランジスタを余分に設けるからには、容量をさらに小さくすることが望ましい。

【0079】

しかし、容量がさらに10分の1、100分の1となれば、電荷がなくなる時間も10分の1、100分の1となるので、リフレッシュの回数も1秒に数百回、数千回となり、およそ現実的でなくなる。すなわち、図6(B)に示されるメモリセルは、トランジスタのオフ状態の抵抗が1×1015Ω以下では実用的ではない。

【0080】

図6(B)に示される回路を用いて、実用的なメモリセルを構成するには、書き込みトランジスタWTのオフ抵抗が1×1018Ω以上、好ましくは1×1021Ω以上であることが必須である。例えば、キャパシタCSの容量を通常のDRAMの千分の1の1×10−17Fとすると、書き込みトランジスタWTのオフ抵抗が1×1018Ωのときは、1秒間に数回、オフ抵抗が1×1021Ωのときは、数分に1回のリフレッシュでよく、通常のDRAMと比較しても消費電力が低減できる。オフ抵抗がさらに大きければよりリフレッシュの頻度を低下させることができる。

【0081】

このような非常に高いオフ抵抗を得るためには、極めて薄いシリコン(特許文献4参照)、あるいは、バンドギャップが2.5電子ボルト以上4電子ボルト以下、好ましくは3電子ボルト以上3.8電子ボルト以下のワイドバンドギャップ半導体を使用すること(特許文献5参照)が必要となる。後者としては、例えば、酸化インジウム、酸化亜鉛等の酸化物半導体、窒化ガリウム等の窒化物半導体、硫化亜鉛等の硫化物半導体等を用いればよい。

【0082】

オフ抵抗は、熱的に励起するキャリアの濃度に比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、バルクのシリコンの場合にはバンドギャップが1.1電子ボルトなので、室温(300K)での熱励起キャリアの濃度は1×1011cm−3程度である。

【0083】

なお、特許文献4では、極めて薄いシリコンでは、量子効果によりバンドギャップが拡大するため、熱励起キャリアはバルクのシリコンより3桁程度少ないと報告されている。

【0084】

一方、バンドギャップ3.2電子ボルトの半導体では熱励起キャリアの濃度は1×10−7cm−3程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2電子ボルトの半導体の抵抗率は、シリコンより18桁も大きい。

【0085】

なお、ドナーやアクセプタによるキャリアは極力、低濃度であることが好ましく、その濃度は、1×1012cm−3以下とすることが好ましい。これらのキャリア濃度によりトランジスタのしきい値が決定される。

【0086】

このように、図6(B)に示される回路をメモリセルとして用いる場合には、トランジスタに用いる半導体の種類や物性が重要である。なお、上記の議論はキャパシタの誘電体の抵抗を無限大としたものであるが、誘電体の厚さやポテンシャル障壁の高さによっては有限の抵抗が生じることがある。その結果、トランジスタのオフ抵抗よりもキャパシタの寄生抵抗が小さくなると、リフレッシュ間隔が想定よりも短くなることがある。

【0087】

可能な限りキャパシタの寄生抵抗を大きくするには、実質的な誘電体の厚さを5nm以上、好ましくは10nm以上、ポテンシャル障壁を1.5電子ボルト以上、好ましくは2.5電子ボルト以上とするとよい。以下図面にしたがって説明する。

【0088】

<図5(A)>

単結晶シリコン等の基板301に導電性領域302a、302b、フローティングゲート303を形成する。このうち、導電性領域302aは図6(B)に共通電位線CLで示される配線となり、書き込みワード線WWL、読み出しワード線RWLと平行に形成する。また、第1の絶縁物304を形成する。

【0089】

<図5(B)>

第1の絶縁物304をエッチングして、フローティングゲート303の表面を露出させ、また、コンタクトホールを形成して、導電性領域302bに接続する第1コンタクトプラグ305を埋め込む。さらに、厚さ2nm乃至10nm、好ましくは2nm乃至5nmの適切な形状、面積の半導体層306と、それを覆う第2の絶縁物307を形成する。半導体層306の材料は上記した条件を満たすものを選択するとよい。

【0090】

第2の絶縁物307は、半導体層306を用いて形成される薄膜トランジスタのゲート絶縁膜として、また、キャパシタの誘電体としても機能する。さらに、第2の絶縁物307はhigh−k材料を用いて構成し、厚さは2nm乃至10nm、好ましくは2nm乃至5nmとする。

【0091】

<図5(C)>

反応性スパッタリング法で酸窒化亜鉛もしくは酸窒化インジウム、酸窒化錫、酸窒化インジウム亜鉛、酸窒化インジウム亜鉛ガリウム(組成式はInaGabZncOdNe、(0≦a≦1、0≦b≦1、0≦c≦1、0≦d≦1、0≦e≦1))等の仕事関数の高い酸窒化物膜(以下、高仕事関数酸窒化物膜308という)を成膜する。

【0092】

例えば、酸窒化亜鉛を成膜するには、酸化亜鉛をターゲットにして、窒素濃度が50%以上かつ酸素濃度が5%以下の雰囲気という条件を採用すればよい。同様に、酸窒化インジウム、酸窒化錫、酸窒化インジウム亜鉛、酸窒化インジウム亜鉛ガリウムを成膜するには、窒素濃度が50%以上かつ酸素濃度が5%以下の雰囲気で、それぞれ、酸化インジウム、酸化錫、酸化インジウム亜鉛、酸化インジウム亜鉛ガリウムをターゲットとして用いればよい。

【0093】

また、その際には、基板温度は100℃乃至600℃、好ましくは150℃乃至450℃とするとよい。また、成膜後、100℃乃至600℃、好ましくは150℃乃至450℃の非酸化性雰囲気で熱処理してもよい。

【0094】

なお、スパッタリング法以外にも、ALD法やCVD法(MOCVD法等)を採用してもよい。特に、第2の絶縁物307の厚さが5nm以下の場合には、第2の絶縁物307へのダメージの少ないALD法やCVD法を用いることが好ましい。

【0095】

酸化インジウム亜鉛ガリウムの例として、組成式InGaZnO4で表されるものは、YbFe2O4構造と呼ばれる結晶構造を取ることが知られている(非特許文献3参照)。しかしながら、例えば、5原子%以上の窒素が添加されるとウルツ鉱型構造が安定相となり、それにともなって電子状態も劇的に変化する。また、YbFe2O4構造に比べるとウルツ鉱型構造は結晶化が容易であるため、比較的低温で結晶化する。

【0096】

電子状態に関しては、例えば、バンドギャップはYbFe2O4構造のものが3.2電子ボルト程度であるが、ウルツ鉱型構造のものでは2.2電子ボルト以下となり、また、電子親和力も、前者が4.3電子ボルト程度のものが、後者では5.5電子ボルト以上となる。電子親和力が4.9電子ボルト以上となるため、欠陥準位によりn型の導電性を呈することとなる。なお、水素はドナーとして機能するため、水素を添加することによってもキャリア濃度を高めることもできる。

【0097】

なお、高仕事関数酸窒化物膜308は、窒素や亜鉛、錫、インジウム以外に酸素を窒素の2乃至5倍含有していると、ゲート絶縁膜との界面でのトラップ準位の発生を抑制する上で好ましい。また、高仕事関数酸窒化物膜308は、水素を1原子%乃至10原子%含有していると、界面の状況が改善され、かつ、キャリアが増加して導電率が向上するため好ましい。

【0098】

なお、酸化インジウム亜鉛ガリウム(In−Ga−Zn−O)の代わりに、二元系金属酸化物である、In−Sn−O、Sn−Zn−O、Al−Zn−O、In−Ga−Oや、三元系金属酸化物であるIn−Sn−Zn−O、In−Al−Zn−O、Sn−Ga−Zn−O、Al−Ga−Zn−O、Sn−Al−Zn−Oや、四元系金属酸化物であるIn−Sn−Ga−Zn−Oなどを用いてもよい。ここで、例えば、In−Ga−Zn−Oとは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物という意味である。

【0099】

その後、導電性の高い金属や金属化合物よりなる導電性膜309を適切な厚さだけ形成する。金属膜としてはアルミニウム、チタン、タンタル、タングステン等やそれらを50%以上有する合金を用いることができ、金属化合物膜としては、それらの窒化物膜を用いることができる。

【0100】

<図5(D)>

高仕事関数酸窒化物膜308と導電性膜309をエッチングして、これらの積層した膜よりなる書き込みワード線310と読み出しワード線311を形成する。また、書き込みワード線310と読み出しワード線311をマスクとして、アルゴンのような希ガス元素、燐やアルミニウム、ガリウム等の酸化されやすい元素等を照射して半導体層306に酸素欠損等を導入し、n型領域312を形成する。窒素イオンを照射しても同様にn型領域を作製できる。

【0101】

<図5(E)>

第3の絶縁物313と、第1コンタクトプラグ305に接続する第2コンタクトプラグ314、およびビット線315を形成する。ビット線315は図6(B)のビット線BLに相当し、書き込みワード線WWLと直交する。

【0102】

このようにして作製されるメモリセルの面積は8F2乃至12F2となる。また、このメモリセルでは、フローティングゲート303と読み出しワード線311の間にキャパシタ316(図6(B)のキャパシタCSに相当)が形成される。薄膜トランジスタはnチャネル型であるため、電荷を保存するためには、キャパシタ側の電位はビット線電位と同じかより高いことが好ましい。

【0103】

同様に、読み出しワード線311の電位は、フローティングゲート303の電位と同じかより低いことが好ましい。その条件が満たされるなら、フローティングゲート303の材料の仕事関数に関して特段の条件はなく、むしろ、仕事関数が半導体層を構成する半導体の電子親和力以下であると半導体層306との接合の抵抗を下げることができて好ましい。

【0104】

読み出しワード線311の電位が、フローティングゲート303の電位より低い場合(すなわち、フローティングゲート303に正の電荷が蓄積されている場合)、これらの間にある半導体層306が空乏化し、誘電体となることがある。その場合、キャパシタ316の誘電体は、第2の絶縁物307と半導体層306の積層であるとみなされる。

【0105】

したがって、キャパシタ316の誘電体の実質的な厚さは第2の絶縁物307の電気的な厚さと半導体層306の電気的な厚さの和となる。例えば、半導体層306と第2の絶縁物307の誘電率が同じであれば、第2の絶縁物307の厚さが2nmであったとしても、半導体層306の厚さが4nmであれば、キャパシタ316の誘電体の実質的な厚さは6nmであるため、トンネル電流は十分に小さくできる。

【0106】

この条件下では電子は、読み出しワード線311から、第2の絶縁物307と半導体層306を経て、フローティングゲート303へ移動しようとするが、読み出しワード線311と第2の絶縁物307の接合部は高仕事関数酸窒化物が用いられているため、ポテンシャル障壁が1.5電子ボルト以上となるためトンネル確率が極めて低く、十分な絶縁性が保たれる。

【0107】

一方、データの書き込みの際には、読み出しワード線311の電位を半導体層306よりも高くすることにより、半導体層に反転層(チャネル)を形成させてもよい。反転層は導電性が高く、よって、ビット線315の電位が、フローティングゲート303に伝わりやすくなる。

【0108】

なお、書き込みワード線310と半導体層306とのトンネル電流を低減させる目的からは、書き込みワード線310の電位を調整して、近傍(少なくとも書き込みワード線310から6nm以内)の半導体層306を空乏化させることが好ましい。

【0109】

(実施の形態4)

図7に本実施の形態を示す。本実施の形態では実施の形態3と同様に図6(B)に示すメモリセルの作製工程について説明する。以下図面にしたがって説明する。なお、詳細は実施の形態3を参照すればよい。

【0110】

<図7(A)>

実施の形態3で説明した方法等により、基板401上に、導電性領域402a、402b、フローティングゲート403、第1の絶縁物404、第1コンタクトプラグ405、半導体層406、第2の絶縁物407、書き込みワード線408、第3の絶縁物409を形成する。なお、ここで、書き込みワード線には特に高仕事関数化合物半導体を用いる必要はない。

【0111】

<図7(B)>

フローティングゲート403、あるいは第1コンタクトプラグ405に接続する第2コンタクトプラグ410を形成する。さらに、高仕事関数酸窒化物膜411をいくつかの第2コンタクトプラグ410と接するように形成する。高仕事関数酸窒化物膜411の作製方法は実施の形態3を参照すればよい。

【0112】

また、高仕事関数酸窒化物膜411を覆って、high−k材料を用いて、第4の絶縁物412を形成する。第4の絶縁物412は、キャパシタ414の誘電体として機能する。厚さは5nm以上10nm以下とすればよい。作製方法等は実施の形態1乃至実施の形態3を参照すればよい。

【0113】

さらに、実施の形態3の書き込みワード線310、読み出しワード線311と同様に高仕事関数酸窒化物膜と導電成膜の積層である読み出しワード線413を第4の絶縁物412上に形成する。この結果、読み出しワード線413と高仕事関数酸窒化物膜411、第4の絶縁物412からなるキャパシタ414が形成される。

【0114】

<図7(C)>

第5の絶縁物415と、第2コンタクトプラグ410のうち、高仕事関数酸窒化物膜411が設けられていないものに接続する第3コンタクトプラグ416、および第3コンタクトプラグ416に接続するビット線417を形成する。このようにして作製されるメモリセルの面積は6F2乃至9F2(Fは最小加工寸法)となる。

【符号の説明】

【0115】

101 基板

102 第1の絶縁物

103a ワード線

103b ワード線

104 第1コンタクトプラグ

105 ビット線

106 第2コンタクトプラグ

107 第2の絶縁物

108 孔

109 第1の高仕事関数化合物半導体層

110 第3の絶縁物

111 第2の高仕事関数化合物半導体層

112 対向電極

113 第4の絶縁物

114 第3コンタクトプラグ

115 第5の絶縁物

116a キャパシタ線

116b キャパシタ線

116c キャパシタ線

201 第1の絶縁物

202 ビット線

203 第2の絶縁物

204 第1コンタクトプラグ

205 半導体層

206 第3の絶縁物

207a ワード線

207b ワード線

208 第4の絶縁物

209a 第2コンタクトプラグ

209b 第2コンタクトプラグ

210 第5の絶縁物

211a 高仕事関数化合物半導体層

211b 高仕事関数化合物半導体層

212 第6の絶縁物

213a 対向電極

213b 対向電極

214 第7の絶縁物

215a 第3コンタクトプラグ

215b 第3コンタクトプラグ

216 キャパシタ線

301 基板

302a 導電性領域

302b 導電性領域

303 フローティングゲート

304 第1の絶縁物

305 第1コンタクトプラグ

306 半導体層

307 第2の絶縁物

308 高仕事関数酸窒化物膜

309 導電性膜

310 書き込みワード線

311 読み出しワード線

312 n型領域

313 第3の絶縁物

314 第2コンタクトプラグ

315 ビット線

316 キャパシタ

401 基板

402a 導電性領域

402b 導電性領域

403 フローティングゲート

404 第1の絶縁物

405 第1コンタクトプラグ

406 半導体層

407 第2の絶縁物

408 書き込みワード線

409 第3の絶縁物

410 第2コンタクトプラグ

411 高仕事関数酸窒化物膜

412 第4の絶縁物

413 読み出しワード線

414 キャパシタ

415 第5の絶縁物

416 第3コンタクトプラグ

417 ビット線

WL ワード線

BL ビット線

CL 共通電位線

CS キャパシタ

WT 書き込みトランジスタ

RT 読み出しトランジスタ

WWL 書き込みワード線

RWL 読み出しワード線

【特許請求の範囲】

【請求項1】

誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体を有するキャパシタ。

【請求項2】

誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体と、前記n型半導体に対向するように前記誘電体の他の面に設けられた導電性を有する材料とを有する半導体装置。

【請求項3】

絶縁物の側面に形成された、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上の膜状のn型半導体と、前記n型半導体上に形成された膜状の誘電体とを有する半導体装置。

【請求項4】

請求項1乃至3のいずれか一において、前記n型半導体は、その仕事関数が5.5電子ボルト以上であることを特徴とする半導体装置。

【請求項5】

前記誘電体はチタン酸ストロンチウム、チタン酸鉛、チタン酸バリウムストロンチウム、ジルコン酸鉛、ジルコン酸バリウム、酸化タンタル、ビスマスチタン酸ストロンチウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化アルミニウム、酸化イットリウム、酸化ランタン、珪酸ジルコニウム、珪酸ハフニウムから選ばれた1つ以上の材料を含むことを特徴とする請求項1乃至4のいずれか一に記載の半導体装置。

【請求項6】

前記誘電体は、ストロンチウム、チタン、バリウム、ジルコニウム、鉛、タンタル、ビスマス、ハフニウム、アルミニウム、イットリウム、ランタンから選ばれた1つ以上の元素が、誘電体を構成する金属元素のうちの50%以上である酸化物であることを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【請求項7】

前記n型半導体の厚さは4nm以上10nm以下であることを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項8】

前記n型半導体は、5原子%以上50原子%以下の濃度の窒素を有することを特徴とする請求項1乃至7のいずれか一に記載の半導体装置。

【請求項1】

誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体を有するキャパシタ。

【請求項2】

誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上のn型半導体と、前記n型半導体に対向するように前記誘電体の他の面に設けられた導電性を有する材料とを有する半導体装置。

【請求項3】

絶縁物の側面に形成された、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有し、仕事関数が5.0電子ボルト以上の膜状のn型半導体と、前記n型半導体上に形成された膜状の誘電体とを有する半導体装置。

【請求項4】

請求項1乃至3のいずれか一において、前記n型半導体は、その仕事関数が5.5電子ボルト以上であることを特徴とする半導体装置。

【請求項5】

前記誘電体はチタン酸ストロンチウム、チタン酸鉛、チタン酸バリウムストロンチウム、ジルコン酸鉛、ジルコン酸バリウム、酸化タンタル、ビスマスチタン酸ストロンチウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化アルミニウム、酸化イットリウム、酸化ランタン、珪酸ジルコニウム、珪酸ハフニウムから選ばれた1つ以上の材料を含むことを特徴とする請求項1乃至4のいずれか一に記載の半導体装置。

【請求項6】

前記誘電体は、ストロンチウム、チタン、バリウム、ジルコニウム、鉛、タンタル、ビスマス、ハフニウム、アルミニウム、イットリウム、ランタンから選ばれた1つ以上の元素が、誘電体を構成する金属元素のうちの50%以上である酸化物であることを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【請求項7】

前記n型半導体の厚さは4nm以上10nm以下であることを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項8】

前記n型半導体は、5原子%以上50原子%以下の濃度の窒素を有することを特徴とする請求項1乃至7のいずれか一に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−178553(P2012−178553A)

【公開日】平成24年9月13日(2012.9.13)

【国際特許分類】

【出願番号】特願2012−19405(P2012−19405)

【出願日】平成24年2月1日(2012.2.1)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成24年9月13日(2012.9.13)

【国際特許分類】

【出願日】平成24年2月1日(2012.2.1)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]