クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

Notice: Undefined index: DEJ in /mnt/www/gzt_disp.php on line 298

【特許請求の範囲】

【請求項1】

サンプリング回路とエッジ検出器と位相選択信号生成回路とクロックデータ生成回路とを具備するクロックデータリカバリ回路であって、

前記サンプリング回路は受信データ信号を多相クロック信号によってサンプリングすることによって、複数のサンプリング信号を生成して、

前記エッジ検出器は、前記複数のサンプリング信号と前記多相クロック信号に応答して、複数のエッジ検出信号を生成して、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数の位相選択信号を生成して、

前記クロックデータ生成回路は、前記複数のサンプリング信号と前記複数の位相選択信号と前記多相クロック信号とに応答して、再生クロックと再生データとを生成して、

前記エッジ検出器は複数のエッジ検出回路を含み、前記エッジ検出器の前記複数のエッジ検出回路は前記複数のサンプリング信号と前記多相クロック信号とに応答して、前記複数のエッジ検出信号を生成して、

前記複数のエッジ検出回路の各エッジ検出回路は、第1のエッジ検出回路と第2のエッジ検出回路とを含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の−1位相よりも進んでいることを検出した場合には、第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の+1位相よりも遅れていることを検出した場合には、第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第1のエッジ検出回路と前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の±1位相の範囲に存在することを検出可能とされ、

前記第1のエッジ検出回路と前記第2のエッジ検出回路が現在供給されている前記受信データ信号の前記データエッジが前記±1位相の範囲に存在することを検出した場合には、前記エッジ検出器の次回のエッジ検出位相は前記1個のエッジ検出クロック信号の前記エッジ検出位相に維持される

ことを特徴とするクロックデータリカバリ回路。

【請求項2】

請求項1において、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数のゲート制御信号を更に生成して、

前記位相選択信号生成回路から生成される前記複数のゲート制御信号は、前記エッジ検出器の前記複数のエッジ検出回路に供給され、

前記エッジ検出器から生成される前記複数のエッジ検出信号のうちの1個のエッジ検出信号は、前記多相クロック信号のうちの現在供給されている前記受信データ信号の前記データエッジに対応する1個のクロック信号を示すための所定の電圧レベルに設定され、

前記所定の電圧レベルに設定された前記1個のエッジ検出信号に応答して、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの1個のゲート制御信号は、所定の信号レベルに設定され、

前記エッジ検出器の前記複数のエッジ検出回路のうちの前記所定の信号レベルに設定される前記1個のゲート制御信号が供給される1個のエッジ検出回路は活性状態に制御され、前記エッジ検出器の前記複数のエッジ検出回路のそれ以外のエッジ検出回路は非活性状態に制御される

ことを特徴とするクロックデータリカバリ回路。

【請求項3】

請求項2において、

前記位相選択信号生成回路は、前記複数の位相選択信号と前記複数のゲート制御信号を生成する複数の位相選択信号生成回路を含み、

前記複数の位相選択信号生成回路の各位相選択信号生成回路から生成される1個の位相選択信号と1個のゲート制御信号とは、実質的に0.5ユニットインターバルの位相差を有する

ことを特徴とするクロックデータリカバリ回路。

【請求項4】

請求項3において、

前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路と前記第2のエッジ検出回路は、第1排他的論理和回路と第2排他的論理和回路をそれぞれ含み、

前記第1のエッジ検出回路の前記第1排他的論理和回路には第1入力信号と第1参照信号とが供給され、前記第2のエッジ検出回路の前記第2排他的論理和回路には第2入力信号と第2参照信号とが供給され、

前記第1排他的論理和回路に供給される前記第1入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−1位相分進んだ1位相進相クロック信号によって前記受信データ信号をサンプリングして形成された1位相進相サンプリング信号であり、

前記第1排他的論理和回路に供給される前記第1参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−2位相分またはそれ以上進んだ複数位相進相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相進相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+1位相分遅れた1位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された1位相遅相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+2位相分またはそれ以上進んだ複数位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相遅相サンプリング信号であり、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第1排他的論理和回路の所定レベルの出力信号に応答して、前記第1のエッジ検出出力信号を生成して、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第2排他的論理和回路の所定レベルの出力信号に応答して、前記第2のエッジ検出出力信号を生成する

ことを特徴とするクロックデータリカバリ回路。

【請求項5】

請求項3において、

電源電圧投入時もしくはスタンバイ解除時の初期化動作では、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの任意の1個のゲート制御信号は、前記所定の信号レベルに設定され、

前記初期化動作では、更に前記位相選択信号生成回路から生成される前記複数の位相選択信号のうちの前記任意の1個のゲート制御信号と実質的に0.5ユニットインターバルの位相差を有する1個の位相選択信号が、前記所定の信号レベルに設定される

ことを特徴とするクロックデータリカバリ回路。

【請求項6】

請求項3において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答した前記エッジ検出位相から前記−1位相分または前記+1位相分の変更による状態遷移を少なくとも2度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とするクロックデータリカバリ回路。

【請求項7】

請求項3において、

前記複数のエッジ検出回路の前記各エッジ検出回路は、第3のエッジ検出回路と第4のエッジ検出回路とを更に含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−1位相から−2位相との間に進んでいることを検出した場合には、前記第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+1位相から+2相との間に遅れていることを検出した場合には、前記第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第3のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−2位相から−3位相との間に進んでいることを検出した場合には、前記第3のエッジ検出出力信号を生成して、

前記第4のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+2位相から+3相との間に遅れていることを検出した場合には、前記第4のエッジ検出出力信号を生成して、

前記エッジ検出器の前記次回のエッジ検出位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−2位相分または前記+2位相分変更される

ことを特徴とするクロックデータリカバリ回路。

【請求項8】

請求項7において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答した前記エッジ検出位相から前記−2位相分または前記+2位相分の変更による状態遷移を1度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とするクロックデータリカバリ回路。

【請求項9】

請求項3において、

前記エッジ検出器は、前記複数のエッジ検出回路の複数の出力端子に接続された複数の積分器を更に含み、

前記複数の積分器の各積分器は、前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路の第1エッジ検出結果と前記第2のエッジ検出回路の第2エッジ検出結果の平均化処理を実行する

ことを特徴とするクロックデータリカバリ回路。

【請求項10】

請求項3において、

前記クロックデータリカバリ回路は、前記クロックデータリカバリ回路の外部から供給される外部クロック信号に応答して前記多相クロックを生成する多相クロック生成回路を更に具備して、

前記クロックデータリカバリ回路の内部で、前記多相クロック生成回路から生成される前記多相クロックが、前記サンプリング回路と前記エッジ検出器と前記位相選択信号生成回路と前記クロックデータ生成回路とに供給される

ことを特徴とするクロックデータリカバリ回路。

【請求項11】

請求項3において、

前記多相クロックを生成する前記多相クロック生成回路は、位相比較器とチャージポンプとループフィルタと電圧制御遅延線路を含むディレイド・ロックド・ループによって構成された

ことを特徴とするクロックデータリカバリ回路。

【請求項12】

クロックデータリカバリ回路と、デシリアライザと、シリアライザと、PLL回路とを含むインターフェースユニットを有する送受信半導体集積回路であって、

パラレル・シリアル変換器としての前記シリアライザは、パラレル送信信号と前記PLL回路から生成されるPLLクロックとからシリアル送信信号を生成するものであり、

前記クロックデータリカバリ回路は、受信データ信号と前記PLL回路から生成される前記PLLクロックとに応答して、再生クロックと再生データとを生成するものであり、

シリアル・パラレル変換器としての前記デシリアライザは、前記クロックデータリカバリ回路から生成される前記再生クロックと前記再生データとからパラレル受信データを生成するものであり、

前記クロックデータリカバリ回路は、サンプリング回路とエッジ検出器と位相選択信号生成回路とクロックデータ生成回路とを具備して、

前記サンプリング回路は受信データ信号を多相クロック信号によってサンプリングすることによって、複数のサンプリング信号を生成して、

前記エッジ検出器は、前記複数のサンプリング信号と前記多相クロック信号に応答して、複数のエッジ検出信号を生成して、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数の位相選択信号を生成して、

前記クロックデータ生成回路は、前記複数のサンプリング信号と前記複数の位相選択信号と前記多相クロック信号とに応答して、再生クロックと再生データとを生成して、

前記エッジ検出器は複数のエッジ検出回路を含み、前記エッジ検出器の前記複数のエッジ検出回路は前記複数のサンプリング信号と前記多相クロック信号とに応答して、前記複数のエッジ検出信号を生成して、

前記複数のエッジ検出回路の各エッジ検出回路は、第1のエッジ検出回路と第2のエッジ検出回路とを含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の−1位相よりも進んでいることを検出した場合には、第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の+1位相よりも遅れていることを検出した場合には、第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第1のエッジ検出回路と前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の±1位相の範囲に存在することを検出可能とされ、

前記第1のエッジ検出回路と前記第2のエッジ検出回路が現在供給されている前記受信データ信号の前記データエッジが前記±1位相の範囲に存在することを検出した場合には、前記エッジ検出器の次回のエッジ検出位相は前記1個のエッジ検出クロック信号の前記エッジ検出位相に維持される

ことを特徴とする送受信半導体集積回路。

【請求項13】

請求項12において、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数のゲート制御信号を更に生成して、

前記位相選択信号生成回路から生成される前記複数のゲート制御信号は、前記エッジ検出器の前記複数のエッジ検出回路に供給され、

前記エッジ検出器から生成される前記複数のエッジ検出信号のうちの1個のエッジ検出信号は、前記多相クロック信号のうちの現在供給されている前記受信データ信号の前記データエッジに対応する1個のクロック信号を示すための所定の電圧レベルに設定され、

前記所定の電圧レベルに設定された前記1個のエッジ検出信号に応答して、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの1個のゲート制御信号は、所定の信号レベルに設定され、

前記エッジ検出器の前記複数のエッジ検出回路のうちの前記所定の信号レベルに設定される前記1個のゲート制御信号が供給される1個のエッジ検出回路は活性状態に制御され、前記エッジ検出器の前記複数のエッジ検出回路のそれ以外のエッジ検出回路は非活性状態に制御される

ことを特徴とする送受信半導体集積回路。

【請求項14】

請求項13において、

前記位相選択信号生成回路は、前記複数の位相選択信号と前記複数のゲート制御信号を生成する複数の位相選択信号生成回路を含み、

前記複数の位相選択信号生成回路の各位相選択信号生成回路から生成される1個の位相選択信号と1個のゲート制御信号とは、実質的に0.5ユニットインターバルの位相差を有する

ことを特徴とする送受信半導体集積回路。

【請求項15】

請求項14において、

前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路と前記第2のエッジ検出回路は、第1排他的論理和回路と第2排他的論理和回路をそれぞれ含み、

前記第1のエッジ検出回路の前記第1排他的論理和回路には第1入力信号と第1参照信号とが供給され、前記第2のエッジ検出回路の前記第2排他的論理和回路には第2入力信号と第2参照信号とが供給され、

前記第1排他的論理和回路に供給される前記第1入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−1位相分進んだ1位相進相クロック信号によって前記受信データ信号をサンプリングして形成された1位相進相サンプリング信号であり、

前記第1排他的論理和回路に供給される前記第1参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−2位相分またはそれ以上進んだ複数位相進相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相進相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+1位相分遅れた1位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された1位相遅相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+2位相分またはそれ以上進んだ複数位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相遅相サンプリング信号であり、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第1排他的論理和回路の所定レベルの出力信号に応答して、前記第1のエッジ検出出力信号を生成して、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第2排他的論理和回路の所定レベルの出力信号に応答して、前記第2のエッジ検出出力信号を生成する

ことを特徴とする送受信半導体集積回路。

【請求項16】

請求項14において、

電源電圧投入時もしくはスタンバイ解除時の初期化動作では、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの任意の1個のゲート制御信号は、前記所定の信号レベルに設定され、

前記初期化動作では、更に前記位相選択信号生成回路から生成される前記複数の位相選択信号のうちの前記任意の1個のゲート制御信号と実質的に0.5ユニットインターバルの位相差を有する1個の位相選択信号が、前記所定の信号レベルに設定される

ことを特徴とする送受信半導体集積回路。

【請求項17】

請求項14において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答した前記エッジ検出位相から前記−1位相分または前記+1位相分の変更による状態遷移を少なくとも2度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とする送受信半導体集積回路。

【請求項18】

請求項14において、

前記複数のエッジ検出回路の前記各エッジ検出回路は、第3のエッジ検出回路と第4のエッジ検出回路とを更に含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−1位相から−2位相との間に進んでいることを検出した場合には、前記第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+1位相から+2相との間に遅れていることを検出した場合には、前記第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第3のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−2位相から−3位相との間に進んでいることを検出した場合には、前記第3のエッジ検出出力信号を生成して、

前記第4のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+2位相から+3相との間に遅れていることを検出した場合には、前記第4のエッジ検出出力信号を生成して、

前記エッジ検出器の前記次回のエッジ検出位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−2位相分または前記+2位相分変更される

ことを特徴とする送受信半導体集積回路。

【請求項19】

請求項18において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答した前記エッジ検出位相から前記−2位相分または前記+2位相分の変更による状態遷移を1度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とする送受信半導体集積回路。

【請求項20】

請求項14において、

前記エッジ検出器は、前記複数のエッジ検出回路の複数の出力端子に接続された複数の積分器を更に含み、

前記複数の積分器の各積分器は、前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路の第1エッジ検出結果と前記第2のエッジ検出回路の第2エッジ検出結果の平均化処理を実行する

ことを特徴とする送受信半導体集積回路。

【請求項1】

サンプリング回路とエッジ検出器と位相選択信号生成回路とクロックデータ生成回路とを具備するクロックデータリカバリ回路であって、

前記サンプリング回路は受信データ信号を多相クロック信号によってサンプリングすることによって、複数のサンプリング信号を生成して、

前記エッジ検出器は、前記複数のサンプリング信号と前記多相クロック信号に応答して、複数のエッジ検出信号を生成して、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数の位相選択信号を生成して、

前記クロックデータ生成回路は、前記複数のサンプリング信号と前記複数の位相選択信号と前記多相クロック信号とに応答して、再生クロックと再生データとを生成して、

前記エッジ検出器は複数のエッジ検出回路を含み、前記エッジ検出器の前記複数のエッジ検出回路は前記複数のサンプリング信号と前記多相クロック信号とに応答して、前記複数のエッジ検出信号を生成して、

前記複数のエッジ検出回路の各エッジ検出回路は、第1のエッジ検出回路と第2のエッジ検出回路とを含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の−1位相よりも進んでいることを検出した場合には、第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の+1位相よりも遅れていることを検出した場合には、第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第1のエッジ検出回路と前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の±1位相の範囲に存在することを検出可能とされ、

前記第1のエッジ検出回路と前記第2のエッジ検出回路が現在供給されている前記受信データ信号の前記データエッジが前記±1位相の範囲に存在することを検出した場合には、前記エッジ検出器の次回のエッジ検出位相は前記1個のエッジ検出クロック信号の前記エッジ検出位相に維持される

ことを特徴とするクロックデータリカバリ回路。

【請求項2】

請求項1において、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数のゲート制御信号を更に生成して、

前記位相選択信号生成回路から生成される前記複数のゲート制御信号は、前記エッジ検出器の前記複数のエッジ検出回路に供給され、

前記エッジ検出器から生成される前記複数のエッジ検出信号のうちの1個のエッジ検出信号は、前記多相クロック信号のうちの現在供給されている前記受信データ信号の前記データエッジに対応する1個のクロック信号を示すための所定の電圧レベルに設定され、

前記所定の電圧レベルに設定された前記1個のエッジ検出信号に応答して、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの1個のゲート制御信号は、所定の信号レベルに設定され、

前記エッジ検出器の前記複数のエッジ検出回路のうちの前記所定の信号レベルに設定される前記1個のゲート制御信号が供給される1個のエッジ検出回路は活性状態に制御され、前記エッジ検出器の前記複数のエッジ検出回路のそれ以外のエッジ検出回路は非活性状態に制御される

ことを特徴とするクロックデータリカバリ回路。

【請求項3】

請求項2において、

前記位相選択信号生成回路は、前記複数の位相選択信号と前記複数のゲート制御信号を生成する複数の位相選択信号生成回路を含み、

前記複数の位相選択信号生成回路の各位相選択信号生成回路から生成される1個の位相選択信号と1個のゲート制御信号とは、実質的に0.5ユニットインターバルの位相差を有する

ことを特徴とするクロックデータリカバリ回路。

【請求項4】

請求項3において、

前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路と前記第2のエッジ検出回路は、第1排他的論理和回路と第2排他的論理和回路をそれぞれ含み、

前記第1のエッジ検出回路の前記第1排他的論理和回路には第1入力信号と第1参照信号とが供給され、前記第2のエッジ検出回路の前記第2排他的論理和回路には第2入力信号と第2参照信号とが供給され、

前記第1排他的論理和回路に供給される前記第1入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−1位相分進んだ1位相進相クロック信号によって前記受信データ信号をサンプリングして形成された1位相進相サンプリング信号であり、

前記第1排他的論理和回路に供給される前記第1参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−2位相分またはそれ以上進んだ複数位相進相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相進相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+1位相分遅れた1位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された1位相遅相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+2位相分またはそれ以上進んだ複数位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相遅相サンプリング信号であり、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第1排他的論理和回路の所定レベルの出力信号に応答して、前記第1のエッジ検出出力信号を生成して、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第2排他的論理和回路の所定レベルの出力信号に応答して、前記第2のエッジ検出出力信号を生成する

ことを特徴とするクロックデータリカバリ回路。

【請求項5】

請求項3において、

電源電圧投入時もしくはスタンバイ解除時の初期化動作では、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの任意の1個のゲート制御信号は、前記所定の信号レベルに設定され、

前記初期化動作では、更に前記位相選択信号生成回路から生成される前記複数の位相選択信号のうちの前記任意の1個のゲート制御信号と実質的に0.5ユニットインターバルの位相差を有する1個の位相選択信号が、前記所定の信号レベルに設定される

ことを特徴とするクロックデータリカバリ回路。

【請求項6】

請求項3において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答した前記エッジ検出位相から前記−1位相分または前記+1位相分の変更による状態遷移を少なくとも2度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とするクロックデータリカバリ回路。

【請求項7】

請求項3において、

前記複数のエッジ検出回路の前記各エッジ検出回路は、第3のエッジ検出回路と第4のエッジ検出回路とを更に含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−1位相から−2位相との間に進んでいることを検出した場合には、前記第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+1位相から+2相との間に遅れていることを検出した場合には、前記第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第3のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−2位相から−3位相との間に進んでいることを検出した場合には、前記第3のエッジ検出出力信号を生成して、

前記第4のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+2位相から+3相との間に遅れていることを検出した場合には、前記第4のエッジ検出出力信号を生成して、

前記エッジ検出器の前記次回のエッジ検出位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−2位相分または前記+2位相分変更される

ことを特徴とするクロックデータリカバリ回路。

【請求項8】

請求項7において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答した前記エッジ検出位相から前記−2位相分または前記+2位相分の変更による状態遷移を1度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とするクロックデータリカバリ回路。

【請求項9】

請求項3において、

前記エッジ検出器は、前記複数のエッジ検出回路の複数の出力端子に接続された複数の積分器を更に含み、

前記複数の積分器の各積分器は、前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路の第1エッジ検出結果と前記第2のエッジ検出回路の第2エッジ検出結果の平均化処理を実行する

ことを特徴とするクロックデータリカバリ回路。

【請求項10】

請求項3において、

前記クロックデータリカバリ回路は、前記クロックデータリカバリ回路の外部から供給される外部クロック信号に応答して前記多相クロックを生成する多相クロック生成回路を更に具備して、

前記クロックデータリカバリ回路の内部で、前記多相クロック生成回路から生成される前記多相クロックが、前記サンプリング回路と前記エッジ検出器と前記位相選択信号生成回路と前記クロックデータ生成回路とに供給される

ことを特徴とするクロックデータリカバリ回路。

【請求項11】

請求項3において、

前記多相クロックを生成する前記多相クロック生成回路は、位相比較器とチャージポンプとループフィルタと電圧制御遅延線路を含むディレイド・ロックド・ループによって構成された

ことを特徴とするクロックデータリカバリ回路。

【請求項12】

クロックデータリカバリ回路と、デシリアライザと、シリアライザと、PLL回路とを含むインターフェースユニットを有する送受信半導体集積回路であって、

パラレル・シリアル変換器としての前記シリアライザは、パラレル送信信号と前記PLL回路から生成されるPLLクロックとからシリアル送信信号を生成するものであり、

前記クロックデータリカバリ回路は、受信データ信号と前記PLL回路から生成される前記PLLクロックとに応答して、再生クロックと再生データとを生成するものであり、

シリアル・パラレル変換器としての前記デシリアライザは、前記クロックデータリカバリ回路から生成される前記再生クロックと前記再生データとからパラレル受信データを生成するものであり、

前記クロックデータリカバリ回路は、サンプリング回路とエッジ検出器と位相選択信号生成回路とクロックデータ生成回路とを具備して、

前記サンプリング回路は受信データ信号を多相クロック信号によってサンプリングすることによって、複数のサンプリング信号を生成して、

前記エッジ検出器は、前記複数のサンプリング信号と前記多相クロック信号に応答して、複数のエッジ検出信号を生成して、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数の位相選択信号を生成して、

前記クロックデータ生成回路は、前記複数のサンプリング信号と前記複数の位相選択信号と前記多相クロック信号とに応答して、再生クロックと再生データとを生成して、

前記エッジ検出器は複数のエッジ検出回路を含み、前記エッジ検出器の前記複数のエッジ検出回路は前記複数のサンプリング信号と前記多相クロック信号とに応答して、前記複数のエッジ検出信号を生成して、

前記複数のエッジ検出回路の各エッジ検出回路は、第1のエッジ検出回路と第2のエッジ検出回路とを含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の−1位相よりも進んでいることを検出した場合には、第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の+1位相よりも遅れていることを検出した場合には、第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第1のエッジ検出回路と前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の±1位相の範囲に存在することを検出可能とされ、

前記第1のエッジ検出回路と前記第2のエッジ検出回路が現在供給されている前記受信データ信号の前記データエッジが前記±1位相の範囲に存在することを検出した場合には、前記エッジ検出器の次回のエッジ検出位相は前記1個のエッジ検出クロック信号の前記エッジ検出位相に維持される

ことを特徴とする送受信半導体集積回路。

【請求項13】

請求項12において、

前記位相選択信号生成回路は、前記複数のエッジ検出信号と前記多相クロック信号に応答して、複数のゲート制御信号を更に生成して、

前記位相選択信号生成回路から生成される前記複数のゲート制御信号は、前記エッジ検出器の前記複数のエッジ検出回路に供給され、

前記エッジ検出器から生成される前記複数のエッジ検出信号のうちの1個のエッジ検出信号は、前記多相クロック信号のうちの現在供給されている前記受信データ信号の前記データエッジに対応する1個のクロック信号を示すための所定の電圧レベルに設定され、

前記所定の電圧レベルに設定された前記1個のエッジ検出信号に応答して、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの1個のゲート制御信号は、所定の信号レベルに設定され、

前記エッジ検出器の前記複数のエッジ検出回路のうちの前記所定の信号レベルに設定される前記1個のゲート制御信号が供給される1個のエッジ検出回路は活性状態に制御され、前記エッジ検出器の前記複数のエッジ検出回路のそれ以外のエッジ検出回路は非活性状態に制御される

ことを特徴とする送受信半導体集積回路。

【請求項14】

請求項13において、

前記位相選択信号生成回路は、前記複数の位相選択信号と前記複数のゲート制御信号を生成する複数の位相選択信号生成回路を含み、

前記複数の位相選択信号生成回路の各位相選択信号生成回路から生成される1個の位相選択信号と1個のゲート制御信号とは、実質的に0.5ユニットインターバルの位相差を有する

ことを特徴とする送受信半導体集積回路。

【請求項15】

請求項14において、

前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路と前記第2のエッジ検出回路は、第1排他的論理和回路と第2排他的論理和回路をそれぞれ含み、

前記第1のエッジ検出回路の前記第1排他的論理和回路には第1入力信号と第1参照信号とが供給され、前記第2のエッジ検出回路の前記第2排他的論理和回路には第2入力信号と第2参照信号とが供給され、

前記第1排他的論理和回路に供給される前記第1入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−1位相分進んだ1位相進相クロック信号によって前記受信データ信号をサンプリングして形成された1位相進相サンプリング信号であり、

前記第1排他的論理和回路に供給される前記第1参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の−2位相分またはそれ以上進んだ複数位相進相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相進相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2入力信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+1位相分遅れた1位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された1位相遅相サンプリング信号であり、

前記第2排他的論理和回路に供給される前記第2参照信号は、前記各エッジ検出回路の前記データエッジ検出位相に対応する前記1個のエッジ検出クロック信号と比較して前記多相クロック信号の+2位相分またはそれ以上進んだ複数位相遅相クロック信号によって前記受信データ信号をサンプリングして形成された複数位相遅相サンプリング信号であり、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第1排他的論理和回路の所定レベルの出力信号に応答して、前記第1のエッジ検出出力信号を生成して、

前記複数のエッジ検出回路の前記各エッジ検出回路は、前記第2排他的論理和回路の所定レベルの出力信号に応答して、前記第2のエッジ検出出力信号を生成する

ことを特徴とする送受信半導体集積回路。

【請求項16】

請求項14において、

電源電圧投入時もしくはスタンバイ解除時の初期化動作では、前記位相選択信号生成回路から生成される前記複数のゲート制御信号のうちの任意の1個のゲート制御信号は、前記所定の信号レベルに設定され、

前記初期化動作では、更に前記位相選択信号生成回路から生成される前記複数の位相選択信号のうちの前記任意の1個のゲート制御信号と実質的に0.5ユニットインターバルの位相差を有する1個の位相選択信号が、前記所定の信号レベルに設定される

ことを特徴とする送受信半導体集積回路。

【請求項17】

請求項14において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答した前記エッジ検出位相から前記−1位相分または前記+1位相分の変更による状態遷移を少なくとも2度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とする送受信半導体集積回路。

【請求項18】

請求項14において、

前記複数のエッジ検出回路の前記各エッジ検出回路は、第3のエッジ検出回路と第4のエッジ検出回路とを更に含み、

前記第1のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−1位相から−2位相との間に進んでいることを検出した場合には、前記第1のエッジ検出出力信号を生成して、

前記第2のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+1位相から+2相との間に遅れていることを検出した場合には、前記第2のエッジ検出出力信号を生成して、

前記エッジ検出器の次回のエッジ検出位相は、前記第1のエッジ検出出力信号または前記第2のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−1位相分または前記+1位相分変更され、

前記第3のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記−2位相から−3位相との間に進んでいることを検出した場合には、前記第3のエッジ検出出力信号を生成して、

前記第4のエッジ検出回路は、現在供給されている前記受信データ信号のデータエッジが、前記多相クロック信号のうちの前記各エッジ検出回路のデータエッジ検出位相に対応する1個のエッジ検出クロック信号のエッジ検出位相から前記多相クロック信号の前記+2位相から+3相との間に遅れていることを検出した場合には、前記第4のエッジ検出出力信号を生成して、

前記エッジ検出器の前記次回のエッジ検出位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答して、前記1個のエッジ検出クロック信号の前記エッジ検出位相から前記−2位相分または前記+2位相分変更される

ことを特徴とする送受信半導体集積回路。

【請求項19】

請求項18において、

前記現在供給されている前記受信データ信号の前記データエッジと比較して次に供給されている受信データ信号のデータエッジが前記多相クロック信号の少なくとも2位相分遷移する場合には、下記追従動作が実行され、

前記追従動作によって、前記エッジ検出器の前記次回のエッジ検出位相と前記クロックデータ生成回路から生成される前記再生クロックの位相は、前記第3のエッジ検出出力信号または前記第4のエッジ検出出力信号に応答した前記エッジ検出位相から前記−2位相分または前記+2位相分の変更による状態遷移を1度実行して、前記受信データ信号の前記データエッジの変化に追従する

ことを特徴とする送受信半導体集積回路。

【請求項20】

請求項14において、

前記エッジ検出器は、前記複数のエッジ検出回路の複数の出力端子に接続された複数の積分器を更に含み、

前記複数の積分器の各積分器は、前記複数のエッジ検出回路の前記各エッジ検出回路の前記第1のエッジ検出回路の第1エッジ検出結果と前記第2のエッジ検出回路の第2エッジ検出結果の平均化処理を実行する

ことを特徴とする送受信半導体集積回路。

【図1】

【図2】

【図3】

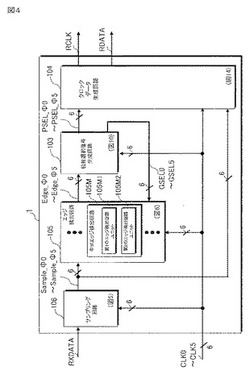

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【公開番号】特開2013−102372(P2013−102372A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−245387(P2011−245387)

【出願日】平成23年11月9日(2011.11.9)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月9日(2011.11.9)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]