クロックト待機モードに応答した集積回路の内部電圧の維持

【課題】メモリデバイス上に配置された基準電圧発生器によって生成された出力基準電圧を制御するための方法および装置。

【解決手段】メモリデバイスのクロックト待機モードを有効にするための信号が受信される。この信号が、上記メモリデバイスがクロックト待機モードにあることを示した場合は、第1の電圧を用いて、上記基準電圧発生器の出力基準電圧として第1の基準電圧が生成される。上記信号が、上記メモリデバイスがクロックト待機モードにないことを示した場合は、第2の電圧を用いて、上記基準電圧発生器の出力基準電圧として第2の基準電圧が生成される。

【解決手段】メモリデバイスのクロックト待機モードを有効にするための信号が受信される。この信号が、上記メモリデバイスがクロックト待機モードにあることを示した場合は、第1の電圧を用いて、上記基準電圧発生器の出力基準電圧として第1の基準電圧が生成される。上記信号が、上記メモリデバイスがクロックト待機モードにないことを示した場合は、第2の電圧を用いて、上記基準電圧発生器の出力基準電圧として第2の基準電圧が生成される。

【発明の詳細な説明】

【発明の詳細な説明】

【0001】

〔発明の背景〕

〔発明の分野〕

本発明の実施形態は、一般的には、デジタル回路におけるクロックト待機モードの改良された形態に関する。

【0002】

〔従来技術の説明〕

集積回路(integrated circuit; IC)デバイスは、変動する外部電圧供給に対する感度を低減するために、内部で生成された様々な電圧を用いて動作することが多い。内部で生成された各電圧は、ICによって必要とされる種々の機能を実行するためにも用いられる。必要な各内部電圧を生成するために、電圧発生回路と称される回路が用いられることがある。ダイナミックランダムアクセスメモリ(dynamic random access memory; DRAM)などの典型的なメモリデバイスは、上記のような電圧発生回路を多数有していることがある。これらの電圧発生回路は、グランド基準に対して正の電圧(例えばブーストされたワード線電圧、すなわちVPP)、およびグランド基準に対して負の電圧(例えばバックバイアス電圧、すなわちVBB、または負のワード線電圧、すなわちVNWL)を含む様々な電圧を生成するように構成されている。

【0003】

所定の装置に設けられた各電圧発生回路は、電圧を生成する間に電力を消費する。ICデバイスによって消費される電力を節約するために、電圧発生回路は、選択的に有効および無効にされるモード(待機モードと称される)に置かれることがある。待機モードでは、ICデバイスが必要な電圧を使用している間は、電圧発生回路が有効にされる。例えばICデバイスがメモリデバイスである場合は、このメモリデバイスが(例えば読み出し、書き込み、またはリフレッシュ)アクセスを行うために電圧発生回路の出力を使用する直前において、電圧発生回路が有効にされる。電圧発生回路は、必要な電圧を生成するために有効にされている間には、電力を消費する。メモリデバイスがアクセスされていないときは、電圧が不要であるため電圧発生回路は無効にされ、これによって節電される。メモリデバイスへの各アクセスは、クロックのタイミングに合わせられているため(例えばリフレッシュ動作は、セルフリフレッシュタイマーによって誘発される)、各アクセスが行われる直前に電圧発生回路を選択的に有効または無効にするために、クロック信号が用いられる。従って待機モードは、クロックト待機モード(clocked standby mode; CSM)と称される。

【0004】

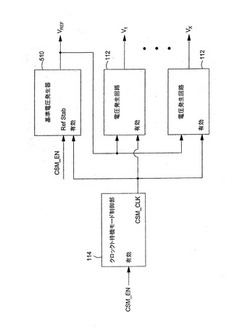

図1は、クロックト待機モードを利用した典型的なメモリデバイス100を示すブロック図である。メモリデバイス100は、その1つ以上のメモリアレイ104へアクセスするために用いられる制御回路102を有している。制御回路102は、メモリデバイスを構成および制御するために用いられる複数の内部回路を有している。例えば、制御回路102は、メモリデバイス100の温度を測定するために用いられる温度センサ108を有している。メモリデバイス100の動作特性(例えばセルフリフレッシュ周期)は、測定された温度に基づいて調節される。

【0005】

メモリデバイス100は、基準電圧発生器110および電圧発生回路112を有している。基準電圧発生器110は、出力基準電圧VREFを生成する。出力基準電圧VREFは、電圧発生回路112が出力電圧VOUT(s)、V1、V2、・・・VXを生成するために用いられる。出力電圧V1、V2、・・・VXおよび基準電圧VREFは、メモリデバイス100の制御回路102およびメモリアレイ104に供給される。上記基準電圧は、制御回路102がメモリアレイ104へ(例えば読み出し、書き込み、またはリフレッシュ)アクセスするために用いられる。基準電圧発生器110および電圧発生回路112は、クロックト待機モード制御部114によって選択的に有効および無効にされる。場合によっては、クロックト待機モード制御部114は、制御回路102によって有効または無効にされる。別の場合では、クロックト待機モード制御部114は、イネーブル信号(enabling signal)を用いずに恒久的に有効にされるか、あるいは、レーザヒューズまたは電子的にプログラム可能なヒューズ(電子ヒューズ)など、メモリデバイス100のヒューズを溶断することによって恒久的に有効にされる。

【0006】

図2は、1つ以上の電圧発生回路112および基準電圧発生器110を選択的に有効にするために用いられる、典型的なクロックト待機モード制御部114を示すブロック図である。クロックト待機モード制御部114への入力は、上記クロックト待機モードを有効にするための信号(CSM_ENと称される)である。CSM_ENがHighの論理値であるときは、上記クロックト待機モードが有効にされ、そしてクロックト待機モード制御部114によって、クロックト待機モードクロック信号(CSM_CLK)が生成される。場合によっては、クロックト待機モード制御部114は、クロックト待機モードクロック信号を生成するために、ベースクロック信号(Base_CLK)と称される別のクロック信号を用いる。クロックト待機モードクロック信号CSM_CLKは、電圧発生回路112および基準電圧発生器110を選択的に有効および無効にするために用いられる。CSM_ENが一定の値(例えばLowの論理値)である場合は、クロックト待機モードは無効にされる。これは、電圧発生回路112および基準電圧発生器110が、常に出力電圧および基準電圧を生成していることを意味している。クロックト待機モードが無効にされたときは、CSM_CLK信号は、電圧発生回路112および基準電圧発生器110を常に有効にするために、一定の値(例えばLowの論理値)に設定される。

【0007】

場合によっては、基準電圧発生器110および電圧発生回路112を有効および無効にすることによって、基準電圧発生器110の出力基準電圧VREF、および電圧発生回路112の出力電圧V1、V2、・・・VXが変動する。例えば、場合によっては、基準電圧発生器110を有効および無効にすることによって、出力基準電圧VREFに電荷が蓄積する。VREFにおける(正または負の)変動によって、電圧発生回路112の出力電圧V1、V2、・・・VXに変化が生じる。別の場合では、たとえVREFが安定を保っていたとしても、電圧発生回路を有効および無効にすることによって、VREFの変化とは関係なく、電圧発生回路112の出力電圧V1、V2、・・・VXに直接変動が生じる。VREF、およびメモリデバイス100の電圧発生回路112の出力電圧V1、V2、・・・VXの変化によって、メモリデバイス100が機能不全を起こす可能性がある。例えば、メモリデバイス100のメモリアレイ104をリフレッシュするために、1つ以上の電圧VREFまたはV1、V2、・・・VXが制御回路102によって用いられる場合は、電圧の変化によってメモリアレイ104が十分にリフレッシュされず、結果としてメモリが失われる。

【0008】

従って、クロックト待機モードによって影響を受ける電圧を調整するための改良された方法および装置が必要とされている。

【0009】

〔本発明の概要〕

本発明の実施形態は、一般的には、メモリデバイス上に配置された基準電圧発生器によって生成された出力基準電圧を制御するための方法および装置を示している。一実施形態では、メモリデバイスのクロックト待機モードを可能にするための信号が受信される。この信号によって、メモリデバイスがクロックト待機モードにあることが示された場合は、上記基準電圧発生器の出力基準電圧として、第1の電圧を用いて第1の基準電圧が生成される。上記信号によって、メモリデバイスがクロックト待機モードにないことが示された場合は、上記基準電圧発生器の出力基準電圧として、第2の電圧を用いて第2の基準電圧が生成される。

【0010】

本発明の別の実施形態では、電圧発生器を含むデバイスのクロックト待機モードを有効にするための制御信号が受信される。この制御信号によって、クロックト待機モードが無効であることを示された場合は、上記電圧発生器によって生成される出力電圧が、上記電圧発生器に供給される入力電圧を用いて生成される。上記制御信号によって、クロックト待機モードが有効であることを示された場合は、上記電圧発生器に供給される入力電圧が変更され、変更された電圧は、上記電圧発生器の出力電圧を生成するために用いられる。

【0011】

本発明の別の実施形態は、基準電圧を生成するための手段、およびクロックト待機モードを制御するための手段を有したメモリデバイスを示している。基準電圧を生成するための上記手段は、メモリデバイスのクロックト待機モードを有効にするための制御信号を受信するように構成されている。上記制御信号によって、メモリデバイスのクロックト待機モードが有効であることを示された場合は、基準電圧を生成するための上記手段は、上記電圧発生器の出力電圧として、第1の入力電圧を用いて第1の基準電圧を生成する。上記制御信号によって、メモリデバイスのクロックト待機モードが無効であることを示された場合は、基準電圧を生成するための上記手段は、電圧発生器の出力電圧として、第2の入力電圧を用いて第2の基準電圧を生成する。クロックト待機モードを制御するための上記手段は、メモリデバイスのクロックト待機モードが有効であるときに、基準電圧を生成するための上記手段を選択的に有効および無効にするように構成されている。

【0012】

本発明のさらに別の実施形態は、電源、基準電圧出力線、第1の回路、および少なくとも1つの抵抗を有した回路を示している。上記第1の回路は、上記電源によって供給された供給電圧を用いて、上記基準電圧出力線へ基準電圧を生成するように構成されている。上記少なくとも1つの抵抗は、上記電源と基準電圧出力線との間に挟まれている。また、上記抵抗は、クロックト待機モードを有効および無効にするための信号によって有効および無効にされる。上記少なくとも1つの抵抗を有効および無効にすることによって、上記基準電圧出力線上の基準電圧が上昇または低下する。

【0013】

〔図面の簡単な説明〕

上述した本発明の特徴が詳しく理解されるように、添付図面に示されている実施形態を参照しながら、前項において概説した本発明をより具体的に説明する。しかし添付図面は、本発明の典型的な実施形態を示すものであって、本発明の範囲を限定するものと考えられることはなく、本発明は同様に効果的な別の実施形態も許容することについて留意されたい。

【0014】

図1は、クロックト待機モードを利用した典型的なメモリデバイスを示すブロック図である。

【0015】

図2は、1つ以上の電圧発生回路を選択的に有効にするために用いられる、典型的なクロックト待機モード制御を示すブロック図である。

【0016】

図3は、典型的な電圧発生回路を示す回路図である。

【0017】

図4は、電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【0018】

図5は、本発明の一実施形態に従って、基準電圧の電圧シフトを補償するために、クロックト待機モードを有効および無効にするための信号(CSM_EN)を用いる、他の基準電圧発生器を示すブロック図である。

【0019】

図6は、本発明の一実施形態に従った、他の基準電圧発生器を示す回路図である。

【0020】

図7は、本発明の一実施形態に従って、選択的に有効にされた補償抵抗を基準電圧発生器へ挿入した場合の影響を示すタイミング図である。

【0021】

図8は、電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【0022】

図9は、本発明の一実施形態に従って、クロックト待機モード中に上昇する基準電圧VREFを生成するために用いられる、他の基準電圧発生回路を示す図である。

【0023】

図10は、本発明の一実施形態に従って、クロックト待機モードが有効にされたときにおける、上昇した基準電圧VREFの出力電圧VOUTに対する影響を示すタイミング図である。

【0024】

〔好ましい実施形態の詳細な説明〕

本発明の実施形態は、一般的には、メモリデバイス上に配置された基準電圧発生器によって生成された出力基準電圧を制御するための方法および装置を示している。一実施形態では、メモリデバイスのクロックト待機モードを可能にするための信号が受信される。この信号によって、メモリデバイスがクロックト待機モードにあることが示された場合は、上記基準電圧発生器の出力基準電圧として、第1の基準電圧が第1の電圧を用いて生成される。上記信号によって、メモリデバイスがクロックト待機モードにないことが示された場合は、上記基準電圧発生器の出力基準電圧として、第2の基準電圧が第2の電圧を用いて生成される。

【0025】

本明細書に記載の回路は、内部で生成された電圧および基準電圧を利用した任意数のデバイスに利点をもたらすように使用することができる。以下の説明は、分かりやすくするために、ダイナミックランダムアクセスメモリ(DRAM)デバイスなどの具体的なメモリデバイスに当てはめているが、これは本明細書に記載の回路を使用したデバイスの実施例を限定するものではない。さらに以下の説明は、Highの論理信号へとアサートされた、あるいはLowの論理信号へと引き下げられた特定の制御信号を参照しているが、これらの信号レベルは単なる典型例であって、本明細書に記載の回路は、任意の極性および/または電圧レベルを有する任意数の信号を用いるように構成できることは当業者であれば理解できるであろう。また、一部の信号は、所定の制御回路またはデバイスから生じたものとして記載されているが、記載されているあらゆる制御信号は、任意の回路またはデバイスから生じることについて理解されたい。同様に、本明細書に記載されている全ての信号名は典型例であって、本発明の実施形態は一般的に、任意の名を有する任意の信号、および/または、このような信号の1つ以上から生じた任意の信号を用いて実施することができる。

【0026】

同様に、記載されているクロックト待機モード制御部、制御回路、電圧発生器、基準電圧発生器、電圧調整器などの特定の回路の形態は、単なる典型例にすぎない。場合によっては、本発明の実施形態の形態をよりよく説明するために、上記のような回路を簡素化した形態が示されている。しかし本発明の実施形態は、このような回路の複雑かつ/または商業的な形態を含む、任意の形態または構成を用いるように適応できることは、当業者であれば理解できるであろう。

【0027】

〔メモリデバイスに対する電圧の生成〕

次に、本発明の実施形態をよりよく理解するために、基準電圧および電圧発生回路112の出力電圧を生成するための典型的な方法および回路について説明する。図3は、典型的な基準電圧発生回路110、および典型的な電圧発生回路112を示す回路図である。これらの回路は、クロックト待機モード信号(CSM_CLK)によって選択的に有効および無効にされる。

【0028】

基準電圧発生器110および電圧発生回路112が有効であるとき(例えば、CSM_CLK信号がLowの論理値であるとき)は、スイッチS1 302、S2 308、およびS3 318は閉じていて、スイッチS4 312は閉じている。これによって電圧発生回路112に電流が流れ、そして基準電圧VREFから出力電圧VOUTが生成される。これについては後述する。

【0029】

本発明の一実施形態として、基準電圧VREFは、2つの抵抗R1 304およびR2 306を有する分圧器によって生成されるようになっていてもよい。上記抵抗R1 304およびR2 306は、スイッチを介して、高電圧(VREG)および低電圧(VGND)に接続されている。上記分圧器、あるいはその他の抵抗、トランジスタ、またはこれ以外のIC素子のグループは、抵抗ネットワーク310とも称される。CSM_CLK信号が電圧発生器112を有効にすると、スイッチS1 302およびS2 308が閉じ、そして抵抗R1 304およびR2 306を流れる電流によって基準電圧が生成される。生成された基準電圧は、以下の方程式によって表される:

VREF=(VREG−VGND)・R2/(R1+R2)

R1 304およびR2 306の値を変えることによって、所望の基準電圧VREFが生成される。

【0030】

抵抗ネットワーク310によって出力された基準電圧は、(電圧調整器とも称される)電圧発生回路112へ入力される。電圧調整器は、入力電圧(VREF)に対して出力電圧(VOUT)を一定の値に保持する電子回路である。電圧発生回路112が有効にされると、VOUTをVREFと比較するためにオペアンプ(op-amp)322が用いられる。オペアンプ322の出力は、電源電圧VREGを用いて電圧VOUTを制御するPMOSトランジスタ314への入力である。PMOSトランジスタ314がオンであるとき(オペアンプ322によって低い電圧が印加されたとき)は、PMOSトランジスタ314に電流が流れ、これによってVOUTが上昇する。PMOSトランジスタ314がオフであるとき(オペアンプ322によって高い電圧が印加されたとき)は、PMOSトランジスタ314に電流は流れない。これによってVOUTが、ロード(load)に接続されている場合は低下する。このように、オペアンプ322の出力電圧のわずかな上昇または低下に対応して、VOUTがわずかに低下または上昇する。

【0031】

調整回路112が有効とされたときに、(例えば、VOUTを使用する回路による電力消費が高いために)VOUTがVREFよりわずかに小さい場合は、PMOSトランジスタ314へ印加される出力電圧がオペアンプ322によって低下する。PMOSトランジスタ314への出力電圧が低下すると、PMOSトランジスタ314によってVOUTへ供給される電流がわずかに上昇する。これによってVOUTが上昇してVREFの値に近づく。同様に、(例えば、VOUTを使用する回路による電力消費が低いために)VOUTがVREFよりわずかに大きい場合であれば、PMOSトランジスタ314へ印加される出力電圧がオペアンプ322によって上昇する。PMOSトランジスタ314への出力電圧が上昇すると、PMOSトランジスタ314によってVOUTへ供給される電流がわずかに低下する。これによってVOUTが低下してVREFの値に近づく。このように電圧調整器は、VREGからVOUTへ供給される電源を上昇または低下させることによって、VREFに対してVOUTを一定の値に保持する。VREFに対するVOUTの電圧レベルを判別するために、抵抗R3 316と、抵抗R1およびR2との比率を用いることができる。

【0032】

CSM_CLKがLowの論理値からHighの論理値へ変化すると、電圧発生器112および基準電圧発生器110が無効にされる。電圧発生器が無効にされると、スイッチS1 302、S2 308、およびS3 318が開き、スイッチS4 312が閉じる。スイッチS1 302、S2 308、およびS3 318が開いているときは、電圧発生回路112および基準電圧発生器110が消費する電力は少ない。電圧発生回路112が無効とされたときには、VOUTは、スイッチS3 318およびS4 312によって、メモリデバイス100内の別の電圧から電子的に絶縁される。回路内の別の電圧から絶縁されているときの出力電圧は、フローティング出力電圧と称される。出力電圧線のキャパシタンスは、出力電圧を一定の値(例えば、電圧発生回路112が無効にされる直前の出力電圧)に保持する傾向がある。しかし場合によっては、フローティング出力電圧は一定の値にとどまらない。フローティング出力電圧は、例えばメモリデバイス100内の漏れ電流によって降下する。この「降下」効果については、図8に照らして以下に詳述する。

【0033】

〔クロックト待機モードに起因するVREFの変動〕

前述したように、基準電圧発生器110を有効および無効にすることによって、基準電圧発生器110の出力電圧VREFが変動する。基準電圧発生器110を有効および無効にすることによって、例えば基準電圧発生器110内への電荷の蓄積がもたらされ、そしてクロックト待機モードが有効とされたときには、基準電圧VREFにおける電圧シフト(DCシフトとも称される)が生じる。図4は、基準電圧発生器110の出力電圧VREFに対する、クロックト待機モードを有効および無効にする信号(CSM_EN)の影響を示すタイミング図である。時間T1では、信号CSM_ENはLowの論理値である。これは、クロックト待機モードが無効であることを示している。従って時間T1では、基準電圧VREFにオフセットはない。

【0034】

後のT2では、信号CSM_ENがHighの論理レベルへ引き上げられる。信号CSM_ENがHighの論理レベルへ引き上げられると、クロックト待機モードが有効になり、そしてクロックト待機モードクロック信号(CSM_CLK)を用いて、基準電圧発生器110が選択的に有効および無効にされる。図示されているように、クロックト待機モードを有効にすることによって、基準電圧発生器の出力電圧VREFに電圧シフトΔVが生じる。後の時間T3において、信号CSM_CLKがLowの論理レベルに引き下げられ、これによってクロックト待機モードが無効になる。基準電圧発生器110を無効状態から有効状態へ切り替える際に、(例えば回路内のキャパシタンスおよびインダクタンスを起因として)本質的にレイテンシが生じるため、基準電圧VREFのレベルが通常に戻るまでには、いくらかの時間(例えば時間T4まで)がかかる。従って時間T4では、基準電圧発生器110の出力電圧VREFには、電圧シフトΔVはもはや存在しない。

【0035】

図4は、クロックト待機モードに起因するVREFにおける正のオフセットを示している。しかし場合によっては、VREFにおける変化ΔVは負のオフセットであってよい。オフセットΔVの方向に関わらず、VREFにおける変化ΔVによって、電圧発生回路112の出力電圧VOUTに変化が生じ、また別の回路に悪影響が及ぼされる。

【0036】

図1を再び参照されたい。基準電圧VREFおよび/または電圧発生回路112の出力電圧VOUTを使用する制御回路102は、これら基準電圧および/または出力電圧が変化した場合は機能不全を起こす。例えば、制御回路102内の温度センサ108は、チップの温度が所定の範囲内であるか否かを判別するために基準電圧VREFを使用する。制御回路102は、測定された温度に基づいて、メモリデバイス100を制御するために用いられる所定の制御信号を設定する。温度センサ108は、基準電圧VREFの変化に対して感受性が非常に高い。基準電圧VREFにおけるシフトΔVのために、温度センサが正確な温度を測定できない場合は、制御回路102による制御信号の設定が不適切となる。これによってメモリデバイス100が機能不全を起こすか、あるいは必要なデバイス仕様を満たすことができなくなる可能性がある。

【0037】

本発明の一実施形態として、基準電圧発生器110は、クロックト待機モードが有効とされたときにVREFに生じる電圧シフトΔVを補償できるように変更されていてもよい。図5は、本発明の一実施形態に従って変更された基準電圧発生器を示すブロック図である。この基準電圧発生器は、基準電圧での電圧シフトを補償するために、クロックト待機モードを有効および無効にするための信号(CSM_EN)を用いる。

【0038】

図6は、本発明の一実施形態に従って変更された基準電圧発生器510を示す回路図である。図6に示されているように、図1〜図3に示されている基準電圧発生器110は、上部抵抗R4 608および下部抵抗R5 610を基準電圧発生器510へ挿入することによって変更できる。上部抵抗R4 608は、電圧発生器510内の高電源電圧(VREG)と、基準電圧VREFを生成するために用いられる抵抗ネットワーク310との間に挿入することができる。上部抵抗R4 608を挿入することによって、抵抗ネットワーク310への電圧入力がVREGからVHIGHへと低下する。同様に、下部抵抗R610は、基準電圧発生器510内の低電源電圧(VGND)と、電圧VREFを生成するために用いられる抵抗ネットワークとの間に挿入することができる。下部抵抗610を挿入することによって、抵抗ネットワーク310への電圧入力がVGNDからVLOWへと上昇する。

【0039】

本発明の一実施形態として、挿入された各抵抗608および610は、クロックト待機モードを有効および無効にするために用いられるクロックト待機モード制御信号CSM_ENを用いて選択的に有効および無効にされるようになっていてもよい。基準電圧発生器510は、上部および下部抵抗を適切に有効および無効にすることによって、クロックト待機モードに起因する電圧変化ΔVを補償する。

【0040】

前述したように、例えばクロックト待機モードが無効とされたときは、クロックト待機モード制御信号CSM_ENはLowの論理値である。CSM_EN信号がLowの論理値であるときは、上部抵抗608は無効であり、下部抵抗610は有効である。抵抗ネットワーク310が(図3に示されている)分圧器を有している場合は、R4 608は無効であり、R5 610は有効である。VREFの式は次の通りとなる:

VREF=(VREG−VGND)・(R2+R5)/(R5+R1+R2)

上記の式が示すように、抵抗R5 610が有効とされたときはVREFが高くなる。従って、R5 610、R1 304、およびR2 306に対して適切な値を選択することによって、クロックト待機モードが無効とされたときに用いられる所望のレベルまで出力基準電圧VREFを上げることができる。

【0041】

後に、CSM_ENがHighの論理値に引き上げられ、クロックト待機モードが有効とされたときは、上部抵抗608が有効になり、下部抵抗610が無効になる。これによってVREFが生成される方法が変わり、クロックト待機モードを有効にすることによって生じたVREFにおける変化ΔVが補償される。例えば抵抗ネットワーク310が分圧器を有している場合は、R4 608は有効であり、R5 610は無効である。VREFの式は次の通りとなる:

VREF=(VREG−VGND)・R2/(R4+R1+R2)

上記の式が示すように、抵抗R4が有効とされたときはVREFが低くなる。従って、R4 608、R1 304、およびR2 306に対して適切な値を選択することによって、クロックト待機モードが有効とされたときに用いられる低さのレベルに出力基準電圧VREFを設定することができる。従って、クロックト待機モードが有効とされたときに上部抵抗608を有効にし、下部抵抗610を無効にすることによって、基準電圧VREFが低い電圧にシフトされる。これによって、正の電圧シフトΔVが補償される。

【0042】

図7は、選択的に有効にされた補償抵抗608および610を基準電圧発生器510へ挿入した場合の影響を示すタイミング図である。前述同様に、時間T1では、信号CSM_ENはLowの論理値である。これは、クロックト待機モードが無効であることを示している。上部抵抗608は無効であり、下部抵抗610は有効である。一実施形態では、生成された基準電圧VREFは、抵抗R5 610、R1 304、およびR2 306によって判別される。従って時間T1では、基準電圧VREFにオフセットはない(例えばVREF=VTARGET)。

【0043】

後のT2において、(CSM_ENがHighの論理レベルであるときに)クロックト待機モードが有効にされ、そしてクロックト待機モードクロックCSM_CLKを用いて、基準電圧発生器510が選択的に有効および無効にされる。クロックト待機モードが有効とされたときは、上部抵抗608が有効にされ、下部抵抗610が無効にされる。これによって、VREFに補償効果(例えばVREFをLowにする効果)がもたらされる。従って、図7の時間T2に示されているように、VREFは、図4(すなわち、クロックト待機モードが無効とされたとき)と比べて、基準電圧発生器510が常に有効であるときとほぼ同じレベル(VTARGET)を維持する。後の時間T3において、CSM_ENはLowの論理レベルへ引き下げられ、これによってクロックト待機モードが無効になる。上部抵抗608が無効にされ、下部抵抗610が有効にされ、そしてVREFがほぼ同じレベルを維持する。

【0044】

抵抗を有効および無効にする際にレイテンシが本質的に生じるため、VREFにおいて期間のわずかなスパイク(spike)tsが生じる一方、抵抗608および610は有効または無効にされる。しかしVREFのスパイクは、程度が小さくかつ期間が限定されているため、メモリセルデバイス100の機能性に優位な影響を及ぼすことはない。また、スパイクの程度およびVREFにおける変化がわずかであるため、VREFは、例えばT4以前において、正確かつ安定した値(VTARGET)をより迅速に回復する。

【0045】

図4〜図7では、クロックト待機モードに起因するVREFにおけるオフセットΔVは正である。しかし場合によっては、前述したように、変化ΔVはVREFにおいて負であってもよい。ΔVが負である場合は、基準電圧発生器510は、前述した方法と同様の方法によってΔVを補償するように変更してもよい。例えば、上部抵抗608および下部抵抗610が有効および無効にされる順番を反対にして、クロックト待機モードが有効とされたときに上部抵抗608が無効になり、下部抵抗610が有効になるようにしてもよい。クロックト待機モードが有効であり、かつΔVが負であるときに、下部抵抗610を有効にし、そして上部抵抗608を有効にすることによって、VREFへの悪影響は、上昇補償電圧(upward compensating voltage)を生成することによって最小限にとどめることができる。

【0046】

より一般的には、各抵抗608および610は、当業者に知られている任意の方法を用いて選択的に有効にすることができる。例えば、ΔVが正である一実施形態では、上部抵抗608および下部抵抗610を選択的に有効および無効にするために、CSM_ENの補数である信号が用いられる。クロックト待機モードが無効であり、基準電圧が安定しているときを示す上記信号は、REF_STABLEと称される。この信号はまた、クロックト待機モードが無効とされたときはHighの値である。クロックト待機モードが有効であり、かつREF_STABLEがLowの論理値であるときは、上部抵抗608および下部抵抗610をそれぞれ有効および無効にし、VREFにおける上昇シフト(upward shift)ΔVを補償するために、上部抵抗608内のPMOSトランジスタ、および下部抵抗610内のNMOSトランジスタが用いられる。抵抗を選択的に有効および無効にするための別の方法は、当業者には容易に明らかとなるであろう。同様に、本発明の実施形態は、トランジスタおよび/またはオペアンプなどの能動素子を有するネットワークを含む、基準電圧VREFを生成するために用いられる別の抵抗ネットワーク310に有利になるように用いることができる。

【0047】

いずれの場合においても、メモリデバイス100がクロックト待機モードにあるか否かに関わらず、VREFは安定している。VREFが安定しているときは、制御回路102などの別の回路、および制御回路102内の温度センサ108は、クロックト待機モードが有効であるか否かに関わらず、VREFの値に依存する。

【0048】

〔クロックト待機モードに起因するVOUTの変動〕

前述したように、クロックト待機モードにある回路を有効および無効にすることによって、電圧発生回路112の出力電圧VOUTが、クロックト待機モードに起因して変動する。図8は、電圧発生回路112の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。時間T1では、CSM_EN信号はLowの論理値である。これは、クロックト待機モードが無効とされたことを示している。従って、クロックト待機モード制御114によって生成された信号CSM_CLKがLowの論理レベルに設定される。これによって基準電圧発生器110および電圧発生回路112が有効にされ、そしてVREFおよびVOUTが一定のレベルに維持される。

【0049】

後のT2において、CSM_EN信号はHighの論理レベルに引き上げられて、これによりクロックト待機モードが有効になる。CSM_EN信号が引き上げられると、クロックト待機モード制御114がCSM_CLK信号を生成する。このCSM_CLK信号は、基準電圧発生器110および電圧発生回路112を選択的に有効および無効にする。従って、CSM_EN信号が引き上げられると、クロックト待機モード制御114がCSM_CLK信号をHighの論理値へアサートし、これによって電圧発生回路112が無効になるため、図3に関連して説明したようにVOUTがフローティングとなる。

【0050】

メモリデバイス100がクロックト待機モードに置かれると、メモリデバイス100への各アクセスが行われる直前か、あるいはメモリデバイス100がVREFおよび/またはVOUTを用いるときにおいて、基準電圧発生器110および電圧発生回路112が選択的に有効にされる。従って後のT3では、CSM_CLK信号がLowの論理レベルへ引き下げられる。これによって電圧発生回路112が再び有効にされ、そして基準電圧発生器110および電圧発生回路112によって、それぞれVREFおよびVOUTが能動的に生成される。この結果、メモリデバイス100の負荷へのVOUTの出力によって、VOUTが臨界値を下回ることはない。

【0051】

基準電圧発生器110および電圧発生回路112が有効にされるたびに、CSM_CLK信号が、パルス幅時間TPWと称される設定時間においてLowとされる。時間TPWが経過した後において(時間T4)、CSM_CLK信号が再びアサートされる。これによって基準電圧発生器110および電圧発生回路112が再び無効にされる。CSM_CLKをアサートおよび引き下げるプロセスは、CSM_EN信号がアサートされている間は継続される。従って、CSM_CLKの周期およびCSM_CLKのパルス幅TPWは、基準電圧発生器110および電圧発生回路112がいつ、どれほどの時間無効にされるのかを決定する。

【0052】

電圧発生回路112が無効とされてVOUTがフローティングとなっている間は、VOUTは、電圧生成回路112が無効にされたことによる初期のフローティングの値そのものを維持するとは限らない。電圧発生回路112が無効にされるたびに、漏れ電流などの副次的効果によってVOUTが緩やかに劣化していく。このVOUTの劣化は、たとえ、図3に関連して説明したスイッチS1 302、S2 308、S3 318、およびS4 312を用いてVOUTが電気的に絶縁されていたとしても生じる。このVOUTの劣化は、図8においてVDROOPとして示されている。上記劣化は、基準電圧発生器110および電圧発生回路112が無効にされるたびに始まり、そしてBase_CLK信号の低下によりVOUTが引き上げられることによって基準電圧発生器110および電圧発生回路112が有効にされるまで続く。場合によっては、VDROOPは、プロセス、電圧、および温度(PVT)の変化によって異なる。電圧発生回路112が有効にされるたびに、電圧発生回路112がVOUTをVREFレベルまで引き戻すことによってVOUTを補正するのに、ある有限の時間がかかる。VDROOPの程度が大きいほど、電圧発生回路112がVOUTを修復する時間が長くなる。

【0053】

VOUTは、メモリデバイス100内の別の回路によって用いられるため、VOUT_MINと称される限界値を下回らないことが重要である。VOUTがVOUT_MINを下回った場合は、VOUTが十分に早く修復されず、またVOUTを用いるメモリデバイス100内の別の回路が正常に機能しなくなる。例えば、CSM_CLKの各周期中に基準電圧発生器110および電圧発生回路112が有効にされる時間TPWは、メモリデバイス100が正常に機能するために必要であるVOUTの標的レベル(VOUT_TARGETと称される)までVOUTを引き戻すには不十分である。従ってその後の周期T5〜T6では、VOUTは、VOUTの平均レベルが、メモリデバイス100が正常に機能するために必要な最低電圧VOUT_MINを超える値に維持されなくなる時間T7まで、VOUT_TARGETをさらに下回る。また場合によっては、降下VDROOPが大きくなりすぎてVOUTが完全に崩壊する。所望するVOUTの値と、電圧降下VDROOPの増加による実際のVOUTの値との差は、図8のタイミング図において、(VOUTを示す)破線と、(VOUT_TARGET付近に維持されたVOUTの所望の値を示す)実線との差によって図示されている。

【0054】

本発明の一実施形態として、VOUTを生成するために用いられる基準電圧VREFは、クロックト待機モードによって生じるVOUTの降下VDROOPの増大を補償するように変更されていてもよい。例えば、VREFは、クロックト待機モードが有効とされたとき(例えば、CSM_ENがHighの論理レベルであるとき)に高くなるように変更されていてもよい。クロックト待機モードが有効になってVREFが上昇すると、VOUTを生成するためにVREFを用いる電圧発生器112(図1に示されている)は、上昇したVREFの値に対応してVOUTをよりHighのレベルへ引き上げようとする。電圧発生器112がVOUTをよりHighのレベルへ引き上げようとすると、VOUTが上昇するレートがこれに対応して上昇し、VOUTの回復(recovery)が早くなる。従ってVREFが上昇すると、VOUTがより高い電圧レベルに維持される。これによってVOUTが、基準電圧発生器110および電圧発生回路112が有効にされる周期TPW中に、電圧降下VDROOPから完全に回復する。

【0055】

図9は、本発明の一実施形態に従って、クロックト待機モード中に上昇する基準電圧VREFを生成するために用いられる、他の基準電圧発生回路910を示す図である。図9に示されている基準電圧発生器910は、図3に示されている基準電圧発生回路110の改良版である。図3に示されている基準電圧発生回路110は、抵抗R2 306と、VREF信号のための基準電圧出力線との間に抵抗R6 912を挿入することによって改良されている。抵抗R6 912は、スイッチS5 914を用いて選択的に有効および無効にされる(短絡される)。

【0056】

本発明の一実施形態として、スイッチS5は、クロックト待機モードを有効および無効にするための信号CSM_ENによって制御されるようになっていてもよい。メモリデバイス100のクロックト待機モードが無効にされると、CSM_ENはLowの論理レベルになり、そしてスイッチS5 914は閉じられる。スイッチS5 914が閉じられると、抵抗R6 912の代わりにスイッチ914に分圧器内の電流が流れ、これによって抵抗R6 912が短絡、すなわち無効になる。抵抗R6 912が無効になると、基準電圧発生器910は、抵抗R1 304およびR2 306のみを用いて、基準電圧VREFを生成する。この基準電圧VREFは、図3に関連して記した方程式と同じ方程式によって表される:

VREF=(VREG−VGND)・R2/(R1+R2)

従って、クロックト待機モードが無効にされると、基準電圧VREFは、抵抗R1 304およびR2 306に対して選択された値に従った標準(初期)値となる。

【0057】

クロックト待機モードが有効にされ、CSM_ENがHighの論理レベルに引き上げられると、スイッチS5が開かれる。これによって、スイッチS5の代わりに抵抗R6 912に電流が流れて、抵抗R6が有効となる。抵抗R6 912が有効にされると、基準電圧発生器910は、抵抗R1 304、R2 306、およびR6 912を用いて基準電圧VREFを生成する。基準電圧発生器が抵抗R1 304、R2 306、およびR6 912を用いて生成した基準電圧VREFは、以下の方程式によって表される:

VREF=(VREG−VGND)・(R2+R6)/(R1+R2+R6)

R6 912に対して適切な値を選択することによって、VREFは、クロックト待機モードが有効にされたときに、所望する分だけ高くなる。

【0058】

図10は、本発明の一実施形態に従って、クロックト待機モードが有効にされたときにおける、上昇した基準電圧VREFの出力電圧VOUTに対する影響を示すタイミング図である。時間T1では、CSM_EN信号はLowの論理値であり、これはクロックト待機モードが無効であることを示している。従って、クロックト待機モード制御部114によって生成された信号CSM_CLKもまたLowの論理レベルに設定される。これによって、基準電圧発生器910および電圧発生回路112が有効にされ、そしてVREFおよびVOUTが一定の値に維持される。スイッチS 914は閉じているため、抵抗R6 912は、VREFを生成するために用いられる分圧器に対して影響を及ぼすことはない。従って、VREFは標準的な動作値に維持される。

【0059】

後のT2では、CSM_EN信号がHighの論理レベルに引き上げられ、クロックト待機モードが有効にされる。CSM_EN信号がHighの論理レベルに引き上げられて、クロックト待機モードが有効にされると、クロックト待機モード制御部114は、クロックト待機モードクロック信号CSM_CLKを生成する。CSM_CLKは、基準電圧発生器910および電圧発生回路112を選択的に有効および無効にする。CSM_ENによって制御されるスイッチS5 914は、CSM_ENがHighの論理値であるときに開かれる。これによって、分圧器内の電流が、スイッチS5 914の代わりに抵抗R6 912に流れる。従って基準電圧発生器910内の分圧器は、(基準電圧発生器910が有効にされたときに、)抵抗R6 912を用いて、基準電圧VREFに対して上昇した値(VREF_BOOSTEDと称される)を生成する。

【0060】

時間T3〜T4では、CSM_CLK信号が引き下げられる。CSM_CLK信号が引き下げられると、基準電圧発生器910および電圧発生回路112が有効にされる。クロックト待機モードが有効にされる(例えばCSM_ENがHighの論理値であり、かつスイッチS5 914が開いている)と、VREFが上昇する。このため、変更された出力電圧VOUT_NEW(暗線で示されている)は、標的電圧VOUT_TARGETまで完全に引き上げられ、従って未変更の電圧VOUT_OLD(破線で示されている)よりも高い電圧に維持される。従って、電圧発生器910および112が無効にされる各周期中(T3〜T4、T5〜T6、およびT7の初め)では、VOUT_NEWは、メモリデバイス100が正常に機能するために必要な最低閾値VOUT_MINを上回る値を維持する。言い換えると、フローティングとなった出力電圧VOUTが、漏れ電流のためにわずかに降下し続けている間に、VOUTを生成するために用いられる上昇したVREFの値が選択される。これによって、VOUTは、周期TPW中に基準電圧発生器110および電圧発生回路112が有効にされるたびに、電圧降下VDROOPから完全に回復する。従って、VOUT_NEWはVOUT_TARGET付近に維持されて、限界値VOUT_MINを下回らないようにされる。このようにして、VOUTを用いた回路は正常に機能する。

【0061】

本明細書に記載の実施形態は、クロックト待機モードによって影響を受ける1つ以上の電圧に関連して説明されている。しかし本発明の実施形態は、基準電圧発生器の基準電圧または出力電圧が、集積回路のいずれの動作特性によっても影響を受ける状況において実施可能であることも想定される。

【0062】

また、以上の説明は、本発明の実施形態に向けられたものであるが、本発明の基本的な範囲から逸脱することなく、本発明の別のさらなる実施形態を考案することができる。本発明の範囲は、特許請求の範囲によって規定される。

【図面の簡単な説明】

【0063】

【図1】クロックト待機モードを利用した典型的なメモリデバイスを示すブロック図である。

【図2】1つ以上の電圧発生回路を選択的に有効にするために用いられる、典型的なクロックト待機モード制御を示すブロック図である。

【図3】典型的な電圧発生回路を示す回路図である。

【図4】電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【図5】本発明の一実施形態に従って、基準電圧の電圧シフトを補償するために、クロックト待機モードを有効および無効にするための信号(CSM_EN)を用いる、他の基準電圧発生器を示すブロック図である。

【図6】本発明の一実施形態に従った、他の基準電圧発生器を示す回路図である。

【図7】本発明の一実施形態に従って、選択的に有効にされた補償抵抗を基準電圧発生器へ挿入した場合の影響を示すタイミング図である。

【図8】電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【図9】本発明の一実施形態に従って、クロックト待機モード中に上昇する基準電圧VREFを生成するために用いられる、他の基準電圧発生回路を示す図である。

【図10】本発明の一実施形態に従って、クロックト待機モードが有効にされたときにおける、上昇した基準電圧VREFの出力電圧VOUTに対する影響を示すタイミング図である。

【発明の詳細な説明】

【0001】

〔発明の背景〕

〔発明の分野〕

本発明の実施形態は、一般的には、デジタル回路におけるクロックト待機モードの改良された形態に関する。

【0002】

〔従来技術の説明〕

集積回路(integrated circuit; IC)デバイスは、変動する外部電圧供給に対する感度を低減するために、内部で生成された様々な電圧を用いて動作することが多い。内部で生成された各電圧は、ICによって必要とされる種々の機能を実行するためにも用いられる。必要な各内部電圧を生成するために、電圧発生回路と称される回路が用いられることがある。ダイナミックランダムアクセスメモリ(dynamic random access memory; DRAM)などの典型的なメモリデバイスは、上記のような電圧発生回路を多数有していることがある。これらの電圧発生回路は、グランド基準に対して正の電圧(例えばブーストされたワード線電圧、すなわちVPP)、およびグランド基準に対して負の電圧(例えばバックバイアス電圧、すなわちVBB、または負のワード線電圧、すなわちVNWL)を含む様々な電圧を生成するように構成されている。

【0003】

所定の装置に設けられた各電圧発生回路は、電圧を生成する間に電力を消費する。ICデバイスによって消費される電力を節約するために、電圧発生回路は、選択的に有効および無効にされるモード(待機モードと称される)に置かれることがある。待機モードでは、ICデバイスが必要な電圧を使用している間は、電圧発生回路が有効にされる。例えばICデバイスがメモリデバイスである場合は、このメモリデバイスが(例えば読み出し、書き込み、またはリフレッシュ)アクセスを行うために電圧発生回路の出力を使用する直前において、電圧発生回路が有効にされる。電圧発生回路は、必要な電圧を生成するために有効にされている間には、電力を消費する。メモリデバイスがアクセスされていないときは、電圧が不要であるため電圧発生回路は無効にされ、これによって節電される。メモリデバイスへの各アクセスは、クロックのタイミングに合わせられているため(例えばリフレッシュ動作は、セルフリフレッシュタイマーによって誘発される)、各アクセスが行われる直前に電圧発生回路を選択的に有効または無効にするために、クロック信号が用いられる。従って待機モードは、クロックト待機モード(clocked standby mode; CSM)と称される。

【0004】

図1は、クロックト待機モードを利用した典型的なメモリデバイス100を示すブロック図である。メモリデバイス100は、その1つ以上のメモリアレイ104へアクセスするために用いられる制御回路102を有している。制御回路102は、メモリデバイスを構成および制御するために用いられる複数の内部回路を有している。例えば、制御回路102は、メモリデバイス100の温度を測定するために用いられる温度センサ108を有している。メモリデバイス100の動作特性(例えばセルフリフレッシュ周期)は、測定された温度に基づいて調節される。

【0005】

メモリデバイス100は、基準電圧発生器110および電圧発生回路112を有している。基準電圧発生器110は、出力基準電圧VREFを生成する。出力基準電圧VREFは、電圧発生回路112が出力電圧VOUT(s)、V1、V2、・・・VXを生成するために用いられる。出力電圧V1、V2、・・・VXおよび基準電圧VREFは、メモリデバイス100の制御回路102およびメモリアレイ104に供給される。上記基準電圧は、制御回路102がメモリアレイ104へ(例えば読み出し、書き込み、またはリフレッシュ)アクセスするために用いられる。基準電圧発生器110および電圧発生回路112は、クロックト待機モード制御部114によって選択的に有効および無効にされる。場合によっては、クロックト待機モード制御部114は、制御回路102によって有効または無効にされる。別の場合では、クロックト待機モード制御部114は、イネーブル信号(enabling signal)を用いずに恒久的に有効にされるか、あるいは、レーザヒューズまたは電子的にプログラム可能なヒューズ(電子ヒューズ)など、メモリデバイス100のヒューズを溶断することによって恒久的に有効にされる。

【0006】

図2は、1つ以上の電圧発生回路112および基準電圧発生器110を選択的に有効にするために用いられる、典型的なクロックト待機モード制御部114を示すブロック図である。クロックト待機モード制御部114への入力は、上記クロックト待機モードを有効にするための信号(CSM_ENと称される)である。CSM_ENがHighの論理値であるときは、上記クロックト待機モードが有効にされ、そしてクロックト待機モード制御部114によって、クロックト待機モードクロック信号(CSM_CLK)が生成される。場合によっては、クロックト待機モード制御部114は、クロックト待機モードクロック信号を生成するために、ベースクロック信号(Base_CLK)と称される別のクロック信号を用いる。クロックト待機モードクロック信号CSM_CLKは、電圧発生回路112および基準電圧発生器110を選択的に有効および無効にするために用いられる。CSM_ENが一定の値(例えばLowの論理値)である場合は、クロックト待機モードは無効にされる。これは、電圧発生回路112および基準電圧発生器110が、常に出力電圧および基準電圧を生成していることを意味している。クロックト待機モードが無効にされたときは、CSM_CLK信号は、電圧発生回路112および基準電圧発生器110を常に有効にするために、一定の値(例えばLowの論理値)に設定される。

【0007】

場合によっては、基準電圧発生器110および電圧発生回路112を有効および無効にすることによって、基準電圧発生器110の出力基準電圧VREF、および電圧発生回路112の出力電圧V1、V2、・・・VXが変動する。例えば、場合によっては、基準電圧発生器110を有効および無効にすることによって、出力基準電圧VREFに電荷が蓄積する。VREFにおける(正または負の)変動によって、電圧発生回路112の出力電圧V1、V2、・・・VXに変化が生じる。別の場合では、たとえVREFが安定を保っていたとしても、電圧発生回路を有効および無効にすることによって、VREFの変化とは関係なく、電圧発生回路112の出力電圧V1、V2、・・・VXに直接変動が生じる。VREF、およびメモリデバイス100の電圧発生回路112の出力電圧V1、V2、・・・VXの変化によって、メモリデバイス100が機能不全を起こす可能性がある。例えば、メモリデバイス100のメモリアレイ104をリフレッシュするために、1つ以上の電圧VREFまたはV1、V2、・・・VXが制御回路102によって用いられる場合は、電圧の変化によってメモリアレイ104が十分にリフレッシュされず、結果としてメモリが失われる。

【0008】

従って、クロックト待機モードによって影響を受ける電圧を調整するための改良された方法および装置が必要とされている。

【0009】

〔本発明の概要〕

本発明の実施形態は、一般的には、メモリデバイス上に配置された基準電圧発生器によって生成された出力基準電圧を制御するための方法および装置を示している。一実施形態では、メモリデバイスのクロックト待機モードを可能にするための信号が受信される。この信号によって、メモリデバイスがクロックト待機モードにあることが示された場合は、上記基準電圧発生器の出力基準電圧として、第1の電圧を用いて第1の基準電圧が生成される。上記信号によって、メモリデバイスがクロックト待機モードにないことが示された場合は、上記基準電圧発生器の出力基準電圧として、第2の電圧を用いて第2の基準電圧が生成される。

【0010】

本発明の別の実施形態では、電圧発生器を含むデバイスのクロックト待機モードを有効にするための制御信号が受信される。この制御信号によって、クロックト待機モードが無効であることを示された場合は、上記電圧発生器によって生成される出力電圧が、上記電圧発生器に供給される入力電圧を用いて生成される。上記制御信号によって、クロックト待機モードが有効であることを示された場合は、上記電圧発生器に供給される入力電圧が変更され、変更された電圧は、上記電圧発生器の出力電圧を生成するために用いられる。

【0011】

本発明の別の実施形態は、基準電圧を生成するための手段、およびクロックト待機モードを制御するための手段を有したメモリデバイスを示している。基準電圧を生成するための上記手段は、メモリデバイスのクロックト待機モードを有効にするための制御信号を受信するように構成されている。上記制御信号によって、メモリデバイスのクロックト待機モードが有効であることを示された場合は、基準電圧を生成するための上記手段は、上記電圧発生器の出力電圧として、第1の入力電圧を用いて第1の基準電圧を生成する。上記制御信号によって、メモリデバイスのクロックト待機モードが無効であることを示された場合は、基準電圧を生成するための上記手段は、電圧発生器の出力電圧として、第2の入力電圧を用いて第2の基準電圧を生成する。クロックト待機モードを制御するための上記手段は、メモリデバイスのクロックト待機モードが有効であるときに、基準電圧を生成するための上記手段を選択的に有効および無効にするように構成されている。

【0012】

本発明のさらに別の実施形態は、電源、基準電圧出力線、第1の回路、および少なくとも1つの抵抗を有した回路を示している。上記第1の回路は、上記電源によって供給された供給電圧を用いて、上記基準電圧出力線へ基準電圧を生成するように構成されている。上記少なくとも1つの抵抗は、上記電源と基準電圧出力線との間に挟まれている。また、上記抵抗は、クロックト待機モードを有効および無効にするための信号によって有効および無効にされる。上記少なくとも1つの抵抗を有効および無効にすることによって、上記基準電圧出力線上の基準電圧が上昇または低下する。

【0013】

〔図面の簡単な説明〕

上述した本発明の特徴が詳しく理解されるように、添付図面に示されている実施形態を参照しながら、前項において概説した本発明をより具体的に説明する。しかし添付図面は、本発明の典型的な実施形態を示すものであって、本発明の範囲を限定するものと考えられることはなく、本発明は同様に効果的な別の実施形態も許容することについて留意されたい。

【0014】

図1は、クロックト待機モードを利用した典型的なメモリデバイスを示すブロック図である。

【0015】

図2は、1つ以上の電圧発生回路を選択的に有効にするために用いられる、典型的なクロックト待機モード制御を示すブロック図である。

【0016】

図3は、典型的な電圧発生回路を示す回路図である。

【0017】

図4は、電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【0018】

図5は、本発明の一実施形態に従って、基準電圧の電圧シフトを補償するために、クロックト待機モードを有効および無効にするための信号(CSM_EN)を用いる、他の基準電圧発生器を示すブロック図である。

【0019】

図6は、本発明の一実施形態に従った、他の基準電圧発生器を示す回路図である。

【0020】

図7は、本発明の一実施形態に従って、選択的に有効にされた補償抵抗を基準電圧発生器へ挿入した場合の影響を示すタイミング図である。

【0021】

図8は、電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【0022】

図9は、本発明の一実施形態に従って、クロックト待機モード中に上昇する基準電圧VREFを生成するために用いられる、他の基準電圧発生回路を示す図である。

【0023】

図10は、本発明の一実施形態に従って、クロックト待機モードが有効にされたときにおける、上昇した基準電圧VREFの出力電圧VOUTに対する影響を示すタイミング図である。

【0024】

〔好ましい実施形態の詳細な説明〕

本発明の実施形態は、一般的には、メモリデバイス上に配置された基準電圧発生器によって生成された出力基準電圧を制御するための方法および装置を示している。一実施形態では、メモリデバイスのクロックト待機モードを可能にするための信号が受信される。この信号によって、メモリデバイスがクロックト待機モードにあることが示された場合は、上記基準電圧発生器の出力基準電圧として、第1の基準電圧が第1の電圧を用いて生成される。上記信号によって、メモリデバイスがクロックト待機モードにないことが示された場合は、上記基準電圧発生器の出力基準電圧として、第2の基準電圧が第2の電圧を用いて生成される。

【0025】

本明細書に記載の回路は、内部で生成された電圧および基準電圧を利用した任意数のデバイスに利点をもたらすように使用することができる。以下の説明は、分かりやすくするために、ダイナミックランダムアクセスメモリ(DRAM)デバイスなどの具体的なメモリデバイスに当てはめているが、これは本明細書に記載の回路を使用したデバイスの実施例を限定するものではない。さらに以下の説明は、Highの論理信号へとアサートされた、あるいはLowの論理信号へと引き下げられた特定の制御信号を参照しているが、これらの信号レベルは単なる典型例であって、本明細書に記載の回路は、任意の極性および/または電圧レベルを有する任意数の信号を用いるように構成できることは当業者であれば理解できるであろう。また、一部の信号は、所定の制御回路またはデバイスから生じたものとして記載されているが、記載されているあらゆる制御信号は、任意の回路またはデバイスから生じることについて理解されたい。同様に、本明細書に記載されている全ての信号名は典型例であって、本発明の実施形態は一般的に、任意の名を有する任意の信号、および/または、このような信号の1つ以上から生じた任意の信号を用いて実施することができる。

【0026】

同様に、記載されているクロックト待機モード制御部、制御回路、電圧発生器、基準電圧発生器、電圧調整器などの特定の回路の形態は、単なる典型例にすぎない。場合によっては、本発明の実施形態の形態をよりよく説明するために、上記のような回路を簡素化した形態が示されている。しかし本発明の実施形態は、このような回路の複雑かつ/または商業的な形態を含む、任意の形態または構成を用いるように適応できることは、当業者であれば理解できるであろう。

【0027】

〔メモリデバイスに対する電圧の生成〕

次に、本発明の実施形態をよりよく理解するために、基準電圧および電圧発生回路112の出力電圧を生成するための典型的な方法および回路について説明する。図3は、典型的な基準電圧発生回路110、および典型的な電圧発生回路112を示す回路図である。これらの回路は、クロックト待機モード信号(CSM_CLK)によって選択的に有効および無効にされる。

【0028】

基準電圧発生器110および電圧発生回路112が有効であるとき(例えば、CSM_CLK信号がLowの論理値であるとき)は、スイッチS1 302、S2 308、およびS3 318は閉じていて、スイッチS4 312は閉じている。これによって電圧発生回路112に電流が流れ、そして基準電圧VREFから出力電圧VOUTが生成される。これについては後述する。

【0029】

本発明の一実施形態として、基準電圧VREFは、2つの抵抗R1 304およびR2 306を有する分圧器によって生成されるようになっていてもよい。上記抵抗R1 304およびR2 306は、スイッチを介して、高電圧(VREG)および低電圧(VGND)に接続されている。上記分圧器、あるいはその他の抵抗、トランジスタ、またはこれ以外のIC素子のグループは、抵抗ネットワーク310とも称される。CSM_CLK信号が電圧発生器112を有効にすると、スイッチS1 302およびS2 308が閉じ、そして抵抗R1 304およびR2 306を流れる電流によって基準電圧が生成される。生成された基準電圧は、以下の方程式によって表される:

VREF=(VREG−VGND)・R2/(R1+R2)

R1 304およびR2 306の値を変えることによって、所望の基準電圧VREFが生成される。

【0030】

抵抗ネットワーク310によって出力された基準電圧は、(電圧調整器とも称される)電圧発生回路112へ入力される。電圧調整器は、入力電圧(VREF)に対して出力電圧(VOUT)を一定の値に保持する電子回路である。電圧発生回路112が有効にされると、VOUTをVREFと比較するためにオペアンプ(op-amp)322が用いられる。オペアンプ322の出力は、電源電圧VREGを用いて電圧VOUTを制御するPMOSトランジスタ314への入力である。PMOSトランジスタ314がオンであるとき(オペアンプ322によって低い電圧が印加されたとき)は、PMOSトランジスタ314に電流が流れ、これによってVOUTが上昇する。PMOSトランジスタ314がオフであるとき(オペアンプ322によって高い電圧が印加されたとき)は、PMOSトランジスタ314に電流は流れない。これによってVOUTが、ロード(load)に接続されている場合は低下する。このように、オペアンプ322の出力電圧のわずかな上昇または低下に対応して、VOUTがわずかに低下または上昇する。

【0031】

調整回路112が有効とされたときに、(例えば、VOUTを使用する回路による電力消費が高いために)VOUTがVREFよりわずかに小さい場合は、PMOSトランジスタ314へ印加される出力電圧がオペアンプ322によって低下する。PMOSトランジスタ314への出力電圧が低下すると、PMOSトランジスタ314によってVOUTへ供給される電流がわずかに上昇する。これによってVOUTが上昇してVREFの値に近づく。同様に、(例えば、VOUTを使用する回路による電力消費が低いために)VOUTがVREFよりわずかに大きい場合であれば、PMOSトランジスタ314へ印加される出力電圧がオペアンプ322によって上昇する。PMOSトランジスタ314への出力電圧が上昇すると、PMOSトランジスタ314によってVOUTへ供給される電流がわずかに低下する。これによってVOUTが低下してVREFの値に近づく。このように電圧調整器は、VREGからVOUTへ供給される電源を上昇または低下させることによって、VREFに対してVOUTを一定の値に保持する。VREFに対するVOUTの電圧レベルを判別するために、抵抗R3 316と、抵抗R1およびR2との比率を用いることができる。

【0032】

CSM_CLKがLowの論理値からHighの論理値へ変化すると、電圧発生器112および基準電圧発生器110が無効にされる。電圧発生器が無効にされると、スイッチS1 302、S2 308、およびS3 318が開き、スイッチS4 312が閉じる。スイッチS1 302、S2 308、およびS3 318が開いているときは、電圧発生回路112および基準電圧発生器110が消費する電力は少ない。電圧発生回路112が無効とされたときには、VOUTは、スイッチS3 318およびS4 312によって、メモリデバイス100内の別の電圧から電子的に絶縁される。回路内の別の電圧から絶縁されているときの出力電圧は、フローティング出力電圧と称される。出力電圧線のキャパシタンスは、出力電圧を一定の値(例えば、電圧発生回路112が無効にされる直前の出力電圧)に保持する傾向がある。しかし場合によっては、フローティング出力電圧は一定の値にとどまらない。フローティング出力電圧は、例えばメモリデバイス100内の漏れ電流によって降下する。この「降下」効果については、図8に照らして以下に詳述する。

【0033】

〔クロックト待機モードに起因するVREFの変動〕

前述したように、基準電圧発生器110を有効および無効にすることによって、基準電圧発生器110の出力電圧VREFが変動する。基準電圧発生器110を有効および無効にすることによって、例えば基準電圧発生器110内への電荷の蓄積がもたらされ、そしてクロックト待機モードが有効とされたときには、基準電圧VREFにおける電圧シフト(DCシフトとも称される)が生じる。図4は、基準電圧発生器110の出力電圧VREFに対する、クロックト待機モードを有効および無効にする信号(CSM_EN)の影響を示すタイミング図である。時間T1では、信号CSM_ENはLowの論理値である。これは、クロックト待機モードが無効であることを示している。従って時間T1では、基準電圧VREFにオフセットはない。

【0034】

後のT2では、信号CSM_ENがHighの論理レベルへ引き上げられる。信号CSM_ENがHighの論理レベルへ引き上げられると、クロックト待機モードが有効になり、そしてクロックト待機モードクロック信号(CSM_CLK)を用いて、基準電圧発生器110が選択的に有効および無効にされる。図示されているように、クロックト待機モードを有効にすることによって、基準電圧発生器の出力電圧VREFに電圧シフトΔVが生じる。後の時間T3において、信号CSM_CLKがLowの論理レベルに引き下げられ、これによってクロックト待機モードが無効になる。基準電圧発生器110を無効状態から有効状態へ切り替える際に、(例えば回路内のキャパシタンスおよびインダクタンスを起因として)本質的にレイテンシが生じるため、基準電圧VREFのレベルが通常に戻るまでには、いくらかの時間(例えば時間T4まで)がかかる。従って時間T4では、基準電圧発生器110の出力電圧VREFには、電圧シフトΔVはもはや存在しない。

【0035】

図4は、クロックト待機モードに起因するVREFにおける正のオフセットを示している。しかし場合によっては、VREFにおける変化ΔVは負のオフセットであってよい。オフセットΔVの方向に関わらず、VREFにおける変化ΔVによって、電圧発生回路112の出力電圧VOUTに変化が生じ、また別の回路に悪影響が及ぼされる。

【0036】

図1を再び参照されたい。基準電圧VREFおよび/または電圧発生回路112の出力電圧VOUTを使用する制御回路102は、これら基準電圧および/または出力電圧が変化した場合は機能不全を起こす。例えば、制御回路102内の温度センサ108は、チップの温度が所定の範囲内であるか否かを判別するために基準電圧VREFを使用する。制御回路102は、測定された温度に基づいて、メモリデバイス100を制御するために用いられる所定の制御信号を設定する。温度センサ108は、基準電圧VREFの変化に対して感受性が非常に高い。基準電圧VREFにおけるシフトΔVのために、温度センサが正確な温度を測定できない場合は、制御回路102による制御信号の設定が不適切となる。これによってメモリデバイス100が機能不全を起こすか、あるいは必要なデバイス仕様を満たすことができなくなる可能性がある。

【0037】

本発明の一実施形態として、基準電圧発生器110は、クロックト待機モードが有効とされたときにVREFに生じる電圧シフトΔVを補償できるように変更されていてもよい。図5は、本発明の一実施形態に従って変更された基準電圧発生器を示すブロック図である。この基準電圧発生器は、基準電圧での電圧シフトを補償するために、クロックト待機モードを有効および無効にするための信号(CSM_EN)を用いる。

【0038】

図6は、本発明の一実施形態に従って変更された基準電圧発生器510を示す回路図である。図6に示されているように、図1〜図3に示されている基準電圧発生器110は、上部抵抗R4 608および下部抵抗R5 610を基準電圧発生器510へ挿入することによって変更できる。上部抵抗R4 608は、電圧発生器510内の高電源電圧(VREG)と、基準電圧VREFを生成するために用いられる抵抗ネットワーク310との間に挿入することができる。上部抵抗R4 608を挿入することによって、抵抗ネットワーク310への電圧入力がVREGからVHIGHへと低下する。同様に、下部抵抗R610は、基準電圧発生器510内の低電源電圧(VGND)と、電圧VREFを生成するために用いられる抵抗ネットワークとの間に挿入することができる。下部抵抗610を挿入することによって、抵抗ネットワーク310への電圧入力がVGNDからVLOWへと上昇する。

【0039】

本発明の一実施形態として、挿入された各抵抗608および610は、クロックト待機モードを有効および無効にするために用いられるクロックト待機モード制御信号CSM_ENを用いて選択的に有効および無効にされるようになっていてもよい。基準電圧発生器510は、上部および下部抵抗を適切に有効および無効にすることによって、クロックト待機モードに起因する電圧変化ΔVを補償する。

【0040】

前述したように、例えばクロックト待機モードが無効とされたときは、クロックト待機モード制御信号CSM_ENはLowの論理値である。CSM_EN信号がLowの論理値であるときは、上部抵抗608は無効であり、下部抵抗610は有効である。抵抗ネットワーク310が(図3に示されている)分圧器を有している場合は、R4 608は無効であり、R5 610は有効である。VREFの式は次の通りとなる:

VREF=(VREG−VGND)・(R2+R5)/(R5+R1+R2)

上記の式が示すように、抵抗R5 610が有効とされたときはVREFが高くなる。従って、R5 610、R1 304、およびR2 306に対して適切な値を選択することによって、クロックト待機モードが無効とされたときに用いられる所望のレベルまで出力基準電圧VREFを上げることができる。

【0041】

後に、CSM_ENがHighの論理値に引き上げられ、クロックト待機モードが有効とされたときは、上部抵抗608が有効になり、下部抵抗610が無効になる。これによってVREFが生成される方法が変わり、クロックト待機モードを有効にすることによって生じたVREFにおける変化ΔVが補償される。例えば抵抗ネットワーク310が分圧器を有している場合は、R4 608は有効であり、R5 610は無効である。VREFの式は次の通りとなる:

VREF=(VREG−VGND)・R2/(R4+R1+R2)

上記の式が示すように、抵抗R4が有効とされたときはVREFが低くなる。従って、R4 608、R1 304、およびR2 306に対して適切な値を選択することによって、クロックト待機モードが有効とされたときに用いられる低さのレベルに出力基準電圧VREFを設定することができる。従って、クロックト待機モードが有効とされたときに上部抵抗608を有効にし、下部抵抗610を無効にすることによって、基準電圧VREFが低い電圧にシフトされる。これによって、正の電圧シフトΔVが補償される。

【0042】

図7は、選択的に有効にされた補償抵抗608および610を基準電圧発生器510へ挿入した場合の影響を示すタイミング図である。前述同様に、時間T1では、信号CSM_ENはLowの論理値である。これは、クロックト待機モードが無効であることを示している。上部抵抗608は無効であり、下部抵抗610は有効である。一実施形態では、生成された基準電圧VREFは、抵抗R5 610、R1 304、およびR2 306によって判別される。従って時間T1では、基準電圧VREFにオフセットはない(例えばVREF=VTARGET)。

【0043】

後のT2において、(CSM_ENがHighの論理レベルであるときに)クロックト待機モードが有効にされ、そしてクロックト待機モードクロックCSM_CLKを用いて、基準電圧発生器510が選択的に有効および無効にされる。クロックト待機モードが有効とされたときは、上部抵抗608が有効にされ、下部抵抗610が無効にされる。これによって、VREFに補償効果(例えばVREFをLowにする効果)がもたらされる。従って、図7の時間T2に示されているように、VREFは、図4(すなわち、クロックト待機モードが無効とされたとき)と比べて、基準電圧発生器510が常に有効であるときとほぼ同じレベル(VTARGET)を維持する。後の時間T3において、CSM_ENはLowの論理レベルへ引き下げられ、これによってクロックト待機モードが無効になる。上部抵抗608が無効にされ、下部抵抗610が有効にされ、そしてVREFがほぼ同じレベルを維持する。

【0044】

抵抗を有効および無効にする際にレイテンシが本質的に生じるため、VREFにおいて期間のわずかなスパイク(spike)tsが生じる一方、抵抗608および610は有効または無効にされる。しかしVREFのスパイクは、程度が小さくかつ期間が限定されているため、メモリセルデバイス100の機能性に優位な影響を及ぼすことはない。また、スパイクの程度およびVREFにおける変化がわずかであるため、VREFは、例えばT4以前において、正確かつ安定した値(VTARGET)をより迅速に回復する。

【0045】

図4〜図7では、クロックト待機モードに起因するVREFにおけるオフセットΔVは正である。しかし場合によっては、前述したように、変化ΔVはVREFにおいて負であってもよい。ΔVが負である場合は、基準電圧発生器510は、前述した方法と同様の方法によってΔVを補償するように変更してもよい。例えば、上部抵抗608および下部抵抗610が有効および無効にされる順番を反対にして、クロックト待機モードが有効とされたときに上部抵抗608が無効になり、下部抵抗610が有効になるようにしてもよい。クロックト待機モードが有効であり、かつΔVが負であるときに、下部抵抗610を有効にし、そして上部抵抗608を有効にすることによって、VREFへの悪影響は、上昇補償電圧(upward compensating voltage)を生成することによって最小限にとどめることができる。

【0046】

より一般的には、各抵抗608および610は、当業者に知られている任意の方法を用いて選択的に有効にすることができる。例えば、ΔVが正である一実施形態では、上部抵抗608および下部抵抗610を選択的に有効および無効にするために、CSM_ENの補数である信号が用いられる。クロックト待機モードが無効であり、基準電圧が安定しているときを示す上記信号は、REF_STABLEと称される。この信号はまた、クロックト待機モードが無効とされたときはHighの値である。クロックト待機モードが有効であり、かつREF_STABLEがLowの論理値であるときは、上部抵抗608および下部抵抗610をそれぞれ有効および無効にし、VREFにおける上昇シフト(upward shift)ΔVを補償するために、上部抵抗608内のPMOSトランジスタ、および下部抵抗610内のNMOSトランジスタが用いられる。抵抗を選択的に有効および無効にするための別の方法は、当業者には容易に明らかとなるであろう。同様に、本発明の実施形態は、トランジスタおよび/またはオペアンプなどの能動素子を有するネットワークを含む、基準電圧VREFを生成するために用いられる別の抵抗ネットワーク310に有利になるように用いることができる。

【0047】

いずれの場合においても、メモリデバイス100がクロックト待機モードにあるか否かに関わらず、VREFは安定している。VREFが安定しているときは、制御回路102などの別の回路、および制御回路102内の温度センサ108は、クロックト待機モードが有効であるか否かに関わらず、VREFの値に依存する。

【0048】

〔クロックト待機モードに起因するVOUTの変動〕

前述したように、クロックト待機モードにある回路を有効および無効にすることによって、電圧発生回路112の出力電圧VOUTが、クロックト待機モードに起因して変動する。図8は、電圧発生回路112の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。時間T1では、CSM_EN信号はLowの論理値である。これは、クロックト待機モードが無効とされたことを示している。従って、クロックト待機モード制御114によって生成された信号CSM_CLKがLowの論理レベルに設定される。これによって基準電圧発生器110および電圧発生回路112が有効にされ、そしてVREFおよびVOUTが一定のレベルに維持される。

【0049】

後のT2において、CSM_EN信号はHighの論理レベルに引き上げられて、これによりクロックト待機モードが有効になる。CSM_EN信号が引き上げられると、クロックト待機モード制御114がCSM_CLK信号を生成する。このCSM_CLK信号は、基準電圧発生器110および電圧発生回路112を選択的に有効および無効にする。従って、CSM_EN信号が引き上げられると、クロックト待機モード制御114がCSM_CLK信号をHighの論理値へアサートし、これによって電圧発生回路112が無効になるため、図3に関連して説明したようにVOUTがフローティングとなる。

【0050】

メモリデバイス100がクロックト待機モードに置かれると、メモリデバイス100への各アクセスが行われる直前か、あるいはメモリデバイス100がVREFおよび/またはVOUTを用いるときにおいて、基準電圧発生器110および電圧発生回路112が選択的に有効にされる。従って後のT3では、CSM_CLK信号がLowの論理レベルへ引き下げられる。これによって電圧発生回路112が再び有効にされ、そして基準電圧発生器110および電圧発生回路112によって、それぞれVREFおよびVOUTが能動的に生成される。この結果、メモリデバイス100の負荷へのVOUTの出力によって、VOUTが臨界値を下回ることはない。

【0051】

基準電圧発生器110および電圧発生回路112が有効にされるたびに、CSM_CLK信号が、パルス幅時間TPWと称される設定時間においてLowとされる。時間TPWが経過した後において(時間T4)、CSM_CLK信号が再びアサートされる。これによって基準電圧発生器110および電圧発生回路112が再び無効にされる。CSM_CLKをアサートおよび引き下げるプロセスは、CSM_EN信号がアサートされている間は継続される。従って、CSM_CLKの周期およびCSM_CLKのパルス幅TPWは、基準電圧発生器110および電圧発生回路112がいつ、どれほどの時間無効にされるのかを決定する。

【0052】

電圧発生回路112が無効とされてVOUTがフローティングとなっている間は、VOUTは、電圧生成回路112が無効にされたことによる初期のフローティングの値そのものを維持するとは限らない。電圧発生回路112が無効にされるたびに、漏れ電流などの副次的効果によってVOUTが緩やかに劣化していく。このVOUTの劣化は、たとえ、図3に関連して説明したスイッチS1 302、S2 308、S3 318、およびS4 312を用いてVOUTが電気的に絶縁されていたとしても生じる。このVOUTの劣化は、図8においてVDROOPとして示されている。上記劣化は、基準電圧発生器110および電圧発生回路112が無効にされるたびに始まり、そしてBase_CLK信号の低下によりVOUTが引き上げられることによって基準電圧発生器110および電圧発生回路112が有効にされるまで続く。場合によっては、VDROOPは、プロセス、電圧、および温度(PVT)の変化によって異なる。電圧発生回路112が有効にされるたびに、電圧発生回路112がVOUTをVREFレベルまで引き戻すことによってVOUTを補正するのに、ある有限の時間がかかる。VDROOPの程度が大きいほど、電圧発生回路112がVOUTを修復する時間が長くなる。

【0053】

VOUTは、メモリデバイス100内の別の回路によって用いられるため、VOUT_MINと称される限界値を下回らないことが重要である。VOUTがVOUT_MINを下回った場合は、VOUTが十分に早く修復されず、またVOUTを用いるメモリデバイス100内の別の回路が正常に機能しなくなる。例えば、CSM_CLKの各周期中に基準電圧発生器110および電圧発生回路112が有効にされる時間TPWは、メモリデバイス100が正常に機能するために必要であるVOUTの標的レベル(VOUT_TARGETと称される)までVOUTを引き戻すには不十分である。従ってその後の周期T5〜T6では、VOUTは、VOUTの平均レベルが、メモリデバイス100が正常に機能するために必要な最低電圧VOUT_MINを超える値に維持されなくなる時間T7まで、VOUT_TARGETをさらに下回る。また場合によっては、降下VDROOPが大きくなりすぎてVOUTが完全に崩壊する。所望するVOUTの値と、電圧降下VDROOPの増加による実際のVOUTの値との差は、図8のタイミング図において、(VOUTを示す)破線と、(VOUT_TARGET付近に維持されたVOUTの所望の値を示す)実線との差によって図示されている。

【0054】

本発明の一実施形態として、VOUTを生成するために用いられる基準電圧VREFは、クロックト待機モードによって生じるVOUTの降下VDROOPの増大を補償するように変更されていてもよい。例えば、VREFは、クロックト待機モードが有効とされたとき(例えば、CSM_ENがHighの論理レベルであるとき)に高くなるように変更されていてもよい。クロックト待機モードが有効になってVREFが上昇すると、VOUTを生成するためにVREFを用いる電圧発生器112(図1に示されている)は、上昇したVREFの値に対応してVOUTをよりHighのレベルへ引き上げようとする。電圧発生器112がVOUTをよりHighのレベルへ引き上げようとすると、VOUTが上昇するレートがこれに対応して上昇し、VOUTの回復(recovery)が早くなる。従ってVREFが上昇すると、VOUTがより高い電圧レベルに維持される。これによってVOUTが、基準電圧発生器110および電圧発生回路112が有効にされる周期TPW中に、電圧降下VDROOPから完全に回復する。

【0055】

図9は、本発明の一実施形態に従って、クロックト待機モード中に上昇する基準電圧VREFを生成するために用いられる、他の基準電圧発生回路910を示す図である。図9に示されている基準電圧発生器910は、図3に示されている基準電圧発生回路110の改良版である。図3に示されている基準電圧発生回路110は、抵抗R2 306と、VREF信号のための基準電圧出力線との間に抵抗R6 912を挿入することによって改良されている。抵抗R6 912は、スイッチS5 914を用いて選択的に有効および無効にされる(短絡される)。

【0056】

本発明の一実施形態として、スイッチS5は、クロックト待機モードを有効および無効にするための信号CSM_ENによって制御されるようになっていてもよい。メモリデバイス100のクロックト待機モードが無効にされると、CSM_ENはLowの論理レベルになり、そしてスイッチS5 914は閉じられる。スイッチS5 914が閉じられると、抵抗R6 912の代わりにスイッチ914に分圧器内の電流が流れ、これによって抵抗R6 912が短絡、すなわち無効になる。抵抗R6 912が無効になると、基準電圧発生器910は、抵抗R1 304およびR2 306のみを用いて、基準電圧VREFを生成する。この基準電圧VREFは、図3に関連して記した方程式と同じ方程式によって表される:

VREF=(VREG−VGND)・R2/(R1+R2)

従って、クロックト待機モードが無効にされると、基準電圧VREFは、抵抗R1 304およびR2 306に対して選択された値に従った標準(初期)値となる。

【0057】

クロックト待機モードが有効にされ、CSM_ENがHighの論理レベルに引き上げられると、スイッチS5が開かれる。これによって、スイッチS5の代わりに抵抗R6 912に電流が流れて、抵抗R6が有効となる。抵抗R6 912が有効にされると、基準電圧発生器910は、抵抗R1 304、R2 306、およびR6 912を用いて基準電圧VREFを生成する。基準電圧発生器が抵抗R1 304、R2 306、およびR6 912を用いて生成した基準電圧VREFは、以下の方程式によって表される:

VREF=(VREG−VGND)・(R2+R6)/(R1+R2+R6)

R6 912に対して適切な値を選択することによって、VREFは、クロックト待機モードが有効にされたときに、所望する分だけ高くなる。

【0058】

図10は、本発明の一実施形態に従って、クロックト待機モードが有効にされたときにおける、上昇した基準電圧VREFの出力電圧VOUTに対する影響を示すタイミング図である。時間T1では、CSM_EN信号はLowの論理値であり、これはクロックト待機モードが無効であることを示している。従って、クロックト待機モード制御部114によって生成された信号CSM_CLKもまたLowの論理レベルに設定される。これによって、基準電圧発生器910および電圧発生回路112が有効にされ、そしてVREFおよびVOUTが一定の値に維持される。スイッチS 914は閉じているため、抵抗R6 912は、VREFを生成するために用いられる分圧器に対して影響を及ぼすことはない。従って、VREFは標準的な動作値に維持される。

【0059】

後のT2では、CSM_EN信号がHighの論理レベルに引き上げられ、クロックト待機モードが有効にされる。CSM_EN信号がHighの論理レベルに引き上げられて、クロックト待機モードが有効にされると、クロックト待機モード制御部114は、クロックト待機モードクロック信号CSM_CLKを生成する。CSM_CLKは、基準電圧発生器910および電圧発生回路112を選択的に有効および無効にする。CSM_ENによって制御されるスイッチS5 914は、CSM_ENがHighの論理値であるときに開かれる。これによって、分圧器内の電流が、スイッチS5 914の代わりに抵抗R6 912に流れる。従って基準電圧発生器910内の分圧器は、(基準電圧発生器910が有効にされたときに、)抵抗R6 912を用いて、基準電圧VREFに対して上昇した値(VREF_BOOSTEDと称される)を生成する。

【0060】

時間T3〜T4では、CSM_CLK信号が引き下げられる。CSM_CLK信号が引き下げられると、基準電圧発生器910および電圧発生回路112が有効にされる。クロックト待機モードが有効にされる(例えばCSM_ENがHighの論理値であり、かつスイッチS5 914が開いている)と、VREFが上昇する。このため、変更された出力電圧VOUT_NEW(暗線で示されている)は、標的電圧VOUT_TARGETまで完全に引き上げられ、従って未変更の電圧VOUT_OLD(破線で示されている)よりも高い電圧に維持される。従って、電圧発生器910および112が無効にされる各周期中(T3〜T4、T5〜T6、およびT7の初め)では、VOUT_NEWは、メモリデバイス100が正常に機能するために必要な最低閾値VOUT_MINを上回る値を維持する。言い換えると、フローティングとなった出力電圧VOUTが、漏れ電流のためにわずかに降下し続けている間に、VOUTを生成するために用いられる上昇したVREFの値が選択される。これによって、VOUTは、周期TPW中に基準電圧発生器110および電圧発生回路112が有効にされるたびに、電圧降下VDROOPから完全に回復する。従って、VOUT_NEWはVOUT_TARGET付近に維持されて、限界値VOUT_MINを下回らないようにされる。このようにして、VOUTを用いた回路は正常に機能する。

【0061】

本明細書に記載の実施形態は、クロックト待機モードによって影響を受ける1つ以上の電圧に関連して説明されている。しかし本発明の実施形態は、基準電圧発生器の基準電圧または出力電圧が、集積回路のいずれの動作特性によっても影響を受ける状況において実施可能であることも想定される。

【0062】

また、以上の説明は、本発明の実施形態に向けられたものであるが、本発明の基本的な範囲から逸脱することなく、本発明の別のさらなる実施形態を考案することができる。本発明の範囲は、特許請求の範囲によって規定される。

【図面の簡単な説明】

【0063】

【図1】クロックト待機モードを利用した典型的なメモリデバイスを示すブロック図である。

【図2】1つ以上の電圧発生回路を選択的に有効にするために用いられる、典型的なクロックト待機モード制御を示すブロック図である。

【図3】典型的な電圧発生回路を示す回路図である。

【図4】電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【図5】本発明の一実施形態に従って、基準電圧の電圧シフトを補償するために、クロックト待機モードを有効および無効にするための信号(CSM_EN)を用いる、他の基準電圧発生器を示すブロック図である。

【図6】本発明の一実施形態に従った、他の基準電圧発生器を示す回路図である。

【図7】本発明の一実施形態に従って、選択的に有効にされた補償抵抗を基準電圧発生器へ挿入した場合の影響を示すタイミング図である。

【図8】電圧発生回路の出力電圧VOUTに対するクロックト待機モードの影響を示すタイミング図である。

【図9】本発明の一実施形態に従って、クロックト待機モード中に上昇する基準電圧VREFを生成するために用いられる、他の基準電圧発生回路を示す図である。

【図10】本発明の一実施形態に従って、クロックト待機モードが有効にされたときにおける、上昇した基準電圧VREFの出力電圧VOUTに対する影響を示すタイミング図である。

【特許請求の範囲】

【請求項1】

メモリデバイス上に配置された基準電圧発生器によって生成された出力基準電圧を制御するための方法であって、

上記メモリデバイスのクロックト待機モードを有効にするための信号を受信し、

上記信号が、上記メモリデバイスが上記クロックト待機モードにあることを示した場合は、第1の電圧を用いて、上記基準電圧発生器の上記出力基準電圧として第1の基準電圧を生成し、

上記信号が、上記メモリデバイスが上記クロックト待機モードにないことを示した場合は、第2の電圧を用いて、上記基準電圧発生器の上記出力基準電圧として第2の基準電圧を生成する、方法。

【請求項2】

上記メモリデバイスが上記クロックト待機モードにあるときに、クロックト待機モードクロック信号が、上記基準電圧発生器を選択的に有効および無効にする、請求項1に記載の方法。

【請求項3】

上記第1の電圧が上記第2の電圧より大きい、請求項1に記載の方法。

【請求項4】

電圧発生回路が、生成された出力基準電圧を用いて出力電圧を維持し、

上記メモリデバイスが上記クロックト待機モードにあるときには、クロックト待機モード制御信号が、上記電圧発生回路を選択的に有効および無効にする、請求項1に記載の方法。

【請求項5】

上記第1の基準電圧が上記第2の基準電圧より大きく、

上記第1の基準電圧が、上記電圧発生回路を選択的に有効および無効にした結果として、上記電圧発生回路によって生じた上記出力電圧における電圧降下を補償する、請求項4に記載の方法。

【請求項6】

電圧発生器によって生じた出力電圧を制御するための方法であって、

上記電圧発生器を有するデバイスのクロックト待機モードを有効にするための制御信号を受信し、

上記制御信号が、上記クロックト待機モードが無効であることを示した場合は、上記電圧発生器に供給された入力電圧を用いて上記出力電圧を生成し、

上記制御信号が、上記クロックト待機モードが有効であることを示した場合は、上記電圧発生器に供給された上記入力電圧を変更し、そして上記電圧発生器の上記出力電圧を生成するために、変更された上記電圧を用いる、方法。

【請求項7】

出力電圧が、調整された電圧を生成するために別の電圧発生回路によって用いられ、

上記入力電圧の変更が、上記出力電圧が上昇するように上記入力電圧を上昇させることを含んでいる、請求項6に記載の方法。

【請求項8】

集積回路デバイスであって、

基準電圧発生器と、

ただし、上記基準電圧発生器は、デバイスがクロックト待機モードにある場合は、第1の供給電圧を用いて、電圧発生器の出力電圧として第1の基準電圧を生成するとともに、デバイスが上記クロックト待機モードにない場合は、第2の供給電圧を用いて、電圧発生器の出力電圧として第2の基準電圧を生成するように構成されていて、

上記クロックト待機モードが有効にされたときに、上記基準電圧発生器を選択的に有効および無効にするように構成されたクロックト待機モード制御回路と、

を有している集積回路デバイス。

【請求項9】

上記デバイスが上記クロックト待機モードにあるときに、上記クロックト待機モード制御回路が、上記基準電圧発生器を選択的に有効および無効にするためのクロックト待機モードクロック信号を生成する、請求項8に記載の回路。

【請求項10】

上記第1の電圧が上記第2の電圧より大きく、

上記第1の電圧が、上記クロックト待機モードを有効化したことに起因する上記基準電圧発生器の出力電圧の変化を低減するように選択されている、請求項8に記載の回路。

【請求項11】

生成された出力基準電圧を用いて出力電圧を維持し、

上記クロックト待機モードを有効にするための信号が、上記デバイスが上記クロックト待機モードにあることを示したときは、クロックト待機モード制御信号が電圧発生回路を選択的に有効および無効にし、かつ

上記第1の基準電圧が上記第2の基準電圧よりも大きくなるように構成されている電圧発生回路をさらに有している、請求項8に記載の回路。

【請求項12】

回路であって、

上記回路のクロックト待機モードを有効にするための制御信号を受信し、

上記制御信号が、上記クロックト待機モードが無効であることを示した場合は、上記基準電圧発生器に供給された入力電圧を用いて出力電圧を生成し、かつ

上記制御信号が、上記クロックト待機モードが有効であることを示した場合は、上記基準電圧発生器に供給された上記入力電圧を変更し、そして変更された上記電圧を用いて、上記基準電圧発生器の出力電圧を生成するように構成された基準電圧発生器を有している、回路。

【請求項13】

上記クロックト待機モードが有効とされたとき、および上記クロックト待機モードが無効とされたときに、上記基準電圧発生器の上記出力電圧がほぼ同じ電圧を維持する、請求項12に記載の回路。

【請求項14】

出力電圧が、調整された電圧を生成するために別の電圧発生回路によって用いられ、

上記入力電圧を変更する工程が、上記出力電圧が上昇するように上記入力電圧を上昇させる工程を含んでいる、請求項12に記載の回路。

【請求項15】

メモリデバイスであって、

上記メモリデバイスのクロックト待機モードを有効にするための制御信号を受信し、

上記制御信号が、上記メモリデバイスの上記クロックト待機モードが有効であることを示した場合は、第1の入力電圧を用いて、電圧発生器の出力電圧として第1の基準電圧を生成し、かつ

上記制御信号が、上記メモリデバイスの上記クロックト待機モードが無効であることを示した場合は、第2の入力電圧を用いて、上記電圧発生器の上記出力電圧として第2の基準電圧を生成するように構成された、基準電圧を生成するための手段と、

上記メモリデバイスの上記クロックト待機モードが有効とされたときに、上記基準電圧を生成するための手段を選択的に有効および無効にするように構成された、上記クロックト待機モードを制御するための手段と、を含んでいるメモリデバイス。

【請求項16】

上記メモリデバイスが上記クロックト待機モードにあるときに、上記クロックト待機モードを制御するための上記手段が、上記基準電圧を生成するための上記手段を選択的に有効および無効にするためのクロックト待機モードクロック信号を生成する、請求項15に記載のメモリデバイス。

【請求項17】

上記第1の電圧が上記第2の電圧より大きい、請求項15に記載のメモリデバイス。

【請求項18】

電源と、

基準電圧出力線と、

上記電源によって供給された供給電圧(supply voltage)を用いて、上記基準電圧出力線上に基準電圧を生成するように構成された第1の回路と、

上記電源と上記基準電圧出力線との間に配置されていて、クロックト待機モードを有効および無効にするための信号によって有効および無効にされ、かつ、有効および無効にされることによって上記基準電圧出力線上の上記基準電圧を上昇または低下させる少なくとも1つの抵抗と、を有している回路。

【請求項19】

上記基準電圧出力線上の上記基準電圧を用いて出力電圧を生成するように構成されていると共に、上記クロックト待機モードが有効とされたときにクロック信号によって選択的に有効および無効にされる電圧発生回路をさらに有し、

上記少なくとも1つの抵抗が、上記クロックト待機モードが有効にされたときに有効とされる、請求項18に記載の回路。

【請求項20】

上記少なくとも1つの抵抗を有効にすることによって、上記基準電圧出力線上の上記基準電圧が上昇し、

上記基準電圧が上昇することによって、上記クロックト待機モードが有効とされたときに上記電圧発生回路を選択的に有効および無効にすることに起因する上記出力電圧の低下を補償する、請求項19に記載の回路。

【請求項1】

メモリデバイス上に配置された基準電圧発生器によって生成された出力基準電圧を制御するための方法であって、

上記メモリデバイスのクロックト待機モードを有効にするための信号を受信し、

上記信号が、上記メモリデバイスが上記クロックト待機モードにあることを示した場合は、第1の電圧を用いて、上記基準電圧発生器の上記出力基準電圧として第1の基準電圧を生成し、

上記信号が、上記メモリデバイスが上記クロックト待機モードにないことを示した場合は、第2の電圧を用いて、上記基準電圧発生器の上記出力基準電圧として第2の基準電圧を生成する、方法。

【請求項2】

上記メモリデバイスが上記クロックト待機モードにあるときに、クロックト待機モードクロック信号が、上記基準電圧発生器を選択的に有効および無効にする、請求項1に記載の方法。

【請求項3】

上記第1の電圧が上記第2の電圧より大きい、請求項1に記載の方法。

【請求項4】

電圧発生回路が、生成された出力基準電圧を用いて出力電圧を維持し、

上記メモリデバイスが上記クロックト待機モードにあるときには、クロックト待機モード制御信号が、上記電圧発生回路を選択的に有効および無効にする、請求項1に記載の方法。

【請求項5】

上記第1の基準電圧が上記第2の基準電圧より大きく、

上記第1の基準電圧が、上記電圧発生回路を選択的に有効および無効にした結果として、上記電圧発生回路によって生じた上記出力電圧における電圧降下を補償する、請求項4に記載の方法。

【請求項6】

電圧発生器によって生じた出力電圧を制御するための方法であって、

上記電圧発生器を有するデバイスのクロックト待機モードを有効にするための制御信号を受信し、

上記制御信号が、上記クロックト待機モードが無効であることを示した場合は、上記電圧発生器に供給された入力電圧を用いて上記出力電圧を生成し、

上記制御信号が、上記クロックト待機モードが有効であることを示した場合は、上記電圧発生器に供給された上記入力電圧を変更し、そして上記電圧発生器の上記出力電圧を生成するために、変更された上記電圧を用いる、方法。

【請求項7】

出力電圧が、調整された電圧を生成するために別の電圧発生回路によって用いられ、

上記入力電圧の変更が、上記出力電圧が上昇するように上記入力電圧を上昇させることを含んでいる、請求項6に記載の方法。

【請求項8】

集積回路デバイスであって、

基準電圧発生器と、

ただし、上記基準電圧発生器は、デバイスがクロックト待機モードにある場合は、第1の供給電圧を用いて、電圧発生器の出力電圧として第1の基準電圧を生成するとともに、デバイスが上記クロックト待機モードにない場合は、第2の供給電圧を用いて、電圧発生器の出力電圧として第2の基準電圧を生成するように構成されていて、

上記クロックト待機モードが有効にされたときに、上記基準電圧発生器を選択的に有効および無効にするように構成されたクロックト待機モード制御回路と、

を有している集積回路デバイス。

【請求項9】

上記デバイスが上記クロックト待機モードにあるときに、上記クロックト待機モード制御回路が、上記基準電圧発生器を選択的に有効および無効にするためのクロックト待機モードクロック信号を生成する、請求項8に記載の回路。

【請求項10】

上記第1の電圧が上記第2の電圧より大きく、

上記第1の電圧が、上記クロックト待機モードを有効化したことに起因する上記基準電圧発生器の出力電圧の変化を低減するように選択されている、請求項8に記載の回路。

【請求項11】

生成された出力基準電圧を用いて出力電圧を維持し、

上記クロックト待機モードを有効にするための信号が、上記デバイスが上記クロックト待機モードにあることを示したときは、クロックト待機モード制御信号が電圧発生回路を選択的に有効および無効にし、かつ

上記第1の基準電圧が上記第2の基準電圧よりも大きくなるように構成されている電圧発生回路をさらに有している、請求項8に記載の回路。

【請求項12】

回路であって、

上記回路のクロックト待機モードを有効にするための制御信号を受信し、

上記制御信号が、上記クロックト待機モードが無効であることを示した場合は、上記基準電圧発生器に供給された入力電圧を用いて出力電圧を生成し、かつ

上記制御信号が、上記クロックト待機モードが有効であることを示した場合は、上記基準電圧発生器に供給された上記入力電圧を変更し、そして変更された上記電圧を用いて、上記基準電圧発生器の出力電圧を生成するように構成された基準電圧発生器を有している、回路。

【請求項13】

上記クロックト待機モードが有効とされたとき、および上記クロックト待機モードが無効とされたときに、上記基準電圧発生器の上記出力電圧がほぼ同じ電圧を維持する、請求項12に記載の回路。

【請求項14】

出力電圧が、調整された電圧を生成するために別の電圧発生回路によって用いられ、

上記入力電圧を変更する工程が、上記出力電圧が上昇するように上記入力電圧を上昇させる工程を含んでいる、請求項12に記載の回路。

【請求項15】

メモリデバイスであって、

上記メモリデバイスのクロックト待機モードを有効にするための制御信号を受信し、

上記制御信号が、上記メモリデバイスの上記クロックト待機モードが有効であることを示した場合は、第1の入力電圧を用いて、電圧発生器の出力電圧として第1の基準電圧を生成し、かつ

上記制御信号が、上記メモリデバイスの上記クロックト待機モードが無効であることを示した場合は、第2の入力電圧を用いて、上記電圧発生器の上記出力電圧として第2の基準電圧を生成するように構成された、基準電圧を生成するための手段と、

上記メモリデバイスの上記クロックト待機モードが有効とされたときに、上記基準電圧を生成するための手段を選択的に有効および無効にするように構成された、上記クロックト待機モードを制御するための手段と、を含んでいるメモリデバイス。

【請求項16】

上記メモリデバイスが上記クロックト待機モードにあるときに、上記クロックト待機モードを制御するための上記手段が、上記基準電圧を生成するための上記手段を選択的に有効および無効にするためのクロックト待機モードクロック信号を生成する、請求項15に記載のメモリデバイス。

【請求項17】

上記第1の電圧が上記第2の電圧より大きい、請求項15に記載のメモリデバイス。

【請求項18】

電源と、

基準電圧出力線と、

上記電源によって供給された供給電圧(supply voltage)を用いて、上記基準電圧出力線上に基準電圧を生成するように構成された第1の回路と、

上記電源と上記基準電圧出力線との間に配置されていて、クロックト待機モードを有効および無効にするための信号によって有効および無効にされ、かつ、有効および無効にされることによって上記基準電圧出力線上の上記基準電圧を上昇または低下させる少なくとも1つの抵抗と、を有している回路。

【請求項19】

上記基準電圧出力線上の上記基準電圧を用いて出力電圧を生成するように構成されていると共に、上記クロックト待機モードが有効とされたときにクロック信号によって選択的に有効および無効にされる電圧発生回路をさらに有し、

上記少なくとも1つの抵抗が、上記クロックト待機モードが有効にされたときに有効とされる、請求項18に記載の回路。

【請求項20】

上記少なくとも1つの抵抗を有効にすることによって、上記基準電圧出力線上の上記基準電圧が上昇し、

上記基準電圧が上昇することによって、上記クロックト待機モードが有効とされたときに上記電圧発生回路を選択的に有効および無効にすることに起因する上記出力電圧の低下を補償する、請求項19に記載の回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2007−128632(P2007−128632A)

【公開日】平成19年5月24日(2007.5.24)

【国際特許分類】

【外国語出願】

【出願番号】特願2006−210182(P2006−210182)

【出願日】平成18年8月1日(2006.8.1)

【出願人】(506211850)キモンダ アクチエンゲゼルシャフト (110)

【Fターム(参考)】

【公開日】平成19年5月24日(2007.5.24)

【国際特許分類】

【出願番号】特願2006−210182(P2006−210182)

【出願日】平成18年8月1日(2006.8.1)

【出願人】(506211850)キモンダ アクチエンゲゼルシャフト (110)

【Fターム(参考)】

[ Back to top ]