クロックバッファ回路及びこれを用いたクロック分配回路

【課題】小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供すること。

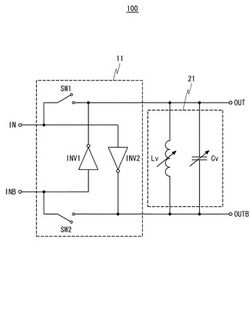

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロックバッファ回路及びこれを用いたクロック分配回路に関し、特に広帯域のクロック信号に対応するクロックバッファ回路及びこれを用いたクロック分配回路に関する。

【背景技術】

【0002】

近年、MISFET(Metal-Insulator-Semiconductor Field-Effect Transistor)の微細化と共に、クロック信号の周波数が向上している。そのため、高性能プロセッサなどの高周波回路では、数GHzの周波数を有するクロック信号が一般的に用いられる。このような高周波回路では、回路全体がクロック信号に同期して動作するので、チップ内部でのクロックタイミングのずれ(クロックスキュー)が大きな問題となる。

【0003】

高周波回路を搭載するチップ内部には、高周波回路にクロック信号を分配するクロック分配回路が搭載される。図16は、従来のクロック分配回路1600の構成例を示すブロック図である。図16に示すように、クロック分配回路1600は、クロック信号源CSOURCE及び複数のインバータINVにより構成される。インバータINVは、クロック信号源CSOURCEと回路ブロックとの間に挿入され、クロックバッファ回路として機能する。つまり、クロック信号は、クロック信号源CSOURCEから、数段のインバータINVを介して、各回路ブロックに供給される。クロック信号源CSOURCEは、クロック分配回路1600と同一チップ上に、又は、別のチップ上に配置される。チップ全体にクロック信号を供給する場合、クロック信号配線やインバータINVでの信号遅延は、回路ブロック毎に異なる。このため、クロック分配回路1600では、回路ブロック毎にクロックスキューが発生するという問題があった。クロックスキューが発生すると、回路ブロック間で信号のやりとりをする際にタイミングがずれてしまうので、誤動作の原因となる。

【0004】

これを解決する方法として、回路レイアウトを利用したH型クロック分配回路が提案されている。図17は、一般的なH型クロック分配回路1700の構成例を示すブロック図である。H型クロック分配回路1700は、クロック信号源CSOURCEから各回路ブロックまでのクロック配線長及びインバータINVの段数を等しくすることにより、タイミングずれを抑制する。しかし、実際の回路では、回路ブロックが完全に対称に配置されるわけではなく、理想的なH型クロック分配を実現することは困難である。

【0005】

また、H型クロック分配回路の他に、能動的にクロックスキューを調整する方法として、PLL(Phase Locked Loop)回路をクロックバッファ回路として用いる手法もある。図18は、PLLを用いてクロックスキューを低減する場合のPLL回路1800の構成例を示すブロック図である。図18に示すように、PLL回路1800は、PLL181及び1個以上のインバータINVにより構成される。クロック信号は、クロック入力INからPLL181へ供給される。PLL181の出力と端子Eとの間には、1個以上のインバータINVが挿入される。端子Eにおけるクロック信号は、PLL181にフィードバックされる。PLL181は、端子Eにおけるクロック信号の位相と端子Fにおけるクロック信号の位相とを揃えるように位相制御を行なう。その結果、端子Eと端子Fとの間のクロックスキューを低減できる。しかし、この手法ではクロックスキューを小さくできるものの、PLL181による消費電力の増大やチップ面積の増大を招くという問題があった。

【0006】

さらに、上述の手法とは異なるクロックスキュー抑制方法として、共振クロックが提案されている(例えば、非特許文献1又は2)。この手法では、インバータの代わりに、LC共振回路をクロックバッファ回路として用いる。図19は、典型的なLC共振回路1900の一例を示すブロック図である。LC共振回路1900は、インバータ部191及びLCタンク部192により構成される。インバータ部191は、インバータINV191及びINV192により構成される。インバータINV191及びINV192は、MISFETにより構成される。インバータINV191の入力はクロック入力INBと接続され、出力はクロック入力INと接続される。インバータINV192の入力はクロック入力INと接続され、出力はクロック入力INBと接続される。LCタンク部192は、クロック出力OUT及びOUTBの間に並列に接続された、インダクタLs及びキャパシタCsで構成される。

【0007】

このLC共振回路1900のクロック入力IN及びINBには、外部からクロック信号が入力される。このときLC共振回路1900(LCタンク部192)の発振周波数と外部クロック周波数とが近い場合には、注入同期(インジェクションロック)が起こる。その結果、LC共振回路1900の発振周波数は、外部クロック周波数に同期する。

【0008】

図16に示すクロック分配回路1600は、入力信号を単純に増幅して出力するので、入力と出力との間には遅延が発生する。一方、このLC共振回路1900では、LC共振回路1900自身が発振器としてクロック信号を発生させる。従って、図18に示すPLL回路1800と同様に、入力(外部からのクロック信号)に対して位相が同期するように動作(注入同期)する。その結果、クロックスキューを抑制することができる。また、LC共振回路1900は、インダクタとキャパシタで電力を蓄積して回生させることができるので、インバータのみを用いた回路よりも低電力で駆動できる。さらに、PLLのような位相制御回路も必要ないので、PLLで消費される電力を低減できる。

【先行技術文献】

【非特許文献】

【0009】

【非特許文献1】Frank O'Mahony et al., "A 10-GHz Global Clock Distribution Using Coupled Standing-Wave Oscillators", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.38, NO.11, NOVEMBER 2003, pp.1813-1820.

【非特許文献2】John Wood et al., "Multi-GigaHertz Low-Power Low-Skew Rotary Clock Scheme", 2001 IEEE International Solid-State Circuits Conference, SESSION25, CLOCK GENERATION AND DISTRIBUTION, 25.5.

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかし、発明者は上述の手法では以下のような問題が有ることを見出した。近年のロジック回路では、低電力化を実現するため、複数のクロック周波数に対応することが求められる。また、テストを行う際に低周波のクロック信号が用いられる場合が有るので、このような低周波のテストクロック信号にも対応することが求められる。

【0011】

ところが、図19に示すようなLC共振回路は、外部から供給されるクロック信号の周波数が共振周波数からずれてしまうと、クロック信号を適切に増幅することができない。従って、複数のクロック周波数に対応することは困難である。加えて、LC共振回路は、高周波クロック信号の増幅には適しているものの、テストに用いられるような低周波クロック信号を増幅することが困難である。つまり、図19に示すようなLC共振回路では、広帯域のクロックバッファ回路を実現することはできない。その結果、LC共振回路を用いて、複数のクロック周波数に対応できるクロック分配回路を構成することもできない。

【0012】

これに対し、高周波クロック信号をLC共振回路で増幅し、低周波クロック信号をインバータ回路で増幅する手法が考え得る。この場合、LC共振回路及びインバータ回路にクロック信号を供給し、LC共振回路及びインバータ回路の出力側に設けたスイッチをクロック信号の周波数に応じて切り換えることにより、好適に増幅されたクロック信号を供給することができる。しかしながら、この手法では、LC共振回路及びインバータ回路の両方をクロック分配回路に設けなくてはならないので、回路構造が複雑化し、回路面積の増大を招いてしまう。

【0013】

すなわち、従来の手法によっては、広帯域のクロック信号に対応した省面積のクロックバッファ回路及びクロック分配回路を実現することはできなかった。

【課題を解決するための手段】

【0014】

本発明の一態様であるクロックバッファ回路は、クロック入力からの入力クロック信号の少なくとも正転出力を、クロック出力へ出力するドライバ部と、前記ドライバ部とクロック出力との間に配置されたLCタンク部と、を備え、前記ドライバ部は、入力クロック信号の周波数に対応した制御信号に応じて、当該ドライバ部の入力と出力とを短絡させるスイッチを備えるものである。

【0015】

本発明の一態様であるクロックバッファ回路によれば、クロック信号の周波数に応じて、クロックバッファ回路の動作を、高周波の入力クロックに対応した共振回路としての動作、又は、低周波の入力クロックに対応したインバータ回路としての動作に切り換えることが可能である。これにより、単一のクロックバッファ回路により、広い周波数帯のクロック信号に対応することが可能である。

【発明の効果】

【0016】

本発明によれば、小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供することができる。

【図面の簡単な説明】

【0017】

【図1】実施の形態1にかかるクロックバッファ回路100の構成を示すブロック図である。

【図2】実施の形態2にかかるクロックバッファ回路200の構成を示すブロック図である。

【図3】実施の形態3にかかるクロックバッファ回路300の構成を示すブロック図である。

【図4】実施の形態4にかかるクロックバッファ回路400の構成を示すブロック図である。

【図5】実施の形態5にかかるクロックバッファ回路500の構成を示すブロック図である。

【図6】実施の形態6にかかるクロックバッファ回路600の構成を示すブロック図である。

【図7】可変インダクタの構成例を示す回路図である。

【図8】実施の形態6におけるシミュレーションに用いたクロック分配回路のブロック図である。

【図9A】実施の形態6における第1のシミュレーション条件におけるシミュレーション結果を示す信号波形である。

【図9B】実施の形態6における第2のシミュレーション条件におけるシミュレーション結果を示す信号波形である。

【図9C】実施の形態6における第3のシミュレーション条件におけるシミュレーション結果を示す信号波形である。

【図10】実施の形態7にかかるクロックバッファ回路のインダクタ−スイッチ部の構成を示す回路図である。

【図11】実施の形態8にかかるクロックバッファ回路のインダクタ−スイッチ部の構成を示す回路図である。

【図12】実施の形態9にかかるクロック分配回路900の構成を示すブロック図である。

【図13】実施の形態10にかかるクロック分配回路1000の構成を示すブロック図である。

【図14】実施の形態10にかかる周波数検出回路の構成例を示す回路図である。

【図15】実施の形態10にかかる周波数検出回路の構成例を示す回路図である。

【図16】従来のクロック分配回路1600の構成例を示すブロック図である。

【図17】一般的なH型クロック分配回路1700の構成例を示すブロック図である。

【図18】PLL回路1800の構成例を示すブロック図である。

【図19】LC共振回路1900の一例を示すブロック図である。

【発明を実施するための形態】

【0018】

以下、図面を参照して本発明の実施の形態について説明する。各図面においては、同一要素には同一の符号が付されており、必要に応じて重複説明は省略される。

【0019】

実施の形態1

まず、本発明の実施の形態1にかかるクロックバッファ回路について説明する。図1は、実施の形態1にかかるクロックバッファ回路100の構成を示すブロック図である。クロックバッファ回路100は、図1に示すように、クロック入力IN及びINBとクロック出力OUT及びOUTBとの間に、ドライバ部11及びLCタンク部21が配置される。クロック入力IN及びINBには、差動クロック信号が入力される。クロック出力OUT及びOUTBからは、差動クロック信号が出力される。

【0020】

ドライバ部11は、インバータINV1及びINV2、スイッチSW1及びSW2により構成される。スイッチSW1は、クロック入力INとクロック出力OUTとの間に接続される。スイッチSW2は、クロック入力INBとクロック出力OUTBとの間に接続される。インバータINV1は、クロック入力INBとクロック出力OUTとの間に接続され、クロック入力INBに入力されるクロック信号の反転信号をクロック出力OUTへ出力する。インバータINV2は、クロック入力INとクロック出力OUTBとの間に接続され、クロック入力INに入力されるクロック信号の反転信号を、クロック出力OUTBへ出力する。

【0021】

LCタンク部21は、可変インダクタLv及び可変容量Cvにより構成される。可変インダクタLv及び可変容量Cvは、クロック出力OUT及びOUTBの間に、並列に接続される。なお、可変インダクタLvは、固定インダクタとしてもよい。可変容量Cvは、固定容量としてもよい。

【0022】

続いて、クロックバッファ回路100の動作について説明する。ドライバ部11のスイッチSW1及びSW2がオンである場合には、クロックバッファ回路100は、図16に示すLC共振回路1600と等価の回路となる。よって、クロックバッファ回路100は、入力クロック信号に対して注入同期し、入力クロック信号の周波数で共振する。つまり、クロックバッファ回路100は、入力クロック信号に同期して信号を増幅するバッファ回路として動作する。クロック入力IN及びINBに入力されたクロック信号は増幅される。増幅されたクロック信号は、それぞれクロック出力OUT及びOUTBから出力クロック信号として出力される。その結果、クロックバッファ回路100のクロックスキューを低減できる。

【0023】

また、クロックバッファ回路100では、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値は可変である。よって、入力クロック信号の周波数がある程度変化しても、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値を調整することにより、入力クロック信号に追従することができる。可変インダクタLvのインダクタンス値及び可変容量Cvの容量値の調整は、外部に設けられた制御回路(不図示)などから、可変インダクタLv及び可変容量Cvへ、制御信号を供給することにより実現できる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。これにより、クロックバッファ回路100は、例えば最大周波数の1/4倍〜1倍の周波数帯において共振が可能となる。

【0024】

ドライバ部11のスイッチSW1及びSW2がオフである場合には、ドライバ部11は、インバータ回路となる。クロック入力IN及びINBに入力されたクロック信号は増幅される。増幅されたクロック信号は、それぞれクロック出力OUT及びOUTBから出力クロック信号として出力される。よって、入力クロック信号の周波数がLCタンク部21の共振周波数に対して約1/4以下である場合でも、クロックバッファ回路100が動作できる。この場合、クロックスキュー低減の効果は発揮されないが、入力クロック信号の周波数が低いので、クロックスキューは問題とはならない。その結果、クロックバッファ回路100は、低周波数の入力クロック信号を増幅できる。

【0025】

すなわち、クロックバッファ回路100は、スイッチSW1及びSW2により、ドライバ部11の動作を切り換えることができる。これにより、クロックバッファ回路100の動作を、共振回路としての動作又はインバータ回路としての動作に切り換えることが可能である。なお、クロックバッファ回路100は、いずれの場合でも、入力クロック信号の正転出力を、出力クロック信号として出力する。

【0026】

なお、スイッチSW1及び2は、外部に設けられた制御回路(不図示)などから、制御信号が供給されることにより開閉することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0027】

従って、クロックバッファ回路100は、広い周波数帯の入力クロック信号に対応することができる。また、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値を変化させることで、LCタンク部21の共振周波数を変化させることができる。その結果、クロックバッファ回路100は、広い周波数帯の入力クロック信号に対して共振することができる。

【0028】

実施の形態2

次に、本発明の実施の形態2にかかるクロックバッファ回路について説明する。図2は、実施の形態2にかかるクロックバッファ回路200の構成を示すブロック図である。クロックバッファ回路200は、図2に示すように、実施の形態1にかかるクロックバッファ回路100のLCタンク部21をLCタンク部22に置き換えた構成を有する。LCタンク部22は、クロック出力OUT及びOUTBの間で、可変インダクタLvに対して直列に接続されるスイッチSW3を有する。なお、図2に示すスイッチSW3の接続位置は単なる例示であり、例えば、可変インダクタLv及びスイッチSW3の位置を入れ換えてもよい。クロックバッファ回路200のその他の構成は、クロックバッファ回路100と同様であるので、説明を省略する。

【0029】

続いて、クロックバッファ回路100の動作について説明する。ドライバ部11のスイッチSW1及びSW2、LCタンク部22のスイッチSW3がオンである場合には、クロックバッファ回路200は、図16に示すLC共振回路と等価の回路となる。よって、クロックバッファ回路200は、クロックバッファ回路100と同様に、入力クロック信号に同期して信号を増幅するバッファ回路として動作する。その結果、クロックバッファ回路200のクロックスキューを低減できる。

【0030】

ドライバ部11のスイッチSW1及びSW2がオフ、LCタンク部22のスイッチSW3がオンである場合には、クロックバッファ回路200は、インバータ回路となる。よって、クロックバッファ回路200は、クロックバッファ回路100と同様に、低周波数の入力クロック信号を増幅できる。

【0031】

ドライバ部11のスイッチSW1及びSW2、LCタンク部22のスイッチSW3がオフである場合には、出力クロック信号の短絡経路が切断され、可変インダクタLvには貫通電流が流れない。この場合、LCタンク部22はLC共振器として機能しない。すなわち、クロックバッファ回路200は、必要に応じてLCタンク部22のオン/オフを切り替えることができる。これにより、さらに低周波の入力クロック信号に対応することが可能となる。

【0032】

また、可変インダクタLvには貫通電流が流れないので、入力クロック信号を停止した場合に、出力クロック信号の出力を速やかに停止することが可能となる。

【0033】

なお、スイッチSW3は、外部に設けられた制御回路(不図示)などから、制御信号が供給されることにより開閉することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0034】

実施の形態3

次に、本発明の実施の形態3にかかるクロックバッファ回路について説明する。図3は、実施の形態3にかかるクロックバッファ回路300の構成を示すブロック図である。クロックバッファ回路300は、図3に示すように、実施の形態2にかかるクロックバッファ回路200のLCタンク部22を、LCタンク部23に置き換えたものである。

【0035】

LCタンク部23は、LCタンク部22における可変インダクタLv及び可変容量Cvを、それぞれ固定インダクタLf及び固定容量Cfに置き換えたものである。クロックバッファ回路300のその他の構成は、クロックバッファ回路200と同様であるので、説明を省略する。

【0036】

クロックバッファ回路300は、LCタンク部23の共振周波数を調整できないことを除き、クロックバッファ回路200と同様の動作が可能である。従って、クロックバッファ回路300によれば、広い周波数帯の入力クロック信号に対応可能な、低消費電力のクロックバッファ回路を実現することができる。

【0037】

実施の形態4

次に、本発明の実施の形態4にかかるクロックバッファ回路について説明する。図4は、実施の形態4にかかるクロックバッファ回路400の構成を示すブロック図である。クロックバッファ回路400は、図4に示すように、実施の形態2にかかるクロックバッファ回路200のLCタンク部22を、LCタンク部24に置き換えたものである。

【0038】

LCタンク部24は、LCタンク部22における可変容量Cvを除去した構成を有する。クロックバッファ回路400は、取り除いた可変容量Cvを、配線の寄生容量及びクロックバッファ回路400に接続される負荷の容量で代替するものである。なお、可変インダクタLvは、固定インダクタとしてもよい。クロックバッファ回路400のその他の構成は、クロックバッファ回路200と同様であるので、説明を省略する。

【0039】

つまり、クロックバッファ回路400は、クロックバッファ回路200と同様に動作することが可能である。従って、クロックバッファ回路400によれば、広い周波数帯の入力クロック信号に対応可能な、低消費電力のクロックバッファ回路を実現することができる。

【0040】

実施の形態5

次に、本発明の実施の形態5にかかるクロックバッファ回路について説明する。図5は、実施の形態5にかかるクロックバッファ回路500の構成を示すブロック図である。クロックバッファ回路500は、図5に示すように、シングルエンド信号である入力クロック信号が供給される。クロックバッファ回路500は、ドライバ部15及びLCタンク部25により構成される。

【0041】

ドライバ部15は、インバータINV3及びINV4、スイッチSW4により構成される。インバータINV3の入力はクロック入力INと接続され、出力はインバータINV4の入力と接続される。インバータINV4の出力はクロック出力OUTと接続される。スイッチSW4は、インバータINV3の入力とインバータINV4の出力との間に接続される。

【0042】

LCタンク部25は、可変インダクタLv、可変容量Cv及びスイッチSW5により構成される。可変インダクタLv及び可変容量Cvは、クロック出力OUTと接地端子との間に、並列に接続される。なお、可変インダクタLvは、固定インダクタとしてもよい。可変容量Cvは、固定容量としてもよい。スイッチSW5は、クロック出力OUTと接地端子との間で、可変インダクタLvに対して直列に接続される。なお、図5に示すスイッチSW5の接続位置は単なる例示であり、例えば、可変インダクタLv及びスイッチSW5の位置を入れ換えてもよい。

【0043】

続いて、クロックバッファ回路500の動作について説明する。ドライバ部15のスイッチSW4及びLCタンク部25のスイッチSW5がオンである場合には、クロックバッファ回路500は、入力クロック信号に対して注入同期し、入力クロック信号の周波数で共振する。つまり、クロックバッファ回路400は、入力クロック信号に同期して信号を増幅するバッファ回路として動作する。その結果、クロックバッファ回路400のクロックスキューを低減できる。

【0044】

また、クロックバッファ回路400では、図1に示すクロックバッファ回路100と同様に、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値は可変である。よって、入力クロック信号の周波数がある程度変化しても、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値を調整することにより、入力クロック信号に追従することができる。可変インダクタLvのインダクタンス値及び可変容量Cvの容量値の調整は、外部に設けられた制御回路(不図示)などから、可変インダクタLv及び可変容量Cvへ、制御信号を供給することにより実現できる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。これにより、クロックバッファ回路400は、例えば最大周波数の1/4倍〜1倍の周波数でも共振が可能となる。

【0045】

ドライバ部15のスイッチSW4がオフ、LCタンク部25のスイッチSW5がオンである場合には、ドライバ部15は、インバータINV3及びINV4からなる正論理のバッファ回路となる。従って、より低い入力クロック信号を増幅することができる。クロックバッファ回路500の動作を、共振回路としての動作又はインバータ回路としての動作に切り換えることが可能である。なお、クロックバッファ回路500は、いずれの場合でも、入力クロック信号の正転出力を、出力クロック信号として出力する。

【0046】

ドライバ部15のスイッチSW4及びLCタンク部25のスイッチSW5がオフである場合には、可変インダクタLvに貫通電流が流れないので、LCタンク部25はLC共振器として機能しない。すなわち、クロックバッファ回路500は、必要に応じてLCタンク部25のオン/オフを切り替えることができる。これにより、さらに低周波の入力クロック信号に対応することが可能となる。

【0047】

また、可変インダクタLvには貫通電流が流れないので、入力クロック信号を停止した場合に、出力クロック信号の出力を速やかに停止することが可能となる。

【0048】

よって、クロックバッファ回路500によれば、広い周波数帯の入力クロック信号に対応できる低消費電力のクロックバッファ回路を提供することができる。

【0049】

実施の形態6

続いて、本発明の実施の形態6にかかるクロックバッファ回路について説明する。図6は、実施の形態6にかかるクロックバッファ回路600の構成を示す回路図である。クロックバッファ回路600は、実施の形態2にかかるクロックバッファ回路200を具体的な回路により構成したものである。

【0050】

電源回路61は、カレントミラー回路を構成するp型MISトランジスタ(MISFET)M8及びM9を有する。p型MISトランジスタM8及びM9のソースは、電源端子と接続される。p型MISトランジスタM8のドレインは、端子IREF、p型MISトランジスタM8及びM9のゲートと接続される。p型MISトランジスタM9のドレインは、ドライバ部11と接続される。これにより、電源回路61は、端子IREFに流れる基準電流の電流値に比例する電流値の電流を、ドライバ部11に供給する。

【0051】

ドライバ部11は、n型MISトランジスタ(MISFET)M1、M3、M5及びM6、p型MISトランジスタ(MISFET)M2及びM4により構成される。n型MISトランジスタM3とp型MISトランジスタM4とは、図2に示すインバータINV1に対応するインバータを構成する。n型MISトランジスタM1とp型MISトランジスタM2とは、図2に示すインバータINV2に対応するインバータを構成する。また、n型MISトランジスタM5は、図2のスイッチSW1に対応し、トランスファゲートとして機能する。n型MISトランジスタM6は、図2のスイッチSW2に対応し、トランスファゲートとして機能する。

【0052】

p型MISトランジスタM2のソースは、電源回路61のp型MISトランジスタM9のドレインと接続される。p型MISトランジスタM2のドレインは、n型MISトランジスタM1のドレインと接続される。n型MISトランジスタM1のソースは、接地端子と接続される。インバータINV2の入力であるn型MISトランジスタM1及びp型MISトランジスタM2のゲートは、クロック入力INと接続される。インバータINV2の出力であるn型MISトランジスタM1のドレインとp型MISトランジスタM2のドレインとの間のノードは、クロック出力OUTBと接続される。

【0053】

p型MISトランジスタM4のソースは、電源回路61のp型MISトランジスタM9のドレインと接続される。p型MISトランジスタM4のドレインは、n型MISトランジスタM3のドレインと接続される。n型MISトランジスタM3のソースは、接地端子と接続される。インバータINV1の入力であるn型MISトランジスタM3及びp型MISトランジスタM4のゲートは、クロック入力INBと接続される。インバータINV1の出力であるn型MISトランジスタM3のドレインとp型MISトランジスタM4のドレインとの間のノードは、クロック出力OUTと接続される。

【0054】

スイッチSW1であるn型MISトランジスタM5は、クロック入力INとクロック出力OUTとの間に接続される。n型MISトランジスタM5のゲートには、制御信号SCNT1が供給される。スイッチSW2であるn型MISトランジスタM6は、クロック入力INBとクロック出力OUTBとの間に接続される。n型MISトランジスタM6のゲートには、制御信号SCNT2が供給される。

【0055】

LCタンク部22は、可変インダクタLv1及びLv2、可変容量Cv、n型MISトランジスタM7により構成される。可変インダクタLv1及びLv2は、図2の可変インダクタLvに対応する。n型MISトランジスタM7は、図2のスイッチSW3に対応し、トランスファゲートとして機能する。n型MISトランジスタM7、可変インダクタLv1及びLv2は、クロック出力OUT及びOUTBの間に直列に接続される(インダクタ−スイッチ部221)。n型MISトランジスタM7のゲートには、制御信号SCNT3が供給される。なお、図6に示すn型MISトランジスタM7、可変インダクタLv1及びLv2の接続順序は単なる例示であり、図6に示す順序に限られない。

【0056】

上述の制御信号SCNT1〜SCNT3は、外部に設けられた制御回路(不図示)などにより供給することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0057】

ここで、制御信号SCNT3は、高レベル及び低レベルからなる2値信号とすることができる。また、高電圧と低電圧との間の任意の電圧を有する信号を制御信号SCNT3として供給し、n型MISトランジスタM7のソース−ドレイン間抵抗を連続的に変化せることで、後述する式(2)に示すように、クロックバッファ回路の共振周波数を変化させることも可能である。

【0058】

可変容量Cvは、クロック出力OUT及びOUTBの間に、インダクタ−スイッチ部221と並列に接続される。例えば、可変容量Cvをシリコンチップ上に形成する場合には、可変容量Cvは、MISトランジスタのゲート容量やMISトランジスタのソース部及びドレイン部のpn接合を利用して形成される。

【0059】

可変インダクタLv1及びLv2のインダクタンス値及び可変容量Cvの容量値の調整は、外部に設けられた制御回路(不図示)などから、これらへ制御信号を供給することにより実現できる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0060】

なお、可変容量Cvは、固定容量としてもよい。また、可変インダクタLv1及びLv2の両方又はいずれか一方を、固定インダクタとしてもよい。可変容量Cvは、容量素子を配置することなく、配線容量をもって代用することもできる。

【0061】

続いて、可変インダクタLv1及びLv2の構成例について説明する。図7は、可変インダクタLv1及びLv2の構成例を示す回路図である。可変インダクタLv1は、固定インダクタLf1及びLf2、スイッチMv1及びMv2により構成される。スイッチMv1はn型MISトランジスタ(MISFET)により構成され、スイッチMv2はp型MISトランジスタ(MISFET)により構成される。

【0062】

固定インダクタLf1、スイッチMv1及び固定インダクタLf4は、端子Aと端子Bとの間に、この順で直列に接続される。スイッチMv2は、固定インダクタLf1の端子A側の端子と、固定インダクタLf3のスイッチMv1側の端子と、の間に接続される。スイッチMv1の制御端子(ゲート端子)とスイッチMv2の制御端子(ゲート端子)には、制御信号SCNT4が供給される。すなわち、スイッチMv1とスイッチMv2とは、制御信号SCNT4に応じて、相補的に動作する。なお、制御信号SCNT4は、外部に設けられた制御回路(不図示)などにより供給することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0063】

制御信号SCNT4が高レベルであれば、スイッチMv1がオン、スイッチMv2がオフとなる。この場合、端子Aと端子Bとの間のインダクタンス値は、固定インダクタLf1及びLf2のインダクタンス値の和となる。一方、制御信号SCNT4が低レベルであれば、スイッチMv1がオフ、スイッチMv2がオンとなる。この場合、端子Aと端子Bとの間のインダクタンス値は、固定インダクタLf2のインダクタンス値となる。つまり、可変インダクタLv1及びLv2が図7の構成を有する場合、制御信号SCNT4により、インダクタンス値を2段階に変化させることができる。

【0064】

続いて、クロックバッファ回路600の動作について説明する。制御信号SCNT1〜3が高レベルである場合には、n型MISトランジスタM5〜M7はオンとなる。その結果、クロック入力INとクロック出力OUTとの間、及び、クロック入力INBとクロック出力OUTBとの間が直結され、共振が生じる(共振状態)。

【0065】

制御信号SCNT1及びSCNT2が低レベル、制御信号SCNT3が高レベルである場合には、n型MISトランジスタM5及びM6はオフ、n型MISトランジスタM7はオンとなる。よって、クロックバッファ回路600は、可変インダクタLv及び可変容量Cvを負荷とするインバータ回路となる。

【0066】

制御信号SCNT1〜3が低レベルである場合には、n型MISトランジスタM5〜M7はオフとなる。よって、クロックバッファ回路600は、可変容量Cvのみを負荷とするインバータ回路となる。

【0067】

クロックバッファ回路600における共振状態は、供給されるクロック信号の周波数が最も高い状態で使用される。ここで、クロック出力OUT及びOUTBのそれぞれに繋がる配線の寄生容量をCw、可変インダクタLv1及びLv2のインダクタンス値を共にLv0とする。このとき、クロックバッファ回路600の共振周波数fは、次の式(1)で示される。

【数1】

【0068】

故に、入力クロック信号の周波数が低くなった場合には、インダクタンス値Lv0や容量値Cvを大きくするように変化させることで、共振周波数fを入力クロック信号に追従させることができる。

【0069】

ただし、一般にオンチップで実現可能な可変容量や可変インダクタの可変範囲は2〜4倍程度である。さらに、式(1)に示すように、共振周波数はインダクタンス値Lv0及び容量値Cvの平方根でしか変化しない。従って、共振周波数が追従できる周波数帯には限界がある。例えば、インダクタンス値が固定で、容量値のみが可変である場合、実現可能な共振周波数の変化量は√2倍程度となる。つまり、最高のクロック周波数の1/√2が追従下限周波数となり、この追従下限周波数以下の周波数では注入同期できない。入力クロック信号の周波数が追従下限周波数以下の場合には、n型MISトランジスタM5及びM6をオフ、n型MISトランジスタM7をオンとする。つまり、クロックバッファ回路600を、可変インダクタLv1及びLv2、可変容量Cvを負荷とするインバータ回路として動作させる。

【0070】

ところが、可変インダクタLv1及びLv2を負荷とする回路では、入力クロック信号の周波数が式(1)に示す共振周波数fから離れるほど、ゲインが下がる。また、入力クロック信号を停止した場合でも、可変インダクタLv1及びLv2に貫通電流が流れてしまし、消費電力が増大する原因となる。このため、入力クロック信号の周波数がさらに低い場合には、n型MISトランジスタM7をオフとする。これにより、可変インダクタLv1及びLv2を非導通状態として、出力クロック信号を停止させる。

【0071】

一方、インダクタンス値及び容量値を共に可変とする場合には、入力クロック信号の最高周波数の1/4程度までは注入同期が可能となるので、この周波数を境として共振状態と非共振状態とを切り替える。

【0072】

上述では、制御信号SCNT3が高レベル又は低レベルの2値である場合について説明した。一方、図6に示すようにn型MISトランジスタM7をトランスファゲートとして使用する場合には、n型MISトランジスタM7のソース−ドレイン間の抵抗がトランスファゲートのオン抵抗となる。n型MISトランジスタM7はMISFETであるので、オン抵抗は制御信号SCNT3の電圧に応じて変化する。n型MISトランジスタM7のオン抵抗をR7とすると、オン抵抗R7を考慮した場合の共振周波数fは、式(2)で表される。

【数2】

【0073】

式(2)に示すように、n型MISトランジスタM7のオン抵抗R7が大きいほど、共振周波数fは下がる。つまり、入力クロック信号の周波数が下がった場合に、制御信号SCNT3の電圧を下げることで、共振周波数fを入力クロック信号の周波数に追従させることができる。同様に、入力クロック信号の周波数が上がった場合に、制御信号SCNT3の電圧を上げることで、共振周波数fを入力クロック信号の周波数に追従させることができる。

【0074】

さらに、本実施の形態にかかる効果を示すために、回路シミュレーションによりクロックバッファ回路の動作を検証した。図8は、シミュレーションに用いたクロック分配回路のブロック図である。クロックバッファ回路CBUF1及びCBUF2は、クロックバッファ回路600と同じ構成を有する。

【0075】

クロックバッファ回路CBUF1のクロック入力IN1及びINB1には、クロック信号源CSOURCEが供給される。クロックバッファ回路CBUF1は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUF1のクロック出力OUT1及びOUTB1から、伝送線路TML1を介して、それぞれクロックバッファ回路CBUF2のクロック入力IN2及びINB2へ供給される。クロックバッファ回路CBUF2は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUF2のクロック出力OUT1及びOUTB1から、伝送線路TML2を介して、次の段の回路へ出力される。

【0076】

本シミュレーションでは、クロックバッファ回路CBUF1のクロック出力OUT1及びOUTB1の間、又は、クロック出力OUT2及びOUTB2の間でのクロック信号のタイミングのずれを観測する。本シミュレーションでは、90nmノードのCMOSプロセスのMISFETを使用することを仮定する。電源電圧は1.0Vと仮定する。インダクタ素子は、同じく90nmノードのCMOSプロセスのメタル配線で実現可能なものとし、低周波での直列インダクタンスを2.1nH、直列抵抗を31Ωとする。また、伝送線路もこのプロセスのメタル配線で実現可能なものとし、幅0.5μmかつ長さ1mmのグローバル配線を配線するもと仮定する。なお、可変容量Cvは設けず、容量負荷は伝送線路の寄生容量のみとする。

【0077】

上記の仮定の下、3つの条件についてシミュレーションを行った。第1のシミュレーション条件は、クロック信号源CSOURCEのクロック信号周波数が5GHzであり、制御信号SCNT1〜3が高レベル(すなわち、n型MISトランジスタM5〜M7がオン)の場合である。図9Aは、第1のシミュレーション条件におけるシミュレーション結果を示す信号波形である。クロックバッファ回路CBUF1及びCBUF2は5GHzで共振するように設計されている。そのため、相補信号のそれぞれの波形(クロック出力端子OUT1及びOUTB1における波形、又はクロック出力端子OUT2及びOUTB2における波形)が交わるタイミングのずれは非常に小さく、図9Aに示すように、わずか7psである。

【0078】

第2のシミュレーション条件は、クロック信号源CSOURCEのクロック信号周波数が1GHzであり、制御信号SCNT1〜3が高レベル(すなわち、n型MISトランジスタM5〜M7がオン)の場合である。図9Bは、第2のシミュレーション条件におけるシミュレーション結果を示す信号波形である。前述のように、クロックバッファ回路CBUF1及びCBUF2は5GHzで共振するように設計されている。そのため、クロックバッファ回路CBUF1及びCBUF2は周波数1GHzのクロック信号に対して共振できない。その結果、図9Bに示すように、出力信号の出力振幅が低下してしまう。

【0079】

第3のシミュレーション条件は、クロック信号源CSOURCEのクロック信号周波数が1GHzであり、制御信号SCNT1〜3が低レベル(すなわち、n型MISトランジスタM5〜M7がオフ)の場合である。図9Cは、第3のシミュレーション条件におけるシミュレーション結果を示す信号波形である。この場合、クロックバッファ回路CBUF1及びCBUF2は、単なるインバータ回路となる。そのため、クロックバッファ回路CBUF1及びCBUF2は、クロック信号の周波数が1GHzでも、動作可能となる。このときのタイミングのずれは49psとなり、共振状態の場合(第1のシミュレーション条件)よりも大きくなるが、遅いクロックでは信号タイミングに余裕があるので、クロック信号のタイミングがずれても誤動作は発生しない。

【0080】

従って、クロックバッファ回路600は、広い周波数帯の入力クロック信号に対応することができる。また、可変インダクタのインダクタンス値及び可変容量の容量値を変化させることで、LCタンク部22の共振周波数を変化させることができる。その結果、クロックバッファ回路600は、広い周波数帯の入力クロック信号に対して共振することができる。さらに、クロックバッファ回路600は、必要に応じてLCタンク部22のオン/オフを切り替えることができる。これにより、さらに低周波の入力クロック信号に対応することが可能となる。

【0081】

実施の形態7

続いて、本発明の実施の形態7にかかるクロックバッファ回路について説明する。本実施の形態にかかるクロックバッファ回路は、実施の形態6にかかるクロックバッファ回路600のインダクタ−スイッチ部221を、インダクタ−スイッチ部222に置き換えた構成を有する。本実施の形態にかかるクロックバッファ回路のその他の構成は、クロックバッファ回路600と同様であるので、以下では、インダクタ−スイッチ部222について説明する。

【0082】

図10は、実施の形態7にかかるクロックバッファ回路のインダクタ−スイッチ部222の構成を示す回路図である。インダクタ−スイッチ部222は、固定インダクタ素子Lf1及びLf2、スイッチSW30により構成される。固定インダクタ素子Lf1及びLf2は、それぞれインダクタ−スイッチ部221の可変インダクタLv1及びLv2に対応する。スイッチSW7は、インダクタ−スイッチ部221のn型MISトランジスタM7に対応する。固定インダクタ素子Lf1、スイッチSW7及び固定インダクタ素子Lf2は、クロック出力OUTBとクロック出力OUTとの間に、この順で接続されている。

【0083】

スイッチSW7は、並列接続されたn(nは、2以上の整数)個のn型MISトランジスタM70_1〜M70_nにより構成される。n型MISトランジスタM70_1〜M70_nのゲートには、それぞれ制御信号SCNT7_1〜SCNT7_nが供給される。すなわち、n型MISトランジスタM70_1〜M70_nは、それぞれ制御信号SCNT7_1〜SCNT7_nに応じて開閉するスイッチ素子として機能する。制御信号SCNT7_1〜SCNT7_nは、インダクタ−スイッチ部221のn型MISトランジスタM70に供給される制御信号SCNT3に対応する。なお、n型MISトランジスタM70_1〜M70_nのそれぞれのソース−ドレイン間のオン抵抗は同じでもよいし、互いに異なっていてもよい。

【0084】

n型MISトランジスタM70_1〜M70_nの合成オン抵抗は、n型MISトランジスタM70_1〜M70_nのうちでオン状態となっているものの個数により変化する。すなわち、制御信号SCNT7_1〜SCNT7_nのそれぞれを、独立して高レベル又は低レベルに変化させることで、n型MISトランジスタM70_1〜M70_nの合成オン抵抗を多段階に変化させることができる。これにより、式(2)に示すように、本実施の形態にかかるクロックバッファ回路の共振周波数を変化させることができる。

【0085】

実施の形態8

続いて、本発明の実施の形態8にかかるクロックバッファ回路について説明する。本実施の形態にかかるクロックバッファ回路は、実施の形態6にかかるクロックバッファ回路600のインダクタ−スイッチ部221を、インダクタ−スイッチ部223に置き換えた構成を有する。本実施の形態にかかるクロックバッファ回路のその他の構成は、クロックバッファ回路600と同様であるので、以下では、インダクタ−スイッチ部223について説明する。

【0086】

図11は、実施の形態8にかかるクロックバッファ回路のインダクタ−スイッチ部223の構成を示す回路図である。インダクタ−スイッチ部223は、固定インダクタ素子Lf1_1、Lf1_2、Lf2_1及びLf2_2、n型MISトランジスタM80_1及びM80_2により構成される。インダクタ−スイッチ部223は、スイッチの機能を包摂した可変インダクタとして構成される。インダクタ−スイッチ部223では、n型MISトランジスタM80_1及びM80_2が、それぞれスイッチ素子として動作する。

【0087】

固定インダクタ素子Lf1_2、固定インダクタ素子Lf1_1、n型MISトランジスタM80_1、固定インダクタ素子Lf2_1及びL固定インダクタ素子Lf2_2は、クロック出力OUTBとクロック出力OUTとの間に、この順で接続されている。n型MISトランジスタM80_2は、固定インダクタ素子Lf1_1及びLf1_2間の接続点Cと、固定インダクタ素子Lf2_1及びLf2_2間の接続点Dと、の間に接続される。すなわち、n型MISトランジスタM80_2がオンとなることにより、接続点Cと接続点Dとをバイパスするバイパス経路が構成される。n型MISトランジスタM80_1及びM80_2のゲートには、それぞれ制御信号SCNT8_1及びSCNT8_2が供給される。

【0088】

続いて、インダクタ−スイッチ部223の動作について説明する。制御信号SCNT8_1が高レベル、制御信号SCNT8_2が低レベルの場合、n型MISトランジスタM80_1はオン、n型MISトランジスタM80_2はオフとなる。よって、クロック出力OUT及びOUTB間の直列インダクタンス値は、固定インダクタ素子Lf1_1、Lf1_2、Lf2_1及びLf2_2のインダクタンス値の和となる。

【0089】

制御信号SCNT8_1が低レベル、制御信号SCNT8_2が高レベルの場合、n型MISトランジスタM80_1はオフ、n型MISトランジスタM80_2はオンとなる。よって、クロック出力OUT及びOUTB間の直列インダクタンス値は、固定インダクタ素子Lf1_2及びLf2_2のインダクタンス値の和となる。

【0090】

制御信号SCNT8_1及び制御信号SCNT8_2の両方が高レベルの場合、n型MISトランジスタM80_1及びM80_2は共にオンとなる。この場合、接続点Cと接続点Dとが短絡されるので、固定インダクタ素子Lf1_1及びLf2_1はインダクタとしては機能しない。よって、クロック出力OUT及びOUTB間の直列インダクタンス値は、固定インダクタ素子Lf1_2及びLf2_2のインダクタンス値の和となる。

【0091】

制御信号SCNT8_1及び制御信号SCNT8_2の両方が低レベルの場合、n型MISトランジスタM80_1及びM80_2は共にオフとなる。よって、クロック出力OUT及びOUTB間は、電気的に切断される。

【0092】

以上のとおり、インダクタ−スイッチ部223によれば、制御信号SCNT8_1及び制御信号SCNT8_2により、インダクタンス値の制御とLCタンク部のオン/オフ制御の両方を行なうことができる。

【0093】

なお、図11に示す構成はあくまで例示であり、この例に限定されるものではない。図9では、バイパス経路が1本で場合を示したが、例えば、m(mは2以上の整数)個の固定インダクタ素子Lf1_1〜Lf1_m、m個の固定インダクタ素子Lf1_1〜Lf1_m及びm個のn型MISトランジスタM80_1〜M80_mを設けることも可能である。例えば、n型MISトランジスタM80_1とクロック出力OUTBとの間に、固定インダクタ素子Lf1_1〜Lf1_mがこの順で直列に接続される。n型MISトランジスタM80_1とクロック出力OUTとの間に、固定インダクタ素子Lf2_1〜Lf2_mがこの順で直列に接続される。そして、n型MISトランジスタM80_k(kは、2以上m以下の整数)により、固定インダクタ素子Lf1_(k−1)及びLf1_k間の接続点と、固定インダクタ素子Lf2_(k−1)及びLf2_k間の接続点と、をバイパスすることができる。これにより、クロック出力OUT及びOUTB間の直列インダクタンス値を、より多段階に変化させることが可能となる。その結果、LCタンク部の共振周波数帯をより広げることができる。

【0094】

実施の形態9

続いて、本発明の実施の形態9にかかるクロック分配回路について説明する。本実施の形態にかかるクロック分配回路は、実施の形態1〜8にかかるクロックバッファ回路を用いて構成される。図12は、実施の形態9にかかるクロック分配回路900の構成を示すブロック図である。

【0095】

クロック分配回路900は、クロック信号源CSOURCE、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2により構成される。ここで、実施の形態1〜8にかかるクロックバッファ回路のいずれかが、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2として用いられる。

【0096】

クロックバッファ回路CBUFa1及びCBUFa2は、従属接続される。同様に、クロックバッファ回路CBUFb1及びCBUFb2も、従属接続される。クロック信号源CSOURCEからのクロック信号は、クロックバッファ回路CBUFa1のクロック入力端子INa1及びINBa1と、クロックバッファ回路CBUFb1のクロック入力端子INb1及びINBb1と、に供給される。

【0097】

クロックバッファ回路CBUFa1は、供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFa1のクロック出力端子OUTa1及びOUTBa1から、それぞれクロックバッファ回路CBUFa2のクロック入力端子INa2及びINBa2へ供給される。クロックバッファ回路CBUFa2は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFa2のクロック出力端子OUTa2及びOUTBa2から、次の段の回路へ出力される。

【0098】

クロックバッファ回路CBUFb1は、供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFb1のクロック出力端子OUTb1及びOUTBb1から、それぞれクロックバッファ回路CBUFb2のクロック入力端子INb2及びINBb2へ供給される。クロックバッファ回路CBUFb2は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFb2のクロック出力端子OUTb2及びOUTBb2から、次の段の回路へ出力される。

【0099】

また、クロック分配回路900の外部からは、クロック分配回路の動作周波数に対応する制御信号CONTが供給される。制御信号CONTは、クロック分配回路900の外部に配置された制御回路(不図示)などによって生成される。制御信号CONTは、クロック信号源CSOURCE及びクロックバッファ回路のそれぞれへ供給される。例えば、制御信号CONTは、図6に示すクロックバッファ回路600の制御信号SCNT1〜3に相当する。このように、制御信号CONTは複数の信号により構成される場合があるが、図面を簡略化するため、図12では、制御信号CONTを1本の信号線により表示している。

【0100】

クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれでは、制御信号(すなわち、クロック信号の周波数)に応じて、内部のトランスファゲート回路、可変インダクタ、可変容量の状態が変化する。これにより、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれを、常に入力されるクロック信号の周波数に対応した回路状態に設定することができる。

【0101】

上述のように、クロック分配回路900は、実施の形態1〜8のいずれかにかかるクロックバッファ回路により構成される。よって、クロック分配回路900は、広い周波数帯のクロック信号に対応することが可能である。例えば、クロック分配回路900は、高周波の入力クロック信号の周波数が変動する場合には、LCタンク部のインダクタ値及び容量値のいずれか一方又は両方を調整することにより、共振周波数を入力クロック信号の周波数にチューニングすることができる。また、スイッチを操作することにより、ドライバ部をインバータ回路として動作させ、LCタンク部をオン/オフ制御できる。これにより、共振周波数とは大幅に周波数が異なる低周波のクロック信号にも対応することができる。つまり、低周波のテストクロック信号などにも対応することが可能となる。

【0102】

従って、クロック分配回路900は、同一のクロックバッファ回路を用いることができる。これにより、クロック分配回路900を共通化できるとともに、クロックバッファ回路及びインバータ回路の両方を設ける必要がない。その結果、従来のクロック分配回路と比べて、回路規模を小さくすることが可能となる。

【0103】

さらに、クロック分配回路900は、従来のクロック分配回路と比べて、消費電力を抑制することも可能である。以下では、クロック分配回路900における消費電力の抑制について説明する。クロック分配回路900は、クロックバッファ回路及びインバータ回路の両方を設ける必要はない。従来の共振型クロック分配回路では、幅広い周波数のクロックで動作するには共振型クロック分配回路と並列にインバータ回路を配置して、両者の出力をスイッチで切り替える必要があった。しかし、本実施の形態では、従来のクロック分配回路と異なり、クロックバッファ回路及びインバータ回路の出力側にスイッチを設ける必要が無い。一般に、クロックバッファ回路及びインバータ回路の出力側における信号は、入力側における信号よりも振幅が大きい。そのため、出力側に設けられたスイッチにおける損失は、入力側のスイッチにおける損失比べて大きくなる。

【0104】

これに対し、クロック分配回路900で用いられる実施の形態1〜8のいずれかにかかるクロックバッファ回路は、入力側にスイッチが設けられる。実施の形態1〜4、6〜8にかかるクロックバッファ回路では、スイッチSW1及びSW2が入力(クロック入力IN及びINB)側に設けられたスイッチに相当する。実施の形態5にかかるクロックバッファ回路では、スイッチSW4が入力(クロック入力IN)側に設けられたスイッチに相当する。

【0105】

つまり、クロック分配回路900では、クロックバッファ回路の入力側にのみスイッチが設けられた構成を有する。従って、クロック分配回路900は、従来のクロック分配回路よりも消費電力を抑制することが可能となる。

【0106】

実施の形態10

続いて、本発明の実施の形態10にかかるクロック分配回路について説明する。本実施の形態にかかるクロック分配回路は、実施の形態9にかかるクロック分配回路900の変形例である。図13は、実施の形態10にかかるクロック分配回路1000の構成を示すブロック図である。

【0107】

クロック分配回路1000は、クロック分配回路1000は、クロック分配回路900と比べて、周波数検出回路DETa1、DETa2、DETb1及びDETb2が追加された構成を有する。

【0108】

周波数検出回路DETa1は、クロックバッファ回路CBUFa1のクロック入力端子INa1及びINBa1に入力されるクロック信号の周波数を検出する。そして、検出した周波数に応じた制御信号CONTa1を、クロックバッファ回路CBUFa1へ出力する。

【0109】

同様に、周波数検出回路DETa2、DETb1及びDETb2は、クロックバッファ回路CBUFa2のクロック入力端子INa2及びINBa2、クロックバッファ回路CBUFb1のクロック入力端子INb1及びINBb1、クロックバッファ回路CBUFb2のクロック入力端子INb2及びINBb2のそれぞれに入力されるクロック信号の周波数を検出する。そして、検出した周波数に応じた制御信号CONTa2、CONTb1及びCONTb2を、それぞれクロックバッファ回路CBUFa2、CBUFb1及びCBUFb2へ出力する。クロック分配回路1000のその他の構成は、クロック分配回路900と同様であるので説明を省略する。

【0110】

続いて、周波数検出回路DETa1、DETa2、DETb1及びDETb2について説明する。以下では、高周波検出回路である周波数検出回路DETH及び低周波検出回路である周波数検出回路DETLを例として説明する。

【0111】

高周波検出回路である周波数検出回路DETHについて説明する。周波数検出回路DETHは、特定の周波数よりも高い周波数の信号がクロック入力INに入力されると、クロック出力OUTが高レベルとなる回路である。図14は、実施の形態10にかかる周波数検出回路DETHの構成例を示す回路図である。周波数検出回路DETHは、図14に示すように、高域通過フィルタHPF及びピーク検出回路PKにより構成される。

【0112】

高域通過フィルタHPFは、抵抗RH及び容量CHにより構成される。容量CHは、クロック入力INとノードVHPとの間に接続される。抵抗RHは、ノードVHPと接地端子との間に接続される。

【0113】

ピーク検出回路PKは、オペアンプOAMP、ダイオードD1、抵抗RP及び容量CPにより構成される。オペアンプOAMPの非反転入力は、ノードVHPと接続される。オペアンプOAMPの出力と出力OUTcとの間には、ダイオードD1が順方向で挿入される。オペアンプOAMPの非反転入力は、ダイオードD1のカソードと接続される。また、出力OUTc及びダイオードD1のアノードと接地端子との間には、抵抗RP及び容量CPが並列に接続される。

【0114】

周波数検出回路DETHは、1/CHRH以上の周波数の信号が入力されると、ノードVHPでの信号振幅は、入力信号と同程度の大きさとなる。一方、それ以下の周波数では、ノードVHPでの信号振幅は小さくなる。このような振幅を有する信号をピーク検出回路PKに入力すると、ピーク検出回路PKは、信号振幅の最大値に相当する電圧を、出力OUTcから出力する。よって、ピーク検出回路PKは、1/CHRH以上の周波数の信号が入力される場合には高レベル、それ以下の周波数の信号が入力される場合には低レベルの電圧を出力する。

【0115】

次いで、低周波検出回路である周波数検出回路DETLについて説明する。周波数検出回路DETLは、特定の周波数よりも低い周波数の信号がクロック入力INに入力されると、クロック出力OUTが高レベルとなる回路である。図15は、実施の形態10にかかる周波数検出回路DETLの構成例を示す回路図である。周波数検出回路DETLは、図15に示すように、低域通過フィルタLPF及びピーク検出回路PKにより構成される。ピーク検出回路PKは、周波数検出回路DETHと同様であるので、説明を省略する。

【0116】

低域通過フィルタLPFは、抵抗RL及び容量CLにより構成される。容量CLは、ノードVLPと接地端子との間に接続される。抵抗RLは、クロック入力INとノードVLPとの間に接続される。

【0117】

周波数検出回路DETLは、1/CLRL以下の周波数の信号が入力されると、ノードVLPでの信号振幅は、入力信号と同程度の大きさとなる。一方、それ以上の周波数では、ノードVLPでの信号振幅は小さくなる。このような振幅を有する信号をピーク検出回路PKに入力すると、ピーク検出回路PKは、信号振幅の最大値に相当する電圧を、出力OUTcから出力する。よって、ピーク検出回路PKは、1/CLRL以上の周波数の信号が入力される場合には高レベル、それ以下の周波数の信号が入力される場合には低レベルの電圧を出力する。

【0118】

クロック分配回路1000では、制御信号CONTa1、CONTa2、CONTb1及びCONTb2は、クロック信号の周波数に対応する信号である。例えば、制御信号CONTは、図6に示すクロックバッファ回路600の制御信号SCNT1〜3に相当する。このように、制御信号CONTa1、CONTa2、CONTb1及びCONTb2は複数の信号により構成される場合があるが、図面を簡略化するため、図13では、制御信号CONTa1、CONTa2、CONTb1及びCONTb2をそれぞれ1本の信号線により表示している。

【0119】

クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれでは、制御信号(すなわち、クロック信号の周波数)に応じて、内部のトランスファゲート回路、可変インダクタ、可変容量の状態が変化する。これにより、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれを、常に入力されるクロック信号の周波数に対応した回路状態に設定することができる。したがって、クロック分配回路1000は、クロック分配回路900と同様の動作を行うことができ、同様の効果を奏する。

【0120】

また、クロック分配回路900では、クロック信号源CSOURCEからクロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれへ、制御信号CONTを供給しなければならない。そのため、複数の長い信号線を設ける必要がある。これに対し、クロック分配回路1000によれば、こうした信号線を設ける必要がないので、より高密度に素子を集積することが可能となる。

【0121】

なお、本実施の形態では、各クロックバッファ回路に対応する周波数検出回路が設けられる場合について説明したが、回路構成はこの例に限られない。例えば、複数のクロックバッファ回路が1つの周波数検出回路を共有し、共有する1つの周波数検出回路からの制御信号を、複数のクロックバッファ回路が受け取る構成とすることもできる。

【0122】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、実施の形態5に係るクロックバッファ回路500は、シングルエンドの入力クロック信号に対応するものであるが、実施の形態1〜4及び6〜8に係る差動クロック信号に対応するクロックバッファ回路と同様の構成転換を行うことが可能である。例えば、クロックバッファ回路500のスイッチSW5を除去した構成とることが可能である。また、クロックバッファ回路500の可変インダクタLvは固定インダクタに置き換えることができる。クロックバッファ回路500の可変インダクタCvは固定容量に置き換えることができる。さらに、クロックバッファ回路500のインダクタスイッチ部(スイッチSW5及び可変インダクタLv)を、実施の形態6〜7にかかるインダクタ−スイッチ部221〜223に置き換えることが可能である。この際、クロック出力OUTと接地端子GNDとの間に、インダクタ−スイッチ部221〜223を配置すればよい。

【0123】

実施の形態9及び10にかかるクロック分配回路900及び100では、クロックバッファ回路が2段従属接続されている例について説明したが、従属接続数はこの例に限られない。すなわち、3以上の任意の個数のクロックバッファ回路を従属接続する構成とすることが可能である。

【0124】

また、上述の実施の形態にかかるクロックバッファ回路は、それ自身が発振器として機能する。従って、例えば実施の形態9及び10にかかるクロック分配回路900及び100では、クロック信号源CSOURCEを、実施の形態1〜8にかかるクロックバッファ回路とすることも可能である。

【符号の説明】

【0125】

11、15 ドライバ部

21〜25 LCタンク部

61 電源回路

70 スイッチ部

100、200、300、400、500、600 クロックバッファ回路

181 PLL

191 インバータ部

192 タンク部

221〜223 インダクタ−スイッチ部

900、1000、1600 クロック分配回路

1700 H型クロック分配回路

1800 PLL回路

1900 共振回路

A、B、E、F 端子

C、D 接続点

CBUF1、CBUF2、CBUFa1、CBUFa2、CBUFb1、CBUFb2 クロックバッファ回路

Cf 固定容量

CH、CL、CP 容量

CONT、CONTa1、CONTa2、CONTb1、CONTb2 制御信号

CSOURCE クロック信号源

Cs キャパシタ

Cv 可変容量

D1 ダイオード

DETa1、DETa2、DETb1、DETb2、DETH、DETL 周波数検出回路

GND 接地端子

HPF 高域通過フィルタ

IN、INB クロック入力

IN1、IN2、INa1、INa2、INb1、INb2 クロック入力端子

INV、INV1〜INV4、INV191、INV192 インバータ

IREF 端子

Lf 固定インダクタ

Lf1、Lf2、Lf1_1〜Lf1_m、Lf2_1〜Lf2_m 固定インダクタ素子

LPF 低域通過フィルタ

Ls インダクタ

Lv、Lv1、Lv2 可変インダクタ

M1、M3、M5〜M7、M70_1〜M70_n、M80_1〜M80_m n型MISトランジスタ(MISFET)

M2、M4、M8、M9 p型MISトランジスタ(MISFET)

Mv1、Mv2 スイッチ

OAMP オペアンプ

OUT、OUTB クロック出力

OUT1、OUT2、OUTa1、OUTa2、OUTb1、OUTb2 クロック出力端子

OUTc 出力

PK ピーク検出回路

RH、RL、RP 抵抗

SCNT1〜SCNT4、SCNT7_1〜SCNT7_n、SCNT8_1、SCNT8_2 制御信号

SW1〜SW5、SW7 スイッチ

TML1、TML2 伝送線路

VHP、VLP ノード

【技術分野】

【0001】

本発明は、クロックバッファ回路及びこれを用いたクロック分配回路に関し、特に広帯域のクロック信号に対応するクロックバッファ回路及びこれを用いたクロック分配回路に関する。

【背景技術】

【0002】

近年、MISFET(Metal-Insulator-Semiconductor Field-Effect Transistor)の微細化と共に、クロック信号の周波数が向上している。そのため、高性能プロセッサなどの高周波回路では、数GHzの周波数を有するクロック信号が一般的に用いられる。このような高周波回路では、回路全体がクロック信号に同期して動作するので、チップ内部でのクロックタイミングのずれ(クロックスキュー)が大きな問題となる。

【0003】

高周波回路を搭載するチップ内部には、高周波回路にクロック信号を分配するクロック分配回路が搭載される。図16は、従来のクロック分配回路1600の構成例を示すブロック図である。図16に示すように、クロック分配回路1600は、クロック信号源CSOURCE及び複数のインバータINVにより構成される。インバータINVは、クロック信号源CSOURCEと回路ブロックとの間に挿入され、クロックバッファ回路として機能する。つまり、クロック信号は、クロック信号源CSOURCEから、数段のインバータINVを介して、各回路ブロックに供給される。クロック信号源CSOURCEは、クロック分配回路1600と同一チップ上に、又は、別のチップ上に配置される。チップ全体にクロック信号を供給する場合、クロック信号配線やインバータINVでの信号遅延は、回路ブロック毎に異なる。このため、クロック分配回路1600では、回路ブロック毎にクロックスキューが発生するという問題があった。クロックスキューが発生すると、回路ブロック間で信号のやりとりをする際にタイミングがずれてしまうので、誤動作の原因となる。

【0004】

これを解決する方法として、回路レイアウトを利用したH型クロック分配回路が提案されている。図17は、一般的なH型クロック分配回路1700の構成例を示すブロック図である。H型クロック分配回路1700は、クロック信号源CSOURCEから各回路ブロックまでのクロック配線長及びインバータINVの段数を等しくすることにより、タイミングずれを抑制する。しかし、実際の回路では、回路ブロックが完全に対称に配置されるわけではなく、理想的なH型クロック分配を実現することは困難である。

【0005】

また、H型クロック分配回路の他に、能動的にクロックスキューを調整する方法として、PLL(Phase Locked Loop)回路をクロックバッファ回路として用いる手法もある。図18は、PLLを用いてクロックスキューを低減する場合のPLL回路1800の構成例を示すブロック図である。図18に示すように、PLL回路1800は、PLL181及び1個以上のインバータINVにより構成される。クロック信号は、クロック入力INからPLL181へ供給される。PLL181の出力と端子Eとの間には、1個以上のインバータINVが挿入される。端子Eにおけるクロック信号は、PLL181にフィードバックされる。PLL181は、端子Eにおけるクロック信号の位相と端子Fにおけるクロック信号の位相とを揃えるように位相制御を行なう。その結果、端子Eと端子Fとの間のクロックスキューを低減できる。しかし、この手法ではクロックスキューを小さくできるものの、PLL181による消費電力の増大やチップ面積の増大を招くという問題があった。

【0006】

さらに、上述の手法とは異なるクロックスキュー抑制方法として、共振クロックが提案されている(例えば、非特許文献1又は2)。この手法では、インバータの代わりに、LC共振回路をクロックバッファ回路として用いる。図19は、典型的なLC共振回路1900の一例を示すブロック図である。LC共振回路1900は、インバータ部191及びLCタンク部192により構成される。インバータ部191は、インバータINV191及びINV192により構成される。インバータINV191及びINV192は、MISFETにより構成される。インバータINV191の入力はクロック入力INBと接続され、出力はクロック入力INと接続される。インバータINV192の入力はクロック入力INと接続され、出力はクロック入力INBと接続される。LCタンク部192は、クロック出力OUT及びOUTBの間に並列に接続された、インダクタLs及びキャパシタCsで構成される。

【0007】

このLC共振回路1900のクロック入力IN及びINBには、外部からクロック信号が入力される。このときLC共振回路1900(LCタンク部192)の発振周波数と外部クロック周波数とが近い場合には、注入同期(インジェクションロック)が起こる。その結果、LC共振回路1900の発振周波数は、外部クロック周波数に同期する。

【0008】

図16に示すクロック分配回路1600は、入力信号を単純に増幅して出力するので、入力と出力との間には遅延が発生する。一方、このLC共振回路1900では、LC共振回路1900自身が発振器としてクロック信号を発生させる。従って、図18に示すPLL回路1800と同様に、入力(外部からのクロック信号)に対して位相が同期するように動作(注入同期)する。その結果、クロックスキューを抑制することができる。また、LC共振回路1900は、インダクタとキャパシタで電力を蓄積して回生させることができるので、インバータのみを用いた回路よりも低電力で駆動できる。さらに、PLLのような位相制御回路も必要ないので、PLLで消費される電力を低減できる。

【先行技術文献】

【非特許文献】

【0009】

【非特許文献1】Frank O'Mahony et al., "A 10-GHz Global Clock Distribution Using Coupled Standing-Wave Oscillators", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.38, NO.11, NOVEMBER 2003, pp.1813-1820.

【非特許文献2】John Wood et al., "Multi-GigaHertz Low-Power Low-Skew Rotary Clock Scheme", 2001 IEEE International Solid-State Circuits Conference, SESSION25, CLOCK GENERATION AND DISTRIBUTION, 25.5.

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかし、発明者は上述の手法では以下のような問題が有ることを見出した。近年のロジック回路では、低電力化を実現するため、複数のクロック周波数に対応することが求められる。また、テストを行う際に低周波のクロック信号が用いられる場合が有るので、このような低周波のテストクロック信号にも対応することが求められる。

【0011】

ところが、図19に示すようなLC共振回路は、外部から供給されるクロック信号の周波数が共振周波数からずれてしまうと、クロック信号を適切に増幅することができない。従って、複数のクロック周波数に対応することは困難である。加えて、LC共振回路は、高周波クロック信号の増幅には適しているものの、テストに用いられるような低周波クロック信号を増幅することが困難である。つまり、図19に示すようなLC共振回路では、広帯域のクロックバッファ回路を実現することはできない。その結果、LC共振回路を用いて、複数のクロック周波数に対応できるクロック分配回路を構成することもできない。

【0012】

これに対し、高周波クロック信号をLC共振回路で増幅し、低周波クロック信号をインバータ回路で増幅する手法が考え得る。この場合、LC共振回路及びインバータ回路にクロック信号を供給し、LC共振回路及びインバータ回路の出力側に設けたスイッチをクロック信号の周波数に応じて切り換えることにより、好適に増幅されたクロック信号を供給することができる。しかしながら、この手法では、LC共振回路及びインバータ回路の両方をクロック分配回路に設けなくてはならないので、回路構造が複雑化し、回路面積の増大を招いてしまう。

【0013】

すなわち、従来の手法によっては、広帯域のクロック信号に対応した省面積のクロックバッファ回路及びクロック分配回路を実現することはできなかった。

【課題を解決するための手段】

【0014】

本発明の一態様であるクロックバッファ回路は、クロック入力からの入力クロック信号の少なくとも正転出力を、クロック出力へ出力するドライバ部と、前記ドライバ部とクロック出力との間に配置されたLCタンク部と、を備え、前記ドライバ部は、入力クロック信号の周波数に対応した制御信号に応じて、当該ドライバ部の入力と出力とを短絡させるスイッチを備えるものである。

【0015】

本発明の一態様であるクロックバッファ回路によれば、クロック信号の周波数に応じて、クロックバッファ回路の動作を、高周波の入力クロックに対応した共振回路としての動作、又は、低周波の入力クロックに対応したインバータ回路としての動作に切り換えることが可能である。これにより、単一のクロックバッファ回路により、広い周波数帯のクロック信号に対応することが可能である。

【発明の効果】

【0016】

本発明によれば、小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供することができる。

【図面の簡単な説明】

【0017】

【図1】実施の形態1にかかるクロックバッファ回路100の構成を示すブロック図である。

【図2】実施の形態2にかかるクロックバッファ回路200の構成を示すブロック図である。

【図3】実施の形態3にかかるクロックバッファ回路300の構成を示すブロック図である。

【図4】実施の形態4にかかるクロックバッファ回路400の構成を示すブロック図である。

【図5】実施の形態5にかかるクロックバッファ回路500の構成を示すブロック図である。

【図6】実施の形態6にかかるクロックバッファ回路600の構成を示すブロック図である。

【図7】可変インダクタの構成例を示す回路図である。

【図8】実施の形態6におけるシミュレーションに用いたクロック分配回路のブロック図である。

【図9A】実施の形態6における第1のシミュレーション条件におけるシミュレーション結果を示す信号波形である。

【図9B】実施の形態6における第2のシミュレーション条件におけるシミュレーション結果を示す信号波形である。

【図9C】実施の形態6における第3のシミュレーション条件におけるシミュレーション結果を示す信号波形である。

【図10】実施の形態7にかかるクロックバッファ回路のインダクタ−スイッチ部の構成を示す回路図である。

【図11】実施の形態8にかかるクロックバッファ回路のインダクタ−スイッチ部の構成を示す回路図である。

【図12】実施の形態9にかかるクロック分配回路900の構成を示すブロック図である。

【図13】実施の形態10にかかるクロック分配回路1000の構成を示すブロック図である。

【図14】実施の形態10にかかる周波数検出回路の構成例を示す回路図である。

【図15】実施の形態10にかかる周波数検出回路の構成例を示す回路図である。

【図16】従来のクロック分配回路1600の構成例を示すブロック図である。

【図17】一般的なH型クロック分配回路1700の構成例を示すブロック図である。

【図18】PLL回路1800の構成例を示すブロック図である。

【図19】LC共振回路1900の一例を示すブロック図である。

【発明を実施するための形態】

【0018】

以下、図面を参照して本発明の実施の形態について説明する。各図面においては、同一要素には同一の符号が付されており、必要に応じて重複説明は省略される。

【0019】

実施の形態1

まず、本発明の実施の形態1にかかるクロックバッファ回路について説明する。図1は、実施の形態1にかかるクロックバッファ回路100の構成を示すブロック図である。クロックバッファ回路100は、図1に示すように、クロック入力IN及びINBとクロック出力OUT及びOUTBとの間に、ドライバ部11及びLCタンク部21が配置される。クロック入力IN及びINBには、差動クロック信号が入力される。クロック出力OUT及びOUTBからは、差動クロック信号が出力される。

【0020】

ドライバ部11は、インバータINV1及びINV2、スイッチSW1及びSW2により構成される。スイッチSW1は、クロック入力INとクロック出力OUTとの間に接続される。スイッチSW2は、クロック入力INBとクロック出力OUTBとの間に接続される。インバータINV1は、クロック入力INBとクロック出力OUTとの間に接続され、クロック入力INBに入力されるクロック信号の反転信号をクロック出力OUTへ出力する。インバータINV2は、クロック入力INとクロック出力OUTBとの間に接続され、クロック入力INに入力されるクロック信号の反転信号を、クロック出力OUTBへ出力する。

【0021】

LCタンク部21は、可変インダクタLv及び可変容量Cvにより構成される。可変インダクタLv及び可変容量Cvは、クロック出力OUT及びOUTBの間に、並列に接続される。なお、可変インダクタLvは、固定インダクタとしてもよい。可変容量Cvは、固定容量としてもよい。

【0022】

続いて、クロックバッファ回路100の動作について説明する。ドライバ部11のスイッチSW1及びSW2がオンである場合には、クロックバッファ回路100は、図16に示すLC共振回路1600と等価の回路となる。よって、クロックバッファ回路100は、入力クロック信号に対して注入同期し、入力クロック信号の周波数で共振する。つまり、クロックバッファ回路100は、入力クロック信号に同期して信号を増幅するバッファ回路として動作する。クロック入力IN及びINBに入力されたクロック信号は増幅される。増幅されたクロック信号は、それぞれクロック出力OUT及びOUTBから出力クロック信号として出力される。その結果、クロックバッファ回路100のクロックスキューを低減できる。

【0023】

また、クロックバッファ回路100では、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値は可変である。よって、入力クロック信号の周波数がある程度変化しても、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値を調整することにより、入力クロック信号に追従することができる。可変インダクタLvのインダクタンス値及び可変容量Cvの容量値の調整は、外部に設けられた制御回路(不図示)などから、可変インダクタLv及び可変容量Cvへ、制御信号を供給することにより実現できる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。これにより、クロックバッファ回路100は、例えば最大周波数の1/4倍〜1倍の周波数帯において共振が可能となる。

【0024】

ドライバ部11のスイッチSW1及びSW2がオフである場合には、ドライバ部11は、インバータ回路となる。クロック入力IN及びINBに入力されたクロック信号は増幅される。増幅されたクロック信号は、それぞれクロック出力OUT及びOUTBから出力クロック信号として出力される。よって、入力クロック信号の周波数がLCタンク部21の共振周波数に対して約1/4以下である場合でも、クロックバッファ回路100が動作できる。この場合、クロックスキュー低減の効果は発揮されないが、入力クロック信号の周波数が低いので、クロックスキューは問題とはならない。その結果、クロックバッファ回路100は、低周波数の入力クロック信号を増幅できる。

【0025】

すなわち、クロックバッファ回路100は、スイッチSW1及びSW2により、ドライバ部11の動作を切り換えることができる。これにより、クロックバッファ回路100の動作を、共振回路としての動作又はインバータ回路としての動作に切り換えることが可能である。なお、クロックバッファ回路100は、いずれの場合でも、入力クロック信号の正転出力を、出力クロック信号として出力する。

【0026】

なお、スイッチSW1及び2は、外部に設けられた制御回路(不図示)などから、制御信号が供給されることにより開閉することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0027】

従って、クロックバッファ回路100は、広い周波数帯の入力クロック信号に対応することができる。また、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値を変化させることで、LCタンク部21の共振周波数を変化させることができる。その結果、クロックバッファ回路100は、広い周波数帯の入力クロック信号に対して共振することができる。

【0028】

実施の形態2

次に、本発明の実施の形態2にかかるクロックバッファ回路について説明する。図2は、実施の形態2にかかるクロックバッファ回路200の構成を示すブロック図である。クロックバッファ回路200は、図2に示すように、実施の形態1にかかるクロックバッファ回路100のLCタンク部21をLCタンク部22に置き換えた構成を有する。LCタンク部22は、クロック出力OUT及びOUTBの間で、可変インダクタLvに対して直列に接続されるスイッチSW3を有する。なお、図2に示すスイッチSW3の接続位置は単なる例示であり、例えば、可変インダクタLv及びスイッチSW3の位置を入れ換えてもよい。クロックバッファ回路200のその他の構成は、クロックバッファ回路100と同様であるので、説明を省略する。

【0029】

続いて、クロックバッファ回路100の動作について説明する。ドライバ部11のスイッチSW1及びSW2、LCタンク部22のスイッチSW3がオンである場合には、クロックバッファ回路200は、図16に示すLC共振回路と等価の回路となる。よって、クロックバッファ回路200は、クロックバッファ回路100と同様に、入力クロック信号に同期して信号を増幅するバッファ回路として動作する。その結果、クロックバッファ回路200のクロックスキューを低減できる。

【0030】

ドライバ部11のスイッチSW1及びSW2がオフ、LCタンク部22のスイッチSW3がオンである場合には、クロックバッファ回路200は、インバータ回路となる。よって、クロックバッファ回路200は、クロックバッファ回路100と同様に、低周波数の入力クロック信号を増幅できる。

【0031】

ドライバ部11のスイッチSW1及びSW2、LCタンク部22のスイッチSW3がオフである場合には、出力クロック信号の短絡経路が切断され、可変インダクタLvには貫通電流が流れない。この場合、LCタンク部22はLC共振器として機能しない。すなわち、クロックバッファ回路200は、必要に応じてLCタンク部22のオン/オフを切り替えることができる。これにより、さらに低周波の入力クロック信号に対応することが可能となる。

【0032】

また、可変インダクタLvには貫通電流が流れないので、入力クロック信号を停止した場合に、出力クロック信号の出力を速やかに停止することが可能となる。

【0033】

なお、スイッチSW3は、外部に設けられた制御回路(不図示)などから、制御信号が供給されることにより開閉することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0034】

実施の形態3

次に、本発明の実施の形態3にかかるクロックバッファ回路について説明する。図3は、実施の形態3にかかるクロックバッファ回路300の構成を示すブロック図である。クロックバッファ回路300は、図3に示すように、実施の形態2にかかるクロックバッファ回路200のLCタンク部22を、LCタンク部23に置き換えたものである。

【0035】

LCタンク部23は、LCタンク部22における可変インダクタLv及び可変容量Cvを、それぞれ固定インダクタLf及び固定容量Cfに置き換えたものである。クロックバッファ回路300のその他の構成は、クロックバッファ回路200と同様であるので、説明を省略する。

【0036】

クロックバッファ回路300は、LCタンク部23の共振周波数を調整できないことを除き、クロックバッファ回路200と同様の動作が可能である。従って、クロックバッファ回路300によれば、広い周波数帯の入力クロック信号に対応可能な、低消費電力のクロックバッファ回路を実現することができる。

【0037】

実施の形態4

次に、本発明の実施の形態4にかかるクロックバッファ回路について説明する。図4は、実施の形態4にかかるクロックバッファ回路400の構成を示すブロック図である。クロックバッファ回路400は、図4に示すように、実施の形態2にかかるクロックバッファ回路200のLCタンク部22を、LCタンク部24に置き換えたものである。

【0038】

LCタンク部24は、LCタンク部22における可変容量Cvを除去した構成を有する。クロックバッファ回路400は、取り除いた可変容量Cvを、配線の寄生容量及びクロックバッファ回路400に接続される負荷の容量で代替するものである。なお、可変インダクタLvは、固定インダクタとしてもよい。クロックバッファ回路400のその他の構成は、クロックバッファ回路200と同様であるので、説明を省略する。

【0039】

つまり、クロックバッファ回路400は、クロックバッファ回路200と同様に動作することが可能である。従って、クロックバッファ回路400によれば、広い周波数帯の入力クロック信号に対応可能な、低消費電力のクロックバッファ回路を実現することができる。

【0040】

実施の形態5

次に、本発明の実施の形態5にかかるクロックバッファ回路について説明する。図5は、実施の形態5にかかるクロックバッファ回路500の構成を示すブロック図である。クロックバッファ回路500は、図5に示すように、シングルエンド信号である入力クロック信号が供給される。クロックバッファ回路500は、ドライバ部15及びLCタンク部25により構成される。

【0041】

ドライバ部15は、インバータINV3及びINV4、スイッチSW4により構成される。インバータINV3の入力はクロック入力INと接続され、出力はインバータINV4の入力と接続される。インバータINV4の出力はクロック出力OUTと接続される。スイッチSW4は、インバータINV3の入力とインバータINV4の出力との間に接続される。

【0042】

LCタンク部25は、可変インダクタLv、可変容量Cv及びスイッチSW5により構成される。可変インダクタLv及び可変容量Cvは、クロック出力OUTと接地端子との間に、並列に接続される。なお、可変インダクタLvは、固定インダクタとしてもよい。可変容量Cvは、固定容量としてもよい。スイッチSW5は、クロック出力OUTと接地端子との間で、可変インダクタLvに対して直列に接続される。なお、図5に示すスイッチSW5の接続位置は単なる例示であり、例えば、可変インダクタLv及びスイッチSW5の位置を入れ換えてもよい。

【0043】

続いて、クロックバッファ回路500の動作について説明する。ドライバ部15のスイッチSW4及びLCタンク部25のスイッチSW5がオンである場合には、クロックバッファ回路500は、入力クロック信号に対して注入同期し、入力クロック信号の周波数で共振する。つまり、クロックバッファ回路400は、入力クロック信号に同期して信号を増幅するバッファ回路として動作する。その結果、クロックバッファ回路400のクロックスキューを低減できる。

【0044】

また、クロックバッファ回路400では、図1に示すクロックバッファ回路100と同様に、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値は可変である。よって、入力クロック信号の周波数がある程度変化しても、可変インダクタLvのインダクタンス値及び可変容量Cvの容量値を調整することにより、入力クロック信号に追従することができる。可変インダクタLvのインダクタンス値及び可変容量Cvの容量値の調整は、外部に設けられた制御回路(不図示)などから、可変インダクタLv及び可変容量Cvへ、制御信号を供給することにより実現できる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。これにより、クロックバッファ回路400は、例えば最大周波数の1/4倍〜1倍の周波数でも共振が可能となる。

【0045】

ドライバ部15のスイッチSW4がオフ、LCタンク部25のスイッチSW5がオンである場合には、ドライバ部15は、インバータINV3及びINV4からなる正論理のバッファ回路となる。従って、より低い入力クロック信号を増幅することができる。クロックバッファ回路500の動作を、共振回路としての動作又はインバータ回路としての動作に切り換えることが可能である。なお、クロックバッファ回路500は、いずれの場合でも、入力クロック信号の正転出力を、出力クロック信号として出力する。

【0046】

ドライバ部15のスイッチSW4及びLCタンク部25のスイッチSW5がオフである場合には、可変インダクタLvに貫通電流が流れないので、LCタンク部25はLC共振器として機能しない。すなわち、クロックバッファ回路500は、必要に応じてLCタンク部25のオン/オフを切り替えることができる。これにより、さらに低周波の入力クロック信号に対応することが可能となる。

【0047】

また、可変インダクタLvには貫通電流が流れないので、入力クロック信号を停止した場合に、出力クロック信号の出力を速やかに停止することが可能となる。

【0048】

よって、クロックバッファ回路500によれば、広い周波数帯の入力クロック信号に対応できる低消費電力のクロックバッファ回路を提供することができる。

【0049】

実施の形態6

続いて、本発明の実施の形態6にかかるクロックバッファ回路について説明する。図6は、実施の形態6にかかるクロックバッファ回路600の構成を示す回路図である。クロックバッファ回路600は、実施の形態2にかかるクロックバッファ回路200を具体的な回路により構成したものである。

【0050】

電源回路61は、カレントミラー回路を構成するp型MISトランジスタ(MISFET)M8及びM9を有する。p型MISトランジスタM8及びM9のソースは、電源端子と接続される。p型MISトランジスタM8のドレインは、端子IREF、p型MISトランジスタM8及びM9のゲートと接続される。p型MISトランジスタM9のドレインは、ドライバ部11と接続される。これにより、電源回路61は、端子IREFに流れる基準電流の電流値に比例する電流値の電流を、ドライバ部11に供給する。

【0051】

ドライバ部11は、n型MISトランジスタ(MISFET)M1、M3、M5及びM6、p型MISトランジスタ(MISFET)M2及びM4により構成される。n型MISトランジスタM3とp型MISトランジスタM4とは、図2に示すインバータINV1に対応するインバータを構成する。n型MISトランジスタM1とp型MISトランジスタM2とは、図2に示すインバータINV2に対応するインバータを構成する。また、n型MISトランジスタM5は、図2のスイッチSW1に対応し、トランスファゲートとして機能する。n型MISトランジスタM6は、図2のスイッチSW2に対応し、トランスファゲートとして機能する。

【0052】

p型MISトランジスタM2のソースは、電源回路61のp型MISトランジスタM9のドレインと接続される。p型MISトランジスタM2のドレインは、n型MISトランジスタM1のドレインと接続される。n型MISトランジスタM1のソースは、接地端子と接続される。インバータINV2の入力であるn型MISトランジスタM1及びp型MISトランジスタM2のゲートは、クロック入力INと接続される。インバータINV2の出力であるn型MISトランジスタM1のドレインとp型MISトランジスタM2のドレインとの間のノードは、クロック出力OUTBと接続される。

【0053】

p型MISトランジスタM4のソースは、電源回路61のp型MISトランジスタM9のドレインと接続される。p型MISトランジスタM4のドレインは、n型MISトランジスタM3のドレインと接続される。n型MISトランジスタM3のソースは、接地端子と接続される。インバータINV1の入力であるn型MISトランジスタM3及びp型MISトランジスタM4のゲートは、クロック入力INBと接続される。インバータINV1の出力であるn型MISトランジスタM3のドレインとp型MISトランジスタM4のドレインとの間のノードは、クロック出力OUTと接続される。

【0054】

スイッチSW1であるn型MISトランジスタM5は、クロック入力INとクロック出力OUTとの間に接続される。n型MISトランジスタM5のゲートには、制御信号SCNT1が供給される。スイッチSW2であるn型MISトランジスタM6は、クロック入力INBとクロック出力OUTBとの間に接続される。n型MISトランジスタM6のゲートには、制御信号SCNT2が供給される。

【0055】

LCタンク部22は、可変インダクタLv1及びLv2、可変容量Cv、n型MISトランジスタM7により構成される。可変インダクタLv1及びLv2は、図2の可変インダクタLvに対応する。n型MISトランジスタM7は、図2のスイッチSW3に対応し、トランスファゲートとして機能する。n型MISトランジスタM7、可変インダクタLv1及びLv2は、クロック出力OUT及びOUTBの間に直列に接続される(インダクタ−スイッチ部221)。n型MISトランジスタM7のゲートには、制御信号SCNT3が供給される。なお、図6に示すn型MISトランジスタM7、可変インダクタLv1及びLv2の接続順序は単なる例示であり、図6に示す順序に限られない。

【0056】

上述の制御信号SCNT1〜SCNT3は、外部に設けられた制御回路(不図示)などにより供給することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0057】

ここで、制御信号SCNT3は、高レベル及び低レベルからなる2値信号とすることができる。また、高電圧と低電圧との間の任意の電圧を有する信号を制御信号SCNT3として供給し、n型MISトランジスタM7のソース−ドレイン間抵抗を連続的に変化せることで、後述する式(2)に示すように、クロックバッファ回路の共振周波数を変化させることも可能である。

【0058】

可変容量Cvは、クロック出力OUT及びOUTBの間に、インダクタ−スイッチ部221と並列に接続される。例えば、可変容量Cvをシリコンチップ上に形成する場合には、可変容量Cvは、MISトランジスタのゲート容量やMISトランジスタのソース部及びドレイン部のpn接合を利用して形成される。

【0059】

可変インダクタLv1及びLv2のインダクタンス値及び可変容量Cvの容量値の調整は、外部に設けられた制御回路(不図示)などから、これらへ制御信号を供給することにより実現できる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0060】

なお、可変容量Cvは、固定容量としてもよい。また、可変インダクタLv1及びLv2の両方又はいずれか一方を、固定インダクタとしてもよい。可変容量Cvは、容量素子を配置することなく、配線容量をもって代用することもできる。

【0061】

続いて、可変インダクタLv1及びLv2の構成例について説明する。図7は、可変インダクタLv1及びLv2の構成例を示す回路図である。可変インダクタLv1は、固定インダクタLf1及びLf2、スイッチMv1及びMv2により構成される。スイッチMv1はn型MISトランジスタ(MISFET)により構成され、スイッチMv2はp型MISトランジスタ(MISFET)により構成される。

【0062】

固定インダクタLf1、スイッチMv1及び固定インダクタLf4は、端子Aと端子Bとの間に、この順で直列に接続される。スイッチMv2は、固定インダクタLf1の端子A側の端子と、固定インダクタLf3のスイッチMv1側の端子と、の間に接続される。スイッチMv1の制御端子(ゲート端子)とスイッチMv2の制御端子(ゲート端子)には、制御信号SCNT4が供給される。すなわち、スイッチMv1とスイッチMv2とは、制御信号SCNT4に応じて、相補的に動作する。なお、制御信号SCNT4は、外部に設けられた制御回路(不図示)などにより供給することができる。例えば、外部に設けられた制御回路はクロック信号の周波数を検出し、検出結果に基づいて制御信号を生成することが可能である。

【0063】

制御信号SCNT4が高レベルであれば、スイッチMv1がオン、スイッチMv2がオフとなる。この場合、端子Aと端子Bとの間のインダクタンス値は、固定インダクタLf1及びLf2のインダクタンス値の和となる。一方、制御信号SCNT4が低レベルであれば、スイッチMv1がオフ、スイッチMv2がオンとなる。この場合、端子Aと端子Bとの間のインダクタンス値は、固定インダクタLf2のインダクタンス値となる。つまり、可変インダクタLv1及びLv2が図7の構成を有する場合、制御信号SCNT4により、インダクタンス値を2段階に変化させることができる。

【0064】

続いて、クロックバッファ回路600の動作について説明する。制御信号SCNT1〜3が高レベルである場合には、n型MISトランジスタM5〜M7はオンとなる。その結果、クロック入力INとクロック出力OUTとの間、及び、クロック入力INBとクロック出力OUTBとの間が直結され、共振が生じる(共振状態)。

【0065】

制御信号SCNT1及びSCNT2が低レベル、制御信号SCNT3が高レベルである場合には、n型MISトランジスタM5及びM6はオフ、n型MISトランジスタM7はオンとなる。よって、クロックバッファ回路600は、可変インダクタLv及び可変容量Cvを負荷とするインバータ回路となる。

【0066】

制御信号SCNT1〜3が低レベルである場合には、n型MISトランジスタM5〜M7はオフとなる。よって、クロックバッファ回路600は、可変容量Cvのみを負荷とするインバータ回路となる。

【0067】

クロックバッファ回路600における共振状態は、供給されるクロック信号の周波数が最も高い状態で使用される。ここで、クロック出力OUT及びOUTBのそれぞれに繋がる配線の寄生容量をCw、可変インダクタLv1及びLv2のインダクタンス値を共にLv0とする。このとき、クロックバッファ回路600の共振周波数fは、次の式(1)で示される。

【数1】

【0068】

故に、入力クロック信号の周波数が低くなった場合には、インダクタンス値Lv0や容量値Cvを大きくするように変化させることで、共振周波数fを入力クロック信号に追従させることができる。

【0069】

ただし、一般にオンチップで実現可能な可変容量や可変インダクタの可変範囲は2〜4倍程度である。さらに、式(1)に示すように、共振周波数はインダクタンス値Lv0及び容量値Cvの平方根でしか変化しない。従って、共振周波数が追従できる周波数帯には限界がある。例えば、インダクタンス値が固定で、容量値のみが可変である場合、実現可能な共振周波数の変化量は√2倍程度となる。つまり、最高のクロック周波数の1/√2が追従下限周波数となり、この追従下限周波数以下の周波数では注入同期できない。入力クロック信号の周波数が追従下限周波数以下の場合には、n型MISトランジスタM5及びM6をオフ、n型MISトランジスタM7をオンとする。つまり、クロックバッファ回路600を、可変インダクタLv1及びLv2、可変容量Cvを負荷とするインバータ回路として動作させる。

【0070】

ところが、可変インダクタLv1及びLv2を負荷とする回路では、入力クロック信号の周波数が式(1)に示す共振周波数fから離れるほど、ゲインが下がる。また、入力クロック信号を停止した場合でも、可変インダクタLv1及びLv2に貫通電流が流れてしまし、消費電力が増大する原因となる。このため、入力クロック信号の周波数がさらに低い場合には、n型MISトランジスタM7をオフとする。これにより、可変インダクタLv1及びLv2を非導通状態として、出力クロック信号を停止させる。

【0071】

一方、インダクタンス値及び容量値を共に可変とする場合には、入力クロック信号の最高周波数の1/4程度までは注入同期が可能となるので、この周波数を境として共振状態と非共振状態とを切り替える。

【0072】

上述では、制御信号SCNT3が高レベル又は低レベルの2値である場合について説明した。一方、図6に示すようにn型MISトランジスタM7をトランスファゲートとして使用する場合には、n型MISトランジスタM7のソース−ドレイン間の抵抗がトランスファゲートのオン抵抗となる。n型MISトランジスタM7はMISFETであるので、オン抵抗は制御信号SCNT3の電圧に応じて変化する。n型MISトランジスタM7のオン抵抗をR7とすると、オン抵抗R7を考慮した場合の共振周波数fは、式(2)で表される。

【数2】

【0073】

式(2)に示すように、n型MISトランジスタM7のオン抵抗R7が大きいほど、共振周波数fは下がる。つまり、入力クロック信号の周波数が下がった場合に、制御信号SCNT3の電圧を下げることで、共振周波数fを入力クロック信号の周波数に追従させることができる。同様に、入力クロック信号の周波数が上がった場合に、制御信号SCNT3の電圧を上げることで、共振周波数fを入力クロック信号の周波数に追従させることができる。

【0074】

さらに、本実施の形態にかかる効果を示すために、回路シミュレーションによりクロックバッファ回路の動作を検証した。図8は、シミュレーションに用いたクロック分配回路のブロック図である。クロックバッファ回路CBUF1及びCBUF2は、クロックバッファ回路600と同じ構成を有する。

【0075】

クロックバッファ回路CBUF1のクロック入力IN1及びINB1には、クロック信号源CSOURCEが供給される。クロックバッファ回路CBUF1は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUF1のクロック出力OUT1及びOUTB1から、伝送線路TML1を介して、それぞれクロックバッファ回路CBUF2のクロック入力IN2及びINB2へ供給される。クロックバッファ回路CBUF2は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUF2のクロック出力OUT1及びOUTB1から、伝送線路TML2を介して、次の段の回路へ出力される。

【0076】

本シミュレーションでは、クロックバッファ回路CBUF1のクロック出力OUT1及びOUTB1の間、又は、クロック出力OUT2及びOUTB2の間でのクロック信号のタイミングのずれを観測する。本シミュレーションでは、90nmノードのCMOSプロセスのMISFETを使用することを仮定する。電源電圧は1.0Vと仮定する。インダクタ素子は、同じく90nmノードのCMOSプロセスのメタル配線で実現可能なものとし、低周波での直列インダクタンスを2.1nH、直列抵抗を31Ωとする。また、伝送線路もこのプロセスのメタル配線で実現可能なものとし、幅0.5μmかつ長さ1mmのグローバル配線を配線するもと仮定する。なお、可変容量Cvは設けず、容量負荷は伝送線路の寄生容量のみとする。

【0077】

上記の仮定の下、3つの条件についてシミュレーションを行った。第1のシミュレーション条件は、クロック信号源CSOURCEのクロック信号周波数が5GHzであり、制御信号SCNT1〜3が高レベル(すなわち、n型MISトランジスタM5〜M7がオン)の場合である。図9Aは、第1のシミュレーション条件におけるシミュレーション結果を示す信号波形である。クロックバッファ回路CBUF1及びCBUF2は5GHzで共振するように設計されている。そのため、相補信号のそれぞれの波形(クロック出力端子OUT1及びOUTB1における波形、又はクロック出力端子OUT2及びOUTB2における波形)が交わるタイミングのずれは非常に小さく、図9Aに示すように、わずか7psである。

【0078】

第2のシミュレーション条件は、クロック信号源CSOURCEのクロック信号周波数が1GHzであり、制御信号SCNT1〜3が高レベル(すなわち、n型MISトランジスタM5〜M7がオン)の場合である。図9Bは、第2のシミュレーション条件におけるシミュレーション結果を示す信号波形である。前述のように、クロックバッファ回路CBUF1及びCBUF2は5GHzで共振するように設計されている。そのため、クロックバッファ回路CBUF1及びCBUF2は周波数1GHzのクロック信号に対して共振できない。その結果、図9Bに示すように、出力信号の出力振幅が低下してしまう。

【0079】

第3のシミュレーション条件は、クロック信号源CSOURCEのクロック信号周波数が1GHzであり、制御信号SCNT1〜3が低レベル(すなわち、n型MISトランジスタM5〜M7がオフ)の場合である。図9Cは、第3のシミュレーション条件におけるシミュレーション結果を示す信号波形である。この場合、クロックバッファ回路CBUF1及びCBUF2は、単なるインバータ回路となる。そのため、クロックバッファ回路CBUF1及びCBUF2は、クロック信号の周波数が1GHzでも、動作可能となる。このときのタイミングのずれは49psとなり、共振状態の場合(第1のシミュレーション条件)よりも大きくなるが、遅いクロックでは信号タイミングに余裕があるので、クロック信号のタイミングがずれても誤動作は発生しない。

【0080】

従って、クロックバッファ回路600は、広い周波数帯の入力クロック信号に対応することができる。また、可変インダクタのインダクタンス値及び可変容量の容量値を変化させることで、LCタンク部22の共振周波数を変化させることができる。その結果、クロックバッファ回路600は、広い周波数帯の入力クロック信号に対して共振することができる。さらに、クロックバッファ回路600は、必要に応じてLCタンク部22のオン/オフを切り替えることができる。これにより、さらに低周波の入力クロック信号に対応することが可能となる。

【0081】

実施の形態7

続いて、本発明の実施の形態7にかかるクロックバッファ回路について説明する。本実施の形態にかかるクロックバッファ回路は、実施の形態6にかかるクロックバッファ回路600のインダクタ−スイッチ部221を、インダクタ−スイッチ部222に置き換えた構成を有する。本実施の形態にかかるクロックバッファ回路のその他の構成は、クロックバッファ回路600と同様であるので、以下では、インダクタ−スイッチ部222について説明する。

【0082】

図10は、実施の形態7にかかるクロックバッファ回路のインダクタ−スイッチ部222の構成を示す回路図である。インダクタ−スイッチ部222は、固定インダクタ素子Lf1及びLf2、スイッチSW30により構成される。固定インダクタ素子Lf1及びLf2は、それぞれインダクタ−スイッチ部221の可変インダクタLv1及びLv2に対応する。スイッチSW7は、インダクタ−スイッチ部221のn型MISトランジスタM7に対応する。固定インダクタ素子Lf1、スイッチSW7及び固定インダクタ素子Lf2は、クロック出力OUTBとクロック出力OUTとの間に、この順で接続されている。

【0083】

スイッチSW7は、並列接続されたn(nは、2以上の整数)個のn型MISトランジスタM70_1〜M70_nにより構成される。n型MISトランジスタM70_1〜M70_nのゲートには、それぞれ制御信号SCNT7_1〜SCNT7_nが供給される。すなわち、n型MISトランジスタM70_1〜M70_nは、それぞれ制御信号SCNT7_1〜SCNT7_nに応じて開閉するスイッチ素子として機能する。制御信号SCNT7_1〜SCNT7_nは、インダクタ−スイッチ部221のn型MISトランジスタM70に供給される制御信号SCNT3に対応する。なお、n型MISトランジスタM70_1〜M70_nのそれぞれのソース−ドレイン間のオン抵抗は同じでもよいし、互いに異なっていてもよい。

【0084】

n型MISトランジスタM70_1〜M70_nの合成オン抵抗は、n型MISトランジスタM70_1〜M70_nのうちでオン状態となっているものの個数により変化する。すなわち、制御信号SCNT7_1〜SCNT7_nのそれぞれを、独立して高レベル又は低レベルに変化させることで、n型MISトランジスタM70_1〜M70_nの合成オン抵抗を多段階に変化させることができる。これにより、式(2)に示すように、本実施の形態にかかるクロックバッファ回路の共振周波数を変化させることができる。

【0085】

実施の形態8

続いて、本発明の実施の形態8にかかるクロックバッファ回路について説明する。本実施の形態にかかるクロックバッファ回路は、実施の形態6にかかるクロックバッファ回路600のインダクタ−スイッチ部221を、インダクタ−スイッチ部223に置き換えた構成を有する。本実施の形態にかかるクロックバッファ回路のその他の構成は、クロックバッファ回路600と同様であるので、以下では、インダクタ−スイッチ部223について説明する。

【0086】

図11は、実施の形態8にかかるクロックバッファ回路のインダクタ−スイッチ部223の構成を示す回路図である。インダクタ−スイッチ部223は、固定インダクタ素子Lf1_1、Lf1_2、Lf2_1及びLf2_2、n型MISトランジスタM80_1及びM80_2により構成される。インダクタ−スイッチ部223は、スイッチの機能を包摂した可変インダクタとして構成される。インダクタ−スイッチ部223では、n型MISトランジスタM80_1及びM80_2が、それぞれスイッチ素子として動作する。

【0087】

固定インダクタ素子Lf1_2、固定インダクタ素子Lf1_1、n型MISトランジスタM80_1、固定インダクタ素子Lf2_1及びL固定インダクタ素子Lf2_2は、クロック出力OUTBとクロック出力OUTとの間に、この順で接続されている。n型MISトランジスタM80_2は、固定インダクタ素子Lf1_1及びLf1_2間の接続点Cと、固定インダクタ素子Lf2_1及びLf2_2間の接続点Dと、の間に接続される。すなわち、n型MISトランジスタM80_2がオンとなることにより、接続点Cと接続点Dとをバイパスするバイパス経路が構成される。n型MISトランジスタM80_1及びM80_2のゲートには、それぞれ制御信号SCNT8_1及びSCNT8_2が供給される。

【0088】

続いて、インダクタ−スイッチ部223の動作について説明する。制御信号SCNT8_1が高レベル、制御信号SCNT8_2が低レベルの場合、n型MISトランジスタM80_1はオン、n型MISトランジスタM80_2はオフとなる。よって、クロック出力OUT及びOUTB間の直列インダクタンス値は、固定インダクタ素子Lf1_1、Lf1_2、Lf2_1及びLf2_2のインダクタンス値の和となる。

【0089】

制御信号SCNT8_1が低レベル、制御信号SCNT8_2が高レベルの場合、n型MISトランジスタM80_1はオフ、n型MISトランジスタM80_2はオンとなる。よって、クロック出力OUT及びOUTB間の直列インダクタンス値は、固定インダクタ素子Lf1_2及びLf2_2のインダクタンス値の和となる。

【0090】

制御信号SCNT8_1及び制御信号SCNT8_2の両方が高レベルの場合、n型MISトランジスタM80_1及びM80_2は共にオンとなる。この場合、接続点Cと接続点Dとが短絡されるので、固定インダクタ素子Lf1_1及びLf2_1はインダクタとしては機能しない。よって、クロック出力OUT及びOUTB間の直列インダクタンス値は、固定インダクタ素子Lf1_2及びLf2_2のインダクタンス値の和となる。

【0091】

制御信号SCNT8_1及び制御信号SCNT8_2の両方が低レベルの場合、n型MISトランジスタM80_1及びM80_2は共にオフとなる。よって、クロック出力OUT及びOUTB間は、電気的に切断される。

【0092】

以上のとおり、インダクタ−スイッチ部223によれば、制御信号SCNT8_1及び制御信号SCNT8_2により、インダクタンス値の制御とLCタンク部のオン/オフ制御の両方を行なうことができる。

【0093】

なお、図11に示す構成はあくまで例示であり、この例に限定されるものではない。図9では、バイパス経路が1本で場合を示したが、例えば、m(mは2以上の整数)個の固定インダクタ素子Lf1_1〜Lf1_m、m個の固定インダクタ素子Lf1_1〜Lf1_m及びm個のn型MISトランジスタM80_1〜M80_mを設けることも可能である。例えば、n型MISトランジスタM80_1とクロック出力OUTBとの間に、固定インダクタ素子Lf1_1〜Lf1_mがこの順で直列に接続される。n型MISトランジスタM80_1とクロック出力OUTとの間に、固定インダクタ素子Lf2_1〜Lf2_mがこの順で直列に接続される。そして、n型MISトランジスタM80_k(kは、2以上m以下の整数)により、固定インダクタ素子Lf1_(k−1)及びLf1_k間の接続点と、固定インダクタ素子Lf2_(k−1)及びLf2_k間の接続点と、をバイパスすることができる。これにより、クロック出力OUT及びOUTB間の直列インダクタンス値を、より多段階に変化させることが可能となる。その結果、LCタンク部の共振周波数帯をより広げることができる。

【0094】

実施の形態9

続いて、本発明の実施の形態9にかかるクロック分配回路について説明する。本実施の形態にかかるクロック分配回路は、実施の形態1〜8にかかるクロックバッファ回路を用いて構成される。図12は、実施の形態9にかかるクロック分配回路900の構成を示すブロック図である。

【0095】

クロック分配回路900は、クロック信号源CSOURCE、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2により構成される。ここで、実施の形態1〜8にかかるクロックバッファ回路のいずれかが、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2として用いられる。

【0096】

クロックバッファ回路CBUFa1及びCBUFa2は、従属接続される。同様に、クロックバッファ回路CBUFb1及びCBUFb2も、従属接続される。クロック信号源CSOURCEからのクロック信号は、クロックバッファ回路CBUFa1のクロック入力端子INa1及びINBa1と、クロックバッファ回路CBUFb1のクロック入力端子INb1及びINBb1と、に供給される。

【0097】

クロックバッファ回路CBUFa1は、供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFa1のクロック出力端子OUTa1及びOUTBa1から、それぞれクロックバッファ回路CBUFa2のクロック入力端子INa2及びINBa2へ供給される。クロックバッファ回路CBUFa2は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFa2のクロック出力端子OUTa2及びOUTBa2から、次の段の回路へ出力される。

【0098】

クロックバッファ回路CBUFb1は、供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFb1のクロック出力端子OUTb1及びOUTBb1から、それぞれクロックバッファ回路CBUFb2のクロック入力端子INb2及びINBb2へ供給される。クロックバッファ回路CBUFb2は供給されたクロック信号を増幅する。増幅されたクロック信号は、クロックバッファ回路CBUFb2のクロック出力端子OUTb2及びOUTBb2から、次の段の回路へ出力される。

【0099】

また、クロック分配回路900の外部からは、クロック分配回路の動作周波数に対応する制御信号CONTが供給される。制御信号CONTは、クロック分配回路900の外部に配置された制御回路(不図示)などによって生成される。制御信号CONTは、クロック信号源CSOURCE及びクロックバッファ回路のそれぞれへ供給される。例えば、制御信号CONTは、図6に示すクロックバッファ回路600の制御信号SCNT1〜3に相当する。このように、制御信号CONTは複数の信号により構成される場合があるが、図面を簡略化するため、図12では、制御信号CONTを1本の信号線により表示している。

【0100】

クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれでは、制御信号(すなわち、クロック信号の周波数)に応じて、内部のトランスファゲート回路、可変インダクタ、可変容量の状態が変化する。これにより、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれを、常に入力されるクロック信号の周波数に対応した回路状態に設定することができる。

【0101】

上述のように、クロック分配回路900は、実施の形態1〜8のいずれかにかかるクロックバッファ回路により構成される。よって、クロック分配回路900は、広い周波数帯のクロック信号に対応することが可能である。例えば、クロック分配回路900は、高周波の入力クロック信号の周波数が変動する場合には、LCタンク部のインダクタ値及び容量値のいずれか一方又は両方を調整することにより、共振周波数を入力クロック信号の周波数にチューニングすることができる。また、スイッチを操作することにより、ドライバ部をインバータ回路として動作させ、LCタンク部をオン/オフ制御できる。これにより、共振周波数とは大幅に周波数が異なる低周波のクロック信号にも対応することができる。つまり、低周波のテストクロック信号などにも対応することが可能となる。

【0102】

従って、クロック分配回路900は、同一のクロックバッファ回路を用いることができる。これにより、クロック分配回路900を共通化できるとともに、クロックバッファ回路及びインバータ回路の両方を設ける必要がない。その結果、従来のクロック分配回路と比べて、回路規模を小さくすることが可能となる。

【0103】

さらに、クロック分配回路900は、従来のクロック分配回路と比べて、消費電力を抑制することも可能である。以下では、クロック分配回路900における消費電力の抑制について説明する。クロック分配回路900は、クロックバッファ回路及びインバータ回路の両方を設ける必要はない。従来の共振型クロック分配回路では、幅広い周波数のクロックで動作するには共振型クロック分配回路と並列にインバータ回路を配置して、両者の出力をスイッチで切り替える必要があった。しかし、本実施の形態では、従来のクロック分配回路と異なり、クロックバッファ回路及びインバータ回路の出力側にスイッチを設ける必要が無い。一般に、クロックバッファ回路及びインバータ回路の出力側における信号は、入力側における信号よりも振幅が大きい。そのため、出力側に設けられたスイッチにおける損失は、入力側のスイッチにおける損失比べて大きくなる。

【0104】

これに対し、クロック分配回路900で用いられる実施の形態1〜8のいずれかにかかるクロックバッファ回路は、入力側にスイッチが設けられる。実施の形態1〜4、6〜8にかかるクロックバッファ回路では、スイッチSW1及びSW2が入力(クロック入力IN及びINB)側に設けられたスイッチに相当する。実施の形態5にかかるクロックバッファ回路では、スイッチSW4が入力(クロック入力IN)側に設けられたスイッチに相当する。

【0105】

つまり、クロック分配回路900では、クロックバッファ回路の入力側にのみスイッチが設けられた構成を有する。従って、クロック分配回路900は、従来のクロック分配回路よりも消費電力を抑制することが可能となる。

【0106】

実施の形態10

続いて、本発明の実施の形態10にかかるクロック分配回路について説明する。本実施の形態にかかるクロック分配回路は、実施の形態9にかかるクロック分配回路900の変形例である。図13は、実施の形態10にかかるクロック分配回路1000の構成を示すブロック図である。

【0107】

クロック分配回路1000は、クロック分配回路1000は、クロック分配回路900と比べて、周波数検出回路DETa1、DETa2、DETb1及びDETb2が追加された構成を有する。

【0108】

周波数検出回路DETa1は、クロックバッファ回路CBUFa1のクロック入力端子INa1及びINBa1に入力されるクロック信号の周波数を検出する。そして、検出した周波数に応じた制御信号CONTa1を、クロックバッファ回路CBUFa1へ出力する。

【0109】

同様に、周波数検出回路DETa2、DETb1及びDETb2は、クロックバッファ回路CBUFa2のクロック入力端子INa2及びINBa2、クロックバッファ回路CBUFb1のクロック入力端子INb1及びINBb1、クロックバッファ回路CBUFb2のクロック入力端子INb2及びINBb2のそれぞれに入力されるクロック信号の周波数を検出する。そして、検出した周波数に応じた制御信号CONTa2、CONTb1及びCONTb2を、それぞれクロックバッファ回路CBUFa2、CBUFb1及びCBUFb2へ出力する。クロック分配回路1000のその他の構成は、クロック分配回路900と同様であるので説明を省略する。

【0110】

続いて、周波数検出回路DETa1、DETa2、DETb1及びDETb2について説明する。以下では、高周波検出回路である周波数検出回路DETH及び低周波検出回路である周波数検出回路DETLを例として説明する。

【0111】

高周波検出回路である周波数検出回路DETHについて説明する。周波数検出回路DETHは、特定の周波数よりも高い周波数の信号がクロック入力INに入力されると、クロック出力OUTが高レベルとなる回路である。図14は、実施の形態10にかかる周波数検出回路DETHの構成例を示す回路図である。周波数検出回路DETHは、図14に示すように、高域通過フィルタHPF及びピーク検出回路PKにより構成される。

【0112】

高域通過フィルタHPFは、抵抗RH及び容量CHにより構成される。容量CHは、クロック入力INとノードVHPとの間に接続される。抵抗RHは、ノードVHPと接地端子との間に接続される。

【0113】

ピーク検出回路PKは、オペアンプOAMP、ダイオードD1、抵抗RP及び容量CPにより構成される。オペアンプOAMPの非反転入力は、ノードVHPと接続される。オペアンプOAMPの出力と出力OUTcとの間には、ダイオードD1が順方向で挿入される。オペアンプOAMPの非反転入力は、ダイオードD1のカソードと接続される。また、出力OUTc及びダイオードD1のアノードと接地端子との間には、抵抗RP及び容量CPが並列に接続される。

【0114】

周波数検出回路DETHは、1/CHRH以上の周波数の信号が入力されると、ノードVHPでの信号振幅は、入力信号と同程度の大きさとなる。一方、それ以下の周波数では、ノードVHPでの信号振幅は小さくなる。このような振幅を有する信号をピーク検出回路PKに入力すると、ピーク検出回路PKは、信号振幅の最大値に相当する電圧を、出力OUTcから出力する。よって、ピーク検出回路PKは、1/CHRH以上の周波数の信号が入力される場合には高レベル、それ以下の周波数の信号が入力される場合には低レベルの電圧を出力する。

【0115】

次いで、低周波検出回路である周波数検出回路DETLについて説明する。周波数検出回路DETLは、特定の周波数よりも低い周波数の信号がクロック入力INに入力されると、クロック出力OUTが高レベルとなる回路である。図15は、実施の形態10にかかる周波数検出回路DETLの構成例を示す回路図である。周波数検出回路DETLは、図15に示すように、低域通過フィルタLPF及びピーク検出回路PKにより構成される。ピーク検出回路PKは、周波数検出回路DETHと同様であるので、説明を省略する。

【0116】

低域通過フィルタLPFは、抵抗RL及び容量CLにより構成される。容量CLは、ノードVLPと接地端子との間に接続される。抵抗RLは、クロック入力INとノードVLPとの間に接続される。

【0117】

周波数検出回路DETLは、1/CLRL以下の周波数の信号が入力されると、ノードVLPでの信号振幅は、入力信号と同程度の大きさとなる。一方、それ以上の周波数では、ノードVLPでの信号振幅は小さくなる。このような振幅を有する信号をピーク検出回路PKに入力すると、ピーク検出回路PKは、信号振幅の最大値に相当する電圧を、出力OUTcから出力する。よって、ピーク検出回路PKは、1/CLRL以上の周波数の信号が入力される場合には高レベル、それ以下の周波数の信号が入力される場合には低レベルの電圧を出力する。

【0118】

クロック分配回路1000では、制御信号CONTa1、CONTa2、CONTb1及びCONTb2は、クロック信号の周波数に対応する信号である。例えば、制御信号CONTは、図6に示すクロックバッファ回路600の制御信号SCNT1〜3に相当する。このように、制御信号CONTa1、CONTa2、CONTb1及びCONTb2は複数の信号により構成される場合があるが、図面を簡略化するため、図13では、制御信号CONTa1、CONTa2、CONTb1及びCONTb2をそれぞれ1本の信号線により表示している。

【0119】

クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれでは、制御信号(すなわち、クロック信号の周波数)に応じて、内部のトランスファゲート回路、可変インダクタ、可変容量の状態が変化する。これにより、クロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれを、常に入力されるクロック信号の周波数に対応した回路状態に設定することができる。したがって、クロック分配回路1000は、クロック分配回路900と同様の動作を行うことができ、同様の効果を奏する。

【0120】

また、クロック分配回路900では、クロック信号源CSOURCEからクロックバッファ回路CBUFa1、CBUFa2、CBUFb1及びCBUFb2のそれぞれへ、制御信号CONTを供給しなければならない。そのため、複数の長い信号線を設ける必要がある。これに対し、クロック分配回路1000によれば、こうした信号線を設ける必要がないので、より高密度に素子を集積することが可能となる。

【0121】

なお、本実施の形態では、各クロックバッファ回路に対応する周波数検出回路が設けられる場合について説明したが、回路構成はこの例に限られない。例えば、複数のクロックバッファ回路が1つの周波数検出回路を共有し、共有する1つの周波数検出回路からの制御信号を、複数のクロックバッファ回路が受け取る構成とすることもできる。

【0122】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、実施の形態5に係るクロックバッファ回路500は、シングルエンドの入力クロック信号に対応するものであるが、実施の形態1〜4及び6〜8に係る差動クロック信号に対応するクロックバッファ回路と同様の構成転換を行うことが可能である。例えば、クロックバッファ回路500のスイッチSW5を除去した構成とることが可能である。また、クロックバッファ回路500の可変インダクタLvは固定インダクタに置き換えることができる。クロックバッファ回路500の可変インダクタCvは固定容量に置き換えることができる。さらに、クロックバッファ回路500のインダクタスイッチ部(スイッチSW5及び可変インダクタLv)を、実施の形態6〜7にかかるインダクタ−スイッチ部221〜223に置き換えることが可能である。この際、クロック出力OUTと接地端子GNDとの間に、インダクタ−スイッチ部221〜223を配置すればよい。

【0123】

実施の形態9及び10にかかるクロック分配回路900及び100では、クロックバッファ回路が2段従属接続されている例について説明したが、従属接続数はこの例に限られない。すなわち、3以上の任意の個数のクロックバッファ回路を従属接続する構成とすることが可能である。

【0124】

また、上述の実施の形態にかかるクロックバッファ回路は、それ自身が発振器として機能する。従って、例えば実施の形態9及び10にかかるクロック分配回路900及び100では、クロック信号源CSOURCEを、実施の形態1〜8にかかるクロックバッファ回路とすることも可能である。

【符号の説明】

【0125】

11、15 ドライバ部

21〜25 LCタンク部

61 電源回路

70 スイッチ部

100、200、300、400、500、600 クロックバッファ回路

181 PLL

191 インバータ部

192 タンク部

221〜223 インダクタ−スイッチ部

900、1000、1600 クロック分配回路

1700 H型クロック分配回路

1800 PLL回路

1900 共振回路

A、B、E、F 端子

C、D 接続点

CBUF1、CBUF2、CBUFa1、CBUFa2、CBUFb1、CBUFb2 クロックバッファ回路

Cf 固定容量

CH、CL、CP 容量

CONT、CONTa1、CONTa2、CONTb1、CONTb2 制御信号

CSOURCE クロック信号源

Cs キャパシタ

Cv 可変容量

D1 ダイオード

DETa1、DETa2、DETb1、DETb2、DETH、DETL 周波数検出回路

GND 接地端子

HPF 高域通過フィルタ

IN、INB クロック入力

IN1、IN2、INa1、INa2、INb1、INb2 クロック入力端子

INV、INV1〜INV4、INV191、INV192 インバータ

IREF 端子

Lf 固定インダクタ

Lf1、Lf2、Lf1_1〜Lf1_m、Lf2_1〜Lf2_m 固定インダクタ素子

LPF 低域通過フィルタ

Ls インダクタ

Lv、Lv1、Lv2 可変インダクタ

M1、M3、M5〜M7、M70_1〜M70_n、M80_1〜M80_m n型MISトランジスタ(MISFET)

M2、M4、M8、M9 p型MISトランジスタ(MISFET)

Mv1、Mv2 スイッチ

OAMP オペアンプ

OUT、OUTB クロック出力

OUT1、OUT2、OUTa1、OUTa2、OUTb1、OUTb2 クロック出力端子

OUTc 出力

PK ピーク検出回路

RH、RL、RP 抵抗

SCNT1〜SCNT4、SCNT7_1〜SCNT7_n、SCNT8_1、SCNT8_2 制御信号

SW1〜SW5、SW7 スイッチ

TML1、TML2 伝送線路

VHP、VLP ノード

【特許請求の範囲】

【請求項1】

クロック入力からの入力クロック信号の少なくとも正転出力を、クロック出力へ出力するドライバ部と、

前記ドライバ部とクロック出力との間に配置されたLCタンク部と、を備え、

前記ドライバ部は、

前記入力クロック信号の周波数に対応した制御信号に応じて、当該ドライバ部の入力と出力とを短絡させるスイッチを備える、

クロックバッファ回路。

【請求項2】

前記入力クロック信号は、一対の差動クロック信号である第1及び第2のクロック信号からなることを特徴とする、

請求項1に記載のクロックバッファ回路。

【請求項3】

前記ドライバ部は、

入力が前記第2のクロック信号が供給される第2のクロック入力と接続され、出力が第1のクロック出力と接続される第1のインバータと、

入力が前記第1のクロック信号が供給される第1のクロック入力と接続され、出力が第2のクロック出力と接続される第2のインバータと、

前記第1のクロック入力と前記第1のインバータの前記出力との間に挿入された第1のスイッチと、

前記第2のクロック入力と前記第2のインバータの前記出力との間に挿入された第2のスイッチと、を備え、

前記第1及び前記第2のスイッチは、前記第1及び前記第2のクロック信号の周波数が予め定められた第1の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項2に記載のクロックバッファ回路。

【請求項4】

前記LCタンク部は、

前記第1及び前記第2のクロック出力の間に並列に接続されたインダクタ及び容量を備えることを特徴とする、

請求項3に記載のクロックバッファ回路。

【請求項5】

前記LCタンク部は、

前記インダクタと直列に接続された第3のスイッチを更に備え、

前記第3のスイッチは、

前記第1及び前記第2のクロック信号の周波数が予め定められた第2の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項4に記載のクロックバッファ回路。

【請求項6】

前記第3のスイッチは、ゲートに前記制御信号が供給されるMISFETにより構成され、

前記入力クロックの周波数が低下する場合には、前記制御信号の電圧が前記MISFETをオフとするように変化し、

前記入力クロックの周波数が上昇する場合には、前記制御信号の電圧が前記MISFETをオンとするように変化することを特徴とする、

請求項5に記載のクロックバッファ回路。

【請求項7】

前記第3のスイッチは、並列接続された複数のMISFETからなり、

前記複数のMISFETのうちでオン状態であるもの数が、前記制御信号に応じて変化することを特徴とする、

請求項5に記載のクロックバッファ回路。

【請求項8】

前記インダクタは可変インダクタであり、前記制御信号に応じてインダクタンス値が変化することを特徴とする、

請求項4乃至7のいずれか一項に記載のクロックバッファ回路。

【請求項9】

前記可変インダクタは、

第1のインダクタ素子及び第2のインダクタ素子と、

前記第1及び前記第2のインダクタ素子の間に挿入された第4のスイッチと、

前記第1のインダクタ素子の前記第4のスイッチ側とは反対側の端子と、前記第4のスイッチの前記第1のインダクタ素子側とは反対側の端子と、の間に挿入された第5のスイッチと、を備え、

前記第4のスイッチと前記第5のスイッチとは、前記制御信号に応じて相補的に開閉することを特徴とする、

請求項8に記載のクロックバッファ回路。

【請求項10】

前記可変インダクタは、

m(mは、2以上の整数)個のスイッチ素子と、

1番目の前記スイッチ素子の一端と前記第1のクロック出力との間に直列に接続されたm個の第3のインダクタ素子と、

前記1番目の前記スイッチ素子の他端と前記第2のクロック出力との間に直列に接続されたm個の第4のインダクタ素子と、を備え、

k(kは、2≦k≦m)番目の前記スイッチ素子の一端は、前記1番目の前記スイッチ素子から数えてk番目の前記第3のインダクタ素子と(k−1)番目の前記第3のインダクタ素子との接続点と接続され、

前記k番目の前記スイッチ素子の他端は、前記1番目の前記スイッチ素子から数えてk番目の前記第4のインダクタ素子と(k−1)番目の前記第4のインダクタ素子との接続点と接続され、

前記制御信号に応じて前記k番目の前記スイッチ素子が閉じることにより、前記1番目の前記スイッチ素子から数えて前記k番目の前記第3のインダクタ素子と前記k番目の前記第4のインダクタ素子とを短絡させることを特徴とする、

請求項8に記載のクロックバッファ回路。

【請求項11】

前記インダクタは、固定インダクタであることを特徴とする、

請求項4乃至7のいずれか一項に記載のクロックバッファ回路。

【請求項12】

前記容量は可変容量であり、前記制御信号に応じて容量値が変化することを特徴とする、

請求項4乃至11のいずれか一項に記載のクロックバッファ回路。

【請求項13】

前記容量は、固定容量であることを特徴とする、

請求項4乃至11のいずれか一項に記載のクロックバッファ回路。

【請求項14】

前記容量は、前記第1及び前記第2のクロック出力間に接続される負荷の容量及び配線の容量のいずれか一方又は両方であることを特徴とする、

請求項4乃至11のいずれか一項に記載のクロックバッファ回路。

【請求項15】

前記入力クロック信号は、シングルエンドのクロック信号であることを特徴とする、

請求項1に記載のクロックバッファ回路。

【請求項16】

前記ドライバ部は、

入力が前記クロック入力と接続され、出力が前記クロック出力と接続される正論理のバッファ回路と、

前記バッファ回路の前記入力と前記出力との間に接続された第1のスイッチと、を備え、

前記第1のスイッチは、前記入力クロック信号の周波数が予め定められた第1の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項15に記載のクロックバッファ回路。

【請求項17】

前記LCタンク部は、

前記クロック出力と接地端子との間に並列に接続されたインダクタ及び容量を備えることを特徴とする、

請求項16に記載のクロックバッファ回路。

【請求項18】

前記LCタンク部は、

前記インダクタと直列に接続された第2のスイッチを更に備え、

前記第2のスイッチは、

前記第入力クロック信号の周波数が予め定められた第2の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項17に記載のクロックバッファ回路。

【請求項19】

前記第2のスイッチは、ゲートに前記制御信号が供給されるMISFETにより構成され、

前記入力クロックの周波数が低下する場合には、前記制御信号の電圧が前記MISFETをオフとするように変化し、

前記入力クロックの周波数が上昇する場合には、前記制御信号の電圧が前記MISFETをオンとするように変化することを特徴とする、

請求項18に記載のクロックバッファ回路。

【請求項20】

前記第2のスイッチは、並列接続された複数のMISFET素子からなり、

前記複数のMISFETのうちでオン状態であるもの数が、前記制御信号に応じて変化することを特徴とする、

請求項18に記載のクロックバッファ回路。

【請求項21】

前記インダクタは可変インダクタであり、前記制御信号に応じてインダクタンス値が変化することを特徴とする、

請求項17乃至20のいずれか一項に記載のクロックバッファ回路。

【請求項22】

前記可変インダクタは、

第1のインダクタ素子及び第2のインダクタ素子と、

前記第1及び前記第2のインダクタ素子の間に挿入された第3のスイッチと、

前記第1のインダクタの前記第3のスイッチ側とは反対側の端子と、前記第3のスイッチの前記第1のインダクタ側とは反対側の端子と、の間に挿入された第4のスイッチと、を備え、

前記第3のスイッチと前記第4のスイッチとは、前記制御信号に応じて相補的に開閉することを特徴とする、

請求項21に記載のクロックバッファ回路。

【請求項23】

前記可変インダクタは、

m(mは、2以上の整数)個のスイッチ素子と、

1番目の前記スイッチ素子の一端と前記クロック出力との間に直列に接続されたm個の第3のインダクタ素子と、

前記1番目の前記スイッチ素子の他端と前記接地端子との間に直列に接続されたm個の第4のインダクタ素子と、を備え、

k(kは、2≦k≦m)番目の前記スイッチ素子の一端は、前記1番目の前記スイッチ素子から数えてk番目の前記第3のインダクタ素子と(k−1)番目の前記第3のインダクタ素子との接続点と接続され、

前記k番目の前記スイッチ素子の他端は、前記1番目の前記スイッチ素子から数えてk番目の前記第4のインダクタ素子と(k−1)番目の前記第4のインダクタ素子との接続点と接続され、

前記制御信号に応じて前記k番目の前記スイッチ素子が閉じることにより、前記1番目の前記スイッチ素子から数えて前記k番目の前記第3のインダクタ素子と前記k番目の前記第4のインダクタ素子とを短絡させることを特徴とする、

請求項21に記載のクロックバッファ回路。

【請求項24】

前記インダクタは、固定インダクタであることを特徴とする、

請求項17乃至20のいずれか一項に記載のクロックバッファ回路。

【請求項25】

前記容量は可変容量であり、前記制御信号に応じて容量値が変化することを特徴とする、

請求項17乃至24のいずれか一項に記載のクロックバッファ回路。

【請求項26】

前記容量は、固定容量であることを特徴とする、

請求項17乃至24のいずれか一項に記載のクロックバッファ回路。

【請求項27】

前記容量は、前記クロック出力に接続される負荷の容量及び配線の容量のいずれか一方又は両方であることを特徴とする、

請求項17乃至24のいずれか一項に記載のクロックバッファ回路。

【請求項28】

請求項1乃至27のいずれか一項に記載の前記クロックバッファ回路を複数備えることを特徴とする、

クロック分配回路。

【請求項29】

複数の前記クロックバッファ回路のうち、任意の個数の前記クロックバッファ回路が従属接続されることを特徴とする、

請求項28に記載のクロックバッファ回路。

【請求項30】

前記複数のクロックバッファ回路に前記制御信号を出力する周波数検出回路を備え、

前記周波数検出回路は、前記入力クロック信号の周波数を検出して、前記周波数に対応する前記制御信号を生成することを特徴とする、

請求項29に記載のクロック分配回路。

【請求項1】

クロック入力からの入力クロック信号の少なくとも正転出力を、クロック出力へ出力するドライバ部と、

前記ドライバ部とクロック出力との間に配置されたLCタンク部と、を備え、

前記ドライバ部は、

前記入力クロック信号の周波数に対応した制御信号に応じて、当該ドライバ部の入力と出力とを短絡させるスイッチを備える、

クロックバッファ回路。

【請求項2】

前記入力クロック信号は、一対の差動クロック信号である第1及び第2のクロック信号からなることを特徴とする、

請求項1に記載のクロックバッファ回路。

【請求項3】

前記ドライバ部は、

入力が前記第2のクロック信号が供給される第2のクロック入力と接続され、出力が第1のクロック出力と接続される第1のインバータと、

入力が前記第1のクロック信号が供給される第1のクロック入力と接続され、出力が第2のクロック出力と接続される第2のインバータと、

前記第1のクロック入力と前記第1のインバータの前記出力との間に挿入された第1のスイッチと、

前記第2のクロック入力と前記第2のインバータの前記出力との間に挿入された第2のスイッチと、を備え、

前記第1及び前記第2のスイッチは、前記第1及び前記第2のクロック信号の周波数が予め定められた第1の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項2に記載のクロックバッファ回路。

【請求項4】

前記LCタンク部は、

前記第1及び前記第2のクロック出力の間に並列に接続されたインダクタ及び容量を備えることを特徴とする、

請求項3に記載のクロックバッファ回路。

【請求項5】

前記LCタンク部は、

前記インダクタと直列に接続された第3のスイッチを更に備え、

前記第3のスイッチは、

前記第1及び前記第2のクロック信号の周波数が予め定められた第2の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項4に記載のクロックバッファ回路。

【請求項6】

前記第3のスイッチは、ゲートに前記制御信号が供給されるMISFETにより構成され、

前記入力クロックの周波数が低下する場合には、前記制御信号の電圧が前記MISFETをオフとするように変化し、

前記入力クロックの周波数が上昇する場合には、前記制御信号の電圧が前記MISFETをオンとするように変化することを特徴とする、

請求項5に記載のクロックバッファ回路。

【請求項7】

前記第3のスイッチは、並列接続された複数のMISFETからなり、

前記複数のMISFETのうちでオン状態であるもの数が、前記制御信号に応じて変化することを特徴とする、

請求項5に記載のクロックバッファ回路。

【請求項8】

前記インダクタは可変インダクタであり、前記制御信号に応じてインダクタンス値が変化することを特徴とする、

請求項4乃至7のいずれか一項に記載のクロックバッファ回路。

【請求項9】

前記可変インダクタは、

第1のインダクタ素子及び第2のインダクタ素子と、

前記第1及び前記第2のインダクタ素子の間に挿入された第4のスイッチと、

前記第1のインダクタ素子の前記第4のスイッチ側とは反対側の端子と、前記第4のスイッチの前記第1のインダクタ素子側とは反対側の端子と、の間に挿入された第5のスイッチと、を備え、

前記第4のスイッチと前記第5のスイッチとは、前記制御信号に応じて相補的に開閉することを特徴とする、

請求項8に記載のクロックバッファ回路。

【請求項10】

前記可変インダクタは、

m(mは、2以上の整数)個のスイッチ素子と、

1番目の前記スイッチ素子の一端と前記第1のクロック出力との間に直列に接続されたm個の第3のインダクタ素子と、

前記1番目の前記スイッチ素子の他端と前記第2のクロック出力との間に直列に接続されたm個の第4のインダクタ素子と、を備え、

k(kは、2≦k≦m)番目の前記スイッチ素子の一端は、前記1番目の前記スイッチ素子から数えてk番目の前記第3のインダクタ素子と(k−1)番目の前記第3のインダクタ素子との接続点と接続され、

前記k番目の前記スイッチ素子の他端は、前記1番目の前記スイッチ素子から数えてk番目の前記第4のインダクタ素子と(k−1)番目の前記第4のインダクタ素子との接続点と接続され、

前記制御信号に応じて前記k番目の前記スイッチ素子が閉じることにより、前記1番目の前記スイッチ素子から数えて前記k番目の前記第3のインダクタ素子と前記k番目の前記第4のインダクタ素子とを短絡させることを特徴とする、

請求項8に記載のクロックバッファ回路。

【請求項11】

前記インダクタは、固定インダクタであることを特徴とする、

請求項4乃至7のいずれか一項に記載のクロックバッファ回路。

【請求項12】

前記容量は可変容量であり、前記制御信号に応じて容量値が変化することを特徴とする、

請求項4乃至11のいずれか一項に記載のクロックバッファ回路。

【請求項13】

前記容量は、固定容量であることを特徴とする、

請求項4乃至11のいずれか一項に記載のクロックバッファ回路。

【請求項14】

前記容量は、前記第1及び前記第2のクロック出力間に接続される負荷の容量及び配線の容量のいずれか一方又は両方であることを特徴とする、

請求項4乃至11のいずれか一項に記載のクロックバッファ回路。

【請求項15】

前記入力クロック信号は、シングルエンドのクロック信号であることを特徴とする、

請求項1に記載のクロックバッファ回路。

【請求項16】

前記ドライバ部は、

入力が前記クロック入力と接続され、出力が前記クロック出力と接続される正論理のバッファ回路と、

前記バッファ回路の前記入力と前記出力との間に接続された第1のスイッチと、を備え、

前記第1のスイッチは、前記入力クロック信号の周波数が予め定められた第1の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項15に記載のクロックバッファ回路。

【請求項17】

前記LCタンク部は、

前記クロック出力と接地端子との間に並列に接続されたインダクタ及び容量を備えることを特徴とする、

請求項16に記載のクロックバッファ回路。

【請求項18】

前記LCタンク部は、

前記インダクタと直列に接続された第2のスイッチを更に備え、

前記第2のスイッチは、

前記第入力クロック信号の周波数が予め定められた第2の周波数以下である場合に、前記制御信号に応じて閉じることを特徴とする、

請求項17に記載のクロックバッファ回路。

【請求項19】

前記第2のスイッチは、ゲートに前記制御信号が供給されるMISFETにより構成され、

前記入力クロックの周波数が低下する場合には、前記制御信号の電圧が前記MISFETをオフとするように変化し、

前記入力クロックの周波数が上昇する場合には、前記制御信号の電圧が前記MISFETをオンとするように変化することを特徴とする、

請求項18に記載のクロックバッファ回路。

【請求項20】

前記第2のスイッチは、並列接続された複数のMISFET素子からなり、

前記複数のMISFETのうちでオン状態であるもの数が、前記制御信号に応じて変化することを特徴とする、

請求項18に記載のクロックバッファ回路。

【請求項21】

前記インダクタは可変インダクタであり、前記制御信号に応じてインダクタンス値が変化することを特徴とする、

請求項17乃至20のいずれか一項に記載のクロックバッファ回路。

【請求項22】

前記可変インダクタは、

第1のインダクタ素子及び第2のインダクタ素子と、

前記第1及び前記第2のインダクタ素子の間に挿入された第3のスイッチと、

前記第1のインダクタの前記第3のスイッチ側とは反対側の端子と、前記第3のスイッチの前記第1のインダクタ側とは反対側の端子と、の間に挿入された第4のスイッチと、を備え、

前記第3のスイッチと前記第4のスイッチとは、前記制御信号に応じて相補的に開閉することを特徴とする、

請求項21に記載のクロックバッファ回路。

【請求項23】

前記可変インダクタは、

m(mは、2以上の整数)個のスイッチ素子と、

1番目の前記スイッチ素子の一端と前記クロック出力との間に直列に接続されたm個の第3のインダクタ素子と、

前記1番目の前記スイッチ素子の他端と前記接地端子との間に直列に接続されたm個の第4のインダクタ素子と、を備え、

k(kは、2≦k≦m)番目の前記スイッチ素子の一端は、前記1番目の前記スイッチ素子から数えてk番目の前記第3のインダクタ素子と(k−1)番目の前記第3のインダクタ素子との接続点と接続され、

前記k番目の前記スイッチ素子の他端は、前記1番目の前記スイッチ素子から数えてk番目の前記第4のインダクタ素子と(k−1)番目の前記第4のインダクタ素子との接続点と接続され、

前記制御信号に応じて前記k番目の前記スイッチ素子が閉じることにより、前記1番目の前記スイッチ素子から数えて前記k番目の前記第3のインダクタ素子と前記k番目の前記第4のインダクタ素子とを短絡させることを特徴とする、

請求項21に記載のクロックバッファ回路。

【請求項24】

前記インダクタは、固定インダクタであることを特徴とする、

請求項17乃至20のいずれか一項に記載のクロックバッファ回路。

【請求項25】

前記容量は可変容量であり、前記制御信号に応じて容量値が変化することを特徴とする、

請求項17乃至24のいずれか一項に記載のクロックバッファ回路。

【請求項26】

前記容量は、固定容量であることを特徴とする、

請求項17乃至24のいずれか一項に記載のクロックバッファ回路。

【請求項27】

前記容量は、前記クロック出力に接続される負荷の容量及び配線の容量のいずれか一方又は両方であることを特徴とする、

請求項17乃至24のいずれか一項に記載のクロックバッファ回路。

【請求項28】

請求項1乃至27のいずれか一項に記載の前記クロックバッファ回路を複数備えることを特徴とする、

クロック分配回路。

【請求項29】

複数の前記クロックバッファ回路のうち、任意の個数の前記クロックバッファ回路が従属接続されることを特徴とする、

請求項28に記載のクロックバッファ回路。

【請求項30】

前記複数のクロックバッファ回路に前記制御信号を出力する周波数検出回路を備え、

前記周波数検出回路は、前記入力クロック信号の周波数を検出して、前記周波数に対応する前記制御信号を生成することを特徴とする、

請求項29に記載のクロック分配回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2012−161039(P2012−161039A)

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願番号】特願2011−21050(P2011−21050)

【出願日】平成23年2月2日(2011.2.2)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願日】平成23年2月2日(2011.2.2)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]