クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、受信信号からクロック信号を復元するクロックリカバリ(Clock Recovery)回路および、復元したクロック信号を用いてデータ信号を再生するデータ再生回路に関する。

【背景技術】

【0002】

例えばGHzクラスの高速データ通信の多くでは、パラレルデータを一旦シリアルデータに変換して伝送を行い、受信機側でシリアルデータをパラレルデータに変換する手法が採用されている。

【0003】

この種の高速シリアルデータ通信に適用される一般的な受信機では、シリアルデータから復元したクロック信号を使用して受信データに同期させた状態でシリアルデータのサンプリングを行うと共に、受信機側のクロックに同期させてデータを再生することが行われる。このように、受信したシリアルデータからクロック信号を復元する回路がクロックリカバリ回路であり、復元したクロック信号を用いてシリアルデータを再生する回路がデータ再生回路である。

【0004】

クロックリカバリ回路では、受信データに含まれるジッタ成分を除去して安定した同期クロックを生成して、シリアルデータのサンプリングを行う必要がある。このため、クロックリカバリ回路には、ジッタ除去のためのフィルタ機能を有する回路(フィルタ回路)が必要となる。

【0005】

クロックリカバリ回路に設けられたフィルタ回路は、受信したシリアルデータにおける遷移エッジの情報をパラレル化した後のデータに対してデジタルフィルタ処理を行う。このデジタルフィルタ処理により、低周波から高周波成分までのジッタ成分が除去された安定した同期クロックが生成される。

【0006】

一方、高速シリアルデータ通信で使用する信号には高いレベルのEMIノイズが含まれている。このため、EMIノイズの低減のため、送信機側にてシリアルデータの生成クロックにスペクトル拡散クロック(Spread Spectrum Clock:以下「SSC」と表記)を用いる技法が登場した。

【0007】

このSSCでは、スペクトル拡散されたクロックを用いて送信される送信データの周波数は、受信機側のクロックに対して、例えば数kHzの周期で周波数変調(数100〜数1000ppm)されており、非常に高周波で変調された信号と見なすことができる。このため、クロックリカバリ回路には、高周波変調されたジッタ成分に追従する機能も要求される。

【0008】

このように、SSC技法を適用したクロックリカバリ回路には、低周波成分から高周波成分までのジッタ成分の除去と、高周波で変調された信号への追従という、相反する動作が要求されることになる。

【0009】

なお、SSC技法を適用したクロックリカバリ回路に係る従来技術として、下記特許文献1に示されたものがある(特許文献1では、CDR(Clock Data Recovery)回路として開示されている)。この特許文献1に示されるCDR回路は、復元クロック信号に応答してシリアルデータをサンプリングしてシリアルサンプリングパルスを生成するサンプラと、シリアルサンプリングパルスをパラレルデータに変換し、パラレルデータから相対的に低速の複数の位相信号を生成し、複数の位相信号を用いて相対的に高速の一つである位相制御信号を生成するCDRループと、位相制御信号に応答して外部から提供される基準クロック信号の位相を進めるか遅らせるようにすることで復元クロック信号を生成する位相補間器を備えて構成されている。

【0010】

この特許文献1では、小さい位相誤差を有しながら、高速で動作するCDR回路を提供することができるとしている。しかしながら、特許文献1に示されたCDR回路では、CDRループが生成する位相制御信号は、クロック信号の2n分の1(90度間隔の位相差を有する4相クロック信号を用いる場合であってもクロック信号のn分の2)の周波数で動作するに過ぎない。例えば、高速シリアルデータのビットレートが1GHzであり、高速シリアルデータを10ビットのパラレルデータに変換する(n=10)場合、50MHz(速くても高々200MHz)の周波数でしか動作することができない。したがって、特許文献1に示されたCDR回路では、1回の位相調整量が大きくならざるを得ず、高速シリアルデータ通信の通信速度が大きくなるに従い、あるいはシリアルパラレル変換のビット数が大きくなるに従って、クロックジッタが増大するという課題があった。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2007−60652号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

本発明は、クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供することを目的とする。

【課題を解決するための手段】

【0013】

本願発明の一態様によれば、第1のクロック信号に同期してシリアル入力信号をサンプリングし、サンプリングデータを出力するサンプラと、前記サンプリングデータに基づき、前記第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路と、第2のクロック信号に同期して、前記シリアル位相情報信号をシリアルパラレル変換し、パラレル位相情報信号を出力するシリアルパラレル変換回路と、前記パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路と、前記位相偏差信号と前記位相遅進信号とに基づき、位相制御信号を生成し、前記第2のクロック信号より高速の第3のクロック信号に同期して、前記位相制御信号を出力する位相制御量処理回路と、前記位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整し前記第1のクロック信号を出力する位相補間回路と、を備えたことを特徴とするクロックリカバリ回路が提供される。

【発明の効果】

【0014】

本発明によれば、クロックジッタが減少し、ジッタ耐性性能が向上するという効果を奏する。

【図面の簡単な説明】

【0015】

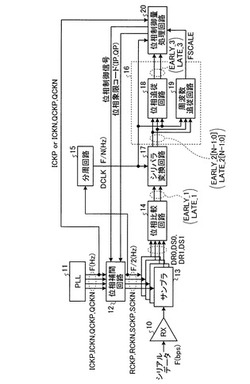

【図1】図1は、クロックリカバリ回路の全体構成図。

【図2】図2は、位相制御量処理回路の詳細構成図。

【図3】図3は、位相制御信号の時間変化の様子を示す図。

【図4】図4は、リングレジスタに適用可能なシフトレジスタの構成例を示す図。

【図5】図5は、位相補間回路に適用可能な回路構成例を示す図。

【図6】図6は、位相象限、位相象限コードIP,QPおよび、各象限において用いられる電流源の関係を示す図。

【図7】図7は、各象限において用いられる電流源および位相象限コードIP,QPを位相空間上に示した図。

【図8】図8は、位相補間回路の出力段に用いられる1/2分周回路の入出力関係を示す図。

【図9】図9は、1/2分周回路の入出力波形を示す図。

【図10】図10は、クロックリカバリ回路をデータ再生回路として用いる場合の一構成例を示す図。

【図11】図11は、シリアルデータと4相クロック信号との位相関係を示す図。

【図12】図12は、サーモメータコードで表現した位相制御信号の一例を示す図。

【図13】図13は、本実施の形態の位相補間回路における位相の動きを説明する図。

【図14】図14は、従来の位相補間回路における位相の動きを説明する図。

【図15】図15は、従来の位相補間回路におけるオーバーシュート現象を説明する図。

【図16】図16は、本実施の形態のクロックリカバリ回路における位相調整の様子(実線部)と、従来のクロックリカバリ回路における位相調整の様子(破線部)を示す図。

【発明を実施するための形態】

【0016】

以下に添付図面を参照して、本発明の実施の形態にかかるクロックリカバリ回路およびデータ再生回路を詳細に説明する。なお、以下の内容により本発明が限定されるものではない。

【0017】

<実施の形態>

図1は、本発明の実施の形態にかかるクロックリカバリ回路の構成を示すブロック図である。図1に示すように、本実施の形態にかかるクロックリカバリ回路は、受信回路10、PLL回路11、位相補間回路12、4個のサンプラ13、位相比較回路14、分周回路15、シリパラ変換(シリアル信号をパラレル信号に変換する処理、以下同様に略記)回路17、位相追従回路18、周波数追従回路19および、位相制御量処理回路20を備えて構成される。なお、上記の構成部のうち、破線部内に位置する位相追従回路18および周波数追従回路19は、分周回路15から出力される相対的に低速な第1のクロック信号であるDCLKで動作するデジタルフィルタ回路16を構成する。

【0018】

つぎに、図1に示すクロックリカバリ回路の動作について説明する。なお、クロックリカバリ回路には、F(bps)のシリアルデータ(Serial Data)が入力されるものとする。シリアルデータは、データに重畳されたクロック信号を備える。

【0019】

まず、受信回路10は、F(bps)のシリアルデータを受信する。一方、PLL回路11は、90度ずつ位相がずれたF(Hz)の4相クロック(ICKP,ICKN,QCKP,QCKN)を生成して位相補間回路12に出力する。位相補間回路12は、後述する位相制御量処理回路20から出力される位相制御信号に基づき、PLL回路11から入力する4相クロックの位相を調整(補間)すると共に、リカバリクロックと称されるF/2(Hz)の相補的なクロック信号(RCKP,RCKN)、およびサンプルドクロックと称されるF/2(Hz)の相補的なクロック信号(SCKP,SCKN)を生成して出力する。4個のサンプラ13は、位相補間回路12から出力される4相クロック信号(RCKP,RCKN,SCKP,SCKN)に同期して、受信回路10を介して入力された受信信号をサンプリングし、サンプリングデータ(DR0,DS0,DR1,DS1)を出力する。

【0020】

位相比較回路14は、サンプラ13から出力されるサンプリングデータ(DR0,DS0,DR1,DS1)の状態から、4相クロック信号(RCKP,RCKN,SCKP,SCKN)とシリアルデータのクロック信号との位相関係を表すシリアル位相情報信号(EARLY_1,LATE_1)を生成してシリパラ変換回路17に出力する。なお、位相関係を表すシリアル位相情報信号とは、受信したシリアルデータのクロックと4相クロック信号(RCKP,RCKN,SCKP,SCKN)との位相関係が進んでいるのか遅れているのかを判定した情報である。

【0021】

分周回路15は、位相補間回路12から出力されるF/2(Hz)のクロックを2/Nに分周してF/N(Hz)(Nは、シリパラ変換における並列ビット数)のクロック信号を生成する。シリパラ変換回路17は、分周回路15から出力されるクロック(DCLK)に同期して、位相比較回路14から出力されるシリアル位相情報信号(EARLY_1,LATE_1)のデータレートを下げたパラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0])に変換する。なお、分周回路15から出力される相対的に低速なクロック(DCLK)は、デジタルフィルタ回路16を構成する位相追従回路18および周波数追従回路19に対しても入力される。

【0022】

デジタルフィルタ回路16は、シリパラ変換回路17から出力されるパラレル位相情報信号のジッタ成分を除去すると共に、位相調整量と位相調整方向を演算する。デジタルフィルタ回路16は、位相追従回路18と周波数追従回路19とを備える。位相追従回路18は、パラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0])を元に、受信機内におけるクロックICKPの位相のズレの方向を判定するための信号でもあり、瞬時的な位相の遅れ/進みを表す位相遅進信号(EARLY_3およびLATE_3)を生成する。周波数追従回路19は、パラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0])を元に、位相の遅れ/進みに関する時間積分を一定時間行い、受信機内のクロック信号に対する受信データの周波数偏差を検出し、位相量に換算した位相偏差信号FSCALEを生成する。すなわち、周波数追従回路19は、パラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0]))から得られる位相情報および周波数情報に基づき、4相クロック信号(RCKP,RCKN,SCKP,SCKN)の位相をシリアルデータのクロック信号の位相に合わせるための、4相クロック信号に対する位相調整量である位相偏差信号FSCALEを決定し、出力する。

【0023】

位相制御量処理回路20には、PLL回路11から出力され、上記第1のクロックよりも高速な第2のクロック信号であるICKP,ICKN,QCKP,QCKNのうちの何れか一つが入力される。位相制御量処理回路20は、位相遅進信号(EARLY_3およびLATE_3)と位相偏差信号FSCALEに基づいて、位相補間回路12がサンプラ13に出力するクロック信号(RCKP,RCKN,SCKP,SCKN)の位相を制御するための位相制御信号を生成して、高速な第2のクロック信号に同期して位相制御信号を位相補間回路12に出力する。位相制御量処理回路20は、例えば、位相遅進信号(EARLY_3およびLATE_3)と、位相偏差信号(FSCALE)とを混合することで生成される位相制御信号と、当該位相制御信号がどの象限に位置するのかを表す位相象限コードとを出力する。これらの詳細については後述する。

【0024】

なお、位相制御量処理回路20から出力される位相制御信号としては、例えば、ビット1もしくはビット0が連続して現れ、ビットの切替も1度しか行われないという特徴を有するサーモメータコード(Thermometer Code)と称される符号列を用いることができる。

【0025】

図2は、本実施の形態にかかる位相制御量処理回路20の構成の一態様を示す図である。図2に示す位相制御量処理回路20は、クロックリカバリ回路の位相調整をより高速に行う機能を有している。なお、図2において、図1に示す構成部と同一または同等のものについては、同一符号を付して示している。

【0026】

図2において、位相制御量処理回路20は、移動量決定回路24、移動方向決定回路26、シフトレジスタ28、位相制御信号の生成回路としてのリングレジスタ34および、位相象限コードの生成回路としてのリングレジスタ36を主たる構成部として構成されている。

【0027】

つぎに、図2に示す位相制御量処理回路20の動作について説明する。なお、位相比較回路14、分周回路15、シリパラ変換回路17、位相追従回路18および周波数追従回路19に関する動作については、上述したとおりであり、詳細な説明は省略する。

【0028】

移動方向決定回路26は、位相追従回路18からの位相遅進信号(EARLY_3およびLATE_3)を元に、後述するリングレジスタ34,36の移動方向(回転方向)を決定する。具体的には、位相進み信号(EARLY_3)に含まれる“1”の数の和と、位相遅れ信号(LATE_3)に含まれる“1”の数の和との比較により、リングレジスタの移動方向が決定される。

【0029】

また、移動量決定回路24は、位相追従回路18からの位相遅進信号(EARLY_3およびLATE_3)と、周波数追従回路19からの位相偏差信号(FSCALE)とを元に、現処理時点におけるクロックICKPの位相に加算もしくは減算させる位相制御量を決定すると共に、決定した位相制御量を低速なクロックであるDCLKに同期して、でシフトレジスタ28に設定する。このシフトレジスタ28に書き込まれたものが新たな位相制御量になる。

【0030】

なお、図2では、位相遅進信号(EARLY_3およびLATE_3)および、位相偏差信号(FSCALE)の3者が移動量決定回路24に入力される構成としているが、移動方向決定回路26の処理結果を受領し、その処理結果と位相偏差信号(FSCALE)とを用いて移動量を決定することでも構わない。このような処理とする場合、移動量決定回路24には、周波数追従回路19からの位相偏差信号(FSCALE)と、移動方向決定回路26の処理結果とが入力される構成となる。

【0031】

シフトレジスタ28に送出された位相制御量の各ビット値は、高速なクロックである例えばICKP(PLL回路11が生成)を反転回路30で反転させたクロックに同期して、シリアル信号として1ビットずつ論理積回路32に送出される。論理積回路32には、クロックICKPが入力され、シフトレジスタ28から送出されたビット値とクロックICKPとの論理積が、後述するリングレジスタ34,36の動作クロック(HSCLK)となる。なお、分周回路15への入力クロックとして、図1に示すように、位相補間回路12によって補間されたクロックである、例えばRCKP(ICKP,QCKP,QCKNでも可)を用いるようにしてもよい。

【0032】

また、シフトレジスタ28のMSB(最終ビット)には0を書き込むことが好ましい。このようにすれば、MSBが論理積回路32に入力されたときには、論理積回路32から出力される動作クロックHSCLKが0となるので、リングレジスタ34,36の動作を確実に停止することができる。なお、この処理は、図2の例であれば、移動量決定回路24が決定した移動量の上限を9ビットに制限することを意味している。したがって、移動量決定回路24が決定した移動量の上限を例えば6ビットに制限する場合には、シフトレジスタ28におけるMSBから4ビット目までに0を書き込むようにすればよい。

【0033】

サーモメータコードである位相制御信号を生成するリングレジスタ34には、予め位相制御信号の出力値となる値が書き込まれている。また、位相象限コード(IP,QP)を生成するリングレジスタ36にも同様に、位相象限コードの出力値となる値が書き込まれている。

【0034】

リングレジスタ34,36は、移動方向決定回路26からの出力信号(DIRECTION)によりリングレジスタ34,36における各ビット列のシフト方向(回転方向)が決定され、上述したクロック信号(HSCLK)により格納されたデータが1ビットずつシフトする。例えば、移動方向が位相を進ませる方向の場合、リングレジスタ34,36に格納されたビット列は時計方向に回転する。すなわち、リングレジスタ34では、上段部にあるレジスタ34aのビット列が右側にシフトし、最右翼にあるビット0が下段部にあるレジスタ34bの最右翼に移動すると共に、レジスタ34bのビット列が左側にシフトし、最左翼にあるビット1がレジスタ34aの最左翼に移動する。同様に、リングレジスタ36では、上段部にあるレジスタ36aのビット列が右側にシフトし、最右翼にあるビット0が下段部にあるレジスタ36bの最右翼に移動すると共に、レジスタ36bのビット列が左側にシフトし、最左翼にあるビット1がレジスタ36aの最左翼に移動する。なお、図2の例では、位相制御信号としては、上段部にあるレジスタ34aに格納されたビット列(16ビット)が出力され、位相象限コードとしては、上段部にあるレジスタ36aの最左翼のビットがQPとして出力されると共に、下段部にあるレジスタ36bにおける左から16ビット目のビットがIPとして出力される。

【0035】

図3は、位相制御量処理回路から出力される位相制御信号の時間変化の様子を示す図であり、上段部には、クロックICKP、クロックDCLK、シリアルデータを、下段部には位相制御量処理回路から出力される位相制御信号を表すビット列(A),(B),(C)を示している。ビット列(A),(B),(C)は5ビットの位相変化を示すビット列であるが、従来の回路では、これらのビット列(A),(B),(C)がDCLOCKの周期(タイミング)で出力されていた。一方、本実施の形態の位相制御量処理回路では、図3に示すように、(A)のビット列を初期値として、(1)→(2)→(3)→(4)の順で1ビットずつビットが変化したビット列が出力される。すなわち、本実施の形態では、位相制御量処理回路20が、高速なクロックであるICKPに同期して、位相制御信号を出力する。

【0036】

このように、位相制御量処理回路20は、低速のクロックDCLKに同期したデジタルフィルタ回路16により決定された位相偏差信号および位相遅進信号を元に、位相制御量を決定し、高速のクロックであるICKPに同期して、位相制御調整量を出力する。これにより、位相補完回路12は、高速のクロックであるICKPに同期して、制御されることとなり、従来に比べ、一度に受ける制御量を減らすことができる。

【0037】

つぎに、本実施の形態のクロックリカバリ回路を具現するさらに詳細な回路構成を例示すると共に、クロックリカバリ回路の具現に必要な技術的事項に関する補足的な説明を適宜行う。

【0038】

図4は、図2に示したリングレジスタ34に適用可能なシフトレジスタの構成例を示す図であり、特に、リングレジスタ34の上段部にあるレジスタ34aの構成を示している。図4に示すシフトレジスタでは、複数のフリップフロップ40と、複数のセレクタ42とが設けられ、各フリップフロップ40の出力が相前後して隣接するセレクタの入力端にカスケード接続されるように構成されると共に、移動方向決定回路26の出力(DIRECTION)がセレクタ42に入力され、論理積回路32の出力(HSCLK)がフリップフロップ40に入力されるように構成されている。

【0039】

このシフトレジスタによれば、信号DIRECTIONにより隣接フリップフロップのどちらを選択するかが決定され、クロック信号HSCLKによりビットシフト動作が行われる。

【0040】

なお、図4のシフトレジスタは、図2に示したリングレジスタ34に適用可能であるとして説明したが、ビット数を変更することでリングレジスタ36に適用することも無論可能である。

【0041】

図5は、図1に示した位相補間回路12に適用可能な回路構成の一例を示す図である。また、図6は、位相象限、リングレジスタ36から出力される位相象限コードIP,QPおよび、各象限において用いられる電流源の関係を示す図表であり、図7は、各象限において用いられる電流源および位相象限コードIP,QPを位相空間上に示した図である。

【0042】

図5に示す位相補間回路では、4個の差動回路における一方側のトランジスタ素子の一端(例えばドレイン)同士が接続され、他方側のトランジスタ素子の一端(例えばドレイン)同士が接続されている。また、各差動回路における一方側のトランジスタ素子の他端(例えばソース)と他方側のトランジスタ素子の他端(例えばソース)同士は接続され、それぞれ異なる電流源I1〜I4に接続されている。さらに、共通に接続された一方側の各トランジスタ素子の一端は抵抗素子を介して電源端(VDD)に接続され、共通に接続された他方側の各トランジスタ素子の一端も抵抗素子を介して電源端(VDD)に接続されている。

【0043】

なお、電流源I1〜I4の大きさを位相調整電流とするとき、この位相調整電流とリングレジスタ34から出力されるとの間には、次式に示す関係がある。

【0044】

I1=(位相制御信号における0の数)×基準電流

I2=(位相制御信号における1の数)×基準電流

I3=(位相制御信号における0の数)×基準電流

I4=(位相制御信号における1の数)×基準電流

【0045】

例えば、第1象限における位相調整を行う場合、図6の表に示されるように電流源I1,I2が用いられる。このとき、PLL回路11から出力されるクロックICKP、QCKPをトランジスタ素子のゲートに入力し、位相制御信号におけるビット値に応じた電流値で電流源I1,I2が動作するので、クロックICKP、QCKPを補間した新たなクロック信号が生成されることになる。

【0046】

両極端の例として、位相制御信号におけるビットがオール“0”であれば、電流源I2の大きさは0となり、ICKPの軸に沿った出力のみが現れ、位相制御信号におけるビットがオール“1”であれば、電流源I1の大きさは0となり、QCKPの軸に沿った出力のみが現れる。したがって、電流源I1,I2の大きさが共に0でなければ第1象限における出力が現れ(図7参照)、この出力を用いてクロック位相が補間されることになる。

【0047】

図8は、位相補間回路の出力段に用いられる1/2分周回路の入出力関係を示す図であり、図9は、1/2分周回路の入出力波形を示す図である。この1/2分周回路は、図5に示す位相補間回路が生成した差動信号(差動クロック)OUTP,OUTNを使用し、周波数を1/2に下げた図9に示すような4相クロック(RCKP,RCKN,SCKP,SCKN)が生成される。なお、ここで生成された4相クロック信号がサンプラ13の動作クロックとなることは、上述したとおりである。

【0048】

図10は、クロックリカバリ回路をデータ再生回路として用いる場合の一構成例を示す図であり、図11は、クロックリカバリ回路が受信データにロックした状態におけるシリアルデータとRCKP,SCKP,RCKN,SCKNとの位相関係を示す図である。

【0049】

サンプラ13(13a〜13d)は、クロックリカバリ回路が受信データにロックした状態において、入力されたシリアルデータの遷移領域をRCKP,RCKNでサンプリングし、安定領域をSCKP、SCKNでサンプリングする(図11参照)。サンプラ13から出力されたサンプリングデータは、位相比較回路14に送られるが、位相比較回路14以降の処理は上述したとおりである。

【0050】

一方、サンプラ13から出力されたサンプリングデータのうち、SCKP、SCKNでサンプリングされたデータは、シリアルデータの安定領域でサンプリングされたデータである。よって、このデータをデータ再生回路の出力とすることが可能である。図10は、この考えによって構成されたものであり、SCKP,SCKNによってサンプリングされるサンプラ13b,13dの出力を、シリパラ変換回路17とは異なるシリパラ変換回路50に入力する構成としている。このように、SCKP,SCKNによってサンプリングされたデータをシリパラ変換回路を介して出力することにより、上述したクロックリカバリ回路をデータ再生回路として使用することができる。

【0051】

図12は、サーモメータコードで表現した位相制御信号の一例を示す図である。図12に示すように、サーモメータコードでは、ビット1もしくはビット0が連続して現れ、且つ、ビットの切替が1度しか行われないことが特徴である。なお、図2において、リングレジスタ34の上段部にあるレジスタ34aに格納されているデータは、図12における位相No15として示されている。すなわち、図2の状態は、位相制御信号が第1象限と第2象限との境界部に位置していることを表している。いま、この状態からリングレジスタ34,36が時計方向に1ビット回転すると、リングレジスタ34からの出力である位相制御信号のビットは、“111……1”となり、リングレジスタ36からの出力である象限信号(IP,QP)は、(0,1)となる。すなわち、位相Noが、“15”から“16”に変化することになる。このようなサーモメータコードを用いれば、位相Noの“1”の変化に対してビット列におけるビット変化が1ビットしか起こらないため、ビット切替時の誤動作を防止する観点から非常に有効である。

【0052】

つぎに、本実施の形態にかかるクロックリカバリ回路の効果について説明する。従来のクロックリカバリ回路では、位相制御量処理回路から出力される位相制御信号が位相象限を跨ぐ制御量である場合、位相変化にオーバーシュートが発生するという問題点があった。この現象は、位相補間回路の動作が、象限信号IP,QPに対しては瞬時に反応するのに対して、サーモメータコードを使用する位相制御信号の変化に対しては瞬時に反応せず、時間遅れが発生するからである。なお、時間遅れが発生する主因は、位相補間回路を構成する定電流回路(差動回路および電流源)における配線等の寄生容量であり、配線等の寄生容量によって定電流回路が安定するまでの時間が延びてしまうからである。

【0053】

上述した時間遅れについて、具体的な例で説明する。いま、例えば図13に示すように第1象限の12番目の位相(位相No12)から第2象限の16番目の位相(位相No16)への切替制御を行う場合を考える(位相Noについては、図12を参照)。本実施の形態のクロックリカバリ回路では、位相の切替を高速なクロックで行っているため、1回の位相制御(位相補間)は1ビットずつ行われる。したがって、第1象限の12番目の位相から第2象限の16番目の位相への切替制御はオーバーシュートなしに行われる。

【0054】

これに対して、従来のクロックリカバリ回路では、象限信号IP,QPが(1,1)から(0,1)に切り替わるため、第1象限の位相である位相No12は、第2象限の位相である位相No20として認識されてしまう(位相No12と位相No20とでは、ビット0の数およびビット1の数が同数である)。したがって、位相No12→位相No16の制御を行う場合、従来のクロックリカバリ回路では、図14に示すように、位相No12→位相No20→位相No16という制御が実行されてしまい、図15に示すようなオーバーシュートが発生することになる。

【0055】

また、従来のクロックリカバリ回路では、SSCのような周波数偏差を持つシリアルデータに追従する場合、1回の位相調整量が大きいため、クロックジッタが多くなってしまうという問題点があった。例えば、位相制御量処理回路の分解能力を1/64UI分割(1UIは送信データ速度Fの逆数)とし、シリパラ変換のビット幅を10ビットとすると、位相調整の更新サイクルはF/10となる。ここで、SATA−Gen2に見られるような3Gbps、−5000ppmの周波数偏差を有するシリアルデータに追従させるためには、最大で5/64UIの位相調整を行う必要があると言われている。一方、従来のクロックリカバリ回路では、位相調整の更新サイクルは、デジタルフィルタの処理サイクル(F/10サイクル)で行っている。したがって、従来のクロックリカバリ回路の考え方では、5/64UIの位相調整はF/10サイクル毎に行う必要がある。

【0056】

これに対して、本実施の形態のクロックリカバリ回路では、位相調整の更新をデータレートのサイクル(Fサイクル)で行っているので、1回の位相調整は1/64UIで充分である(F/10サイクルに換算すれば10/64UIの位相調整を行っていることに相当する)。

【0057】

図16は、本実施の形態のクロックリカバリ回路における位相調整の様子(実線部)と、従来のクロックリカバリ回路における位相調整の様子(破線部)を示す図である。図16において、直線で示した波形K1は、SSCによる位相変化を簡略的に示したものである。本実施の形態では、従来のクロックリカバリ回路のように5/64UIの位相調整を一度に行う必要がないため、クロックジッタを減少させることが可能となる。

【0058】

以上説明したように、本実施の形態にかかるクロックリカバリ回路によれば、シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号に基づいて位相偏差信号と位相遅進信号を演算し、これらの位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力し、この位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号の位相を補間して出力することとしたので、クロックジッタを低減させることができるという効果が得られる。

【符号の説明】

【0059】

10 受信回路、11 PLL回路、12 位相補間回路、13(13a〜13d) サンプラ、14 位相比較回路、15 分周回路、16 デジタルフィルタ回路、17,50 シリパラ変換回路、18 位相追従回路、19 周波数追従回路、20 位相制御量処理回路、24 移動量決定回路、26 移動方向決定回路、28 シフトレジスタ、30 反転回路、32 論理積回路、34,36 リングレジスタ、34a,34b,36a,36b レジスタ、40 フリップフロップ、42 セレクタ

【技術分野】

【0001】

本発明は、受信信号からクロック信号を復元するクロックリカバリ(Clock Recovery)回路および、復元したクロック信号を用いてデータ信号を再生するデータ再生回路に関する。

【背景技術】

【0002】

例えばGHzクラスの高速データ通信の多くでは、パラレルデータを一旦シリアルデータに変換して伝送を行い、受信機側でシリアルデータをパラレルデータに変換する手法が採用されている。

【0003】

この種の高速シリアルデータ通信に適用される一般的な受信機では、シリアルデータから復元したクロック信号を使用して受信データに同期させた状態でシリアルデータのサンプリングを行うと共に、受信機側のクロックに同期させてデータを再生することが行われる。このように、受信したシリアルデータからクロック信号を復元する回路がクロックリカバリ回路であり、復元したクロック信号を用いてシリアルデータを再生する回路がデータ再生回路である。

【0004】

クロックリカバリ回路では、受信データに含まれるジッタ成分を除去して安定した同期クロックを生成して、シリアルデータのサンプリングを行う必要がある。このため、クロックリカバリ回路には、ジッタ除去のためのフィルタ機能を有する回路(フィルタ回路)が必要となる。

【0005】

クロックリカバリ回路に設けられたフィルタ回路は、受信したシリアルデータにおける遷移エッジの情報をパラレル化した後のデータに対してデジタルフィルタ処理を行う。このデジタルフィルタ処理により、低周波から高周波成分までのジッタ成分が除去された安定した同期クロックが生成される。

【0006】

一方、高速シリアルデータ通信で使用する信号には高いレベルのEMIノイズが含まれている。このため、EMIノイズの低減のため、送信機側にてシリアルデータの生成クロックにスペクトル拡散クロック(Spread Spectrum Clock:以下「SSC」と表記)を用いる技法が登場した。

【0007】

このSSCでは、スペクトル拡散されたクロックを用いて送信される送信データの周波数は、受信機側のクロックに対して、例えば数kHzの周期で周波数変調(数100〜数1000ppm)されており、非常に高周波で変調された信号と見なすことができる。このため、クロックリカバリ回路には、高周波変調されたジッタ成分に追従する機能も要求される。

【0008】

このように、SSC技法を適用したクロックリカバリ回路には、低周波成分から高周波成分までのジッタ成分の除去と、高周波で変調された信号への追従という、相反する動作が要求されることになる。

【0009】

なお、SSC技法を適用したクロックリカバリ回路に係る従来技術として、下記特許文献1に示されたものがある(特許文献1では、CDR(Clock Data Recovery)回路として開示されている)。この特許文献1に示されるCDR回路は、復元クロック信号に応答してシリアルデータをサンプリングしてシリアルサンプリングパルスを生成するサンプラと、シリアルサンプリングパルスをパラレルデータに変換し、パラレルデータから相対的に低速の複数の位相信号を生成し、複数の位相信号を用いて相対的に高速の一つである位相制御信号を生成するCDRループと、位相制御信号に応答して外部から提供される基準クロック信号の位相を進めるか遅らせるようにすることで復元クロック信号を生成する位相補間器を備えて構成されている。

【0010】

この特許文献1では、小さい位相誤差を有しながら、高速で動作するCDR回路を提供することができるとしている。しかしながら、特許文献1に示されたCDR回路では、CDRループが生成する位相制御信号は、クロック信号の2n分の1(90度間隔の位相差を有する4相クロック信号を用いる場合であってもクロック信号のn分の2)の周波数で動作するに過ぎない。例えば、高速シリアルデータのビットレートが1GHzであり、高速シリアルデータを10ビットのパラレルデータに変換する(n=10)場合、50MHz(速くても高々200MHz)の周波数でしか動作することができない。したがって、特許文献1に示されたCDR回路では、1回の位相調整量が大きくならざるを得ず、高速シリアルデータ通信の通信速度が大きくなるに従い、あるいはシリアルパラレル変換のビット数が大きくなるに従って、クロックジッタが増大するという課題があった。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2007−60652号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

本発明は、クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供することを目的とする。

【課題を解決するための手段】

【0013】

本願発明の一態様によれば、第1のクロック信号に同期してシリアル入力信号をサンプリングし、サンプリングデータを出力するサンプラと、前記サンプリングデータに基づき、前記第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路と、第2のクロック信号に同期して、前記シリアル位相情報信号をシリアルパラレル変換し、パラレル位相情報信号を出力するシリアルパラレル変換回路と、前記パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路と、前記位相偏差信号と前記位相遅進信号とに基づき、位相制御信号を生成し、前記第2のクロック信号より高速の第3のクロック信号に同期して、前記位相制御信号を出力する位相制御量処理回路と、前記位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整し前記第1のクロック信号を出力する位相補間回路と、を備えたことを特徴とするクロックリカバリ回路が提供される。

【発明の効果】

【0014】

本発明によれば、クロックジッタが減少し、ジッタ耐性性能が向上するという効果を奏する。

【図面の簡単な説明】

【0015】

【図1】図1は、クロックリカバリ回路の全体構成図。

【図2】図2は、位相制御量処理回路の詳細構成図。

【図3】図3は、位相制御信号の時間変化の様子を示す図。

【図4】図4は、リングレジスタに適用可能なシフトレジスタの構成例を示す図。

【図5】図5は、位相補間回路に適用可能な回路構成例を示す図。

【図6】図6は、位相象限、位相象限コードIP,QPおよび、各象限において用いられる電流源の関係を示す図。

【図7】図7は、各象限において用いられる電流源および位相象限コードIP,QPを位相空間上に示した図。

【図8】図8は、位相補間回路の出力段に用いられる1/2分周回路の入出力関係を示す図。

【図9】図9は、1/2分周回路の入出力波形を示す図。

【図10】図10は、クロックリカバリ回路をデータ再生回路として用いる場合の一構成例を示す図。

【図11】図11は、シリアルデータと4相クロック信号との位相関係を示す図。

【図12】図12は、サーモメータコードで表現した位相制御信号の一例を示す図。

【図13】図13は、本実施の形態の位相補間回路における位相の動きを説明する図。

【図14】図14は、従来の位相補間回路における位相の動きを説明する図。

【図15】図15は、従来の位相補間回路におけるオーバーシュート現象を説明する図。

【図16】図16は、本実施の形態のクロックリカバリ回路における位相調整の様子(実線部)と、従来のクロックリカバリ回路における位相調整の様子(破線部)を示す図。

【発明を実施するための形態】

【0016】

以下に添付図面を参照して、本発明の実施の形態にかかるクロックリカバリ回路およびデータ再生回路を詳細に説明する。なお、以下の内容により本発明が限定されるものではない。

【0017】

<実施の形態>

図1は、本発明の実施の形態にかかるクロックリカバリ回路の構成を示すブロック図である。図1に示すように、本実施の形態にかかるクロックリカバリ回路は、受信回路10、PLL回路11、位相補間回路12、4個のサンプラ13、位相比較回路14、分周回路15、シリパラ変換(シリアル信号をパラレル信号に変換する処理、以下同様に略記)回路17、位相追従回路18、周波数追従回路19および、位相制御量処理回路20を備えて構成される。なお、上記の構成部のうち、破線部内に位置する位相追従回路18および周波数追従回路19は、分周回路15から出力される相対的に低速な第1のクロック信号であるDCLKで動作するデジタルフィルタ回路16を構成する。

【0018】

つぎに、図1に示すクロックリカバリ回路の動作について説明する。なお、クロックリカバリ回路には、F(bps)のシリアルデータ(Serial Data)が入力されるものとする。シリアルデータは、データに重畳されたクロック信号を備える。

【0019】

まず、受信回路10は、F(bps)のシリアルデータを受信する。一方、PLL回路11は、90度ずつ位相がずれたF(Hz)の4相クロック(ICKP,ICKN,QCKP,QCKN)を生成して位相補間回路12に出力する。位相補間回路12は、後述する位相制御量処理回路20から出力される位相制御信号に基づき、PLL回路11から入力する4相クロックの位相を調整(補間)すると共に、リカバリクロックと称されるF/2(Hz)の相補的なクロック信号(RCKP,RCKN)、およびサンプルドクロックと称されるF/2(Hz)の相補的なクロック信号(SCKP,SCKN)を生成して出力する。4個のサンプラ13は、位相補間回路12から出力される4相クロック信号(RCKP,RCKN,SCKP,SCKN)に同期して、受信回路10を介して入力された受信信号をサンプリングし、サンプリングデータ(DR0,DS0,DR1,DS1)を出力する。

【0020】

位相比較回路14は、サンプラ13から出力されるサンプリングデータ(DR0,DS0,DR1,DS1)の状態から、4相クロック信号(RCKP,RCKN,SCKP,SCKN)とシリアルデータのクロック信号との位相関係を表すシリアル位相情報信号(EARLY_1,LATE_1)を生成してシリパラ変換回路17に出力する。なお、位相関係を表すシリアル位相情報信号とは、受信したシリアルデータのクロックと4相クロック信号(RCKP,RCKN,SCKP,SCKN)との位相関係が進んでいるのか遅れているのかを判定した情報である。

【0021】

分周回路15は、位相補間回路12から出力されるF/2(Hz)のクロックを2/Nに分周してF/N(Hz)(Nは、シリパラ変換における並列ビット数)のクロック信号を生成する。シリパラ変換回路17は、分周回路15から出力されるクロック(DCLK)に同期して、位相比較回路14から出力されるシリアル位相情報信号(EARLY_1,LATE_1)のデータレートを下げたパラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0])に変換する。なお、分周回路15から出力される相対的に低速なクロック(DCLK)は、デジタルフィルタ回路16を構成する位相追従回路18および周波数追従回路19に対しても入力される。

【0022】

デジタルフィルタ回路16は、シリパラ変換回路17から出力されるパラレル位相情報信号のジッタ成分を除去すると共に、位相調整量と位相調整方向を演算する。デジタルフィルタ回路16は、位相追従回路18と周波数追従回路19とを備える。位相追従回路18は、パラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0])を元に、受信機内におけるクロックICKPの位相のズレの方向を判定するための信号でもあり、瞬時的な位相の遅れ/進みを表す位相遅進信号(EARLY_3およびLATE_3)を生成する。周波数追従回路19は、パラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0])を元に、位相の遅れ/進みに関する時間積分を一定時間行い、受信機内のクロック信号に対する受信データの周波数偏差を検出し、位相量に換算した位相偏差信号FSCALEを生成する。すなわち、周波数追従回路19は、パラレル位相情報信号(EARLY_2[N−1:0],LATE_2[N−1:0]))から得られる位相情報および周波数情報に基づき、4相クロック信号(RCKP,RCKN,SCKP,SCKN)の位相をシリアルデータのクロック信号の位相に合わせるための、4相クロック信号に対する位相調整量である位相偏差信号FSCALEを決定し、出力する。

【0023】

位相制御量処理回路20には、PLL回路11から出力され、上記第1のクロックよりも高速な第2のクロック信号であるICKP,ICKN,QCKP,QCKNのうちの何れか一つが入力される。位相制御量処理回路20は、位相遅進信号(EARLY_3およびLATE_3)と位相偏差信号FSCALEに基づいて、位相補間回路12がサンプラ13に出力するクロック信号(RCKP,RCKN,SCKP,SCKN)の位相を制御するための位相制御信号を生成して、高速な第2のクロック信号に同期して位相制御信号を位相補間回路12に出力する。位相制御量処理回路20は、例えば、位相遅進信号(EARLY_3およびLATE_3)と、位相偏差信号(FSCALE)とを混合することで生成される位相制御信号と、当該位相制御信号がどの象限に位置するのかを表す位相象限コードとを出力する。これらの詳細については後述する。

【0024】

なお、位相制御量処理回路20から出力される位相制御信号としては、例えば、ビット1もしくはビット0が連続して現れ、ビットの切替も1度しか行われないという特徴を有するサーモメータコード(Thermometer Code)と称される符号列を用いることができる。

【0025】

図2は、本実施の形態にかかる位相制御量処理回路20の構成の一態様を示す図である。図2に示す位相制御量処理回路20は、クロックリカバリ回路の位相調整をより高速に行う機能を有している。なお、図2において、図1に示す構成部と同一または同等のものについては、同一符号を付して示している。

【0026】

図2において、位相制御量処理回路20は、移動量決定回路24、移動方向決定回路26、シフトレジスタ28、位相制御信号の生成回路としてのリングレジスタ34および、位相象限コードの生成回路としてのリングレジスタ36を主たる構成部として構成されている。

【0027】

つぎに、図2に示す位相制御量処理回路20の動作について説明する。なお、位相比較回路14、分周回路15、シリパラ変換回路17、位相追従回路18および周波数追従回路19に関する動作については、上述したとおりであり、詳細な説明は省略する。

【0028】

移動方向決定回路26は、位相追従回路18からの位相遅進信号(EARLY_3およびLATE_3)を元に、後述するリングレジスタ34,36の移動方向(回転方向)を決定する。具体的には、位相進み信号(EARLY_3)に含まれる“1”の数の和と、位相遅れ信号(LATE_3)に含まれる“1”の数の和との比較により、リングレジスタの移動方向が決定される。

【0029】

また、移動量決定回路24は、位相追従回路18からの位相遅進信号(EARLY_3およびLATE_3)と、周波数追従回路19からの位相偏差信号(FSCALE)とを元に、現処理時点におけるクロックICKPの位相に加算もしくは減算させる位相制御量を決定すると共に、決定した位相制御量を低速なクロックであるDCLKに同期して、でシフトレジスタ28に設定する。このシフトレジスタ28に書き込まれたものが新たな位相制御量になる。

【0030】

なお、図2では、位相遅進信号(EARLY_3およびLATE_3)および、位相偏差信号(FSCALE)の3者が移動量決定回路24に入力される構成としているが、移動方向決定回路26の処理結果を受領し、その処理結果と位相偏差信号(FSCALE)とを用いて移動量を決定することでも構わない。このような処理とする場合、移動量決定回路24には、周波数追従回路19からの位相偏差信号(FSCALE)と、移動方向決定回路26の処理結果とが入力される構成となる。

【0031】

シフトレジスタ28に送出された位相制御量の各ビット値は、高速なクロックである例えばICKP(PLL回路11が生成)を反転回路30で反転させたクロックに同期して、シリアル信号として1ビットずつ論理積回路32に送出される。論理積回路32には、クロックICKPが入力され、シフトレジスタ28から送出されたビット値とクロックICKPとの論理積が、後述するリングレジスタ34,36の動作クロック(HSCLK)となる。なお、分周回路15への入力クロックとして、図1に示すように、位相補間回路12によって補間されたクロックである、例えばRCKP(ICKP,QCKP,QCKNでも可)を用いるようにしてもよい。

【0032】

また、シフトレジスタ28のMSB(最終ビット)には0を書き込むことが好ましい。このようにすれば、MSBが論理積回路32に入力されたときには、論理積回路32から出力される動作クロックHSCLKが0となるので、リングレジスタ34,36の動作を確実に停止することができる。なお、この処理は、図2の例であれば、移動量決定回路24が決定した移動量の上限を9ビットに制限することを意味している。したがって、移動量決定回路24が決定した移動量の上限を例えば6ビットに制限する場合には、シフトレジスタ28におけるMSBから4ビット目までに0を書き込むようにすればよい。

【0033】

サーモメータコードである位相制御信号を生成するリングレジスタ34には、予め位相制御信号の出力値となる値が書き込まれている。また、位相象限コード(IP,QP)を生成するリングレジスタ36にも同様に、位相象限コードの出力値となる値が書き込まれている。

【0034】

リングレジスタ34,36は、移動方向決定回路26からの出力信号(DIRECTION)によりリングレジスタ34,36における各ビット列のシフト方向(回転方向)が決定され、上述したクロック信号(HSCLK)により格納されたデータが1ビットずつシフトする。例えば、移動方向が位相を進ませる方向の場合、リングレジスタ34,36に格納されたビット列は時計方向に回転する。すなわち、リングレジスタ34では、上段部にあるレジスタ34aのビット列が右側にシフトし、最右翼にあるビット0が下段部にあるレジスタ34bの最右翼に移動すると共に、レジスタ34bのビット列が左側にシフトし、最左翼にあるビット1がレジスタ34aの最左翼に移動する。同様に、リングレジスタ36では、上段部にあるレジスタ36aのビット列が右側にシフトし、最右翼にあるビット0が下段部にあるレジスタ36bの最右翼に移動すると共に、レジスタ36bのビット列が左側にシフトし、最左翼にあるビット1がレジスタ36aの最左翼に移動する。なお、図2の例では、位相制御信号としては、上段部にあるレジスタ34aに格納されたビット列(16ビット)が出力され、位相象限コードとしては、上段部にあるレジスタ36aの最左翼のビットがQPとして出力されると共に、下段部にあるレジスタ36bにおける左から16ビット目のビットがIPとして出力される。

【0035】

図3は、位相制御量処理回路から出力される位相制御信号の時間変化の様子を示す図であり、上段部には、クロックICKP、クロックDCLK、シリアルデータを、下段部には位相制御量処理回路から出力される位相制御信号を表すビット列(A),(B),(C)を示している。ビット列(A),(B),(C)は5ビットの位相変化を示すビット列であるが、従来の回路では、これらのビット列(A),(B),(C)がDCLOCKの周期(タイミング)で出力されていた。一方、本実施の形態の位相制御量処理回路では、図3に示すように、(A)のビット列を初期値として、(1)→(2)→(3)→(4)の順で1ビットずつビットが変化したビット列が出力される。すなわち、本実施の形態では、位相制御量処理回路20が、高速なクロックであるICKPに同期して、位相制御信号を出力する。

【0036】

このように、位相制御量処理回路20は、低速のクロックDCLKに同期したデジタルフィルタ回路16により決定された位相偏差信号および位相遅進信号を元に、位相制御量を決定し、高速のクロックであるICKPに同期して、位相制御調整量を出力する。これにより、位相補完回路12は、高速のクロックであるICKPに同期して、制御されることとなり、従来に比べ、一度に受ける制御量を減らすことができる。

【0037】

つぎに、本実施の形態のクロックリカバリ回路を具現するさらに詳細な回路構成を例示すると共に、クロックリカバリ回路の具現に必要な技術的事項に関する補足的な説明を適宜行う。

【0038】

図4は、図2に示したリングレジスタ34に適用可能なシフトレジスタの構成例を示す図であり、特に、リングレジスタ34の上段部にあるレジスタ34aの構成を示している。図4に示すシフトレジスタでは、複数のフリップフロップ40と、複数のセレクタ42とが設けられ、各フリップフロップ40の出力が相前後して隣接するセレクタの入力端にカスケード接続されるように構成されると共に、移動方向決定回路26の出力(DIRECTION)がセレクタ42に入力され、論理積回路32の出力(HSCLK)がフリップフロップ40に入力されるように構成されている。

【0039】

このシフトレジスタによれば、信号DIRECTIONにより隣接フリップフロップのどちらを選択するかが決定され、クロック信号HSCLKによりビットシフト動作が行われる。

【0040】

なお、図4のシフトレジスタは、図2に示したリングレジスタ34に適用可能であるとして説明したが、ビット数を変更することでリングレジスタ36に適用することも無論可能である。

【0041】

図5は、図1に示した位相補間回路12に適用可能な回路構成の一例を示す図である。また、図6は、位相象限、リングレジスタ36から出力される位相象限コードIP,QPおよび、各象限において用いられる電流源の関係を示す図表であり、図7は、各象限において用いられる電流源および位相象限コードIP,QPを位相空間上に示した図である。

【0042】

図5に示す位相補間回路では、4個の差動回路における一方側のトランジスタ素子の一端(例えばドレイン)同士が接続され、他方側のトランジスタ素子の一端(例えばドレイン)同士が接続されている。また、各差動回路における一方側のトランジスタ素子の他端(例えばソース)と他方側のトランジスタ素子の他端(例えばソース)同士は接続され、それぞれ異なる電流源I1〜I4に接続されている。さらに、共通に接続された一方側の各トランジスタ素子の一端は抵抗素子を介して電源端(VDD)に接続され、共通に接続された他方側の各トランジスタ素子の一端も抵抗素子を介して電源端(VDD)に接続されている。

【0043】

なお、電流源I1〜I4の大きさを位相調整電流とするとき、この位相調整電流とリングレジスタ34から出力されるとの間には、次式に示す関係がある。

【0044】

I1=(位相制御信号における0の数)×基準電流

I2=(位相制御信号における1の数)×基準電流

I3=(位相制御信号における0の数)×基準電流

I4=(位相制御信号における1の数)×基準電流

【0045】

例えば、第1象限における位相調整を行う場合、図6の表に示されるように電流源I1,I2が用いられる。このとき、PLL回路11から出力されるクロックICKP、QCKPをトランジスタ素子のゲートに入力し、位相制御信号におけるビット値に応じた電流値で電流源I1,I2が動作するので、クロックICKP、QCKPを補間した新たなクロック信号が生成されることになる。

【0046】

両極端の例として、位相制御信号におけるビットがオール“0”であれば、電流源I2の大きさは0となり、ICKPの軸に沿った出力のみが現れ、位相制御信号におけるビットがオール“1”であれば、電流源I1の大きさは0となり、QCKPの軸に沿った出力のみが現れる。したがって、電流源I1,I2の大きさが共に0でなければ第1象限における出力が現れ(図7参照)、この出力を用いてクロック位相が補間されることになる。

【0047】

図8は、位相補間回路の出力段に用いられる1/2分周回路の入出力関係を示す図であり、図9は、1/2分周回路の入出力波形を示す図である。この1/2分周回路は、図5に示す位相補間回路が生成した差動信号(差動クロック)OUTP,OUTNを使用し、周波数を1/2に下げた図9に示すような4相クロック(RCKP,RCKN,SCKP,SCKN)が生成される。なお、ここで生成された4相クロック信号がサンプラ13の動作クロックとなることは、上述したとおりである。

【0048】

図10は、クロックリカバリ回路をデータ再生回路として用いる場合の一構成例を示す図であり、図11は、クロックリカバリ回路が受信データにロックした状態におけるシリアルデータとRCKP,SCKP,RCKN,SCKNとの位相関係を示す図である。

【0049】

サンプラ13(13a〜13d)は、クロックリカバリ回路が受信データにロックした状態において、入力されたシリアルデータの遷移領域をRCKP,RCKNでサンプリングし、安定領域をSCKP、SCKNでサンプリングする(図11参照)。サンプラ13から出力されたサンプリングデータは、位相比較回路14に送られるが、位相比較回路14以降の処理は上述したとおりである。

【0050】

一方、サンプラ13から出力されたサンプリングデータのうち、SCKP、SCKNでサンプリングされたデータは、シリアルデータの安定領域でサンプリングされたデータである。よって、このデータをデータ再生回路の出力とすることが可能である。図10は、この考えによって構成されたものであり、SCKP,SCKNによってサンプリングされるサンプラ13b,13dの出力を、シリパラ変換回路17とは異なるシリパラ変換回路50に入力する構成としている。このように、SCKP,SCKNによってサンプリングされたデータをシリパラ変換回路を介して出力することにより、上述したクロックリカバリ回路をデータ再生回路として使用することができる。

【0051】

図12は、サーモメータコードで表現した位相制御信号の一例を示す図である。図12に示すように、サーモメータコードでは、ビット1もしくはビット0が連続して現れ、且つ、ビットの切替が1度しか行われないことが特徴である。なお、図2において、リングレジスタ34の上段部にあるレジスタ34aに格納されているデータは、図12における位相No15として示されている。すなわち、図2の状態は、位相制御信号が第1象限と第2象限との境界部に位置していることを表している。いま、この状態からリングレジスタ34,36が時計方向に1ビット回転すると、リングレジスタ34からの出力である位相制御信号のビットは、“111……1”となり、リングレジスタ36からの出力である象限信号(IP,QP)は、(0,1)となる。すなわち、位相Noが、“15”から“16”に変化することになる。このようなサーモメータコードを用いれば、位相Noの“1”の変化に対してビット列におけるビット変化が1ビットしか起こらないため、ビット切替時の誤動作を防止する観点から非常に有効である。

【0052】

つぎに、本実施の形態にかかるクロックリカバリ回路の効果について説明する。従来のクロックリカバリ回路では、位相制御量処理回路から出力される位相制御信号が位相象限を跨ぐ制御量である場合、位相変化にオーバーシュートが発生するという問題点があった。この現象は、位相補間回路の動作が、象限信号IP,QPに対しては瞬時に反応するのに対して、サーモメータコードを使用する位相制御信号の変化に対しては瞬時に反応せず、時間遅れが発生するからである。なお、時間遅れが発生する主因は、位相補間回路を構成する定電流回路(差動回路および電流源)における配線等の寄生容量であり、配線等の寄生容量によって定電流回路が安定するまでの時間が延びてしまうからである。

【0053】

上述した時間遅れについて、具体的な例で説明する。いま、例えば図13に示すように第1象限の12番目の位相(位相No12)から第2象限の16番目の位相(位相No16)への切替制御を行う場合を考える(位相Noについては、図12を参照)。本実施の形態のクロックリカバリ回路では、位相の切替を高速なクロックで行っているため、1回の位相制御(位相補間)は1ビットずつ行われる。したがって、第1象限の12番目の位相から第2象限の16番目の位相への切替制御はオーバーシュートなしに行われる。

【0054】

これに対して、従来のクロックリカバリ回路では、象限信号IP,QPが(1,1)から(0,1)に切り替わるため、第1象限の位相である位相No12は、第2象限の位相である位相No20として認識されてしまう(位相No12と位相No20とでは、ビット0の数およびビット1の数が同数である)。したがって、位相No12→位相No16の制御を行う場合、従来のクロックリカバリ回路では、図14に示すように、位相No12→位相No20→位相No16という制御が実行されてしまい、図15に示すようなオーバーシュートが発生することになる。

【0055】

また、従来のクロックリカバリ回路では、SSCのような周波数偏差を持つシリアルデータに追従する場合、1回の位相調整量が大きいため、クロックジッタが多くなってしまうという問題点があった。例えば、位相制御量処理回路の分解能力を1/64UI分割(1UIは送信データ速度Fの逆数)とし、シリパラ変換のビット幅を10ビットとすると、位相調整の更新サイクルはF/10となる。ここで、SATA−Gen2に見られるような3Gbps、−5000ppmの周波数偏差を有するシリアルデータに追従させるためには、最大で5/64UIの位相調整を行う必要があると言われている。一方、従来のクロックリカバリ回路では、位相調整の更新サイクルは、デジタルフィルタの処理サイクル(F/10サイクル)で行っている。したがって、従来のクロックリカバリ回路の考え方では、5/64UIの位相調整はF/10サイクル毎に行う必要がある。

【0056】

これに対して、本実施の形態のクロックリカバリ回路では、位相調整の更新をデータレートのサイクル(Fサイクル)で行っているので、1回の位相調整は1/64UIで充分である(F/10サイクルに換算すれば10/64UIの位相調整を行っていることに相当する)。

【0057】

図16は、本実施の形態のクロックリカバリ回路における位相調整の様子(実線部)と、従来のクロックリカバリ回路における位相調整の様子(破線部)を示す図である。図16において、直線で示した波形K1は、SSCによる位相変化を簡略的に示したものである。本実施の形態では、従来のクロックリカバリ回路のように5/64UIの位相調整を一度に行う必要がないため、クロックジッタを減少させることが可能となる。

【0058】

以上説明したように、本実施の形態にかかるクロックリカバリ回路によれば、シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号に基づいて位相偏差信号と位相遅進信号を演算し、これらの位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力し、この位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号の位相を補間して出力することとしたので、クロックジッタを低減させることができるという効果が得られる。

【符号の説明】

【0059】

10 受信回路、11 PLL回路、12 位相補間回路、13(13a〜13d) サンプラ、14 位相比較回路、15 分周回路、16 デジタルフィルタ回路、17,50 シリパラ変換回路、18 位相追従回路、19 周波数追従回路、20 位相制御量処理回路、24 移動量決定回路、26 移動方向決定回路、28 シフトレジスタ、30 反転回路、32 論理積回路、34,36 リングレジスタ、34a,34b,36a,36b レジスタ、40 フリップフロップ、42 セレクタ

【特許請求の範囲】

【請求項1】

第1のクロック信号に同期してシリアル入力信号をサンプリングし、サンプリングデータを出力するサンプラと、

前記サンプリングデータに基づき、前記第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路と、

第2のクロック信号に同期して、前記シリアル位相情報信号をシリアルパラレル変換し、パラレル位相情報信号を出力するシリアルパラレル変換回路と、

前記パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路と、

前記位相偏差信号と前記位相遅進信号とに基づき、位相制御信号を生成し、前記第2のクロック信号より高速の第3のクロック信号に同期して、前記位相制御信号を出力する位相制御量処理回路と、

前記位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整し前記第1のクロック信号を出力する位相補間回路と、

を備えたことを特徴とするクロックリカバリ回路。

【請求項2】

前記第3のクロック信号と、前記基準クロック信号とが、同一クロック信号源からのクロック信号であることを特徴とする請求項1に記載のクロックリカバリ回路。

【請求項3】

前記位相制御量処理回路は、

前記位相偏差信号と前記位相遅進信号とに基づき、連続した0又は1のパラレル信号である位相制御量を生成し、前記第2のクロック信号に同期して、前記位相制御量を出力する移動量決定回路と、

前記位相制御量を、前記第1のクロックに同期してシリアル信号として出力するシフトレジスタと、

リングレジスタから構成され、前記シフトレジスタから出力される前記位相制御量に基づき、前記位相制御信号を出力する位相制御コード生成回路と、

前記位相偏差信号と前記位相遅進信号とに基づき、前記リングレジスタの移動方向を決定する移動方向決定回路と、

を備えることを特徴とする請求項1または2に記載のクロックリカバリ回路。

【請求項4】

前記位相遅進信号は、前記第1のクロック信号の位相を進ませる位相進み信号と、この第1のクロック信号の位相を遅らせる位相遅れ信号とを含んでおり、

前記移動方向決定回路は、前記位相進み信号に含まれる1の数の和と、前記位相遅れ信号に含まれる1の数の和との比較により、移動方向を決定することを特徴とする請求項3に記載のクロックリカバリ回路。

【請求項5】

第1のクロック信号に同期してシリアル入力信号をサンプリングし、サンプリングデータを出力するサンプラと、

前記サンプリングデータに基づき、前記第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路と、

第2のクロック信号に同期して、前記シリアル位相情報信号をシリアルパラレル変換し、パラレル位相情報信号を出力する第1のシリアルパラレル変換回路と、

前記パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路と、

前記位相偏差信号と前記位相遅進信号とに基づき、位相制御信号を生成し、前記第2のクロック信号より高速の第3のクロック信号に同期して、前記位相制御信号を出力する位相制御量処理回路と、

前記位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整し前記第1のクロック信号を出力する位相補間回路と、

前記第1のクロック信号に同期して、前記サンプリングデータをシリアルパラレル変換し、再生データを出力する第2のシリアルパラレル変換回路と、

を備えたことを特徴とするデータ再生回路。

【請求項1】

第1のクロック信号に同期してシリアル入力信号をサンプリングし、サンプリングデータを出力するサンプラと、

前記サンプリングデータに基づき、前記第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路と、

第2のクロック信号に同期して、前記シリアル位相情報信号をシリアルパラレル変換し、パラレル位相情報信号を出力するシリアルパラレル変換回路と、

前記パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路と、

前記位相偏差信号と前記位相遅進信号とに基づき、位相制御信号を生成し、前記第2のクロック信号より高速の第3のクロック信号に同期して、前記位相制御信号を出力する位相制御量処理回路と、

前記位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整し前記第1のクロック信号を出力する位相補間回路と、

を備えたことを特徴とするクロックリカバリ回路。

【請求項2】

前記第3のクロック信号と、前記基準クロック信号とが、同一クロック信号源からのクロック信号であることを特徴とする請求項1に記載のクロックリカバリ回路。

【請求項3】

前記位相制御量処理回路は、

前記位相偏差信号と前記位相遅進信号とに基づき、連続した0又は1のパラレル信号である位相制御量を生成し、前記第2のクロック信号に同期して、前記位相制御量を出力する移動量決定回路と、

前記位相制御量を、前記第1のクロックに同期してシリアル信号として出力するシフトレジスタと、

リングレジスタから構成され、前記シフトレジスタから出力される前記位相制御量に基づき、前記位相制御信号を出力する位相制御コード生成回路と、

前記位相偏差信号と前記位相遅進信号とに基づき、前記リングレジスタの移動方向を決定する移動方向決定回路と、

を備えることを特徴とする請求項1または2に記載のクロックリカバリ回路。

【請求項4】

前記位相遅進信号は、前記第1のクロック信号の位相を進ませる位相進み信号と、この第1のクロック信号の位相を遅らせる位相遅れ信号とを含んでおり、

前記移動方向決定回路は、前記位相進み信号に含まれる1の数の和と、前記位相遅れ信号に含まれる1の数の和との比較により、移動方向を決定することを特徴とする請求項3に記載のクロックリカバリ回路。

【請求項5】

第1のクロック信号に同期してシリアル入力信号をサンプリングし、サンプリングデータを出力するサンプラと、

前記サンプリングデータに基づき、前記第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路と、

第2のクロック信号に同期して、前記シリアル位相情報信号をシリアルパラレル変換し、パラレル位相情報信号を出力する第1のシリアルパラレル変換回路と、

前記パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路と、

前記位相偏差信号と前記位相遅進信号とに基づき、位相制御信号を生成し、前記第2のクロック信号より高速の第3のクロック信号に同期して、前記位相制御信号を出力する位相制御量処理回路と、

前記位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整し前記第1のクロック信号を出力する位相補間回路と、

前記第1のクロック信号に同期して、前記サンプリングデータをシリアルパラレル変換し、再生データを出力する第2のシリアルパラレル変換回路と、

を備えたことを特徴とするデータ再生回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2011−61729(P2011−61729A)

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願番号】特願2009−212290(P2009−212290)

【出願日】平成21年9月14日(2009.9.14)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願日】平成21年9月14日(2009.9.14)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]