クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明はクロック再生回路に関し、特に、外部データ信号列に同期した内部クロック信号を生成するクロック再生回路に関する。

【背景技術】

【0002】

クロック再生回路は、外部データ信号列に同期した内部クロック信号を生成するものである。外部データ信号列は、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を含む。従来のクロック再生回路は、制御電圧に基いて内部クロック信号を生成する電圧制御型発振器と、外部データ信号列の位相と内部クロック信号の位相とを比較し、比較結果を示す信号を出力する位相比較器と、位相比較器の出力信号に応答して正電流または負電流を出力するチャージポンプ回路と、チャージポンプ回路の出力電流を積分して制御電圧を発生するループフィルタとを備える(たとえば、非特許文献1,2参照)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】CHARLES R. HOGGE,JR.,“A Self Correcting Clock Recovery Circuit”,IEEE TRANSACTIONS ON ELECTRON DEVICES,VOL.ED-32,NO.12,DECEMBER 1985

【非特許文献2】Jafar Savoj and Behzad Razavi, “Design of Half-Rate Clock and Data Recovery Circuits for Optical Communication Systems”, Proceedings of the 2001 Design Automation Conference, pp. 121-126, Jun. 2001.

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来のクロック再生回路では、外部データ信号列の論理レベルが遷移する毎に位相を比較していたので、回路のオープンループゲインがデータ遷移密度に比例し、データパターンに依存するジッタが大きいと言う問題があった。また、データパターンに依存して動作電流および電源電圧が変動することも、ジッタが大きくなる原因となっていた。

【0005】

また、想定されるデータ遷移密度の変動範囲で最適なジッタ伝達特性を得るには、データ遷移密度の変動幅に応じてループフィルタのキャパシタの容量値を大きくする必要がある。このためデータ遷移密度の変動幅が大きくなるほどループフィルタの面積が増大すると言う問題があった。

【0006】

また、データ遷移密度の変動範囲は、高速シリアルインタフェースの規格が採用する符号化方式で決まる。SATA(Serial Advanced Technology Attachment)、PCI(Peripheral Component Interconnect)Express等で採用されている8B10B符号化では、同じ論理のデータが連続する数の最大値である最大ラン・レングス(Max . Run Length)が5であり、データ遷移密度の変動範囲は20%〜100%であり、データ遷移密度の最大値は最小値の5倍である。

【0007】

これに対して、64B66B符号化では、最大ラン・レングスは66であり、データ遷移密度の変動範囲は1.5%〜100%であり、データ遷移密度の最大値は最小値の約67倍にもなる。従来のクロック再生回路では、データ遷移密度の最大値が最小値の5倍である場合はクロック信号の再生が可能であるが、それが67倍になると対応不能である。

【0008】

それゆえに、この発明の主たる目的は、ジッタが小さく、面積が小さく、データ遷移密度の変動幅が大きい場合でもクロック信号を再生することが可能なクロック再生回路を提供することである。

【課題を解決するための手段】

【0009】

この発明に係るクロック再生回路は、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を受け、受けた複数のデータ信号に同期した内部クロック信号を生成するクロック再生回路であって、複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりまたは立ち下がりエッジを抽出するエッジ抽出回路と、制御電圧に基いて内部クロック信号を生成する電圧制御型発振器と、エッジ抽出回路によって抽出された各立ち上がりまたは立ち下がりエッジの位相と電圧制御型発振器によって生成された内部クロック信号の位相とを比較し、比較結果を示す信号を出力する位相比較器と、位相比較器の出力信号に応答して正電流または負電流を出力するチャージポンプ回路と、チャージポンプ回路の出力電流を積分して制御電圧を発生するループフィルタとを備えたものである。

【発明の効果】

【0010】

この発明に係るクロック再生回路では、複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりまたは立ち下がりエッジを抽出し、抽出した各立ち上がりまたは立ち下がりエッジの位相と内部クロック信号の位相とを比較する。したがって、各データ信号グループで1回だけ位相比較を行なうので、データ信号の論理レベルが遷移する毎に位相比較を行なう従来に比べ、ジッタの低減化と面積の縮小化を図ることができ、データ遷移密度の変動幅が大きい場合でもクロック信号を再生することができる。

【図面の簡単な説明】

【0011】

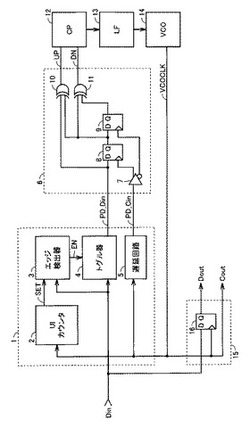

【図1】この発明の実施の形態1によるクロック再生回路の構成を示す回路ブロック図である。

【図2】図1に示したクロック再生回路の動作を示すタイムチャートである。

【図3】図1に示したUIカウンタの構成を示す回路図である。

【図4】図3に示したUIカウンタの動作を示すタイムチャートである。

【図5】図1に示したエッジ検出回路の構成を示す回路図である。

【図6】図5に示したエッジ検出回路の動作を示すタイムチャートである。

【図7】図1に示したトグル器の構成を示す回路図である。

【図8】図3に示したトグル器の動作を示すタイムチャートである。

【図9】実施の形態1の比較例を示す回路ブロック図である。

【図10】図9に示したクロック再生回路の動作を示すタイムチャートである。

【図11】この発明の実施の形態2によるクロック再生回路のエッジ検出回路の構成を示す回路図である。

【図12】図11に示したエッジ検出回路の動作を示すタイムチャートである。

【図13】図11で説明したクロック再生回路のトグル器の構成を示す回路図である。

【図14】図13に示したトグル器の動作を示すタイムチャートである。

【図15】この発明の実施の形態3によるクロック再生回路の構成を示す回路ブロック図である。

【図16】図15に示したクロック再生回路の動作を示すタイムチャートである。

【図17】この発明の実施の形態4によるUIカウンタの構成を示す回路ブロック図である。

【図18】図17に示したUIカウンタの動作を示すタイムチャートである。

【図19】この発明の実施の形態5による半導体装置の要部を示すブロック図である。

【発明を実施するための形態】

【0012】

上述のとおり、従来のクロック再生回路では、外部データ信号列の論理レベルが遷移する毎に位相比較が行なわれる。しかし、外部データ信号列の論理レベルが遷移する毎に位相比較を行なう必要はなく、クロック再生回路のループ帯域の20倍以上の周波数で位相比較を行なえば足りる。

【0013】

そこで、本願発明では、外部データ信号列に含まれる複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に、1つの立ち上がりエッジ(または立ち下がりエッジ)を抽出し、抽出した立ち上がりエッジ(または立ち下がりエッジ)の位相と内部クロック信号の位相とを比較する。したがって、位相比較器におけるデータ遷移密度を均一化することができるので、ジッタの低減化と面積の縮小化を図ることができる。また、データ遷移密度の変動幅が大きい場合でもクロック信号を再生することができる。

【0014】

たとえば、SATA Gen2では、外部データ信号列のデータレートは3Gbpsである。しかし、その外部データ信号列からクロック信号を再生する場合、ループ帯域(10MHz)の20倍である200MHzまでは位相比較周波数を下げることができる。換言すれば、位相比較器に入力されるデータ信号列のデータレートを200Mbpsまで下げることができる。

【0015】

3Gbps/200Mbps=15であるから、本願発明では、外部データ信号列に含まれる複数のデータ信号をたとえば15個ずつグループ化し、各データ信号グループ毎に、1つの立ち上がりエッジ(または立ち下がりエッジ)を抽出し、抽出した立ち上がりエッジ(または立ち下がりエッジ)の位相と内部クロック信号の位相とを比較する。

【0016】

ただし、SATA Gen2では、外部データ信号列Vinの最大ラン・レングスは5であるので、各データ信号グループ毎に1つのエッジを抽出するためには、各データ信号グループにおけるデータ信号の数を最大ラン・レングス(すなわち5)以上にする必要がある。以下、図面を用いて本願発明を詳細に説明する。

【0017】

[実施の形態1]

この発明の実施の形態1によるクロック再生回路は、図1に示すように、エッジ抽出回路1、位相比較器6、チャージポンプ回路(CP)12、ループフィルタ(LF)13、電圧制御型発振器(VCO)14、およびリタイム回路15を備える。

【0018】

エッジ抽出回路1は、外部データ信号列Vinを受ける。外部データ信号列Vinは、図2(a)〜(g)に示すように、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を含む。図2(a)〜(g)では、外部クロック信号の位相と内部クロック信号VCOCLKまたはPD_Cinとの位相が一致している状態が示されている。外部クロック信号の隣接する2つの立ち下がりエッジの間の期間で1つのデータ信号が伝送される。

【0019】

外部データ信号列Vinの最大ラン・レングスは5である。ここでは、10クロック周期を1UG(Unit Group)とする。1UGは、外部クロック信号の立ち上がりエッジで開始され、外部クロック信号の10個のパルスを含む。図2(a)〜(g)では、3つのUG1〜UG3が示されている。データ遷移(外部データ信号列Dinの論理レベルの遷移)は、1UG当たり最大で10回発生する。UG1〜UG3では、それぞれ7回、5回、2回のデータ遷移が発生している。UGのデータ遷移密度DT_Dinは、そのUGにおいて発生したデータ遷移の回数と、発生し得るデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_Dinは、それぞれ7/10,5/10,2/10である。なお、図面および説明の簡単化のため、図2(a)〜(g)では回路の遅延時間は0とされている。

【0020】

エッジ抽出回路1は、各UG毎に、外部データ信号列Dinの最初の立ち上がりエッジを抽出する。すなわち、エッジ抽出回路1は、図1に示すように、UI(Unit Interval)カウンタ2、エッジ検出器3、トグル器4、および遅延回路5を含む。

【0021】

UIカウンタ2は、図3に示すように、フリップフロップ20,23,24,26、インバータ21,25,27、およびNANDゲート22を含む。フリップフロップ20のクロック端子は内部クロック信号VCOCLKを受ける。フリップフロップ20の出力信号φ20は、インバータ21を介してNANDゲート22の一方入力ノードに与えられる。NANDゲート22の出力信号φ22はフリップフロップ23のデータ入力端子に与えられ、フリップフロップ23の出力信号φ23はフリップフロップ24のデータ入力端子に与えられる。

【0022】

フリップフロップ24の出力信号φ24は、NANDゲート22の他方入力ノードに与えられるとともに、インバータ25を介してフリップフロップ20のデータ入力端子に与えられる。内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ20,23,24の各々は入力信号を保持および出力する。

【0023】

また、フリップフロップ20の出力信号φ20は、フリップフロップ26のクロック端子に与えられる。フリップフロップ26の出力信号は、インバータ27を介してフリップフロップ26のデータ入力端子に与えられる。信号φ20が「L」レベルから「H」レベルに立ち上げられると、フリップフロップ26は入力信号を保持および出力する。フリップフロップ23の出力信号は、UIカウンタ2の出力信号SETとなる。

【0024】

図4(a)〜(f)は、それぞれ信号VCOCLK,φ20,φ22,φ23,φ24,SETを示すタイムチャートである。信号φ20,φ22,φ23,φ24の各々は、内部クロック信号VCOCLKの5倍の周期を有するクロック信号となる。信号SETは、内部クロック信号VCOの10倍の周期を有するクロック信号となる。各UGにおいて、内部クロック信号VCOCLKの1番目の立ち上がりエッジに応答して信号SETが「H」レベルに立ち上げられ、内部クロック信号VCOCLKの5番目の立ち上がりエッジに応答して信号SETが「L」レベルに立ち下げられる。すなわち、内部クロック信号VCOCLKを10倍に分周した信号が信号SETとなる。

【0025】

エッジ検出器3は、信号SETの立ち上がりエッジに応答して信号ENを「L」レベルから「H」レベルに立ち上げた後、外部データ信号列Dinの最初の立ち上がりエッジに応答して信号ENを「H」レベルから「L」レベルに立ち下げる。

【0026】

エッジ検出器3は、図5に示すように、フリップフロップ30,31、ゲート回路32,33、セレクタ34,35、およびインバータ36,37を含む。フリップフロップ30のデータ入力端子は「H」レベル(電源電圧VCC)の信号を受け、そのクロック端子は外部データ信号列Dinを受け、そのリセット端子はゲート回路32の出力信号を受ける。リセット端子が「L」レベルにされると、フリップフロップ30の出力信号Din_Qは「H」レベルにリセットされる。外部データ信号列Dinが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ30の出力信号Din_Qは「L」レベルに立ち下げられる。

【0027】

ゲート回路32は、信号SELとリセット信号RESETの論理和信号の反転信号を出力する。リセット信号RESETが「H」レベルである場合は、ゲート回路32は「L」レベルの信号を出力する。リセット信号RESETが「L」レベルである場合は、ゲート回路32はインバータとして動作し、信号SELの反転信号を出力する。

【0028】

フリップフロップ31のデータ入力端子は「H」レベルの信号を受け、そのクロック端子は信号SETを受け、そのリセット端子はゲート回路33の出力信号を受ける。リセット端子が「L」レベルにされると、フリップフロップ31の出力信号SET_Qは「L」レベルにリセットされる。信号SETが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ31の出力信号SET_Qは「H」レベルに立ち上げられる。

【0029】

ゲート回路33は、信号SELの反転信号とリセット信号RESETとの論理和信号の反転信号を出力する。リセット信号RESETが「H」レベルである場合は、ゲート回路32は「L」レベルの信号を出力する。リセット信号RESETが「L」レベルである場合は、ゲート回路32はバッファとして動作し、信号SELを出力する。

【0030】

セレクタ34は、フリップフロップ30,31の出力信号Din_Q,SET_Qを受け、信号SELが「L」レベル(0)である場合は信号Din_Qを通過させ、信号SELが「H」レベル(1)である場合は信号SEL_Qを通過させる。セレクタ34を通過した信号は、インバータ36,37で遅延されてエッジ検出器3の出力信号ENとなる。

【0031】

セレクタ35は、信号ENと「H」レベルの信号とを受け、リセット信号RESETが「L」レベルである場合はリセット信号ENの反転信号を通過させ、リセット信号RESETが「H」レベルである場合は「H」レベルの信号を通過させる。セレクタ35を通過した信号が信号SELとなる。

【0032】

図6(a)〜(g)は、それぞれ信号RESET,Din,SET,Din_Q,SET_Q,SEL,ENを示すタイムチャートである。リセット信号RESETが「H」レベルである場合は、ゲート回路32,33の出力信号がともに「L」レベルとなり、フリップフロップ30,31がリセットされる。また、信号Din_Q,SELが「H」レベルになり、信号SET_Q,ENが「L」レベルになる。

【0033】

リセット信号RESETが「L」レベルにされると、ゲート回路32がインバータとして動作し、ゲート回路33がバッファとして動作する。信号SELが「H」レベルであるので、フリップフロップ31のリセットが解除される。

【0034】

時刻t0において信号SETが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ31の出力信号SET_Qが「L」レベルから「H」レベルに立ち上げられる。これに応じて信号ENが「H」レベルに立ち上げられ、信号SELが「L」レベルに立ち下げられ、フリップフロップ31がリセットされるとともに、フリップフロップ30のリセットが解除される。したがって、信号SET_Qは、信号SETの立ち上がりエッジに応答してパルス的に「H」レベルになる。

【0035】

次に、外部データ信号列Dinが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ30の出力信号Din_Qが「H」レベルから「L」レベルに立ち下げられる。これに応じて信号ENが「L」レベルに立ち下げられ、信号SELが「H」レベルに立ち上げられ、フリップフロップ30がリセットされるとともに、フリップフロップ31のリセットが解除される。したがって、信号Din_Qは、外部データ信号列Dinの最初の立ち上がりエッジに応答してパルス的に「L」レベルになる。また、信号ENは、各UGにおいて、信号SETの立ち上がりエッジに応答して「L」レベルから「H」レベルに立ち上げられ、外部データ信号列Dinの最初の立ち上がりエッジに応答して「H」レベルから「L」レベルに立ち下げられる。

【0036】

トグル器4は、図7に示すように、セレクタ40、フリップフロップ41、およびインバータ42を含む。セレクタ40は、「H」レベルの信号と外部データ信号列Dinを受け、信号ENが「L」レベルである場合は「H」レベルの信号を通過させ、信号ENが「H」レベルである場合は外部データ信号列Dinを通過させる。セレクタ40を通過した信号は、信号INとなり、フリップフロップ41のクロック端子に与えられる。フリップフロップ41の出力信号PD_Dinは、インバータ42を介してフリップフロップ41のデータ入力端子に与えられる。

【0037】

図8(a)〜(d)は、信号Din,EN,IN,PD_Dinを示すタイムチャートである。信号ENが「H」レベルである期間は、外部データ信号列Dinがセレクタ40を通過して信号INとなる。信号INが「L」レベルから「H」レベルに立ち上げられる毎にフリップフロップ41の出力信号PD_Dinの論理レベルが反転される。信号ENが「L」レベルである期間は、「H」レベルの信号がセレクタ40を通過して信号INとなる。フリップフロップ41の出力信号PD_Dinは、信号ENが「L」レベルに立ち下げられる前の論理レベルに維持される。

【0038】

なお、図5および図6(a)〜(g)で示したように、信号ENは「H」レベルに立ち上げられた後に、外部データ信号列Dinの最初の立ち上がりエッジに応答して「L」レベルに立ち下げられる。したがって、図2(a)〜(g)に示すように、信号PD_Dinの論理レベルは、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジに応答して反転する。

【0039】

信号PD_Dinのデータ遷移(信号PD_Dinの論理レベルの遷移)は、1UG毎に必ず1回発生する。UGのデータ遷移密度DT_PD_Dinは、そのUGにおいて発生した信号PD_Dinのデータ遷移の回数(1回)と、外部データ信号列Dinのデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_PD_Dinは、ともに1/10となる。

【0040】

図1に戻って、遅延回路5は、内部クロック信号VCOCLKを所定の遅延時間だけ遅延させてクロック信号PD_Cinを生成する。遅延回路5の遅延時間は、トグル器4の遅延時間に等しく設定される。

【0041】

位相比較器6は、信号PD_Dinの位相とクロック信号VCOCLKの位相とを比較し、比較結果を示す信号UP,DNを出力する。すなわち、位相比較器6は、バッファ回路7、フリップフロップ8,9、およびEX−ORゲート10,11を含む。バッファ回路7は、クロック信号PD_Cinおよびその相補信号を出力する。

【0042】

フリップフロップ8のクロック端子はバッファ回路7からのクロック信号PD_Cinを受け、そのデータ入力端子は信号PD_Dinを受ける。フリップフロップ9のクロック端子はバッファ回路7からのクロック信号PD_Cinの相補信号を受け、そのデータ入力端子はフリップフロップ8の出力信号を受ける。EX−ORゲート10は、信号PD_Dinとフリップフロップ8の出力信号とを受け、信号UPを出力する。EX−ORゲート11は、フリップフロップ8,9の出力信号を受け、信号DNを出力する。

【0043】

図2(a)〜(g)に示すように、信号PD_Dinとクロック信号PD_Cinとの位相差が信号UPのパルス幅となり、クロック信号PD_Cinの半周期が信号DNのパルス幅となる。

【0044】

チャージポンプ回路12は、信号UPのパルス幅に比例した正電流をループフィルタ13に供給するとともに、信号DNのパルス幅に比例した負電流をループフィルタ13に供給する。ループフィルタ13は、所定容量値のキャパシタと所定抵抗値の抵抗素子を含み、チャージポンプ回路12の出力電流を積分して制御電圧を生成する。電圧制御型発振器14は、ループフィルタ13で生成された制御電圧に応じた周波数で発振して内部クロック信号VCOCLKを出力する。

【0045】

リタイム回路15は、フリップフロップ16を含む。フリップフロップ16のクロック端子は内部クロック信号VCOCLKを受け、そのデータ入力端子は外部データ信号列Dinを受ける。フリップフロップ16は、内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられる毎に外部クロック信号列Dinを保持および出力する。クロック再生回路は、フリップフロップ16の出力信号を内部データ信号列Doutとして出力するとともに、電圧制御型発振器14の出力信号VCOCLKを内部クロック信号Coutとして出力する。

【0046】

[比較例]

図9は、実施の形態1の比較例となるクロック再生回路の構成を示す回路ブロック図であって、図1と対比される図である。図9において、このクロック再生回路が図1のクロック再生回路と異なる点は、エッジ抽出回路1およびリタイム回路15が除去されている点である。外部データ信号列Dinおよび内部クロック信号VCOCLKは、位相比較器6に直接入力される。バッファ回路7で生成されたクロック信号VCOCLKの相補信号が内部クロック信号Coutとして出力され、フリップフロップ9の出力信号が内部データ信号列Doutとして出力される。

【0047】

図10(a)〜(d)は、図9に示したクロック再生回路の動作を示すタイムチャートであって、図2(a)〜(g)と対比される図である。外部データ信号列Vinは、図10(a)〜(d)に示すように、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を含む。図10(a)〜(d)では、外部クロック信号の位相と内部クロック信号VCOCLKとの位相が一致している状態が示されている。外部クロック信号の隣接する2つの立ち下がりエッジの間の期間で1つのデータ信号が伝送される。

【0048】

外部データ信号列Vinの最大ラン・レングスは5である。ここでは、5クロック周期を1UGとする。1UGは、外部クロック信号の立ち上がりエッジで開始され、外部クロック信号の5個のパルスを含む。図10(a)〜(d)では、6つのUG1〜UG6が示されている。データ遷移(外部データ信号列Dinの論理レベルの遷移)は、1UG当たり最大で5回発生する。UG1〜UG6では、それぞれ5回、2回、4回、1回、1回、1回のデータ遷移が発生している。UGのデータ遷移密度DT_Dinは、そのUGにおいて発生したデータ遷移の回数と、発生し得るデータ遷移の最大値(5回)との比である。UG1〜UG6のデータ遷移密度DT_Dinは、それぞれ5/5,2/5,4/5,1/5,1/5,1/5である。なお、図面および説明の簡単化のため、図2(a)〜(g)では回路の遅延時間は0とされている。

【0049】

このクロック再生回路では、外部データ信号列Dinの論理レベルが変化する毎に信号UP,DNの各々がパルス的に変化する。したがって、外部データ信号列Dinの論理レベルが変化する回数と信号UP,DNの各々のパルス数とは同じである。

【0050】

この比較例では、外部データ信号列Dinの論理レベルが遷移する毎に位相比較が行なわれ、オープンループゲインがデータ遷移密度DT_Dinに比例するため、データパターンに依存するジッタが大きいと言う問題がある。また、データパターンに依存して動作電流および電源電圧が変動することも、ジッタが大きくなる原因となる。

【0051】

また、想定されるデータ遷移密度DT_Dinの変動範囲で最適なジッタ伝達特性を得るには、データ遷移密度DT_Dinの変動幅に応じてループフィルタ13のキャパシタの容量値を大きくする必要がある。このためデータ遷移密度DT_Dinの変動幅が大きくなるほどループフィルタ13の面積が増大すると言う問題がある。

【0052】

また、データ遷移密度DT_Dinの変動範囲は、高速シリアルインタフェースの規格が採用する符号化方式で決まる。この比較例で採用されている8B10B符号化では、最大ラン・レングスが5であり、データ遷移密度DT_Dinの変動範囲は20%〜100%であり、データ遷移密度DT_Dinの最大値は最小値の5倍である。

【0053】

しかし、64B66B符号化では、最大ラン・レングスは66であり、データ遷移密度の変動範囲は1.5%〜100%であり、データ遷移密度の最大値は最小値の約67倍にもなる。図9のクロック再生回路では、データ遷移密度の最大値が最小値の5倍である場合は対応可能であるが、それが67倍になると対応不能であり、クロック信号を再生することはできない。

【0054】

これに対して本願発明では、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジを抽出し、抽出した立ち上がりエッジに同期した信号PD_Dinの位相と内部クロック信号PD_Cinの位相とを比較するので、位相比較器6におけるデータ遷移密度DT_PD_Dinは一定値になる。したがって、外部データ信号列Dinのデータパターンに依存するジッタを小さくすることができる。また、ループフィルタ13のキャパシタの容量値および面積を小さくすることができる。また、外部データ信号列Dinのデータ遷移密度DT_Dinの変動幅が大きい場合でも、クロック信号を再生することができる。

【0055】

[実施の形態2]

実施の形態1では、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジを抽出し、抽出した立ち上がりエッジに同期した信号PD_Dinの位相と内部クロック信号PD_Cinの位相とを比較した。

【0056】

これに対して本実施の形態2では、各UGにおいて外部データ信号列Dinの最初の立ち下がりエッジを抽出し、抽出した立ち下がりエッジに同期した信号PD_Dinの位相と内部クロック信号PD_Cinの位相とを比較する。本実施の形態2のクロック再生回路は、図1のクロック再生回路のエッジ検出器3およびトグル器4をそれぞれエッジ検出器45およびトグル器47で置換したものである。

【0057】

図11はエッジ検出器45の構成を示す回路図であって、図5と対比される図である。このエッジ検出器45は、図5のエッジ検出器3のフリップフロップ30をフリップフロップ46で置換したものである。フリップフロップ46は、ゲート回路32の出力信号が「L」レベルにされると、リセットされて「H」レベルの信号を出力する。また、フリップフロップ46は、外部データ信号列Dinが「H」レベルから「L」レベルに立ち下げられると、「H」レベルの信号を保持し、その反転信号である「L」レベルの信号を出力する。

【0058】

図12(a)〜(g)はエッジ検出器45の動作を示すタイムチャートであって、図6(a)〜(g)と対比される図である。図12(a)〜(g)において、リセット信号RESETが「H」レベルである場合は、ゲート回路32,33の出力信号がともに「L」レベルとなり、フリップフロップ31,46がリセットされる。また、信号Din_Q,SELが「H」レベルになり、信号SET_Q,ENが「L」レベルになる。

【0059】

リセット信号RESETが「L」レベルにされると、ゲート回路32がインバータとして動作し、ゲート回路33がバッファとして動作する。信号SELが「H」レベルであるので、フリップフロップ31のリセットが解除される。

【0060】

時刻t0において信号SETが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ31の出力信号SET_Qが「L」レベルから「H」レベルに立ち上げられる。これに応じて信号ENが「H」レベルに立ち上げられ、信号SELが「L」レベルに立ち下げられ、フリップフロップ31がリセットされるとともに、フリップフロップ46のリセットが解除される。したがって、信号SET_Qは、信号SETの立ち上がりエッジに応答してパルス的に「H」レベルになる。

【0061】

次に、外部データ信号列Dinが「H」レベルから「L」レベルに立ち下げられると、フリップフロップ46の出力信号Din_Qが「H」レベルから「L」レベルに立ち下げられる。これに応じて信号ENが「L」レベルに立ち下げられ、信号SELが「H」レベルに立ち上げられ、フリップフロップ46がリセットされるとともに、フリップフロップ31のリセットが解除される。したがって、信号Din_Qは、外部データ信号列Dinの最初の立ち下がりエッジに応答してパルス的に「L」レベルになる。また、信号ENは、各UGにおいて、信号SETの立ち上がりエッジに応答して「L」レベルから「H」レベルに立ち上げられ、外部データ信号列Dinの最初の立ち下がりエッジに応答して「H」レベルから「L」レベルに立ち下げられる。

【0062】

図13はトグル器47の構成を示す回路図であって、図7と対比される図である。このトグル器47は、図7のトグル器4の電源電圧VCCを接地電圧VSSで置換し、フリップフロップ41をフリップフロップ48で置換したものである。

【0063】

セレクタ40は、「L」レベル(接地電圧VSS)の信号と外部データ信号列Dinを受け、信号ENが「L」レベルである場合は「L」レベルの信号を通過させ、信号ENが「H」レベルである場合は外部データ信号列Dinを通過させる。セレクタ40を通過した信号は、信号INとなり、フリップフロップ48のクロック端子に与えられる。フリップフロップ48の出力信号PD_Dinは、インバータ42を介してフリップフロップ48のデータ入力端子に与えられる。

【0064】

図14(a)〜(d)は、信号Din,EN,IN,PD_Dinを示すタイムチャートであって、図8(a)〜(d)と対比される図である。信号ENが「H」レベルである期間は、外部データ信号列Dinがセレクタ40を通過して信号INとなる。信号INが「H」レベルから「L」レベルに立ち下げられる毎にフリップフロップ48の出力信号PD_Dinの論理レベルが反転される。信号ENが「L」レベルである期間は、「L」レベルの信号がセレクタ40を通過して信号INとなる。フリップフロップ48の出力信号PD_Dinは、信号ENが「L」レベルに立ち下げられる前の論理レベルに維持される。

【0065】

なお、図11および図12(a)〜(g)で示したように、信号ENは「H」レベルに立ち上げられた後に、外部データ信号列Dinの最初の立ち下がりエッジに応答して「L」レベルに立ち下げられる。したがって、信号PD_Dinの論理レベルは、各UGにおいて外部データ信号列Dinの最初の立ち下がりエッジに応答して反転する。

【0066】

他の構成および動作は、実施の形態1と同じであるので、その説明は繰り返さない。この実施の形態2でも、実施の形態1と同じ効果が得られる。

【0067】

[実施の形態3]

図15は、この発明の実施の形態3によるクロック再生回路の構成を示す回路ブロック図であって、図1と対比される図である。また図16(a)〜(i)は、図15に示したクロック再生回路の動作を示すタイムチャートであって、図2(a)〜(g)と対比される図である。

【0068】

図15において、このクロック再生回路は、エッジ抽出回路1R,1F、位相比較器6R,6F、チャージポンプ回路12R,12F、ループフィルタ13、電圧制御型発振器14、およびリタイム回路15を備える。

【0069】

外部データ信号列Vinは、図2(a)〜(g)で説明した通りである。UG1〜UG3のデータ遷移密度DT_Dinは、それぞれ7/10,5/10,2/10である。なお、図面および説明の簡単化のため、図16(a)〜(i)では回路の遅延時間は0とされている。

【0070】

エッジ抽出回路1Rは、図1のエッジ抽出回路1と同じ構成であり、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転する信号PD_DinRと、内部クロック信号VCOCLKを所定時間だけ遅延させたクロック信号PD_CinRとを生成する。

【0071】

信号PD_DinRのデータ遷移(信号PD_DinRの論理レベルの遷移)は、1UG毎に必ず1回発生する。UGのデータ遷移密度DT_PD_DinRは、そのUGにおいて発生した信号PD_DinRのデータ遷移の回数(1回)と、外部データ信号列Dinのデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_PD_DinRは、ともに1/10となる。

【0072】

エッジ抽出回路1Fは、実施の形態2のクロック再生回路のエッジ抽出回路と同じ構成であり、各UGにおいて外部データ信号列Dinの最初の立ち下がりエッジに応答して論理レベルが反転する信号PD_DinFと、内部クロック信号VCOCLKを所定時間だけ遅延させたクロック信号PD_CinFとを生成する。

【0073】

信号PD_DinFのデータ遷移(信号PD_DinFの論理レベルの遷移)は、1UG毎に必ず1回発生する。UGのデータ遷移密度DT_PD_DinFは、そのUGにおいて発生した信号PD_DinFのデータ遷移の回数(1回)と、外部データ信号列Dinのデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_PD_DinFは、ともに1/10となる。したがって、DT_PD_DinRとDT_PD_DinFの和であるDT_PDは2/10となる。

【0074】

位相比較器6Rは、エッジ抽出回路1Rからの信号PD_DinR,PD_CinRの位相を比較し、比較結果を示す信号UPR,DNRを生成する。信号PD_DinRとクロック信号PD_CinRとの位相差が信号UPRのパルス幅となり、クロック信号PD_CinRの半周期が信号DNRのパルス幅となる。

【0075】

位相比較器6Fは、エッジ抽出回路1Fからの信号PD_DinF,PD_CinFの位相を比較し、比較結果を示す信号UPF,DNFを生成する。信号PD_DinFとクロック信号PD_CinFとの位相差が信号UPFのパルス幅となり、クロック信号PD_CinFの半周期が信号DNFのパルス幅となる。

【0076】

チャージポンプ回路12Rは、信号UPRのパルス幅に比例した正電流をループフィルタ13に供給するとともに、信号DNRのパルス幅に比例した負電流をループフィルタ13に供給する。チャージポンプ回路12Fは、信号UPFのパルス幅に比例した正電流をループフィルタ13に供給するとともに、信号DNFのパルス幅に比例した負電流をループフィルタ13に供給する。

【0077】

ループフィルタ13は、チャージポンプ回路12R,12Fの出力電流を積分して制御電圧を生成する。電圧制御型発振器14は、ループフィルタ13で生成された制御電圧に応じた周波数で発振して内部クロック信号VCOCLKを出力する。リタイム回路15は、図1で示したものと同じである。

【0078】

この実施の形態3では、実施の形態1と同じ効果が得られる他、実施の形態1と比べてチャージポンプ回路の出力電流を時間軸方向に分散させることができ、電源電圧の変動を抑制することができる。

【0079】

[実施の形態4]

図17は、この発明の実施の形態4によるクロック再生回路のUIカウンタ50の構成を示す回路図である。図17において、このUIカウンタ50は、フリップフロップ51,54、加算器52、セレクタ53、およびNORゲート55を含む。

【0080】

フリップフロップ51のデータ入力端子は信号UI_Regを受け、そのクロック端子は内部クロック信号VCOCLKを受ける。信号UI_Regは、UIカウント数Nを設定する信号であり、複数ビットのデータ信号を含む。UIカウント数Nは、たとえばレジスタに格納され、書き換え可能になっている。

【0081】

加算器52は、フリップフロップ54の出力信号STATEに−1を加算する。セレクタ53は、加算器52の出力信号とフリップフロップ51の出力信号とを受ける。信号SETが「L」レベルである場合は、加算器52の出力信号がセレクタ53を通過し、信号SETが「H」レベルである場合は、フリップフロップ51の出力信号がセレクタ53を通過する。フリップフロップ54のデータ入力端子はセレクタ53の出力信号を受け、そのクロック端子は内部クロック信号VCOCLKを受ける。NORゲート55は、フリップフロップ54の出力信号STATEを受け、信号SETを出力する。

【0082】

図18(a)〜(c)は、それぞれ信号VCOCLK,STATE,SETを示すタイムチャートである。内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられる毎に、フリップフロップ51は信号UI_Regを保持および出力し、フリップフロップ54はセレクタ53の出力信号を保持および出力する。

【0083】

信号STATEが0でない場合は、信号SETが「L」レベルになり、加算器52の出力信号がセレクタ53を通過してフリップフロップ54のデータ入力端子に入力される。内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられる毎に、信号STATEの値がデクレメント(−1)される。信号STATEの値が0になると、信号SETが「L」レベルから「H」レベルに立ち上げられ、信号UI_Regがセレクタ53を通過してフリップフロップ54に与えられる。次に、内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられると、信号STATEがN−1にリセットされ、信号SETが「L」レベルに立ち下げられる。他の構成および動作は、実施の形態1と同じであるので、その説明は繰り返さない。

【0084】

この実施の形態4では、実施の形態1と同じ効果が得られる他、UIカウント数Nを所望の値に変更することができる。

【0085】

なお、クロック再生回路のループ帯域は規格で定められており、10MHz程度である。そのため、UIカウント数Nを大きくした場合、それに応じてチャージポンプ回路12のゲインを大きくし、ループゲインを一定値に維持する必要がある。そこで、実施の形態4の変更例では、UIカウント数Nに応じてゲインが変更されるチャージポンプ回路でチャージポンプ回路12が置換される。

【0086】

[実施の形態5]

図19は、この発明の実施の形態5による半導体装置の要部を示すブロック図である。図19において、この半導体装置は、入力端子T1,T4,T5、出力端子T2,T3、受信回路(RxFE)60、クロック再生回路(CDR)61、シリアル/パラレル変換回路(DES)62、ロジック回路63、PLL(Phase Locked Loop)回路64、パラレル/シリアル変換回路(SER)65、および送信回路(TxFE)66を備える。

【0087】

受信回路60は、外部から入力端子T4,T5を介して与えられた差動信号RXP,RXTをシングルエンドのデータ信号に変換する。クロック再生回路61は、実施の形態1〜4のうちのいずれかの実施の形態のクロック再生回路であり、受信回路60からの外部データ信号列Dinに基いて内部データ信号列Doutおよび内部クロック信号Coutを生成する。内部データ信号列Doutは、内部クロック信号Coutに同期してシリアルに伝送される複数のデータ信号を含む。

【0088】

シリアル/パラレル変換回路62は、内部クロック信号Coutに同期して動作し、内部データ信号列Doutに含まれる複数のデータ信号をNビットずつグループ化し、Nビット幅のパラレルデータ信号列に変換する。シリアル/パラレル変換回路62は、Nビット幅のパラレルデータ信号列と、それに同期したクロック信号φ62をロジック回路63に与える。

【0089】

ロジック回路63は、シリアル/パラレル変換回路62からのパラレルデータ信号列をクロック信号φ62に同期して取り込み、取り込んだデータ信号に基いて所定の動作を行なう。

【0090】

また、PLL回路64は、外部から入力端子T1を介して与えられる参照クロック信号REFCLKに応答して内部クロック信号φ64を生成し、生成した内部クロック信号φ64をロジック回路63およびパラレル/シリアル変換回路65に与える。

【0091】

ロジック回路63は、PLL回路64からの内部クロック信号φ64に同期して動作する。また、ロジック回路63は、所定の動作を行なってNビット幅のパラレルデータ信号列を生成し、生成したパラレルデータ信号列と、それに同期したクロック信号φ63とをパラレル/シリアル変換回路65に与える。

【0092】

パラレル/シリアル変換回路65は、ロジック回路63からのNビット幅のパラレルデータ信号をクロック信号φ63に同期して取り込み、取り込んだNビット幅のパラレルデータ信号列を1ビット幅のデータ信号列に変換し、そのデータ信号列を内部クロック信号φ64に同期して出力する。送信回路(TxFE)66は、パラレル/シリアル変換回路65からのデータ信号を差動信号TXP,TXNに変換して出力端子T2,T3に出力する。この実施の形態5では、実施の形態1〜4と同じ効果が得られる。

【0093】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0094】

1,1R,1F エッジ抽出回路、2,50 UIカウンタ、3,45 エッジ検出器、4,47 トグル器、5 遅延回路、6,6R,6F 位相比較器、7 バッファ回路、8,9,16,20,23,24,26,30,31,41,46,48,51,54 フリップフロップ、10,11 EX−ORゲート、12,12R,12F チャージポンプ回路、13 ループフィルタ、14 電圧制御型発振器、15 リタイム回路、21,25,27,36,37,42 インバータ、22 NANDゲート、32,33 ゲート回路、34,35,40,53 セレクタ、55 NORゲート、60 受信回路、61 クロック再生回路、62 シリアル/パラレル変換回路、63 ロジック回路、64 PLL回路、65 パラレル/シリアル変換回路、66 送信回路、T1,T4,T5 入力端子、T2,T3 出力端子。

【技術分野】

【0001】

この発明はクロック再生回路に関し、特に、外部データ信号列に同期した内部クロック信号を生成するクロック再生回路に関する。

【背景技術】

【0002】

クロック再生回路は、外部データ信号列に同期した内部クロック信号を生成するものである。外部データ信号列は、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を含む。従来のクロック再生回路は、制御電圧に基いて内部クロック信号を生成する電圧制御型発振器と、外部データ信号列の位相と内部クロック信号の位相とを比較し、比較結果を示す信号を出力する位相比較器と、位相比較器の出力信号に応答して正電流または負電流を出力するチャージポンプ回路と、チャージポンプ回路の出力電流を積分して制御電圧を発生するループフィルタとを備える(たとえば、非特許文献1,2参照)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】CHARLES R. HOGGE,JR.,“A Self Correcting Clock Recovery Circuit”,IEEE TRANSACTIONS ON ELECTRON DEVICES,VOL.ED-32,NO.12,DECEMBER 1985

【非特許文献2】Jafar Savoj and Behzad Razavi, “Design of Half-Rate Clock and Data Recovery Circuits for Optical Communication Systems”, Proceedings of the 2001 Design Automation Conference, pp. 121-126, Jun. 2001.

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来のクロック再生回路では、外部データ信号列の論理レベルが遷移する毎に位相を比較していたので、回路のオープンループゲインがデータ遷移密度に比例し、データパターンに依存するジッタが大きいと言う問題があった。また、データパターンに依存して動作電流および電源電圧が変動することも、ジッタが大きくなる原因となっていた。

【0005】

また、想定されるデータ遷移密度の変動範囲で最適なジッタ伝達特性を得るには、データ遷移密度の変動幅に応じてループフィルタのキャパシタの容量値を大きくする必要がある。このためデータ遷移密度の変動幅が大きくなるほどループフィルタの面積が増大すると言う問題があった。

【0006】

また、データ遷移密度の変動範囲は、高速シリアルインタフェースの規格が採用する符号化方式で決まる。SATA(Serial Advanced Technology Attachment)、PCI(Peripheral Component Interconnect)Express等で採用されている8B10B符号化では、同じ論理のデータが連続する数の最大値である最大ラン・レングス(Max . Run Length)が5であり、データ遷移密度の変動範囲は20%〜100%であり、データ遷移密度の最大値は最小値の5倍である。

【0007】

これに対して、64B66B符号化では、最大ラン・レングスは66であり、データ遷移密度の変動範囲は1.5%〜100%であり、データ遷移密度の最大値は最小値の約67倍にもなる。従来のクロック再生回路では、データ遷移密度の最大値が最小値の5倍である場合はクロック信号の再生が可能であるが、それが67倍になると対応不能である。

【0008】

それゆえに、この発明の主たる目的は、ジッタが小さく、面積が小さく、データ遷移密度の変動幅が大きい場合でもクロック信号を再生することが可能なクロック再生回路を提供することである。

【課題を解決するための手段】

【0009】

この発明に係るクロック再生回路は、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を受け、受けた複数のデータ信号に同期した内部クロック信号を生成するクロック再生回路であって、複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりまたは立ち下がりエッジを抽出するエッジ抽出回路と、制御電圧に基いて内部クロック信号を生成する電圧制御型発振器と、エッジ抽出回路によって抽出された各立ち上がりまたは立ち下がりエッジの位相と電圧制御型発振器によって生成された内部クロック信号の位相とを比較し、比較結果を示す信号を出力する位相比較器と、位相比較器の出力信号に応答して正電流または負電流を出力するチャージポンプ回路と、チャージポンプ回路の出力電流を積分して制御電圧を発生するループフィルタとを備えたものである。

【発明の効果】

【0010】

この発明に係るクロック再生回路では、複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりまたは立ち下がりエッジを抽出し、抽出した各立ち上がりまたは立ち下がりエッジの位相と内部クロック信号の位相とを比較する。したがって、各データ信号グループで1回だけ位相比較を行なうので、データ信号の論理レベルが遷移する毎に位相比較を行なう従来に比べ、ジッタの低減化と面積の縮小化を図ることができ、データ遷移密度の変動幅が大きい場合でもクロック信号を再生することができる。

【図面の簡単な説明】

【0011】

【図1】この発明の実施の形態1によるクロック再生回路の構成を示す回路ブロック図である。

【図2】図1に示したクロック再生回路の動作を示すタイムチャートである。

【図3】図1に示したUIカウンタの構成を示す回路図である。

【図4】図3に示したUIカウンタの動作を示すタイムチャートである。

【図5】図1に示したエッジ検出回路の構成を示す回路図である。

【図6】図5に示したエッジ検出回路の動作を示すタイムチャートである。

【図7】図1に示したトグル器の構成を示す回路図である。

【図8】図3に示したトグル器の動作を示すタイムチャートである。

【図9】実施の形態1の比較例を示す回路ブロック図である。

【図10】図9に示したクロック再生回路の動作を示すタイムチャートである。

【図11】この発明の実施の形態2によるクロック再生回路のエッジ検出回路の構成を示す回路図である。

【図12】図11に示したエッジ検出回路の動作を示すタイムチャートである。

【図13】図11で説明したクロック再生回路のトグル器の構成を示す回路図である。

【図14】図13に示したトグル器の動作を示すタイムチャートである。

【図15】この発明の実施の形態3によるクロック再生回路の構成を示す回路ブロック図である。

【図16】図15に示したクロック再生回路の動作を示すタイムチャートである。

【図17】この発明の実施の形態4によるUIカウンタの構成を示す回路ブロック図である。

【図18】図17に示したUIカウンタの動作を示すタイムチャートである。

【図19】この発明の実施の形態5による半導体装置の要部を示すブロック図である。

【発明を実施するための形態】

【0012】

上述のとおり、従来のクロック再生回路では、外部データ信号列の論理レベルが遷移する毎に位相比較が行なわれる。しかし、外部データ信号列の論理レベルが遷移する毎に位相比較を行なう必要はなく、クロック再生回路のループ帯域の20倍以上の周波数で位相比較を行なえば足りる。

【0013】

そこで、本願発明では、外部データ信号列に含まれる複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に、1つの立ち上がりエッジ(または立ち下がりエッジ)を抽出し、抽出した立ち上がりエッジ(または立ち下がりエッジ)の位相と内部クロック信号の位相とを比較する。したがって、位相比較器におけるデータ遷移密度を均一化することができるので、ジッタの低減化と面積の縮小化を図ることができる。また、データ遷移密度の変動幅が大きい場合でもクロック信号を再生することができる。

【0014】

たとえば、SATA Gen2では、外部データ信号列のデータレートは3Gbpsである。しかし、その外部データ信号列からクロック信号を再生する場合、ループ帯域(10MHz)の20倍である200MHzまでは位相比較周波数を下げることができる。換言すれば、位相比較器に入力されるデータ信号列のデータレートを200Mbpsまで下げることができる。

【0015】

3Gbps/200Mbps=15であるから、本願発明では、外部データ信号列に含まれる複数のデータ信号をたとえば15個ずつグループ化し、各データ信号グループ毎に、1つの立ち上がりエッジ(または立ち下がりエッジ)を抽出し、抽出した立ち上がりエッジ(または立ち下がりエッジ)の位相と内部クロック信号の位相とを比較する。

【0016】

ただし、SATA Gen2では、外部データ信号列Vinの最大ラン・レングスは5であるので、各データ信号グループ毎に1つのエッジを抽出するためには、各データ信号グループにおけるデータ信号の数を最大ラン・レングス(すなわち5)以上にする必要がある。以下、図面を用いて本願発明を詳細に説明する。

【0017】

[実施の形態1]

この発明の実施の形態1によるクロック再生回路は、図1に示すように、エッジ抽出回路1、位相比較器6、チャージポンプ回路(CP)12、ループフィルタ(LF)13、電圧制御型発振器(VCO)14、およびリタイム回路15を備える。

【0018】

エッジ抽出回路1は、外部データ信号列Vinを受ける。外部データ信号列Vinは、図2(a)〜(g)に示すように、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を含む。図2(a)〜(g)では、外部クロック信号の位相と内部クロック信号VCOCLKまたはPD_Cinとの位相が一致している状態が示されている。外部クロック信号の隣接する2つの立ち下がりエッジの間の期間で1つのデータ信号が伝送される。

【0019】

外部データ信号列Vinの最大ラン・レングスは5である。ここでは、10クロック周期を1UG(Unit Group)とする。1UGは、外部クロック信号の立ち上がりエッジで開始され、外部クロック信号の10個のパルスを含む。図2(a)〜(g)では、3つのUG1〜UG3が示されている。データ遷移(外部データ信号列Dinの論理レベルの遷移)は、1UG当たり最大で10回発生する。UG1〜UG3では、それぞれ7回、5回、2回のデータ遷移が発生している。UGのデータ遷移密度DT_Dinは、そのUGにおいて発生したデータ遷移の回数と、発生し得るデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_Dinは、それぞれ7/10,5/10,2/10である。なお、図面および説明の簡単化のため、図2(a)〜(g)では回路の遅延時間は0とされている。

【0020】

エッジ抽出回路1は、各UG毎に、外部データ信号列Dinの最初の立ち上がりエッジを抽出する。すなわち、エッジ抽出回路1は、図1に示すように、UI(Unit Interval)カウンタ2、エッジ検出器3、トグル器4、および遅延回路5を含む。

【0021】

UIカウンタ2は、図3に示すように、フリップフロップ20,23,24,26、インバータ21,25,27、およびNANDゲート22を含む。フリップフロップ20のクロック端子は内部クロック信号VCOCLKを受ける。フリップフロップ20の出力信号φ20は、インバータ21を介してNANDゲート22の一方入力ノードに与えられる。NANDゲート22の出力信号φ22はフリップフロップ23のデータ入力端子に与えられ、フリップフロップ23の出力信号φ23はフリップフロップ24のデータ入力端子に与えられる。

【0022】

フリップフロップ24の出力信号φ24は、NANDゲート22の他方入力ノードに与えられるとともに、インバータ25を介してフリップフロップ20のデータ入力端子に与えられる。内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ20,23,24の各々は入力信号を保持および出力する。

【0023】

また、フリップフロップ20の出力信号φ20は、フリップフロップ26のクロック端子に与えられる。フリップフロップ26の出力信号は、インバータ27を介してフリップフロップ26のデータ入力端子に与えられる。信号φ20が「L」レベルから「H」レベルに立ち上げられると、フリップフロップ26は入力信号を保持および出力する。フリップフロップ23の出力信号は、UIカウンタ2の出力信号SETとなる。

【0024】

図4(a)〜(f)は、それぞれ信号VCOCLK,φ20,φ22,φ23,φ24,SETを示すタイムチャートである。信号φ20,φ22,φ23,φ24の各々は、内部クロック信号VCOCLKの5倍の周期を有するクロック信号となる。信号SETは、内部クロック信号VCOの10倍の周期を有するクロック信号となる。各UGにおいて、内部クロック信号VCOCLKの1番目の立ち上がりエッジに応答して信号SETが「H」レベルに立ち上げられ、内部クロック信号VCOCLKの5番目の立ち上がりエッジに応答して信号SETが「L」レベルに立ち下げられる。すなわち、内部クロック信号VCOCLKを10倍に分周した信号が信号SETとなる。

【0025】

エッジ検出器3は、信号SETの立ち上がりエッジに応答して信号ENを「L」レベルから「H」レベルに立ち上げた後、外部データ信号列Dinの最初の立ち上がりエッジに応答して信号ENを「H」レベルから「L」レベルに立ち下げる。

【0026】

エッジ検出器3は、図5に示すように、フリップフロップ30,31、ゲート回路32,33、セレクタ34,35、およびインバータ36,37を含む。フリップフロップ30のデータ入力端子は「H」レベル(電源電圧VCC)の信号を受け、そのクロック端子は外部データ信号列Dinを受け、そのリセット端子はゲート回路32の出力信号を受ける。リセット端子が「L」レベルにされると、フリップフロップ30の出力信号Din_Qは「H」レベルにリセットされる。外部データ信号列Dinが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ30の出力信号Din_Qは「L」レベルに立ち下げられる。

【0027】

ゲート回路32は、信号SELとリセット信号RESETの論理和信号の反転信号を出力する。リセット信号RESETが「H」レベルである場合は、ゲート回路32は「L」レベルの信号を出力する。リセット信号RESETが「L」レベルである場合は、ゲート回路32はインバータとして動作し、信号SELの反転信号を出力する。

【0028】

フリップフロップ31のデータ入力端子は「H」レベルの信号を受け、そのクロック端子は信号SETを受け、そのリセット端子はゲート回路33の出力信号を受ける。リセット端子が「L」レベルにされると、フリップフロップ31の出力信号SET_Qは「L」レベルにリセットされる。信号SETが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ31の出力信号SET_Qは「H」レベルに立ち上げられる。

【0029】

ゲート回路33は、信号SELの反転信号とリセット信号RESETとの論理和信号の反転信号を出力する。リセット信号RESETが「H」レベルである場合は、ゲート回路32は「L」レベルの信号を出力する。リセット信号RESETが「L」レベルである場合は、ゲート回路32はバッファとして動作し、信号SELを出力する。

【0030】

セレクタ34は、フリップフロップ30,31の出力信号Din_Q,SET_Qを受け、信号SELが「L」レベル(0)である場合は信号Din_Qを通過させ、信号SELが「H」レベル(1)である場合は信号SEL_Qを通過させる。セレクタ34を通過した信号は、インバータ36,37で遅延されてエッジ検出器3の出力信号ENとなる。

【0031】

セレクタ35は、信号ENと「H」レベルの信号とを受け、リセット信号RESETが「L」レベルである場合はリセット信号ENの反転信号を通過させ、リセット信号RESETが「H」レベルである場合は「H」レベルの信号を通過させる。セレクタ35を通過した信号が信号SELとなる。

【0032】

図6(a)〜(g)は、それぞれ信号RESET,Din,SET,Din_Q,SET_Q,SEL,ENを示すタイムチャートである。リセット信号RESETが「H」レベルである場合は、ゲート回路32,33の出力信号がともに「L」レベルとなり、フリップフロップ30,31がリセットされる。また、信号Din_Q,SELが「H」レベルになり、信号SET_Q,ENが「L」レベルになる。

【0033】

リセット信号RESETが「L」レベルにされると、ゲート回路32がインバータとして動作し、ゲート回路33がバッファとして動作する。信号SELが「H」レベルであるので、フリップフロップ31のリセットが解除される。

【0034】

時刻t0において信号SETが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ31の出力信号SET_Qが「L」レベルから「H」レベルに立ち上げられる。これに応じて信号ENが「H」レベルに立ち上げられ、信号SELが「L」レベルに立ち下げられ、フリップフロップ31がリセットされるとともに、フリップフロップ30のリセットが解除される。したがって、信号SET_Qは、信号SETの立ち上がりエッジに応答してパルス的に「H」レベルになる。

【0035】

次に、外部データ信号列Dinが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ30の出力信号Din_Qが「H」レベルから「L」レベルに立ち下げられる。これに応じて信号ENが「L」レベルに立ち下げられ、信号SELが「H」レベルに立ち上げられ、フリップフロップ30がリセットされるとともに、フリップフロップ31のリセットが解除される。したがって、信号Din_Qは、外部データ信号列Dinの最初の立ち上がりエッジに応答してパルス的に「L」レベルになる。また、信号ENは、各UGにおいて、信号SETの立ち上がりエッジに応答して「L」レベルから「H」レベルに立ち上げられ、外部データ信号列Dinの最初の立ち上がりエッジに応答して「H」レベルから「L」レベルに立ち下げられる。

【0036】

トグル器4は、図7に示すように、セレクタ40、フリップフロップ41、およびインバータ42を含む。セレクタ40は、「H」レベルの信号と外部データ信号列Dinを受け、信号ENが「L」レベルである場合は「H」レベルの信号を通過させ、信号ENが「H」レベルである場合は外部データ信号列Dinを通過させる。セレクタ40を通過した信号は、信号INとなり、フリップフロップ41のクロック端子に与えられる。フリップフロップ41の出力信号PD_Dinは、インバータ42を介してフリップフロップ41のデータ入力端子に与えられる。

【0037】

図8(a)〜(d)は、信号Din,EN,IN,PD_Dinを示すタイムチャートである。信号ENが「H」レベルである期間は、外部データ信号列Dinがセレクタ40を通過して信号INとなる。信号INが「L」レベルから「H」レベルに立ち上げられる毎にフリップフロップ41の出力信号PD_Dinの論理レベルが反転される。信号ENが「L」レベルである期間は、「H」レベルの信号がセレクタ40を通過して信号INとなる。フリップフロップ41の出力信号PD_Dinは、信号ENが「L」レベルに立ち下げられる前の論理レベルに維持される。

【0038】

なお、図5および図6(a)〜(g)で示したように、信号ENは「H」レベルに立ち上げられた後に、外部データ信号列Dinの最初の立ち上がりエッジに応答して「L」レベルに立ち下げられる。したがって、図2(a)〜(g)に示すように、信号PD_Dinの論理レベルは、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジに応答して反転する。

【0039】

信号PD_Dinのデータ遷移(信号PD_Dinの論理レベルの遷移)は、1UG毎に必ず1回発生する。UGのデータ遷移密度DT_PD_Dinは、そのUGにおいて発生した信号PD_Dinのデータ遷移の回数(1回)と、外部データ信号列Dinのデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_PD_Dinは、ともに1/10となる。

【0040】

図1に戻って、遅延回路5は、内部クロック信号VCOCLKを所定の遅延時間だけ遅延させてクロック信号PD_Cinを生成する。遅延回路5の遅延時間は、トグル器4の遅延時間に等しく設定される。

【0041】

位相比較器6は、信号PD_Dinの位相とクロック信号VCOCLKの位相とを比較し、比較結果を示す信号UP,DNを出力する。すなわち、位相比較器6は、バッファ回路7、フリップフロップ8,9、およびEX−ORゲート10,11を含む。バッファ回路7は、クロック信号PD_Cinおよびその相補信号を出力する。

【0042】

フリップフロップ8のクロック端子はバッファ回路7からのクロック信号PD_Cinを受け、そのデータ入力端子は信号PD_Dinを受ける。フリップフロップ9のクロック端子はバッファ回路7からのクロック信号PD_Cinの相補信号を受け、そのデータ入力端子はフリップフロップ8の出力信号を受ける。EX−ORゲート10は、信号PD_Dinとフリップフロップ8の出力信号とを受け、信号UPを出力する。EX−ORゲート11は、フリップフロップ8,9の出力信号を受け、信号DNを出力する。

【0043】

図2(a)〜(g)に示すように、信号PD_Dinとクロック信号PD_Cinとの位相差が信号UPのパルス幅となり、クロック信号PD_Cinの半周期が信号DNのパルス幅となる。

【0044】

チャージポンプ回路12は、信号UPのパルス幅に比例した正電流をループフィルタ13に供給するとともに、信号DNのパルス幅に比例した負電流をループフィルタ13に供給する。ループフィルタ13は、所定容量値のキャパシタと所定抵抗値の抵抗素子を含み、チャージポンプ回路12の出力電流を積分して制御電圧を生成する。電圧制御型発振器14は、ループフィルタ13で生成された制御電圧に応じた周波数で発振して内部クロック信号VCOCLKを出力する。

【0045】

リタイム回路15は、フリップフロップ16を含む。フリップフロップ16のクロック端子は内部クロック信号VCOCLKを受け、そのデータ入力端子は外部データ信号列Dinを受ける。フリップフロップ16は、内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられる毎に外部クロック信号列Dinを保持および出力する。クロック再生回路は、フリップフロップ16の出力信号を内部データ信号列Doutとして出力するとともに、電圧制御型発振器14の出力信号VCOCLKを内部クロック信号Coutとして出力する。

【0046】

[比較例]

図9は、実施の形態1の比較例となるクロック再生回路の構成を示す回路ブロック図であって、図1と対比される図である。図9において、このクロック再生回路が図1のクロック再生回路と異なる点は、エッジ抽出回路1およびリタイム回路15が除去されている点である。外部データ信号列Dinおよび内部クロック信号VCOCLKは、位相比較器6に直接入力される。バッファ回路7で生成されたクロック信号VCOCLKの相補信号が内部クロック信号Coutとして出力され、フリップフロップ9の出力信号が内部データ信号列Doutとして出力される。

【0047】

図10(a)〜(d)は、図9に示したクロック再生回路の動作を示すタイムチャートであって、図2(a)〜(g)と対比される図である。外部データ信号列Vinは、図10(a)〜(d)に示すように、外部クロック信号に同期してシリアルに伝送される複数のデータ信号を含む。図10(a)〜(d)では、外部クロック信号の位相と内部クロック信号VCOCLKとの位相が一致している状態が示されている。外部クロック信号の隣接する2つの立ち下がりエッジの間の期間で1つのデータ信号が伝送される。

【0048】

外部データ信号列Vinの最大ラン・レングスは5である。ここでは、5クロック周期を1UGとする。1UGは、外部クロック信号の立ち上がりエッジで開始され、外部クロック信号の5個のパルスを含む。図10(a)〜(d)では、6つのUG1〜UG6が示されている。データ遷移(外部データ信号列Dinの論理レベルの遷移)は、1UG当たり最大で5回発生する。UG1〜UG6では、それぞれ5回、2回、4回、1回、1回、1回のデータ遷移が発生している。UGのデータ遷移密度DT_Dinは、そのUGにおいて発生したデータ遷移の回数と、発生し得るデータ遷移の最大値(5回)との比である。UG1〜UG6のデータ遷移密度DT_Dinは、それぞれ5/5,2/5,4/5,1/5,1/5,1/5である。なお、図面および説明の簡単化のため、図2(a)〜(g)では回路の遅延時間は0とされている。

【0049】

このクロック再生回路では、外部データ信号列Dinの論理レベルが変化する毎に信号UP,DNの各々がパルス的に変化する。したがって、外部データ信号列Dinの論理レベルが変化する回数と信号UP,DNの各々のパルス数とは同じである。

【0050】

この比較例では、外部データ信号列Dinの論理レベルが遷移する毎に位相比較が行なわれ、オープンループゲインがデータ遷移密度DT_Dinに比例するため、データパターンに依存するジッタが大きいと言う問題がある。また、データパターンに依存して動作電流および電源電圧が変動することも、ジッタが大きくなる原因となる。

【0051】

また、想定されるデータ遷移密度DT_Dinの変動範囲で最適なジッタ伝達特性を得るには、データ遷移密度DT_Dinの変動幅に応じてループフィルタ13のキャパシタの容量値を大きくする必要がある。このためデータ遷移密度DT_Dinの変動幅が大きくなるほどループフィルタ13の面積が増大すると言う問題がある。

【0052】

また、データ遷移密度DT_Dinの変動範囲は、高速シリアルインタフェースの規格が採用する符号化方式で決まる。この比較例で採用されている8B10B符号化では、最大ラン・レングスが5であり、データ遷移密度DT_Dinの変動範囲は20%〜100%であり、データ遷移密度DT_Dinの最大値は最小値の5倍である。

【0053】

しかし、64B66B符号化では、最大ラン・レングスは66であり、データ遷移密度の変動範囲は1.5%〜100%であり、データ遷移密度の最大値は最小値の約67倍にもなる。図9のクロック再生回路では、データ遷移密度の最大値が最小値の5倍である場合は対応可能であるが、それが67倍になると対応不能であり、クロック信号を再生することはできない。

【0054】

これに対して本願発明では、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジを抽出し、抽出した立ち上がりエッジに同期した信号PD_Dinの位相と内部クロック信号PD_Cinの位相とを比較するので、位相比較器6におけるデータ遷移密度DT_PD_Dinは一定値になる。したがって、外部データ信号列Dinのデータパターンに依存するジッタを小さくすることができる。また、ループフィルタ13のキャパシタの容量値および面積を小さくすることができる。また、外部データ信号列Dinのデータ遷移密度DT_Dinの変動幅が大きい場合でも、クロック信号を再生することができる。

【0055】

[実施の形態2]

実施の形態1では、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジを抽出し、抽出した立ち上がりエッジに同期した信号PD_Dinの位相と内部クロック信号PD_Cinの位相とを比較した。

【0056】

これに対して本実施の形態2では、各UGにおいて外部データ信号列Dinの最初の立ち下がりエッジを抽出し、抽出した立ち下がりエッジに同期した信号PD_Dinの位相と内部クロック信号PD_Cinの位相とを比較する。本実施の形態2のクロック再生回路は、図1のクロック再生回路のエッジ検出器3およびトグル器4をそれぞれエッジ検出器45およびトグル器47で置換したものである。

【0057】

図11はエッジ検出器45の構成を示す回路図であって、図5と対比される図である。このエッジ検出器45は、図5のエッジ検出器3のフリップフロップ30をフリップフロップ46で置換したものである。フリップフロップ46は、ゲート回路32の出力信号が「L」レベルにされると、リセットされて「H」レベルの信号を出力する。また、フリップフロップ46は、外部データ信号列Dinが「H」レベルから「L」レベルに立ち下げられると、「H」レベルの信号を保持し、その反転信号である「L」レベルの信号を出力する。

【0058】

図12(a)〜(g)はエッジ検出器45の動作を示すタイムチャートであって、図6(a)〜(g)と対比される図である。図12(a)〜(g)において、リセット信号RESETが「H」レベルである場合は、ゲート回路32,33の出力信号がともに「L」レベルとなり、フリップフロップ31,46がリセットされる。また、信号Din_Q,SELが「H」レベルになり、信号SET_Q,ENが「L」レベルになる。

【0059】

リセット信号RESETが「L」レベルにされると、ゲート回路32がインバータとして動作し、ゲート回路33がバッファとして動作する。信号SELが「H」レベルであるので、フリップフロップ31のリセットが解除される。

【0060】

時刻t0において信号SETが「L」レベルから「H」レベルに立ち上げられると、フリップフロップ31の出力信号SET_Qが「L」レベルから「H」レベルに立ち上げられる。これに応じて信号ENが「H」レベルに立ち上げられ、信号SELが「L」レベルに立ち下げられ、フリップフロップ31がリセットされるとともに、フリップフロップ46のリセットが解除される。したがって、信号SET_Qは、信号SETの立ち上がりエッジに応答してパルス的に「H」レベルになる。

【0061】

次に、外部データ信号列Dinが「H」レベルから「L」レベルに立ち下げられると、フリップフロップ46の出力信号Din_Qが「H」レベルから「L」レベルに立ち下げられる。これに応じて信号ENが「L」レベルに立ち下げられ、信号SELが「H」レベルに立ち上げられ、フリップフロップ46がリセットされるとともに、フリップフロップ31のリセットが解除される。したがって、信号Din_Qは、外部データ信号列Dinの最初の立ち下がりエッジに応答してパルス的に「L」レベルになる。また、信号ENは、各UGにおいて、信号SETの立ち上がりエッジに応答して「L」レベルから「H」レベルに立ち上げられ、外部データ信号列Dinの最初の立ち下がりエッジに応答して「H」レベルから「L」レベルに立ち下げられる。

【0062】

図13はトグル器47の構成を示す回路図であって、図7と対比される図である。このトグル器47は、図7のトグル器4の電源電圧VCCを接地電圧VSSで置換し、フリップフロップ41をフリップフロップ48で置換したものである。

【0063】

セレクタ40は、「L」レベル(接地電圧VSS)の信号と外部データ信号列Dinを受け、信号ENが「L」レベルである場合は「L」レベルの信号を通過させ、信号ENが「H」レベルである場合は外部データ信号列Dinを通過させる。セレクタ40を通過した信号は、信号INとなり、フリップフロップ48のクロック端子に与えられる。フリップフロップ48の出力信号PD_Dinは、インバータ42を介してフリップフロップ48のデータ入力端子に与えられる。

【0064】

図14(a)〜(d)は、信号Din,EN,IN,PD_Dinを示すタイムチャートであって、図8(a)〜(d)と対比される図である。信号ENが「H」レベルである期間は、外部データ信号列Dinがセレクタ40を通過して信号INとなる。信号INが「H」レベルから「L」レベルに立ち下げられる毎にフリップフロップ48の出力信号PD_Dinの論理レベルが反転される。信号ENが「L」レベルである期間は、「L」レベルの信号がセレクタ40を通過して信号INとなる。フリップフロップ48の出力信号PD_Dinは、信号ENが「L」レベルに立ち下げられる前の論理レベルに維持される。

【0065】

なお、図11および図12(a)〜(g)で示したように、信号ENは「H」レベルに立ち上げられた後に、外部データ信号列Dinの最初の立ち下がりエッジに応答して「L」レベルに立ち下げられる。したがって、信号PD_Dinの論理レベルは、各UGにおいて外部データ信号列Dinの最初の立ち下がりエッジに応答して反転する。

【0066】

他の構成および動作は、実施の形態1と同じであるので、その説明は繰り返さない。この実施の形態2でも、実施の形態1と同じ効果が得られる。

【0067】

[実施の形態3]

図15は、この発明の実施の形態3によるクロック再生回路の構成を示す回路ブロック図であって、図1と対比される図である。また図16(a)〜(i)は、図15に示したクロック再生回路の動作を示すタイムチャートであって、図2(a)〜(g)と対比される図である。

【0068】

図15において、このクロック再生回路は、エッジ抽出回路1R,1F、位相比較器6R,6F、チャージポンプ回路12R,12F、ループフィルタ13、電圧制御型発振器14、およびリタイム回路15を備える。

【0069】

外部データ信号列Vinは、図2(a)〜(g)で説明した通りである。UG1〜UG3のデータ遷移密度DT_Dinは、それぞれ7/10,5/10,2/10である。なお、図面および説明の簡単化のため、図16(a)〜(i)では回路の遅延時間は0とされている。

【0070】

エッジ抽出回路1Rは、図1のエッジ抽出回路1と同じ構成であり、各UGにおいて外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転する信号PD_DinRと、内部クロック信号VCOCLKを所定時間だけ遅延させたクロック信号PD_CinRとを生成する。

【0071】

信号PD_DinRのデータ遷移(信号PD_DinRの論理レベルの遷移)は、1UG毎に必ず1回発生する。UGのデータ遷移密度DT_PD_DinRは、そのUGにおいて発生した信号PD_DinRのデータ遷移の回数(1回)と、外部データ信号列Dinのデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_PD_DinRは、ともに1/10となる。

【0072】

エッジ抽出回路1Fは、実施の形態2のクロック再生回路のエッジ抽出回路と同じ構成であり、各UGにおいて外部データ信号列Dinの最初の立ち下がりエッジに応答して論理レベルが反転する信号PD_DinFと、内部クロック信号VCOCLKを所定時間だけ遅延させたクロック信号PD_CinFとを生成する。

【0073】

信号PD_DinFのデータ遷移(信号PD_DinFの論理レベルの遷移)は、1UG毎に必ず1回発生する。UGのデータ遷移密度DT_PD_DinFは、そのUGにおいて発生した信号PD_DinFのデータ遷移の回数(1回)と、外部データ信号列Dinのデータ遷移の最大値(10回)との比である。UG1〜UG3のデータ遷移密度DT_PD_DinFは、ともに1/10となる。したがって、DT_PD_DinRとDT_PD_DinFの和であるDT_PDは2/10となる。

【0074】

位相比較器6Rは、エッジ抽出回路1Rからの信号PD_DinR,PD_CinRの位相を比較し、比較結果を示す信号UPR,DNRを生成する。信号PD_DinRとクロック信号PD_CinRとの位相差が信号UPRのパルス幅となり、クロック信号PD_CinRの半周期が信号DNRのパルス幅となる。

【0075】

位相比較器6Fは、エッジ抽出回路1Fからの信号PD_DinF,PD_CinFの位相を比較し、比較結果を示す信号UPF,DNFを生成する。信号PD_DinFとクロック信号PD_CinFとの位相差が信号UPFのパルス幅となり、クロック信号PD_CinFの半周期が信号DNFのパルス幅となる。

【0076】

チャージポンプ回路12Rは、信号UPRのパルス幅に比例した正電流をループフィルタ13に供給するとともに、信号DNRのパルス幅に比例した負電流をループフィルタ13に供給する。チャージポンプ回路12Fは、信号UPFのパルス幅に比例した正電流をループフィルタ13に供給するとともに、信号DNFのパルス幅に比例した負電流をループフィルタ13に供給する。

【0077】

ループフィルタ13は、チャージポンプ回路12R,12Fの出力電流を積分して制御電圧を生成する。電圧制御型発振器14は、ループフィルタ13で生成された制御電圧に応じた周波数で発振して内部クロック信号VCOCLKを出力する。リタイム回路15は、図1で示したものと同じである。

【0078】

この実施の形態3では、実施の形態1と同じ効果が得られる他、実施の形態1と比べてチャージポンプ回路の出力電流を時間軸方向に分散させることができ、電源電圧の変動を抑制することができる。

【0079】

[実施の形態4]

図17は、この発明の実施の形態4によるクロック再生回路のUIカウンタ50の構成を示す回路図である。図17において、このUIカウンタ50は、フリップフロップ51,54、加算器52、セレクタ53、およびNORゲート55を含む。

【0080】

フリップフロップ51のデータ入力端子は信号UI_Regを受け、そのクロック端子は内部クロック信号VCOCLKを受ける。信号UI_Regは、UIカウント数Nを設定する信号であり、複数ビットのデータ信号を含む。UIカウント数Nは、たとえばレジスタに格納され、書き換え可能になっている。

【0081】

加算器52は、フリップフロップ54の出力信号STATEに−1を加算する。セレクタ53は、加算器52の出力信号とフリップフロップ51の出力信号とを受ける。信号SETが「L」レベルである場合は、加算器52の出力信号がセレクタ53を通過し、信号SETが「H」レベルである場合は、フリップフロップ51の出力信号がセレクタ53を通過する。フリップフロップ54のデータ入力端子はセレクタ53の出力信号を受け、そのクロック端子は内部クロック信号VCOCLKを受ける。NORゲート55は、フリップフロップ54の出力信号STATEを受け、信号SETを出力する。

【0082】

図18(a)〜(c)は、それぞれ信号VCOCLK,STATE,SETを示すタイムチャートである。内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられる毎に、フリップフロップ51は信号UI_Regを保持および出力し、フリップフロップ54はセレクタ53の出力信号を保持および出力する。

【0083】

信号STATEが0でない場合は、信号SETが「L」レベルになり、加算器52の出力信号がセレクタ53を通過してフリップフロップ54のデータ入力端子に入力される。内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられる毎に、信号STATEの値がデクレメント(−1)される。信号STATEの値が0になると、信号SETが「L」レベルから「H」レベルに立ち上げられ、信号UI_Regがセレクタ53を通過してフリップフロップ54に与えられる。次に、内部クロック信号VCOCLKが「L」レベルから「H」レベルに立ち上げられると、信号STATEがN−1にリセットされ、信号SETが「L」レベルに立ち下げられる。他の構成および動作は、実施の形態1と同じであるので、その説明は繰り返さない。

【0084】

この実施の形態4では、実施の形態1と同じ効果が得られる他、UIカウント数Nを所望の値に変更することができる。

【0085】

なお、クロック再生回路のループ帯域は規格で定められており、10MHz程度である。そのため、UIカウント数Nを大きくした場合、それに応じてチャージポンプ回路12のゲインを大きくし、ループゲインを一定値に維持する必要がある。そこで、実施の形態4の変更例では、UIカウント数Nに応じてゲインが変更されるチャージポンプ回路でチャージポンプ回路12が置換される。

【0086】

[実施の形態5]

図19は、この発明の実施の形態5による半導体装置の要部を示すブロック図である。図19において、この半導体装置は、入力端子T1,T4,T5、出力端子T2,T3、受信回路(RxFE)60、クロック再生回路(CDR)61、シリアル/パラレル変換回路(DES)62、ロジック回路63、PLL(Phase Locked Loop)回路64、パラレル/シリアル変換回路(SER)65、および送信回路(TxFE)66を備える。

【0087】

受信回路60は、外部から入力端子T4,T5を介して与えられた差動信号RXP,RXTをシングルエンドのデータ信号に変換する。クロック再生回路61は、実施の形態1〜4のうちのいずれかの実施の形態のクロック再生回路であり、受信回路60からの外部データ信号列Dinに基いて内部データ信号列Doutおよび内部クロック信号Coutを生成する。内部データ信号列Doutは、内部クロック信号Coutに同期してシリアルに伝送される複数のデータ信号を含む。

【0088】

シリアル/パラレル変換回路62は、内部クロック信号Coutに同期して動作し、内部データ信号列Doutに含まれる複数のデータ信号をNビットずつグループ化し、Nビット幅のパラレルデータ信号列に変換する。シリアル/パラレル変換回路62は、Nビット幅のパラレルデータ信号列と、それに同期したクロック信号φ62をロジック回路63に与える。

【0089】

ロジック回路63は、シリアル/パラレル変換回路62からのパラレルデータ信号列をクロック信号φ62に同期して取り込み、取り込んだデータ信号に基いて所定の動作を行なう。

【0090】

また、PLL回路64は、外部から入力端子T1を介して与えられる参照クロック信号REFCLKに応答して内部クロック信号φ64を生成し、生成した内部クロック信号φ64をロジック回路63およびパラレル/シリアル変換回路65に与える。

【0091】

ロジック回路63は、PLL回路64からの内部クロック信号φ64に同期して動作する。また、ロジック回路63は、所定の動作を行なってNビット幅のパラレルデータ信号列を生成し、生成したパラレルデータ信号列と、それに同期したクロック信号φ63とをパラレル/シリアル変換回路65に与える。

【0092】

パラレル/シリアル変換回路65は、ロジック回路63からのNビット幅のパラレルデータ信号をクロック信号φ63に同期して取り込み、取り込んだNビット幅のパラレルデータ信号列を1ビット幅のデータ信号列に変換し、そのデータ信号列を内部クロック信号φ64に同期して出力する。送信回路(TxFE)66は、パラレル/シリアル変換回路65からのデータ信号を差動信号TXP,TXNに変換して出力端子T2,T3に出力する。この実施の形態5では、実施の形態1〜4と同じ効果が得られる。

【0093】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0094】

1,1R,1F エッジ抽出回路、2,50 UIカウンタ、3,45 エッジ検出器、4,47 トグル器、5 遅延回路、6,6R,6F 位相比較器、7 バッファ回路、8,9,16,20,23,24,26,30,31,41,46,48,51,54 フリップフロップ、10,11 EX−ORゲート、12,12R,12F チャージポンプ回路、13 ループフィルタ、14 電圧制御型発振器、15 リタイム回路、21,25,27,36,37,42 インバータ、22 NANDゲート、32,33 ゲート回路、34,35,40,53 セレクタ、55 NORゲート、60 受信回路、61 クロック再生回路、62 シリアル/パラレル変換回路、63 ロジック回路、64 PLL回路、65 パラレル/シリアル変換回路、66 送信回路、T1,T4,T5 入力端子、T2,T3 出力端子。

【特許請求の範囲】

【請求項1】

外部クロック信号に同期してシリアルに伝送される複数のデータ信号を受け、受けた前記複数のデータ信号に同期した内部クロック信号を生成するクロック再生回路であって、

前記複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりまたは立ち下がりエッジを抽出するエッジ抽出回路と、

制御電圧に基いて前記内部クロック信号を生成する電圧制御型発振器と、

前記エッジ抽出回路によって抽出された各立ち上がりまたは立ち下がりエッジの位相と前記電圧制御型発振器によって生成された前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する位相比較器と、

前記位相比較器の出力信号に応答して正電流または負電流を出力するチャージポンプ回路と、

前記チャージポンプ回路の出力電流を積分して前記制御電圧を発生するループフィルタとを備える、クロック再生回路。

【請求項2】

前記予め定められた数は、前記複数のデータ信号の最大ラン・レングス以上の数に設定されている、請求項1に記載のクロック再生回路。

【請求項3】

前記エッジ抽出回路は、各データ信号グループ毎に最初の立ち上がりまたは立ち下がりエッジを抽出する、請求項1または請求項2に記載のクロック再生回路。

【請求項4】

前記エッジ抽出回路は、

前記データ信号グループに同期した第1の信号を生成する信号発生回路と、

前記第1の信号に応答して第2の信号を第1の論理レベルにし、前記最初の立ち上がりまたは立ち下がりエッジに応答して前記第2の信号を第2の論理レベルにするエッジ検出器と、

前記第2の信号が第2の論理レベルにされる毎に第3の信号の論理レベルを反転させるトグル器とを含み、

前記位相比較器は、前記第3の信号の位相と前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する、請求項3に記載のクロック再生回路。

【請求項5】

前記予め定められた数は変更可能になっている、請求項1から請求項4までのいずれかに記載のクロック再生回路。

【請求項6】

さらに、前記複数のデータ信号を受け、各データ信号を前記内部クロック信号に同期して保持および出力するリタイム回路を備える、請求項1から請求項5までのいずれかに記載のクロック再生回路。

【請求項7】

外部クロック信号に同期してシリアルに伝送される複数のデータ信号を受け、受けた前記複数のデータ信号に同期した内部クロック信号を生成するクロック再生回路であって、

前記複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりエッジを抽出する第1のエッジ抽出回路と、

前記複数のデータ信号を前記予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち下がりエッジを抽出する第2のエッジ抽出回路と、

制御電圧に基いて前記内部クロック信号を生成する電圧制御型発振器と、

前記第1のエッジ抽出回路によって抽出された各立ち上がりエッジの位相と前記電圧制御型発振器によって生成された前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する第1の位相比較器と、

前記第2のエッジ抽出回路によって抽出された各立ち下がりエッジの位相と前記電圧制御型発振器によって生成された前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する第2の位相比較器と、

前記第1の位相比較器の出力信号に応答して正電流または負電流を供給する第1のチャージポンプ回路と、

前記第2の位相比較器の出力信号に応答して正電流または負電流を供給する第2のチャージポンプ回路と、

前記第1および第2のチャージポンプ回路の出力電流を積分して前記制御電圧を発生するループフィルタとを備える、クロック再生回路。

【請求項1】

外部クロック信号に同期してシリアルに伝送される複数のデータ信号を受け、受けた前記複数のデータ信号に同期した内部クロック信号を生成するクロック再生回路であって、

前記複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりまたは立ち下がりエッジを抽出するエッジ抽出回路と、

制御電圧に基いて前記内部クロック信号を生成する電圧制御型発振器と、

前記エッジ抽出回路によって抽出された各立ち上がりまたは立ち下がりエッジの位相と前記電圧制御型発振器によって生成された前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する位相比較器と、

前記位相比較器の出力信号に応答して正電流または負電流を出力するチャージポンプ回路と、

前記チャージポンプ回路の出力電流を積分して前記制御電圧を発生するループフィルタとを備える、クロック再生回路。

【請求項2】

前記予め定められた数は、前記複数のデータ信号の最大ラン・レングス以上の数に設定されている、請求項1に記載のクロック再生回路。

【請求項3】

前記エッジ抽出回路は、各データ信号グループ毎に最初の立ち上がりまたは立ち下がりエッジを抽出する、請求項1または請求項2に記載のクロック再生回路。

【請求項4】

前記エッジ抽出回路は、

前記データ信号グループに同期した第1の信号を生成する信号発生回路と、

前記第1の信号に応答して第2の信号を第1の論理レベルにし、前記最初の立ち上がりまたは立ち下がりエッジに応答して前記第2の信号を第2の論理レベルにするエッジ検出器と、

前記第2の信号が第2の論理レベルにされる毎に第3の信号の論理レベルを反転させるトグル器とを含み、

前記位相比較器は、前記第3の信号の位相と前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する、請求項3に記載のクロック再生回路。

【請求項5】

前記予め定められた数は変更可能になっている、請求項1から請求項4までのいずれかに記載のクロック再生回路。

【請求項6】

さらに、前記複数のデータ信号を受け、各データ信号を前記内部クロック信号に同期して保持および出力するリタイム回路を備える、請求項1から請求項5までのいずれかに記載のクロック再生回路。

【請求項7】

外部クロック信号に同期してシリアルに伝送される複数のデータ信号を受け、受けた前記複数のデータ信号に同期した内部クロック信号を生成するクロック再生回路であって、

前記複数のデータ信号を予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち上がりエッジを抽出する第1のエッジ抽出回路と、

前記複数のデータ信号を前記予め定められた数ずつグループ化し、各データ信号グループ毎に1つの立ち下がりエッジを抽出する第2のエッジ抽出回路と、

制御電圧に基いて前記内部クロック信号を生成する電圧制御型発振器と、

前記第1のエッジ抽出回路によって抽出された各立ち上がりエッジの位相と前記電圧制御型発振器によって生成された前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する第1の位相比較器と、

前記第2のエッジ抽出回路によって抽出された各立ち下がりエッジの位相と前記電圧制御型発振器によって生成された前記内部クロック信号の位相とを比較し、比較結果を示す信号を出力する第2の位相比較器と、

前記第1の位相比較器の出力信号に応答して正電流または負電流を供給する第1のチャージポンプ回路と、

前記第2の位相比較器の出力信号に応答して正電流または負電流を供給する第2のチャージポンプ回路と、

前記第1および第2のチャージポンプ回路の出力電流を積分して前記制御電圧を発生するループフィルタとを備える、クロック再生回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−17076(P2013−17076A)

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願番号】特願2011−149119(P2011−149119)

【出願日】平成23年7月5日(2011.7.5)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願日】平成23年7月5日(2011.7.5)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]