クロック出力回路

【課題】クロック出力回路1にて電流消費を抑えつつ、周波数が安定したクロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロックを出力するクロック出力回路に関するものである。

【背景技術】

【0002】

従来、マイクロコンピュータの周辺回路として、発振信号をクロックとしてマイクロコンピュータに出力する発振回路と、電源が投入された後に予め決められた一定期間経過すると、リセット信号をマイクロコンピュータに出力するリセット回路とを備えるものがある。

【0003】

ここで、上記一定期間は、電源の投入後に発振回路の発振が安定するのに要する時間である。

【0004】

このことにより、電源の投入後一定期間経過すると、マイクロコンピュータは、リセット回路からリセット信号を受けるので、安定した発信を行う発振回路から出力されるクロックに基づいてマイクロコンピュータが正常に動作を開始することになる。

【0005】

また、特許文献1のクロック出力回路のように、発振回路の出力信号の振幅が安定化すると、発振回路の出力信号をマイクロコンピュータに出力することを許可する出力制御回路を備えるものがある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平4−105108号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述のマイクロコンピュータの周辺回路では、発振回路の起動後一定期間経過すると、マイクロコンピュータが発振回路から出力されるクロックに基づいて動作を開始するため、発振回路の起動後一定期間経過する前に、実際には発振回路の発振が安定してマイクロコンピュータが動作可能になっているにも関わらず、マイクロコンピュータが待機している場合がある。このため、必要以上に長い時間、マイクロコンピュータが待機することになり、発振回路などで余分な電流が消費される。

【0008】

これに対して、上述の特許文献1では、発振回路の出力信号の振幅が安定化すると、出力制御回路が発振回路に対して発振信号をマイクロコンピュータに出力することを許可するため、マイクロコンピュータが待機する時間を短くすることができる。しかし、この場合、発振回路の発振周波数が不安定であるにも関わらず、発振回路の出力信号の振幅が安定すると、出力制御回路が発振回路に対して発振信号の出力を許可して、発振回路の発振出力がクロックとしてマイクロコンピュータに出力される恐れがある。すなわち、周波数が不安定な状態でクロックが発振回路からマイクロコンピュータに与えられる恐れがある。

【0009】

本発明は上記点に鑑みて、発振回路での無駄な電流の消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するため、請求項1に記載の発明では、発振信号を出力する発振回路(10)と、

前記発振信号の信号レベルが第1閾値(Th1)以上のときローレベルの出力信号を出力し、前記信号レベルが第1閾値未満のときハイレベルの出力信号を出力する第1のNOTゲート(21A)と、

前記信号レベルが第2閾値(Th2)以上のときローレベルの出力信号を出力し、前記信号レベルが第2閾値未満のときハイレベルの出力信号を出力する第2のNOTゲート(22A)と、

前記第1、第2のNOTゲートのうち一方のNOTゲートがハイレベル信号を出力するときにローレベル信号を出力し、前記一方のNOTゲートがローレベル信号を出力するときにハイレベル信号を出力する第3のNOTゲート(23)と、

前記第1、第2のNOTゲートのうち一方のNOTゲート以外の他方のNOTゲートの出力信号と前記第3のNOTゲートの出力信号とをそれぞれ入力信号として、前記それぞれの入力信号が順次互いに相反するレベルになるとき前記入力信号を矩形波に波形整形してクロックとして出力するフリップフロップ回路(24)と、を備え、

前記第1閾値(Th1)は、前記第2閾値(Th2)よりも大きい値に設定されており、

前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなり、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とする。

【0011】

請求項1に記載の発明によれば、発振信号の周波数が高くなるほど第1閾値が大きくなるので、振幅が小さい場合には、発振信号の周波数が高くなるほど、第1のNOTゲートの出力信号のレベルがハイレベルからローレベルに変化し難くなる。これに加えて、発振信号の周波数が高くなるほど第2閾値が小さくなるので、振幅が小さい場合には、発振信号の周波数が高くなるほど、第2のNOTゲートの出力信号のレベルがローレベルからハイレベルに変化し難くなる。

【0012】

このため、振幅が小さく、かつ発振信号の周波数が高い場合には、第1、第2のNOTゲートの出力信号が互いに相反するレベルになる。これに伴い、他方のNOTゲートの出力信号と第3のNOTゲートの出力信号とが同一レベルになるので、フリップフロップ回路からクロックが出力され難くなる。

【0013】

ここで、発振回路はその起動時において予め設定された周波数よりも高くなり、かつ、発振信号の振幅が予め設定された振幅よりも小さくなるオーバートーン発振が生じる場合がある。

【0014】

これに対して、請求項1に記載の発明では、上述の如く、振幅が小さく、かつ発振信号の周波数が高い場合には、フリップフロップ回路からクロックが出力されない。このため、発振回路においてオーバートーン発振が生じているときには(すなわち、発振回路の発振が不安定化であるときには)、フリップフロップ回路からクロックが出力されなくなる。その後、発振回路の発振周波数が低下して予め設定された周波数に移行すると(すなわち、発振回路の発振が安定化すると)、他方の論理ゲートの出力信号と第3のNOTゲートの出力信号とが相違するレベルになるので、フリップフロップ回路がクロックを出力することができる。

【0015】

このため、発振回路においてオーバートーン発振が生じているときだけ、フリップフロップ回路からクロックが出力されなくなる。したがって、必要以上に長い時間、クロックの出力を待機させることはない。すなわち、クロックの出力を待機させるための発振安定時間を短くして、発振回路の電流の消費を抑えることができる。

【0016】

以上により、発振回路の電流の消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することができる。

【0017】

請求項2に記載の発明では、前記第1のNOTゲート(21A)は、

電源とグランドとの間に配置される第1のpMOSトランジスタ(25a)と、

前記第1のpMOSトランジスタ(25a)とグランドとの間に並列配置される複数の第1のnMOSトランジスタ(25b)とを備え、

前記第1のpMOSトランジスタ(25a)のゲート端子と前記複数の第1のnMOSトランジスタ(25b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記第1のpMOSトランジスタのドレイン端子と前記複数の第1のnMOSトランジスタのドレイン端子とが接続されて前記第1のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第1のnMOSトランジスタ(25b)のうち隣り合う2つの第1のnMOSトランジスタ毎に前記2つの第1のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されることにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする。

【0018】

請求項3に記載の発明では、前記第2のNOTゲート(22A)は、

電源とグランドとの間に並列配置される複数の第2のpMOSトランジスタ(25d)と、

前記複数の第2のpMOSトランジスタとグランドとの間に配置される第2のnMOSトランジスタ(25e)とを備え、

前記複数の第2のpMOSトランジスタのゲート端子と前記第2のnMOSトランジスタのゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第2のpMOSトランジスタのドレイン端子と前記第2のnMOSトランジスタのドレイン端子とが接続されて前記第2のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第2のpMOSトランジスタ(25d)のうち隣り合う2つの第2のpMOSトランジスタ毎に前記2つの第2のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されることにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなっていることを特徴とする。

【0019】

請求項4に記載の発明では、前記第1のNOTゲート(21A)は、

電源とグランドとの間に並列配置される複数の第3のpMOSトランジスタ(26d)と、

前記第3のpMOSトランジスタ(26d)とグランドとの間に並列配置される複数の第3のnMOSトランジスタ(26b)とを備え、

前記複数の第3のpMOSトランジスタ(26d)のゲート端子と前記複数の第3のnMOSトランジスタ(26b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第3のpMOSトランジスタのドレイン端子と前記複数の第3のnMOSトランジスタのドレイン端子とが接続されて前記第1のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第3のnMOSトランジスタ(26b)のうち隣り合う2つの第3のnMOSトランジスタ毎に前記2つの第3のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されており、

前記複数の第3のpMOSトランジスタのうち隣り合う2つの第3のpMOSトランジスタ毎に前記2つの第3のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されており、

前記第2の抵抗素子(Rp)の抵抗値を前記第1の抵抗素子(Rn)の抵抗値に比べて小さく設定することにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする。

【0020】

請求項5に記載の発明では、前記第2のNOTゲート(22A)は、

電源とグランドとの間に並列配置される複数の第3のpMOSトランジスタ(26d)と、

前記第3のpMOSトランジスタ(26d)とグランドとの間に並列配置される複数の第3のnMOSトランジスタ(26b)とを備え、

前記複数の第3のpMOSトランジスタ(26d)のゲート端子と前記複数の第3のnMOSトランジスタ(26b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第3のpMOSトランジスタのドレイン端子と前記複数の第3のnMOSトランジスタのドレイン端子とが接続されて前記第2のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第3のnMOSトランジスタ(26b)のうち隣り合う2つの第3のnMOSトランジスタ毎に前記2つの第3のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されており、

前記複数の第3のpMOSトランジスタのうち隣り合う2つの第3のpMOSトランジスタ毎に前記2つの第3のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されており、

前記第2の抵抗素子(Rp)の抵抗値を前記第1の抵抗素子(Rn)の抵抗値に比べて大きく設定することにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とする。

【0021】

請求項6に記載の発明では、発振信号を出力する発振回路(10)と、

前記発振信号の信号レベルが第1閾値(Th1)以上のときローレベルの出力信号を出力し、前記信号レベルが前記第1閾値未満のときハイレベルの出力信号を出力する第1の信号出力回路(21A)を有し、前記第1の信号出力回路(21A)の出力信号とイネーブル信号とに基づいてハイレベル或いはローレベルの出力信号を出力する第1の論理ゲート(21B、21C)と、

前記信号レベルが第2閾値(Th2)以上のときローレベルの出力信号を出力し、前記信号レベルが前記第2閾値未満のときハイレベルの出力信号を出力する第2の信号出力回路(22A)を有し、前記第2の信号出力回路(22A)の出力信号と前記イネーブル信号とに基づいてハイレベル或いはローレベルの出力信号を出力する第2の論理ゲート(22B、22C)と、

前記第1、第2の論理ゲートのうち一方の論理ゲートがハイレベル信号を出力するときにローレベル信号を出力し、前記一方の論理ゲートがローレベル信号を出力するときにハイレベル信号を出力する第3のNOTゲート(23)と、

前記第1、第2の論理ゲートのうち一方の論理ゲート以外の他方の論理ゲートの出力信号と前記第3のNOTゲートの出力信号とをそれぞれ入力信号として、前記それぞれの入力信号が順次互いに相反するレベルになるとき前記入力信号を矩形波に波形整形してクロックとして出力するフリップフロップ回路(24)と、を備え、

前記イネーブル信号は、当該クロック出力回路に対してクロック出力の許可を外部装置が指令するための信号であり、前記イネーブル信号によって当該クロック出力回路に対してクロック出力の許可を前記外部装置が指令する際には、前記第1の論理ゲートはその出力信号として、前記第1の信号出力回路の出力信号を出力し、かつ前記第2の論理ゲートはその出力信号として、前記第2の信号出力回路の出力信号を出力するものであり、

前記第1閾値(Th1)は、前記第2閾値(Th2)よりも大きい値に設定されており、

前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなり、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とする。

【0022】

請求項6に記載の発明によれば、発振信号の周波数が高くなるほど第1閾値が大きくなるので、発振信号の振幅が小さい場合には、周波数が高くなるほど、第1の信号出力回路の出力信号がハイレベルからローレベルに変化し難くなる。これに加えて、発振信号の周波数が高くなるほど第2閾値が小さくなるので、発振信号の振幅が小さい場合には、周波数が高くなるほど、第2の信号出力回路の出力信号のレベルがローレベルからハイレベルに変化し難くなる。

【0023】

したがって、発振信号の振幅が小さく、かつ周波数が高い場合には、第1、第2の信号出力回路の出力信号が互いに相反するレベルになる。このため、イネーブル信号によって当該クロック出力回路に対してクロック出力の許可を外部装置が指令する際にも、第1、第2の論理ゲートの出力信号が互いに相反するレベルになる。これに伴い、第1、第2の論理ゲートのうち他方の論理ゲートの出力信号と第3のNOTゲートの出力信号とが同一レベルになるので、フリップフロップ回路からクロックが出力されない。

【0024】

すなわち、外部装置がクロック出力回路に対してクロック出力の許可を指令する場合においても、発振信号の振幅が小さく、かつ周波数が高い場合には、フリップフロップ回路からクロックが出力されない。このため、上述の請求項1に記載の発明と同様、発振回路においてオーバートーン発振が生じているときには、フリップフロップ回路からクロックが出力されなくなる。その後、発振回路の発振周波数が低下して予め設定された周波数に移行すると、他方の論理ゲートの出力信号と第3のNOTゲートの出力信号とが相違するレベルになるので、フリップフロップ回路がクロックを出力することができる。したがって、必要以上に長い時間、クロックの出力を待機させることはない。すなわち、クロックの出力を待機させるための発振安定時間を短くして、発振回路の電流の消費を抑えることができる。

【0025】

したがって、上記請求項1に記載の発明と同様、発振回路での無駄な電力消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することができる。

【0026】

請求項7に記載の発明では、前記第1の信号出力回路(21A)は、

電源とグランドとの間に配置される第1のpMOSトランジスタ(25a)と、

前記第1のpMOSトランジスタとグランドとの間に並列配置される複数の第1のnMOSトランジスタ(25b)とを備え、

前記第1のpMOSトランジスタ(25a)のゲート端子と前記複数の第1のnMOSトランジスタ(25b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記第1のpMOSトランジスタのドレイン端子と前記複数の第1のnMOSトランジスタのドレイン端子との間の共通接続端子が前記第1の信号出力回路の出力信号を出力する出力端子を構成し、

前記複数の第1のnMOSトランジスタ(25b)のうち隣り合う2つの第1のnMOSトランジスタ毎に前記2つの第1のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されることにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする。

【0027】

請求項8に記載の発明では、前記第1の論理ゲート(21B)は、前記電源と前記複数の第1のnMOSトランジスタ(25b)との間で前記第1のpMOSトランジスタ(25a)に対して直列配置されて前記イネーブル信号に基づいてオン、オフする第4のpMOSトランジスタ(27a)と、前記第1のpMOSトランジスタ(25a)とグランドとの間で前記複数の第1のnMOSトランジスタ(25b)に対して並列配置されて前記イネーブル信号に応じてオン、オフする第4のnMOSトランジスタ(27b)とを備えることにより、前記第1の論理ゲートが前記発振信号と前記イネーブル信号とに基づいてNOR演算するNORゲートを構成することを特徴とする。

【0028】

請求項9に記載の発明では、前記第1の論理ゲート(21C)は、前記電源と前記複数の第1のnMOSトランジスタ(25b)との間で前記第1のpMOSトランジスタ(25a)に対して並列配置されて前記イネーブル信号に基づいてオン、オフする第5のpMOSトランジスタ(28a)と、前記第1のpMOSトランジスタ(25a)とグランドとの間で前記複数の第1のnMOSトランジスタ(25b)と直列配置されて前記イネーブル信号に基づいてオン、オフする第5のnMOSトランジスタ(28b)とを備えることにより、前記第1の論理ゲートが前記発振信号と前記イネーブル信号に基づいてNAND演算してこのNAND演算するNANDゲートを構成することを特徴とする。

【0029】

請求項10に記載の発明では、前記第2の信号出力回路(22A)は、

電源とグランドとの間に並列配置される複数の第2のpMOSトランジスタ(25d)と、

前記複数の第2のpMOSトランジスタとグランドとの間に配置される第2のnMOSトランジスタ(25e)とを備え、

前記複数の第2のpMOSトランジスタ(25d)のゲート端子と第2のnMOSトランジスタ(25e)とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第2のpMOSトランジスタのドレイン端子と前記第2のnMOSトランジスタのドレイン端子との間の共通接続端子が前記第2の信号出力回路の出力信号を出力する出力端子を構成し、

前記複数の第2のpMOSトランジスタのうち隣り合う2つの第2のpMOSトランジスタ(25d)毎に前記第2のpMOSトランジスタ(25d)のゲート端子の間には第2の抵抗素子(Rp)が配置されることにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなっていることを特徴とする。

【0030】

請求項11に記載の発明では、前記第2の論理ゲート(22B)は、前記電源とグランドとの間で前記複数の第2のpMOSトランジスタ(25d)に対して直列接続されて前記イネーブル信号に応じてオン、オフする第6のpMOSトランジスタ(27d)と、前記複数の第2のpMOSトランジスタ(25d)とグランドとの間で前記第2のnMOSトランジスタ(25e)に対して並列配置されて前記イネーブル信号に応じてオン、オフする第6のnMOSトランジスタ(27e)とを備えることにより、前記第2の論理ゲート(22B)が前記発振信号と前記イネーブル信号とに基づいてNOR演算するNORゲートを構成していることを特徴とする。

【0031】

請求項12に記載の発明では、前記第2の論理ゲート(22C)は、前記電源と前記第2のnMOSトランジスタ(25e)との間で前記複数の第2のpMOSトランジスタ(25d)に対して並列配置されて前記イネーブル信号に応じてオン、オフする第7のpMOSトランジスタ(28d)と、前記複数の第2のpMOSトランジスタ(25d)とグランドとの間で前記第2のnMOSトランジスタ(25e)に対して直列接続されて前記イネーブル信号に応じてオン、オフする第7のnMOSトランジスタ(28e)とを備えることにより、前記第2の論理ゲート(22C)が前記発振信号と前記イネーブル信号とに基づいてNAND演算するNANDゲートを構成していることを特徴とする。

【0032】

請求項13に記載の発明では、前記複数の第1のnMOSトランジスタ(25b)のうち隣り合う2つの第1のnMOSトランジスタ毎にて前記隣り合う2つの第1のnMOSトランジスタのうち後段の第1のnMOSトランジスタのゲート端子とソース端子との間に第1のコンデンサ(C1)が配置されていることを特徴とする。

【0033】

請求項14に記載の発明では、前記複数の第2のpMOSトランジスタ(25d)のうち前記隣り合う2つの第2のpMOSトランジスタ毎にて前記2つの第2のpMOSトランジスタのうち後段の第2のnMOSトランジスタのゲート端子とソース端子との間に第2のコンデンサ(C2)が配置されていることを特徴とする。

【0034】

請求項15に記載の発明では、前記フリップフロップ回路から出力される前記クロックの個数をカウントするカウンタ回路(31)と、

前記カウンタ回路のカウント値が一定期間の間にて第1閾値以上になるか否かを判定する第1の判定回路(32)と、

前記一定期間の間における前記カウント値が第1閾値以上であると前記第1の判定回路が判定したときには他の装置に対して前記クロックを出力し、前記一定期間の間における前記カウント値が第1閾値未満であると前記第1の判定回路が判定したときには前記他の装置に対する前記クロックの出力を停止する出力制御回路(50)とを備えていることを特徴とする。

【0035】

請求項16に記載の発明では、前記カウンタ回路のカウント値が一定期間の間にて第2閾値未満になるか否かを判定する第2の判定回路(32)を備え、

前記一定期間の間における前記カウント値が第1閾値以上であると前記第1の判定回路が判定し、かつ前記一定期間の間における前記カウント値が第2閾値未満であると前記第2の判定回路が判定したときには前記出力制御回路(50)が前記他の装置に対して前記クロックを出力し、

前記一定期間の間における前記カウント値が第1閾値未満であると前記第1の判定回路が判定したとき、或いは記一定期間の間における前記カウント値が第2閾値以上であると前記第2の判定回路が判定したときには前記出力制御回路(50)が前記他の装置に対する前記クロックの出力を停止することを特徴とする。

【0036】

請求項17に記載の発明では、前記発振回路は、その出力信号の信号波形が正弦波状となる正弦波信号を前記発振信号として出力することを特徴とする。

【0037】

請求項18に記載の発明では、前記発振回路は、その出力信号の信号波形が周期的に二等辺三角形となる三角波信号を前記発振信号として出力することを特徴とする。

【0038】

請求項19に記載の発明では、前記発振回路は、その出力信号の信号波形がノコギリ波状となるノコギリ波信号を前記発振信号として出力することを特徴とする。

【0039】

なお、この欄および特許請求の範囲で記載した各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【図面の簡単な説明】

【0040】

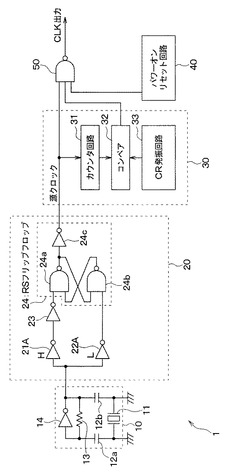

【図1】本発明の第1実施形態におけるクロック出力回路の電気回路構成を示す図である。

【図2】図1のNOTゲートの回路構成の詳細を示す図である。

【図3】図1のNOTゲートの回路構成の詳細を示す図である。

【図4】図1の周波数カウンタの作動を説明するための図である。

【図5】第1実施形態における閾値の変化を説明するためのNOTゲートの回路構成を示す図である。

【図6】第1実施形態において入力スルーレートと閾値との関係を示す特性図である。

【図7】本発明の第2実施形態におけるNOTゲートの電気回路構成を示す図である。

【図8】第2実施形態におけるNOTゲートの発振信号の周波数と第1、第2閾値の関係を示す図である。

【図9】本発明の第3実施形態におけるNORゲートの電気回路構成を示す図である。

【図10】第3実施形態におけるNORゲートの電気回路構成を示す図である。

【図11】本発明の第4実施形態におけるNANDゲートの電気回路構成を示す図である。

【図12】第4実施形態におけるNANDゲートの電気回路構成を示す図である。

【図13】本発明の第5実施形態におけるNORゲートの電気回路構成を示す図である。

【図14】第5実施形態におけるNORゲートの電気回路構成を示す図である。

【図15】本発明の第5実施形態における源クロック、CR発振回路の出力信号、比較器の出力信号のタイミングチャートである。

【発明を実施するための形態】

【0041】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、説明の簡略化を図るべく、図中、同一符号を付してある。

【0042】

(第1実施形態)

図1に本発明のクロック出力回路1の第1実施形態の電気回路構成を示す。

【0043】

クロック出力回路1は、マイクロコンピュータなどの他の装置にクロック(図中CLKと記す)を出力するもので、発振回路10、フィルタ回路20、周波数カウンタ30、パワーオンリセット回路40、およびNANDゲート50を備える。

【0044】

発振回路10は、発振子11、コンデンサ12a、12b、抵抗素子13、およびNOTゲート14から構成されて、発振子11の発振に基づいて発振信号を出力する周知の回路である。

【0045】

本実施形態の発振信号としては、信号波形が正弦波状となる正弦波信号が用いられている。発振子11としては、水晶発振子などを用いることができる。

【0046】

フィルタ回路20は、後述するように、発振回路10から出力される発振信号のうち、発振回路10の起動時における高い周波数で振幅が小さい発振信号を除去するもので、NOTゲート21A、22A、23、およびRSフリップフロップ24から構成されている。

【0047】

NOTゲート21Aは、発振信号の信号レベルが第1閾値Th1以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第1閾値Th1未満のときハイレベルの出力信号を出力する第1のNOTゲートである。なお、NOTゲート21Aの具体的な回路構成は後述する。

【0048】

NOTゲート22Aは、発振信号の信号レベルが第2閾値Th2以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第2閾値Th2未満のときハイレベルの出力信号を出力する第2のNOTゲートである。なお、NOTゲート22Aの具体的な回路構成は後述する。

【0049】

NOTゲート23は、NOTゲート21Aの出力信号のレベルがハイレベルのとき出力信号がローレベルになり、NOTゲート21Aの出力信号のレベルがローレベルのとき出力信号がハイレベルになるものである。

【0050】

RSフリップフロップ回路24は、NOTゲート22Aの出力信号をセット入力(入力信号)とし、NOTゲート23の出力信号をリセット入力(入力信号)として、セット入力およびリセット入力に応じてクロックを出力する周知のRSフリップフロップである。

【0051】

なお、RSフリップフロップ回路24から出力されるクロックとクロック出力回路1からマイクロコンピュータに与えられるクロックCLKとを区別するために、RSフリップフロップ回路24から出力されるクロックを便宜上、源クロックともいう。

【0052】

具体的には、RSフリップフロップ回路24は、NANDゲート24a、24b、およびNOTゲート24cから構成されている。

【0053】

NANDゲート24aは、NANDゲート24bの出力信号とNOTゲート23の出力信号とに基づいてNAND演算を行う。NANDゲート24bは、NANDゲート24aの出力信号とNOTゲート22Aの出力信号とに基づいてNAND演算を行う。NOTゲート24cは、NANDゲート24aの出力信号のNOT演算を行う。

【0054】

周波数カウンタ30は、RSフリップフロップ回路24から出力される源クロックの周波数をカウントして、このカウントした源クロックの周波数が一定周波数以上であるか否かを判定するためのもので、カウンタ回路31、比較回路(図中コンペアと記す)32、およびCR発振回路33から構成されている。

【0055】

カウンタ回路31は、RSフリップフロップ回路24から出力される源クロックの個数を数えるカウンタである。比較回路32は、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達するか否かを判定する。CR発振回路33は、コンデンサおよび抵抗素子を用いて帰還回路を構成して発振を生じさせる周知の回路である。

【0056】

パワーオンリセット回路40は、電源から出力される電源電圧に応じてハイレベル信号を出力する。

【0057】

NANDゲート50は、パワーオンリセット回路40の出力信号、比較回路32の出力信号、およびRSフリップフロップ回路24の出力信号(源クロック)を用いてNAND演算を行う。

【0058】

次に、本実施形態のNOTゲート21Aの回路構成について図2(a)、(b)を参照して説明する。

【0059】

図2(a)にNOTゲート21Aの回路構成を示す。図2(b)にNOTゲート21Aの第1閾値Th1と発振信号の周波数との関係を示す。

【0060】

NOTゲート21Aは、1つのpMOSトランジスタ25aおよびM個のnMOSトランジスタ25bを備える。Mは2以上の整数である。

【0061】

pMOSトランジスタ25aは、電源とグランドとの間に配置されている第1のpMOSトランジスタである。M個のnMOSトランジスタ25bは、pMOSトランジスタ25aのドレイン端子とグランドとの間に並列に配置されている。nMOSトランジスタ25bは、特許請求の範囲に記載の第1のnMOSトランジスタに対応している

pMOSトランジスタ25aのゲート端子とM個のnMOSトランジスタ25bのゲート端子とが接続されて、発振回路10の出力信号が与えられる入力端子25gを構成している。

【0062】

pMOSトランジスタ25aのドレイン端子とM個のnMOSトランジスタ25bのドレイン端子とが接続されて、NOTゲート21A自体の出力信号を出力する出力端子25cを構成している。

【0063】

M個のnMOSトランジスタ25bにおいて隣り合う2つのnMOSトランジスタ25b毎に、2つのnMOSトランジスタ25bのうち前段のnMOSトランジスタ25bのゲート端子と後段のnMOSトランジスタ25bのゲート端子との間に配置される抵抗素子(第1の抵抗素子)Rnが設けられている。

【0064】

つまり、M個のnMOSトランジスタ25bのうち最後段のnMOSトランジスタ25bと入力端子25gとの間には、(M−1)個の抵抗素子Rnが直列に接続されている。

【0065】

ここで、最後段のnMOSトランジスタ25bは、M個のnMOSトランジスタ25bのうち入力端子25gから最も離れた箇所に位置するnMOSトランジスタ25bである。

【0066】

(M−1)個の抵抗素子Rnにおいて隣接する2つの抵抗素子Rn毎にこの2つの抵抗素子Rnの間の共通接続端子とnMOSトランジスタ25bのゲート端子とが接続されている。(M−1)個の抵抗素子Rnは、M個のnMOSトランジスタ25bのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第1の遅延回路を構成している。

【0067】

このように構成されるNOTゲート21Aでは、発振信号の周波数が高くなるほど、第1の閾値Th1が大きくなる(図2(b)参照)。第1の閾値Th1は、NOTゲート21Aの出力信号のレベルVoをハイレベルからローレベルに変化させる入力信号のレベルViである。

【0068】

なお、図2(b)中の縦軸は、NOTゲート21Aの出力信号(電圧レベル)Voとし、横軸は、NOTゲート21Aの入力信号(すなわち、発振信号)Viし、VDDが電源電圧である。

【0069】

次に、本実施形態のNOTゲート22Aの回路構成について説明する。

【0070】

図3(a)にNOTゲート22Aの回路構成を示す。図3(b)にNOTゲート22Aの第2閾値Th2と発振信号の周波数との関係を示す。

【0071】

NOTゲート22Aは、M個のpMOSトランジスタ25d、および1つのnMOSトランジスタ25eを備えている。

【0072】

M個のpMOSトランジスタ25dは、電源とグランドとの間に配置されている。nMOSトランジスタ25eは、M個のpMOSトランジスタ25dとグランドとの間に直列に配置されている。

【0073】

M個のpMOSトランジスタ25dのゲート端子とnMOSトランジスタ25eのゲート端子とが接続されて、発振回路10の出力信号が与えられる入力端子25hを構成している。

【0074】

M個のpMOSトランジスタ25dのドレイン端子とnMOSトランジスタ25eのドレイン端子とが接続されて、NOTゲート22A自体の出力信号を出力する出力端子25fを構成している。

【0075】

M個のpMOSトランジスタ25dにおいて隣り合う2つのpMOSトランジスタ25d毎に、2つのpMOSトランジスタ25dのうち前段のpMOSトランジスタ25dのゲート端子と後段のpMOSトランジスタ25dのゲート端子との間に配置される抵抗素子Rpが設けられている。

【0076】

つまり、M個のpMOSトランジスタ25bのうち最後段のpMOSトランジスタ25dと入力端子25hとの間には、(M−1)個の抵抗素子Rpが直列に接続されている。

【0077】

ここで、最後段のpMOSトランジスタ25dは、M個のpMOSトランジスタ25dのうち入力端子25hから最も離れた箇所に位置するpMOSトランジスタ25dである。

【0078】

(M−1)個の抵抗素子Rpにおいて隣接する2つの抵抗素子Rp毎に2つの抵抗素子Rpの間の共通接続端子とpMOSトランジスタ25dのゲート端子とが接続されている。(M−1)個の抵抗素子Rpは、M個のpMOSトランジスタ25dのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第2の遅延回路を構成している。

【0079】

第2の遅延回路では、発振信号の周波数が高くなるほど、(M−1)個のpMOSトランジスタ25dのゲート電圧が低下するのに生じる遅延時間が長くなる。

【0080】

このように構成されるNOTゲート22Aでは、発振信号の周波数が高くなるほど、第2の閾値Th2が小さくなる(図3(b)参照)。第2の閾値Th2は、出力信号のレベルVoをハイレベルからローレベルに変化させる入力信号のレベルViである。

【0081】

なお、図3(b)中の縦軸はNOTゲート22Aの出力レベルVoとし、横軸はNOTゲート22Aの入力レベル(すなわち、発振信号)Viし、VDDが電源電圧である。

【0082】

本実施形態の図2のNOTゲート21Aの閾値Th1は、図3のNOTゲート22Aの閾値Th2に比べて大きな値に設定されている。

【0083】

ここで、図2のNOTゲート21Aの第1の閾値Th1は、M個のnMOSトランジスタ25bのトランジスタサイズの合計とpMOSトランジスタ25aのトランジスタサイズとの比率によって設定される。図3のNOTゲート22Aの第2の閾値Th2は、M個のpMOSトランジスタ25dのトランジスタサイズの合計とnMOSトランジスタ25eのトランジスタサイズとの比率によって設定される。

【0084】

なお、図3のpMOSトランジスタ25dが特許請求の範囲に記載の第2のpMOSトランジスタに対応し、図3のnMOSトランジスタ25eが特許請求の範囲に記載の第2のnMOSトランジスタに対応し、図3の抵抗素子Rpが特許請求の範囲に記載の第2の抵抗素子に対応する。

【0085】

次に、本実施形態のクロック出力回路1の作動の説明に先立って、RSフリップフロップ24の作動について説明する。

【0086】

まず、図1のNOTゲート23、22Aの出力レベルがローレベルになると、NOTゲート24a、24bの出力レベルがローレベルになる。このため、NOTゲート24cの出力レベルがハイレベルになる。

【0087】

次に、NOTゲート23の出力レベルがローレベルで、NOTゲート22Aの出力レベルがハイレベルになると、NOTゲート24aの出力レベルがハイレベルになり、NOTゲート24bの出力レベルがローレベルになる。

【0088】

次に、NOTゲート23の出力レベルがハイレベルで、NOTゲート22Aの出力レベルがローレベルになると、NOTゲート24aの出力レベルがローレベルになり、NOTゲート24bの出力レベルがハイレベルになる。

【0089】

また、NOTゲート23、22Aの出力レベルがハイレベルになると、NOTゲート24a、24bの出力レベルが変化しない。このため、NOTゲート24cの出力レベルが変化しない。

【0090】

このように、NOTゲート23、22Aの出力レベルが互いに相違するレベルであるときには、NOTゲート24aの出力レベルが、NOTゲート23の出力レベルと相違する出力レベルになる。このため、NOTゲート23、22Aの出力レベルが互いに相違するレベルであるときには、NOTゲート24cの出力レベルは、NOTゲート23の出力レベルと同一の出力レベルとなる。このことにより、RSフリップフロップ24は発振信号の波形を矩形波に整形する役割を果たすことになる。

【0091】

次に、本実施形態のクロック出力回路1の作動について説明する。

【0092】

まず、電源が投入されて発振回路10が起動してオーバートーン発振が生じる場合がある。この場合、発振信号の周波数が予め設定された周波数よりも高くなり、かつ、発振信号の振幅が予め設定された振幅よりも小さくなる。

【0093】

ここで、発振信号の周波数が高い場合には、NOTゲート21Aの第1の閾値Th1が高くなり、NOTゲート22Aの第2の閾値Th2が低くなる。したがって、第1、第2の閾値Th1、Th2が互いに離れることになる。

【0094】

このため、発振信号の振幅が小さい場合には、発振信号の信号レベルが、一周期に亘って、第2の閾値Th2よりも大きく、かつ第1の閾値Th1未満となる場合が生じる。

【0095】

このため、発振信号の一周期に亘って、NOTゲート22Aの出力レベルがローレベルになり、NOTゲート21Aの出力レベルがハイレベルになる。このため、NOTゲート23の出力レベルがローレベルになる。つまり、NOTゲート23、22Aの出力レベルがそれぞれローレベルになるので、NOTゲート24cの出力レベルがハイレベルになる。このとき、RSフリップフロップ24が発振信号の波形を矩形波に整形する役割を停止することになる。

【0096】

その後、発振子11の発振の安定化が進んで、振幅が大きくなり、かつ周波数が低下する。このとき、発振信号の周波数の低下に伴って、NOTゲート21Aの第1の閾値Th1が低下して、NOTゲート22Aの第2の閾値Th2が高くなるので、第1、第2の閾値Th1が互いに近づくことになる。

【0097】

このため、発振信号の信号レベルの変化に伴って、NOTゲート21A、22Aの出力信号のレベルが変化する。

【0098】

具体的には、第1、第2の閾値Th1、Th2よりも発振信号の信号レベルが高いときには、NOTゲート21A、22Aの出力信号がそれぞれローレベルになる。このため、NOTゲート23の出力信号がハイレベルになる。このとき、NOTゲート24cの出力信号がローレベルになる。

【0099】

その後、発振信号の信号レベルが第1、第2の閾値Th1、Th2の間に位置するときには、NOTゲート21Aの出力信号がハイレベルで、NOTゲート22Aの信号レベルがローレベルになる。このため、NOTゲート23の出力信号がローレベルになる。このとき、NOTゲート24cの出力信号がハイレベルになる。

【0100】

次に、第1、第2の閾値Th1、Th2よりも発振信号の信号レベルが低くなると、NOTゲート21A、22Aの出力信号がそれぞれハイレベルになる。このため、NOTゲート23の出力信号がローレベルになる。このとき、NOTゲート24cの出力信号がハイレベルになる。

【0101】

このように発振信号の信号レベルが変化すると、NOTゲート24cの出力信号がローレベル→ハイレベル→ローレベル→ハイレベル・・・のように順次切り替わる。

【0102】

以上により、RSフリップフロップ24は、発振信号の波形を矩形波に整形して、この波形整形した信号を源クロック(図4(a)参照)としてNANDゲート50およびカウンタ回路31に出力する。

【0103】

ここで、発振子11の発振の安定化が進んで、源クロックの周波数(すなわち、発振信号の周波数)が低下したものの、源クロックの周波数が所定周波数に到達していないときには、次のように、図1のパワーオンリセット回路40の出力信号、および比較回路32の出力信号に応じてNANDゲート50がクロックCLKの出力をマスクする。

【0104】

具体的には、パワーオンリセット回路40は、電源が投入されて電源電圧が一定値以上になると、ハイレベル信号をNANDゲート50に出力する。CR発振回路33は発振して周期的に出力信号のレベルが変化する発振信号を出力信号としてカウンタ回路31に出力する(図4(b)参照)。図4(b)では、CR発振回路33の出力信号が一周期毎にローレベルからハイレベルに変化する例を示している。

【0105】

カウンタ回路31は、RSフリップフロップ24から出力される源クロックの数をカウントしてそのカウント値を比較回路32に出力する。比較回路32は、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達したか否かを判定する。すなわち、比較回路32は、一定期間の間において、カウンタ回路31のカウント値が第1の閾値nに到達したか否かを判定する。図4では、CR発振回路33の出力信号の立ち上がりタイミングt1、t2の間において、カウンタ回路31のカウント値が第1の閾値nに到達したか否かを判定する例を示している。

【0106】

源クロックの周波数が所定周波数に到達していないときには、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達していないと比較回路32が判定する。このとき、比較回路32がローレベル信号をNANDゲート50に出力する。このため、パワーオンリセット回路40がハイレベル信号をNANDゲート50に出力していても、NANDゲート50の出力信号はハイレベルを維持する。すなわち、NANDゲート50がクロックCLKの出力をマスクする。

【0107】

その後、発振回路10の発振子11の発振の安定化が進んで、源クロックの周波数が所定周波数に到達すると、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達したと比較回路32が判定する。このとき、比較回路32がハイレベル信号をNANDゲート50に出力する。このため、NANDゲート50の出力信号は、NOTゲート24cの出力信号のレベルの変化に伴って順次変化する。すなわち、NANDゲート50がクロックCLKの出力を開始する。

【0108】

以上説明した本実施形態によれば、発振信号を出力する発振回路10と、発振信号の信号レベルが第1の閾値Th1以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第1の閾値Th1未満のときハイレベルの出力信号を出力するNOTゲート21Aと、発振信号の信号レベルが第2の閾値Th2以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第2の閾値未満のときハイレベルの出力信号を出力するNOTゲート22Aと、NOTゲート21Aの出力信号のレベルと相反するレベルの出力信号を出力するNOTゲート23と、NOTゲート22A、23をそれぞれ入力信号として、それぞれの入力信号が順次互いに相反するレベルになるとき入力信号を矩形波に波形整形してクロックとして出力するRSフリップフロップ回路24とを備える。第1の閾値Th1は、第2の閾値Th2よりも大きい値に設定されており、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなることを特徴とする。

【0109】

したがって、発振信号の振幅が小さい場合において発振信号の周波数が高いときには、第1の閾値Th1が大きくなるので、NOTゲート21Aの出力信号のレベルがハイレベルからローレベルに変化しなくなる。これに加えて、振幅が小さい場合には、発振信号の周波数が高いときには、第2の閾値Th2が小さくなるので、NOTゲート22Aの出力信号のレベルがローレベルからハイレベルに変化しなくなる。

【0110】

以上により、振幅が小さく、かつ発振信号の周波数が高いときには、NOTゲート21Aの出力信号のレベルがハイレベルで、かつNOTゲート22Aの出力信号のレベルがローレベルとなる。このため、NOTゲート23、22Aの出力信号が互いに同一レベルになるので、RSフリップフロップ回路24から源クロックが出力されなくなる。すなわち、発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24から源クロックが出力されることが待機される。その後、発振子11の発振が安定化して、発振信号の振幅が大きくなり、かつ周波数が低くなるとRSフリップフロップ回路24が源クロックの出力を開始する。すなわち、オーバートーン発振が終わると、RSフリップフロップ回路24が源クロックの出力を開始することになる。

【0111】

以上により、必要以上に長い時間、源クロックの出力を待機されることを避けることができる。このため、クロックの出力を待機させる発振安定時間を短くすることができる。したがって、発振回路10の電流の消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することができる。

【0112】

本実施形態では、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達していないときには、比較回路32は、源クロックの周波数が所定周波数に到達していないと判定して、ローレベル信号をNANDゲート50に出力する。このため、NANDゲート50がクロックCLKの出力をマスクする。これにより、周波数が安定していないクロックCLKを出力することを未然に避けることができる。

【0113】

次に、本実施形態のNOTゲート22Aの第2閾値Th2と発振信号の周波数との関係を調べるためのシミュレーションの結果について図5、図6を用いて説明する。

【0114】

本シミュレーションでは、発振信号のスルーレート(入力スルーレート)と図5のNOTゲート22Aの第2閾値Th2との関係を調べたものである。

スルーレートとは、立ち上がりタイミング(或いは立ち下がりタイミング)において、単位時間あたりの発振信号の信号レベルの変化量を示すものである。

【0115】

図5のNOTゲート22Aは、1つのnMOSトランジスタ25e、1つの抵抗素子Rp、および2つのpMOSトランジスタ25dから構成されている。

【0116】

図6は縦軸をNOTゲート22Aの第2の閾値Th2とし、横軸を発振信号のスルーレート(図中入力スルーレートと記す)とし、抵抗素子Rpの抵抗値をパラメータとして第2の閾値Th2と発振信号のスルーレートとの関係を示す特性図である。

【0117】

ここで、図6中の符号G1は抵抗素子Rpの抵抗値を1kΩとしたときのグラフであり、図6中の符号G2は抵抗素子Rpの抵抗値を100kΩとしたときのグラフであり、図6中の符号G3は抵抗素子Rpの抵抗値を1MΩとしたときのグラフである。

【0118】

図6中の符号G1、G2、G3から分かるように、発振信号のスルーレート(入力スルーレート)の上昇に伴って第2の閾値Th2が下がることがこと分かる。

ここで、一般的に、発振信号の周波数が高くなるほど、発振信号のスルーレートが大きくなる。このため、本シミュレーションの結果から、発振信号の周波数が高くなるほど、NOTゲート22Aの第2の閾値Th2が下がることが分かる。

【0119】

このような発振信号の周波数の上昇に伴う第2の閾値Th2の低下は、NOTゲート22Aの寄生抵抗や寄生容量で生じるものではない。

【0120】

上述の第1実施形態では、発振回路10から出力される発振信号としては、信号波形が正弦波状となる正弦波信号を用いた例について説明したが、これに代えて、出力信号の波形が周期的に二等辺三角形となる三角波信号を発振信号として用いてもよい。

【0121】

また、これに限らず、発振回路10から出力される発振信号としては、信号波形がノコギリ歯状となるノコギリ波信号(すなわち、出力信号の波形が周期的に直角三角形状になるノコギリ波信号)を用いてもよい。

【0122】

以下、発振信号の周波数とRSフリップフロップ24の出力との関係についてシミュレーションで調べた結果について説明する。

【0123】

(1)発振信号として三角波信号を用いて、発振信号の振幅を徐々に大きくした場合において、発振信号の周波数を4MHzとしたときには、発振信号の振幅が3.98V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0124】

一方、発振信号の周波数を10MHzとした場合には、発振信号の振幅が4.20V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0125】

以上により、発振信号の周波数が高くなるほど、RSフリップフロップ24が源クロックの出力を開始する発振信号の振幅(論理閾値)が大きくなる。このことから、NOTゲート21Aの第1閾値Th1、およびNOTゲート22Aの第2閾値Th2が周波数によって変化していることが分かる。

【0126】

(2)発振信号をノコギリ波信号としたときに、発振信号の周波数を4MHz、10MHzとして、上記(1)と同様のシミュレーションを実施したところ、発振信号の周波数を4MHzとしたときには、発振信号の振幅が3.89V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0127】

一方、発振信号の周波数を10MHzとした場合には、発振信号の振幅が4.20V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0128】

このことにより、発振信号の周波数が高い場合には、RSフリップフロップ24が源クロックの出力を開始する発振信号の振幅(論理閾値)が大きくなることが分かる。

【0129】

(第2実施形態)

上述の第1実施形態では、1つのnMOSトランジスタ25aおよびM個のnMOSトランジスタ25bからNOTゲート21A(図2参照)を構成し、M個のpMOSトランジスタ25dと1つのnMOSトランジスタ25eからNOTゲート22A(図3参照)を構成する例について説明したが、これに代えて、本実施形態では、M個のpMOSトランジスタ25dおよびM個のnMOSトランジスタ25bからNOTゲート21A(22A)を構成する例について説明する。

【0130】

図7に本実施形態のNOTゲート21A(22A)の回路構成を示す。本実施形態のNOTゲート21A、22Aは、後述する抵抗素子Rp、Rnの値が異なるだけで、同様な構成になっている。

【0131】

NOTゲート21A、22Aは、図3のM個のpMOSトランジスタ25dおよび(M−1)個の抵抗素子Rpと、図2のM個のnMOSトランジスタ25bおよび(M−1)個の抵抗素子Rnとを組み合わせたものである。

【0132】

本実施形態のpMOSトランジスタ25dの個数とnMOSトランジスタ25bの個数とは同一個数で、抵抗素子Rpの個数と抵抗素子Rnの個数とは同一個数である。

【0133】

ここで、NOTゲート21A(22A)は、図2のNOTゲート21Aと同様、M個のnMOSトランジスタ25bのうち最後段のnMOSトランジスタ25bと入力端子25gとの間には、(M−1)個の抵抗素子Rnが直列に接続されている。

【0134】

(M−1)個の抵抗素子Rnは、M個のnMOSトランジスタ25bのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第1の遅延回路を構成している。

【0135】

第1の遅延回路では、発振信号の周波数が高くなるほど、(M−1)個のnMOSトランジスタ25bのゲート電圧が上昇するのに生じる遅延時間が長くなる。

【0136】

本実施形態のNOTゲート21A(22A)は、図3のNOTゲート22Aと同様、M個のpMOSトランジスタ25dのうち最後段のpMOSトランジスタ25dと入力端子25hとの間には、(M−1)個の抵抗素子Rpが直列に接続されている。

【0137】

(M−1)個の抵抗素子Rpは、M個のpMOSトランジスタ25dのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第2の遅延回路を構成している。

【0138】

第2の遅延回路では、発振信号の周波数が高くなるほど、(M−1)個のpMOSトランジスタ25dのゲート電圧が低下するのに生じる遅延時間が長くなる。

【0139】

本実施形態のNOTゲート21Aでは、抵抗素子Rnの抵抗値を抵抗素子Rpの抵抗値に比べて極めて大きい値に設定している(抵抗素子Rn≫抵抗素子Rp)。このため、第1の遅延回路の遅延時間を第2の遅延回路の遅延時間に比べて長い時間に設定することができる。これにより、図2のNOTゲート21Aと同様に、発振信号の周波数が高くなるほど第1の閾値Th1を大きくすることができる(図8(a)参照)。

【0140】

本実施形態のNOTゲート22Aでは、抵抗素子Rnの抵抗値を抵抗素子Rpの抵抗値に比べて極めて小さい値に設定している(抵抗素子Rn≪抵抗素子Rp)。このため、第2の遅延回路の遅延時間を第1の遅延回路の遅延時間に比べて長い時間に設定することができる。これにより、図3のNOTゲート22Aと同様に、発振信号の周波数が高くなるほど第2の閾値Th2を小さくすることができる(図8(b)参照)。

【0141】

なお、図7のpMOSトランジスタ25dが特許請求の範囲に記載の第3のpMOSトランジスタに対応し、図7のnMOSトランジスタ25bが特許請求の範囲に記載の第3のnMOSトランジスタに対応し、図7の抵抗素子Rnが特許請求の範囲に記載の第1の抵抗素子に対応し、図7の抵抗素子Rpが特許請求の範囲に記載の第2の抵抗素子に対応する。

【0142】

(第3実施形態)

上述の第1実施形態では、NOTゲート21A、22Aを用いてフィルタ回路20を構成した例について説明したが、これに限らず、本実施形態では、NORゲート21B、22Bを用いてフィルタ回路20を構成する例について説明する。

【0143】

図9に本実施形態のNORゲート21Bの回路構成を示す。

【0144】

NORゲート21Bは、図2のNOTゲート21Aに代えて用いられるものである。NORゲート21Bは、発振信号とイネーブル信号とに基づいてNOR演算する第1の論理ゲートであって、図2のNOTゲート21Aに対してpMOSトランジスタ27a、およびnMOSトランジスタ27bを追加したものである。

【0145】

ここで、イネーブル信号は、電子制御回路(外部装置)がクロック出力回路1に対してクロックCLKの出力の許可、或いは不許可を指令する信号である。

【0146】

pMOSトランジスタ27aは、nMOSトランジスタ25aとM個のnMOSトランジスタ25bとの間に配置されている。nMOSトランジスタ27bは、pMOSトランジスタ27aとグランドとの間でM個のnMOSトランジスタ25bに並列に配置されている。

【0147】

pMOSトランジスタ27aのゲート端子とnMOSトランジスタ27bのゲート端子とが接続されて、イネーブル信号が入力される入力端子27cを構成している。

【0148】

pMOSトランジスタ27aのドレイン端子、M個のnMOSトランジスタ25bのドレイン端子、およびnMOSトランジスタ27bのドレイン端子が接続されて、出力端子25cを構成している。出力端子25cは、NORゲート21B自体の信号を出力するものである。

【0149】

図10に本実施形態のNORゲート22Bの回路構成を示す。NORゲート22Bは、図3のNOTゲート22Aに代えて用いられるものである。NORゲート22Bは、発振信号とイネーブル信号とによってNOR演算する第2の演算ゲートであって、図3のNOTゲート22Aに対してpMOSトランジスタ27dおよびnMOSトランジスタ27eを追加したものである。

【0150】

pMOSトランジスタ27dは、M個のpMOSトランジスタ25dとnMOSトランジスタ25eとの間に配置されている。nMOSトランジスタ27eは、pMOSトランジスタ27dとグランドとの間で、nMOSトランジスタ25eと並列に接続されている。

【0151】

pMOSトランジスタ27dのゲート端子とnMOSトランジスタ27eのゲート端子とが接続されて、イネーブル信号が入力される入力端子27gを構成している。

【0152】

pMOSトランジスタ27dのドレイン端子とnMOSトランジスタ25e、27eのドレイン端子とが接続されて、出力端子25fを構成している。出力端子25fは、NORゲート21B自体の出力信号を出力するものである。

【0153】

次に、本実施形態のNORゲート21B、22Bの作動について説明する。

【0154】

まず、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可しないときには、イネーブル信号としてのハイレベル信号を図9のNORゲート21Bの入力端子27cに出力する。

【0155】

このとき、pMOSトランジスタ27aはオフする一方、nMOSトランジスタ27bはオンする。このため、NORゲート21Bの入力端子25gに発振信号が発振回路10から与えられても、NORゲート21Bの出力端子25cから出力される出力信号は、ローレベルを維持する。

【0156】

これに加えて、電子制御回路は、イネーブル信号としてのハイレベル信号を図10のNORゲート22Bの入力端子27gに出力する。

【0157】

このとき、pMOSトランジスタ27dはオフする一方、nMOSトランジスタ27eはオンする。このため、NORゲート22Bの入力端子25hに発振信号が発振回路10から与えられても、NORゲート22Bの出力端子25fから出力される出力信号は、ローレベルを維持する。

【0158】

このように、電子制御回路がNORゲート21Bの入力端子27cおよびNORゲート22Bの入力端子27gに対してイネーブル信号としてのハイレベル信号を出力する際には、NORゲート21B、22Bの出力信号は、ローレベルを維持する。このため、フィルタ回路20から源クロックが出力されなくなる。これに伴い、NANDゲート50からクロックが出力されなくなる。

【0159】

次に、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可するときには、イネーブル信号としてのローレベル信号を図9のNORゲート21Bの入力端子27cに出力する。このとき、pMOSトランジスタ27aはオンする一方、nMOSトランジスタ27bはオフする。このため、NORゲート21Bは、その出力信号として、NOTゲート21Aの出力信号を出力する。

【0160】

これに加えて、電子制御回路は、クロック出力回路1に対してイネーブル信号としてのローレベル信号をNORゲート22Bの入力端子27gに出力する。このとき、pMOSトランジスタ27dはオンする一方、nMOSトランジスタ27eはオフする。このため、NORゲート22Bは、その出力信号として、NOTゲート22Aの出力信号を出力する。

【0161】

このように、電子制御回路がNORゲート21Bの入力端子27cおよびNORゲート22Bの入力端子27gに対してイネーブル信号としてのローレベル信号を出力する際には、NORゲート21Bは、その出力信号として、NOTゲート21Aの出力信号を出力し、かつNORゲート22Bは、その出力信号として、NOTゲート22Aの出力信号を出力する。このため、電子制御回路がイネーブル信号としてのローレベル信号を出力する際には、上述第1実施形態と同様に、フィルタ回路20が源クロックを出力する。これに伴い、上述第1実施形態と同様に、NANDゲート50がクロックを出力する。

【0162】

以上説明した本実施形態によれば、電子制御回路は、クロックCLKの出力の許可するときには、イネーブル信号としてのローレベル信号をNORゲート21B(22B)の入力端子27c(27g)に出力する。これに伴い、NORゲート21Bは、その出力信号として、NOTゲート21Aの出力信号を出力し、NORゲート22Bは、その出力信号として、NOTゲート22Aの出力信号を出力する。したがって、NOTゲート21A(22A)に代えてNORゲート21B(22B)を用いてフィルタ回路20を構成することができる。

【0163】

なお、図9のNOTゲート21Aが特許請求の範囲に記載の第1の信号出力回路に対応し、図10のNOTゲート22Aが特許請求の範囲に記載の第2の信号出力回路に対応する。

(第4実施形態)

上述の第1実施形態では、NOTゲート21A(22A)を用いてフィルタ回路20を構成した例について説明したが、これに限らず、本実施形態では、NANDゲート21C(22C)を用いてフィルタ回路20を構成する例について説明する。

【0164】

本実施形態のNANDゲート21Cは、図2のNOTゲート21Aに代えて用いられるものであって、発振信号とイネーブル信号とに基づいてNAND演算する第1の論理ゲートである。

【0165】

図11に本実施形態のNANDゲート21Cの回路構成を示す。

【0166】

NANDゲート21Cは、図2のNOTゲート21Aに対してpMOSトランジスタ28aおよびnMOSトランジスタ28bを追加したものである。

【0167】

pMOSトランジスタ28aは、電源とM個のnMOSトランジスタ25bとの間にpMOSトランジスタ25aと並列に配置されている。nMOSトランジスタ28bは、pMOSトランジスタ25a、28aとM個のnMOSトランジスタ25bとの間に配置されている。

【0168】

pMOSトランジスタ28aのゲート端子とnMOSトランジスタ28bのゲート端子とが接続されて、イネーブル信号が入力される入力端子28cを構成している。

【0169】

pMOSトランジスタ25a、28aのドレイン端子およびnMOSトランジスタ28bのドレイン端子が接続されて、出力端子25cを構成している。出力端子25cは、NANDゲート21C自体の出力信号を出力するものである。

【0170】

また、本実施形態のNORゲート22Cは、図3のNOTゲート22Aに代えて用いられるものであって、発振信号とイネーブル信号とに基づいてNAND演算する。

【0171】

図12に本実施形態のNORゲート22Cの回路構成を示す。

【0172】

NANDゲート22Cは、発振信号とイネーブル信号とによってNAND演算する第2の論理ゲートである。NANDゲート22Cは、図3のNOTゲート22Aに対してpMOSトランジスタ28dおよびnMOSトランジスタ28eを追加したものである。

【0173】

pMOSトランジスタ28dは、電源とnMOSトランジスタ25eとの間でM個のpMOSトランジスタ25dと並列に配置されている。nMOSトランジスタ28eは、M個のpMOSトランジスタ25dおよびpMOSトランジスタ28dとnMOSトランジスタ25eとの間に配置されている。

【0174】

pMOSトランジスタ28dのゲート端子とnMOSトランジスタ28eのゲート端子とが接続されて、イネーブル信号が入力される入力端子28fを構成している。

【0175】

M個のpMOSトランジスタ25dのドレイン端子、pMOSトランジスタ28dのドレイン端子、およびnMOSトランジスタ28eのドレイン端子が接続されて、出力端子25fを構成している。出力端子25fは、NORゲート22C自体の出力信号を出力するものである。

【0176】

次に、本実施形態のNANDゲート21C、22Cの作動について説明する。

【0177】

まず、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可しないときには、イネーブル信号としてのローレベル信号を図11のNANDゲート21Bの入力端子28cに出力する。

【0178】

このとき、pMOSトランジスタ28aがオンして、nMOSトランジスタ28bがオフする。このため、図11のNANDゲート21Cの入力端子25gに発振信号が発振回路10から与えられても、NANDゲート21Cの出力端子25cから出力される出力信号は、ハイレベルを維持する。

【0179】

これに加えて、電子制御回路がイネーブル信号としてのローレベル信号を図12のNANDゲート22Cの入力端子28fに出力する。

【0180】

このとき、pMOSトランジスタ28dがオンして、nMOSトランジスタ28eがオフする。このため、NANDゲート22Bの入力端子25hに発振信号が発振回路10から与えられても、図12のNANDゲート22Bの出力端子25fから出力される出力信号は、ハイレベルを維持する。

【0181】

このように、電子制御回路がNANDゲート21Cの入力端子28cおよびNANDゲート22Cの入力端子28fに対してイネーブル信号としてのローレベル信号を出力する際には、NANDゲート21C、22Cの出力信号は、ハイレベルを維持する。このため、フィルタ回路20から源クロックが出力されなくなる。これに伴い、NANDゲート50からクロックが出力されなくなる。

【0182】

次に、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可するときには、イネーブル信号としてのハイレベル信号を図11のNANDゲート21Cの入力端子28cに出力する。このとき、pMOSトランジスタ28aがオフして、nMOSトランジスタ28bがオンする。このため、NANDゲート21Cは、その出力信号として、NOTゲート21Aの出力信号を出力する。

【0183】

これに加えて、電子制御回路は、イネーブル信号としてのハイレベル信号を図12のNANDゲート22Cの入力端子28fに出力する。このとき、pMOSトランジスタ28dがオフして、nMOSトランジスタ28eがオンする。このため、NANDゲート22Cは、その出力信号として、NOTゲート22Aの出力信号を出力する。

【0184】

このように、電子制御回路がNANDゲート21Cの入力端子28cおよびNANDゲート22Cの入力端子28fに対してイネーブル信号としてのハイレベル信号を出力する際には、NANDゲート21Cは、その出力信号として、NOTゲート21Aの出力信号を出力し、かつNANDゲート22Cは、その出力信号として、NOTゲート22Aの出力信号を出力する。このため、電子制御回路がイネーブル信号としてのハイレベル信号を出力する際には、上述第1実施形態と同様に、フィルタ回路20が源クロックを出力する。これに伴い、上述第1実施形態と同様に、NANDゲート50がクロックを出力する。

【0185】

以上説明した本実施形態によれば、電子制御回路は、クロックCLKの出力の許可するときには、イネーブル信号としてのハイレベル信号をNANDゲート21C(22C)の入力端子28c(28f)に出力する。これに伴い、NANDゲート21Cは、その出力信号としてNOTゲート21Aの出力信号を出力し、NANDゲート22Cは、その出力信号として、NOTゲート22Aの出力信号を出力する。したがって、NORゲート21A(22A)に代えてNAND21C(22C)を用いてフィルタ回路20を構成することができる。

【0186】

なお、図11のNOTゲート21Aが特許請求の範囲に記載の第1の信号出力回路に対応し、図12のNOTゲート22Aが特許請求の範囲に記載の第2の信号出力回路に対応する。

【0187】

(第5実施形態)

上述の第1実施形態では、NOTゲート21A(22A)の遅延回路を(M−1)個の抵抗素子Rp(Rn)を用いて構成した例について説明したが、これに代えて、本実施形態では、(M−1)個の抵抗素子Rp(Rn)に加えて(M−1)個のコンデンサを用いてNOTゲート21A(22A)の遅延回路を構成する例について説明する。

【0188】

図13に本実施形態のNOTゲート21Aの回路構成を示す。

【0189】

本実施形態のNOTゲート21Aは、図2のNOTゲート21Aに(M−1)個のコンデンサ(第1のコンデンサ)C1が追加されている。

【0190】

具体的には、NOTゲート21Aでは、M個のnMOSトランジスタ25bのうち最前段のnMOSトランジスタ25b以外の(M−1)個のnMOSトランジスタ25bに、コンデンサC1が1つずつ設けられている。コンデンサC1は、nMOSトランジスタ25b毎にそのゲート端子とソース端子との間に配置されている。最前段のnMOSトランジスタ25bとは、M個のnMOSトランジスタ25bのうち入力端子25gに最も近いnMOSトランジスタ25bのことである。

【0191】

nMOSトランジスタ25b毎のコンデンサC1は、第1の遅延回路の遅延時間を調整することにより、発振信号に周波数に対する第1の閾値Th1の値を設定することができる。

【0192】

図14に本実施形態のNOTゲート22Aの回路構成を示す。

【0193】

本実施形態のNOTゲート21Aは、図3のNOTゲート22Aに(M−1)個のコンデンサ(第2のコンデンサ)C2が追加されている。

【0194】

具体的には、NOTゲート21Aでは、M個のpMOSトランジスタ25dのうち最前段のpMOSトランジスタ25d以外の(M−1)個のpMOSトランジスタ25dに、コンデンサC2が1つずつ設けられている。コンデンサC2は、pMOSトランジスタ25d毎にそのゲート端子とソース端子との間に配置されている。pMOSトランジスタ25d毎のコンデンサC2は、第2の遅延回路の遅延時間を調整することにより、発振信号に周波数に対する第2の閾値Th2の値を設定することができる。最前段のpMOSトランジスタ25dとは、M個のpMOSトランジスタ25dのうち入力端子25hに最も近いpMOSトランジスタ25dのことである。

【0195】

次に、本実施形態の発振信号の周波数とRSフリップフロップ24の出力との関係についてシミュレーションで調べた結果について説明する。

【0196】

本シミュレーションでは、抵抗素子Rn、Rpの抵抗値を100kΩとし、コンデンサC1、C2の静電容量を0.5pFとし、発振信号を正弦波信号とし、発振信号の周波数を4MHz、10MHzとして、発振信号の振幅を徐々に大きくした。

【0197】

発振信号の周波数を4MHzとしたときには、発振信号の振幅が3.02V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0198】

一方、発振信号の周波数を10MHzとした場合には、発振信号の振幅が3.39V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0199】

以上により、発振信号の周波数が高くなるほど、RSフリップフロップ24が源クロックの出力を開始する発振信号の振幅(論理閾値)が大きくなる。このことから、NOTゲート21Aの第1閾値Th1、およびNOTゲート22Aの第2閾値Th2が周波数によって変化していることが分かる。

【0200】

(第6実施形態)

上述の第1実施形態では、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達していないときには、NANDゲート50がクロックCLKの出力をマスクする例について説明したが、これに加えて、本実施形態では、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第2の閾値m(>第1の閾値n)以上になると、NANDゲート50がクロックCLKの出力をマスクする例について説明する。

【0201】

図15に本実施形態の作動を示す。

【0202】

CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n未満であるときには、比較回路32がローレベル信号をNANDゲート50に出力する。この場合、発振信号の周波数が低すぎると判定されることになる。

【0203】

CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第2の閾値m以上であるときには、比較回路32がローレベル信号をNANDゲート50に出力する。この場合、発振信号の周波数が高すぎる判定されることになる。

【0204】

このように、CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n未満であるとき、或いはカウンタ回路31のカウント値が第2の閾値m以上であるときには、発振信号の周波数が所望の周波数範囲から外れているとして、NANDゲート50がクロックCLKの出力をマスクする。

【0205】

また、CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n以上で、かつ第2の閾値m未満であるときには、比較回路32がハイレベル信号をNANDゲート50に出力する。このため、発振信号の周波数が所望の周波数範囲内に入っているとして、NANDゲート50がクロックCLKを出力する。

【0206】

以上説明した本実施形態によれば、CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n未満であるとき、或いはカウンタ回路31のカウント値が第2の閾値m以上であるときには、発振信号の周波数が所望の周波数範囲から外れているとして、NANDゲート50がクロックCLKの出力をマスクする。CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n以上で、かつ第2の閾値m未満であるときに、発振信号の周波数が所望の周波数範囲内に入っているとして、NANDゲート50がクロックCLKを出力する。したがって、他の装置に出力するクロックの周波数のバラツキを抑えることができる。

【0207】

(他の実施形態)

上述の第1実施形態では、図2のNOTゲート21Aを構成するnMOSトランジスタ25bの個数と、図3のNOTゲート22Aを構成するpMOSトランジスタ25dの個数とをそれぞれ同一数(M個)とした例について説明したが、これに限らず、図2のNOTゲート21Aを構成するnMOSトランジスタ25bの個数と、図3のNOTゲート22Aを構成するpMOSトランジスタ25dの個数とを相違する数にしてもよい。

【0208】

上述の第1実施形態では、NOTゲート21Aの出力端子にNOTゲート23を接続した例について説明したが、これに代えて、NOTゲート22Aの出力端子にNOTゲート23を接続してもよい。

【0209】

上述の第1実施形態では、NOTゲート22A、23の出力信号を波形整形してクロック(源クロック)を生成するためにRSフリップフロップ24を用いる例について説明したが、これに限らず、NOTゲート22A、23の出力信号を波形整形してクロック(源クロック)を生成するのであれば、RSフリップフロップ以外のフリップフロップを用いてもよい。

【0210】

上述の第3実施形態では、図9のNORゲート21Bとして、図2のNOTゲート21Aに対してpMOSトランジスタ27aおよびnMOSトランジスタ27bを加えて構成したものについて説明したが、これに代えて、図7のNOTゲート21Aに対してpMOSトランジスタ27aおよびnMOSトランジスタ27bを追加して図9のNORゲート21Bを構成してもよい。

【0211】

上述の第3実施形態では、図10のNORゲート22Bとして、図3のNOTゲート22Aに対してpMOSトランジスタ27dおよびnMOSトランジスタ27eを追加して構成したものについて説明したが、これに代えて、図7のNOTゲート22Aに対してpMOSトランジスタ27dおよびnMOSトランジスタ27eを追加して構成してもよい。

【0212】

上述の第3、第4実施形態では、NOTゲート21A(22A)に代わる第1の論理ゲートとして、NORゲート21B(22B)或いはNANDゲート21C(22C)を用いた例について説明したが、これに代えて、第1の論理ゲートとして、NORゲート、NANDゲート以外の回路を用いてもよい。

【0213】

上述の第4実施形態では、図11のNANDゲート21Cとしては、図2のNOTゲート21Aに対してpMOSトランジスタ28aおよびnMOSトランジスタ28bを追加して構成したものを示したが、これに代えて、図7のNOTゲート21Aに対してpMOSトランジスタ28aおよびnMOSトランジスタ28bを追加してNANDゲート21Cを構成してもよい。

【0214】

上述の第4実施形態では、図12のNORゲート22Cとしては、図3のNOTゲート22Aに対してpMOSトランジスタ28dおよびnMOSトランジスタ28eを追加して構成したものについて説明したが、これに代えて、図7のNOTゲート22Aに対してpMOSトランジスタ28dおよびnMOSトランジスタ28eを追加して構成してもよい。

【0215】

上述の第5実施形態では、図13のNOTゲート21Aとしては、図2のNOTゲート21Aに(M−1)個のコンデンサC1を追加して構成したものについて説明したが、これと同様に、図9のNOTゲート21Aに(M−1)個のコンデンサC1を追加して構成したものをNORゲート21Bとしてもよい。また、図11のNOTゲート21Aに(M−1)個のコンデンサC1を追加して構成したものをNORゲート21Cとしてもよい。

【0216】

上述の第5実施形態では、図14のNOTゲート22Aとしては、図3のNOTゲート22Aに(M−1)個のコンデンサC2を追加して構成したものについて説明したが、これと同様に、図10のNOTゲート22Aに(M−1)個のコンデンサC2を追加して構成したものをNORゲート22Bとしてもよい。

また、図12のNOTゲート22Aに(M−1)個のコンデンサC2を追加して構成したものをNORゲート22Cとしてもよい。

【符号の説明】

【0217】

1 クロック出力回路

10 発振回路

11 発振子

12a コンデンサ

12b コンデンサ

13 抵抗素子

14 NOTゲート

20 フィルタ回路

21A NOTゲート

22A NOTゲート

21B NORゲート

22B NORゲート

21C NANDゲート

22C NANDゲート

23 NOTゲート

24 RSフリップフロップ

30 周波数カウンタ

31 カウンタ回路、

32 比較回路、

33 CR発振回路

40 パワーオンリセット回路

50 NANDゲート

25a pMOSトランジスタ

25b nMOSトランジスタ

25d pMOSトランジスタ

25e nMOSトランジスタ

25h 入力端子

25f 出力端子

27a pMOSトランジスタ

27b nMOSトランジスタ

28a pMOSトランジスタ

28b nMOSトランジスタ

28d pMOSトランジスタ

28e nMOSトランジスタ

Rp 抵抗素子

Rn 抵抗素子

Th1 第1の閾値

Th2 第2の閾値

C1 コンデンサ

C2 コンデンサ

【技術分野】

【0001】

本発明は、クロックを出力するクロック出力回路に関するものである。

【背景技術】

【0002】

従来、マイクロコンピュータの周辺回路として、発振信号をクロックとしてマイクロコンピュータに出力する発振回路と、電源が投入された後に予め決められた一定期間経過すると、リセット信号をマイクロコンピュータに出力するリセット回路とを備えるものがある。

【0003】

ここで、上記一定期間は、電源の投入後に発振回路の発振が安定するのに要する時間である。

【0004】

このことにより、電源の投入後一定期間経過すると、マイクロコンピュータは、リセット回路からリセット信号を受けるので、安定した発信を行う発振回路から出力されるクロックに基づいてマイクロコンピュータが正常に動作を開始することになる。

【0005】

また、特許文献1のクロック出力回路のように、発振回路の出力信号の振幅が安定化すると、発振回路の出力信号をマイクロコンピュータに出力することを許可する出力制御回路を備えるものがある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平4−105108号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述のマイクロコンピュータの周辺回路では、発振回路の起動後一定期間経過すると、マイクロコンピュータが発振回路から出力されるクロックに基づいて動作を開始するため、発振回路の起動後一定期間経過する前に、実際には発振回路の発振が安定してマイクロコンピュータが動作可能になっているにも関わらず、マイクロコンピュータが待機している場合がある。このため、必要以上に長い時間、マイクロコンピュータが待機することになり、発振回路などで余分な電流が消費される。

【0008】

これに対して、上述の特許文献1では、発振回路の出力信号の振幅が安定化すると、出力制御回路が発振回路に対して発振信号をマイクロコンピュータに出力することを許可するため、マイクロコンピュータが待機する時間を短くすることができる。しかし、この場合、発振回路の発振周波数が不安定であるにも関わらず、発振回路の出力信号の振幅が安定すると、出力制御回路が発振回路に対して発振信号の出力を許可して、発振回路の発振出力がクロックとしてマイクロコンピュータに出力される恐れがある。すなわち、周波数が不安定な状態でクロックが発振回路からマイクロコンピュータに与えられる恐れがある。

【0009】

本発明は上記点に鑑みて、発振回路での無駄な電流の消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するため、請求項1に記載の発明では、発振信号を出力する発振回路(10)と、

前記発振信号の信号レベルが第1閾値(Th1)以上のときローレベルの出力信号を出力し、前記信号レベルが第1閾値未満のときハイレベルの出力信号を出力する第1のNOTゲート(21A)と、

前記信号レベルが第2閾値(Th2)以上のときローレベルの出力信号を出力し、前記信号レベルが第2閾値未満のときハイレベルの出力信号を出力する第2のNOTゲート(22A)と、

前記第1、第2のNOTゲートのうち一方のNOTゲートがハイレベル信号を出力するときにローレベル信号を出力し、前記一方のNOTゲートがローレベル信号を出力するときにハイレベル信号を出力する第3のNOTゲート(23)と、

前記第1、第2のNOTゲートのうち一方のNOTゲート以外の他方のNOTゲートの出力信号と前記第3のNOTゲートの出力信号とをそれぞれ入力信号として、前記それぞれの入力信号が順次互いに相反するレベルになるとき前記入力信号を矩形波に波形整形してクロックとして出力するフリップフロップ回路(24)と、を備え、

前記第1閾値(Th1)は、前記第2閾値(Th2)よりも大きい値に設定されており、

前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなり、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とする。

【0011】

請求項1に記載の発明によれば、発振信号の周波数が高くなるほど第1閾値が大きくなるので、振幅が小さい場合には、発振信号の周波数が高くなるほど、第1のNOTゲートの出力信号のレベルがハイレベルからローレベルに変化し難くなる。これに加えて、発振信号の周波数が高くなるほど第2閾値が小さくなるので、振幅が小さい場合には、発振信号の周波数が高くなるほど、第2のNOTゲートの出力信号のレベルがローレベルからハイレベルに変化し難くなる。

【0012】

このため、振幅が小さく、かつ発振信号の周波数が高い場合には、第1、第2のNOTゲートの出力信号が互いに相反するレベルになる。これに伴い、他方のNOTゲートの出力信号と第3のNOTゲートの出力信号とが同一レベルになるので、フリップフロップ回路からクロックが出力され難くなる。

【0013】

ここで、発振回路はその起動時において予め設定された周波数よりも高くなり、かつ、発振信号の振幅が予め設定された振幅よりも小さくなるオーバートーン発振が生じる場合がある。

【0014】

これに対して、請求項1に記載の発明では、上述の如く、振幅が小さく、かつ発振信号の周波数が高い場合には、フリップフロップ回路からクロックが出力されない。このため、発振回路においてオーバートーン発振が生じているときには(すなわち、発振回路の発振が不安定化であるときには)、フリップフロップ回路からクロックが出力されなくなる。その後、発振回路の発振周波数が低下して予め設定された周波数に移行すると(すなわち、発振回路の発振が安定化すると)、他方の論理ゲートの出力信号と第3のNOTゲートの出力信号とが相違するレベルになるので、フリップフロップ回路がクロックを出力することができる。

【0015】

このため、発振回路においてオーバートーン発振が生じているときだけ、フリップフロップ回路からクロックが出力されなくなる。したがって、必要以上に長い時間、クロックの出力を待機させることはない。すなわち、クロックの出力を待機させるための発振安定時間を短くして、発振回路の電流の消費を抑えることができる。

【0016】

以上により、発振回路の電流の消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することができる。

【0017】

請求項2に記載の発明では、前記第1のNOTゲート(21A)は、

電源とグランドとの間に配置される第1のpMOSトランジスタ(25a)と、

前記第1のpMOSトランジスタ(25a)とグランドとの間に並列配置される複数の第1のnMOSトランジスタ(25b)とを備え、

前記第1のpMOSトランジスタ(25a)のゲート端子と前記複数の第1のnMOSトランジスタ(25b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記第1のpMOSトランジスタのドレイン端子と前記複数の第1のnMOSトランジスタのドレイン端子とが接続されて前記第1のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第1のnMOSトランジスタ(25b)のうち隣り合う2つの第1のnMOSトランジスタ毎に前記2つの第1のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されることにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする。

【0018】

請求項3に記載の発明では、前記第2のNOTゲート(22A)は、

電源とグランドとの間に並列配置される複数の第2のpMOSトランジスタ(25d)と、

前記複数の第2のpMOSトランジスタとグランドとの間に配置される第2のnMOSトランジスタ(25e)とを備え、

前記複数の第2のpMOSトランジスタのゲート端子と前記第2のnMOSトランジスタのゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第2のpMOSトランジスタのドレイン端子と前記第2のnMOSトランジスタのドレイン端子とが接続されて前記第2のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第2のpMOSトランジスタ(25d)のうち隣り合う2つの第2のpMOSトランジスタ毎に前記2つの第2のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されることにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなっていることを特徴とする。

【0019】

請求項4に記載の発明では、前記第1のNOTゲート(21A)は、

電源とグランドとの間に並列配置される複数の第3のpMOSトランジスタ(26d)と、

前記第3のpMOSトランジスタ(26d)とグランドとの間に並列配置される複数の第3のnMOSトランジスタ(26b)とを備え、

前記複数の第3のpMOSトランジスタ(26d)のゲート端子と前記複数の第3のnMOSトランジスタ(26b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第3のpMOSトランジスタのドレイン端子と前記複数の第3のnMOSトランジスタのドレイン端子とが接続されて前記第1のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第3のnMOSトランジスタ(26b)のうち隣り合う2つの第3のnMOSトランジスタ毎に前記2つの第3のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されており、

前記複数の第3のpMOSトランジスタのうち隣り合う2つの第3のpMOSトランジスタ毎に前記2つの第3のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されており、

前記第2の抵抗素子(Rp)の抵抗値を前記第1の抵抗素子(Rn)の抵抗値に比べて小さく設定することにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする。

【0020】

請求項5に記載の発明では、前記第2のNOTゲート(22A)は、

電源とグランドとの間に並列配置される複数の第3のpMOSトランジスタ(26d)と、

前記第3のpMOSトランジスタ(26d)とグランドとの間に並列配置される複数の第3のnMOSトランジスタ(26b)とを備え、

前記複数の第3のpMOSトランジスタ(26d)のゲート端子と前記複数の第3のnMOSトランジスタ(26b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第3のpMOSトランジスタのドレイン端子と前記複数の第3のnMOSトランジスタのドレイン端子とが接続されて前記第2のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第3のnMOSトランジスタ(26b)のうち隣り合う2つの第3のnMOSトランジスタ毎に前記2つの第3のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されており、

前記複数の第3のpMOSトランジスタのうち隣り合う2つの第3のpMOSトランジスタ毎に前記2つの第3のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されており、

前記第2の抵抗素子(Rp)の抵抗値を前記第1の抵抗素子(Rn)の抵抗値に比べて大きく設定することにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とする。

【0021】

請求項6に記載の発明では、発振信号を出力する発振回路(10)と、

前記発振信号の信号レベルが第1閾値(Th1)以上のときローレベルの出力信号を出力し、前記信号レベルが前記第1閾値未満のときハイレベルの出力信号を出力する第1の信号出力回路(21A)を有し、前記第1の信号出力回路(21A)の出力信号とイネーブル信号とに基づいてハイレベル或いはローレベルの出力信号を出力する第1の論理ゲート(21B、21C)と、

前記信号レベルが第2閾値(Th2)以上のときローレベルの出力信号を出力し、前記信号レベルが前記第2閾値未満のときハイレベルの出力信号を出力する第2の信号出力回路(22A)を有し、前記第2の信号出力回路(22A)の出力信号と前記イネーブル信号とに基づいてハイレベル或いはローレベルの出力信号を出力する第2の論理ゲート(22B、22C)と、

前記第1、第2の論理ゲートのうち一方の論理ゲートがハイレベル信号を出力するときにローレベル信号を出力し、前記一方の論理ゲートがローレベル信号を出力するときにハイレベル信号を出力する第3のNOTゲート(23)と、

前記第1、第2の論理ゲートのうち一方の論理ゲート以外の他方の論理ゲートの出力信号と前記第3のNOTゲートの出力信号とをそれぞれ入力信号として、前記それぞれの入力信号が順次互いに相反するレベルになるとき前記入力信号を矩形波に波形整形してクロックとして出力するフリップフロップ回路(24)と、を備え、

前記イネーブル信号は、当該クロック出力回路に対してクロック出力の許可を外部装置が指令するための信号であり、前記イネーブル信号によって当該クロック出力回路に対してクロック出力の許可を前記外部装置が指令する際には、前記第1の論理ゲートはその出力信号として、前記第1の信号出力回路の出力信号を出力し、かつ前記第2の論理ゲートはその出力信号として、前記第2の信号出力回路の出力信号を出力するものであり、

前記第1閾値(Th1)は、前記第2閾値(Th2)よりも大きい値に設定されており、

前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなり、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とする。

【0022】

請求項6に記載の発明によれば、発振信号の周波数が高くなるほど第1閾値が大きくなるので、発振信号の振幅が小さい場合には、周波数が高くなるほど、第1の信号出力回路の出力信号がハイレベルからローレベルに変化し難くなる。これに加えて、発振信号の周波数が高くなるほど第2閾値が小さくなるので、発振信号の振幅が小さい場合には、周波数が高くなるほど、第2の信号出力回路の出力信号のレベルがローレベルからハイレベルに変化し難くなる。

【0023】

したがって、発振信号の振幅が小さく、かつ周波数が高い場合には、第1、第2の信号出力回路の出力信号が互いに相反するレベルになる。このため、イネーブル信号によって当該クロック出力回路に対してクロック出力の許可を外部装置が指令する際にも、第1、第2の論理ゲートの出力信号が互いに相反するレベルになる。これに伴い、第1、第2の論理ゲートのうち他方の論理ゲートの出力信号と第3のNOTゲートの出力信号とが同一レベルになるので、フリップフロップ回路からクロックが出力されない。

【0024】

すなわち、外部装置がクロック出力回路に対してクロック出力の許可を指令する場合においても、発振信号の振幅が小さく、かつ周波数が高い場合には、フリップフロップ回路からクロックが出力されない。このため、上述の請求項1に記載の発明と同様、発振回路においてオーバートーン発振が生じているときには、フリップフロップ回路からクロックが出力されなくなる。その後、発振回路の発振周波数が低下して予め設定された周波数に移行すると、他方の論理ゲートの出力信号と第3のNOTゲートの出力信号とが相違するレベルになるので、フリップフロップ回路がクロックを出力することができる。したがって、必要以上に長い時間、クロックの出力を待機させることはない。すなわち、クロックの出力を待機させるための発振安定時間を短くして、発振回路の電流の消費を抑えることができる。

【0025】

したがって、上記請求項1に記載の発明と同様、発振回路での無駄な電力消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することができる。

【0026】

請求項7に記載の発明では、前記第1の信号出力回路(21A)は、

電源とグランドとの間に配置される第1のpMOSトランジスタ(25a)と、

前記第1のpMOSトランジスタとグランドとの間に並列配置される複数の第1のnMOSトランジスタ(25b)とを備え、

前記第1のpMOSトランジスタ(25a)のゲート端子と前記複数の第1のnMOSトランジスタ(25b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記第1のpMOSトランジスタのドレイン端子と前記複数の第1のnMOSトランジスタのドレイン端子との間の共通接続端子が前記第1の信号出力回路の出力信号を出力する出力端子を構成し、

前記複数の第1のnMOSトランジスタ(25b)のうち隣り合う2つの第1のnMOSトランジスタ毎に前記2つの第1のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されることにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする。

【0027】

請求項8に記載の発明では、前記第1の論理ゲート(21B)は、前記電源と前記複数の第1のnMOSトランジスタ(25b)との間で前記第1のpMOSトランジスタ(25a)に対して直列配置されて前記イネーブル信号に基づいてオン、オフする第4のpMOSトランジスタ(27a)と、前記第1のpMOSトランジスタ(25a)とグランドとの間で前記複数の第1のnMOSトランジスタ(25b)に対して並列配置されて前記イネーブル信号に応じてオン、オフする第4のnMOSトランジスタ(27b)とを備えることにより、前記第1の論理ゲートが前記発振信号と前記イネーブル信号とに基づいてNOR演算するNORゲートを構成することを特徴とする。

【0028】

請求項9に記載の発明では、前記第1の論理ゲート(21C)は、前記電源と前記複数の第1のnMOSトランジスタ(25b)との間で前記第1のpMOSトランジスタ(25a)に対して並列配置されて前記イネーブル信号に基づいてオン、オフする第5のpMOSトランジスタ(28a)と、前記第1のpMOSトランジスタ(25a)とグランドとの間で前記複数の第1のnMOSトランジスタ(25b)と直列配置されて前記イネーブル信号に基づいてオン、オフする第5のnMOSトランジスタ(28b)とを備えることにより、前記第1の論理ゲートが前記発振信号と前記イネーブル信号に基づいてNAND演算してこのNAND演算するNANDゲートを構成することを特徴とする。

【0029】

請求項10に記載の発明では、前記第2の信号出力回路(22A)は、

電源とグランドとの間に並列配置される複数の第2のpMOSトランジスタ(25d)と、

前記複数の第2のpMOSトランジスタとグランドとの間に配置される第2のnMOSトランジスタ(25e)とを備え、

前記複数の第2のpMOSトランジスタ(25d)のゲート端子と第2のnMOSトランジスタ(25e)とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第2のpMOSトランジスタのドレイン端子と前記第2のnMOSトランジスタのドレイン端子との間の共通接続端子が前記第2の信号出力回路の出力信号を出力する出力端子を構成し、

前記複数の第2のpMOSトランジスタのうち隣り合う2つの第2のpMOSトランジスタ(25d)毎に前記第2のpMOSトランジスタ(25d)のゲート端子の間には第2の抵抗素子(Rp)が配置されることにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなっていることを特徴とする。

【0030】

請求項11に記載の発明では、前記第2の論理ゲート(22B)は、前記電源とグランドとの間で前記複数の第2のpMOSトランジスタ(25d)に対して直列接続されて前記イネーブル信号に応じてオン、オフする第6のpMOSトランジスタ(27d)と、前記複数の第2のpMOSトランジスタ(25d)とグランドとの間で前記第2のnMOSトランジスタ(25e)に対して並列配置されて前記イネーブル信号に応じてオン、オフする第6のnMOSトランジスタ(27e)とを備えることにより、前記第2の論理ゲート(22B)が前記発振信号と前記イネーブル信号とに基づいてNOR演算するNORゲートを構成していることを特徴とする。

【0031】

請求項12に記載の発明では、前記第2の論理ゲート(22C)は、前記電源と前記第2のnMOSトランジスタ(25e)との間で前記複数の第2のpMOSトランジスタ(25d)に対して並列配置されて前記イネーブル信号に応じてオン、オフする第7のpMOSトランジスタ(28d)と、前記複数の第2のpMOSトランジスタ(25d)とグランドとの間で前記第2のnMOSトランジスタ(25e)に対して直列接続されて前記イネーブル信号に応じてオン、オフする第7のnMOSトランジスタ(28e)とを備えることにより、前記第2の論理ゲート(22C)が前記発振信号と前記イネーブル信号とに基づいてNAND演算するNANDゲートを構成していることを特徴とする。

【0032】

請求項13に記載の発明では、前記複数の第1のnMOSトランジスタ(25b)のうち隣り合う2つの第1のnMOSトランジスタ毎にて前記隣り合う2つの第1のnMOSトランジスタのうち後段の第1のnMOSトランジスタのゲート端子とソース端子との間に第1のコンデンサ(C1)が配置されていることを特徴とする。

【0033】

請求項14に記載の発明では、前記複数の第2のpMOSトランジスタ(25d)のうち前記隣り合う2つの第2のpMOSトランジスタ毎にて前記2つの第2のpMOSトランジスタのうち後段の第2のnMOSトランジスタのゲート端子とソース端子との間に第2のコンデンサ(C2)が配置されていることを特徴とする。

【0034】

請求項15に記載の発明では、前記フリップフロップ回路から出力される前記クロックの個数をカウントするカウンタ回路(31)と、

前記カウンタ回路のカウント値が一定期間の間にて第1閾値以上になるか否かを判定する第1の判定回路(32)と、

前記一定期間の間における前記カウント値が第1閾値以上であると前記第1の判定回路が判定したときには他の装置に対して前記クロックを出力し、前記一定期間の間における前記カウント値が第1閾値未満であると前記第1の判定回路が判定したときには前記他の装置に対する前記クロックの出力を停止する出力制御回路(50)とを備えていることを特徴とする。

【0035】

請求項16に記載の発明では、前記カウンタ回路のカウント値が一定期間の間にて第2閾値未満になるか否かを判定する第2の判定回路(32)を備え、

前記一定期間の間における前記カウント値が第1閾値以上であると前記第1の判定回路が判定し、かつ前記一定期間の間における前記カウント値が第2閾値未満であると前記第2の判定回路が判定したときには前記出力制御回路(50)が前記他の装置に対して前記クロックを出力し、

前記一定期間の間における前記カウント値が第1閾値未満であると前記第1の判定回路が判定したとき、或いは記一定期間の間における前記カウント値が第2閾値以上であると前記第2の判定回路が判定したときには前記出力制御回路(50)が前記他の装置に対する前記クロックの出力を停止することを特徴とする。

【0036】

請求項17に記載の発明では、前記発振回路は、その出力信号の信号波形が正弦波状となる正弦波信号を前記発振信号として出力することを特徴とする。

【0037】

請求項18に記載の発明では、前記発振回路は、その出力信号の信号波形が周期的に二等辺三角形となる三角波信号を前記発振信号として出力することを特徴とする。

【0038】

請求項19に記載の発明では、前記発振回路は、その出力信号の信号波形がノコギリ波状となるノコギリ波信号を前記発振信号として出力することを特徴とする。

【0039】

なお、この欄および特許請求の範囲で記載した各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【図面の簡単な説明】

【0040】

【図1】本発明の第1実施形態におけるクロック出力回路の電気回路構成を示す図である。

【図2】図1のNOTゲートの回路構成の詳細を示す図である。

【図3】図1のNOTゲートの回路構成の詳細を示す図である。

【図4】図1の周波数カウンタの作動を説明するための図である。

【図5】第1実施形態における閾値の変化を説明するためのNOTゲートの回路構成を示す図である。

【図6】第1実施形態において入力スルーレートと閾値との関係を示す特性図である。

【図7】本発明の第2実施形態におけるNOTゲートの電気回路構成を示す図である。

【図8】第2実施形態におけるNOTゲートの発振信号の周波数と第1、第2閾値の関係を示す図である。

【図9】本発明の第3実施形態におけるNORゲートの電気回路構成を示す図である。

【図10】第3実施形態におけるNORゲートの電気回路構成を示す図である。

【図11】本発明の第4実施形態におけるNANDゲートの電気回路構成を示す図である。

【図12】第4実施形態におけるNANDゲートの電気回路構成を示す図である。

【図13】本発明の第5実施形態におけるNORゲートの電気回路構成を示す図である。

【図14】第5実施形態におけるNORゲートの電気回路構成を示す図である。

【図15】本発明の第5実施形態における源クロック、CR発振回路の出力信号、比較器の出力信号のタイミングチャートである。

【発明を実施するための形態】

【0041】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、説明の簡略化を図るべく、図中、同一符号を付してある。

【0042】

(第1実施形態)

図1に本発明のクロック出力回路1の第1実施形態の電気回路構成を示す。

【0043】

クロック出力回路1は、マイクロコンピュータなどの他の装置にクロック(図中CLKと記す)を出力するもので、発振回路10、フィルタ回路20、周波数カウンタ30、パワーオンリセット回路40、およびNANDゲート50を備える。

【0044】

発振回路10は、発振子11、コンデンサ12a、12b、抵抗素子13、およびNOTゲート14から構成されて、発振子11の発振に基づいて発振信号を出力する周知の回路である。

【0045】

本実施形態の発振信号としては、信号波形が正弦波状となる正弦波信号が用いられている。発振子11としては、水晶発振子などを用いることができる。

【0046】

フィルタ回路20は、後述するように、発振回路10から出力される発振信号のうち、発振回路10の起動時における高い周波数で振幅が小さい発振信号を除去するもので、NOTゲート21A、22A、23、およびRSフリップフロップ24から構成されている。

【0047】

NOTゲート21Aは、発振信号の信号レベルが第1閾値Th1以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第1閾値Th1未満のときハイレベルの出力信号を出力する第1のNOTゲートである。なお、NOTゲート21Aの具体的な回路構成は後述する。

【0048】

NOTゲート22Aは、発振信号の信号レベルが第2閾値Th2以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第2閾値Th2未満のときハイレベルの出力信号を出力する第2のNOTゲートである。なお、NOTゲート22Aの具体的な回路構成は後述する。

【0049】

NOTゲート23は、NOTゲート21Aの出力信号のレベルがハイレベルのとき出力信号がローレベルになり、NOTゲート21Aの出力信号のレベルがローレベルのとき出力信号がハイレベルになるものである。

【0050】

RSフリップフロップ回路24は、NOTゲート22Aの出力信号をセット入力(入力信号)とし、NOTゲート23の出力信号をリセット入力(入力信号)として、セット入力およびリセット入力に応じてクロックを出力する周知のRSフリップフロップである。

【0051】

なお、RSフリップフロップ回路24から出力されるクロックとクロック出力回路1からマイクロコンピュータに与えられるクロックCLKとを区別するために、RSフリップフロップ回路24から出力されるクロックを便宜上、源クロックともいう。

【0052】

具体的には、RSフリップフロップ回路24は、NANDゲート24a、24b、およびNOTゲート24cから構成されている。

【0053】

NANDゲート24aは、NANDゲート24bの出力信号とNOTゲート23の出力信号とに基づいてNAND演算を行う。NANDゲート24bは、NANDゲート24aの出力信号とNOTゲート22Aの出力信号とに基づいてNAND演算を行う。NOTゲート24cは、NANDゲート24aの出力信号のNOT演算を行う。

【0054】

周波数カウンタ30は、RSフリップフロップ回路24から出力される源クロックの周波数をカウントして、このカウントした源クロックの周波数が一定周波数以上であるか否かを判定するためのもので、カウンタ回路31、比較回路(図中コンペアと記す)32、およびCR発振回路33から構成されている。

【0055】

カウンタ回路31は、RSフリップフロップ回路24から出力される源クロックの個数を数えるカウンタである。比較回路32は、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達するか否かを判定する。CR発振回路33は、コンデンサおよび抵抗素子を用いて帰還回路を構成して発振を生じさせる周知の回路である。

【0056】

パワーオンリセット回路40は、電源から出力される電源電圧に応じてハイレベル信号を出力する。

【0057】

NANDゲート50は、パワーオンリセット回路40の出力信号、比較回路32の出力信号、およびRSフリップフロップ回路24の出力信号(源クロック)を用いてNAND演算を行う。

【0058】

次に、本実施形態のNOTゲート21Aの回路構成について図2(a)、(b)を参照して説明する。

【0059】

図2(a)にNOTゲート21Aの回路構成を示す。図2(b)にNOTゲート21Aの第1閾値Th1と発振信号の周波数との関係を示す。

【0060】

NOTゲート21Aは、1つのpMOSトランジスタ25aおよびM個のnMOSトランジスタ25bを備える。Mは2以上の整数である。

【0061】

pMOSトランジスタ25aは、電源とグランドとの間に配置されている第1のpMOSトランジスタである。M個のnMOSトランジスタ25bは、pMOSトランジスタ25aのドレイン端子とグランドとの間に並列に配置されている。nMOSトランジスタ25bは、特許請求の範囲に記載の第1のnMOSトランジスタに対応している

pMOSトランジスタ25aのゲート端子とM個のnMOSトランジスタ25bのゲート端子とが接続されて、発振回路10の出力信号が与えられる入力端子25gを構成している。

【0062】

pMOSトランジスタ25aのドレイン端子とM個のnMOSトランジスタ25bのドレイン端子とが接続されて、NOTゲート21A自体の出力信号を出力する出力端子25cを構成している。

【0063】

M個のnMOSトランジスタ25bにおいて隣り合う2つのnMOSトランジスタ25b毎に、2つのnMOSトランジスタ25bのうち前段のnMOSトランジスタ25bのゲート端子と後段のnMOSトランジスタ25bのゲート端子との間に配置される抵抗素子(第1の抵抗素子)Rnが設けられている。

【0064】

つまり、M個のnMOSトランジスタ25bのうち最後段のnMOSトランジスタ25bと入力端子25gとの間には、(M−1)個の抵抗素子Rnが直列に接続されている。

【0065】

ここで、最後段のnMOSトランジスタ25bは、M個のnMOSトランジスタ25bのうち入力端子25gから最も離れた箇所に位置するnMOSトランジスタ25bである。

【0066】

(M−1)個の抵抗素子Rnにおいて隣接する2つの抵抗素子Rn毎にこの2つの抵抗素子Rnの間の共通接続端子とnMOSトランジスタ25bのゲート端子とが接続されている。(M−1)個の抵抗素子Rnは、M個のnMOSトランジスタ25bのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第1の遅延回路を構成している。

【0067】

このように構成されるNOTゲート21Aでは、発振信号の周波数が高くなるほど、第1の閾値Th1が大きくなる(図2(b)参照)。第1の閾値Th1は、NOTゲート21Aの出力信号のレベルVoをハイレベルからローレベルに変化させる入力信号のレベルViである。

【0068】

なお、図2(b)中の縦軸は、NOTゲート21Aの出力信号(電圧レベル)Voとし、横軸は、NOTゲート21Aの入力信号(すなわち、発振信号)Viし、VDDが電源電圧である。

【0069】

次に、本実施形態のNOTゲート22Aの回路構成について説明する。

【0070】

図3(a)にNOTゲート22Aの回路構成を示す。図3(b)にNOTゲート22Aの第2閾値Th2と発振信号の周波数との関係を示す。

【0071】

NOTゲート22Aは、M個のpMOSトランジスタ25d、および1つのnMOSトランジスタ25eを備えている。

【0072】

M個のpMOSトランジスタ25dは、電源とグランドとの間に配置されている。nMOSトランジスタ25eは、M個のpMOSトランジスタ25dとグランドとの間に直列に配置されている。

【0073】

M個のpMOSトランジスタ25dのゲート端子とnMOSトランジスタ25eのゲート端子とが接続されて、発振回路10の出力信号が与えられる入力端子25hを構成している。

【0074】

M個のpMOSトランジスタ25dのドレイン端子とnMOSトランジスタ25eのドレイン端子とが接続されて、NOTゲート22A自体の出力信号を出力する出力端子25fを構成している。

【0075】

M個のpMOSトランジスタ25dにおいて隣り合う2つのpMOSトランジスタ25d毎に、2つのpMOSトランジスタ25dのうち前段のpMOSトランジスタ25dのゲート端子と後段のpMOSトランジスタ25dのゲート端子との間に配置される抵抗素子Rpが設けられている。

【0076】

つまり、M個のpMOSトランジスタ25bのうち最後段のpMOSトランジスタ25dと入力端子25hとの間には、(M−1)個の抵抗素子Rpが直列に接続されている。

【0077】

ここで、最後段のpMOSトランジスタ25dは、M個のpMOSトランジスタ25dのうち入力端子25hから最も離れた箇所に位置するpMOSトランジスタ25dである。

【0078】

(M−1)個の抵抗素子Rpにおいて隣接する2つの抵抗素子Rp毎に2つの抵抗素子Rpの間の共通接続端子とpMOSトランジスタ25dのゲート端子とが接続されている。(M−1)個の抵抗素子Rpは、M個のpMOSトランジスタ25dのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第2の遅延回路を構成している。

【0079】

第2の遅延回路では、発振信号の周波数が高くなるほど、(M−1)個のpMOSトランジスタ25dのゲート電圧が低下するのに生じる遅延時間が長くなる。

【0080】

このように構成されるNOTゲート22Aでは、発振信号の周波数が高くなるほど、第2の閾値Th2が小さくなる(図3(b)参照)。第2の閾値Th2は、出力信号のレベルVoをハイレベルからローレベルに変化させる入力信号のレベルViである。

【0081】

なお、図3(b)中の縦軸はNOTゲート22Aの出力レベルVoとし、横軸はNOTゲート22Aの入力レベル(すなわち、発振信号)Viし、VDDが電源電圧である。

【0082】

本実施形態の図2のNOTゲート21Aの閾値Th1は、図3のNOTゲート22Aの閾値Th2に比べて大きな値に設定されている。

【0083】

ここで、図2のNOTゲート21Aの第1の閾値Th1は、M個のnMOSトランジスタ25bのトランジスタサイズの合計とpMOSトランジスタ25aのトランジスタサイズとの比率によって設定される。図3のNOTゲート22Aの第2の閾値Th2は、M個のpMOSトランジスタ25dのトランジスタサイズの合計とnMOSトランジスタ25eのトランジスタサイズとの比率によって設定される。

【0084】

なお、図3のpMOSトランジスタ25dが特許請求の範囲に記載の第2のpMOSトランジスタに対応し、図3のnMOSトランジスタ25eが特許請求の範囲に記載の第2のnMOSトランジスタに対応し、図3の抵抗素子Rpが特許請求の範囲に記載の第2の抵抗素子に対応する。

【0085】

次に、本実施形態のクロック出力回路1の作動の説明に先立って、RSフリップフロップ24の作動について説明する。

【0086】

まず、図1のNOTゲート23、22Aの出力レベルがローレベルになると、NOTゲート24a、24bの出力レベルがローレベルになる。このため、NOTゲート24cの出力レベルがハイレベルになる。

【0087】

次に、NOTゲート23の出力レベルがローレベルで、NOTゲート22Aの出力レベルがハイレベルになると、NOTゲート24aの出力レベルがハイレベルになり、NOTゲート24bの出力レベルがローレベルになる。

【0088】

次に、NOTゲート23の出力レベルがハイレベルで、NOTゲート22Aの出力レベルがローレベルになると、NOTゲート24aの出力レベルがローレベルになり、NOTゲート24bの出力レベルがハイレベルになる。

【0089】

また、NOTゲート23、22Aの出力レベルがハイレベルになると、NOTゲート24a、24bの出力レベルが変化しない。このため、NOTゲート24cの出力レベルが変化しない。

【0090】

このように、NOTゲート23、22Aの出力レベルが互いに相違するレベルであるときには、NOTゲート24aの出力レベルが、NOTゲート23の出力レベルと相違する出力レベルになる。このため、NOTゲート23、22Aの出力レベルが互いに相違するレベルであるときには、NOTゲート24cの出力レベルは、NOTゲート23の出力レベルと同一の出力レベルとなる。このことにより、RSフリップフロップ24は発振信号の波形を矩形波に整形する役割を果たすことになる。

【0091】

次に、本実施形態のクロック出力回路1の作動について説明する。

【0092】

まず、電源が投入されて発振回路10が起動してオーバートーン発振が生じる場合がある。この場合、発振信号の周波数が予め設定された周波数よりも高くなり、かつ、発振信号の振幅が予め設定された振幅よりも小さくなる。

【0093】

ここで、発振信号の周波数が高い場合には、NOTゲート21Aの第1の閾値Th1が高くなり、NOTゲート22Aの第2の閾値Th2が低くなる。したがって、第1、第2の閾値Th1、Th2が互いに離れることになる。

【0094】

このため、発振信号の振幅が小さい場合には、発振信号の信号レベルが、一周期に亘って、第2の閾値Th2よりも大きく、かつ第1の閾値Th1未満となる場合が生じる。

【0095】

このため、発振信号の一周期に亘って、NOTゲート22Aの出力レベルがローレベルになり、NOTゲート21Aの出力レベルがハイレベルになる。このため、NOTゲート23の出力レベルがローレベルになる。つまり、NOTゲート23、22Aの出力レベルがそれぞれローレベルになるので、NOTゲート24cの出力レベルがハイレベルになる。このとき、RSフリップフロップ24が発振信号の波形を矩形波に整形する役割を停止することになる。

【0096】

その後、発振子11の発振の安定化が進んで、振幅が大きくなり、かつ周波数が低下する。このとき、発振信号の周波数の低下に伴って、NOTゲート21Aの第1の閾値Th1が低下して、NOTゲート22Aの第2の閾値Th2が高くなるので、第1、第2の閾値Th1が互いに近づくことになる。

【0097】

このため、発振信号の信号レベルの変化に伴って、NOTゲート21A、22Aの出力信号のレベルが変化する。

【0098】

具体的には、第1、第2の閾値Th1、Th2よりも発振信号の信号レベルが高いときには、NOTゲート21A、22Aの出力信号がそれぞれローレベルになる。このため、NOTゲート23の出力信号がハイレベルになる。このとき、NOTゲート24cの出力信号がローレベルになる。

【0099】

その後、発振信号の信号レベルが第1、第2の閾値Th1、Th2の間に位置するときには、NOTゲート21Aの出力信号がハイレベルで、NOTゲート22Aの信号レベルがローレベルになる。このため、NOTゲート23の出力信号がローレベルになる。このとき、NOTゲート24cの出力信号がハイレベルになる。

【0100】

次に、第1、第2の閾値Th1、Th2よりも発振信号の信号レベルが低くなると、NOTゲート21A、22Aの出力信号がそれぞれハイレベルになる。このため、NOTゲート23の出力信号がローレベルになる。このとき、NOTゲート24cの出力信号がハイレベルになる。

【0101】

このように発振信号の信号レベルが変化すると、NOTゲート24cの出力信号がローレベル→ハイレベル→ローレベル→ハイレベル・・・のように順次切り替わる。

【0102】

以上により、RSフリップフロップ24は、発振信号の波形を矩形波に整形して、この波形整形した信号を源クロック(図4(a)参照)としてNANDゲート50およびカウンタ回路31に出力する。

【0103】

ここで、発振子11の発振の安定化が進んで、源クロックの周波数(すなわち、発振信号の周波数)が低下したものの、源クロックの周波数が所定周波数に到達していないときには、次のように、図1のパワーオンリセット回路40の出力信号、および比較回路32の出力信号に応じてNANDゲート50がクロックCLKの出力をマスクする。

【0104】

具体的には、パワーオンリセット回路40は、電源が投入されて電源電圧が一定値以上になると、ハイレベル信号をNANDゲート50に出力する。CR発振回路33は発振して周期的に出力信号のレベルが変化する発振信号を出力信号としてカウンタ回路31に出力する(図4(b)参照)。図4(b)では、CR発振回路33の出力信号が一周期毎にローレベルからハイレベルに変化する例を示している。

【0105】

カウンタ回路31は、RSフリップフロップ24から出力される源クロックの数をカウントしてそのカウント値を比較回路32に出力する。比較回路32は、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達したか否かを判定する。すなわち、比較回路32は、一定期間の間において、カウンタ回路31のカウント値が第1の閾値nに到達したか否かを判定する。図4では、CR発振回路33の出力信号の立ち上がりタイミングt1、t2の間において、カウンタ回路31のカウント値が第1の閾値nに到達したか否かを判定する例を示している。

【0106】

源クロックの周波数が所定周波数に到達していないときには、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達していないと比較回路32が判定する。このとき、比較回路32がローレベル信号をNANDゲート50に出力する。このため、パワーオンリセット回路40がハイレベル信号をNANDゲート50に出力していても、NANDゲート50の出力信号はハイレベルを維持する。すなわち、NANDゲート50がクロックCLKの出力をマスクする。

【0107】

その後、発振回路10の発振子11の発振の安定化が進んで、源クロックの周波数が所定周波数に到達すると、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達したと比較回路32が判定する。このとき、比較回路32がハイレベル信号をNANDゲート50に出力する。このため、NANDゲート50の出力信号は、NOTゲート24cの出力信号のレベルの変化に伴って順次変化する。すなわち、NANDゲート50がクロックCLKの出力を開始する。

【0108】

以上説明した本実施形態によれば、発振信号を出力する発振回路10と、発振信号の信号レベルが第1の閾値Th1以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第1の閾値Th1未満のときハイレベルの出力信号を出力するNOTゲート21Aと、発振信号の信号レベルが第2の閾値Th2以上のときローレベルの出力信号を出力し、発振信号の信号レベルが第2の閾値未満のときハイレベルの出力信号を出力するNOTゲート22Aと、NOTゲート21Aの出力信号のレベルと相反するレベルの出力信号を出力するNOTゲート23と、NOTゲート22A、23をそれぞれ入力信号として、それぞれの入力信号が順次互いに相反するレベルになるとき入力信号を矩形波に波形整形してクロックとして出力するRSフリップフロップ回路24とを備える。第1の閾値Th1は、第2の閾値Th2よりも大きい値に設定されており、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなることを特徴とする。

【0109】

したがって、発振信号の振幅が小さい場合において発振信号の周波数が高いときには、第1の閾値Th1が大きくなるので、NOTゲート21Aの出力信号のレベルがハイレベルからローレベルに変化しなくなる。これに加えて、振幅が小さい場合には、発振信号の周波数が高いときには、第2の閾値Th2が小さくなるので、NOTゲート22Aの出力信号のレベルがローレベルからハイレベルに変化しなくなる。

【0110】

以上により、振幅が小さく、かつ発振信号の周波数が高いときには、NOTゲート21Aの出力信号のレベルがハイレベルで、かつNOTゲート22Aの出力信号のレベルがローレベルとなる。このため、NOTゲート23、22Aの出力信号が互いに同一レベルになるので、RSフリップフロップ回路24から源クロックが出力されなくなる。すなわち、発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24から源クロックが出力されることが待機される。その後、発振子11の発振が安定化して、発振信号の振幅が大きくなり、かつ周波数が低くなるとRSフリップフロップ回路24が源クロックの出力を開始する。すなわち、オーバートーン発振が終わると、RSフリップフロップ回路24が源クロックの出力を開始することになる。

【0111】

以上により、必要以上に長い時間、源クロックの出力を待機されることを避けることができる。このため、クロックの出力を待機させる発振安定時間を短くすることができる。したがって、発振回路10の電流の消費を抑えつつ、周波数が安定したクロックを出力するようにしたクロック出力回路を提供することができる。

【0112】

本実施形態では、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達していないときには、比較回路32は、源クロックの周波数が所定周波数に到達していないと判定して、ローレベル信号をNANDゲート50に出力する。このため、NANDゲート50がクロックCLKの出力をマスクする。これにより、周波数が安定していないクロックCLKを出力することを未然に避けることができる。

【0113】

次に、本実施形態のNOTゲート22Aの第2閾値Th2と発振信号の周波数との関係を調べるためのシミュレーションの結果について図5、図6を用いて説明する。

【0114】

本シミュレーションでは、発振信号のスルーレート(入力スルーレート)と図5のNOTゲート22Aの第2閾値Th2との関係を調べたものである。

スルーレートとは、立ち上がりタイミング(或いは立ち下がりタイミング)において、単位時間あたりの発振信号の信号レベルの変化量を示すものである。

【0115】

図5のNOTゲート22Aは、1つのnMOSトランジスタ25e、1つの抵抗素子Rp、および2つのpMOSトランジスタ25dから構成されている。

【0116】

図6は縦軸をNOTゲート22Aの第2の閾値Th2とし、横軸を発振信号のスルーレート(図中入力スルーレートと記す)とし、抵抗素子Rpの抵抗値をパラメータとして第2の閾値Th2と発振信号のスルーレートとの関係を示す特性図である。

【0117】

ここで、図6中の符号G1は抵抗素子Rpの抵抗値を1kΩとしたときのグラフであり、図6中の符号G2は抵抗素子Rpの抵抗値を100kΩとしたときのグラフであり、図6中の符号G3は抵抗素子Rpの抵抗値を1MΩとしたときのグラフである。

【0118】

図6中の符号G1、G2、G3から分かるように、発振信号のスルーレート(入力スルーレート)の上昇に伴って第2の閾値Th2が下がることがこと分かる。

ここで、一般的に、発振信号の周波数が高くなるほど、発振信号のスルーレートが大きくなる。このため、本シミュレーションの結果から、発振信号の周波数が高くなるほど、NOTゲート22Aの第2の閾値Th2が下がることが分かる。

【0119】

このような発振信号の周波数の上昇に伴う第2の閾値Th2の低下は、NOTゲート22Aの寄生抵抗や寄生容量で生じるものではない。

【0120】

上述の第1実施形態では、発振回路10から出力される発振信号としては、信号波形が正弦波状となる正弦波信号を用いた例について説明したが、これに代えて、出力信号の波形が周期的に二等辺三角形となる三角波信号を発振信号として用いてもよい。

【0121】

また、これに限らず、発振回路10から出力される発振信号としては、信号波形がノコギリ歯状となるノコギリ波信号(すなわち、出力信号の波形が周期的に直角三角形状になるノコギリ波信号)を用いてもよい。

【0122】

以下、発振信号の周波数とRSフリップフロップ24の出力との関係についてシミュレーションで調べた結果について説明する。

【0123】

(1)発振信号として三角波信号を用いて、発振信号の振幅を徐々に大きくした場合において、発振信号の周波数を4MHzとしたときには、発振信号の振幅が3.98V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0124】

一方、発振信号の周波数を10MHzとした場合には、発振信号の振幅が4.20V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0125】

以上により、発振信号の周波数が高くなるほど、RSフリップフロップ24が源クロックの出力を開始する発振信号の振幅(論理閾値)が大きくなる。このことから、NOTゲート21Aの第1閾値Th1、およびNOTゲート22Aの第2閾値Th2が周波数によって変化していることが分かる。

【0126】

(2)発振信号をノコギリ波信号としたときに、発振信号の周波数を4MHz、10MHzとして、上記(1)と同様のシミュレーションを実施したところ、発振信号の周波数を4MHzとしたときには、発振信号の振幅が3.89V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0127】

一方、発振信号の周波数を10MHzとした場合には、発振信号の振幅が4.20V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0128】

このことにより、発振信号の周波数が高い場合には、RSフリップフロップ24が源クロックの出力を開始する発振信号の振幅(論理閾値)が大きくなることが分かる。

【0129】

(第2実施形態)

上述の第1実施形態では、1つのnMOSトランジスタ25aおよびM個のnMOSトランジスタ25bからNOTゲート21A(図2参照)を構成し、M個のpMOSトランジスタ25dと1つのnMOSトランジスタ25eからNOTゲート22A(図3参照)を構成する例について説明したが、これに代えて、本実施形態では、M個のpMOSトランジスタ25dおよびM個のnMOSトランジスタ25bからNOTゲート21A(22A)を構成する例について説明する。

【0130】

図7に本実施形態のNOTゲート21A(22A)の回路構成を示す。本実施形態のNOTゲート21A、22Aは、後述する抵抗素子Rp、Rnの値が異なるだけで、同様な構成になっている。

【0131】

NOTゲート21A、22Aは、図3のM個のpMOSトランジスタ25dおよび(M−1)個の抵抗素子Rpと、図2のM個のnMOSトランジスタ25bおよび(M−1)個の抵抗素子Rnとを組み合わせたものである。

【0132】

本実施形態のpMOSトランジスタ25dの個数とnMOSトランジスタ25bの個数とは同一個数で、抵抗素子Rpの個数と抵抗素子Rnの個数とは同一個数である。

【0133】

ここで、NOTゲート21A(22A)は、図2のNOTゲート21Aと同様、M個のnMOSトランジスタ25bのうち最後段のnMOSトランジスタ25bと入力端子25gとの間には、(M−1)個の抵抗素子Rnが直列に接続されている。

【0134】

(M−1)個の抵抗素子Rnは、M個のnMOSトランジスタ25bのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第1の遅延回路を構成している。

【0135】

第1の遅延回路では、発振信号の周波数が高くなるほど、(M−1)個のnMOSトランジスタ25bのゲート電圧が上昇するのに生じる遅延時間が長くなる。

【0136】

本実施形態のNOTゲート21A(22A)は、図3のNOTゲート22Aと同様、M個のpMOSトランジスタ25dのうち最後段のpMOSトランジスタ25dと入力端子25hとの間には、(M−1)個の抵抗素子Rpが直列に接続されている。

【0137】

(M−1)個の抵抗素子Rpは、M個のpMOSトランジスタ25dのそれぞれのゲート端子とソース端子との間の静電容量、および、ゲート端子とドレイン端子との間の静電容量とともに、第2の遅延回路を構成している。

【0138】

第2の遅延回路では、発振信号の周波数が高くなるほど、(M−1)個のpMOSトランジスタ25dのゲート電圧が低下するのに生じる遅延時間が長くなる。

【0139】

本実施形態のNOTゲート21Aでは、抵抗素子Rnの抵抗値を抵抗素子Rpの抵抗値に比べて極めて大きい値に設定している(抵抗素子Rn≫抵抗素子Rp)。このため、第1の遅延回路の遅延時間を第2の遅延回路の遅延時間に比べて長い時間に設定することができる。これにより、図2のNOTゲート21Aと同様に、発振信号の周波数が高くなるほど第1の閾値Th1を大きくすることができる(図8(a)参照)。

【0140】

本実施形態のNOTゲート22Aでは、抵抗素子Rnの抵抗値を抵抗素子Rpの抵抗値に比べて極めて小さい値に設定している(抵抗素子Rn≪抵抗素子Rp)。このため、第2の遅延回路の遅延時間を第1の遅延回路の遅延時間に比べて長い時間に設定することができる。これにより、図3のNOTゲート22Aと同様に、発振信号の周波数が高くなるほど第2の閾値Th2を小さくすることができる(図8(b)参照)。

【0141】

なお、図7のpMOSトランジスタ25dが特許請求の範囲に記載の第3のpMOSトランジスタに対応し、図7のnMOSトランジスタ25bが特許請求の範囲に記載の第3のnMOSトランジスタに対応し、図7の抵抗素子Rnが特許請求の範囲に記載の第1の抵抗素子に対応し、図7の抵抗素子Rpが特許請求の範囲に記載の第2の抵抗素子に対応する。

【0142】

(第3実施形態)

上述の第1実施形態では、NOTゲート21A、22Aを用いてフィルタ回路20を構成した例について説明したが、これに限らず、本実施形態では、NORゲート21B、22Bを用いてフィルタ回路20を構成する例について説明する。

【0143】

図9に本実施形態のNORゲート21Bの回路構成を示す。

【0144】

NORゲート21Bは、図2のNOTゲート21Aに代えて用いられるものである。NORゲート21Bは、発振信号とイネーブル信号とに基づいてNOR演算する第1の論理ゲートであって、図2のNOTゲート21Aに対してpMOSトランジスタ27a、およびnMOSトランジスタ27bを追加したものである。

【0145】

ここで、イネーブル信号は、電子制御回路(外部装置)がクロック出力回路1に対してクロックCLKの出力の許可、或いは不許可を指令する信号である。

【0146】

pMOSトランジスタ27aは、nMOSトランジスタ25aとM個のnMOSトランジスタ25bとの間に配置されている。nMOSトランジスタ27bは、pMOSトランジスタ27aとグランドとの間でM個のnMOSトランジスタ25bに並列に配置されている。

【0147】

pMOSトランジスタ27aのゲート端子とnMOSトランジスタ27bのゲート端子とが接続されて、イネーブル信号が入力される入力端子27cを構成している。

【0148】

pMOSトランジスタ27aのドレイン端子、M個のnMOSトランジスタ25bのドレイン端子、およびnMOSトランジスタ27bのドレイン端子が接続されて、出力端子25cを構成している。出力端子25cは、NORゲート21B自体の信号を出力するものである。

【0149】

図10に本実施形態のNORゲート22Bの回路構成を示す。NORゲート22Bは、図3のNOTゲート22Aに代えて用いられるものである。NORゲート22Bは、発振信号とイネーブル信号とによってNOR演算する第2の演算ゲートであって、図3のNOTゲート22Aに対してpMOSトランジスタ27dおよびnMOSトランジスタ27eを追加したものである。

【0150】

pMOSトランジスタ27dは、M個のpMOSトランジスタ25dとnMOSトランジスタ25eとの間に配置されている。nMOSトランジスタ27eは、pMOSトランジスタ27dとグランドとの間で、nMOSトランジスタ25eと並列に接続されている。

【0151】

pMOSトランジスタ27dのゲート端子とnMOSトランジスタ27eのゲート端子とが接続されて、イネーブル信号が入力される入力端子27gを構成している。

【0152】

pMOSトランジスタ27dのドレイン端子とnMOSトランジスタ25e、27eのドレイン端子とが接続されて、出力端子25fを構成している。出力端子25fは、NORゲート21B自体の出力信号を出力するものである。

【0153】

次に、本実施形態のNORゲート21B、22Bの作動について説明する。

【0154】

まず、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可しないときには、イネーブル信号としてのハイレベル信号を図9のNORゲート21Bの入力端子27cに出力する。

【0155】

このとき、pMOSトランジスタ27aはオフする一方、nMOSトランジスタ27bはオンする。このため、NORゲート21Bの入力端子25gに発振信号が発振回路10から与えられても、NORゲート21Bの出力端子25cから出力される出力信号は、ローレベルを維持する。

【0156】

これに加えて、電子制御回路は、イネーブル信号としてのハイレベル信号を図10のNORゲート22Bの入力端子27gに出力する。

【0157】

このとき、pMOSトランジスタ27dはオフする一方、nMOSトランジスタ27eはオンする。このため、NORゲート22Bの入力端子25hに発振信号が発振回路10から与えられても、NORゲート22Bの出力端子25fから出力される出力信号は、ローレベルを維持する。

【0158】

このように、電子制御回路がNORゲート21Bの入力端子27cおよびNORゲート22Bの入力端子27gに対してイネーブル信号としてのハイレベル信号を出力する際には、NORゲート21B、22Bの出力信号は、ローレベルを維持する。このため、フィルタ回路20から源クロックが出力されなくなる。これに伴い、NANDゲート50からクロックが出力されなくなる。

【0159】

次に、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可するときには、イネーブル信号としてのローレベル信号を図9のNORゲート21Bの入力端子27cに出力する。このとき、pMOSトランジスタ27aはオンする一方、nMOSトランジスタ27bはオフする。このため、NORゲート21Bは、その出力信号として、NOTゲート21Aの出力信号を出力する。

【0160】

これに加えて、電子制御回路は、クロック出力回路1に対してイネーブル信号としてのローレベル信号をNORゲート22Bの入力端子27gに出力する。このとき、pMOSトランジスタ27dはオンする一方、nMOSトランジスタ27eはオフする。このため、NORゲート22Bは、その出力信号として、NOTゲート22Aの出力信号を出力する。

【0161】

このように、電子制御回路がNORゲート21Bの入力端子27cおよびNORゲート22Bの入力端子27gに対してイネーブル信号としてのローレベル信号を出力する際には、NORゲート21Bは、その出力信号として、NOTゲート21Aの出力信号を出力し、かつNORゲート22Bは、その出力信号として、NOTゲート22Aの出力信号を出力する。このため、電子制御回路がイネーブル信号としてのローレベル信号を出力する際には、上述第1実施形態と同様に、フィルタ回路20が源クロックを出力する。これに伴い、上述第1実施形態と同様に、NANDゲート50がクロックを出力する。

【0162】

以上説明した本実施形態によれば、電子制御回路は、クロックCLKの出力の許可するときには、イネーブル信号としてのローレベル信号をNORゲート21B(22B)の入力端子27c(27g)に出力する。これに伴い、NORゲート21Bは、その出力信号として、NOTゲート21Aの出力信号を出力し、NORゲート22Bは、その出力信号として、NOTゲート22Aの出力信号を出力する。したがって、NOTゲート21A(22A)に代えてNORゲート21B(22B)を用いてフィルタ回路20を構成することができる。

【0163】

なお、図9のNOTゲート21Aが特許請求の範囲に記載の第1の信号出力回路に対応し、図10のNOTゲート22Aが特許請求の範囲に記載の第2の信号出力回路に対応する。

(第4実施形態)

上述の第1実施形態では、NOTゲート21A(22A)を用いてフィルタ回路20を構成した例について説明したが、これに限らず、本実施形態では、NANDゲート21C(22C)を用いてフィルタ回路20を構成する例について説明する。

【0164】

本実施形態のNANDゲート21Cは、図2のNOTゲート21Aに代えて用いられるものであって、発振信号とイネーブル信号とに基づいてNAND演算する第1の論理ゲートである。

【0165】

図11に本実施形態のNANDゲート21Cの回路構成を示す。

【0166】

NANDゲート21Cは、図2のNOTゲート21Aに対してpMOSトランジスタ28aおよびnMOSトランジスタ28bを追加したものである。

【0167】

pMOSトランジスタ28aは、電源とM個のnMOSトランジスタ25bとの間にpMOSトランジスタ25aと並列に配置されている。nMOSトランジスタ28bは、pMOSトランジスタ25a、28aとM個のnMOSトランジスタ25bとの間に配置されている。

【0168】

pMOSトランジスタ28aのゲート端子とnMOSトランジスタ28bのゲート端子とが接続されて、イネーブル信号が入力される入力端子28cを構成している。

【0169】

pMOSトランジスタ25a、28aのドレイン端子およびnMOSトランジスタ28bのドレイン端子が接続されて、出力端子25cを構成している。出力端子25cは、NANDゲート21C自体の出力信号を出力するものである。

【0170】

また、本実施形態のNORゲート22Cは、図3のNOTゲート22Aに代えて用いられるものであって、発振信号とイネーブル信号とに基づいてNAND演算する。

【0171】

図12に本実施形態のNORゲート22Cの回路構成を示す。

【0172】

NANDゲート22Cは、発振信号とイネーブル信号とによってNAND演算する第2の論理ゲートである。NANDゲート22Cは、図3のNOTゲート22Aに対してpMOSトランジスタ28dおよびnMOSトランジスタ28eを追加したものである。

【0173】

pMOSトランジスタ28dは、電源とnMOSトランジスタ25eとの間でM個のpMOSトランジスタ25dと並列に配置されている。nMOSトランジスタ28eは、M個のpMOSトランジスタ25dおよびpMOSトランジスタ28dとnMOSトランジスタ25eとの間に配置されている。

【0174】

pMOSトランジスタ28dのゲート端子とnMOSトランジスタ28eのゲート端子とが接続されて、イネーブル信号が入力される入力端子28fを構成している。

【0175】

M個のpMOSトランジスタ25dのドレイン端子、pMOSトランジスタ28dのドレイン端子、およびnMOSトランジスタ28eのドレイン端子が接続されて、出力端子25fを構成している。出力端子25fは、NORゲート22C自体の出力信号を出力するものである。

【0176】

次に、本実施形態のNANDゲート21C、22Cの作動について説明する。

【0177】

まず、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可しないときには、イネーブル信号としてのローレベル信号を図11のNANDゲート21Bの入力端子28cに出力する。

【0178】

このとき、pMOSトランジスタ28aがオンして、nMOSトランジスタ28bがオフする。このため、図11のNANDゲート21Cの入力端子25gに発振信号が発振回路10から与えられても、NANDゲート21Cの出力端子25cから出力される出力信号は、ハイレベルを維持する。

【0179】

これに加えて、電子制御回路がイネーブル信号としてのローレベル信号を図12のNANDゲート22Cの入力端子28fに出力する。

【0180】

このとき、pMOSトランジスタ28dがオンして、nMOSトランジスタ28eがオフする。このため、NANDゲート22Bの入力端子25hに発振信号が発振回路10から与えられても、図12のNANDゲート22Bの出力端子25fから出力される出力信号は、ハイレベルを維持する。

【0181】

このように、電子制御回路がNANDゲート21Cの入力端子28cおよびNANDゲート22Cの入力端子28fに対してイネーブル信号としてのローレベル信号を出力する際には、NANDゲート21C、22Cの出力信号は、ハイレベルを維持する。このため、フィルタ回路20から源クロックが出力されなくなる。これに伴い、NANDゲート50からクロックが出力されなくなる。

【0182】

次に、電子制御回路がクロック出力回路1に対してクロックCLKの出力の許可するときには、イネーブル信号としてのハイレベル信号を図11のNANDゲート21Cの入力端子28cに出力する。このとき、pMOSトランジスタ28aがオフして、nMOSトランジスタ28bがオンする。このため、NANDゲート21Cは、その出力信号として、NOTゲート21Aの出力信号を出力する。

【0183】

これに加えて、電子制御回路は、イネーブル信号としてのハイレベル信号を図12のNANDゲート22Cの入力端子28fに出力する。このとき、pMOSトランジスタ28dがオフして、nMOSトランジスタ28eがオンする。このため、NANDゲート22Cは、その出力信号として、NOTゲート22Aの出力信号を出力する。

【0184】

このように、電子制御回路がNANDゲート21Cの入力端子28cおよびNANDゲート22Cの入力端子28fに対してイネーブル信号としてのハイレベル信号を出力する際には、NANDゲート21Cは、その出力信号として、NOTゲート21Aの出力信号を出力し、かつNANDゲート22Cは、その出力信号として、NOTゲート22Aの出力信号を出力する。このため、電子制御回路がイネーブル信号としてのハイレベル信号を出力する際には、上述第1実施形態と同様に、フィルタ回路20が源クロックを出力する。これに伴い、上述第1実施形態と同様に、NANDゲート50がクロックを出力する。

【0185】

以上説明した本実施形態によれば、電子制御回路は、クロックCLKの出力の許可するときには、イネーブル信号としてのハイレベル信号をNANDゲート21C(22C)の入力端子28c(28f)に出力する。これに伴い、NANDゲート21Cは、その出力信号としてNOTゲート21Aの出力信号を出力し、NANDゲート22Cは、その出力信号として、NOTゲート22Aの出力信号を出力する。したがって、NORゲート21A(22A)に代えてNAND21C(22C)を用いてフィルタ回路20を構成することができる。

【0186】

なお、図11のNOTゲート21Aが特許請求の範囲に記載の第1の信号出力回路に対応し、図12のNOTゲート22Aが特許請求の範囲に記載の第2の信号出力回路に対応する。

【0187】

(第5実施形態)

上述の第1実施形態では、NOTゲート21A(22A)の遅延回路を(M−1)個の抵抗素子Rp(Rn)を用いて構成した例について説明したが、これに代えて、本実施形態では、(M−1)個の抵抗素子Rp(Rn)に加えて(M−1)個のコンデンサを用いてNOTゲート21A(22A)の遅延回路を構成する例について説明する。

【0188】

図13に本実施形態のNOTゲート21Aの回路構成を示す。

【0189】

本実施形態のNOTゲート21Aは、図2のNOTゲート21Aに(M−1)個のコンデンサ(第1のコンデンサ)C1が追加されている。

【0190】

具体的には、NOTゲート21Aでは、M個のnMOSトランジスタ25bのうち最前段のnMOSトランジスタ25b以外の(M−1)個のnMOSトランジスタ25bに、コンデンサC1が1つずつ設けられている。コンデンサC1は、nMOSトランジスタ25b毎にそのゲート端子とソース端子との間に配置されている。最前段のnMOSトランジスタ25bとは、M個のnMOSトランジスタ25bのうち入力端子25gに最も近いnMOSトランジスタ25bのことである。

【0191】

nMOSトランジスタ25b毎のコンデンサC1は、第1の遅延回路の遅延時間を調整することにより、発振信号に周波数に対する第1の閾値Th1の値を設定することができる。

【0192】

図14に本実施形態のNOTゲート22Aの回路構成を示す。

【0193】

本実施形態のNOTゲート21Aは、図3のNOTゲート22Aに(M−1)個のコンデンサ(第2のコンデンサ)C2が追加されている。

【0194】

具体的には、NOTゲート21Aでは、M個のpMOSトランジスタ25dのうち最前段のpMOSトランジスタ25d以外の(M−1)個のpMOSトランジスタ25dに、コンデンサC2が1つずつ設けられている。コンデンサC2は、pMOSトランジスタ25d毎にそのゲート端子とソース端子との間に配置されている。pMOSトランジスタ25d毎のコンデンサC2は、第2の遅延回路の遅延時間を調整することにより、発振信号に周波数に対する第2の閾値Th2の値を設定することができる。最前段のpMOSトランジスタ25dとは、M個のpMOSトランジスタ25dのうち入力端子25hに最も近いpMOSトランジスタ25dのことである。

【0195】

次に、本実施形態の発振信号の周波数とRSフリップフロップ24の出力との関係についてシミュレーションで調べた結果について説明する。

【0196】

本シミュレーションでは、抵抗素子Rn、Rpの抵抗値を100kΩとし、コンデンサC1、C2の静電容量を0.5pFとし、発振信号を正弦波信号とし、発振信号の周波数を4MHz、10MHzとして、発振信号の振幅を徐々に大きくした。

【0197】

発振信号の周波数を4MHzとしたときには、発振信号の振幅が3.02V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0198】

一方、発振信号の周波数を10MHzとした場合には、発振信号の振幅が3.39V以上になると、RSフリップフロップ24おいて源クロックの出力を開始する。

【0199】

以上により、発振信号の周波数が高くなるほど、RSフリップフロップ24が源クロックの出力を開始する発振信号の振幅(論理閾値)が大きくなる。このことから、NOTゲート21Aの第1閾値Th1、およびNOTゲート22Aの第2閾値Th2が周波数によって変化していることが分かる。

【0200】

(第6実施形態)

上述の第1実施形態では、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第1の閾値nに到達していないときには、NANDゲート50がクロックCLKの出力をマスクする例について説明したが、これに加えて、本実施形態では、CR発振回路33の出力信号の一周期の間において、カウンタ回路31のカウント値が第2の閾値m(>第1の閾値n)以上になると、NANDゲート50がクロックCLKの出力をマスクする例について説明する。

【0201】

図15に本実施形態の作動を示す。

【0202】

CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n未満であるときには、比較回路32がローレベル信号をNANDゲート50に出力する。この場合、発振信号の周波数が低すぎると判定されることになる。

【0203】

CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第2の閾値m以上であるときには、比較回路32がローレベル信号をNANDゲート50に出力する。この場合、発振信号の周波数が高すぎる判定されることになる。

【0204】

このように、CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n未満であるとき、或いはカウンタ回路31のカウント値が第2の閾値m以上であるときには、発振信号の周波数が所望の周波数範囲から外れているとして、NANDゲート50がクロックCLKの出力をマスクする。

【0205】

また、CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n以上で、かつ第2の閾値m未満であるときには、比較回路32がハイレベル信号をNANDゲート50に出力する。このため、発振信号の周波数が所望の周波数範囲内に入っているとして、NANDゲート50がクロックCLKを出力する。

【0206】

以上説明した本実施形態によれば、CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n未満であるとき、或いはカウンタ回路31のカウント値が第2の閾値m以上であるときには、発振信号の周波数が所望の周波数範囲から外れているとして、NANDゲート50がクロックCLKの出力をマスクする。CR発振回路33の出力信号の一周期の間におけるカウンタ回路31のカウント値が第1の閾値n以上で、かつ第2の閾値m未満であるときに、発振信号の周波数が所望の周波数範囲内に入っているとして、NANDゲート50がクロックCLKを出力する。したがって、他の装置に出力するクロックの周波数のバラツキを抑えることができる。

【0207】

(他の実施形態)

上述の第1実施形態では、図2のNOTゲート21Aを構成するnMOSトランジスタ25bの個数と、図3のNOTゲート22Aを構成するpMOSトランジスタ25dの個数とをそれぞれ同一数(M個)とした例について説明したが、これに限らず、図2のNOTゲート21Aを構成するnMOSトランジスタ25bの個数と、図3のNOTゲート22Aを構成するpMOSトランジスタ25dの個数とを相違する数にしてもよい。

【0208】

上述の第1実施形態では、NOTゲート21Aの出力端子にNOTゲート23を接続した例について説明したが、これに代えて、NOTゲート22Aの出力端子にNOTゲート23を接続してもよい。

【0209】

上述の第1実施形態では、NOTゲート22A、23の出力信号を波形整形してクロック(源クロック)を生成するためにRSフリップフロップ24を用いる例について説明したが、これに限らず、NOTゲート22A、23の出力信号を波形整形してクロック(源クロック)を生成するのであれば、RSフリップフロップ以外のフリップフロップを用いてもよい。

【0210】

上述の第3実施形態では、図9のNORゲート21Bとして、図2のNOTゲート21Aに対してpMOSトランジスタ27aおよびnMOSトランジスタ27bを加えて構成したものについて説明したが、これに代えて、図7のNOTゲート21Aに対してpMOSトランジスタ27aおよびnMOSトランジスタ27bを追加して図9のNORゲート21Bを構成してもよい。

【0211】

上述の第3実施形態では、図10のNORゲート22Bとして、図3のNOTゲート22Aに対してpMOSトランジスタ27dおよびnMOSトランジスタ27eを追加して構成したものについて説明したが、これに代えて、図7のNOTゲート22Aに対してpMOSトランジスタ27dおよびnMOSトランジスタ27eを追加して構成してもよい。

【0212】

上述の第3、第4実施形態では、NOTゲート21A(22A)に代わる第1の論理ゲートとして、NORゲート21B(22B)或いはNANDゲート21C(22C)を用いた例について説明したが、これに代えて、第1の論理ゲートとして、NORゲート、NANDゲート以外の回路を用いてもよい。

【0213】

上述の第4実施形態では、図11のNANDゲート21Cとしては、図2のNOTゲート21Aに対してpMOSトランジスタ28aおよびnMOSトランジスタ28bを追加して構成したものを示したが、これに代えて、図7のNOTゲート21Aに対してpMOSトランジスタ28aおよびnMOSトランジスタ28bを追加してNANDゲート21Cを構成してもよい。

【0214】

上述の第4実施形態では、図12のNORゲート22Cとしては、図3のNOTゲート22Aに対してpMOSトランジスタ28dおよびnMOSトランジスタ28eを追加して構成したものについて説明したが、これに代えて、図7のNOTゲート22Aに対してpMOSトランジスタ28dおよびnMOSトランジスタ28eを追加して構成してもよい。

【0215】

上述の第5実施形態では、図13のNOTゲート21Aとしては、図2のNOTゲート21Aに(M−1)個のコンデンサC1を追加して構成したものについて説明したが、これと同様に、図9のNOTゲート21Aに(M−1)個のコンデンサC1を追加して構成したものをNORゲート21Bとしてもよい。また、図11のNOTゲート21Aに(M−1)個のコンデンサC1を追加して構成したものをNORゲート21Cとしてもよい。

【0216】

上述の第5実施形態では、図14のNOTゲート22Aとしては、図3のNOTゲート22Aに(M−1)個のコンデンサC2を追加して構成したものについて説明したが、これと同様に、図10のNOTゲート22Aに(M−1)個のコンデンサC2を追加して構成したものをNORゲート22Bとしてもよい。

また、図12のNOTゲート22Aに(M−1)個のコンデンサC2を追加して構成したものをNORゲート22Cとしてもよい。

【符号の説明】

【0217】

1 クロック出力回路

10 発振回路

11 発振子

12a コンデンサ

12b コンデンサ

13 抵抗素子

14 NOTゲート

20 フィルタ回路

21A NOTゲート

22A NOTゲート

21B NORゲート

22B NORゲート

21C NANDゲート

22C NANDゲート

23 NOTゲート

24 RSフリップフロップ

30 周波数カウンタ

31 カウンタ回路、

32 比較回路、

33 CR発振回路

40 パワーオンリセット回路

50 NANDゲート

25a pMOSトランジスタ

25b nMOSトランジスタ

25d pMOSトランジスタ

25e nMOSトランジスタ

25h 入力端子

25f 出力端子

27a pMOSトランジスタ

27b nMOSトランジスタ

28a pMOSトランジスタ

28b nMOSトランジスタ

28d pMOSトランジスタ

28e nMOSトランジスタ

Rp 抵抗素子

Rn 抵抗素子

Th1 第1の閾値

Th2 第2の閾値

C1 コンデンサ

C2 コンデンサ

【特許請求の範囲】

【請求項1】

発振信号を出力する発振回路(10)と、

前記発振信号の信号レベルが第1閾値(Th1)以上のときローレベルの出力信号を出力し、前記信号レベルが第1閾値未満のときハイレベルの出力信号を出力する第1のNOTゲート(21A)と、

前記信号レベルが第2閾値(Th2)以上のときローレベルの出力信号を出力し、前記信号レベルが第2閾値未満のときハイレベルの出力信号を出力する第2のNOTゲート(22A)と、

前記第1、第2のNOTゲートのうち一方のNOTゲートがハイレベル信号を出力するときにローレベル信号を出力し、前記一方のNOTゲートがローレベル信号を出力するときにハイレベル信号を出力する第3のNOTゲート(23)と、

前記第1、第2のNOTゲートのうち一方のNOTゲート以外の他方のNOTゲートの出力信号と前記第3のNOTゲートの出力信号とをそれぞれ入力信号として、前記それぞれの入力信号が順次互いに相反するレベルになるとき前記入力信号を矩形波に波形整形してクロックとして出力するフリップフロップ回路(24)と、を備え、

前記第1閾値(Th1)は、前記第2閾値(Th2)よりも大きい値に設定されており、

前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなり、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とするクロック出力回路。

【請求項2】

前記第1のNOTゲート(21A)は、

電源とグランドとの間に配置される第1のpMOSトランジスタ(25a)と、

前記第1のpMOSトランジスタ(25a)とグランドとの間に並列配置される複数の第1のnMOSトランジスタ(25b)とを備え、

前記第1のpMOSトランジスタ(25a)のゲート端子と前記複数の第1のnMOSトランジスタ(25b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記第1のpMOSトランジスタのドレイン端子と前記複数の第1のnMOSトランジスタのドレイン端子とが接続されて前記第1のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第1のnMOSトランジスタ(25b)のうち隣り合う2つの第1のnMOSトランジスタ毎に前記2つの第1のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されることにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする請求項1に記載のクロック出力回路。

【請求項3】

前記第2のNOTゲート(22A)は、

電源とグランドとの間に並列配置される複数の第2のpMOSトランジスタ(25d)と、

前記複数の第2のpMOSトランジスタとグランドとの間に配置される第2のnMOSトランジスタ(25e)とを備え、

前記複数の第2のpMOSトランジスタのゲート端子と前記第2のnMOSトランジスタのゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第2のpMOSトランジスタのドレイン端子と前記第2のnMOSトランジスタのドレイン端子とが接続されて前記第2のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第2のpMOSトランジスタ(25d)のうち隣り合う2つの第2のpMOSトランジスタ毎に前記2つの第2のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されることにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなっていることを特徴とする請求項1または2に記載のクロック出力回路。

【請求項4】

前記第1のNOTゲート(21A)は、

電源とグランドとの間に並列配置される複数の第3のpMOSトランジスタ(26d)と、

前記第3のpMOSトランジスタ(26d)とグランドとの間に並列配置される複数の第3のnMOSトランジスタ(26b)とを備え、

前記複数の第3のpMOSトランジスタ(26d)のゲート端子と前記複数の第3のnMOSトランジスタ(26b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第3のpMOSトランジスタのドレイン端子と前記複数の第3のnMOSトランジスタのドレイン端子とが接続されて前記第1のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第3のnMOSトランジスタ(26b)のうち隣り合う2つの第3のnMOSトランジスタ毎に前記2つの第3のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されており、

前記複数の第3のpMOSトランジスタのうち隣り合う2つの第3のpMOSトランジスタ毎に前記2つの第3のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されており、

前記第2の抵抗素子(Rp)の抵抗値を前記第1の抵抗素子(Rn)の抵抗値に比べて小さく設定することにより、前記発振信号の周波数が高くなるほど前記第1閾値(Th1)が大きくなっていることを特徴とする請求項1に記載のクロック出力回路。

【請求項5】

前記第2のNOTゲート(22A)は、

電源とグランドとの間に並列配置される複数の第3のpMOSトランジスタ(26d)と、

前記第3のpMOSトランジスタ(26d)とグランドとの間に並列配置される複数の第3のnMOSトランジスタ(26b)とを備え、

前記複数の第3のpMOSトランジスタ(26d)のゲート端子と前記複数の第3のnMOSトランジスタ(26b)のゲート端子とが接続されて前記発振回路の出力信号が与えられる入力端子を構成し、前記複数の第3のpMOSトランジスタのドレイン端子と前記複数の第3のnMOSトランジスタのドレイン端子とが接続されて前記第2のNOTゲート自体の出力信号を出力する出力端子を構成し、

前記複数の第3のnMOSトランジスタ(26b)のうち隣り合う2つの第3のnMOSトランジスタ毎に前記2つの第3のnMOSトランジスタのゲート端子の間には第1の抵抗素子(Rn)が配置されており、

前記複数の第3のpMOSトランジスタのうち隣り合う2つの第3のpMOSトランジスタ毎に前記2つの第3のpMOSトランジスタのゲート端子の間には第2の抵抗素子(Rp)が配置されており、

前記第2の抵抗素子(Rp)の抵抗値を前記第1の抵抗素子(Rn)の抵抗値に比べて大きく設定することにより、前記発振信号の周波数が高くなるほど前記第2閾値(Th2)が小さくなることを特徴とする請求項1または4に記載のクロック出力回路。

【請求項6】

発振信号を出力する発振回路(10)と、

前記発振信号の信号レベルが第1閾値(Th1)以上のときローレベルの出力信号を出力し、前記信号レベルが前記第1閾値未満のときハイレベルの出力信号を出力する第1の信号出力回路(21A)を有し、前記第1の信号出力回路(21A)の出力信号とイネーブル信号とに基づいてハイレベル或いはローレベルの出力信号を出力する第1の論理ゲート(21B、21C)と、

前記信号レベルが第2閾値(Th2)以上のときローレベルの出力信号を出力し、前記信号レベルが前記第2閾値未満のときハイレベルの出力信号を出力する第2の信号出力回路(22A)を有し、前記第2の信号出力回路(22A)の出力信号と前記イネーブル信号とに基づいてハイレベル或いはローレベルの出力信号を出力する第2の論理ゲート(22B、22C)と、

前記第1、第2の論理ゲートのうち一方の論理ゲートがハイレベル信号を出力するときにローレベル信号を出力し、前記一方の論理ゲートがローレベル信号を出力するときにハイレベル信号を出力する第3のNOTゲート(23)と、

前記第1、第2の論理ゲートのうち一方の論理ゲート以外の他方の論理ゲートの出力信号と前記第3のNOTゲートの出力信号とをそれぞれ入力信号として、前記それぞれの入力信号が順次互いに相反するレベルになるとき前記入力信号を矩形波に波形整形してクロックとして出力するフリップフロップ回路(24)と、を備え、

前記イネーブル信号は、当該クロック出力回路に対してクロック出力の許可を外部装置が指令するための信号であり、前記イネーブル信号によって当該クロック出力回路に対してクロック出力の許可を前記外部装置が指令する際には、前記第1の論理ゲートはその出力信号として、前記第1の信号出力回路の出力信号を出力し、かつ前記第2の論理ゲートはその出力信号として、前記第2の信号出力回路の出力信号を出力するものであり、

前記第1閾値(Th1)は、前記第2閾値(Th2)よりも大きい値に設定されており、