クロック分周回路

【課題】nビットカウンタを有するクロック分周回路において、分周された出力が、分周比によらず一定のタイミングで出力されるクロック分周回路(1)を提供する。

【解決手段】所望の分周比1/mを選択するデコーダ(4)を有し、nビットカウンタ2が、分周比mに対応した加算数2n/m(3)を加算してカウントする機能を有し、分周比に対応した出力が、全て最上位のカウンタから出力することを特徴とする。ここで、n、mは正の整数で、n>2、m>=2、2n/2>=m。

【解決手段】所望の分周比1/mを選択するデコーダ(4)を有し、nビットカウンタ2が、分周比mに対応した加算数2n/m(3)を加算してカウントする機能を有し、分周比に対応した出力が、全て最上位のカウンタから出力することを特徴とする。ここで、n、mは正の整数で、n>2、m>=2、2n/2>=m。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロック分周回路に関し、特に、入力されるクロック信号を設定された分周比で分周するクロック分周回路に関する。

【背景技術】

【0002】

クロック分周回路11は、図6に示したように、一般的に分周比を決めるカウンタ12、分周クロックを生成するためのデコーダ13、および分周比を選択するセレクタ14のブロックで構成される。

【0003】

このブロックの中で、デコーダ13およびセレクタ14は、組み合わせ論理で構成されるため、選択される分周比で論理段数およびトランジスタサイズが異なることになり、その結果得られる分周出力のタイミングが分周比によって変動してしまう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3508762号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以上のような問題点から本願発明は、nビットカウンタを有するクロック分周回路において、分周された出力が、分周比によらず一定のタイミングで出力されるクロック分周回路を提供することを課題とする。

【課題を解決するための手段】

【0006】

本発明は係る課題に鑑みなされたものであり、請求項1の発明は、

nビットカウンタを有するクロック分周回路であつて、

所望の分周比1/mを選択するセレクタを有し、nビットカウンタが、分周比1/mに対応した加算数2n/mを加算してカウントする機能を有することを特徴とするクロック分周回路、としたものである。

ここで、n、mは正の整数で、n>2、m≧2、2n/2≧m。

【発明の効果】

【0007】

本発明のクロック分周回路は以上のような構成であるので、nビットカウンタを有するクロック分周回路において、分周された出力が、分周比によらず一定のタイミングで出力されるクロック分周回路とすることができる。

【図面の簡単な説明】

【0008】

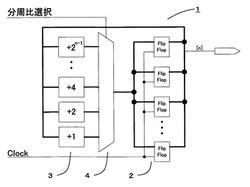

【図1】本発明のクロック分周回路の一例を模式的に示した説明図である。

【図2】図1の回路の1例を設計するためのVerilogHDL記述の説明図である。

【図3】図2のVerilogHDL記述で設計された回路の説明図である。

【図4】図3の回路の各分周比に応じたカウンタの入出力を示した説明図である。

【図5】図3の回路の論理シミュレーション結果を示す説明図である。

【図6】従来のクロック分周回路の例を示す説明図である。

【発明を実施するための形態】

【0009】

以下本発明を実施するための形態につき説明する。図1は、本発明のクロック分周回路の一例を模式的に示した説明図である。本発明のクロック分周回路1は、nビットカウンタ2を有する。そして、所望の分周比1/mを選択するセレクタ4を有し、nビットカウンタが、分周比1/mに対応した加算数(2n/m)3を加算してカウントする機能を有する。ここで、n、mは正の整数で、n>2、m≧2、2n/2≧mである。このような機能を有するので、分周された出力は、常に最上位のビットカウンタから出力され、分周比によらず、全て同じタイミングで出力される。

【0010】

このクロック分周回路の機能について、4ビット、16進のカウンタを有する分周回路を例として、以下に説明する。

【0011】

図2は、このような機能を有する回路を設計するためのVerilogHDLでの記述である。図で、各信号を、クロックCLK、リセットRSTN、分周選択1DIV−SEL0、分周選択2DIV−SEL1、分周回路の出力DIV−CK、とする。カウンタとして4ビット、16進のD−FFを用いた分周回路とする。分周選択の信号は、分周比を選択するもので、分周選択1DIV−SEL0、分周選択2DIV−SEL1がそれぞれ、(0、0)(0、1)(1、0)(1、1)の場合、分周比1/2、1/4、1/8、1/16とする。クロック信号CLKは立ち上がりでカウンタの入力を有効とし、リセットRSTNは立下りでカウンタをリセットする。

【0012】

リセットRSTN信号が入力した場合は、立下りで各々のD−FFをクリアし出力を“0”とする。

【0013】

分周比1/2とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(0、0)として選択し、クロック信号が立ち上がる毎に加算数「8」(16進数)を加算してカウントする。

同様にして、分周比1/4とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(0、1)とし、クロック信号が立ち上がる毎に加算数「4」(16進数)を加算してカウントする。

同様にして、分周比1/8とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(1、0)として選択し、クロック信号が立ち上がる毎に加算数「2」(16進数)を加算してカウントする。

同様にして、分周比1/16とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(1、1)として選択し、クロック信号が立ち上がる毎に加算数「1」(16進数)を加算してカウントする。

分周された信号は、出力端子DIV−CKに出力する。

【0014】

このような条件で設計された回路の例を図3に示す。図で、D−FFおよびその入力、出力を、下位のビットから(D−FF0、D0、Q0)、(D−FF1、D1、Q1)、(D−FF2、D2、Q2)、(D−FF3、D3、Q3)とする。図では、分周選択1DIV−SEL0、分周選択2DIV−SEL1で分周比をデコードする。そして各分周比に応じた加算数が加算され、カウンタでカウントされる。なお、セレクタやカウンタの回路を図上では分離していない。

【0015】

この回路から、各分周比に応じたカウンタの入出力の関係を図4に示した。出力は全て

最上位のビットに対応するD−FF3から出力される。これから、各分周比に応じてカウンタが動作し、分周された信号が出力されることが解る。この回路の論理シミュレーション結果を図5に示した。図5の(a)、(b)、(c)、(d)が、それぞれ分周比1/2、1/4、1/8、1/16に対応した結果である。図では、クロックCLKと分周回路の出力DIV−CKを示している。さらに、カウンタの出力COUNTも示しており、それぞれビット(波形)と共に加算された数も示している。1/2分周ではクロックの立ち上がりで+8(16進数)を加算しているので、0、8、0、8・・・の繰り返し。1/4分周では+4で加算しているので、0、4、8、c、0、4、8、c、・・・と繰り返している。1/8では+2で、0、2、4、6、8、a、c、e、0、2、4、・・・。1/16では、+1で、1、2、3、4、〜d、e、f、0、1、2、3・・・となっている。

【0016】

このように、図3の回路は、所望の分周比を選択するセレクタ機能を有し、4ビットカウンタが、分周比に対応した加算数を加算してカウントする機能を有するクロック分周回路となっている。

【0017】

以上で述べたように、本願発明のクロック分周回路では、各分周比に応じた出力が最上位のカウンタからそれぞれ出力されるので、分周比によらず一定のタイミングで出力されるクロック分周回路とすることができる。

【符号の説明】

【0018】

1・・・クロック分周回路

2・・・nビットカウンタ

3・・・加算数

4・・・セレクタ

11・・・クロック分周回路

12・・・カウンタ

13・・・デコーダ

14・・・セレクタ

【技術分野】

【0001】

本発明は、クロック分周回路に関し、特に、入力されるクロック信号を設定された分周比で分周するクロック分周回路に関する。

【背景技術】

【0002】

クロック分周回路11は、図6に示したように、一般的に分周比を決めるカウンタ12、分周クロックを生成するためのデコーダ13、および分周比を選択するセレクタ14のブロックで構成される。

【0003】

このブロックの中で、デコーダ13およびセレクタ14は、組み合わせ論理で構成されるため、選択される分周比で論理段数およびトランジスタサイズが異なることになり、その結果得られる分周出力のタイミングが分周比によって変動してしまう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3508762号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以上のような問題点から本願発明は、nビットカウンタを有するクロック分周回路において、分周された出力が、分周比によらず一定のタイミングで出力されるクロック分周回路を提供することを課題とする。

【課題を解決するための手段】

【0006】

本発明は係る課題に鑑みなされたものであり、請求項1の発明は、

nビットカウンタを有するクロック分周回路であつて、

所望の分周比1/mを選択するセレクタを有し、nビットカウンタが、分周比1/mに対応した加算数2n/mを加算してカウントする機能を有することを特徴とするクロック分周回路、としたものである。

ここで、n、mは正の整数で、n>2、m≧2、2n/2≧m。

【発明の効果】

【0007】

本発明のクロック分周回路は以上のような構成であるので、nビットカウンタを有するクロック分周回路において、分周された出力が、分周比によらず一定のタイミングで出力されるクロック分周回路とすることができる。

【図面の簡単な説明】

【0008】

【図1】本発明のクロック分周回路の一例を模式的に示した説明図である。

【図2】図1の回路の1例を設計するためのVerilogHDL記述の説明図である。

【図3】図2のVerilogHDL記述で設計された回路の説明図である。

【図4】図3の回路の各分周比に応じたカウンタの入出力を示した説明図である。

【図5】図3の回路の論理シミュレーション結果を示す説明図である。

【図6】従来のクロック分周回路の例を示す説明図である。

【発明を実施するための形態】

【0009】

以下本発明を実施するための形態につき説明する。図1は、本発明のクロック分周回路の一例を模式的に示した説明図である。本発明のクロック分周回路1は、nビットカウンタ2を有する。そして、所望の分周比1/mを選択するセレクタ4を有し、nビットカウンタが、分周比1/mに対応した加算数(2n/m)3を加算してカウントする機能を有する。ここで、n、mは正の整数で、n>2、m≧2、2n/2≧mである。このような機能を有するので、分周された出力は、常に最上位のビットカウンタから出力され、分周比によらず、全て同じタイミングで出力される。

【0010】

このクロック分周回路の機能について、4ビット、16進のカウンタを有する分周回路を例として、以下に説明する。

【0011】

図2は、このような機能を有する回路を設計するためのVerilogHDLでの記述である。図で、各信号を、クロックCLK、リセットRSTN、分周選択1DIV−SEL0、分周選択2DIV−SEL1、分周回路の出力DIV−CK、とする。カウンタとして4ビット、16進のD−FFを用いた分周回路とする。分周選択の信号は、分周比を選択するもので、分周選択1DIV−SEL0、分周選択2DIV−SEL1がそれぞれ、(0、0)(0、1)(1、0)(1、1)の場合、分周比1/2、1/4、1/8、1/16とする。クロック信号CLKは立ち上がりでカウンタの入力を有効とし、リセットRSTNは立下りでカウンタをリセットする。

【0012】

リセットRSTN信号が入力した場合は、立下りで各々のD−FFをクリアし出力を“0”とする。

【0013】

分周比1/2とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(0、0)として選択し、クロック信号が立ち上がる毎に加算数「8」(16進数)を加算してカウントする。

同様にして、分周比1/4とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(0、1)とし、クロック信号が立ち上がる毎に加算数「4」(16進数)を加算してカウントする。

同様にして、分周比1/8とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(1、0)として選択し、クロック信号が立ち上がる毎に加算数「2」(16進数)を加算してカウントする。

同様にして、分周比1/16とするため、分周選択1DIV−SEL0、分周選択2DIV−SEL1を(1、1)として選択し、クロック信号が立ち上がる毎に加算数「1」(16進数)を加算してカウントする。

分周された信号は、出力端子DIV−CKに出力する。

【0014】

このような条件で設計された回路の例を図3に示す。図で、D−FFおよびその入力、出力を、下位のビットから(D−FF0、D0、Q0)、(D−FF1、D1、Q1)、(D−FF2、D2、Q2)、(D−FF3、D3、Q3)とする。図では、分周選択1DIV−SEL0、分周選択2DIV−SEL1で分周比をデコードする。そして各分周比に応じた加算数が加算され、カウンタでカウントされる。なお、セレクタやカウンタの回路を図上では分離していない。

【0015】

この回路から、各分周比に応じたカウンタの入出力の関係を図4に示した。出力は全て

最上位のビットに対応するD−FF3から出力される。これから、各分周比に応じてカウンタが動作し、分周された信号が出力されることが解る。この回路の論理シミュレーション結果を図5に示した。図5の(a)、(b)、(c)、(d)が、それぞれ分周比1/2、1/4、1/8、1/16に対応した結果である。図では、クロックCLKと分周回路の出力DIV−CKを示している。さらに、カウンタの出力COUNTも示しており、それぞれビット(波形)と共に加算された数も示している。1/2分周ではクロックの立ち上がりで+8(16進数)を加算しているので、0、8、0、8・・・の繰り返し。1/4分周では+4で加算しているので、0、4、8、c、0、4、8、c、・・・と繰り返している。1/8では+2で、0、2、4、6、8、a、c、e、0、2、4、・・・。1/16では、+1で、1、2、3、4、〜d、e、f、0、1、2、3・・・となっている。

【0016】

このように、図3の回路は、所望の分周比を選択するセレクタ機能を有し、4ビットカウンタが、分周比に対応した加算数を加算してカウントする機能を有するクロック分周回路となっている。

【0017】

以上で述べたように、本願発明のクロック分周回路では、各分周比に応じた出力が最上位のカウンタからそれぞれ出力されるので、分周比によらず一定のタイミングで出力されるクロック分周回路とすることができる。

【符号の説明】

【0018】

1・・・クロック分周回路

2・・・nビットカウンタ

3・・・加算数

4・・・セレクタ

11・・・クロック分周回路

12・・・カウンタ

13・・・デコーダ

14・・・セレクタ

【特許請求の範囲】

【請求項1】

nビットカウンタを有するクロック分周回路であつて、

所望の分周比1/mを選択するセレクタを有し、nビットカウンタが、分周比1/mに対応した加算数2n/mを加算してカウントする機能を有することを特徴とするクロック分周回路。

ここで、n、mは正の整数で、n>2、m≧2、2n/2≧m。

【請求項1】

nビットカウンタを有するクロック分周回路であつて、

所望の分周比1/mを選択するセレクタを有し、nビットカウンタが、分周比1/mに対応した加算数2n/mを加算してカウントする機能を有することを特徴とするクロック分周回路。

ここで、n、mは正の整数で、n>2、m≧2、2n/2≧m。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−115690(P2013−115690A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−261547(P2011−261547)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000003193)凸版印刷株式会社 (10,630)

[ Back to top ]