クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、低電圧下においても制御可能な、ノイズに対する影響の少ない、正確で確実に動作可能なクロック生成回路に関するものである。

【背景技術】

【0002】

位相同期ループ(PLL:Phase Locked Loop)は、従来から広範囲の分野で利用されている、入力クロックに同期した周期または逓倍クロックを出力する回路である。最近のマイクロプロセッサの動作周波数は高く、例えば、数百MHzの高速クロックで動作するのでPLLをマイクロプロセッサに内蔵することは不可欠になっている。

【0003】

従来のPLLは、電圧制御発信器(VCO:Voltage Control Oscillator)の制御電圧を保持するキャパシタの電圧をチャージポンプにより制御して発信周波数を制御するアナログ型PLLであった。しかし、従来のアナログ型PLLは、低電圧下での制御が困難であり、ノイズに弱く、また動作が安定するまでのロック時間が長く、入力クロックの供給が停止するとPLLの発信が停止し、再度動作を開始するまでに長い時間を要するという課題があった。

【0004】

従来では、上記した課題を解決するために、様々な提案がなされている。例えば、以下に記載する非特許文献1の従来技術では、デジタルディレイラインを用いた周波数逓倍回路を開示している。

【0005】

図8は、従来の周波数逓倍回路10の構成を示すブロック図であり、図において、1はフリップフロップ回路(Flip−Flop)、2は分周器(Divider)、3はコンパレータ、4は制御回路、6および7はそれぞれ遅延回路である。また、図9は、図8に示した従来の周波数逓倍回路10の動作を示すタイミングチャートである。

【0006】

次に動作について説明する。図8に示した従来の周波数逓倍回路10の動作において、デジタルディレイラインである遅延回路6,7の遅延時間の初期状態によっては、図9のタイミングチャート内のタイミングT1からタイミングT2の間に示すように、フリップフロップ回路1からパルスが出力されない状態に落ちる可能性がある。

【0007】

この場合、入力クロックの立ち上がりエッジ(タイミングT1)から、分周器2の出力信号Mをネゲートするまでの遅延時間と、フリップフロップ回路1の出力信号Aとしての逓倍クロック出力信号の4パルス目の立ち下がり時刻(タイミングT1)から出力信号Mをアサートするまでの遅延時間の差によっては、図9に示すタイミングT1からタイミングT2までのように、入力クロックの1周期の間、出力信号Mがアサートされ続けて正確な逓倍出力信号を出力できない状態が発生するという課題があった。

【0008】

また、上記した従来技術である非特許文献1に開示された周波数逓倍回路10では、入力クロックと分周器2の出力信号Mとの間の位相同期に関しては何も言及されておらず、このためPLLの機能としては不十分なものとなっていた。

【0009】

一方、従来のデジタルディレイラインを用いた位相同期回路とデジタルディレイラインを用いた図8に示した周波数逓倍回路10を組み合わせたものがある。

【0010】

図10は、デジタルディレイラインを用いた位相同期回路とデジタルディレイラインを用いた図8に示した周波数逓倍回路10とを組み合わせた従来のクロック生成回路15を示すブロック図であり、図において、10は図8に示した周波数逓倍回路、11は位相同期回路、12は位相同期回路11を構成するデジタルディレイライン、13はデジタルカウンタ、そして14はコンパレータである。

【0011】

次に動作について説明する。周波数逓倍回路10から出力される逓倍クロック出力信号(出力クロック)は、位相同期回路11内のデジタルディレイライン12へ入力され、デジタルディレイライン12から外部へPLL出力信号が出力される。また、コンパレータ14は、このPLL出力信号の位相と入力クロックとの位相を比較し、比較結果をデジタルディレイライン12へフィードバックして入力クロックとPLL出力信号との間の遅延を調整し両者の位相を一致させている。

【0012】

しかしながら、図10に示す従来のクロック生成回路15の構成では、例えば、デジタルディレイライン12の遅延時間が入力クロックの周期より長くなると、周波数逓倍回路10内のコンパレータ3、または位相同期回路11内のコンパレータ14での比較結果により実施される周期または位相の補正がPLL出力信号に反映されるまで多くの時間がかかり、このため、電圧値、温度値等によるPLL出力信号のずれに対する補正能力が悪くなるという課題があった。

【0013】

図11は、図10に示すクロック生成回路15の動作を示すタイミングチャートである。図11のタイミングチャートに示すように、位相同期回路11内のデジタルディレイライン12での遅延時間が、入力クロックの2倍の遅延時間でロックしてしまった場合、タイミングT4で周波数逓倍回路10内のコンパレータ3から出力された比較結果が、PLL出力信号として位相同期回路11から出力されるのはタイミングT4からカウントして入力クロックの2周期後となる。この場合、補正能力は低下するのみならず、タイミングT5での不正確なPLL出力信号により、不正確な遅延補正演算処理が行われて正しくロックできないといった事態が発生する危険性がある。

【0014】

図12は、従来のデジタルディレイライン12を示すブロック図であり、図において、17はデジタルディレイライン12を構成する複数の遅延素子、18は複数の遅延素子の中から1つを選択するセレクタである。例えば、上記非特許文献1や非特許文献2に開示の従来のデジタルディレイライン12では、セレクタ18が遅延素子17内の1つを選択して遅延時間を調整していた。

【0015】

しかしながら、このような従来のデジタルディレイラインの構成では、デジタルディレイラインの遅延が短い場合においても、全ての遅延素子17をスイッチする必要があり、不必要に電力を消費するといった課題があった。

【0016】

図13は、従来の他のデジタルディレイラインを示す構成図である。図に示すように、従来の他のデジタルディレイラインの構成では、消費電力を抑えるため、入力取り込み位置を制御信号a,bを用いて制御することで、各遅延素子を選択的に活性化させ所望の遅延時間を得るものである。しかしながら、図13に示す従来の他のデジタルディレイラインの構成では、クロック生成回路の動作中にカウンタ値が変化した場合、例えば、図13内のノードaからノードbへ入力位置がシフトした場合、図14に示すデジタルディレイラインの動作を示すタイミングチャート内に示すタイミングT8での出力aに不定な電位が乗ってしまうという課題があった。

【先行技術文献】

【非特許文献】

【0017】

【非特許文献1】A Portable Clock Multiplier Generator Using Digital CMOS Standard Cells,Michel Comber他2名,IEEE Journal of Solid-State circuits,Vol.31,No.7,Jul.1996

【非特許文献2】Multifrequency Zero-Jitter Delay-Locked Loop(Avener Efendovich他3名:IEEE Journal of Solid-State Circuits,Vol.29,No.1,JAN.1994

【発明の概要】

【発明が解決しようとする課題】

【0018】

上記したように、従来のクロック生成回路においては、デジタルディレイラインを用いたデジタルPLLにおいて、デジタルディレイラインの初期状態では、周波数逓倍回路10の出力信号である逓倍クロック出力信号が正確に出力されない場合が発生し、また位相同期回路11内のデジタルディレイライン12の初期状態によっては、周波数逓倍回路10もしくは位相同期回路11内のコンパレータ3および14での比較結果に基づいて計算されたデジタルディレイラインの遅延時間の変化がPLL出力信号に反映される以前に、次の位相比較を実行し、温度や電圧の変動に対する補正能力が低下し、位相ロックが困難になるという課題があった。

【0019】

さらに、デジタルディレイライン内の全ての素子をスイッチングすると、無駄な電力を消費し、あるいはこの無駄な電力消費を防止するため、デジタルディレイラインの入力取り込み位置を制御して遅延時間を調整する方式にすると、動作中にカウンタ値が変化する場合に、デジタルディレイラインの出力にハザードが乗って正確に位相ロックができないといった課題があった。

【0020】

この発明は上記のような課題を解決するためになされたもので、位相ロックの精度を向上できるクロック生成回路を得ることを目的とする。

【課題を解決するための手段】

【0021】

上述した課題を解決し、目的を達成するために、本発明の1つの側面にかかるクロック生成回路は、入力されたクロック信号(以下、入力クロックという)の所定逓倍数のクロック信号を出力し(以下、出力された所定逓倍数のクロック信号を出力クロックという)、前記出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定することを特徴とする。

【発明の効果】

【0022】

本発明によれば、逓倍回路が、入力されたクロック信号の所定逓倍数のクロック信号を出力し(以下、出力クロックという)、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有し、位相同期回路が、逓倍回路内の第1の遅延回路から出力された出力クロックを入力し、出力クロックを所定時間遅延させる第2の遅延回路および第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有し、逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタ(1ビットのフリップフロップ)をさらに有し、第3のカウンタのカウンタ値が、第1の値から第2の値に変化した時、第2の遅延回路の遅延時間が第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように第2のカウンタのカウンタ値を設定するように構成したので、逓倍回路がロックした後に位相同期回路での初期状態を逓倍回路の1周期分かそれより少し大きくして位相ロックの精度を向上できる。

【図面の簡単な説明】

【0023】

【図1】この発明の実施の形態1によるクロック生成回路を示すブロック図である。

【図2】図1に示したクロック生成回路内のPLLの構成を示すブロック図である。

【図3】PLLの動作を示すタイミングチャートである。

【図4】ディレイ微調整回路の構成を示す回路図である。

【図5】逓倍部内のカウンタの下位3ビット値、各制御信号およびディレイ微調整回路から出力される4逓倍出力の関係を示したタイミングチャートである。

【図6】位相同期部の動作を示すタイミングチャートである。

【図7】デジタルディレイラインの構成を示す回路図である。

【図8】従来の周波数逓倍回路の構成を示すブロック図である。

【図9】図8に示した従来の周波数逓倍回路の動作を示すタイミングチャートである。

【図10】デジタルディレイラインを用いた位相同期回路とデジタルディレイラインを用いた図8に示した従来の周波数逓倍回路を組み合わせた従来のクロック生成回路を示すブロック図である。

【図11】図10に示す従来のクロック生成回路の動作を示すタイミングチャートである。

【図12】従来のデジタルディレイラインを示すブロック図である。

【図13】従来の他のデジタルディレイラインを示す構成図である。

【図14】図13に示す従来のデジタルディレイラインの動作を示すタイミングチャートである。

【発明を実施するための形態】

【0024】

以下に、本発明にかかるクロック生成回路の実施の形態を図面に基づいて詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。

【0025】

実施の形態1.

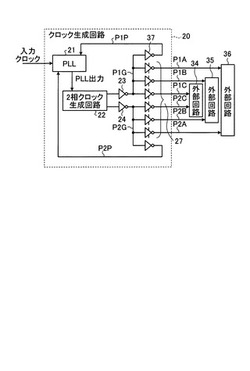

図1は、この発明の実施の形態1によるクロック生成回路20を示すブロック図であり、図において、21は位相同期ループ(Phase Locked Loop、以下、PLLという)、22は2相クロック生成回路、23,24および37はインバータ、27はゲート制御のインバータからなるクロックドライバ、34,35,36はこの実施の形態1のクロック生成回路20で生成されたクロック信号を供給される外部回路である。クロック生成回路20は、PLL21、2相クロック生成回路22、インバータ23,24およびクロックドライバ27から構成されている。

【0026】

次に動作について説明する。この発明の実施の形態1のクロック生成回路20内のPLL21は、入力されたクロック信号(以下、入力クロックという)の4逓倍のクロック信号としてのPLL出力信号(以下、PLL出力という)を出力する。このPLL出力信号は、2相クロック生成回路22で2相ノンオーバラップ信号P1G,P2Gとなる。この2相ノンオーバラップ信号P1G,P2Gは、各ブロックのクロックドライバ27を介して外部回路34,35,36へ供給される。クロックドライバ27の出力信号P1C,P2Cは外部回路34へ出力され、クロックドライバ27の出力信号P1B,P2Bは外部回路35へ出力され、そしてクロックドライバ27の出力信号P1A,P2Aは外部回路36へ出力される。

【0027】

例えば、外部回路34の出力状態が変化しない場合(即ち、外部回路34が動作していない場合)、クロックドライバの出力信号P1C,P2Cは常にロウレベル(Lレベル)に固定され、外部回路34へ出力される。また、外部回路35の出力状態が変化しない場合(即ち、外部回路35が動作していない場合)、クロックドライバの出力信号P1B,P2Bは常にロウレベル(Lレベル)に固定され、外部回路35へ出力される。同様に、外部回路36の出力状態が変化しない場合(即ち、外部回路36が動作していない場合)、クロックドライバの出力信号P1A,P2Aは常にロウレベル(Lレベル)に固定され外部回路36へ出力される。PLL21は、クロック入力とインバータ37の出力である制御信号P1Pとの位相が一致するように、その出力(以下、PLL出力という)を制御する機能を備えている。

【0028】

図2は、図1に示したクロック生成回路20内のPLL21の構成を示すブロック図であり、PLL21は逓倍回路40(以下、逓倍部40という)および位相同期回路41(以下、位相同期部41という)の2つの部分から構成されている。

【0029】

以下、PLL21を構成する逓倍部40および位相同期部41に関して詳細に説明する。逓倍部40は、入力クロックの4逓倍クロックを生成する機能を備えている。この実施の形態1では、逓倍部40は4逓倍クロックを生成するが、この発明はこれに限定されることなく、例えば、2逓倍クロック、6逓倍クロック、8逓倍クロック等、所定の逓倍クロックを生成するPLLでもよい。

【0030】

次に逓倍部40の動作について説明する。図3は、PLL21の動作を示すタイミングチャートである。図2に示す逓倍部40において、太線で示したループはリングオシレータ100を示している。逓倍部40は、この太線で示されたリングオシレータ100で生成された4逓倍クロックを位相同期部41へ出力する。但し、このリングオシレータ100は、制御信号DL−ACTがネゲートされている間は、強制的にLレベルに設定され、制御信号DL−STATがアサートされている間は、強制的にHレベルに設定される。

【0031】

図3のタイミングチャートに示されるように、制御信号DL−ACTは、入力クロックの立ち上がりエッジでアサートされ(例えば、タイミングT10)、4逓倍出力の4パルス目の立ち下がりエッジでネゲートされる(例えば、タイミングT11)。

【0032】

デジタルディレイライン(第1の遅延回路)56は、96個の遅延素子(例えば、セレクタ)が直列に接続されて構成されており、遅延時間を96段階に調整可能である。例えば、10ビットのカウンタ(第1のカウンタ)52の上位7ビットで、デジタルディレイライン56の遅延時間を制御する。制御信号PLL−resetがアサートされた時のカウンタ52の初期値は1であり、これはデジタルディレイライン56の遅延時間を最小値に制御する。カウンタ52は、入力クロックの2周期毎に1つカウントアップされる。

【0033】

入力クロックの立ち上がりエッジとDL−OUTの立ち下がりエッジの位相が一致した時点(即ち、タイミングT12の次の入力クロック立ち上がりタイミングT13)で、カウンタ52のカウントアップが停止する。このように、カウンタ52は、デジタルディレイライン56の遅延時間を最小値から除々に大きく設定できるので、誤って3逓倍や2逓倍でロックすることなく、従来例で説明したように、分周器からの出力信号がアサートされ続けて、正確な逓倍出力信号が出力できないといった状態を避けることができる。

【0034】

例えば、入力クロックの立ち上がり時に、制御信号DL−ACTがアサートされ続けた場合、入力クロックの1周期の間に4逓倍出力が4パルス出ていないと逓倍回路40は判断し、制御信号PLL−rsetをアサートし、カウンタ52をリセットさせる。これにより、電源投入直後等の初期状態においてPLL21の動作が不安定な場合においても、確実にPLL21の動作をリセットできる。また、制御信号PLL−resetは、外部から供給される外部リセット信号によっても、アサート可能である。この外部リセット信号は、チップ外部の装置から供給されるリセット入力や、電源投入時にアサートされるパワーオンリセット信号等から生成される。

【0035】

図4は、ディレイ微調整回路の構成を示す回路図であり、図において、59はディレイ微調整回路(第1の遅延回路)、75および76は遅延素子である。

【0036】

次に、ディレイ微調整回路59の動作について説明する。ディレイ微調整回路59は、DL−CNT生成回路57から出力される制御信号DL−CNTがHレベルの時、遅延素子75の1段分の遅延を追加する。これにより、デジタルディレイライン56での遅延時間の微調整を行う。DL−CNT生成回路57から出力される制御信号DL−CNTを、入力クロックのサイクルの途中で切り替えることで、同一入力クロックサイクル内で4逓倍出力の一部のパルス幅を遅延素子1段分広げることができる。

【0037】

DL−CNT生成回路57は、10ビットのカウンタ52の下位3ビット値とパルスカウンタ400の出力C1〜C7の値に基づいて制御信号DL−CNTを生成する。

【0038】

図5は、逓倍部40内のカウンタ52の下位3ビット値、各種の制御信号DL−CNT、C1〜C8、DL−ACT、およびディレイ微調整回路59から出力される4逓倍出力の関係を示したタイミングチャートである。図5のタイミングチャートに示すように、10ビットのカウンタ52の下位3ビット値が0の時は、ディレイ微調整回路59から出力される4逓倍出力の全てのパルスが同一パルス幅を有している。そして、カウンタ52の下位3ビット値が、例えば1から7へと増加してゆくにつれて、ディレイ微調整回路59内の遅延素子1段の遅延時間幅を持つパルスが、ディレイ微調整回路59から4逓倍出力として出力される。

【0039】

カウンタ52のカウンタ値が、入力クロック数でカウントして20サイクル以上停止した場合、ロック検出回路(第3のカウンタ)60はロック検出信号を出力する。このロック検出信号がアサートされた場合でも、周囲の温度、電圧、その他の要因により、入力クロックの立ち上がりエッジと制御信号DL−OUTの立ち下がりエッジの位相がずれた場合は、そのずれに応じてカウンタ52のカウンタ値を1つ毎増加/減少させ位相のずれを解消する。但し、一旦、ロック検出信号がアサートされたら、制御信号PLL−resetがカウンタ52へ入力されない限りこのロック検出信号はネゲートされない。

【0040】

次に、PLL21内の位相同期部41の動作について説明する。図6は、位相同期部41の動作を示すタイミングチャートである。位相同期部41内では、逓倍部40から出力された4逓倍出力を、位相同期部41内に組み込まれた2つのデジタルディレイライン(第2の遅延回路)69および71で所定時間遅延させ、入力クロックの位相と制御信号P1Pの位相を一致させる動作を行う。位相同期部41はリセット直後は動作せず、逓倍部40内のロック検出回路60からロック検出信号がアサートされるとその動作を開始する。

【0041】

位相同期部41内のカウンタ(第2のカウンタ)65は、上位5ビット値でデジタルディレイライン69を、下位3ビット値でデジタルディレイライン71の動作を制御する。デジタルディレイライン71は、逓倍部40内のデジタルディレイライン56内で用いられている遅延素子を8個直列に接続した構成を有する。デジタルディレイライン69は、デジタルディレイライン71内の各遅延素子の約6〜8倍(この範囲は、温度、電圧、プロセス変動等に基づいて変動する)の遅延時間を有する遅延素子が32個直列に接続された構成を有する。

【0042】

位相同期部41では、デジタルディレイライン69が入力クロックの位相と制御信号P1Pの位相を大まかに合わせ、次に、デジタルディレイライン71が両者の位相を詳細に調整する。

【0043】

カウンタ65の初期値として、ロック検出回路60から出力されたロック検出信号がアサートされた時の、逓倍部40内のカウンタ52のカウンタ値がセットされる。入力クロックの立ち上がりエッジと制御信号P1Pの立ち上がりエッジの位相差により、カウンタ65のカウンタ値を1つ増加減少させ、両者の位相が一致したところで、カウンタ65のカウント動作は停止する。但し、一旦、カウント動作が停止した場合でも、温度、電圧、その他の影響で入力クロックの位相と制御信号P1Pの位相がずれた場合は、ずれの大きさに応じてカウンタ65のカウンタ値を1つ毎増加減少させ、両者の位相を一致させる。

【0044】

逓倍部40内のカウンタ52のカウンタ値を初期値として設定する意味は、位相同期部41の動作が開始された時、位相を早くする(カウンタ値を減算する)場合と、位相を遅くする(カウンタ値を加算する)場合の、いずれの方向に動作させても確実に同期するエッジを得るため、あらかじめ半周期分の遅延時間を持たせたことや、位相同期部41がロックした場合のデジタルディレイライン69の遅延時間を入力クロックの1周期以内に設定させ、確実にロックを行い高いロック性能を得るためである。仮に、位相同期部41のデジタルディレイライン69の遅延時間が2周期以上でロックしようとすると、逓倍部40内のカウンタ52又は位相同期部41内のカウンタ65の値の変化が制御信号P1Pに乗せられる以前に次の位相比較を実行することになるので、ロック動作が困難になりロック性能が低下することになる。

【0045】

次に、逓倍部40内や位相同期部41内に組み込まれているデジタルディレイライン56,69,71について説明する。

【0046】

図7は、デジタルディレイライン56,69,71のそれぞれの構成を示す回路図であり、図において、各遅延素子n(n=0,...y,y−1,...,n−1,n)は、直列に接続された2つのPMOSTrおよび直列に接続された2つのNMOSTrがさらに直列に接続されて得られる回路を2組並列に並べた構成を有する。PMOSTrの組とNMOSTrの組とを直列に接続する直列接続点は、各遅延素子の出力ノードと次段の遅延素子との間に設けられた出力インバータに接続されている。各遅延素子には入力として入力パルスを入力する入力ノードがある。逓倍部40内のデジタルディレイライン56は、この遅延素子を96個(即ち、n=95)直接に接続した構成を有し、位相同期部41内のデジタルディレイライン71は、遅延素子を8個(n=7)直列に接続した構成を、またデジタルディレイライン69は遅延素子を32個(n=31)直列に接続した構成を有している。

【0047】

次に、デジタルディレイラインの動作について説明する。カウンタ52,65から出力されるカウンタ値により、各デジタルディレイライン56,69,71内の所定の遅延素子が制御信号 ̄WL(n)により選択され、選択された遅延素子の入力ノードn(n=0,...y,y+1,...,n−1,n)から制御信号としての入力パルスが入力される。

【0048】

このように、入力パルスの入力位置を変えることにより、デジタルディレイライン56,69,71の遅延時間を調整する。入力位置を変える方式は、出力位置を変えてデジタルディレイラインの遅延時間を変化させる従来の方式と比較すると、特に高周波を用いる場合にスイッチングするトランジスタ数を減少できるからである。

【0049】

カウンタ52,65の各カウンタ値がyの場合、制御信号 ̄WL(y)が入力される遅延素子yの入力ノードyを介して入力パルスが遅延素子y内に入力されるが、この場合、2つの制御信号、即ち制御信号 ̄WL(y)および制御信号 ̄WL(y+1)がアサートされるので、遅延素子yと遅延素子y+1との2ヶ所から入力パルスが取り込まれるため、従来例で説明した図14のタイミングチャート内のタイミングT7からタイミングT8間に示すような出力aに不定な電位が乗る状態を確実に回避できる。

【0050】

以上のように、この実施の形態1によれば、第1の遅延回路および第2の遅延回路から構成され、第1の遅延回路および第2の遅延回路のそれぞれは、互いに直列に接続された複数個の遅延素子から構成され、第1の遅延回路あるいは第2の遅延回路に対応した第1のカウンタあるいは第2のカウンタから出力されるカウンタ値の値に応じて複数の遅延素子のいずれかの遅延素子が選択され、選択された遅延素子およびこれに隣接する遅延素子により遅延時間が設定され制御されるように構成したので、誤動作を防止でき、またこれを組み込んだクロック生成回路やDLL(Delay Locked Loop)の消費電力を低減することができる。

【0051】

また、この実施の形態1によれば、遅延素子のそれぞれが、直列に接続されたn個のPMOSTrの組および直列に接続されたn個のNMOSTrの組とをさらに互いに直列に接続させて得られる回路を2組並列に並べた構成を有し、n個のPMOSTrの組とn個のNMOSTrの組との接点に隣接するPMOSTrおよびNMOSTrのゲートを互いに接続するように構成したので、クロック生成回路の消費電力を低減することができる。

【0052】

さらに、この実施の形態1によれば、逓倍回路が、入力されたクロック信号の所定逓倍数のクロック信号を出力し(以下、出力クロックという)、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有し、位相同期回路が、逓倍回路内の第1の遅延回路から出力された出力クロックを入力し、出力クロックを所定時間遅延させる第2の遅延回路および第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有し、逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタ(1ビットのフリップフロップ)をさらに有し、第3のカウンタのカウンタ値が、第1の値から第2の値に変化した時、第2の遅延回路の遅延時間が第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように第2のカウンタのカウンタ値を設定するように構成したので、逓倍回路がロックした後に位相同期回路での初期状態を逓倍回路の1周期分かそれより少し大きくしてロックの精度を向上することができる。

【0053】

また、この実施の形態1によれば、デジタルディレイラインの遅延時間をカウンタで設定し、外部から供給されるリセット信号あるいは入力クロックの1周期の間に逓倍回路から出力される逓倍出力のパルス数が所望の逓倍数未満の場合、デジタルディレイラインの遅延時間を設定するカウンタのカウンタ値をリセットし、リセット直後のデジタルディレイラインの遅延時間が最小値となるようなカウンタ値に設定し、その後、徐々にデジタルディレイラインの遅延時間を増加するので、低電圧下でも制御が容易で、確実に所望の逓倍数で出力クロックをロックでき、またカウンタの初期状態がいかなる場合においても確実に正確な逓倍クロックを供給できる。さらに、デジタルディレイラインはカウンタで指定された遅延素子と隣接する遅延素子の2箇所から入力パルスを供給するので誤動作を防止でき、また消費電力を低減するとともに温度や電圧等の変動に対する補正能力を向上できる。

【産業上の利用可能性】

【0054】

以上のように、本発明にかかるクロック生成回路は、入力クロックを逓倍したクロックの生成に有用であり、特に、低電圧下においても制御可能な、ノイズに対する影響の少ない、正確で確実なクロックの生成に適している。

【符号の説明】

【0055】

20 クロック生成回路

40 逓倍部(逓倍回路)

41 位相同期部(位相同期回路)

52 カウンタ(第1のカウンタ)

56 デジタルディレイライン(第1の遅延回路)

59 ディレイ微調整回路(第1の遅延回路)

60 ロック検出回路(第3のカウンタ)

65 カウンタ(第2のカウンタ)

69,71 デジタルディレイライン(第2の遅延回路)

【技術分野】

【0001】

この発明は、低電圧下においても制御可能な、ノイズに対する影響の少ない、正確で確実に動作可能なクロック生成回路に関するものである。

【背景技術】

【0002】

位相同期ループ(PLL:Phase Locked Loop)は、従来から広範囲の分野で利用されている、入力クロックに同期した周期または逓倍クロックを出力する回路である。最近のマイクロプロセッサの動作周波数は高く、例えば、数百MHzの高速クロックで動作するのでPLLをマイクロプロセッサに内蔵することは不可欠になっている。

【0003】

従来のPLLは、電圧制御発信器(VCO:Voltage Control Oscillator)の制御電圧を保持するキャパシタの電圧をチャージポンプにより制御して発信周波数を制御するアナログ型PLLであった。しかし、従来のアナログ型PLLは、低電圧下での制御が困難であり、ノイズに弱く、また動作が安定するまでのロック時間が長く、入力クロックの供給が停止するとPLLの発信が停止し、再度動作を開始するまでに長い時間を要するという課題があった。

【0004】

従来では、上記した課題を解決するために、様々な提案がなされている。例えば、以下に記載する非特許文献1の従来技術では、デジタルディレイラインを用いた周波数逓倍回路を開示している。

【0005】

図8は、従来の周波数逓倍回路10の構成を示すブロック図であり、図において、1はフリップフロップ回路(Flip−Flop)、2は分周器(Divider)、3はコンパレータ、4は制御回路、6および7はそれぞれ遅延回路である。また、図9は、図8に示した従来の周波数逓倍回路10の動作を示すタイミングチャートである。

【0006】

次に動作について説明する。図8に示した従来の周波数逓倍回路10の動作において、デジタルディレイラインである遅延回路6,7の遅延時間の初期状態によっては、図9のタイミングチャート内のタイミングT1からタイミングT2の間に示すように、フリップフロップ回路1からパルスが出力されない状態に落ちる可能性がある。

【0007】

この場合、入力クロックの立ち上がりエッジ(タイミングT1)から、分周器2の出力信号Mをネゲートするまでの遅延時間と、フリップフロップ回路1の出力信号Aとしての逓倍クロック出力信号の4パルス目の立ち下がり時刻(タイミングT1)から出力信号Mをアサートするまでの遅延時間の差によっては、図9に示すタイミングT1からタイミングT2までのように、入力クロックの1周期の間、出力信号Mがアサートされ続けて正確な逓倍出力信号を出力できない状態が発生するという課題があった。

【0008】

また、上記した従来技術である非特許文献1に開示された周波数逓倍回路10では、入力クロックと分周器2の出力信号Mとの間の位相同期に関しては何も言及されておらず、このためPLLの機能としては不十分なものとなっていた。

【0009】

一方、従来のデジタルディレイラインを用いた位相同期回路とデジタルディレイラインを用いた図8に示した周波数逓倍回路10を組み合わせたものがある。

【0010】

図10は、デジタルディレイラインを用いた位相同期回路とデジタルディレイラインを用いた図8に示した周波数逓倍回路10とを組み合わせた従来のクロック生成回路15を示すブロック図であり、図において、10は図8に示した周波数逓倍回路、11は位相同期回路、12は位相同期回路11を構成するデジタルディレイライン、13はデジタルカウンタ、そして14はコンパレータである。

【0011】

次に動作について説明する。周波数逓倍回路10から出力される逓倍クロック出力信号(出力クロック)は、位相同期回路11内のデジタルディレイライン12へ入力され、デジタルディレイライン12から外部へPLL出力信号が出力される。また、コンパレータ14は、このPLL出力信号の位相と入力クロックとの位相を比較し、比較結果をデジタルディレイライン12へフィードバックして入力クロックとPLL出力信号との間の遅延を調整し両者の位相を一致させている。

【0012】

しかしながら、図10に示す従来のクロック生成回路15の構成では、例えば、デジタルディレイライン12の遅延時間が入力クロックの周期より長くなると、周波数逓倍回路10内のコンパレータ3、または位相同期回路11内のコンパレータ14での比較結果により実施される周期または位相の補正がPLL出力信号に反映されるまで多くの時間がかかり、このため、電圧値、温度値等によるPLL出力信号のずれに対する補正能力が悪くなるという課題があった。

【0013】

図11は、図10に示すクロック生成回路15の動作を示すタイミングチャートである。図11のタイミングチャートに示すように、位相同期回路11内のデジタルディレイライン12での遅延時間が、入力クロックの2倍の遅延時間でロックしてしまった場合、タイミングT4で周波数逓倍回路10内のコンパレータ3から出力された比較結果が、PLL出力信号として位相同期回路11から出力されるのはタイミングT4からカウントして入力クロックの2周期後となる。この場合、補正能力は低下するのみならず、タイミングT5での不正確なPLL出力信号により、不正確な遅延補正演算処理が行われて正しくロックできないといった事態が発生する危険性がある。

【0014】

図12は、従来のデジタルディレイライン12を示すブロック図であり、図において、17はデジタルディレイライン12を構成する複数の遅延素子、18は複数の遅延素子の中から1つを選択するセレクタである。例えば、上記非特許文献1や非特許文献2に開示の従来のデジタルディレイライン12では、セレクタ18が遅延素子17内の1つを選択して遅延時間を調整していた。

【0015】

しかしながら、このような従来のデジタルディレイラインの構成では、デジタルディレイラインの遅延が短い場合においても、全ての遅延素子17をスイッチする必要があり、不必要に電力を消費するといった課題があった。

【0016】

図13は、従来の他のデジタルディレイラインを示す構成図である。図に示すように、従来の他のデジタルディレイラインの構成では、消費電力を抑えるため、入力取り込み位置を制御信号a,bを用いて制御することで、各遅延素子を選択的に活性化させ所望の遅延時間を得るものである。しかしながら、図13に示す従来の他のデジタルディレイラインの構成では、クロック生成回路の動作中にカウンタ値が変化した場合、例えば、図13内のノードaからノードbへ入力位置がシフトした場合、図14に示すデジタルディレイラインの動作を示すタイミングチャート内に示すタイミングT8での出力aに不定な電位が乗ってしまうという課題があった。

【先行技術文献】

【非特許文献】

【0017】

【非特許文献1】A Portable Clock Multiplier Generator Using Digital CMOS Standard Cells,Michel Comber他2名,IEEE Journal of Solid-State circuits,Vol.31,No.7,Jul.1996

【非特許文献2】Multifrequency Zero-Jitter Delay-Locked Loop(Avener Efendovich他3名:IEEE Journal of Solid-State Circuits,Vol.29,No.1,JAN.1994

【発明の概要】

【発明が解決しようとする課題】

【0018】

上記したように、従来のクロック生成回路においては、デジタルディレイラインを用いたデジタルPLLにおいて、デジタルディレイラインの初期状態では、周波数逓倍回路10の出力信号である逓倍クロック出力信号が正確に出力されない場合が発生し、また位相同期回路11内のデジタルディレイライン12の初期状態によっては、周波数逓倍回路10もしくは位相同期回路11内のコンパレータ3および14での比較結果に基づいて計算されたデジタルディレイラインの遅延時間の変化がPLL出力信号に反映される以前に、次の位相比較を実行し、温度や電圧の変動に対する補正能力が低下し、位相ロックが困難になるという課題があった。

【0019】

さらに、デジタルディレイライン内の全ての素子をスイッチングすると、無駄な電力を消費し、あるいはこの無駄な電力消費を防止するため、デジタルディレイラインの入力取り込み位置を制御して遅延時間を調整する方式にすると、動作中にカウンタ値が変化する場合に、デジタルディレイラインの出力にハザードが乗って正確に位相ロックができないといった課題があった。

【0020】

この発明は上記のような課題を解決するためになされたもので、位相ロックの精度を向上できるクロック生成回路を得ることを目的とする。

【課題を解決するための手段】

【0021】

上述した課題を解決し、目的を達成するために、本発明の1つの側面にかかるクロック生成回路は、入力されたクロック信号(以下、入力クロックという)の所定逓倍数のクロック信号を出力し(以下、出力された所定逓倍数のクロック信号を出力クロックという)、前記出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定することを特徴とする。

【発明の効果】

【0022】

本発明によれば、逓倍回路が、入力されたクロック信号の所定逓倍数のクロック信号を出力し(以下、出力クロックという)、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有し、位相同期回路が、逓倍回路内の第1の遅延回路から出力された出力クロックを入力し、出力クロックを所定時間遅延させる第2の遅延回路および第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有し、逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタ(1ビットのフリップフロップ)をさらに有し、第3のカウンタのカウンタ値が、第1の値から第2の値に変化した時、第2の遅延回路の遅延時間が第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように第2のカウンタのカウンタ値を設定するように構成したので、逓倍回路がロックした後に位相同期回路での初期状態を逓倍回路の1周期分かそれより少し大きくして位相ロックの精度を向上できる。

【図面の簡単な説明】

【0023】

【図1】この発明の実施の形態1によるクロック生成回路を示すブロック図である。

【図2】図1に示したクロック生成回路内のPLLの構成を示すブロック図である。

【図3】PLLの動作を示すタイミングチャートである。

【図4】ディレイ微調整回路の構成を示す回路図である。

【図5】逓倍部内のカウンタの下位3ビット値、各制御信号およびディレイ微調整回路から出力される4逓倍出力の関係を示したタイミングチャートである。

【図6】位相同期部の動作を示すタイミングチャートである。

【図7】デジタルディレイラインの構成を示す回路図である。

【図8】従来の周波数逓倍回路の構成を示すブロック図である。

【図9】図8に示した従来の周波数逓倍回路の動作を示すタイミングチャートである。

【図10】デジタルディレイラインを用いた位相同期回路とデジタルディレイラインを用いた図8に示した従来の周波数逓倍回路を組み合わせた従来のクロック生成回路を示すブロック図である。

【図11】図10に示す従来のクロック生成回路の動作を示すタイミングチャートである。

【図12】従来のデジタルディレイラインを示すブロック図である。

【図13】従来の他のデジタルディレイラインを示す構成図である。

【図14】図13に示す従来のデジタルディレイラインの動作を示すタイミングチャートである。

【発明を実施するための形態】

【0024】

以下に、本発明にかかるクロック生成回路の実施の形態を図面に基づいて詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。

【0025】

実施の形態1.

図1は、この発明の実施の形態1によるクロック生成回路20を示すブロック図であり、図において、21は位相同期ループ(Phase Locked Loop、以下、PLLという)、22は2相クロック生成回路、23,24および37はインバータ、27はゲート制御のインバータからなるクロックドライバ、34,35,36はこの実施の形態1のクロック生成回路20で生成されたクロック信号を供給される外部回路である。クロック生成回路20は、PLL21、2相クロック生成回路22、インバータ23,24およびクロックドライバ27から構成されている。

【0026】

次に動作について説明する。この発明の実施の形態1のクロック生成回路20内のPLL21は、入力されたクロック信号(以下、入力クロックという)の4逓倍のクロック信号としてのPLL出力信号(以下、PLL出力という)を出力する。このPLL出力信号は、2相クロック生成回路22で2相ノンオーバラップ信号P1G,P2Gとなる。この2相ノンオーバラップ信号P1G,P2Gは、各ブロックのクロックドライバ27を介して外部回路34,35,36へ供給される。クロックドライバ27の出力信号P1C,P2Cは外部回路34へ出力され、クロックドライバ27の出力信号P1B,P2Bは外部回路35へ出力され、そしてクロックドライバ27の出力信号P1A,P2Aは外部回路36へ出力される。

【0027】

例えば、外部回路34の出力状態が変化しない場合(即ち、外部回路34が動作していない場合)、クロックドライバの出力信号P1C,P2Cは常にロウレベル(Lレベル)に固定され、外部回路34へ出力される。また、外部回路35の出力状態が変化しない場合(即ち、外部回路35が動作していない場合)、クロックドライバの出力信号P1B,P2Bは常にロウレベル(Lレベル)に固定され、外部回路35へ出力される。同様に、外部回路36の出力状態が変化しない場合(即ち、外部回路36が動作していない場合)、クロックドライバの出力信号P1A,P2Aは常にロウレベル(Lレベル)に固定され外部回路36へ出力される。PLL21は、クロック入力とインバータ37の出力である制御信号P1Pとの位相が一致するように、その出力(以下、PLL出力という)を制御する機能を備えている。

【0028】

図2は、図1に示したクロック生成回路20内のPLL21の構成を示すブロック図であり、PLL21は逓倍回路40(以下、逓倍部40という)および位相同期回路41(以下、位相同期部41という)の2つの部分から構成されている。

【0029】

以下、PLL21を構成する逓倍部40および位相同期部41に関して詳細に説明する。逓倍部40は、入力クロックの4逓倍クロックを生成する機能を備えている。この実施の形態1では、逓倍部40は4逓倍クロックを生成するが、この発明はこれに限定されることなく、例えば、2逓倍クロック、6逓倍クロック、8逓倍クロック等、所定の逓倍クロックを生成するPLLでもよい。

【0030】

次に逓倍部40の動作について説明する。図3は、PLL21の動作を示すタイミングチャートである。図2に示す逓倍部40において、太線で示したループはリングオシレータ100を示している。逓倍部40は、この太線で示されたリングオシレータ100で生成された4逓倍クロックを位相同期部41へ出力する。但し、このリングオシレータ100は、制御信号DL−ACTがネゲートされている間は、強制的にLレベルに設定され、制御信号DL−STATがアサートされている間は、強制的にHレベルに設定される。

【0031】

図3のタイミングチャートに示されるように、制御信号DL−ACTは、入力クロックの立ち上がりエッジでアサートされ(例えば、タイミングT10)、4逓倍出力の4パルス目の立ち下がりエッジでネゲートされる(例えば、タイミングT11)。

【0032】

デジタルディレイライン(第1の遅延回路)56は、96個の遅延素子(例えば、セレクタ)が直列に接続されて構成されており、遅延時間を96段階に調整可能である。例えば、10ビットのカウンタ(第1のカウンタ)52の上位7ビットで、デジタルディレイライン56の遅延時間を制御する。制御信号PLL−resetがアサートされた時のカウンタ52の初期値は1であり、これはデジタルディレイライン56の遅延時間を最小値に制御する。カウンタ52は、入力クロックの2周期毎に1つカウントアップされる。

【0033】

入力クロックの立ち上がりエッジとDL−OUTの立ち下がりエッジの位相が一致した時点(即ち、タイミングT12の次の入力クロック立ち上がりタイミングT13)で、カウンタ52のカウントアップが停止する。このように、カウンタ52は、デジタルディレイライン56の遅延時間を最小値から除々に大きく設定できるので、誤って3逓倍や2逓倍でロックすることなく、従来例で説明したように、分周器からの出力信号がアサートされ続けて、正確な逓倍出力信号が出力できないといった状態を避けることができる。

【0034】

例えば、入力クロックの立ち上がり時に、制御信号DL−ACTがアサートされ続けた場合、入力クロックの1周期の間に4逓倍出力が4パルス出ていないと逓倍回路40は判断し、制御信号PLL−rsetをアサートし、カウンタ52をリセットさせる。これにより、電源投入直後等の初期状態においてPLL21の動作が不安定な場合においても、確実にPLL21の動作をリセットできる。また、制御信号PLL−resetは、外部から供給される外部リセット信号によっても、アサート可能である。この外部リセット信号は、チップ外部の装置から供給されるリセット入力や、電源投入時にアサートされるパワーオンリセット信号等から生成される。

【0035】

図4は、ディレイ微調整回路の構成を示す回路図であり、図において、59はディレイ微調整回路(第1の遅延回路)、75および76は遅延素子である。

【0036】

次に、ディレイ微調整回路59の動作について説明する。ディレイ微調整回路59は、DL−CNT生成回路57から出力される制御信号DL−CNTがHレベルの時、遅延素子75の1段分の遅延を追加する。これにより、デジタルディレイライン56での遅延時間の微調整を行う。DL−CNT生成回路57から出力される制御信号DL−CNTを、入力クロックのサイクルの途中で切り替えることで、同一入力クロックサイクル内で4逓倍出力の一部のパルス幅を遅延素子1段分広げることができる。

【0037】

DL−CNT生成回路57は、10ビットのカウンタ52の下位3ビット値とパルスカウンタ400の出力C1〜C7の値に基づいて制御信号DL−CNTを生成する。

【0038】

図5は、逓倍部40内のカウンタ52の下位3ビット値、各種の制御信号DL−CNT、C1〜C8、DL−ACT、およびディレイ微調整回路59から出力される4逓倍出力の関係を示したタイミングチャートである。図5のタイミングチャートに示すように、10ビットのカウンタ52の下位3ビット値が0の時は、ディレイ微調整回路59から出力される4逓倍出力の全てのパルスが同一パルス幅を有している。そして、カウンタ52の下位3ビット値が、例えば1から7へと増加してゆくにつれて、ディレイ微調整回路59内の遅延素子1段の遅延時間幅を持つパルスが、ディレイ微調整回路59から4逓倍出力として出力される。

【0039】

カウンタ52のカウンタ値が、入力クロック数でカウントして20サイクル以上停止した場合、ロック検出回路(第3のカウンタ)60はロック検出信号を出力する。このロック検出信号がアサートされた場合でも、周囲の温度、電圧、その他の要因により、入力クロックの立ち上がりエッジと制御信号DL−OUTの立ち下がりエッジの位相がずれた場合は、そのずれに応じてカウンタ52のカウンタ値を1つ毎増加/減少させ位相のずれを解消する。但し、一旦、ロック検出信号がアサートされたら、制御信号PLL−resetがカウンタ52へ入力されない限りこのロック検出信号はネゲートされない。

【0040】

次に、PLL21内の位相同期部41の動作について説明する。図6は、位相同期部41の動作を示すタイミングチャートである。位相同期部41内では、逓倍部40から出力された4逓倍出力を、位相同期部41内に組み込まれた2つのデジタルディレイライン(第2の遅延回路)69および71で所定時間遅延させ、入力クロックの位相と制御信号P1Pの位相を一致させる動作を行う。位相同期部41はリセット直後は動作せず、逓倍部40内のロック検出回路60からロック検出信号がアサートされるとその動作を開始する。

【0041】

位相同期部41内のカウンタ(第2のカウンタ)65は、上位5ビット値でデジタルディレイライン69を、下位3ビット値でデジタルディレイライン71の動作を制御する。デジタルディレイライン71は、逓倍部40内のデジタルディレイライン56内で用いられている遅延素子を8個直列に接続した構成を有する。デジタルディレイライン69は、デジタルディレイライン71内の各遅延素子の約6〜8倍(この範囲は、温度、電圧、プロセス変動等に基づいて変動する)の遅延時間を有する遅延素子が32個直列に接続された構成を有する。

【0042】

位相同期部41では、デジタルディレイライン69が入力クロックの位相と制御信号P1Pの位相を大まかに合わせ、次に、デジタルディレイライン71が両者の位相を詳細に調整する。

【0043】

カウンタ65の初期値として、ロック検出回路60から出力されたロック検出信号がアサートされた時の、逓倍部40内のカウンタ52のカウンタ値がセットされる。入力クロックの立ち上がりエッジと制御信号P1Pの立ち上がりエッジの位相差により、カウンタ65のカウンタ値を1つ増加減少させ、両者の位相が一致したところで、カウンタ65のカウント動作は停止する。但し、一旦、カウント動作が停止した場合でも、温度、電圧、その他の影響で入力クロックの位相と制御信号P1Pの位相がずれた場合は、ずれの大きさに応じてカウンタ65のカウンタ値を1つ毎増加減少させ、両者の位相を一致させる。

【0044】

逓倍部40内のカウンタ52のカウンタ値を初期値として設定する意味は、位相同期部41の動作が開始された時、位相を早くする(カウンタ値を減算する)場合と、位相を遅くする(カウンタ値を加算する)場合の、いずれの方向に動作させても確実に同期するエッジを得るため、あらかじめ半周期分の遅延時間を持たせたことや、位相同期部41がロックした場合のデジタルディレイライン69の遅延時間を入力クロックの1周期以内に設定させ、確実にロックを行い高いロック性能を得るためである。仮に、位相同期部41のデジタルディレイライン69の遅延時間が2周期以上でロックしようとすると、逓倍部40内のカウンタ52又は位相同期部41内のカウンタ65の値の変化が制御信号P1Pに乗せられる以前に次の位相比較を実行することになるので、ロック動作が困難になりロック性能が低下することになる。

【0045】

次に、逓倍部40内や位相同期部41内に組み込まれているデジタルディレイライン56,69,71について説明する。

【0046】

図7は、デジタルディレイライン56,69,71のそれぞれの構成を示す回路図であり、図において、各遅延素子n(n=0,...y,y−1,...,n−1,n)は、直列に接続された2つのPMOSTrおよび直列に接続された2つのNMOSTrがさらに直列に接続されて得られる回路を2組並列に並べた構成を有する。PMOSTrの組とNMOSTrの組とを直列に接続する直列接続点は、各遅延素子の出力ノードと次段の遅延素子との間に設けられた出力インバータに接続されている。各遅延素子には入力として入力パルスを入力する入力ノードがある。逓倍部40内のデジタルディレイライン56は、この遅延素子を96個(即ち、n=95)直接に接続した構成を有し、位相同期部41内のデジタルディレイライン71は、遅延素子を8個(n=7)直列に接続した構成を、またデジタルディレイライン69は遅延素子を32個(n=31)直列に接続した構成を有している。

【0047】

次に、デジタルディレイラインの動作について説明する。カウンタ52,65から出力されるカウンタ値により、各デジタルディレイライン56,69,71内の所定の遅延素子が制御信号 ̄WL(n)により選択され、選択された遅延素子の入力ノードn(n=0,...y,y+1,...,n−1,n)から制御信号としての入力パルスが入力される。

【0048】

このように、入力パルスの入力位置を変えることにより、デジタルディレイライン56,69,71の遅延時間を調整する。入力位置を変える方式は、出力位置を変えてデジタルディレイラインの遅延時間を変化させる従来の方式と比較すると、特に高周波を用いる場合にスイッチングするトランジスタ数を減少できるからである。

【0049】

カウンタ52,65の各カウンタ値がyの場合、制御信号 ̄WL(y)が入力される遅延素子yの入力ノードyを介して入力パルスが遅延素子y内に入力されるが、この場合、2つの制御信号、即ち制御信号 ̄WL(y)および制御信号 ̄WL(y+1)がアサートされるので、遅延素子yと遅延素子y+1との2ヶ所から入力パルスが取り込まれるため、従来例で説明した図14のタイミングチャート内のタイミングT7からタイミングT8間に示すような出力aに不定な電位が乗る状態を確実に回避できる。

【0050】

以上のように、この実施の形態1によれば、第1の遅延回路および第2の遅延回路から構成され、第1の遅延回路および第2の遅延回路のそれぞれは、互いに直列に接続された複数個の遅延素子から構成され、第1の遅延回路あるいは第2の遅延回路に対応した第1のカウンタあるいは第2のカウンタから出力されるカウンタ値の値に応じて複数の遅延素子のいずれかの遅延素子が選択され、選択された遅延素子およびこれに隣接する遅延素子により遅延時間が設定され制御されるように構成したので、誤動作を防止でき、またこれを組み込んだクロック生成回路やDLL(Delay Locked Loop)の消費電力を低減することができる。

【0051】

また、この実施の形態1によれば、遅延素子のそれぞれが、直列に接続されたn個のPMOSTrの組および直列に接続されたn個のNMOSTrの組とをさらに互いに直列に接続させて得られる回路を2組並列に並べた構成を有し、n個のPMOSTrの組とn個のNMOSTrの組との接点に隣接するPMOSTrおよびNMOSTrのゲートを互いに接続するように構成したので、クロック生成回路の消費電力を低減することができる。

【0052】

さらに、この実施の形態1によれば、逓倍回路が、入力されたクロック信号の所定逓倍数のクロック信号を出力し(以下、出力クロックという)、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有し、位相同期回路が、逓倍回路内の第1の遅延回路から出力された出力クロックを入力し、出力クロックを所定時間遅延させる第2の遅延回路および第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有し、逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタ(1ビットのフリップフロップ)をさらに有し、第3のカウンタのカウンタ値が、第1の値から第2の値に変化した時、第2の遅延回路の遅延時間が第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように第2のカウンタのカウンタ値を設定するように構成したので、逓倍回路がロックした後に位相同期回路での初期状態を逓倍回路の1周期分かそれより少し大きくしてロックの精度を向上することができる。

【0053】

また、この実施の形態1によれば、デジタルディレイラインの遅延時間をカウンタで設定し、外部から供給されるリセット信号あるいは入力クロックの1周期の間に逓倍回路から出力される逓倍出力のパルス数が所望の逓倍数未満の場合、デジタルディレイラインの遅延時間を設定するカウンタのカウンタ値をリセットし、リセット直後のデジタルディレイラインの遅延時間が最小値となるようなカウンタ値に設定し、その後、徐々にデジタルディレイラインの遅延時間を増加するので、低電圧下でも制御が容易で、確実に所望の逓倍数で出力クロックをロックでき、またカウンタの初期状態がいかなる場合においても確実に正確な逓倍クロックを供給できる。さらに、デジタルディレイラインはカウンタで指定された遅延素子と隣接する遅延素子の2箇所から入力パルスを供給するので誤動作を防止でき、また消費電力を低減するとともに温度や電圧等の変動に対する補正能力を向上できる。

【産業上の利用可能性】

【0054】

以上のように、本発明にかかるクロック生成回路は、入力クロックを逓倍したクロックの生成に有用であり、特に、低電圧下においても制御可能な、ノイズに対する影響の少ない、正確で確実なクロックの生成に適している。

【符号の説明】

【0055】

20 クロック生成回路

40 逓倍部(逓倍回路)

41 位相同期部(位相同期回路)

52 カウンタ(第1のカウンタ)

56 デジタルディレイライン(第1の遅延回路)

59 ディレイ微調整回路(第1の遅延回路)

60 ロック検出回路(第3のカウンタ)

65 カウンタ(第2のカウンタ)

69,71 デジタルディレイライン(第2の遅延回路)

【特許請求の範囲】

【請求項1】

入力されたクロック信号(以下、入力クロックという)の所定逓倍数のクロック信号を出力し(以下、出力された所定逓倍数のクロック信号を出力クロックという)、前記出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定することを特徴とするクロック生成回路。

【請求項1】

入力されたクロック信号(以下、入力クロックという)の所定逓倍数のクロック信号を出力し(以下、出力された所定逓倍数のクロック信号を出力クロックという)、前記出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定することを特徴とするクロック生成回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2010−233226(P2010−233226A)

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願番号】特願2010−91689(P2010−91689)

【出願日】平成22年4月12日(2010.4.12)

【分割の表示】特願2007−68344(P2007−68344)の分割

【原出願日】平成10年1月23日(1998.1.23)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願日】平成22年4月12日(2010.4.12)

【分割の表示】特願2007−68344(P2007−68344)の分割

【原出願日】平成10年1月23日(1998.1.23)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]