クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば画像読取装置用駆動クロックを生成するための、遅延同期ループ回路(以下、DLL回路という。)を備えたクロック生成回路に関する。

【背景技術】

【0002】

DLL回路は、基準クロックと、電圧制御遅延線から出力された基準クロックに対して遅延クロックの遅延量をロックさせる回路であり、その遅延クロックを例えば画像読取装置のCCDに駆動クロックを供給する(例えば、特許文献1参照。)。

【0003】

また、特許文献2においては、「広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現ために、基準クロックを第1の個数の電圧制御遅延素子で遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子で遅延させて第2の遅延クロックを生成する遅延部と、上記基準クロックの位相と上記第1の遅延クロックの位相とを比較する位相比較部と、遅延制御電流を出力するチャージポンプと、遅延制御部と、上記基準クロックの位相と上記第2の遅延クロックの位相とを比較し、上記基準クロックと上記第1の遅延クロックとの位相差を判定する判定部と、上記位相差が閾値より大きい場合、上記遅延制御電流が第1の値になり、上記閾値以下の場合、上記第1の値より小さい第2の値になるように制御するチャージ制御部とを備えたことを特徴としている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、従来技術に係る回路構成が複雑でサイズが大きく、位相補正精度も比較的悪いという問題点があった。

【0005】

本発明の目的は以上の問題点を解決し、従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供することにある。

【課題を解決するための手段】

【0006】

本発明に係るクロック生成回路は、基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、

上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたことを特徴とする。

【0007】

上記クロック生成回路において、上記位相オフセット手段は、上記検出レベルが第1の値であるときはカウンタの計数値をインクリメントする一方、上記検出レベルが第2の値であるときはカウンタの計数値をインクリメントすることを禁止し、上記カウンタの計数値に基づいて、上記DLL回路の位相差に対応する位相オフセット補正の状態を時間的に平均化して判断し、上記判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御することを特徴とする。

【0008】

また、上記クロック生成回路において、上記位相オフセット手段は、上記複数の遅延素子に対して遅延量を増大させる第1のバイアス制御パルス及び遅延量を減少させる第2のバイアス制御パルスを制御してその遅延量を制御し、上記位相オフセット補正の値が負であるときは、上記第1のバイアス制御パルスの幅を増大する一方、上記位相オフセット補正の値が正であるときは、上記第2のバイアス制御パルスの幅を増大することにより、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する。

【0009】

さらに、上記クロック生成回路において、上記位相オフセット手段は、上記複数の遅延素子の中間段の遅延素子からの駆動クロックに基づいて、上記複数の遅延素子とはタップ幅が小さい複数の別の遅延素子を用いてバイアス制御パルスのためのタイミングクロックを生成し、当該タイミングクロックのタイミングで上記第1のバイアス制御パルス又は上記第2のバイアス制御パルスを生成することを特徴とする。

【発明の効果】

【0010】

従って、本発明によれば、基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたので、従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供できる。

【図面の簡単な説明】

【0011】

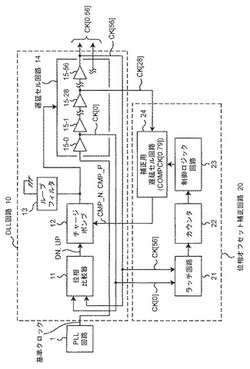

【図1】本発明の実施形態に係る画像読取装置のためのクロック生成回路の構成を示すブロック図である。

【図2】図1のチャージポンプ12の詳細構成を示す回路図である。

【図3】図1の位相オフセット補正回路20の概略動作を示すタイミングチャートであって、(a)は位相オフセット量Toffが正の場合のタイミングチャートであり、(b)は位相オフセット量Toffが負の場合のタイミングチャートである。

【図4】図1のクロック生成回路の位相オフセット補正前の動作を示すタイミングチャートである。

【図5】図1のクロック生成回路の位相オフセット補正中(その1)の動作を示すタイミングチャートである。

【図6】図1のクロック生成回路の位相オフセット補正中(その2)の動作を示すタイミングチャートである。

【図7】図1のクロック生成回路の位相オフセット補正完了時の動作を示すタイミングチャートである。

【図8】図1のクロック生成回路によって実行される位相オフセット補正処理を示すフローチャートである。

【発明を実施するための形態】

【0012】

以下、本発明に係る実施形態について図面を参照して説明する。なお、以下の各実施形態において、同様の構成要素については同一の符号を付している。

【0013】

図1は本発明の実施形態に係る画像読取装置のためのクロック生成回路の構成を示すブロック図である。図1のクロック生成回路は、PLL回路1と、DLL回路10と、位相オフセット補正回路20とを備えて構成され、特に、位相オフセット補正回路20を備えたことを特徴としている。ここで、DLL回路10は、位相比較器11と、チャージポンプ12と、例えば一端が接地されたキャパシタC13にてなるループフィルタ13と、例えば57個の電圧制御遅延素子(例えばインバータ)15−0〜15−56(各遅延量が例えば280ps)が縦続接続されてなる遅延セル回路14とを備えて構成される。また、位相オフセット補正回路20は、ラッチ回路21と、カウンタ22と、制御ロジック回路23と、補正用遅延セル回路24とを備えて構成される。ここで、補正用遅延セル回路24は、例えば80個の電圧制御遅延素子(各遅延量が例えば70ps)が縦続接続されてなる回路により、遅延セル回路14からの中間段の駆動クロックCK[28]に基づいて80個の補正制御パルスCOMPCK[0:79]を発生して、補正制御パルスCOMPCK[0:79]のタイミングで制御ロジック回路23からの制御によりパルス幅が制御されるポジティブ補正パルスCMP_P及びネガティブ補正パルスCMP_Nを発生してチャージポンプ12に出力する。

【0014】

図1において、PLL回路1からの基準クロックは、遅延セル回路14内の電圧制御遅延素子15−0に入力され、各電圧制御遅延素子15−0〜15−56により画像読取装置のためのCCD駆動クロックCK[0:56]を発生して出力する。初段の電圧制御遅延素子15−0から出力されるクロックCK[0]は位相比較器11及びラッチ回路21に出力され、中間段の電圧制御遅延素子15−28から出力されるクロックCK[28]は補正用遅延セル回路24に出力され、最終段の電圧制御遅延素子15−56から出力されるクロックCK[56]は位相比較器11及びラッチ回路21に出力される。位相比較器11は入力される2つのクロックの位相を比較し、その比較結果に基づいて、入力される2つのクロックの位相差を実質的に0になるようにするために、クロックCK[56]に対する移相量を所定値だけ大きくするときは(すなわち、実際には、すべてのクロック[0:56]の遅延量を大きくする)ダウンパルスDNをチャージポンプ12に出力し、クロックCK[56]に対する移相量を所定値だけ小さくするときは(すなわち、実際には、すべてのクロック[0:56]の遅延量を小さくする)アップパルスUPをチャージポンプ12に出力する。チャージポンプ12は、入力される4つのパルスに基づいて遅延セル回路14内の電圧制御遅延素子15−0〜15−56の駆動バイアス電圧BYPD(図2)を制御することで遅延量を変化させる。

【0015】

図2は図1のチャージポンプ12の詳細構成を示す回路図である。図2において、チャージポンプ12は、2個のオアゲート31,32と、電源電圧VDDと接地との間に縦続接続されたソース電流源33とスイッチ35,36とシンク電流源34とからなる直列回路とを備えて構成される。なお、C13はループフィルタ13のキャパシタである。位相比較器11からのダウンパルスDN又は補正用遅延セル回路24からのネガティブ補正パルスCMP_Nに応答して制御パルスSRCによりスイッチ35がオンとなり所定の正の駆動バイアス電圧が発生されて、遅延セル回路14内の電圧制御遅延素子15−0〜15−56に印加されて遅延量が大きくなり位相オフセット補正量が大きくなる。一方、位相比較器11からのアップパルスUP又は補正用遅延セル回路24からのポジティブ補正パルスCMP_Pに応答して制御パルスSNKによりスイッチ36がオンとなり所定の負の駆動バイアス電圧が発生されて、遅延セル回路14内の電圧制御遅延素子15−0〜15−56に印加されて遅延量が小さくなり位相オフセット補正量が小さくなる。ただし、図4〜図7を参照して動作説明するように、DLL回路10の制御ループにより最終的な位相オフセット補正量が決定される。ここで、位相オフセット補正量はDLL回路10の位相比較結果の位相差に対応する。

【0016】

図3は図1の位相オフセット補正回路20の概略動作を示すタイミングチャートであって、図3(a)は位相オフセット量Toffが正の場合のタイミングチャートであり、図3(b)は位相オフセット量Toffが負の場合のタイミングチャートである。

【0017】

図3(a)において、位相オフセット量Toffが正の場合、ラッチ回路21は、クロックCK[0]の立ち上がりエッジでクロックCK[56]をラッチし、LレベルであればパルスSNKの期間においてカウンタ22の計数値cntを1だけインクリメントする。この動作を例えば64回行う。これは、現実のクロックCK[0],CK[56]にはジッタが重畳されているので平均処理を行う動作が必要であるからである。なお、図3(b)において、位相オフセット量Toffが負の場合において、ラッチの結果がHレベルときはパルスSRCの期間においてカウンタ22の計数値cntをインクリメントせず禁止する。そして、カウンタ22の計数値cntから、位相オフセット量Toffの状態を以下のように判断する。ここで、カウンタ22の計数値cntに基づいて、判断しているのは、ノイズの影響を排除して時間的に平均化するためである。

【0018】

(a)cnt>32+Xのとき:位相オフセット量Toffは正である。

(b)32+X≧cnt≧32−Yのとき:位相オフセット量Toffは十分小さい。

(c)32−Y>cntのとき:位相オフセット量Toffは負である。

ここで、X及びYの値は各レジスタ設定で変更可能であり、0<X<32、0<Y<32の範囲で予め決定されて設定される。

【0019】

次いで、図2及び図4乃至図7を参照して図1のクロック生成回路(特に、図2のチャージポンプの位相オフセット補正処理の一例について以下に説明する。なお、補正のステップ幅は、好ましくはDLL回路10内の遅延セル回路14のタップ幅の1/4以下に設定する。また、補正の範囲は、例えば基準クロックが40MHzであるときに±4.0ns以上である。さらに、補正用遅延セル回路24は例えば互いに縦続接続された複数のインバータで構成され、補正のステップ幅は例えば80ps(最悪ケースで120ps)であり、補正の範囲は±6.4ns程度(最悪ケースで±4.0ns程度)である。

【0020】

本実施形態では、図2のソース電流源33及びシンク電流源34がそれぞれオンする期間をアップパルスUP及びダウンパルスDN以外に、補正パルスCMP_PもしくはCMP_N信号で調整することを特徴としている。補正パルスCMP_P,CMP_N信号の幅は、位相オフセット補正の制御ロジック回路23による検出結果により例えば以下のごとく増減される。

【0021】

図4は図1のクロック生成回路の位相オフセット補正前の動作を示すタイミングチャートである。補正前の図4は、アップパルスUPが出力されており、位相オフセット補正量Toffは正の場合である。位相オフセット補正量Toffが正なので、制御ロジック回路23はポジティブ補正パルスCMP_Pの幅を所定のステップ幅でインクリメントすると、図5のようになる。

【0022】

図5は図1のクロック生成回路の位相オフセット補正中(その1)の動作を示すタイミングチャートである。図5において、スイッチ35,36のチャージオフセットによるエラーを回避するために、この場合においてネガティブ補正パルスCMP_Nも最小幅分だけ生成することが好ましい。なお、ポジティブ補正パルスCMP_Pの幅は補正用遅延セル回路24により補正クロックCOMPCK[0:79]に基づいて作成される。図5の場合において、ポジティブ補正パルスCMP_Pのパルス幅を増大すると、DLL回路10内の制御ループはアップパルスUPのパルス幅を狭める方向に制御されるので、位相オフセット補正量Toffは0になる方向に減少される。さらに、同様の動作を続けて行くと、位相オフセット補正量Toffはさらに小さくなり、最終的にはDLL回路10の位相差を実質的に0に制御でき、図6のようになる。

【0023】

図6は図1のクロック生成回路の位相オフセット補正中(その2)の動作を示すタイミングチャートである。図6において、制御ロジック回路23は位相オフセット補正量Toffは所定のしきい値よりも小さく、十分に小さいと判断すると、図7のごとく補正動作は完了する。

【0024】

以上の図4〜図7はポジティブ補正パルスCMP_Pによる補正動作であるが、ネガティブ補正パルスCMP_Nによる補正動作も同様に動作する。すなわち、位相オフセット補正量Toffが負であるときに、ネガティブ補正パルスCMP_Nの幅を増大すると、DLL回路10内の制御ループはダウンパルスDNのパルス幅を狭める方向に制御されるので、位相オフセット補正量Toffは0になる方向に減少される。さらに、同様の動作を続けて行くと、位相オフセット補正量Toffはさらに小さくなり、DLL回路10の位相差を実質的に0に制御できる。

【0025】

図7は図1のクロック生成回路の位相オフセット補正完了時の動作を示すタイミングチャートである。図7において、位相オフセット補正量Toffがポジティブ補正パルスCMP_Pのパルス幅調整ステップの1ステップ幅未満になった状態で位相オフセット補正が完了する。

【0026】

図8は図1のクロック生成回路によって実行される位相オフセット補正処理を示すフローチャートである。

【0027】

図8において、ステップS1において電源がオンされたか否かについて判断し、YESのときはステップS2に進む一方、NOのときはステップS1に戻り電源がオンされるまでステップS1の処理を継続する。ステップS2において、DLL回路10はロック完了であるか否かが判断され、YESのときはステップS3に進む一方、NOのときはステップS2に戻る。ステップS3では、カウンタ22の計数値cnt及び検出回数パラメータkをそれぞれ0に初期化した後、ステップS4において検出回数パラメータkが64であるか否かが判断され、YESのときはステップS9に進む一方、NOのときはステップS5に進む。

【0028】

ステップS5において、ラッチ回路21は、クロックCK[0]の立ち上がりエッジでクロックCK[56]をラッチして、ステップS6で当該ラッチ値がLレベルであるか否かが判断され、YESのときはステップS7に進む一方、NOのときはステップS8に進む。ステップS7では、カウンタ22の計数値cntを1だけインクリメントした後、ステップS8で検出回数パラメータkを1だけインクリメントし、ステップS4に戻る。

【0029】

ステップS9では、カウンタ22の計数値cnt>X+32(ここで、XはレジスタXでの設定値であり、0<X<32である。)であるか否かが判断され、YESのときはステップS11に進む一方、NOのときはステップS10に進む。ステップS10では、カウンタ22の計数値cnt<32−Y(ここで、YはレジスタYでの設定値であり、0<Y<32である。)であるか否かが判断され、YESのときはステップS14に進む一方、NOのときは位相オフセット補正が完了していると判断して当該処理を終了する。

【0030】

ステップS11において、補正用遅延セル回路24から出力されるネガティブ補正パルスCMP_Nの幅が0であるか否かが判断され、YESのときはステップS12に進む一方、NOのときはステップS13に進む。ステップS12では、ポジティブ補正パルスCMP_Pの幅を所定のステップ幅(例えば、80ps)だけインクリメントした後、ステップS17に進む。また、ステップS13では、ネガティブ補正パルスCMP_Nの幅を上記ステップ幅だけデクリメントした後、ステップS17に進む。

【0031】

ステップS14において、補正用遅延セル回路24から出力されるポジティブ補正パルスCMP_Pの幅が0であるか否かが判断され、YESのときはステップS15に進む一方、NOのときはステップS16に進む。ステップS15では、ネガティブ補正パルスCMP_Nの幅を上記ステップ幅だけインクリメントした後、ステップS17に進む。また、ステップS16では、ポジティブ補正パルスCMP_Pの幅を上記ステップ幅だけデクリメントした後、ステップS17に進む。

【0032】

ステップS17では、カウンタ22の計数値cntを0にリセットし、所定の時間だけ待機した後、ステップS3に戻る。

【0033】

以上のようにして、図1のクロック生成回路において位相オフセット補正処理が実行される。これにより、DLL回路10の位相比較器11に入力されるクロックCK[0]とクロックCK「56]との間の位相差が実質的に0となるように位相オフセット補正される。

【産業上の利用可能性】

【0034】

以上詳述したように、本発明によれば、基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたので、従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供できる。

【0035】

なお、本発明に係るDLL回路を備えたクロック生成回路は、例えばディジタルカメラ又は複合機などの画像読取装置のCCDのための駆動クロックを生成するために用いられる。

【符号の説明】

【0036】

1…PLL回路、

10…DLL回路、

11…位相比較器、

12…チャージポンプ、

13…ループフィルタ、

14…遅延セル回路、

15−0〜15−56…電圧制御遅延素子、

20…位相オフセット補正回路、

21…ラッチ回路、

22…カウンタ、

23…制御ロジック回路、

24…補正用遅延セル回路、

31,32…オアゲート、

33…ソース電流源、

34…シンク電流源、

35,36…スイッチ、

C13…キャパシタ。

【先行技術文献】

【特許文献】

【0037】

【特許文献1】特許第3966012号公報

【特許文献2】特開2010−157923号公報

【技術分野】

【0001】

本発明は、例えば画像読取装置用駆動クロックを生成するための、遅延同期ループ回路(以下、DLL回路という。)を備えたクロック生成回路に関する。

【背景技術】

【0002】

DLL回路は、基準クロックと、電圧制御遅延線から出力された基準クロックに対して遅延クロックの遅延量をロックさせる回路であり、その遅延クロックを例えば画像読取装置のCCDに駆動クロックを供給する(例えば、特許文献1参照。)。

【0003】

また、特許文献2においては、「広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現ために、基準クロックを第1の個数の電圧制御遅延素子で遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子で遅延させて第2の遅延クロックを生成する遅延部と、上記基準クロックの位相と上記第1の遅延クロックの位相とを比較する位相比較部と、遅延制御電流を出力するチャージポンプと、遅延制御部と、上記基準クロックの位相と上記第2の遅延クロックの位相とを比較し、上記基準クロックと上記第1の遅延クロックとの位相差を判定する判定部と、上記位相差が閾値より大きい場合、上記遅延制御電流が第1の値になり、上記閾値以下の場合、上記第1の値より小さい第2の値になるように制御するチャージ制御部とを備えたことを特徴としている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、従来技術に係る回路構成が複雑でサイズが大きく、位相補正精度も比較的悪いという問題点があった。

【0005】

本発明の目的は以上の問題点を解決し、従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供することにある。

【課題を解決するための手段】

【0006】

本発明に係るクロック生成回路は、基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、

上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたことを特徴とする。

【0007】

上記クロック生成回路において、上記位相オフセット手段は、上記検出レベルが第1の値であるときはカウンタの計数値をインクリメントする一方、上記検出レベルが第2の値であるときはカウンタの計数値をインクリメントすることを禁止し、上記カウンタの計数値に基づいて、上記DLL回路の位相差に対応する位相オフセット補正の状態を時間的に平均化して判断し、上記判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御することを特徴とする。

【0008】

また、上記クロック生成回路において、上記位相オフセット手段は、上記複数の遅延素子に対して遅延量を増大させる第1のバイアス制御パルス及び遅延量を減少させる第2のバイアス制御パルスを制御してその遅延量を制御し、上記位相オフセット補正の値が負であるときは、上記第1のバイアス制御パルスの幅を増大する一方、上記位相オフセット補正の値が正であるときは、上記第2のバイアス制御パルスの幅を増大することにより、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する。

【0009】

さらに、上記クロック生成回路において、上記位相オフセット手段は、上記複数の遅延素子の中間段の遅延素子からの駆動クロックに基づいて、上記複数の遅延素子とはタップ幅が小さい複数の別の遅延素子を用いてバイアス制御パルスのためのタイミングクロックを生成し、当該タイミングクロックのタイミングで上記第1のバイアス制御パルス又は上記第2のバイアス制御パルスを生成することを特徴とする。

【発明の効果】

【0010】

従って、本発明によれば、基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたので、従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供できる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施形態に係る画像読取装置のためのクロック生成回路の構成を示すブロック図である。

【図2】図1のチャージポンプ12の詳細構成を示す回路図である。

【図3】図1の位相オフセット補正回路20の概略動作を示すタイミングチャートであって、(a)は位相オフセット量Toffが正の場合のタイミングチャートであり、(b)は位相オフセット量Toffが負の場合のタイミングチャートである。

【図4】図1のクロック生成回路の位相オフセット補正前の動作を示すタイミングチャートである。

【図5】図1のクロック生成回路の位相オフセット補正中(その1)の動作を示すタイミングチャートである。

【図6】図1のクロック生成回路の位相オフセット補正中(その2)の動作を示すタイミングチャートである。

【図7】図1のクロック生成回路の位相オフセット補正完了時の動作を示すタイミングチャートである。

【図8】図1のクロック生成回路によって実行される位相オフセット補正処理を示すフローチャートである。

【発明を実施するための形態】

【0012】

以下、本発明に係る実施形態について図面を参照して説明する。なお、以下の各実施形態において、同様の構成要素については同一の符号を付している。

【0013】

図1は本発明の実施形態に係る画像読取装置のためのクロック生成回路の構成を示すブロック図である。図1のクロック生成回路は、PLL回路1と、DLL回路10と、位相オフセット補正回路20とを備えて構成され、特に、位相オフセット補正回路20を備えたことを特徴としている。ここで、DLL回路10は、位相比較器11と、チャージポンプ12と、例えば一端が接地されたキャパシタC13にてなるループフィルタ13と、例えば57個の電圧制御遅延素子(例えばインバータ)15−0〜15−56(各遅延量が例えば280ps)が縦続接続されてなる遅延セル回路14とを備えて構成される。また、位相オフセット補正回路20は、ラッチ回路21と、カウンタ22と、制御ロジック回路23と、補正用遅延セル回路24とを備えて構成される。ここで、補正用遅延セル回路24は、例えば80個の電圧制御遅延素子(各遅延量が例えば70ps)が縦続接続されてなる回路により、遅延セル回路14からの中間段の駆動クロックCK[28]に基づいて80個の補正制御パルスCOMPCK[0:79]を発生して、補正制御パルスCOMPCK[0:79]のタイミングで制御ロジック回路23からの制御によりパルス幅が制御されるポジティブ補正パルスCMP_P及びネガティブ補正パルスCMP_Nを発生してチャージポンプ12に出力する。

【0014】

図1において、PLL回路1からの基準クロックは、遅延セル回路14内の電圧制御遅延素子15−0に入力され、各電圧制御遅延素子15−0〜15−56により画像読取装置のためのCCD駆動クロックCK[0:56]を発生して出力する。初段の電圧制御遅延素子15−0から出力されるクロックCK[0]は位相比較器11及びラッチ回路21に出力され、中間段の電圧制御遅延素子15−28から出力されるクロックCK[28]は補正用遅延セル回路24に出力され、最終段の電圧制御遅延素子15−56から出力されるクロックCK[56]は位相比較器11及びラッチ回路21に出力される。位相比較器11は入力される2つのクロックの位相を比較し、その比較結果に基づいて、入力される2つのクロックの位相差を実質的に0になるようにするために、クロックCK[56]に対する移相量を所定値だけ大きくするときは(すなわち、実際には、すべてのクロック[0:56]の遅延量を大きくする)ダウンパルスDNをチャージポンプ12に出力し、クロックCK[56]に対する移相量を所定値だけ小さくするときは(すなわち、実際には、すべてのクロック[0:56]の遅延量を小さくする)アップパルスUPをチャージポンプ12に出力する。チャージポンプ12は、入力される4つのパルスに基づいて遅延セル回路14内の電圧制御遅延素子15−0〜15−56の駆動バイアス電圧BYPD(図2)を制御することで遅延量を変化させる。

【0015】

図2は図1のチャージポンプ12の詳細構成を示す回路図である。図2において、チャージポンプ12は、2個のオアゲート31,32と、電源電圧VDDと接地との間に縦続接続されたソース電流源33とスイッチ35,36とシンク電流源34とからなる直列回路とを備えて構成される。なお、C13はループフィルタ13のキャパシタである。位相比較器11からのダウンパルスDN又は補正用遅延セル回路24からのネガティブ補正パルスCMP_Nに応答して制御パルスSRCによりスイッチ35がオンとなり所定の正の駆動バイアス電圧が発生されて、遅延セル回路14内の電圧制御遅延素子15−0〜15−56に印加されて遅延量が大きくなり位相オフセット補正量が大きくなる。一方、位相比較器11からのアップパルスUP又は補正用遅延セル回路24からのポジティブ補正パルスCMP_Pに応答して制御パルスSNKによりスイッチ36がオンとなり所定の負の駆動バイアス電圧が発生されて、遅延セル回路14内の電圧制御遅延素子15−0〜15−56に印加されて遅延量が小さくなり位相オフセット補正量が小さくなる。ただし、図4〜図7を参照して動作説明するように、DLL回路10の制御ループにより最終的な位相オフセット補正量が決定される。ここで、位相オフセット補正量はDLL回路10の位相比較結果の位相差に対応する。

【0016】

図3は図1の位相オフセット補正回路20の概略動作を示すタイミングチャートであって、図3(a)は位相オフセット量Toffが正の場合のタイミングチャートであり、図3(b)は位相オフセット量Toffが負の場合のタイミングチャートである。

【0017】

図3(a)において、位相オフセット量Toffが正の場合、ラッチ回路21は、クロックCK[0]の立ち上がりエッジでクロックCK[56]をラッチし、LレベルであればパルスSNKの期間においてカウンタ22の計数値cntを1だけインクリメントする。この動作を例えば64回行う。これは、現実のクロックCK[0],CK[56]にはジッタが重畳されているので平均処理を行う動作が必要であるからである。なお、図3(b)において、位相オフセット量Toffが負の場合において、ラッチの結果がHレベルときはパルスSRCの期間においてカウンタ22の計数値cntをインクリメントせず禁止する。そして、カウンタ22の計数値cntから、位相オフセット量Toffの状態を以下のように判断する。ここで、カウンタ22の計数値cntに基づいて、判断しているのは、ノイズの影響を排除して時間的に平均化するためである。

【0018】

(a)cnt>32+Xのとき:位相オフセット量Toffは正である。

(b)32+X≧cnt≧32−Yのとき:位相オフセット量Toffは十分小さい。

(c)32−Y>cntのとき:位相オフセット量Toffは負である。

ここで、X及びYの値は各レジスタ設定で変更可能であり、0<X<32、0<Y<32の範囲で予め決定されて設定される。

【0019】

次いで、図2及び図4乃至図7を参照して図1のクロック生成回路(特に、図2のチャージポンプの位相オフセット補正処理の一例について以下に説明する。なお、補正のステップ幅は、好ましくはDLL回路10内の遅延セル回路14のタップ幅の1/4以下に設定する。また、補正の範囲は、例えば基準クロックが40MHzであるときに±4.0ns以上である。さらに、補正用遅延セル回路24は例えば互いに縦続接続された複数のインバータで構成され、補正のステップ幅は例えば80ps(最悪ケースで120ps)であり、補正の範囲は±6.4ns程度(最悪ケースで±4.0ns程度)である。

【0020】

本実施形態では、図2のソース電流源33及びシンク電流源34がそれぞれオンする期間をアップパルスUP及びダウンパルスDN以外に、補正パルスCMP_PもしくはCMP_N信号で調整することを特徴としている。補正パルスCMP_P,CMP_N信号の幅は、位相オフセット補正の制御ロジック回路23による検出結果により例えば以下のごとく増減される。

【0021】

図4は図1のクロック生成回路の位相オフセット補正前の動作を示すタイミングチャートである。補正前の図4は、アップパルスUPが出力されており、位相オフセット補正量Toffは正の場合である。位相オフセット補正量Toffが正なので、制御ロジック回路23はポジティブ補正パルスCMP_Pの幅を所定のステップ幅でインクリメントすると、図5のようになる。

【0022】

図5は図1のクロック生成回路の位相オフセット補正中(その1)の動作を示すタイミングチャートである。図5において、スイッチ35,36のチャージオフセットによるエラーを回避するために、この場合においてネガティブ補正パルスCMP_Nも最小幅分だけ生成することが好ましい。なお、ポジティブ補正パルスCMP_Pの幅は補正用遅延セル回路24により補正クロックCOMPCK[0:79]に基づいて作成される。図5の場合において、ポジティブ補正パルスCMP_Pのパルス幅を増大すると、DLL回路10内の制御ループはアップパルスUPのパルス幅を狭める方向に制御されるので、位相オフセット補正量Toffは0になる方向に減少される。さらに、同様の動作を続けて行くと、位相オフセット補正量Toffはさらに小さくなり、最終的にはDLL回路10の位相差を実質的に0に制御でき、図6のようになる。

【0023】

図6は図1のクロック生成回路の位相オフセット補正中(その2)の動作を示すタイミングチャートである。図6において、制御ロジック回路23は位相オフセット補正量Toffは所定のしきい値よりも小さく、十分に小さいと判断すると、図7のごとく補正動作は完了する。

【0024】

以上の図4〜図7はポジティブ補正パルスCMP_Pによる補正動作であるが、ネガティブ補正パルスCMP_Nによる補正動作も同様に動作する。すなわち、位相オフセット補正量Toffが負であるときに、ネガティブ補正パルスCMP_Nの幅を増大すると、DLL回路10内の制御ループはダウンパルスDNのパルス幅を狭める方向に制御されるので、位相オフセット補正量Toffは0になる方向に減少される。さらに、同様の動作を続けて行くと、位相オフセット補正量Toffはさらに小さくなり、DLL回路10の位相差を実質的に0に制御できる。

【0025】

図7は図1のクロック生成回路の位相オフセット補正完了時の動作を示すタイミングチャートである。図7において、位相オフセット補正量Toffがポジティブ補正パルスCMP_Pのパルス幅調整ステップの1ステップ幅未満になった状態で位相オフセット補正が完了する。

【0026】

図8は図1のクロック生成回路によって実行される位相オフセット補正処理を示すフローチャートである。

【0027】

図8において、ステップS1において電源がオンされたか否かについて判断し、YESのときはステップS2に進む一方、NOのときはステップS1に戻り電源がオンされるまでステップS1の処理を継続する。ステップS2において、DLL回路10はロック完了であるか否かが判断され、YESのときはステップS3に進む一方、NOのときはステップS2に戻る。ステップS3では、カウンタ22の計数値cnt及び検出回数パラメータkをそれぞれ0に初期化した後、ステップS4において検出回数パラメータkが64であるか否かが判断され、YESのときはステップS9に進む一方、NOのときはステップS5に進む。

【0028】

ステップS5において、ラッチ回路21は、クロックCK[0]の立ち上がりエッジでクロックCK[56]をラッチして、ステップS6で当該ラッチ値がLレベルであるか否かが判断され、YESのときはステップS7に進む一方、NOのときはステップS8に進む。ステップS7では、カウンタ22の計数値cntを1だけインクリメントした後、ステップS8で検出回数パラメータkを1だけインクリメントし、ステップS4に戻る。

【0029】

ステップS9では、カウンタ22の計数値cnt>X+32(ここで、XはレジスタXでの設定値であり、0<X<32である。)であるか否かが判断され、YESのときはステップS11に進む一方、NOのときはステップS10に進む。ステップS10では、カウンタ22の計数値cnt<32−Y(ここで、YはレジスタYでの設定値であり、0<Y<32である。)であるか否かが判断され、YESのときはステップS14に進む一方、NOのときは位相オフセット補正が完了していると判断して当該処理を終了する。

【0030】

ステップS11において、補正用遅延セル回路24から出力されるネガティブ補正パルスCMP_Nの幅が0であるか否かが判断され、YESのときはステップS12に進む一方、NOのときはステップS13に進む。ステップS12では、ポジティブ補正パルスCMP_Pの幅を所定のステップ幅(例えば、80ps)だけインクリメントした後、ステップS17に進む。また、ステップS13では、ネガティブ補正パルスCMP_Nの幅を上記ステップ幅だけデクリメントした後、ステップS17に進む。

【0031】

ステップS14において、補正用遅延セル回路24から出力されるポジティブ補正パルスCMP_Pの幅が0であるか否かが判断され、YESのときはステップS15に進む一方、NOのときはステップS16に進む。ステップS15では、ネガティブ補正パルスCMP_Nの幅を上記ステップ幅だけインクリメントした後、ステップS17に進む。また、ステップS16では、ポジティブ補正パルスCMP_Pの幅を上記ステップ幅だけデクリメントした後、ステップS17に進む。

【0032】

ステップS17では、カウンタ22の計数値cntを0にリセットし、所定の時間だけ待機した後、ステップS3に戻る。

【0033】

以上のようにして、図1のクロック生成回路において位相オフセット補正処理が実行される。これにより、DLL回路10の位相比較器11に入力されるクロックCK[0]とクロックCK「56]との間の位相差が実質的に0となるように位相オフセット補正される。

【産業上の利用可能性】

【0034】

以上詳述したように、本発明によれば、基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたので、従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供できる。

【0035】

なお、本発明に係るDLL回路を備えたクロック生成回路は、例えばディジタルカメラ又は複合機などの画像読取装置のCCDのための駆動クロックを生成するために用いられる。

【符号の説明】

【0036】

1…PLL回路、

10…DLL回路、

11…位相比較器、

12…チャージポンプ、

13…ループフィルタ、

14…遅延セル回路、

15−0〜15−56…電圧制御遅延素子、

20…位相オフセット補正回路、

21…ラッチ回路、

22…カウンタ、

23…制御ロジック回路、

24…補正用遅延セル回路、

31,32…オアゲート、

33…ソース電流源、

34…シンク電流源、

35,36…スイッチ、

C13…キャパシタ。

【先行技術文献】

【特許文献】

【0037】

【特許文献1】特許第3966012号公報

【特許文献2】特開2010−157923号公報

【特許請求の範囲】

【請求項1】

基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、

上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたことを特徴とするクロック生成回路。

【請求項2】

上記位相オフセット手段は、上記検出レベルが第1の値であるときはカウンタの計数値をインクリメントする一方、上記検出レベルが第2の値であるときはカウンタの計数値をインクリメントすることを禁止し、上記カウンタの計数値に基づいて、上記DLL回路の位相差に対応する位相オフセット補正の状態を時間的に平均化して判断し、上記判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御することを特徴とする請求項1記載のクロック生成回路。

【請求項3】

上記位相オフセット手段は、上記複数の遅延素子に対して遅延量を増大させる第1のバイアス制御パルス及び遅延量を減少させる第2のバイアス制御パルスを制御してその遅延量を制御し、上記位相オフセット補正の値が負であるときは、上記第1のバイアス制御パルスの幅を増大する一方、上記位相オフセット補正の値が正であるときは、上記第2のバイアス制御パルスの幅を増大することにより、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する請求項1又は2記載のクロック生成回路。

【請求項4】

上記位相オフセット手段は、上記複数の遅延素子の中間段の遅延素子からの駆動クロックに基づいて、上記複数の遅延素子とはタップ幅が小さい複数の別の遅延素子を用いてバイアス制御パルスのためのタイミングクロックを生成し、当該タイミングクロックのタイミングで上記第1のバイアス制御パルス又は上記第2のバイアス制御パルスを生成することを特徴とする請求項3記載のクロック生成回路。

【請求項1】

基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、

上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えたことを特徴とするクロック生成回路。

【請求項2】

上記位相オフセット手段は、上記検出レベルが第1の値であるときはカウンタの計数値をインクリメントする一方、上記検出レベルが第2の値であるときはカウンタの計数値をインクリメントすることを禁止し、上記カウンタの計数値に基づいて、上記DLL回路の位相差に対応する位相オフセット補正の状態を時間的に平均化して判断し、上記判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御することを特徴とする請求項1記載のクロック生成回路。

【請求項3】

上記位相オフセット手段は、上記複数の遅延素子に対して遅延量を増大させる第1のバイアス制御パルス及び遅延量を減少させる第2のバイアス制御パルスを制御してその遅延量を制御し、上記位相オフセット補正の値が負であるときは、上記第1のバイアス制御パルスの幅を増大する一方、上記位相オフセット補正の値が正であるときは、上記第2のバイアス制御パルスの幅を増大することにより、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する請求項1又は2記載のクロック生成回路。

【請求項4】

上記位相オフセット手段は、上記複数の遅延素子の中間段の遅延素子からの駆動クロックに基づいて、上記複数の遅延素子とはタップ幅が小さい複数の別の遅延素子を用いてバイアス制御パルスのためのタイミングクロックを生成し、当該タイミングクロックのタイミングで上記第1のバイアス制御パルス又は上記第2のバイアス制御パルスを生成することを特徴とする請求項3記載のクロック生成回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−195682(P2012−195682A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−56730(P2011−56730)

【出願日】平成23年3月15日(2011.3.15)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月15日(2011.3.15)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]