クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロック発振回路に関するものであり、特に発振周波数のトリミングを行う機能を備えたクロック発振回路に関するものである。

【背景技術】

【0002】

CPU(Central Processing Unit)等の動作クロックを生成する装置として、セラミック振動子や水晶発振器等が存在する。これらの装置は、周波数精度は高いがサイズが比較的大きいため、小型の電子装置、例えばデジタルカメラや携帯電話等に内蔵するには不向きである。このため近年、比較的小型であるCR発振回路を用いた、クロック発振回路が実用化されている。

【0003】

上記の一例として、クロック信号を出力する発振部と、外部入力される校正クロック信号を基準として発振部の発振周波数を計測する周波数計測回路と、計測結果に基づいて発振部の発振周波数を調整するトリミング制御回路と、を備えたクロック発振回路が開示・提案されている(例えば特許文献1を参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−341119号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながらCR発振回路は、装置特性や温度条件等により発振周波数にばらつきが生じ易く、周波数精度が高いとはいえない。このため、高精度の発振周波数が要求される電子装置では、例えばCR発振回路の外部に調整用の素子を設けたり、或いは電子装置の製造段階において水晶発振器等を外部接続して周波数調整動作を行ったりする必要があった。

【0006】

本発明は、本願の発明者により見出された上記の問題点に鑑み、発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明に係るクロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を出力する発振部と、前記クロック信号の発振周波数を計測する第1カウンタと、外部より与えられる基準クロック信号の発振周波数を計測する第2カウンタと、前記第1カウンタの計測値と前記第2カウンタの計測値とを比較する比較回路と、前記クロック信号の発振周波数と前記基準クロック信号の発振周波数とが一致するように、前記比較回路の出力をモニタしながら、前記周波数調整コードの自動探索を行う周波数調整コード探索回路と、自動探索済みの前記周波数調整コードを格納するレジスタと、を有し、前記発振部は、通常動作時において、前記レジスタに格納された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、周波数調整動作時において、前記周波数調整コード探索回路により設定された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定することを特徴とする構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成るクロック発振回路は、前記周波数調整コード探索回路が、前記周波数調整動作時において、前記クロック発振回路の外部に対する前記クロック信号の出力を停止するよう前記発振部を制御することを特徴とする構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成るクロック発振回路は、前記周波数調整コード探索回路が、前記周波数調整動作時において、前記比較回路の出力に基づいて前記周波数調整コードを更新する更新動作と、更新後の前記周波数調整コードを前記発振部に設定する設定動作とを、予め定められた回数だけ繰り返し行うことを特徴とする構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成るクロック発振回路は、前記発振部が、mビット(mは自然数)の前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、前記周波数調整コード探索回路は、前記更新動作と前記設定動作との繰り返しをm回行い、1回の前記更新動作において前記比較回路の出力を前記周波数調整コードの1ビットに反映することを特徴とする構成(第4の構成)にするとよい。

【0011】

また、上記第4の構成から成るクロック発振回路は、前記周波数調整コード探索回路が、自動探索済みの前記周波数調整コードを前記レジスタに格納した後、前記周波数調整コードの読み出しを許可するフラグを設定することを特徴とする構成(第5の構成)にするとよい。

【発明の効果】

【0012】

本発明によれば、通常動作を行うための動作系統と、発振周波数のクロックトリミングを行う周波数調整動作を行うための動作系統との二系統を備え、通常動作時においてクロックトリミングが不要であるクロック発振回路を提供することができる。

【0013】

また本発明によれば、周波数調整動作時において、クロック発振回路の外部装置に対して動作限界を超えるクロック信号が供給される事態を回避することが可能なクロック発振回路を提供することができる。

【図面の簡単な説明】

【0014】

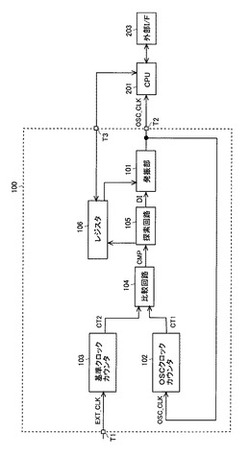

【図1】本発明に係るクロック発振回路を含んだ電子装置を示すブロック図

【図2】本発明に係るクロック発振回路を示すブロック図

【図3】発振周波数のカウントタイミングを示す模式図

【図4】その他の実施形態に係るクロック発振回路を示すブロック図

【発明を実施するための形態】

【0015】

<装置構成>

図1は、本発明のクロック発振回路を備える電子装置の、内部構成の一例を示す図である。本構成例の電子装置は、例えば携帯電話やデジタルカメラのような、携帯可能な程度に小型であり、且つ高精度のCPU処理が要求される装置を想定している。

【0016】

本構成例の電子装置は、クロック発振回路100と、CPU(Central Processing Unit)201と、ROM(Read Only Memory)202と、外部I/F203と、I2Cバス204とを有する。また、発振周波数の調整に用いるOSC(Oscillator)として、水晶発振器301をクロック発振回路100に外部接続可能である。

【0017】

なお水晶発振器301は、クロック発振回路100の周波数調整時において一時的に用いられる装置である。従って、一般ユーザがクロック発振回路100を備えた電子装置を使用する段階では、水晶発振器301はクロック発振回路100に接続されていない。

【0018】

クロック発振回路100は、不図示のCR発振回路を用いて、CPU201を動作させるためのクロック信号(OSC_CLK)を生成して出力する。なお、クロック発振回路100の内部構成については後述する。

【0019】

CPU201は、データの演算処理を行うロジック回路である。CPU201は、所定のコマンドをクロック発振回路100へ送信する。これを受けたクロック発振回路100は、受信したコマンドに基づき、後述する周波数調整動作やクロック生成動作を実施する。

【0020】

ROM202は、CPU201が実行するシステムプログラムや、クロック発振回路100の動作に関連する各種設定情報等を記録した、不揮発性の記録媒体である。なおROM202は、書き換え可能な不揮発性半導体メモリを含む構成でもよい。

【0021】

外部I/F203(インタフェース部)は、I2Cバス204を介して外部の装置と通信を行うためのインタフェースである。

【0022】

水晶発振器301は、発振周波数の調整時において、クロック発振回路100に対してEXT_CLKを与える。なお、EXT_CLKの発振周波数は、電子装置に要求される動作精度に応じて、電子装置の設計段階等において決定される。本実施形態では一例として、4.5MHzの発振周波数を用いるものとする。

【0023】

<クロック発振回路の構成>

次に、クロック発振回路100の内部構成について、図2を用いつつ説明する。図2は、本発明のクロック発振回路の内部構成の一例を示す図である。クロック発振回路100は、発振部101と、OSCクロックカウンタ102(第1カウンタ)と、基準クロックカウンタ103(第2カウンタ)と、比較回路104と、探索回路105(周波数調整コード探索回路)と、レジスタ106と、を集積化した半導体集積回路装置である。

【0024】

またクロック発振回路100は、外部との電気的な接続を確立するために、外部端子T1〜T3を有する。外部端子T1は、発振周波数の調整時において、水晶発振器301により生成される基準クロック信号(EXT_CLK)を入力する入力端子である。外部端子T2は、OSC_CLKの出力端子である。外部端子T3は、レジスタ106をCPU201に接続するための入出力端子である。

【0025】

発振部101の入力端は、探索回路105と、レジスタ106とに接続されている。発振部101の出力端は、OSCクロックカウンタ102に接続されている。また、外部端子T2を介して、CPU201に接続されている。OSCクロックカウンタ102の出力端は、比較回路104に接続されている。基準クロックカウンタ103の入力端は、外部端子T1に接続されている。比較回路104の出力端は、探索回路105に接続されている。探索回路105の出力端は、発振部101とレジスタ106とに接続されている。レジスタ106の入出力端は、外部端子T3を介して、CPU201に接続されている。またレジスタ106の出力端は、発振部101に接続されている。

【0026】

発振部101は、不図示のCR発振回路を有する。発振部101は、後述する周波数調整コードに基づいてCR発振回路の抵抗(R)部分を調整することにより、発振周波数を変化させる。なお本実施形態では、8ビットのR−2RラダーからなるCR発振回路を用いる。このため、周波数調整コードとして8ビットのデータを用いる。

【0027】

OSCクロックカウンタ102は、発振部101により生成されるクロック信号であるOSC_CLKを入力し、発振周波数のカウントを行う。そしてカウントされた値を示す信号(CT1)を、比較回路104へ送る。

【0028】

標準クロックカウンタ103は、水晶発振器301により生成される基準クロック信号であるEXT_CLKを入力し、発振周波数のカウントを行う。そしてカウントされた値を示す信号(CT2)を、比較回路104へ送る。

【0029】

比較回路104は、CT1とCT2とを比較し、比較結果を示す信号(CMP)を探索回路105へ送る。なおCMPは、CT1とCT2との大小関係を示す情報である。

【0030】

探索回路105は、比較回路104より入力されるCMPを参照しつつ、CT1とCT2とが一致するように発振部101の発振周波数を調整する。これにより、周波数調整コードの探索を行う。そして探索した周波数調整コードを、レジスタ106に格納する。本実施形態では、8ビットの周波数調整コードを用いるため、8回の比較及び調整による探索処理を行う。なお、探索処理の詳細については後述する。

【0031】

レジスタ106は、上述の周波数調整コードを記録するための揮発性の記録媒体である。レジスタ106は、探索回路105により探索された周波数調整コードが格納され、CPU201により読み出される。また、CPU201により探索済みの周波数調整コードが格納され、発振部101により読み出される。発振部101は、通常動作時において、レジスタ106より読み出した周波数調整コードを用いて、発振周波数の設定を行う。

【0032】

<クロック発振回路の動作>

次に、クロック発振回路100の動作について説明する。本実施形態のクロック発振回路100は、クロック発振回路100を備える電子装置の電源が投入された段階で、動作を開始する。クロック発振回路100の動作は、周波数調整動作と、通常動作との二つに大別される。何れの動作を行うかは、例えばCPU201に電気的に接続されたディップスイッチや、或いは不図示のフラッシュメモリに予め記録されている動作設定情報等により決定する。ここではまず、周波数調整動作について説明する。

【0033】

クロック発振回路100の周波数調整は、電子装置の工場出荷前に実施される。周波数調整動作を行うにあたっては、まずクロック発振回路100に水晶発振器301が外部接続される。

【0034】

この状態において電源が投入されると、CPU201は、発振部101より入力される未調整のクロック信号による仮動作を開始する。なお未調整のクロック信号の発振周波数は、CPU201がオーバークロックとならない程度に低くなるよう、予め設定されているものとする。

【0035】

仮動作を開始したCPU201は、ROM202より、予め用意されている周波数調整用のプログラムを読み出し、実行する。このプログラムの実行後、周波数調整コード探索指令を含むI2Cコマンドが送信されると、CPU201からクロック発振回路100に対して、周波数調整コード探索指令が送信される。

【0036】

この周波数調整コード探索指令がCPU201から送信されると、不図示の管理レジスタのフラグ情報が書き換えられ、周波数調整開始を示すフラグがONになる。

【0037】

探索回路105は、定期的にこの管理レジスタを監視しており、上記フラグがONになったのを検知した段階で、周波数調整コードの探索処理を開始する。なおこの探索処理はハードウェアロジックによって行われる。

【0038】

周波数調整コードの探索処理が開始されると、探索回路105は発振部101に対して、試験用の周波数調整コード(OSC_DI)を示す設定信号(DI)を送信する。OSC_DIは、通常の周波数調整コードと同じく8ビットの情報であり、その初期値は最大値と最小値との中間値、つまり2進数表記では0b1000_0000、10進数表記では0d128である。

【0039】

DIを受けた発振部101は、発振部101に含まれるCR発振回路に対してOSC_DIの設定を行う。これによりCR発振回路に含まれる8ビットのR−2Rラダー部の調整が行われ、OSC_CLKの発振周波数が決定される。なお発振周波数は、OSC_DIが大きい程高く、小さい程低くなるように設定される。

【0040】

この状態で発振部101がOSC_CLKの生成を行うと、OSC_CLKはOSCクロックカウンタ102に送られ、発振周波数のカウントが行われる。カウント結果を示すCT1は比較回路104へ送られる。

【0041】

またあわせて、基準クロックカウンタ103は、T1を介して水晶発振器301から入力されるEXT_CLKのカウントを行う。カウント結果を示すCT2は比較回路104へ送られる。なお、OSCクロックカウンタ102と基準クロックカウンタ103とがカウントを開始するタイミングは、探索回路105が探索処理を開始する際に生成するトリミング開始信号(START)により同期される。

【0042】

比較器104はCT1の値とCT2の値とを比較し、比較結果を示すCMPを探索回路105へ送信する。これを受けた探索回路105は、CMPが「CT1>CT2」を示す場合に、OSC_DIの最上位ビットを0に確定する。逆にCMPが「CT1≦CT2」を示す場合に、OSC_DIの最上位ビットを1に確定する。

【0043】

なお、このようにCMPに応じて数値を変更する対象ビットを、以降は比較ビットという。1回目の比較ビットはOSC_DIの最上位ビットであり、2回目以降の比較ビットは、前回の比較ビットの下位ビットにあたる。つまり2回目の比較ビットは第6ビットであり、8回目の比較ビットは第0ビットとなる。

【0044】

1回目の比較が完了すると、探索回路105は、比較ビットを一つ下位のビットに移す。比較ビットはまず1に設定される。従って例えば、1回目の比較結果が「CT1>CT2」であった場合、第7ビットが「0」に設定され、第6ビットが「1」に設定されるため、この時点でのOSC_DIは0b0100_0000(0d63)となる。探索回路105はこのOSC_DIを発振部101に設定する。そしてOSC_CLKの生成、カウント、比較が再度行われる。

【0045】

以上の繰り返しを、第7ビットから第0ビットまでの8回行う。この結果、最終的に得られたOSC_DIを、周波数調整コードとしてレジスタ106に格納する。併せて探索回路105は、不図示の管理レジスタのフラグ情報が書き換え、周波数調整が終了したことを示すフラグをONにする。

【0046】

上記の探索処理の具体的な処理タイミング及び数値を示した一例を、図3を用いて説明する。図3の最上段のSTARTは、探索回路105が探索処理を開始する際に生成するトリミング開始信号である。

【0047】

その下段のENDは、周波数調整の終了タイミングをとるためのトリミング停止信号である。トリミング停止信号は、トリミング開始信号がONになってから所定時間後に、探索回路105によりOFFされる。

【0048】

ENDの下段のREF_CNTは、基準クロックカウンタ103のカウント数を示している。その下段のVOC_CNTは、OSCクロックカウンタ102のカウント数を示している。最下段のOSC_DIは、上述の試験用の周波数調整コードである。

【0049】

本実施形態の基準クロックカウンタ103は、STARTがONとなった時点でカウントを開始する。そしてREF_CNTが2047となった時点で、0にリセットする。基準クロックカウンタ103がリセットされると、同じタイミングでOSCクロックカウンタ102もリセットされる。基準クロックカウンタ103は、REF_CNTの0〜2047を一周期としてカウントを行う。

【0050】

OSCクロックカウンタ102は、基準クロックカウンタ103と同期してリセット及びカウントの開始を行う。ただしOSCクロックカウンタ102のカウントの停止は、REF_CNTが1023となった時点、つまり基準クロックカウンタ103のカウント周期の半分の時点で行う。

【0051】

OSCクロックカウンタ102は、カウント停止した時点でのVOC_CNTの値を、CT1として比較器104へ送信する。併せて基準クロックカウンタ103は、この時点でのREF_CNTの値(1023)を、CT2として比較器104へ送信する。

【0052】

なお図3に示すように、OSCクロックカウンタ102が停止してから次にリセットがかかるまでに所定の空白時間が発生するが、この時間の間に、上述した比較器104による比較、探索回路105によるOSC_DIの更新、更新されたOSC_DIによる発振部101の発振周波数の設定、及び発振部101の安定待ちが行われる。

【0053】

図3の例では、まず一回目のリセット(図中のr1)が発生した時点で、REF_CNT及びVOC_CNTが、0を初期値として増加していく。この時点でのVOC_CNTは、未調整の発振部101により生成されたクロック信号の発振周波数をカウントしたものとなる。この状態でREF_CNTが1023になると、VOC_CNTのカウントが停止される。ただしこのカウント値は周波数調整に用いられないため、破棄される。

【0054】

VOC_CNTの第一回カウントが停止した時点で、探索回路105はOSC_DIの最上位ビットを比較ビットに設定する。この結果、図3のOSC_DIに示すように、この時点でのOSC_DIは0b1000_0000(0d128)となる。

【0055】

次に二回目のリセット(図中のr2)が発生すると、再びREF_CNT及びVOC_CNTが0から増加していく。そしてREF_CNTが1023になった時点で、VOC_CNTが1177となっている。このため、比較回路104の比較結果がCT1(VOC_CNT)>CT2(REF_CNT)となる。この結果、比較ビットである第7ビットが「0」に確定される。そして、比較ビットが下位ビットに移行され、OSC_DIは0b0100_0000(0d64)となる。

【0056】

次に三回目のリセット(図中のr3)が発生した後、REF_CNTが1023になった時点で、VOC_CNTが1040となっている。このため、比較回路104の比較結果がCT1>CT2となる。この結果、比較ビットである第6ビットが「0」に確定される。そして比較ビットが下位ビットに移行され、OSC_DIは0b0010_0000(0d32)となる。

【0057】

次に四回目のリセット(図中のr4)が発生した後、REF_CNTが1023になった時点で、VOC_CNTが982となっている。このため、比較回路104の比較結果がCT1≦CT2となる。この結果、比較ビットである第5ビットが「1」に確定される。そして比較ビットが下位ビットに移行され、OSC_DIは0b0011_0000(0d48)となる。

【0058】

以上の処理を第0ビットまで繰り返す。九回目のリセット(図中のr9)の発生後、REF_CNTが1023になった時点でVOC_CNTが1022となっている。このため、比較回路104の比較結果がCT1≦CT2となる。この結果、比較ビットである第0ビットが「1」に確定される。OSC_DIは0b0011_0111(0d55)となる。この値が、探索された周波数調整コードとして、レジスタ106に格納される。

【0059】

なお、九回目のリセット後、REF_CNTが1023となった時点でENDがONになっているため、探索処理は終了され、OSCクロックカウンタ102及び基準クロックカウンタ103のカウントも停止される。

【0060】

以上のように本実施形態では、比較結果がCT1>CT2である場合に比較ビットに0を設定し、CT1≦CT2である場合に比較ビットに1を設定している。このため、探索処理によって得られる周波数調整コードの値が小さい程、未調整の発振部101の発振周波数が目標値よりも高く、つまり周波数調整のために発振周波数を下げる必要があるとみなされる。

【0061】

レジスタ106に格納された周波数調整コードは、I2Cコマンドにより読み出され、不図示のフラッシュメモリ等に記録される。ただし、周波数調整コードの探索が完了していないことが管理レジスタ等により示されている場合は、I2Cコマンドを受信したとしても読み出しは行われない

【0062】

次に、クロック発振回路100の通常動作について説明する。

【0063】

クロック発振回路100の通常動作時は、水晶発振器301がクロック発振回路100に接続されていない。また、OSCクロックカウンタ102、基準クロックカウンタ103、比較回路104、及び探索回路105は動作しない。

【0064】

この状態において電源が投入されると、CPU201は、発振部101より入力される未調整のクロック信号による仮動作を開始する。仮動作を開始したCPU201は、ROM202より、通常動作用のプログラムを読み出し、実行する。プログラムの実行後、フラッシュメモリ等に記録された探索済みの周波数調整コードをレジスタ106に格納する指示を含むI2CコマンドをCPU201へ送信する。

【0065】

このI2Cコマンドが外部I/F203を介して受信されると、周波数調整コードがレジスタ106に書き込まれる。発振部101は、レジスタ106より周波数調整コードを読み出し、周波数調整コードの設定を行う。

【0066】

これにより発振部101に含まれる8ビットのR−2Rラダー部の調整が行われる。そして調整後の状態でOSC_CLKを生成し、外部端子T2を介してCPU201へ出力する。以降、CPU201は、OSC_CLKにより通常動作を行う。

<その他の変形例>

【0067】

なお、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【0068】

例えば、上記実施形態では発振部101がOSC_CLKを出力する出力端が一つであるが、図4に示すように、複数の出力端を備える形態でもよい。これにより、OSCクロックカウンタ102とCPU201とに対して、OSC_CLKを出力するか否かを個別に制御可能とする。探索回路105は、通常動作時において、CPU201にのみOSC_CLKを出力するよう発振部101を制御する。また探索回路105は、周波数調整動作時において、OSCクロックカウンタ102にのみOSC_CLKを出力するよう発振部101を制御する。以上の構成とすることにより、例えば周波数調整動作時においてOSC_CLKが一時的にCPU201の動作限界クロックを上回り、装置の誤動作を招くといった事態を回避することができる。

【0069】

また上記実施形態では、REF_CNTとして11bitの値(0〜2047)を用い、この中間値(1023)とVOC_CNTとを比較しているが、これらの具体的な数値は設計の段階において適宜変更が可能である。

【産業上の利用可能性】

【0070】

本発明は、マイクロプロセッサ、画像処理プロセッサ、マルチメディアプロセッサ、IPコア、モバイル機器、ゲーム機、PDAなどの装置において、クロック信号の精度の向上を図る上で有用な技術である。

【符号の説明】

【0071】

100 クロック発振回路

101 発振部

102 OSCクロックカウンタ(第1カウンタ)

103 基準クロックカウンタ(第2カウンタ)

104 比較回路

105 探索回路(周波数調整コード探索回路)

106 レジスタ

201 CPU

202 ROM

203 外部I/F

204 I2Cバス

301 水晶発振器

【技術分野】

【0001】

本発明は、クロック発振回路に関するものであり、特に発振周波数のトリミングを行う機能を備えたクロック発振回路に関するものである。

【背景技術】

【0002】

CPU(Central Processing Unit)等の動作クロックを生成する装置として、セラミック振動子や水晶発振器等が存在する。これらの装置は、周波数精度は高いがサイズが比較的大きいため、小型の電子装置、例えばデジタルカメラや携帯電話等に内蔵するには不向きである。このため近年、比較的小型であるCR発振回路を用いた、クロック発振回路が実用化されている。

【0003】

上記の一例として、クロック信号を出力する発振部と、外部入力される校正クロック信号を基準として発振部の発振周波数を計測する周波数計測回路と、計測結果に基づいて発振部の発振周波数を調整するトリミング制御回路と、を備えたクロック発振回路が開示・提案されている(例えば特許文献1を参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−341119号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながらCR発振回路は、装置特性や温度条件等により発振周波数にばらつきが生じ易く、周波数精度が高いとはいえない。このため、高精度の発振周波数が要求される電子装置では、例えばCR発振回路の外部に調整用の素子を設けたり、或いは電子装置の製造段階において水晶発振器等を外部接続して周波数調整動作を行ったりする必要があった。

【0006】

本発明は、本願の発明者により見出された上記の問題点に鑑み、発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明に係るクロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を出力する発振部と、前記クロック信号の発振周波数を計測する第1カウンタと、外部より与えられる基準クロック信号の発振周波数を計測する第2カウンタと、前記第1カウンタの計測値と前記第2カウンタの計測値とを比較する比較回路と、前記クロック信号の発振周波数と前記基準クロック信号の発振周波数とが一致するように、前記比較回路の出力をモニタしながら、前記周波数調整コードの自動探索を行う周波数調整コード探索回路と、自動探索済みの前記周波数調整コードを格納するレジスタと、を有し、前記発振部は、通常動作時において、前記レジスタに格納された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、周波数調整動作時において、前記周波数調整コード探索回路により設定された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定することを特徴とする構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成るクロック発振回路は、前記周波数調整コード探索回路が、前記周波数調整動作時において、前記クロック発振回路の外部に対する前記クロック信号の出力を停止するよう前記発振部を制御することを特徴とする構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成るクロック発振回路は、前記周波数調整コード探索回路が、前記周波数調整動作時において、前記比較回路の出力に基づいて前記周波数調整コードを更新する更新動作と、更新後の前記周波数調整コードを前記発振部に設定する設定動作とを、予め定められた回数だけ繰り返し行うことを特徴とする構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成るクロック発振回路は、前記発振部が、mビット(mは自然数)の前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、前記周波数調整コード探索回路は、前記更新動作と前記設定動作との繰り返しをm回行い、1回の前記更新動作において前記比較回路の出力を前記周波数調整コードの1ビットに反映することを特徴とする構成(第4の構成)にするとよい。

【0011】

また、上記第4の構成から成るクロック発振回路は、前記周波数調整コード探索回路が、自動探索済みの前記周波数調整コードを前記レジスタに格納した後、前記周波数調整コードの読み出しを許可するフラグを設定することを特徴とする構成(第5の構成)にするとよい。

【発明の効果】

【0012】

本発明によれば、通常動作を行うための動作系統と、発振周波数のクロックトリミングを行う周波数調整動作を行うための動作系統との二系統を備え、通常動作時においてクロックトリミングが不要であるクロック発振回路を提供することができる。

【0013】

また本発明によれば、周波数調整動作時において、クロック発振回路の外部装置に対して動作限界を超えるクロック信号が供給される事態を回避することが可能なクロック発振回路を提供することができる。

【図面の簡単な説明】

【0014】

【図1】本発明に係るクロック発振回路を含んだ電子装置を示すブロック図

【図2】本発明に係るクロック発振回路を示すブロック図

【図3】発振周波数のカウントタイミングを示す模式図

【図4】その他の実施形態に係るクロック発振回路を示すブロック図

【発明を実施するための形態】

【0015】

<装置構成>

図1は、本発明のクロック発振回路を備える電子装置の、内部構成の一例を示す図である。本構成例の電子装置は、例えば携帯電話やデジタルカメラのような、携帯可能な程度に小型であり、且つ高精度のCPU処理が要求される装置を想定している。

【0016】

本構成例の電子装置は、クロック発振回路100と、CPU(Central Processing Unit)201と、ROM(Read Only Memory)202と、外部I/F203と、I2Cバス204とを有する。また、発振周波数の調整に用いるOSC(Oscillator)として、水晶発振器301をクロック発振回路100に外部接続可能である。

【0017】

なお水晶発振器301は、クロック発振回路100の周波数調整時において一時的に用いられる装置である。従って、一般ユーザがクロック発振回路100を備えた電子装置を使用する段階では、水晶発振器301はクロック発振回路100に接続されていない。

【0018】

クロック発振回路100は、不図示のCR発振回路を用いて、CPU201を動作させるためのクロック信号(OSC_CLK)を生成して出力する。なお、クロック発振回路100の内部構成については後述する。

【0019】

CPU201は、データの演算処理を行うロジック回路である。CPU201は、所定のコマンドをクロック発振回路100へ送信する。これを受けたクロック発振回路100は、受信したコマンドに基づき、後述する周波数調整動作やクロック生成動作を実施する。

【0020】

ROM202は、CPU201が実行するシステムプログラムや、クロック発振回路100の動作に関連する各種設定情報等を記録した、不揮発性の記録媒体である。なおROM202は、書き換え可能な不揮発性半導体メモリを含む構成でもよい。

【0021】

外部I/F203(インタフェース部)は、I2Cバス204を介して外部の装置と通信を行うためのインタフェースである。

【0022】

水晶発振器301は、発振周波数の調整時において、クロック発振回路100に対してEXT_CLKを与える。なお、EXT_CLKの発振周波数は、電子装置に要求される動作精度に応じて、電子装置の設計段階等において決定される。本実施形態では一例として、4.5MHzの発振周波数を用いるものとする。

【0023】

<クロック発振回路の構成>

次に、クロック発振回路100の内部構成について、図2を用いつつ説明する。図2は、本発明のクロック発振回路の内部構成の一例を示す図である。クロック発振回路100は、発振部101と、OSCクロックカウンタ102(第1カウンタ)と、基準クロックカウンタ103(第2カウンタ)と、比較回路104と、探索回路105(周波数調整コード探索回路)と、レジスタ106と、を集積化した半導体集積回路装置である。

【0024】

またクロック発振回路100は、外部との電気的な接続を確立するために、外部端子T1〜T3を有する。外部端子T1は、発振周波数の調整時において、水晶発振器301により生成される基準クロック信号(EXT_CLK)を入力する入力端子である。外部端子T2は、OSC_CLKの出力端子である。外部端子T3は、レジスタ106をCPU201に接続するための入出力端子である。

【0025】

発振部101の入力端は、探索回路105と、レジスタ106とに接続されている。発振部101の出力端は、OSCクロックカウンタ102に接続されている。また、外部端子T2を介して、CPU201に接続されている。OSCクロックカウンタ102の出力端は、比較回路104に接続されている。基準クロックカウンタ103の入力端は、外部端子T1に接続されている。比較回路104の出力端は、探索回路105に接続されている。探索回路105の出力端は、発振部101とレジスタ106とに接続されている。レジスタ106の入出力端は、外部端子T3を介して、CPU201に接続されている。またレジスタ106の出力端は、発振部101に接続されている。

【0026】

発振部101は、不図示のCR発振回路を有する。発振部101は、後述する周波数調整コードに基づいてCR発振回路の抵抗(R)部分を調整することにより、発振周波数を変化させる。なお本実施形態では、8ビットのR−2RラダーからなるCR発振回路を用いる。このため、周波数調整コードとして8ビットのデータを用いる。

【0027】

OSCクロックカウンタ102は、発振部101により生成されるクロック信号であるOSC_CLKを入力し、発振周波数のカウントを行う。そしてカウントされた値を示す信号(CT1)を、比較回路104へ送る。

【0028】

標準クロックカウンタ103は、水晶発振器301により生成される基準クロック信号であるEXT_CLKを入力し、発振周波数のカウントを行う。そしてカウントされた値を示す信号(CT2)を、比較回路104へ送る。

【0029】

比較回路104は、CT1とCT2とを比較し、比較結果を示す信号(CMP)を探索回路105へ送る。なおCMPは、CT1とCT2との大小関係を示す情報である。

【0030】

探索回路105は、比較回路104より入力されるCMPを参照しつつ、CT1とCT2とが一致するように発振部101の発振周波数を調整する。これにより、周波数調整コードの探索を行う。そして探索した周波数調整コードを、レジスタ106に格納する。本実施形態では、8ビットの周波数調整コードを用いるため、8回の比較及び調整による探索処理を行う。なお、探索処理の詳細については後述する。

【0031】

レジスタ106は、上述の周波数調整コードを記録するための揮発性の記録媒体である。レジスタ106は、探索回路105により探索された周波数調整コードが格納され、CPU201により読み出される。また、CPU201により探索済みの周波数調整コードが格納され、発振部101により読み出される。発振部101は、通常動作時において、レジスタ106より読み出した周波数調整コードを用いて、発振周波数の設定を行う。

【0032】

<クロック発振回路の動作>

次に、クロック発振回路100の動作について説明する。本実施形態のクロック発振回路100は、クロック発振回路100を備える電子装置の電源が投入された段階で、動作を開始する。クロック発振回路100の動作は、周波数調整動作と、通常動作との二つに大別される。何れの動作を行うかは、例えばCPU201に電気的に接続されたディップスイッチや、或いは不図示のフラッシュメモリに予め記録されている動作設定情報等により決定する。ここではまず、周波数調整動作について説明する。

【0033】

クロック発振回路100の周波数調整は、電子装置の工場出荷前に実施される。周波数調整動作を行うにあたっては、まずクロック発振回路100に水晶発振器301が外部接続される。

【0034】

この状態において電源が投入されると、CPU201は、発振部101より入力される未調整のクロック信号による仮動作を開始する。なお未調整のクロック信号の発振周波数は、CPU201がオーバークロックとならない程度に低くなるよう、予め設定されているものとする。

【0035】

仮動作を開始したCPU201は、ROM202より、予め用意されている周波数調整用のプログラムを読み出し、実行する。このプログラムの実行後、周波数調整コード探索指令を含むI2Cコマンドが送信されると、CPU201からクロック発振回路100に対して、周波数調整コード探索指令が送信される。

【0036】

この周波数調整コード探索指令がCPU201から送信されると、不図示の管理レジスタのフラグ情報が書き換えられ、周波数調整開始を示すフラグがONになる。

【0037】

探索回路105は、定期的にこの管理レジスタを監視しており、上記フラグがONになったのを検知した段階で、周波数調整コードの探索処理を開始する。なおこの探索処理はハードウェアロジックによって行われる。

【0038】

周波数調整コードの探索処理が開始されると、探索回路105は発振部101に対して、試験用の周波数調整コード(OSC_DI)を示す設定信号(DI)を送信する。OSC_DIは、通常の周波数調整コードと同じく8ビットの情報であり、その初期値は最大値と最小値との中間値、つまり2進数表記では0b1000_0000、10進数表記では0d128である。

【0039】

DIを受けた発振部101は、発振部101に含まれるCR発振回路に対してOSC_DIの設定を行う。これによりCR発振回路に含まれる8ビットのR−2Rラダー部の調整が行われ、OSC_CLKの発振周波数が決定される。なお発振周波数は、OSC_DIが大きい程高く、小さい程低くなるように設定される。

【0040】

この状態で発振部101がOSC_CLKの生成を行うと、OSC_CLKはOSCクロックカウンタ102に送られ、発振周波数のカウントが行われる。カウント結果を示すCT1は比較回路104へ送られる。

【0041】

またあわせて、基準クロックカウンタ103は、T1を介して水晶発振器301から入力されるEXT_CLKのカウントを行う。カウント結果を示すCT2は比較回路104へ送られる。なお、OSCクロックカウンタ102と基準クロックカウンタ103とがカウントを開始するタイミングは、探索回路105が探索処理を開始する際に生成するトリミング開始信号(START)により同期される。

【0042】

比較器104はCT1の値とCT2の値とを比較し、比較結果を示すCMPを探索回路105へ送信する。これを受けた探索回路105は、CMPが「CT1>CT2」を示す場合に、OSC_DIの最上位ビットを0に確定する。逆にCMPが「CT1≦CT2」を示す場合に、OSC_DIの最上位ビットを1に確定する。

【0043】

なお、このようにCMPに応じて数値を変更する対象ビットを、以降は比較ビットという。1回目の比較ビットはOSC_DIの最上位ビットであり、2回目以降の比較ビットは、前回の比較ビットの下位ビットにあたる。つまり2回目の比較ビットは第6ビットであり、8回目の比較ビットは第0ビットとなる。

【0044】

1回目の比較が完了すると、探索回路105は、比較ビットを一つ下位のビットに移す。比較ビットはまず1に設定される。従って例えば、1回目の比較結果が「CT1>CT2」であった場合、第7ビットが「0」に設定され、第6ビットが「1」に設定されるため、この時点でのOSC_DIは0b0100_0000(0d63)となる。探索回路105はこのOSC_DIを発振部101に設定する。そしてOSC_CLKの生成、カウント、比較が再度行われる。

【0045】

以上の繰り返しを、第7ビットから第0ビットまでの8回行う。この結果、最終的に得られたOSC_DIを、周波数調整コードとしてレジスタ106に格納する。併せて探索回路105は、不図示の管理レジスタのフラグ情報が書き換え、周波数調整が終了したことを示すフラグをONにする。

【0046】

上記の探索処理の具体的な処理タイミング及び数値を示した一例を、図3を用いて説明する。図3の最上段のSTARTは、探索回路105が探索処理を開始する際に生成するトリミング開始信号である。

【0047】

その下段のENDは、周波数調整の終了タイミングをとるためのトリミング停止信号である。トリミング停止信号は、トリミング開始信号がONになってから所定時間後に、探索回路105によりOFFされる。

【0048】

ENDの下段のREF_CNTは、基準クロックカウンタ103のカウント数を示している。その下段のVOC_CNTは、OSCクロックカウンタ102のカウント数を示している。最下段のOSC_DIは、上述の試験用の周波数調整コードである。

【0049】

本実施形態の基準クロックカウンタ103は、STARTがONとなった時点でカウントを開始する。そしてREF_CNTが2047となった時点で、0にリセットする。基準クロックカウンタ103がリセットされると、同じタイミングでOSCクロックカウンタ102もリセットされる。基準クロックカウンタ103は、REF_CNTの0〜2047を一周期としてカウントを行う。

【0050】

OSCクロックカウンタ102は、基準クロックカウンタ103と同期してリセット及びカウントの開始を行う。ただしOSCクロックカウンタ102のカウントの停止は、REF_CNTが1023となった時点、つまり基準クロックカウンタ103のカウント周期の半分の時点で行う。

【0051】

OSCクロックカウンタ102は、カウント停止した時点でのVOC_CNTの値を、CT1として比較器104へ送信する。併せて基準クロックカウンタ103は、この時点でのREF_CNTの値(1023)を、CT2として比較器104へ送信する。

【0052】

なお図3に示すように、OSCクロックカウンタ102が停止してから次にリセットがかかるまでに所定の空白時間が発生するが、この時間の間に、上述した比較器104による比較、探索回路105によるOSC_DIの更新、更新されたOSC_DIによる発振部101の発振周波数の設定、及び発振部101の安定待ちが行われる。

【0053】

図3の例では、まず一回目のリセット(図中のr1)が発生した時点で、REF_CNT及びVOC_CNTが、0を初期値として増加していく。この時点でのVOC_CNTは、未調整の発振部101により生成されたクロック信号の発振周波数をカウントしたものとなる。この状態でREF_CNTが1023になると、VOC_CNTのカウントが停止される。ただしこのカウント値は周波数調整に用いられないため、破棄される。

【0054】

VOC_CNTの第一回カウントが停止した時点で、探索回路105はOSC_DIの最上位ビットを比較ビットに設定する。この結果、図3のOSC_DIに示すように、この時点でのOSC_DIは0b1000_0000(0d128)となる。

【0055】

次に二回目のリセット(図中のr2)が発生すると、再びREF_CNT及びVOC_CNTが0から増加していく。そしてREF_CNTが1023になった時点で、VOC_CNTが1177となっている。このため、比較回路104の比較結果がCT1(VOC_CNT)>CT2(REF_CNT)となる。この結果、比較ビットである第7ビットが「0」に確定される。そして、比較ビットが下位ビットに移行され、OSC_DIは0b0100_0000(0d64)となる。

【0056】

次に三回目のリセット(図中のr3)が発生した後、REF_CNTが1023になった時点で、VOC_CNTが1040となっている。このため、比較回路104の比較結果がCT1>CT2となる。この結果、比較ビットである第6ビットが「0」に確定される。そして比較ビットが下位ビットに移行され、OSC_DIは0b0010_0000(0d32)となる。

【0057】

次に四回目のリセット(図中のr4)が発生した後、REF_CNTが1023になった時点で、VOC_CNTが982となっている。このため、比較回路104の比較結果がCT1≦CT2となる。この結果、比較ビットである第5ビットが「1」に確定される。そして比較ビットが下位ビットに移行され、OSC_DIは0b0011_0000(0d48)となる。

【0058】

以上の処理を第0ビットまで繰り返す。九回目のリセット(図中のr9)の発生後、REF_CNTが1023になった時点でVOC_CNTが1022となっている。このため、比較回路104の比較結果がCT1≦CT2となる。この結果、比較ビットである第0ビットが「1」に確定される。OSC_DIは0b0011_0111(0d55)となる。この値が、探索された周波数調整コードとして、レジスタ106に格納される。

【0059】

なお、九回目のリセット後、REF_CNTが1023となった時点でENDがONになっているため、探索処理は終了され、OSCクロックカウンタ102及び基準クロックカウンタ103のカウントも停止される。

【0060】

以上のように本実施形態では、比較結果がCT1>CT2である場合に比較ビットに0を設定し、CT1≦CT2である場合に比較ビットに1を設定している。このため、探索処理によって得られる周波数調整コードの値が小さい程、未調整の発振部101の発振周波数が目標値よりも高く、つまり周波数調整のために発振周波数を下げる必要があるとみなされる。

【0061】

レジスタ106に格納された周波数調整コードは、I2Cコマンドにより読み出され、不図示のフラッシュメモリ等に記録される。ただし、周波数調整コードの探索が完了していないことが管理レジスタ等により示されている場合は、I2Cコマンドを受信したとしても読み出しは行われない

【0062】

次に、クロック発振回路100の通常動作について説明する。

【0063】

クロック発振回路100の通常動作時は、水晶発振器301がクロック発振回路100に接続されていない。また、OSCクロックカウンタ102、基準クロックカウンタ103、比較回路104、及び探索回路105は動作しない。

【0064】

この状態において電源が投入されると、CPU201は、発振部101より入力される未調整のクロック信号による仮動作を開始する。仮動作を開始したCPU201は、ROM202より、通常動作用のプログラムを読み出し、実行する。プログラムの実行後、フラッシュメモリ等に記録された探索済みの周波数調整コードをレジスタ106に格納する指示を含むI2CコマンドをCPU201へ送信する。

【0065】

このI2Cコマンドが外部I/F203を介して受信されると、周波数調整コードがレジスタ106に書き込まれる。発振部101は、レジスタ106より周波数調整コードを読み出し、周波数調整コードの設定を行う。

【0066】

これにより発振部101に含まれる8ビットのR−2Rラダー部の調整が行われる。そして調整後の状態でOSC_CLKを生成し、外部端子T2を介してCPU201へ出力する。以降、CPU201は、OSC_CLKにより通常動作を行う。

<その他の変形例>

【0067】

なお、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【0068】

例えば、上記実施形態では発振部101がOSC_CLKを出力する出力端が一つであるが、図4に示すように、複数の出力端を備える形態でもよい。これにより、OSCクロックカウンタ102とCPU201とに対して、OSC_CLKを出力するか否かを個別に制御可能とする。探索回路105は、通常動作時において、CPU201にのみOSC_CLKを出力するよう発振部101を制御する。また探索回路105は、周波数調整動作時において、OSCクロックカウンタ102にのみOSC_CLKを出力するよう発振部101を制御する。以上の構成とすることにより、例えば周波数調整動作時においてOSC_CLKが一時的にCPU201の動作限界クロックを上回り、装置の誤動作を招くといった事態を回避することができる。

【0069】

また上記実施形態では、REF_CNTとして11bitの値(0〜2047)を用い、この中間値(1023)とVOC_CNTとを比較しているが、これらの具体的な数値は設計の段階において適宜変更が可能である。

【産業上の利用可能性】

【0070】

本発明は、マイクロプロセッサ、画像処理プロセッサ、マルチメディアプロセッサ、IPコア、モバイル機器、ゲーム機、PDAなどの装置において、クロック信号の精度の向上を図る上で有用な技術である。

【符号の説明】

【0071】

100 クロック発振回路

101 発振部

102 OSCクロックカウンタ(第1カウンタ)

103 基準クロックカウンタ(第2カウンタ)

104 比較回路

105 探索回路(周波数調整コード探索回路)

106 レジスタ

201 CPU

202 ROM

203 外部I/F

204 I2Cバス

301 水晶発振器

【特許請求の範囲】

【請求項1】

周波数調整コードに応じた発振周波数のクロック信号を出力する発振部と、

前記クロック信号の発振周波数を計測する第1カウンタと、

外部より与えられる基準クロック信号の発振周波数を計測する第2カウンタと、

前記第1カウンタの計測値と前記第2カウンタの計測値とを比較する比較回路と、

前記クロック信号の発振周波数と前記基準クロック信号の発振周波数とが一致するように、前記比較回路の出力をモニタしながら、前記周波数調整コードの自動探索を行う周波数調整コード探索回路と、

自動探索済みの前記周波数調整コードを格納するレジスタと、

を有し、

前記発振部は、

通常動作時において、前記レジスタに格納された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、

周波数調整動作時において、前記周波数調整コード探索回路により設定された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定すること

を特徴とするクロック発振回路。

【請求項2】

前記周波数調整コード探索回路は、前記周波数調整動作時において、前記クロック発振回路の外部に対する前記クロック信号の出力を停止するよう前記発振部を制御すること

を特徴とする請求項1に記載のクロック発振回路。

【請求項3】

前記周波数調整コード探索回路は、前記周波数調整動作時において、前記比較回路の出力に基づいて前記周波数調整コードを更新する更新動作と、更新後の前記周波数調整コードを前記発振部に設定する設定動作とを、予め定められた回数だけ繰り返し行うこと

を特徴とする請求項2に記載のクロック発振回路。

【請求項4】

前記発振部は、mビット(mは自然数)の前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、

前記周波数調整コード探索回路は、前記更新動作と前記設定動作との繰り返しをm回行い、1回の前記更新動作において前記比較回路の出力を前記周波数調整コードの1ビットに反映すること

を特徴とする請求項3に記載のクロック発振回路。

【請求項5】

前記周波数調整コード探索回路は、自動探索済みの前記周波数調整コードを前記レジスタに格納した後、前記周波数調整コードの読み出しを許可するフラグを設定すること

を特徴とする請求項4に記載のクロック発振回路。

【請求項1】

周波数調整コードに応じた発振周波数のクロック信号を出力する発振部と、

前記クロック信号の発振周波数を計測する第1カウンタと、

外部より与えられる基準クロック信号の発振周波数を計測する第2カウンタと、

前記第1カウンタの計測値と前記第2カウンタの計測値とを比較する比較回路と、

前記クロック信号の発振周波数と前記基準クロック信号の発振周波数とが一致するように、前記比較回路の出力をモニタしながら、前記周波数調整コードの自動探索を行う周波数調整コード探索回路と、

自動探索済みの前記周波数調整コードを格納するレジスタと、

を有し、

前記発振部は、

通常動作時において、前記レジスタに格納された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、

周波数調整動作時において、前記周波数調整コード探索回路により設定された前記周波数調整コードに応じて前記クロック信号の発振周波数を設定すること

を特徴とするクロック発振回路。

【請求項2】

前記周波数調整コード探索回路は、前記周波数調整動作時において、前記クロック発振回路の外部に対する前記クロック信号の出力を停止するよう前記発振部を制御すること

を特徴とする請求項1に記載のクロック発振回路。

【請求項3】

前記周波数調整コード探索回路は、前記周波数調整動作時において、前記比較回路の出力に基づいて前記周波数調整コードを更新する更新動作と、更新後の前記周波数調整コードを前記発振部に設定する設定動作とを、予め定められた回数だけ繰り返し行うこと

を特徴とする請求項2に記載のクロック発振回路。

【請求項4】

前記発振部は、mビット(mは自然数)の前記周波数調整コードに応じて前記クロック信号の発振周波数を設定し、

前記周波数調整コード探索回路は、前記更新動作と前記設定動作との繰り返しをm回行い、1回の前記更新動作において前記比較回路の出力を前記周波数調整コードの1ビットに反映すること

を特徴とする請求項3に記載のクロック発振回路。

【請求項5】

前記周波数調整コード探索回路は、自動探索済みの前記周波数調整コードを前記レジスタに格納した後、前記周波数調整コードの読み出しを許可するフラグを設定すること

を特徴とする請求項4に記載のクロック発振回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−58947(P2013−58947A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−196636(P2011−196636)

【出願日】平成23年9月9日(2011.9.9)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月9日(2011.9.9)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]