クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はクロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法に関し、特にクロックをデータに重畳したエンベデッド信号からリカバリクロックを発生させるクロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法に関する。

【背景技術】

【0002】

近年、高速シリアルI/Fにおいて、送信側からはシリアルデータの先頭クロックをデータに埋め込んだエンベデッド(embedded)信号を送信し、受信側では受信したエンベデッド信号からシリアルデータの先頭クロックのエッジ情報を抽出し、その抽出した先頭クロックエッジから復元したリカバリクロック(再生クロック)でデータをサンプリングして元のシリアルデータを復元するデータ送受信方法が普及している。

【0003】

このような高速シリアルI/Fの受信回路では、入力されるエンベデッド信号に基づいて、データを抽出するリカバリクロックを発生させるために、DLL(Delay Locked Loop)が用いられている。

【0004】

DLLを用いたクロック発生回路として、例えば、特許文献1〜3が知られている。なお、特許文献1〜3には、エンベデッド信号については記載されていない。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−21706号公報

【特許文献2】特開2009−278528号公報

【特許文献3】特許第3945894号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

DLLは、基準信号に対しフィードバック制御することでロック状態となり、遅延信号を発生させている。このため、DLLを用いたクロック発生回路では、基準となる信号が停止すると、フィードバック制御ができなくなることから、クロックの生成も停止してしまう。基準となる信号が停止する原因としては、クロック発生回路の内部状態が不安定となることによる誤動作が考えられる。

【0007】

このような誤動作を防ぐため、特許文献3には、電源投入時に回路をリセットするパワーオンリセット信号が記載されている。

【0008】

図10は、従来のクロック発生回路における、パワーオンリセット信号によるリセット動作を示している。すなわち、装置に電源が投入されると(S901)、まず、パワーオンリセット回路が動作してパワーオンリセット信号が生成され(S902)、生成されたパワーオンリセット信号によってクロック発生回路の内部状態をリセットし(S903)、その後、クロックの発生が開始され通常動作となる(S904)。

【0009】

しかし、パワーオンリセット信号によるリセットでは、電源投入の電源の立上り条件等に影響されてリセットがかかる条件が制限される場合がある。

【0010】

図11は、電源投入時の電源電圧とパワーオンリセット信号の関係を示している。すなわち、パワーオンリセット信号は、電源投入後の電圧波形の立上りに従って生成される。図11(a)のように電圧波形の傾きが緩やかな場合には、パワーオンリセット信号のパルス幅はより広くなり、図11(b)のように電圧波形の傾きが急な場合には、パワーオンリセット信号のパルス幅はより狭くなる。したがって、電圧波形が急峻になると、パワーオンリセット信号が非常に細くなり、回路によっては正常にリセットできない場合がある。その場合には、クロック発生回路がリセットされずにクロック生成が停止したままとなる。なお、全ての電源立ち上がり波形に対して回路を確実にリセットするようなパワーオンリセット信号を生成しようとすると、表示装置メーカーに対して表示装置用駆動回路の電源立ち上げ時間の規格を決める必要があり、表示装置用駆動回路の汎用性を損なうことになる。また、電源立ち上げ時間規格はワースト条件でも守られる必要があるため、この規格で決めた時間はパワーオンリセットがずっと掛かっていることになり、ワースト条件以外の場合には必要のない時間を装置の立ち上げのためにエンドユーザを待たせることになってしまう。さらに、表示装置メーカーが電源の立ち上げ時間を短縮して電源投入後の表示装置の立ち上げ時間を短くしようとしても駆動回路がこの規格時間は立ち上がらないことになり、これも表示装置の駆動回路の汎用性を損なうことになる。

【0011】

また、パワーオンリセット信号によるリセットのみでは、通常動作後に回路が誤動作した場合、クロックを正常に生成することができない。

【0012】

図12は、従来のクロック発生回路において、パワーオンリセット後に誤動作が生じる場合の動作を示している。すなわち、図10で示したように、電源投入しパワーオンリセット後に通常動作となる(S901〜S904)。その後、外来ノイズ等の影響により回路の内部状態が不安定になると、クロックの生成が停止する(S905)。そして、そのまま内部状態が回復しないと、復帰せずにクロックの生成が停止したままとなる(S906)。

【0013】

このように、従来のクロック発生回路では、クロックの生成が停止した状態から回復するためにパワーオンリセット信号を用いても、電源投入時にリセットできない場合があるとともに、通常動作時に誤動作を起こした場合は正常な状態に回復することができないという問題があった。

【課題を解決するための手段】

【0014】

本発明に係るクロック発生回路は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、を備えるものである。

【0015】

また、本発明に係る表示装置用駆動回路は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、前記抽出クロックに対し遅延制御されたリカバリクロックを出力するクロック出力回路と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、前記リカバリクロックに基づき前記エンベデッド信号のシリアルデータをパラレルデータに変換するシリアルパラレル変換回路と、前記パラレルデータに応じて表示装置を駆動する駆動信号を出力する駆動信号出力回路と、を備えるものである。

【0016】

さらに、本発明に係るクロック発生回路の制御方法は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路を備えるクロック発生回路の制御方法であって、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記抽出クロックの停止を検出した場合、前記クロック抽出回路を初期状態にリセットするものである。

【0017】

本発明では、エンベデッド信号と抽出クロックとに基づき抽出クロックの停止を検出し、クロック抽出回路をリセットするため、電源投入時や通常動作時においてクロックが停止した場合であっても、より確実に正常な状態に回復することが可能となる。

【発明の効果】

【0018】

本発明によれば、電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法を提供することができる。

【図面の簡単な説明】

【0019】

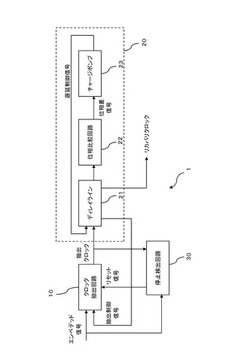

【図1】本発明の実施の形態に係る表示システムの構成を示すブロック図である。

【図2】本発明の実施の形態に係るクロック発生回路の構成を示すブロック図である。

【図3】本発明の実施の形態に係るクロック発生回路の動作を示すタイミングチャートである。

【図4】本発明の実施の形態に係る停止検出回路の構成を示すブロック図である。

【図5】本発明の実施の形態に係る停止検出回路の動作を示すフローチャートである。

【図6】本発明の実施の形態に係る停止検出回路の回路構成を示す回路図である。

【図7】本発明の実施の形態に係る停止検出回路の動作を示すタイミングチャートである。

【図8】本発明の実施の形態に係る停止検出回路の動作を示すタイミングチャートである。

【図9】本発明の実施の形態に係る停止検出回路の動作を説明するための図である。

【図10】従来のクロック発生回路の動作を示すフローチャートである。

【図11】従来のクロック発生回路におけるパワーオンリセット信号を説明するための波形図である。

【図12】従来のクロック発生回路の動作を示すフローチャートである。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

【0021】

まず、図1を用いて、本発明の実施の形態に係る表示システムの構成について説明する。図に示されるように、この表示システムは、表示パネル(表示装置)200と、表示パネルを駆動する駆動装置(駆動回路)100を備えている。

【0022】

表示パネル200は、駆動装置100から供給される駆動信号に応じて、表示画素を駆動させ所望の表示を行う。表示パネル200は、例えば、液晶表示パネルやプラズマ表示パネル、有機EL表示パネル等である。表示パネル200は、複数の画素を駆動するために、複数のソース線や複数のゲート線が設けられており、駆動装置100の駆動信号が、ソース線やゲート線に供給される。

【0023】

駆動装置100は、表示データとクロックを含むエンベデッド信号が入力され、表示データに応じた駆動信号を出力する。そして、駆動装置100は、クロックデータリカバリ回路8と駆動信号出力回路9を備えている。例えば、駆動装置100は、1チップの半導体装置であるが、クロックデータリカバリ回路8と駆動信号出力回路9をそれぞれ1チップの半導体装置としてもよい。

【0024】

駆動装置100に入力されるエンベデッド信号は、高速シリアルI/Fが受信するシリアル信号であり、例えば、データ期間と呼ばれる期間では、クロック成分とデータ成分とが分離して含まれており、スルー期間と呼ばれる期間では、クロック成分のみが含まれている。

【0025】

クロックデータリカバリ回路8は、入力されるエンベデッド信号から、クロックを再生するとともに、シリアル信号をパラレル信号に変換する。そして、クロックデータリカバリ回路8は、受信回路2、シリアルパラレル変換回路3、クロック発生回路1を備えている。

【0026】

受信回路2は、入力されたエンベデッド信号をシリアルパラレル変換回路3とクロック発生回路1へ出力する。すなわち、受信回路2は、差動信号として入力される信号を、シリアルパラレル変換回路3及びクロック発生回路1で処理可能な、ハイレベルとローレベルからなるディジタル信号として出力する。なお、この例ではエンベデッド信号が小振幅差動信号であるため、受信回路2を設けているが、エンベデッド信号が例えばCMOS信号である場合は、受信回路2を設けずに、エンベデッド信号を直接、シリアルパラレル変換回路3及びクロック発生回路1へ入力してもよい。

【0027】

クロック発生回路1は、入力されるエンベデッド信号から、クロックを抽出してリカバリクロックを生成し、シリアルパラレル変換回路3へ出力する。クロック発生回路1については、後述する。

【0028】

シリアルパラレル変換回路3は、リカバリクロックに基づくタイミングで、エンベデッド信号に含まれるシリアル信号の表示データ(階調信号)をパラレル信号に変換する。

【0029】

駆動信号出力回路9は、パラレル信号に変換された表示データに応じて駆動信号を出力する。そして、駆動信号出力回路9は、シフトレジスタラッチ回路4、D/A変換回路5、ボルテージフォロア回路6、ロジック制御回路7を備えている。

【0030】

シフトレジスタラッチ回路4は、入力されたパラレル信号を、シフトレジスタにより順次ラッチ回路に出力数分の階調信号が揃うまで保持し、全てのパラレル信号(階調信号)がそろったタイミングでD/A変換回路5へ出力する。

【0031】

D/A変換回路5は駆動回路の出力数分のD/A変換回路を持ち、ロジック制御回路7の制御に従って、ディジタル信号として入力されるパラレル信号を、アナログ信号に変換しボルテージフォロア回路へ出力する。

【0032】

ボルテージフォロア回路6は駆動回路の出力数分のボルテージフォロアアンプ回路を持ち、ロジック制御回路7の制御に従って、入力されるアナログ信号を増幅して駆動信号を生成し、表示パネルへ出力する。

【0033】

次に、駆動装置100のクロックデータリカバリ回路8に設けられたクロック発生回路1について説明する。

【0034】

図2は、クロック発生回路1の構成を示している。図に示されるように、クロック発生回路1は、クロック抽出回路10、DLL(Delay Locked Loop)20及び停止検出回路30を備えている。

【0035】

クロック抽出回路10は、エンベデッド信号と抽出制御信号とが入力され、エンベデッド信号から、抽出制御信号に応じた抽出範囲でクロックを抽出し、抽出したクロックを抽出クロックとして出力する。また、リセット信号により、クロック抽出回路10の内部の回路状態を初期状態にリセットする。具体的には、リセット信号としてハイレベルの信号が入力されると、不図示のフリップフロップ等の状態がリセットされる。

【0036】

DLL20は、クロック抽出回路10が抽出した抽出クロックに対し、遅延制御を行ってリカバリクロックを生成し出力するクロック出力回路である。例えば、位相の異なる複数のクロック(マルチクロック)のうちの、一つのクロックをリカバリクロックとして出力する。そして、DLL20は、ディレイライン21、位相比較回路22、チャージポンプ23を備えている。

【0037】

ディレイライン21は、抽出クロックと遅延制御信号とが入力され、遅延制御信号に応じて、抽出クロックを遅延させてリカバリクロックを生成する。さらに、ディレイライン21は、クロック抽出回路10の抽出範囲を抽出制御信号により制御する。例えば、リカバリクロックにより抽出範囲を制御する。

【0038】

位相比較回路22は、リカバリクロックが入力され、リカバリクロックの位相を検出し、位相差に応じた位相差信号を出力する。ここでは図示を省略しているが、例えば、位相比較回路22は、リカバリクロックと抽出クロックの位相を比較し、その位相差に応じて位相差信号を生成する。

【0039】

チャージポンプ23は、位相差信号が入力され、位相差信号の電圧レベルを昇圧し、遅延制御信号として出力する。この遅延制御信号によって、ディレイラインの遅延量が制御される。

【0040】

停止検出回路30は、抽出クロックとエンベデッド信号とを入力し、抽出クロックとエンベデッド信号とに基づいて抽出クロックの停止を検出する。そして、抽出クロックの停止を検出した場合、リセット信号をクロック抽出回路10に出力する。

【0041】

以下、停止検出回路30について説明するが、まず、停止検出回路30が検出対象とする抽出クロックについて説明する。

【0042】

図3は、クロック抽出回路10の正常時と異常時の抽出クロックを示している。クロック抽出回路10には、図3(a)のように、エンベデッド信号が入力されるとともに、DLL20から抽出制御信号が入力されている。

【0043】

正常時においては、図3(b)に示すように、クロック抽出回路10は、エンベッドクロックが入力されると、抽出制御信号で制御される範囲でクロック成分を抽出し、抽出クロックを生成する。

【0044】

そうすると、抽出された抽出クロックがDLL20に入力され、ディレイライン21、位相比較回路22、チャージポンプ23を介し、ディレイライン21にフィードバックされ、さらにDLL20に抽出クロックが入力され続けるとDLL20がロック状態となる。

【0045】

ところが、クロック抽出回路10の内部回路とDLL20からの入力状態により、クロックが抽出されない動作条件に陥る場合がある。具体的には、クロック抽出回路10は、不図示のフリップフロップなどの内部状態を保持する内部回路を有しており、この回路の内部状態が不安定となり異常な値になった場合に、誤動作しうる。

【0046】

このような異常時には、クロック抽出回路10は、クロックを正常に抽出できないため、抽出クロックの出力が停止する。すなわち、クロック抽出回路10の出力は、図3(c)や図3(d)に示すように、ハイレベルもしくはローレベルのままとなる。このようなクロック成分が抽出されず出力されない状態を抽出クロックの停止と呼ぶ。

【0047】

そうすると、ディレイライン21、位相比較回路22、チャージポンプ23にクロックが供給されなくなるため、フィードバックが起こらなくなり、DLL20がロックできない状態になってしまう。したがって、クロック抽出回路10は、内部状態によってクロックを抽出できなくなり、DLL20もロックできないため、クロック抽出回路10もDLL20も、動作が停止したままとなる。

【0048】

本発明では、この状態から確実に回復するために、停止検出回路30で、抽出クロックの停止を検出し、クロック抽出回路10をリセットする。

【0049】

次に、図4及び図5を用いて、本発明の停止検出回路30の構成及び動作について、その概略を説明する。

【0050】

図4に示されるように、停止検出回路30は、エンベデッド信号モニタ部31、抽出クロックモニタ部32、比較部33を備えている。

【0051】

エンベデッド信号モニタ部31は、エンベデッド信号が入力され、エンベデッド信号に基づいた第1の比較信号を出力する。すなわち、クロック抽出回路10に入力されている信号と同じエンベデッド信号に基づいた信号は、抽出クロックの停止を検出するための信号であり、比較部33で比較可能な信号である。

【0052】

抽出クロックモニタ部32は、抽出クロックが入力され、抽出クロックに基づいた第2の比較信号を出力する。すなわち、抽出クロックに基づいた信号は、抽出クロックの停止を検出するための信号であり、比較部33で比較可能な信号である。

【0053】

例えば、第1の比較信号及び第2の比較信号は、クロック発生回路1に入力される信号が高速シリアルI/Fによるエンベデッド信号であっても、両信号を確実なタイミングで比較動作が可能な周期の信号である。

【0054】

比較部33は、第1の比較信号及び第2の比較信号を比較し、比較結果に基づいて抽出クロックの停止を検出し、リセット信号を出力する。すなわち、エンベデッド信号に基づいた信号の信号レベルと、抽出クロックに基づいた信号レベルとを比較することで、抽出クロックの停止を検出する。エンベデッド信号に基づいた第1の比較信号が検出されている状態で、抽出クロックに基づいた第2の比較回路が検出されない場合には、抽出クロックが停止していると判断する。エンベデッド信号は、一定の周期以内に必ずクロックエッジが入力されることが保証されている。一方、停止の検査をする対象の抽出クロックは、この表示装置用駆動回路のシステムクロック(リカバリクロック)の元の信号であるため、その停止の検出をするためには、必ず動作するエンベデッド信号を利用する必要がある。このように、エンベデッド信号と抽出クロックの両信号を比較することでのみ、抽出クロックの停止を正確に検出することができる。

【0055】

図5を用いて、停止検出回路30の動作を説明すると、まず、駆動装置100を含むシステムに電源が投入されると(S101)、クロック抽出回路10、DLL20、停止検出回路30などの全ての内部回路に電源が供給され、各回路の動作が開始する。

【0056】

この実施例では、受信回路2およびDLL20はアナログ回路であり、クロック抽出回路10と検出回路30はディジタル回路である。アナログ回路は、電源電圧が規定値に達するまでは正常な動作を期待することはできないが、比較的回路が簡単なディジタル回路は電源電圧が低い段階から動作することができる。

【0057】

電源電圧がある程度以上に高くなった段階でエンベデッド信号が外部から入力され、受信回路2が動作する。ディジタル回路であるクロック抽出回路10と検出回路30は、前出の通りすでに動作できる状態になっているため、抽出クロックの停止判定が行われる(S102)。この停止判定は、後述のように所定の周期で行われる。すなわち、エンベデッド信号モニタ部31は、エンベデッド信号に基づき第1比較信号を生成し、抽出クロックモニタ部32は、抽出クロックに基づき第2の比較信号を生成し、比較部33は、第1の比較信号と第2の比較信号とを比較する。

【0058】

通常、電源立ち上げ時に入力するエンベデッド信号は、クロックエッジを含むデータだけが変化する信号やシリアル信号のデータが最も変化する信号(例えば、101010....)にするのが一般的である。

【0059】

電源投入(S101)直後は、前出の通りアナログ回路である受信回路2およびDLL20は正常に動作することが期待できない。そのため、しばらくは停止判定(S102)で抽出クロック停止と判定(S103 Yes)され、クロック抽出回路リセット(S104)を繰り返すことになる。これが従来技術のパワーオンリセットと同様の機能を果たす。従来技術と異なるのは、各種の条件が整って抽出クロックが停止していないと判定されると同時に、クロック抽出回路のリセットは行われなくなり、通常動作に入れる点である。つまり、電源投入後の表示装置用駆動回路の立ち上がり時間が必要最小限で済むという効果がある。

【0060】

停止判定の結果、抽出クロックが停止していないと判断された場合(S103)、クロック抽出回路のリセットは行われず、そのまま停止判定(S102)が繰り返し行われる。すなわち、比較部33は、第1の比較信号の信号レベルと第2の比較信号の信号レベルとが、一致していれば、抽出クロックは停止していないと判断し、リセット信号を出力しない。エンベデッド信号に基づいた信号がハイレベルで出力されていて、かつ、抽出クロックに基づいた信号もハイレベルで出力されている場合には、クロック抽出回路10が正常に動作していると判断される。また、エンベデッド信号に基づいた信号がローレベルで出力されていて、かつ、抽出クロックに基づいた信号もローレベルで出力されている場合も、同様である。

【0061】

停止判定の結果、抽出クロックが停止していると判断された場合(S103)、クロック抽出回路をリセットする(S104)。電源投入時以外の通常時は、リセットが終わってから、次の抽出クロックの停止判定(S102)までにはクロック抽出回路10は正常動作に戻るのが普通である。その後は、さらに停止判定(S102)が後述の所定の周期で繰り返し行われる。すなわち、比較部33は、第1の比較信号の信号レベルと第2の比較信号の信号レベルとが、不一致ならば、抽出クロックは停止していると判断し、リセット信号を出力する。エンベデッド信号に基づいた信号がハイレベルで出力されていて、かつ、図3の抽出クロック異常時(b)のように抽出クロックに基づいた信号がローレベルで出力されている場合には、クロック抽出回路10が異常であると判断される。これにより、例えば、抽出クロックがローレベルのままで停止していることが検出される。

【0062】

なお、抽出クロックがハイレベルのままで停止していることを検出することも可能である。例えば、図3の抽出クロック異常時(c)のように抽出クロックがハイレベルのままの場合、上記と同様に、エンベデッド信号に基づいた信号をハイレベル、かつ、抽出クロックに基づいた信号をローレベルとして、クロック停止を検出してもよいし、エンベデッド信号に基づいた信号をローレベル、かつ、抽出クロックに基づいた信号をハイレベルとして、抽出クロックの停止を検出してもよい。

【0063】

このように、常に抽出クロックの停止を所定の周期で繰り返し判定するため、電源投入時、クロック抽出回路から抽出クロックが出力されない場合、抽出クロックの停止を検出してリセットを行い、かつ、通常動作時に外来ノイズによりクロック抽出回路から抽出クロックが出力されない場合も、抽出クロックの停止を検出しリセットを行う。

【0064】

続いて、図6〜図9を用いて、本発明の停止検出回路30の構成及び動作について、具体的に説明する。

【0065】

図6に示されるように、エンベデッド信号モニタ部31は、エンベデッド信号を2のN乗分周する分周回路31aで構成される。この分周回路31aは、2のN乗分周するために、N個のフリップフロップ311〜31Nから構成されている。また、複数のフリップフロップ311〜31Nを縦列接続したカウンタ回路でもある。

【0066】

1段目のフリップフロップ311のクロック端子にエンベデッド信号が入力され、各フリップフロップは、反転出力端子がデータ入力端子に接続されており、正転出力端子が次段のフリップフロップのクロック端子に接続されている。N段目のフリップフロップ31Nの正転出力端子から、エンベデッド信号を2のN乗分周した2のN乗分周信号が出力される。ここでは、エンベデッド信号の2のN乗分周信号が第1の比較信号として出力される。

【0067】

このように、エンベデッド信号モニタ部31は、分周回路であり、フリーランカウンタで構成されているため、各フリップフロップの内部状態にかかわらず動作が可能である。すなわち、電源投入時や外来ノイズにより各フリップフロップの内部状態が不安定であった場合、カウンタの初期値が変動することはあっても、エンベデッド信号が入力さえすれば、常にカウンタ動作が行われ分周信号が生成される。この例では、消費電力が小さい非同期カウンタを使用しているが、もちろん、エンベデッド信号を入力クロックとする同期カウンタにしても同様の機能を果たす。

【0068】

抽出クロックモニタ部32は、分周信号をシフトするシフト回路32aで構成される。このシフト回路32aは、1つのフリップフロップ321を有している。フリップフロップ321は、抽出クロックが入力されるタイミングに応じて、エンベデッド信号の2のN乗分周信号をラッチし出力する。ここでは、エンベデッド信号の2のN乗分周信号を抽出クロックによってシフトしたシフト信号が、第2の比較信号として出力される。ここで、シフト回路32aのクロック信号(被検査信号)として抽出クロックを使用した例を示しているが、被検査信号は必ずしも抽出クロックには限らず、抽出クロックを元に動作する信号であれば何でもよい。例えば、リカバリークロック等も被検査信号として使用することができる。

【0069】

比較部33は、排他的論理和331及びフリップフロップ332で構成される。排他的論理和331は、エンベデッド信号の2のN乗分周信号と、フリップフロップ321で2のN乗分周信号が抽出クロックによりシフトされたシフト信号とを、排他的論理和演算した結果を出力する。すなわち、2のN乗分周信号とシフト信号とが、同じ信号レベルであれば、ローレベルを出力し、違う信号レベルであれば、ハイレベルを出力する。

【0070】

フリップフロップ332は、排他的論理和331の結果を所定のタイミングで出力する。出力するタイミングは、エンベデッド信号に基づいたタイミングである。すなわち、分周回路の分周信号のタイミングであり、ここでは、エンベデッド信号を2の(N−1)乗分周した2の(N−1)乗分周信号のタイミングである。2の(N−1)乗分周信号の立下りエッジのタイミングで、排他的論理和331の出力をラッチし、リセット信号として出力する。

【0071】

図7は、本発明の停止検出回路における、抽出クロックが正常に抽出されている場合の具体的な動作を示している。

【0072】

図7(a)のように、エンベデッド信号が、分周回路31aに入力されると、各フリップフロップにより順次分周された信号が出力される。すなわち、1段目のフリップフロップ311からは、エンベデッド信号を2分周した分周信号が出力され、図7(b)のように、N−1段目のフリップフロップ31(N−1)からは、2の(N−1)乗分周した分周信号が出力され、図7(c)のように、N段目のフリップフロップ31Nからは、2のN乗分周した分周信号が出力される。

【0073】

そして、図7(d)のように、シフト回路32aは、エンベデッド信号の2のN乗分周信号を、抽出クロックによってシフトしたシフト信号を出力する。すなわち、フリップフロップ321が抽出クロックの立上りタイミングでラッチした信号が出力される。ここでは、フリップフロップ321によって、2のN乗分周信号が、抽出クロックの1クロック分シフトされる。

【0074】

さらに、図7(f)のように、2の(N−1)乗分周信号の立下りのタイミングにおいて、2のN乗分周信号とシフト信号とがハイレベルであるため、リセット信号はローレベルのままとなる。すなわち、2の(N−1)乗分周信号の立下りのタイミングでは、2のN乗分周信号とシフト信号とが同じハイレベルであり、排他的論理和331の出力がローレベルであるため、フリップフロップ332の出力はローレベルである。

【0075】

このように、図7では、抽出クロックが停止していないため、抽出クロックによって2のN乗分周信号が必ずシフトされる。このシフト信号と、シフト前の2のN乗分周信号との排他的論理和は、2の(N−1)乗分周クロックの立下りエッジで常に等しくなり、フリップフロップの結果は常にローレベルとなる。したがって、クロック抽出回路10が抽出クロックを出力している間は、クロック抽出回路にはリセット信号が入力されない。

【0076】

図8は、本発明の停止検出回路における、抽出クロックが停止した場合の具体的な動作を示している。

【0077】

図8(a)〜(c)のように、図7と同様、分周回路31aでは、エンベデッド信号の2のN乗分周信号を出力している。しかし、ここでは、電源投入時や外来ノイズ等の影響によって、図8(e)のように、抽出クロックが停止している。

【0078】

そうすると、図8(d)のように、シフト回路32aからは、2のN乗分周信号をシフトしたシフト信号が出力されない。したがって、図8(f)のように、2の(N−1)乗分周信号の立下りのタイミングにおいて、2のN乗分周信号がハイレベルでシフト信号がローレベルであるため、リセット信号はハイレベルとなり、次の2の(N−1)乗分周信号の立下りのタイミングにおいて、2のN乗分周信号とシフト信号がローレベルであるため、リセット信号はローレベルとなり、ハイレベルとローレベルが繰り返される。

【0079】

リセット信号がハイレベルになると、クロック抽出回路10は、内部回路の状態が初期化されるため、異常状態が回復し、抽出クロックの生成が開始される。そうすると、図7の状態に戻り、抽出クロックが検出されるため、リセット信号の出力が停止する。例えば、図8では、リセット信号が2つ出力されているが、1つのリセット信号により抽出クロックの生成が開始されれば、1つのリセット信号のみとなる。また、2つのリセット信号によっても、抽出クロックの生成が開始されなければ、さらにリセット信号が出力され、抽出クロックの生成が開始されるまで繰り返される。

【0080】

このように、図8では、抽出クロックが停止しているため、シフト回路32aのシフト信号が固定値となり、エンベデッド信号の2のN乗分周信号は、ハイレベルとローレベルを繰り返す。そのため、2のN乗分周信号とシフト信号の排他的論理和は、2の(N−1)乗分周クロックの立下りエッジで交互に不一致となり、フリップフロップの出力結果はハイレベルとローレベルを繰り返す。そのため、2のN乗分周信号の周期でクロック抽出回路10にリセット信号の入力と解除とが繰り返される。これが、抽出クロックが動作するまで繰り返される。なお、図8では、抽出クロックがローレベルのまま停止した場合について説明したが、抽出クロックがハイレベルのまま停止した場合でも、シフト信号が生成されないため、リセット信号の入力と解除のタイミングが逆になるが、同様の動作となる。

【0081】

ここで、エンベデッド信号の2のN乗分周信号のハイレベル期間またはローレベル期間に、抽出クロックの検出を行うため、少なくとも、2のN乗分周信号の周期は、抽出クロックの周期よりも長いことが必要である。すなわち、2のN乗分周信号の周期は、入力エンベデッド信号とクロック抽出回路10の動作が正常であれば、抽出クロックが必ず含まれるエンベデッド信号に重畳されたシリアル信号のビット長の時間より長い長さである。図7、図8の例では、エンベデッド信号の2のN乗分周として8分周(2の3乗分周)した例である。この例では、エンベデッド信号に含まれる元のシリアルデータのデータ長が16ビット以下であることを想定している。エンベデッド信号に含まれる元のシリアルデータのデータ長の値より大きい分周数でエンベデッド信号を分周することで、抽出クロックを正確に検出することができる。

【0082】

というのも、エンベデッド信号は重畳したシリアルデータの値によって、先頭のクロックのエッジを含んで、これと同じエッジが最大でデータ長の半分発生する。これをシリアルデータのデータ長以上の分周数で分周することで、本来の抽出クロックの周期内に最大1回だけ抽出クロックの停止判定を行うようにすることができる。もちろん、シリアルデータの値がすべて同一(ハイだけ、またはローだけ)の場合は本来の抽出クロックの周期内に停止判定が発生しない場合があるが、エンベデッド信号の規格により先頭のクロックのエッジだけは必ず発生するため、停止判定の周期が多少延びるだけで本質的な問題は起こらない。

【0083】

なお、エンベデッド信号の2のN乗分周信号とシフト信号を比較するタイミングは、図7、図8では、エンベデッド信号の2の(N−1)乗分周信号の立下りのタイミングとしている。このタイミングが、2のN乗分周信号のハイレベル期間またはローレベル期間の中央付近となるため、2のN乗分周信号とシフト信号とを確実に比較することができる。図9(a)に示すように、エンベデッド信号の2のN乗分周信号とシフト信号との比較タイミングは、2のN乗分周信号のハイレベル期間とシフト信号のハイレベル期間とが重なるタイミングであれば、その他のタイミングでもよいが、誤りなく比較するために、できるだけ両信号のハイレベル期間の中央付近で比較することが好ましい。

【0084】

また、図7、図8では、エンベデッド信号の2のN乗分周信号とシフト信号とは、抽出クロックの1クロック分シフトした例を示した。図9(b)に示すように、2のN乗分周信号とシフト信号とは、比較するタイミングで重なっていれば、さらにシフトしてもよいが、誤りなく比較するために、できるだけ両信号のハイレベル期間がより長く重なっていることが好ましい。なお、1クロックよりも早いタイミングで、2のN乗分周信号をシフト回路から出力してもよい。

【0085】

以上のように、本発明では、エンベデッド信号からクロックを抽出するクロック抽出回路において、抽出クロックの出力が停止されたことを検出し、クロック抽出回路をリセットする。これにより、電源投入時や通常動作時であっても、クロック抽出回路をリセットするため、クロック抽出回路の内部状態を初期化し、抽出クロックの生成を再開させることが可能となる。

【0086】

また、エンベデッド信号と抽出クロックとに基づいて、抽出クロックの停止を検出するため、エンベデッド信号が一定周期でない場合でも、精度よく、抽出クロックの停止を検出することができる。

【0087】

従来のようにパワーオンリセット信号を用いなくても電源立ち上げ時のリセットが可能になるとともに、電源立ち上げ時のリセットが終了した後の通常動作時に抽出クロックが停止した場合についても回復が可能となる。

【0088】

また、十分なパワーオンリセット信号を得るためには、必要以上の時間を電源の立ち上げ時に必要とするが、本発明では、エンベデッド信号の分周数を元のシリアルデータのデータ長以上にして、エンベデッド信号のデータの変化を最大にすることで、必要最小限の待ち時間で電源の立ち上げを終了することができる。フリップフロップと排他的論理和により、内部状態に動作が影響されない構成としているため、電源投入時やノイズ等に影響されることなく、抽出クロックの停止を検出しリセットして抽出クロックを回復することが可能である。

【0089】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0090】

1 クロック発生回路

2 受信回路

3 シリアルパラレル変換回路

4 シフトレジスタラッチ回路

5 D/A変換回路

6 ボルテージフォロア回路

7 ロジック制御回路

8 クロックデータリカバリ回路

9 駆動信号出力回路

10 クロック抽出回路

20 DLL

21 ディレイライン

22 位相比較回路

23 チャージポンプ

30 停止検出回路

31 エンベデッド信号モニタ部

31a 分周回路

311〜31N フリップフロップ

32 抽出クロックモニタ部

32a シフト回路

321 フリップフロップ

33 比較部

331 排他的論理和

332 フリップフロップ

100 駆動装置

200 表示パネル

【技術分野】

【0001】

本発明はクロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法に関し、特にクロックをデータに重畳したエンベデッド信号からリカバリクロックを発生させるクロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法に関する。

【背景技術】

【0002】

近年、高速シリアルI/Fにおいて、送信側からはシリアルデータの先頭クロックをデータに埋め込んだエンベデッド(embedded)信号を送信し、受信側では受信したエンベデッド信号からシリアルデータの先頭クロックのエッジ情報を抽出し、その抽出した先頭クロックエッジから復元したリカバリクロック(再生クロック)でデータをサンプリングして元のシリアルデータを復元するデータ送受信方法が普及している。

【0003】

このような高速シリアルI/Fの受信回路では、入力されるエンベデッド信号に基づいて、データを抽出するリカバリクロックを発生させるために、DLL(Delay Locked Loop)が用いられている。

【0004】

DLLを用いたクロック発生回路として、例えば、特許文献1〜3が知られている。なお、特許文献1〜3には、エンベデッド信号については記載されていない。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−21706号公報

【特許文献2】特開2009−278528号公報

【特許文献3】特許第3945894号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

DLLは、基準信号に対しフィードバック制御することでロック状態となり、遅延信号を発生させている。このため、DLLを用いたクロック発生回路では、基準となる信号が停止すると、フィードバック制御ができなくなることから、クロックの生成も停止してしまう。基準となる信号が停止する原因としては、クロック発生回路の内部状態が不安定となることによる誤動作が考えられる。

【0007】

このような誤動作を防ぐため、特許文献3には、電源投入時に回路をリセットするパワーオンリセット信号が記載されている。

【0008】

図10は、従来のクロック発生回路における、パワーオンリセット信号によるリセット動作を示している。すなわち、装置に電源が投入されると(S901)、まず、パワーオンリセット回路が動作してパワーオンリセット信号が生成され(S902)、生成されたパワーオンリセット信号によってクロック発生回路の内部状態をリセットし(S903)、その後、クロックの発生が開始され通常動作となる(S904)。

【0009】

しかし、パワーオンリセット信号によるリセットでは、電源投入の電源の立上り条件等に影響されてリセットがかかる条件が制限される場合がある。

【0010】

図11は、電源投入時の電源電圧とパワーオンリセット信号の関係を示している。すなわち、パワーオンリセット信号は、電源投入後の電圧波形の立上りに従って生成される。図11(a)のように電圧波形の傾きが緩やかな場合には、パワーオンリセット信号のパルス幅はより広くなり、図11(b)のように電圧波形の傾きが急な場合には、パワーオンリセット信号のパルス幅はより狭くなる。したがって、電圧波形が急峻になると、パワーオンリセット信号が非常に細くなり、回路によっては正常にリセットできない場合がある。その場合には、クロック発生回路がリセットされずにクロック生成が停止したままとなる。なお、全ての電源立ち上がり波形に対して回路を確実にリセットするようなパワーオンリセット信号を生成しようとすると、表示装置メーカーに対して表示装置用駆動回路の電源立ち上げ時間の規格を決める必要があり、表示装置用駆動回路の汎用性を損なうことになる。また、電源立ち上げ時間規格はワースト条件でも守られる必要があるため、この規格で決めた時間はパワーオンリセットがずっと掛かっていることになり、ワースト条件以外の場合には必要のない時間を装置の立ち上げのためにエンドユーザを待たせることになってしまう。さらに、表示装置メーカーが電源の立ち上げ時間を短縮して電源投入後の表示装置の立ち上げ時間を短くしようとしても駆動回路がこの規格時間は立ち上がらないことになり、これも表示装置の駆動回路の汎用性を損なうことになる。

【0011】

また、パワーオンリセット信号によるリセットのみでは、通常動作後に回路が誤動作した場合、クロックを正常に生成することができない。

【0012】

図12は、従来のクロック発生回路において、パワーオンリセット後に誤動作が生じる場合の動作を示している。すなわち、図10で示したように、電源投入しパワーオンリセット後に通常動作となる(S901〜S904)。その後、外来ノイズ等の影響により回路の内部状態が不安定になると、クロックの生成が停止する(S905)。そして、そのまま内部状態が回復しないと、復帰せずにクロックの生成が停止したままとなる(S906)。

【0013】

このように、従来のクロック発生回路では、クロックの生成が停止した状態から回復するためにパワーオンリセット信号を用いても、電源投入時にリセットできない場合があるとともに、通常動作時に誤動作を起こした場合は正常な状態に回復することができないという問題があった。

【課題を解決するための手段】

【0014】

本発明に係るクロック発生回路は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、を備えるものである。

【0015】

また、本発明に係る表示装置用駆動回路は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、前記抽出クロックに対し遅延制御されたリカバリクロックを出力するクロック出力回路と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、前記リカバリクロックに基づき前記エンベデッド信号のシリアルデータをパラレルデータに変換するシリアルパラレル変換回路と、前記パラレルデータに応じて表示装置を駆動する駆動信号を出力する駆動信号出力回路と、を備えるものである。

【0016】

さらに、本発明に係るクロック発生回路の制御方法は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路を備えるクロック発生回路の制御方法であって、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記抽出クロックの停止を検出した場合、前記クロック抽出回路を初期状態にリセットするものである。

【0017】

本発明では、エンベデッド信号と抽出クロックとに基づき抽出クロックの停止を検出し、クロック抽出回路をリセットするため、電源投入時や通常動作時においてクロックが停止した場合であっても、より確実に正常な状態に回復することが可能となる。

【発明の効果】

【0018】

本発明によれば、電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法を提供することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態に係る表示システムの構成を示すブロック図である。

【図2】本発明の実施の形態に係るクロック発生回路の構成を示すブロック図である。

【図3】本発明の実施の形態に係るクロック発生回路の動作を示すタイミングチャートである。

【図4】本発明の実施の形態に係る停止検出回路の構成を示すブロック図である。

【図5】本発明の実施の形態に係る停止検出回路の動作を示すフローチャートである。

【図6】本発明の実施の形態に係る停止検出回路の回路構成を示す回路図である。

【図7】本発明の実施の形態に係る停止検出回路の動作を示すタイミングチャートである。

【図8】本発明の実施の形態に係る停止検出回路の動作を示すタイミングチャートである。

【図9】本発明の実施の形態に係る停止検出回路の動作を説明するための図である。

【図10】従来のクロック発生回路の動作を示すフローチャートである。

【図11】従来のクロック発生回路におけるパワーオンリセット信号を説明するための波形図である。

【図12】従来のクロック発生回路の動作を示すフローチャートである。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

【0021】

まず、図1を用いて、本発明の実施の形態に係る表示システムの構成について説明する。図に示されるように、この表示システムは、表示パネル(表示装置)200と、表示パネルを駆動する駆動装置(駆動回路)100を備えている。

【0022】

表示パネル200は、駆動装置100から供給される駆動信号に応じて、表示画素を駆動させ所望の表示を行う。表示パネル200は、例えば、液晶表示パネルやプラズマ表示パネル、有機EL表示パネル等である。表示パネル200は、複数の画素を駆動するために、複数のソース線や複数のゲート線が設けられており、駆動装置100の駆動信号が、ソース線やゲート線に供給される。

【0023】

駆動装置100は、表示データとクロックを含むエンベデッド信号が入力され、表示データに応じた駆動信号を出力する。そして、駆動装置100は、クロックデータリカバリ回路8と駆動信号出力回路9を備えている。例えば、駆動装置100は、1チップの半導体装置であるが、クロックデータリカバリ回路8と駆動信号出力回路9をそれぞれ1チップの半導体装置としてもよい。

【0024】

駆動装置100に入力されるエンベデッド信号は、高速シリアルI/Fが受信するシリアル信号であり、例えば、データ期間と呼ばれる期間では、クロック成分とデータ成分とが分離して含まれており、スルー期間と呼ばれる期間では、クロック成分のみが含まれている。

【0025】

クロックデータリカバリ回路8は、入力されるエンベデッド信号から、クロックを再生するとともに、シリアル信号をパラレル信号に変換する。そして、クロックデータリカバリ回路8は、受信回路2、シリアルパラレル変換回路3、クロック発生回路1を備えている。

【0026】

受信回路2は、入力されたエンベデッド信号をシリアルパラレル変換回路3とクロック発生回路1へ出力する。すなわち、受信回路2は、差動信号として入力される信号を、シリアルパラレル変換回路3及びクロック発生回路1で処理可能な、ハイレベルとローレベルからなるディジタル信号として出力する。なお、この例ではエンベデッド信号が小振幅差動信号であるため、受信回路2を設けているが、エンベデッド信号が例えばCMOS信号である場合は、受信回路2を設けずに、エンベデッド信号を直接、シリアルパラレル変換回路3及びクロック発生回路1へ入力してもよい。

【0027】

クロック発生回路1は、入力されるエンベデッド信号から、クロックを抽出してリカバリクロックを生成し、シリアルパラレル変換回路3へ出力する。クロック発生回路1については、後述する。

【0028】

シリアルパラレル変換回路3は、リカバリクロックに基づくタイミングで、エンベデッド信号に含まれるシリアル信号の表示データ(階調信号)をパラレル信号に変換する。

【0029】

駆動信号出力回路9は、パラレル信号に変換された表示データに応じて駆動信号を出力する。そして、駆動信号出力回路9は、シフトレジスタラッチ回路4、D/A変換回路5、ボルテージフォロア回路6、ロジック制御回路7を備えている。

【0030】

シフトレジスタラッチ回路4は、入力されたパラレル信号を、シフトレジスタにより順次ラッチ回路に出力数分の階調信号が揃うまで保持し、全てのパラレル信号(階調信号)がそろったタイミングでD/A変換回路5へ出力する。

【0031】

D/A変換回路5は駆動回路の出力数分のD/A変換回路を持ち、ロジック制御回路7の制御に従って、ディジタル信号として入力されるパラレル信号を、アナログ信号に変換しボルテージフォロア回路へ出力する。

【0032】

ボルテージフォロア回路6は駆動回路の出力数分のボルテージフォロアアンプ回路を持ち、ロジック制御回路7の制御に従って、入力されるアナログ信号を増幅して駆動信号を生成し、表示パネルへ出力する。

【0033】

次に、駆動装置100のクロックデータリカバリ回路8に設けられたクロック発生回路1について説明する。

【0034】

図2は、クロック発生回路1の構成を示している。図に示されるように、クロック発生回路1は、クロック抽出回路10、DLL(Delay Locked Loop)20及び停止検出回路30を備えている。

【0035】

クロック抽出回路10は、エンベデッド信号と抽出制御信号とが入力され、エンベデッド信号から、抽出制御信号に応じた抽出範囲でクロックを抽出し、抽出したクロックを抽出クロックとして出力する。また、リセット信号により、クロック抽出回路10の内部の回路状態を初期状態にリセットする。具体的には、リセット信号としてハイレベルの信号が入力されると、不図示のフリップフロップ等の状態がリセットされる。

【0036】

DLL20は、クロック抽出回路10が抽出した抽出クロックに対し、遅延制御を行ってリカバリクロックを生成し出力するクロック出力回路である。例えば、位相の異なる複数のクロック(マルチクロック)のうちの、一つのクロックをリカバリクロックとして出力する。そして、DLL20は、ディレイライン21、位相比較回路22、チャージポンプ23を備えている。

【0037】

ディレイライン21は、抽出クロックと遅延制御信号とが入力され、遅延制御信号に応じて、抽出クロックを遅延させてリカバリクロックを生成する。さらに、ディレイライン21は、クロック抽出回路10の抽出範囲を抽出制御信号により制御する。例えば、リカバリクロックにより抽出範囲を制御する。

【0038】

位相比較回路22は、リカバリクロックが入力され、リカバリクロックの位相を検出し、位相差に応じた位相差信号を出力する。ここでは図示を省略しているが、例えば、位相比較回路22は、リカバリクロックと抽出クロックの位相を比較し、その位相差に応じて位相差信号を生成する。

【0039】

チャージポンプ23は、位相差信号が入力され、位相差信号の電圧レベルを昇圧し、遅延制御信号として出力する。この遅延制御信号によって、ディレイラインの遅延量が制御される。

【0040】

停止検出回路30は、抽出クロックとエンベデッド信号とを入力し、抽出クロックとエンベデッド信号とに基づいて抽出クロックの停止を検出する。そして、抽出クロックの停止を検出した場合、リセット信号をクロック抽出回路10に出力する。

【0041】

以下、停止検出回路30について説明するが、まず、停止検出回路30が検出対象とする抽出クロックについて説明する。

【0042】

図3は、クロック抽出回路10の正常時と異常時の抽出クロックを示している。クロック抽出回路10には、図3(a)のように、エンベデッド信号が入力されるとともに、DLL20から抽出制御信号が入力されている。

【0043】

正常時においては、図3(b)に示すように、クロック抽出回路10は、エンベッドクロックが入力されると、抽出制御信号で制御される範囲でクロック成分を抽出し、抽出クロックを生成する。

【0044】

そうすると、抽出された抽出クロックがDLL20に入力され、ディレイライン21、位相比較回路22、チャージポンプ23を介し、ディレイライン21にフィードバックされ、さらにDLL20に抽出クロックが入力され続けるとDLL20がロック状態となる。

【0045】

ところが、クロック抽出回路10の内部回路とDLL20からの入力状態により、クロックが抽出されない動作条件に陥る場合がある。具体的には、クロック抽出回路10は、不図示のフリップフロップなどの内部状態を保持する内部回路を有しており、この回路の内部状態が不安定となり異常な値になった場合に、誤動作しうる。

【0046】

このような異常時には、クロック抽出回路10は、クロックを正常に抽出できないため、抽出クロックの出力が停止する。すなわち、クロック抽出回路10の出力は、図3(c)や図3(d)に示すように、ハイレベルもしくはローレベルのままとなる。このようなクロック成分が抽出されず出力されない状態を抽出クロックの停止と呼ぶ。

【0047】

そうすると、ディレイライン21、位相比較回路22、チャージポンプ23にクロックが供給されなくなるため、フィードバックが起こらなくなり、DLL20がロックできない状態になってしまう。したがって、クロック抽出回路10は、内部状態によってクロックを抽出できなくなり、DLL20もロックできないため、クロック抽出回路10もDLL20も、動作が停止したままとなる。

【0048】

本発明では、この状態から確実に回復するために、停止検出回路30で、抽出クロックの停止を検出し、クロック抽出回路10をリセットする。

【0049】

次に、図4及び図5を用いて、本発明の停止検出回路30の構成及び動作について、その概略を説明する。

【0050】

図4に示されるように、停止検出回路30は、エンベデッド信号モニタ部31、抽出クロックモニタ部32、比較部33を備えている。

【0051】

エンベデッド信号モニタ部31は、エンベデッド信号が入力され、エンベデッド信号に基づいた第1の比較信号を出力する。すなわち、クロック抽出回路10に入力されている信号と同じエンベデッド信号に基づいた信号は、抽出クロックの停止を検出するための信号であり、比較部33で比較可能な信号である。

【0052】

抽出クロックモニタ部32は、抽出クロックが入力され、抽出クロックに基づいた第2の比較信号を出力する。すなわち、抽出クロックに基づいた信号は、抽出クロックの停止を検出するための信号であり、比較部33で比較可能な信号である。

【0053】

例えば、第1の比較信号及び第2の比較信号は、クロック発生回路1に入力される信号が高速シリアルI/Fによるエンベデッド信号であっても、両信号を確実なタイミングで比較動作が可能な周期の信号である。

【0054】

比較部33は、第1の比較信号及び第2の比較信号を比較し、比較結果に基づいて抽出クロックの停止を検出し、リセット信号を出力する。すなわち、エンベデッド信号に基づいた信号の信号レベルと、抽出クロックに基づいた信号レベルとを比較することで、抽出クロックの停止を検出する。エンベデッド信号に基づいた第1の比較信号が検出されている状態で、抽出クロックに基づいた第2の比較回路が検出されない場合には、抽出クロックが停止していると判断する。エンベデッド信号は、一定の周期以内に必ずクロックエッジが入力されることが保証されている。一方、停止の検査をする対象の抽出クロックは、この表示装置用駆動回路のシステムクロック(リカバリクロック)の元の信号であるため、その停止の検出をするためには、必ず動作するエンベデッド信号を利用する必要がある。このように、エンベデッド信号と抽出クロックの両信号を比較することでのみ、抽出クロックの停止を正確に検出することができる。

【0055】

図5を用いて、停止検出回路30の動作を説明すると、まず、駆動装置100を含むシステムに電源が投入されると(S101)、クロック抽出回路10、DLL20、停止検出回路30などの全ての内部回路に電源が供給され、各回路の動作が開始する。

【0056】

この実施例では、受信回路2およびDLL20はアナログ回路であり、クロック抽出回路10と検出回路30はディジタル回路である。アナログ回路は、電源電圧が規定値に達するまでは正常な動作を期待することはできないが、比較的回路が簡単なディジタル回路は電源電圧が低い段階から動作することができる。

【0057】

電源電圧がある程度以上に高くなった段階でエンベデッド信号が外部から入力され、受信回路2が動作する。ディジタル回路であるクロック抽出回路10と検出回路30は、前出の通りすでに動作できる状態になっているため、抽出クロックの停止判定が行われる(S102)。この停止判定は、後述のように所定の周期で行われる。すなわち、エンベデッド信号モニタ部31は、エンベデッド信号に基づき第1比較信号を生成し、抽出クロックモニタ部32は、抽出クロックに基づき第2の比較信号を生成し、比較部33は、第1の比較信号と第2の比較信号とを比較する。

【0058】

通常、電源立ち上げ時に入力するエンベデッド信号は、クロックエッジを含むデータだけが変化する信号やシリアル信号のデータが最も変化する信号(例えば、101010....)にするのが一般的である。

【0059】

電源投入(S101)直後は、前出の通りアナログ回路である受信回路2およびDLL20は正常に動作することが期待できない。そのため、しばらくは停止判定(S102)で抽出クロック停止と判定(S103 Yes)され、クロック抽出回路リセット(S104)を繰り返すことになる。これが従来技術のパワーオンリセットと同様の機能を果たす。従来技術と異なるのは、各種の条件が整って抽出クロックが停止していないと判定されると同時に、クロック抽出回路のリセットは行われなくなり、通常動作に入れる点である。つまり、電源投入後の表示装置用駆動回路の立ち上がり時間が必要最小限で済むという効果がある。

【0060】

停止判定の結果、抽出クロックが停止していないと判断された場合(S103)、クロック抽出回路のリセットは行われず、そのまま停止判定(S102)が繰り返し行われる。すなわち、比較部33は、第1の比較信号の信号レベルと第2の比較信号の信号レベルとが、一致していれば、抽出クロックは停止していないと判断し、リセット信号を出力しない。エンベデッド信号に基づいた信号がハイレベルで出力されていて、かつ、抽出クロックに基づいた信号もハイレベルで出力されている場合には、クロック抽出回路10が正常に動作していると判断される。また、エンベデッド信号に基づいた信号がローレベルで出力されていて、かつ、抽出クロックに基づいた信号もローレベルで出力されている場合も、同様である。

【0061】

停止判定の結果、抽出クロックが停止していると判断された場合(S103)、クロック抽出回路をリセットする(S104)。電源投入時以外の通常時は、リセットが終わってから、次の抽出クロックの停止判定(S102)までにはクロック抽出回路10は正常動作に戻るのが普通である。その後は、さらに停止判定(S102)が後述の所定の周期で繰り返し行われる。すなわち、比較部33は、第1の比較信号の信号レベルと第2の比較信号の信号レベルとが、不一致ならば、抽出クロックは停止していると判断し、リセット信号を出力する。エンベデッド信号に基づいた信号がハイレベルで出力されていて、かつ、図3の抽出クロック異常時(b)のように抽出クロックに基づいた信号がローレベルで出力されている場合には、クロック抽出回路10が異常であると判断される。これにより、例えば、抽出クロックがローレベルのままで停止していることが検出される。

【0062】

なお、抽出クロックがハイレベルのままで停止していることを検出することも可能である。例えば、図3の抽出クロック異常時(c)のように抽出クロックがハイレベルのままの場合、上記と同様に、エンベデッド信号に基づいた信号をハイレベル、かつ、抽出クロックに基づいた信号をローレベルとして、クロック停止を検出してもよいし、エンベデッド信号に基づいた信号をローレベル、かつ、抽出クロックに基づいた信号をハイレベルとして、抽出クロックの停止を検出してもよい。

【0063】

このように、常に抽出クロックの停止を所定の周期で繰り返し判定するため、電源投入時、クロック抽出回路から抽出クロックが出力されない場合、抽出クロックの停止を検出してリセットを行い、かつ、通常動作時に外来ノイズによりクロック抽出回路から抽出クロックが出力されない場合も、抽出クロックの停止を検出しリセットを行う。

【0064】

続いて、図6〜図9を用いて、本発明の停止検出回路30の構成及び動作について、具体的に説明する。

【0065】

図6に示されるように、エンベデッド信号モニタ部31は、エンベデッド信号を2のN乗分周する分周回路31aで構成される。この分周回路31aは、2のN乗分周するために、N個のフリップフロップ311〜31Nから構成されている。また、複数のフリップフロップ311〜31Nを縦列接続したカウンタ回路でもある。

【0066】

1段目のフリップフロップ311のクロック端子にエンベデッド信号が入力され、各フリップフロップは、反転出力端子がデータ入力端子に接続されており、正転出力端子が次段のフリップフロップのクロック端子に接続されている。N段目のフリップフロップ31Nの正転出力端子から、エンベデッド信号を2のN乗分周した2のN乗分周信号が出力される。ここでは、エンベデッド信号の2のN乗分周信号が第1の比較信号として出力される。

【0067】

このように、エンベデッド信号モニタ部31は、分周回路であり、フリーランカウンタで構成されているため、各フリップフロップの内部状態にかかわらず動作が可能である。すなわち、電源投入時や外来ノイズにより各フリップフロップの内部状態が不安定であった場合、カウンタの初期値が変動することはあっても、エンベデッド信号が入力さえすれば、常にカウンタ動作が行われ分周信号が生成される。この例では、消費電力が小さい非同期カウンタを使用しているが、もちろん、エンベデッド信号を入力クロックとする同期カウンタにしても同様の機能を果たす。

【0068】

抽出クロックモニタ部32は、分周信号をシフトするシフト回路32aで構成される。このシフト回路32aは、1つのフリップフロップ321を有している。フリップフロップ321は、抽出クロックが入力されるタイミングに応じて、エンベデッド信号の2のN乗分周信号をラッチし出力する。ここでは、エンベデッド信号の2のN乗分周信号を抽出クロックによってシフトしたシフト信号が、第2の比較信号として出力される。ここで、シフト回路32aのクロック信号(被検査信号)として抽出クロックを使用した例を示しているが、被検査信号は必ずしも抽出クロックには限らず、抽出クロックを元に動作する信号であれば何でもよい。例えば、リカバリークロック等も被検査信号として使用することができる。

【0069】

比較部33は、排他的論理和331及びフリップフロップ332で構成される。排他的論理和331は、エンベデッド信号の2のN乗分周信号と、フリップフロップ321で2のN乗分周信号が抽出クロックによりシフトされたシフト信号とを、排他的論理和演算した結果を出力する。すなわち、2のN乗分周信号とシフト信号とが、同じ信号レベルであれば、ローレベルを出力し、違う信号レベルであれば、ハイレベルを出力する。

【0070】

フリップフロップ332は、排他的論理和331の結果を所定のタイミングで出力する。出力するタイミングは、エンベデッド信号に基づいたタイミングである。すなわち、分周回路の分周信号のタイミングであり、ここでは、エンベデッド信号を2の(N−1)乗分周した2の(N−1)乗分周信号のタイミングである。2の(N−1)乗分周信号の立下りエッジのタイミングで、排他的論理和331の出力をラッチし、リセット信号として出力する。

【0071】

図7は、本発明の停止検出回路における、抽出クロックが正常に抽出されている場合の具体的な動作を示している。

【0072】

図7(a)のように、エンベデッド信号が、分周回路31aに入力されると、各フリップフロップにより順次分周された信号が出力される。すなわち、1段目のフリップフロップ311からは、エンベデッド信号を2分周した分周信号が出力され、図7(b)のように、N−1段目のフリップフロップ31(N−1)からは、2の(N−1)乗分周した分周信号が出力され、図7(c)のように、N段目のフリップフロップ31Nからは、2のN乗分周した分周信号が出力される。

【0073】

そして、図7(d)のように、シフト回路32aは、エンベデッド信号の2のN乗分周信号を、抽出クロックによってシフトしたシフト信号を出力する。すなわち、フリップフロップ321が抽出クロックの立上りタイミングでラッチした信号が出力される。ここでは、フリップフロップ321によって、2のN乗分周信号が、抽出クロックの1クロック分シフトされる。

【0074】

さらに、図7(f)のように、2の(N−1)乗分周信号の立下りのタイミングにおいて、2のN乗分周信号とシフト信号とがハイレベルであるため、リセット信号はローレベルのままとなる。すなわち、2の(N−1)乗分周信号の立下りのタイミングでは、2のN乗分周信号とシフト信号とが同じハイレベルであり、排他的論理和331の出力がローレベルであるため、フリップフロップ332の出力はローレベルである。

【0075】

このように、図7では、抽出クロックが停止していないため、抽出クロックによって2のN乗分周信号が必ずシフトされる。このシフト信号と、シフト前の2のN乗分周信号との排他的論理和は、2の(N−1)乗分周クロックの立下りエッジで常に等しくなり、フリップフロップの結果は常にローレベルとなる。したがって、クロック抽出回路10が抽出クロックを出力している間は、クロック抽出回路にはリセット信号が入力されない。

【0076】

図8は、本発明の停止検出回路における、抽出クロックが停止した場合の具体的な動作を示している。

【0077】

図8(a)〜(c)のように、図7と同様、分周回路31aでは、エンベデッド信号の2のN乗分周信号を出力している。しかし、ここでは、電源投入時や外来ノイズ等の影響によって、図8(e)のように、抽出クロックが停止している。

【0078】

そうすると、図8(d)のように、シフト回路32aからは、2のN乗分周信号をシフトしたシフト信号が出力されない。したがって、図8(f)のように、2の(N−1)乗分周信号の立下りのタイミングにおいて、2のN乗分周信号がハイレベルでシフト信号がローレベルであるため、リセット信号はハイレベルとなり、次の2の(N−1)乗分周信号の立下りのタイミングにおいて、2のN乗分周信号とシフト信号がローレベルであるため、リセット信号はローレベルとなり、ハイレベルとローレベルが繰り返される。

【0079】

リセット信号がハイレベルになると、クロック抽出回路10は、内部回路の状態が初期化されるため、異常状態が回復し、抽出クロックの生成が開始される。そうすると、図7の状態に戻り、抽出クロックが検出されるため、リセット信号の出力が停止する。例えば、図8では、リセット信号が2つ出力されているが、1つのリセット信号により抽出クロックの生成が開始されれば、1つのリセット信号のみとなる。また、2つのリセット信号によっても、抽出クロックの生成が開始されなければ、さらにリセット信号が出力され、抽出クロックの生成が開始されるまで繰り返される。

【0080】

このように、図8では、抽出クロックが停止しているため、シフト回路32aのシフト信号が固定値となり、エンベデッド信号の2のN乗分周信号は、ハイレベルとローレベルを繰り返す。そのため、2のN乗分周信号とシフト信号の排他的論理和は、2の(N−1)乗分周クロックの立下りエッジで交互に不一致となり、フリップフロップの出力結果はハイレベルとローレベルを繰り返す。そのため、2のN乗分周信号の周期でクロック抽出回路10にリセット信号の入力と解除とが繰り返される。これが、抽出クロックが動作するまで繰り返される。なお、図8では、抽出クロックがローレベルのまま停止した場合について説明したが、抽出クロックがハイレベルのまま停止した場合でも、シフト信号が生成されないため、リセット信号の入力と解除のタイミングが逆になるが、同様の動作となる。

【0081】

ここで、エンベデッド信号の2のN乗分周信号のハイレベル期間またはローレベル期間に、抽出クロックの検出を行うため、少なくとも、2のN乗分周信号の周期は、抽出クロックの周期よりも長いことが必要である。すなわち、2のN乗分周信号の周期は、入力エンベデッド信号とクロック抽出回路10の動作が正常であれば、抽出クロックが必ず含まれるエンベデッド信号に重畳されたシリアル信号のビット長の時間より長い長さである。図7、図8の例では、エンベデッド信号の2のN乗分周として8分周(2の3乗分周)した例である。この例では、エンベデッド信号に含まれる元のシリアルデータのデータ長が16ビット以下であることを想定している。エンベデッド信号に含まれる元のシリアルデータのデータ長の値より大きい分周数でエンベデッド信号を分周することで、抽出クロックを正確に検出することができる。

【0082】

というのも、エンベデッド信号は重畳したシリアルデータの値によって、先頭のクロックのエッジを含んで、これと同じエッジが最大でデータ長の半分発生する。これをシリアルデータのデータ長以上の分周数で分周することで、本来の抽出クロックの周期内に最大1回だけ抽出クロックの停止判定を行うようにすることができる。もちろん、シリアルデータの値がすべて同一(ハイだけ、またはローだけ)の場合は本来の抽出クロックの周期内に停止判定が発生しない場合があるが、エンベデッド信号の規格により先頭のクロックのエッジだけは必ず発生するため、停止判定の周期が多少延びるだけで本質的な問題は起こらない。

【0083】

なお、エンベデッド信号の2のN乗分周信号とシフト信号を比較するタイミングは、図7、図8では、エンベデッド信号の2の(N−1)乗分周信号の立下りのタイミングとしている。このタイミングが、2のN乗分周信号のハイレベル期間またはローレベル期間の中央付近となるため、2のN乗分周信号とシフト信号とを確実に比較することができる。図9(a)に示すように、エンベデッド信号の2のN乗分周信号とシフト信号との比較タイミングは、2のN乗分周信号のハイレベル期間とシフト信号のハイレベル期間とが重なるタイミングであれば、その他のタイミングでもよいが、誤りなく比較するために、できるだけ両信号のハイレベル期間の中央付近で比較することが好ましい。

【0084】

また、図7、図8では、エンベデッド信号の2のN乗分周信号とシフト信号とは、抽出クロックの1クロック分シフトした例を示した。図9(b)に示すように、2のN乗分周信号とシフト信号とは、比較するタイミングで重なっていれば、さらにシフトしてもよいが、誤りなく比較するために、できるだけ両信号のハイレベル期間がより長く重なっていることが好ましい。なお、1クロックよりも早いタイミングで、2のN乗分周信号をシフト回路から出力してもよい。

【0085】

以上のように、本発明では、エンベデッド信号からクロックを抽出するクロック抽出回路において、抽出クロックの出力が停止されたことを検出し、クロック抽出回路をリセットする。これにより、電源投入時や通常動作時であっても、クロック抽出回路をリセットするため、クロック抽出回路の内部状態を初期化し、抽出クロックの生成を再開させることが可能となる。

【0086】

また、エンベデッド信号と抽出クロックとに基づいて、抽出クロックの停止を検出するため、エンベデッド信号が一定周期でない場合でも、精度よく、抽出クロックの停止を検出することができる。

【0087】

従来のようにパワーオンリセット信号を用いなくても電源立ち上げ時のリセットが可能になるとともに、電源立ち上げ時のリセットが終了した後の通常動作時に抽出クロックが停止した場合についても回復が可能となる。

【0088】

また、十分なパワーオンリセット信号を得るためには、必要以上の時間を電源の立ち上げ時に必要とするが、本発明では、エンベデッド信号の分周数を元のシリアルデータのデータ長以上にして、エンベデッド信号のデータの変化を最大にすることで、必要最小限の待ち時間で電源の立ち上げを終了することができる。フリップフロップと排他的論理和により、内部状態に動作が影響されない構成としているため、電源投入時やノイズ等に影響されることなく、抽出クロックの停止を検出しリセットして抽出クロックを回復することが可能である。

【0089】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0090】

1 クロック発生回路

2 受信回路

3 シリアルパラレル変換回路

4 シフトレジスタラッチ回路

5 D/A変換回路

6 ボルテージフォロア回路

7 ロジック制御回路

8 クロックデータリカバリ回路

9 駆動信号出力回路

10 クロック抽出回路

20 DLL

21 ディレイライン

22 位相比較回路

23 チャージポンプ

30 停止検出回路

31 エンベデッド信号モニタ部

31a 分周回路

311〜31N フリップフロップ

32 抽出クロックモニタ部

32a シフト回路

321 フリップフロップ

33 比較部

331 排他的論理和

332 フリップフロップ

100 駆動装置

200 表示パネル

【特許請求の範囲】

【請求項1】

クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、

前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、を備えるクロック発生回路。

【請求項2】

前記停止検出回路は、前記エンベデッド信号が検出されている状態で、前記抽出クロックが検出されない場合、前記リセット信号を出力する、請求項1に記載のクロック発生回路。

【請求項3】

前記停止検出回路は、

前記エンベデッド信号に基づき第1の比較信号を生成するエンベデッド信号モニタ部と、

前記抽出クロックに基づき第2の比較信号を生成する抽出クロックモニタ部と、

前記第1の比較信号と前記第2の比較信号とを比較し、前記比較した結果に基づいて前記リセット信号を出力する比較部と、を備える請求項1または2に記載のクロック発生回路。

【請求項4】

前記エンベデッド信号モニタ部は、前記エンベデッド信号を分周する分周回路であり、

前記第1の比較信号は、エンベデッド信号を分周した分周信号である、請求項3に記載のクロック発生回路。

【請求項5】

前記データは固定のデータ長を持つシリアル信号であり、前記分周回路は、前記エンベデッド信号を前記シリアル信号のデータ長以上の数に分周する分周回路である、請求項4に記載のクロック発生回路。

【請求項6】

前記分周回路は、前記抽出クロックの周期よりも分周信号の周期が長くなるように、前記エンベデッド信号を分周する、請求項4に記載のクロック発生回路。

【請求項7】

前記抽出クロックモニタ部は、前記抽出クロックと前記第1の比較信号に基づき、前記第2の比較信号を生成する、請求項3乃至6のいずれかに記載のクロック発生回路。

【請求項8】

前記抽出クロックモニタ部は、前記抽出クロックに応じて、前記第1の比較信号のタイミングをシフトした前記第2の比較信号を生成するシフト回路である、請求項7に記載のクロック発生回路。

【請求項9】

前記シフト回路は、フリップフロップを有し、

前記フリップフロップは、前記抽出クロックに応じて、前記第1の比較信号をラッチし、前記ラッチした信号を前記第2の比較信号として出力する、請求項8に記載のクロック発生回路。

【請求項10】

前記比較部は、前記第1の比較信号の信号レベルと前記第2の比較信号の信号レベルとが、不一致の場合に、前記リセット信号を出力する、請求項3乃至9のいずれかに記載のクロック発生回路。

【請求項11】

前記比較部は、排他的論理和回路を有し、

前記排他的論理和回路は、前記第1の比較信号と前記第2の比較信号とに対し排他的論理和演算を行い、当該演算結果を前記リセット信号として出力する、請求項10に記載のクロック発生回路。

【請求項12】

前記比較部は、前記抽出クロックが出力されている状態のときに、前記第1の比較信号のハイレベル期間と前記第2の比較信号のハイレベル期間とが重なるタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至11のいずれか一つに記載のクロック発生回路。

【請求項13】

前記比較部は、前記エンベデッド信号に基づいたタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至12のいずれか一つに記載のクロック発生回路。

【請求項14】

前記比較部は、前記第1の比較信号の周期よりも短い周期のタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至13のいずれか一つに記載のクロック発生回路。

【請求項15】

前記第1の比較信号は、前記エンベデッド信号を2のN乗分周(Nは自然数)した分周信号であり、

前記比較部は、前記エンベデッド信号を2の(N−1)乗分周した分周信号のタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至14のいずれか一つに記載のクロック発生回路。

【請求項16】

前記比較部は、フリップフロップを有し、

前記フリップフロップは、前記エンベデッド信号を2の(N−1)乗分周した分周信号のタイミングで、前記第1の比較信号と前記第2の比較信号との比較結果をラッチし、前記ラッチした信号を前記リセット信号として出力する、請求項15に記載のクロック発生回路。

【請求項17】

前記クロック出力回路は、クロックの抽出範囲を制御する抽出制御信号を出力し、

前記クロック抽出回路は、前記抽出制御信号に基づいて、前記エンベデッド信号から抽出クロックを抽出する、請求項1乃至16のいずれかに記載のクロック発生回路。

【請求項18】

前記クロック出力回路は、遅延ロックループ回路であり、

前記遅延ロックループ回路は、前記抽出クロックから遅延信号を生成するディレイライン回路と、前記遅延信号と前記抽出クロックとの位相差に基づいて位相差信号を生成する位相比較回路と、前記位相差信号の電圧レベルを昇圧して前記ディレイライン回路の遅延を制御するするチャージポンプ回路とを有する、請求項1乃至17のいずれか一つに記載のクロック発生回路。

【請求項19】

クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、

前記抽出クロックに対し遅延制御されたリカバリクロックを出力するクロック出力回路と、

前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、

前記リカバリクロックに基づき前記エンベデッド信号のシリアルデータをパラレルデータに変換するシリアルパラレル変換回路と、

前記パラレルデータに応じて表示装置を駆動する駆動信号を出力する駆動信号出力回路と、を備える表示装置用駆動回路。

【請求項20】

クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路を備えるクロック発生回路の制御方法であって、

前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、

前記抽出クロックの停止を検出した場合、前記クロック抽出回路を初期状態にリセットする、クロック発生回路の制御方法。

【請求項1】

クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、

前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、を備えるクロック発生回路。

【請求項2】

前記停止検出回路は、前記エンベデッド信号が検出されている状態で、前記抽出クロックが検出されない場合、前記リセット信号を出力する、請求項1に記載のクロック発生回路。

【請求項3】

前記停止検出回路は、

前記エンベデッド信号に基づき第1の比較信号を生成するエンベデッド信号モニタ部と、

前記抽出クロックに基づき第2の比較信号を生成する抽出クロックモニタ部と、

前記第1の比較信号と前記第2の比較信号とを比較し、前記比較した結果に基づいて前記リセット信号を出力する比較部と、を備える請求項1または2に記載のクロック発生回路。

【請求項4】

前記エンベデッド信号モニタ部は、前記エンベデッド信号を分周する分周回路であり、

前記第1の比較信号は、エンベデッド信号を分周した分周信号である、請求項3に記載のクロック発生回路。

【請求項5】

前記データは固定のデータ長を持つシリアル信号であり、前記分周回路は、前記エンベデッド信号を前記シリアル信号のデータ長以上の数に分周する分周回路である、請求項4に記載のクロック発生回路。

【請求項6】

前記分周回路は、前記抽出クロックの周期よりも分周信号の周期が長くなるように、前記エンベデッド信号を分周する、請求項4に記載のクロック発生回路。

【請求項7】

前記抽出クロックモニタ部は、前記抽出クロックと前記第1の比較信号に基づき、前記第2の比較信号を生成する、請求項3乃至6のいずれかに記載のクロック発生回路。

【請求項8】

前記抽出クロックモニタ部は、前記抽出クロックに応じて、前記第1の比較信号のタイミングをシフトした前記第2の比較信号を生成するシフト回路である、請求項7に記載のクロック発生回路。

【請求項9】

前記シフト回路は、フリップフロップを有し、

前記フリップフロップは、前記抽出クロックに応じて、前記第1の比較信号をラッチし、前記ラッチした信号を前記第2の比較信号として出力する、請求項8に記載のクロック発生回路。

【請求項10】

前記比較部は、前記第1の比較信号の信号レベルと前記第2の比較信号の信号レベルとが、不一致の場合に、前記リセット信号を出力する、請求項3乃至9のいずれかに記載のクロック発生回路。

【請求項11】

前記比較部は、排他的論理和回路を有し、

前記排他的論理和回路は、前記第1の比較信号と前記第2の比較信号とに対し排他的論理和演算を行い、当該演算結果を前記リセット信号として出力する、請求項10に記載のクロック発生回路。

【請求項12】

前記比較部は、前記抽出クロックが出力されている状態のときに、前記第1の比較信号のハイレベル期間と前記第2の比較信号のハイレベル期間とが重なるタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至11のいずれか一つに記載のクロック発生回路。

【請求項13】

前記比較部は、前記エンベデッド信号に基づいたタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至12のいずれか一つに記載のクロック発生回路。

【請求項14】

前記比較部は、前記第1の比較信号の周期よりも短い周期のタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至13のいずれか一つに記載のクロック発生回路。

【請求項15】

前記第1の比較信号は、前記エンベデッド信号を2のN乗分周(Nは自然数)した分周信号であり、

前記比較部は、前記エンベデッド信号を2の(N−1)乗分周した分周信号のタイミングで、前記第1の比較信号と前記第2の比較信号とを比較する、請求項3乃至14のいずれか一つに記載のクロック発生回路。

【請求項16】

前記比較部は、フリップフロップを有し、

前記フリップフロップは、前記エンベデッド信号を2の(N−1)乗分周した分周信号のタイミングで、前記第1の比較信号と前記第2の比較信号との比較結果をラッチし、前記ラッチした信号を前記リセット信号として出力する、請求項15に記載のクロック発生回路。

【請求項17】

前記クロック出力回路は、クロックの抽出範囲を制御する抽出制御信号を出力し、

前記クロック抽出回路は、前記抽出制御信号に基づいて、前記エンベデッド信号から抽出クロックを抽出する、請求項1乃至16のいずれかに記載のクロック発生回路。

【請求項18】

前記クロック出力回路は、遅延ロックループ回路であり、

前記遅延ロックループ回路は、前記抽出クロックから遅延信号を生成するディレイライン回路と、前記遅延信号と前記抽出クロックとの位相差に基づいて位相差信号を生成する位相比較回路と、前記位相差信号の電圧レベルを昇圧して前記ディレイライン回路の遅延を制御するするチャージポンプ回路とを有する、請求項1乃至17のいずれか一つに記載のクロック発生回路。

【請求項19】

クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路と、

前記抽出クロックに対し遅延制御されたリカバリクロックを出力するクロック出力回路と、

前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路と、

前記リカバリクロックに基づき前記エンベデッド信号のシリアルデータをパラレルデータに変換するシリアルパラレル変換回路と、

前記パラレルデータに応じて表示装置を駆動する駆動信号を出力する駆動信号出力回路と、を備える表示装置用駆動回路。

【請求項20】

クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路を備えるクロック発生回路の制御方法であって、

前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、

前記抽出クロックの停止を検出した場合、前記クロック抽出回路を初期状態にリセットする、クロック発生回路の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−249072(P2012−249072A)

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願番号】特願2011−119141(P2011−119141)

【出願日】平成23年5月27日(2011.5.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願日】平成23年5月27日(2011.5.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]