グラフィックスコントローラ、グラフィックスコントローラを備えるシステム、同システムにおける周辺装置への電力切断制御方法、および同方法を機械で実行可能な命令プログラムを含んだ機械可読媒体

【課題】電力切断保護回路を制御するための回路及び方法。

【解決手段】電力切断保護制御回路及び方法。メモリペア及び選択回路を設ける。メモリペアはその第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納されたデータをそれぞれの記憶出力に供給する。メモリペアには第1及び第2記憶素子のうちの一つの出力をスイッチの第1制御状態に対応するようにさせ、第1及び第2記憶素子の他方をスイッチの第2制御状態に対応するようにさせる極性選択入力がある。選択回路は入力がメモリペアのそれぞれの記憶出力に接続され、出力がスイッチを制御するためにスイッチの制御線に接続されている。選択回路の選択線は、第1及び第2記憶素子の記憶出力の一方又は他方を選択するために、入力間で選択する。

【解決手段】電力切断保護制御回路及び方法。メモリペア及び選択回路を設ける。メモリペアはその第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納されたデータをそれぞれの記憶出力に供給する。メモリペアには第1及び第2記憶素子のうちの一つの出力をスイッチの第1制御状態に対応するようにさせ、第1及び第2記憶素子の他方をスイッチの第2制御状態に対応するようにさせる極性選択入力がある。選択回路は入力がメモリペアのそれぞれの記憶出力に接続され、出力がスイッチを制御するためにスイッチの制御線に接続されている。選択回路の選択線は、第1及び第2記憶素子の記憶出力の一方又は他方を選択するために、入力間で選択する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、特にグラフィックスコントローラ及び周辺装置を含んで構成されたシステムで使用するための電力切断保護回路を制御するための回路及び方法に関する。より具体的には、周辺装置及びグラフィックスコントローラに共通に供給される電力の損失に起因するダメージからグラフィックスコントローラを守るためのそうした回路及び方法に関する発明である。

【背景技術】

【0002】

グラフィックスディスプレイシステムは、一般に、LCDパネルなどグラフィックス表示装置とホストCPUとの間にグラフィックスコントローラチップを用いている。概して、そうしたシステムは一つ以上の周辺装置も含んでいる。例えば、携帯電話では、カメラ周辺装置をグラフィックスコントローラに接続するのがますます一般的になってきている。カメラもホストCPUも対応する画像データ集合を供給する機能を有する。グラフィックスコントローラは、表示装置に供給するためのデータ集合間で選択することも、或いは表示装置に供給するために一つのデータ集合をもう一つのデータ集合の上にオーバーレイすることもできる。

【0003】

周辺装置がカメラの場合、グラフィックスコントローラは周辺装置から画像データを受け取る。もしくは、データを周辺装置に供給することも可能である。どちらにしても、普通はグラフィックスコントローラと周辺装置とは異なる電圧レベルで電力供給されるから、グラフィックスコントローラと周辺装置との間で交換されるデータは、一般的に、レベルシフトされなければならない。そのために、グラフィックスコントローラには、例えば、パラレルデータバスのビット毎にレベルシフタが設けられる。レベルシフタは一般的にCMOS技術で形成される。

【0004】

グラフィックスコントローラには各レベルシフタの片側に電力を供給するために周辺装置から電力を受け取るための端子がある一方、内部で、グラフィックスコントローラが使用する電力は各レベルシフタの他方の側に供給される。周辺装置からの電力がオンになっている限り、レベルシフタは正常に機能する。

【0005】

それに対して、グラフィックスコントローラは電力がオンのままの状態で、周辺装置の電力がオフになった場合には、CMOSのラッチアップが原因でレベルシフタにダメージが生じる。それでも、例えば、周辺装置から受け取った画像を処理しているときの電力消費を減らすために、グラフィックスコントローラの電力がオンになっている間に周辺装置の電力をオフにすることが好ましい場合が多い。

【0006】

この問題は、グラフィックスコントローラに電力切断保護回路を設けることで解決されてきた。電力切断保護回路は、ホストCPUが周辺装置をオフにするのと実質的に同時にホストCPUが書きこむレジスタを含んで構成された別の回路によって制御される。レベルシフタを接地に接続しているそれぞれのMOSFETをオンにするのにレジスタの内容を使用する。こうすると、周辺装置からの電力が切断されたときレベルシフタのCMOSラッチアップを防ぐことができる。

【0007】

この問題解決法は完全とはいえない。周辺装置の電力がオフになるとグラフィックスコントローラがリセットされる場合には、MOSFETが再びオフになってしまうためにレジスタの内容が失われるので、レベルシフタは切断回路が解決するはずだった問題に直面する。

【0008】

【特許文献1】米国特許第6,101,600号明細書

【発明の開示】

【発明が解決しようとする課題】

【0009】

それゆえに、先行技術で提供されてきた保護よりも一層ロバストな保護を提供できる電力切断保護回路を制御するための回路及び方法に対するニーズがある。

【課題を解決するための手段】

【0010】

グラフィックスコントローラで使用するための、本発明による好適な電力切断保護制御回路及び方法を開示している。グラフィックスコントローラは周辺装置に接続され、ホストによって制御される。グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラで信号を処理するのに適した別の電圧レベルにシフトするためのレベルシフタを含んで構成されている。レベルシフタと接地との間の電流経路にスイッチが設けられている。このスイッチは、スイッチのそれぞれの第1及び第2制御状態でオン又はオフである。

【0011】

好適な電力切断制御回路はメモリペアと選択回路とを含んで構成される。メモリペアは、ペアの第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納したデータをそれぞれの記憶出力に供給する。メモリペアは、第1及び第2記憶素子のうちの一方の記憶データ出力をスイッチの第1制御状態に対応させ、他方の記憶データ出力をスイッチの第2制御状態に対応させるようにする極性選択入力を有している。選択回路は入力がメモリペアのそれぞれの記憶出力に接続され、出力がスイッチを制御するためのスイッチの制御線に接続されている。選択回路の選択線は、第1及び第2記憶素子の記憶出力の一方又は他方を選択するために、入力間で選択する。

【0012】

対応する方法及び媒体も開示している。

【0013】

本章で述べた概要は、図面及び詳細な説明の中で何を説明しているかを大まかに判定する手段として提供しているのであって、発明の範囲を限定するつもりはないことを理解するべきである。本発明の目的、特徴、作用効果については、添付の図面と共に以下に述べる詳細な説明を考慮すれば容易に理解できるだろう。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施形態を図面に基づいて説明する。

【0015】

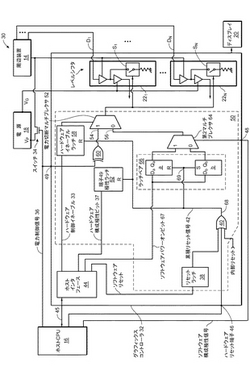

図1に示すのは、グラフィックスコントローラ12、カメラなど周辺装置14、ホストCPU16、安定化電源18、及びLCDパネルなどグラフィックス表示装置20を有する典型的な電子コンピューティング及び表示システム10の電力切断保護回路8を制御するための先行技術による回路である。グラフィックスコントローラは、一般的に、画像データを組み合わせてコンポジットにするために、カメラ及びCPUから流れてくる画像データを管理し、そのコンポジットデータを表示装置に供給する。ホストCPU16はグラフィックスコントローラ内のホストインタフェース24を介してグラフィックスコントローラ12と通信する。

【0016】

本発明の好適な文脈であるシステム10は構成要素8及び12〜20で形成されているが、システムの動作の仕方及びシステムの具体的な形は大きく異なって構わない。例えば、ホストはコンピュータ又はCPU以外の何かで構わないし、グラフィックス表示装置が不要になるように発明の電力切断制御回路及び方法をグラフィックスコントローラ以外のデバイスやチップに実施しても構わない。また、周辺装置はカメラ以外の何かで構わない。

【0017】

Nは一般的に8であるとして、周辺装置14は幾つかのデータ線D1 - DNを備える。電源はグラフィックスコントローラ12及び周辺装置14それぞれに電力供給するための2つの電源出力VGとVPを備える。データ線D毎にレベルシフタがあると考えるとして、2つの電圧は各々レベルシフタ221及び22Nのそれぞれの側に供給される。レベルシフタは内部処理するためにグラフィックスコントローラにレベルシフトされたデータを供給する。しかしながら、制御信号又はその他の信号をシフトするためにもレベルシフタを使用して構わない。

【0018】

スイッチS1〜SNを制御するためにレジスタ"R"がグラフィックスコントローラに備えられている。スイッチは閉じた状態のときそれぞれのレベルシフタ22を接地に接続する。スイッチSは電力切断保護回路の役目を果たす。スイッチは普通はMOSFETだけれども、任意の所望する技術のもので構わない。

【0019】

ホストCPU16は、典型的にはMOSFETのスイッチ26を用いて周辺装置だけでなくグラフィックスコントローラ12にも供給される電力VPを制御する。CPUはスイッチ26を先ずオフにし、その後、"1"をレジスタ"R"に書き込むようホストインタフェース24にコマンドを出す。レジスタ"R"の出力はバッファ28に接続されている。バッファ28はスイッチSを制御するための信号を駆動する。"1"がレジスタ"R"に格納されることにより、バッファ28はスイッチSをオンにする信号を駆動する。

【0020】

CPU16は、リセット線30を起動することによって、いつでもリセットするようグラフィックスコントローラ12に命令することができる。しかしながら、グラフィックスコントローラがリセットされると、レジスタ"R"の内容が失われる。つまり、"1"は"0"で置き換えられる。これがスイッチSをオフにするので、レベルシフタ22に大電流が生じる。これは電力を消費してCMOSラッチアップを引き起こすことがある。

【0021】

この問題は、レジスタ"R"に("1"の代わりに)"0"を格納するとスイッチ"S"がオンになるようにグラフィックスコントローラを修正変更して回避できると先ず考えるかもしれない。このシナリオでは、CPUがスイッチ26をオフにして、レジスタ"R"に"0"を書き込むようホストインタフェース24にコマンドを出し、スイッチ"S"をオンにする。そうすると、周辺装置への電力がオフになっている間にグラフィックスコントローラがリセットされた場合には、レジスタ"R"の内容は"0"のままで、スイッチSはオンのままである。

【0022】

しかし、この「解決法」は一つの問題を生む。先のシナリオを続けると、CPUはスイッチ26をオンにし、レジスタ"R"に"1"を書き込むようホストインタフェース24にコマンドを出して、スイッチ"S"をオフにする。周辺装置がオンになっているときにスイッチ"S"はオフになるのが望ましい。しかしながら、周辺装置への電力がオンになっている間にグラフィックスコントローラがリセットされると、レジスタRの内容が"0"になって、スイッチ"S"をオンにする。周辺装置がオンになっている時にスイッチ"S"もオンになると、レベルシフタに大電流を生じさせることがあり、電力を消費してCMOSラッチアップを引き起こす可能性がある。

【0023】

図2に示すのは、本発明による、電子コンピューティング及び表示システム30のための好適な電力切断保護制御回路50である。システム30はグラフィックスコントローラ32を含んで構成されている。システム30には、周辺装置14、CPU16、電源18、及びグラフィックス表示装置20も含まれている。これらの構成要素は上に説明したものと同じでも構わない。さらに、グラフィックスコントローラ32はレベルシフタ221及び22Nを含み、各シフタには電力切断保護回路の機能を果たすスイッチ"S"がある。好適な回路50は切断保護回路S1〜SNのハードウェア制御又はソフトウェア制御どちらにも対応できる。

【0024】

周辺装置14は、一般的に、データのビットをグラフィックスコントローラに並列で送るための幾つかのデータ線D1〜DNを備えている。しかしながら、データのシリアル送信に1本のデータ線だけを用いても構わない。さらに、別の実施例において、周辺装置14はデータ線D1〜DNでデータのビットを受け取っても構わない。

【0025】

電源には、グラフィックスコントローラ32及び周辺装置14それぞれに電力供給するための2つの電圧出力VGとVPが設けられている。2つの電圧は各々、レベルシフタ221と22Nのそれぞれの側に供給される。グラフィックスコントローラにはデータ線D毎にレベルシフタが設けられている。レベルシフタは内部処理用にレベルシフトされたデータをグラフィックスコントローラに供給する。別の実施例において、レベルシフタはレベルシフトされたデータを周辺装置に供給する。スイッチS1〜SNはそれぞれのレベルシフタ22を接地に接続して、電力切断保護を提供する。スイッチは一般的にはMOSFET(NMOS又はPMOS)だけれども、任意の好ましい技術のもので構わない。

【0026】

電源18の電圧出力VPはスイッチ34の制御によって周辺装置14及びレベルシフタ22に接続又は接続解除される。スイッチ34をオン又はオフにするためにホスト16が電力制御信号36が発して、電力VPを周辺装置14及びレベルシフタ22に接続又は接続解除する。

【0027】

ホストCPU16はグラフィックスコントローラ内のホストインタフェース44に接続されたバス45を介してグラフィックスコントローラ32と通信する。ホストインタフェース44は、ホストからの命令に応じて、以下に説明する出力ビットを出す。

【0028】

本発明による、電力切断保護回路を制御するための回路の好適な実施例50を図2に示した。回路50はグラフィックスコントローラ32にオンボードで設けられている。当業者ならば、別の実施例においては望む通りに、任意の技術を用いて、回路50及びその変形例をハードウェア、ファームウェア、ソフトウェア、或いはこれらのタイプの構成要素の組合せでインプリメントして構わないことを容易に理解するだろう。

【0029】

電源切断マルチプレクサ52は電源切断保護回路のスイッチSを直接に駆動する。各スイッチSは2つの制御状態を有する。第1制御状態では、スイッチSがオンつまり閉じた状態である。第2制御状態では、スイッチSがオフつまり開いた状態である。各スイッチSは第1制御状態でそれぞれのレベルシフタ及び接地間の電流経路をつなぎ、第2制御状態で経路を遮断する。スイッチを一般的なものとして表示している。マルチプレクサ52からの高信号又は低信号どちらの信号を用いてスイッチSをある特定の制御状態に入れても構わない。スイッチSはMOSFETが好ましいが、望むところの任意の技術のスイッチで構わない。

【0030】

電力切断マルチプレクサ52は2入力、すなわちハードウェア制御用の入力54とソフトウェア制御用の入力56とを有する。マルチプレクサ52の入力は、ハードウェアイネーブルラッチ58の出力によって選択され、ハードウェアイネーブルラッチ58はホストインタフェース44の線33に出力されたハードウェア制御イネーブルビットによってセットされる。

【0031】

ハードウェア制御

ハードウェア制御イネーブルビットは電力切断保護回路のハードウェア制御とソフトウェア制御の間で選択する。表示している実施例において、ハードウェア制御イネーブルビットを"1"にするとハードウェア制御を選択する。ハードウェア制御モードで、ホストCPUはグラフィックスコントローラ32の端子49を介して電力切断保護回路を制御する。

【0032】

ハードウェア制御は、排他的論理和ゲート60を含んだ論理回路と端子49極性ラッチ62(pin 49 polarity latch 62)を有する回路50にインプリメントされるのが好ましい。この論理回路はグラフィックスコントローラの端子49から得る電力制御信号を用いる。上述のごとく、ホストは電力VPを周辺装置14に接続及び接続解除するのに電力制御信号36を用いる。VP及びスイッチの両方を制御するのに一つの信号36を用いるのは有益ではあるけれども、この論理回路は電力制御信号36を使用する必要がない。別の実施例において、この回路は、端子49からのスイッチSのハードウェア制御専用の信号を使用する。

【0033】

端子49極性ラッチ62は、ホストインタフェース44の線37に供給されるハードウェア構成極性ビットによって設定される。ハードウェア極性ビットは、出力VPが接続解除になると間違いなくスイッチSが第1制御状態(オンつまり閉じた状態)になるようにするのに必要な値("1"か"0")をとるためにホストによって構成される。電力制御信号36とラッチ62の出力は排他的論理和ゲート60に入力される。排他的論理和ゲート60の出力54は電力切断マルチプレクサ52の第1入力に接続される。

【0034】

例はハードウェア制御モードを説明するものである。周辺装置への電力出力VPは、電力制御信号36がローになると接続解除されると仮定する。また、スイッチSは、電力切断マルチプレクサ52への入力54がハイになると、第1制御状態(オン)になると仮定しよう。ハードウェア極性ビットをハイ(端子49極性ラッチ62に格納されている)に設定すると、電力制御信号36がローの場合、排他的論理和ゲート60がハイの出力を供給する。このハイの信号は、周辺装置への電力VPが接続解除されていると、スイッチSをオンにするためにマルチプレクサ52を通って送られる。

【0035】

ホスト16は、周辺装置に電力VPを供給して周辺装置を再びオンにする。ホスト16は、スイッチ34を再びオンにして電力VPを供給する。ホストは電力制御信号36をハイに遷移させてこれを行なう。それが排他的論理和ゲート60をトグルさせる。例の説明を続けると、ホストが電力制御信号36をハイに遷移させると、排他的論理和60の出力がローになり、スイッチSをオフにする。したがって、周辺装置への電力VPが接続されると、スイッチSはオフになる。

【0036】

この例をまとめると、次のような一覧表になる。

【0037】

グラフィックスコントローラ32がリセットされた場合には、端子49極性ラッチ62に保持されているハードウェア極性ビットがリセットされる。

【0038】

線42に供給されたリセット信号がグラフィックスコントローラのリセットを示している。リセット信号はいろいろな異なる影響の結果アサートされることがあり、「累積」リセット信号と呼ばれる。例えば、累積リセット信号は、グラフィックスコントローラ32のハードウェアリセット端子46に供給されたハードウェア信号、ビット又はコードによるか、或いは、ホストインタフェース44を介してリセットラッチ38に対して出されたソフトウェア命令としてかのどちらかで、ホスト16の命令から生じることがある。もしくは、グラフィックスコントローラが自ら、内部リセット信号、ビット又はコードを生成しても構わない。当業者ならばすぐ分かるように、概して、信号、ビット、コード(例えば、バイト)などは同じように機能し、しかるべき修正変更によって互いに置き換えて使用可能なことを理解するべきである。そうした信号、ビット、コードなどを本書では総称的に「表示(indication)」と呼ぶ。

【0039】

別の論理回路はグラフィックスコントローラをリセットするために上記のルートのどれかを選択する。具体的には、好適な回路50において、3入力論理和ゲート40は線42に累積リセット信号を生成する。論理和ゲート40への第1入力はリセットラッチ38に接続される。第2入力はハードウェアリセット端子46に接続される。そして第3入力は内部リセット信号に接続される。論理和ゲート40の出力は線42に接続される。線42はラッチ58、62、a及びbに接続される。

【0040】

端子49極性ラッチ62に格納されている内容は、累積リセット信号が線42上でアサートされると、"0"にリセットされる。したがって、ラッチ62に格納されているハードウェア極性ビットがスイッチSを第1制御状態(オン)にするために"1"だった場合には、電力VPが周辺装置から接続解除されている間に累積リセット信号が線42上でアサートされることにより、スイッチSがオフになる。この結果は好ましくない。

【0041】

こうした好ましくない結果にならないように、リセット時にメモリ損失になりやすいグラフィックスコントローラレジスタの使用に依存しないハードウェア制御を設けることができる。例えば、グラフィックスコントローラの端子49をスイッチSに直接に接続することができる。しかしながら、この手法では、ホストが供給した電力制御信号36の極性がスイッチSの要件にマッチしていなければならない。グラフィックスコントローラがある特定のシステムで使用可能などんな極性の信号でも使用する能力をもっていると自由度が高まるし好ましいから、電力制御信号36が事前に定義された極性を必要とするのは欠点である。任意のホスト16がスイッチ"S"を作動させるための2つの状態のうちのいずれかを必要とするグラフィックスコントローラチップ32を作動させられるように、必要な極性を端子49極性ラッチ62を介してソフトウェアで構成できるのは本発明の傑出した利点である。

【0042】

電力VPが周辺装置から接続解除されると、端子49極性ラッチ62に格納されている内容は"1"になり、スイッチ"S"をオンにする。しかしながら、累積リセット信号が線42上でアサートされると、ラッチ62の内容は"0"にリセットされる。そのために、ハードウェア制御モードで動作していて電力VPが周辺装置から接続解除されると、グラフィックスコントローラのリセット時にスイッチSの状態が変わる。この好ましくない状態変化を回避するために、回路50は線42上の累積リセット信号をハードウェアイネーブルラッチ58に接続する。ラッチ58をリセットすることで電力切断マルチプレクサ52をソフトウェア制御を選択するよう制御する。以下に述べるように、VPがオフの状態で且つハードウェア制御下で動作しているとき、このソフトウェア制御の選択によってスイッチSの状態の好ましくない変化を防ぐことができる。リセット後、ホストは、いつでも、ハードウェアイネーブルラッチ58に"1"を書き込んでハードウェア制御を再び選択することができる。

【0043】

ソフトウェア制御

好適な実施例50ではハードウェアイネーブルラッチ58に"0"を書き込むことによってソフトウェア制御をインプリメントする。このゼロを、「通常」の場合には、ソフトウェアインタフェースを介してか、又はグラフィックスコントローラ32をリセットすることによってかいずれかのやり方で書き込むので構わない。ラッチ58の出力により、第2マルチプレクサ64の出力56がスイッチSを駆動するための電力切断マルチプレクサ52への入力56として選択される。

【0044】

通常の場合、ソフトウェア制御は、周辺装置への電力VPが接続又は接続解除のどちらかになると、スイッチSの状態を必要に応じて変えるようになっている。

【0045】

第2マルチプレクサ64は、グラフィックスコントローラ32の端子48で使用可能になるソフトウェア構成極性信号の制御下で、メモリ記憶素子のペア66、具体的にはR-Sラッチ"a"と"b"間で選択する。各ラッチはデータ記憶入力"D"(Da、Db)とデータ記憶入力からラッチされたデータを出力するための対応するデータ記憶出力"Q"(Qa、Qb)とを有する。ラッチの一つ"a"はリセット入力"R"を有し、他方のラッチ"b"はセット入力"S"を有する。好適な実施例において、入力R及びSは結び合わされて極性選択入力69を形成し、極性選択入力69はラッチ"a"と"b"のリセット入力及びセット入力に接続されている。

【0046】

ソフトウェアパワーオンビットはラッチ"a"と"b"の両データ記憶入力Dへのホストインタフェース44の線67に供給される。したがって、ラッチ"a"と"b"は通常動作時に同じデータ記憶出力Qを生成する。ラッチペアの両方のラッチが同じデータ記憶出力を生成する場合には、端子48上のソフトウェア構成極性信号は第2マルチプレクサ64の出力56に影響を及ぼさない。

【0047】

線37に供給されたハードウェア極性ビットと同様に、線67に供給されたソフトウェア極性ビットは望むとおりにスイッチSを制御するのに適するようにホストによってセットされ、ハイかローかどちらかの信号によって第1制御状態になるスイッチとインタフェースをとる柔軟性を提供する。

【0048】

しかしながら、グラフィックスコントローラがリセットされた場合には、累積リセット信号が線42に供給される。これによりラッチペア66のラッチの片方"a"が"0"にリセットされ、他方"b"が"1"にリセットされる。ホスト16は、スイッチSの望ましい状態に適したラッチ"a"か"b"どちらかを選択するために、端子48上の望ましいソフトウェア構成極性信号をアサートする。

【0049】

ソフトウェア制御下で作動しているときの通常動作及びリセット動作の例を考慮してみよう。周辺装置への電力VPがオンになっている場合には、スイッチSは第2制御状態(オフつまり開いた状態)であるはずで、周辺装置への電力がオフの場合にはスイッチSは第1制御状態(オンつまり閉じた状態)になっているはずである。電力切断マルチプレクサ52からの信号出力がハイのときスイッチSは第1制御状態で、電力切断マルチプレクサ52からの信号出力がローのときスイッチSは第2制御状態になると仮定しよう。

【0050】

通常動作の例として、周辺装置への電力VPがオンの場合、線67上のソフトウェアパワーオンビットはスイッチをオフに維持するためにローのはずである。電力VPをオフにしようとすると、ホストが線67上のソフトウェアパワーオンビットをローからハイにトグルしてスイッチをオンにする。

【0051】

リセット動作の例として、線67上のソフトウェアパワーオンビットはハイで、第2マルチプレクサ64の出力も対応してハイであると仮定しよう。グラフィックスコントローラがリセットされると、ラッチペア69に格納されている内容はリセットの結果失われる。線42上のリセット信号はラッチ"a"を"0"にリセットし、ラッチ"b"を"1"にセットする。マルチプレクサ64の出力をハイに維持するために、ホストは端子48上のソフトウェア構成極性ビットをロー(この例では)にすることでラッチ"b"のデータ記憶出力を選択する。ラッチ"b"を選択することで、マルチプレクサ64の出力がハイに維持される。

【0052】

周辺装置への電力を回復すると、ホストは線67上のソフトウェアパワーオンビットを操作してスイッチSのコントロールを取り戻すことができる。ホスト16が回路要件を認識するようにしさえすれば、ソフトウェア構成極性ビットの使用により、図2に表示した回路の変形例のソフトウェア制御下で同じ程度のコントロールを提供できることが容易に明白になるはずである。

【0053】

ソフトウェア制御を説明してきたが、ハードウェア制御モードで動作していてリセットが発生すると、スイッチSの状態の変化がソフトウェア制御の選択によって防止される様子を次に例をあげて説明する。電力制御信号36がローのとき周辺装置電力出力VPは接続解除されると仮定しよう。また、マルチプレクサ52への入力54がハイのときスイッチSがオンになると仮定しよう。ホストが端子49極性ラッチ62に"1"を格納し、電力制御信号36をローにアサートして周辺装置への電力をオフにした場合、その結果として排他的論理和ゲート60がハイの出力を生成して、スイッチ"S"をオンにするので、望ましい。線42上のリセット信号をアサートすると端子49極性ラッチ62が"0"にリセットされる。しかしながら、電力制御信号36は依然としてローである。そのために、排他的論理和ゲート60がハイの出力を生成して、スイッチSをオフにする。述べたように、この結果は好ましくない。

【0054】

しかしながら、線42上のリセット信号をアサートすることにより、ハードウェアイネーブルラッチ58もゼロにリセットされて、グラフィックスコントローラをソフトウェアモードにし、排他的論理和ゲート60の出力を一時的に無意味にする。さらに、リセット信号をアサートすることによりラッチ"a"が"0"にリセットされ、ラッチ"b"は"1"にセットされる。ホストが端子48上のローのソフトウェア構成極性信号をアサートして、ラッチ"b"を選択する。ラッチ"b"に格納されている"1"がスイッチSをオン状態に復元するので、望ましい。

【0055】

本発明の電力切断回路及び方法は、当業者ならば容易に明白になるように、ハードウェアかソフトウェア、又はその両方でインプリメント可能で、機械が実行する一つ以上の命令プログラムを含んだ機械可読媒体を採用しても構わない。

【0056】

具体的な電力切断回路及び方法を好適な例として表示すると共に説明してきたが、すでに述べたものに加えて、発明の原理から逸脱せずに、他の構成及び方法を使用できることを認識するはずである。

【0057】

上記の明細書で用いた用語や表現は本書における説明のためであって限定のためではない。そうした用語や表現を使用したからといって、表示し説明した特徴の均等物又はその一部分を除外するつもりはない。発明の範囲は下記の請求項によってのみ定義及び限定されるものと認識している。

【図面の簡単な説明】

【0058】

【図1】グラフィックスコントローラ及び周辺装置を含んで構成されたシステムの電力切断保護回路を制御するための先行技術による回路の概略図。

【図2】本発明による、グラフィックスコントローラ及び周辺装置を含んで構成されたシステムの電力切断保護回路を制御するための好適な回路の概略図。

【符号の説明】

【0059】

12 グラフィックスコントローラ

14 周辺装置

16 ホストCPU

18 電源

20 ディスプレイ

24 ホストインタフェース

30 リセット

32 グラフィックスコントローラ

33 ハードウェア制御イネーブル

34 スイッチ

36 電力制御信号

37 ハードウェア構成極性ビット

38 リセットラッチ

42 累積リセット信号

44 ホストインタフェース

46 ハードウェアリセット端子

49 端子

52 電力切断マルチプレクサ

58 ハードウェアイネーブルラッチ

62 極性ラッチ

64 第2マルチプレクサ

66 ラッチペア

67 ソフトウェアパワーオンビット

【技術分野】

【0001】

本発明は、特にグラフィックスコントローラ及び周辺装置を含んで構成されたシステムで使用するための電力切断保護回路を制御するための回路及び方法に関する。より具体的には、周辺装置及びグラフィックスコントローラに共通に供給される電力の損失に起因するダメージからグラフィックスコントローラを守るためのそうした回路及び方法に関する発明である。

【背景技術】

【0002】

グラフィックスディスプレイシステムは、一般に、LCDパネルなどグラフィックス表示装置とホストCPUとの間にグラフィックスコントローラチップを用いている。概して、そうしたシステムは一つ以上の周辺装置も含んでいる。例えば、携帯電話では、カメラ周辺装置をグラフィックスコントローラに接続するのがますます一般的になってきている。カメラもホストCPUも対応する画像データ集合を供給する機能を有する。グラフィックスコントローラは、表示装置に供給するためのデータ集合間で選択することも、或いは表示装置に供給するために一つのデータ集合をもう一つのデータ集合の上にオーバーレイすることもできる。

【0003】

周辺装置がカメラの場合、グラフィックスコントローラは周辺装置から画像データを受け取る。もしくは、データを周辺装置に供給することも可能である。どちらにしても、普通はグラフィックスコントローラと周辺装置とは異なる電圧レベルで電力供給されるから、グラフィックスコントローラと周辺装置との間で交換されるデータは、一般的に、レベルシフトされなければならない。そのために、グラフィックスコントローラには、例えば、パラレルデータバスのビット毎にレベルシフタが設けられる。レベルシフタは一般的にCMOS技術で形成される。

【0004】

グラフィックスコントローラには各レベルシフタの片側に電力を供給するために周辺装置から電力を受け取るための端子がある一方、内部で、グラフィックスコントローラが使用する電力は各レベルシフタの他方の側に供給される。周辺装置からの電力がオンになっている限り、レベルシフタは正常に機能する。

【0005】

それに対して、グラフィックスコントローラは電力がオンのままの状態で、周辺装置の電力がオフになった場合には、CMOSのラッチアップが原因でレベルシフタにダメージが生じる。それでも、例えば、周辺装置から受け取った画像を処理しているときの電力消費を減らすために、グラフィックスコントローラの電力がオンになっている間に周辺装置の電力をオフにすることが好ましい場合が多い。

【0006】

この問題は、グラフィックスコントローラに電力切断保護回路を設けることで解決されてきた。電力切断保護回路は、ホストCPUが周辺装置をオフにするのと実質的に同時にホストCPUが書きこむレジスタを含んで構成された別の回路によって制御される。レベルシフタを接地に接続しているそれぞれのMOSFETをオンにするのにレジスタの内容を使用する。こうすると、周辺装置からの電力が切断されたときレベルシフタのCMOSラッチアップを防ぐことができる。

【0007】

この問題解決法は完全とはいえない。周辺装置の電力がオフになるとグラフィックスコントローラがリセットされる場合には、MOSFETが再びオフになってしまうためにレジスタの内容が失われるので、レベルシフタは切断回路が解決するはずだった問題に直面する。

【0008】

【特許文献1】米国特許第6,101,600号明細書

【発明の開示】

【発明が解決しようとする課題】

【0009】

それゆえに、先行技術で提供されてきた保護よりも一層ロバストな保護を提供できる電力切断保護回路を制御するための回路及び方法に対するニーズがある。

【課題を解決するための手段】

【0010】

グラフィックスコントローラで使用するための、本発明による好適な電力切断保護制御回路及び方法を開示している。グラフィックスコントローラは周辺装置に接続され、ホストによって制御される。グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラで信号を処理するのに適した別の電圧レベルにシフトするためのレベルシフタを含んで構成されている。レベルシフタと接地との間の電流経路にスイッチが設けられている。このスイッチは、スイッチのそれぞれの第1及び第2制御状態でオン又はオフである。

【0011】

好適な電力切断制御回路はメモリペアと選択回路とを含んで構成される。メモリペアは、ペアの第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納したデータをそれぞれの記憶出力に供給する。メモリペアは、第1及び第2記憶素子のうちの一方の記憶データ出力をスイッチの第1制御状態に対応させ、他方の記憶データ出力をスイッチの第2制御状態に対応させるようにする極性選択入力を有している。選択回路は入力がメモリペアのそれぞれの記憶出力に接続され、出力がスイッチを制御するためのスイッチの制御線に接続されている。選択回路の選択線は、第1及び第2記憶素子の記憶出力の一方又は他方を選択するために、入力間で選択する。

【0012】

対応する方法及び媒体も開示している。

【0013】

本章で述べた概要は、図面及び詳細な説明の中で何を説明しているかを大まかに判定する手段として提供しているのであって、発明の範囲を限定するつもりはないことを理解するべきである。本発明の目的、特徴、作用効果については、添付の図面と共に以下に述べる詳細な説明を考慮すれば容易に理解できるだろう。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施形態を図面に基づいて説明する。

【0015】

図1に示すのは、グラフィックスコントローラ12、カメラなど周辺装置14、ホストCPU16、安定化電源18、及びLCDパネルなどグラフィックス表示装置20を有する典型的な電子コンピューティング及び表示システム10の電力切断保護回路8を制御するための先行技術による回路である。グラフィックスコントローラは、一般的に、画像データを組み合わせてコンポジットにするために、カメラ及びCPUから流れてくる画像データを管理し、そのコンポジットデータを表示装置に供給する。ホストCPU16はグラフィックスコントローラ内のホストインタフェース24を介してグラフィックスコントローラ12と通信する。

【0016】

本発明の好適な文脈であるシステム10は構成要素8及び12〜20で形成されているが、システムの動作の仕方及びシステムの具体的な形は大きく異なって構わない。例えば、ホストはコンピュータ又はCPU以外の何かで構わないし、グラフィックス表示装置が不要になるように発明の電力切断制御回路及び方法をグラフィックスコントローラ以外のデバイスやチップに実施しても構わない。また、周辺装置はカメラ以外の何かで構わない。

【0017】

Nは一般的に8であるとして、周辺装置14は幾つかのデータ線D1 - DNを備える。電源はグラフィックスコントローラ12及び周辺装置14それぞれに電力供給するための2つの電源出力VGとVPを備える。データ線D毎にレベルシフタがあると考えるとして、2つの電圧は各々レベルシフタ221及び22Nのそれぞれの側に供給される。レベルシフタは内部処理するためにグラフィックスコントローラにレベルシフトされたデータを供給する。しかしながら、制御信号又はその他の信号をシフトするためにもレベルシフタを使用して構わない。

【0018】

スイッチS1〜SNを制御するためにレジスタ"R"がグラフィックスコントローラに備えられている。スイッチは閉じた状態のときそれぞれのレベルシフタ22を接地に接続する。スイッチSは電力切断保護回路の役目を果たす。スイッチは普通はMOSFETだけれども、任意の所望する技術のもので構わない。

【0019】

ホストCPU16は、典型的にはMOSFETのスイッチ26を用いて周辺装置だけでなくグラフィックスコントローラ12にも供給される電力VPを制御する。CPUはスイッチ26を先ずオフにし、その後、"1"をレジスタ"R"に書き込むようホストインタフェース24にコマンドを出す。レジスタ"R"の出力はバッファ28に接続されている。バッファ28はスイッチSを制御するための信号を駆動する。"1"がレジスタ"R"に格納されることにより、バッファ28はスイッチSをオンにする信号を駆動する。

【0020】

CPU16は、リセット線30を起動することによって、いつでもリセットするようグラフィックスコントローラ12に命令することができる。しかしながら、グラフィックスコントローラがリセットされると、レジスタ"R"の内容が失われる。つまり、"1"は"0"で置き換えられる。これがスイッチSをオフにするので、レベルシフタ22に大電流が生じる。これは電力を消費してCMOSラッチアップを引き起こすことがある。

【0021】

この問題は、レジスタ"R"に("1"の代わりに)"0"を格納するとスイッチ"S"がオンになるようにグラフィックスコントローラを修正変更して回避できると先ず考えるかもしれない。このシナリオでは、CPUがスイッチ26をオフにして、レジスタ"R"に"0"を書き込むようホストインタフェース24にコマンドを出し、スイッチ"S"をオンにする。そうすると、周辺装置への電力がオフになっている間にグラフィックスコントローラがリセットされた場合には、レジスタ"R"の内容は"0"のままで、スイッチSはオンのままである。

【0022】

しかし、この「解決法」は一つの問題を生む。先のシナリオを続けると、CPUはスイッチ26をオンにし、レジスタ"R"に"1"を書き込むようホストインタフェース24にコマンドを出して、スイッチ"S"をオフにする。周辺装置がオンになっているときにスイッチ"S"はオフになるのが望ましい。しかしながら、周辺装置への電力がオンになっている間にグラフィックスコントローラがリセットされると、レジスタRの内容が"0"になって、スイッチ"S"をオンにする。周辺装置がオンになっている時にスイッチ"S"もオンになると、レベルシフタに大電流を生じさせることがあり、電力を消費してCMOSラッチアップを引き起こす可能性がある。

【0023】

図2に示すのは、本発明による、電子コンピューティング及び表示システム30のための好適な電力切断保護制御回路50である。システム30はグラフィックスコントローラ32を含んで構成されている。システム30には、周辺装置14、CPU16、電源18、及びグラフィックス表示装置20も含まれている。これらの構成要素は上に説明したものと同じでも構わない。さらに、グラフィックスコントローラ32はレベルシフタ221及び22Nを含み、各シフタには電力切断保護回路の機能を果たすスイッチ"S"がある。好適な回路50は切断保護回路S1〜SNのハードウェア制御又はソフトウェア制御どちらにも対応できる。

【0024】

周辺装置14は、一般的に、データのビットをグラフィックスコントローラに並列で送るための幾つかのデータ線D1〜DNを備えている。しかしながら、データのシリアル送信に1本のデータ線だけを用いても構わない。さらに、別の実施例において、周辺装置14はデータ線D1〜DNでデータのビットを受け取っても構わない。

【0025】

電源には、グラフィックスコントローラ32及び周辺装置14それぞれに電力供給するための2つの電圧出力VGとVPが設けられている。2つの電圧は各々、レベルシフタ221と22Nのそれぞれの側に供給される。グラフィックスコントローラにはデータ線D毎にレベルシフタが設けられている。レベルシフタは内部処理用にレベルシフトされたデータをグラフィックスコントローラに供給する。別の実施例において、レベルシフタはレベルシフトされたデータを周辺装置に供給する。スイッチS1〜SNはそれぞれのレベルシフタ22を接地に接続して、電力切断保護を提供する。スイッチは一般的にはMOSFET(NMOS又はPMOS)だけれども、任意の好ましい技術のもので構わない。

【0026】

電源18の電圧出力VPはスイッチ34の制御によって周辺装置14及びレベルシフタ22に接続又は接続解除される。スイッチ34をオン又はオフにするためにホスト16が電力制御信号36が発して、電力VPを周辺装置14及びレベルシフタ22に接続又は接続解除する。

【0027】

ホストCPU16はグラフィックスコントローラ内のホストインタフェース44に接続されたバス45を介してグラフィックスコントローラ32と通信する。ホストインタフェース44は、ホストからの命令に応じて、以下に説明する出力ビットを出す。

【0028】

本発明による、電力切断保護回路を制御するための回路の好適な実施例50を図2に示した。回路50はグラフィックスコントローラ32にオンボードで設けられている。当業者ならば、別の実施例においては望む通りに、任意の技術を用いて、回路50及びその変形例をハードウェア、ファームウェア、ソフトウェア、或いはこれらのタイプの構成要素の組合せでインプリメントして構わないことを容易に理解するだろう。

【0029】

電源切断マルチプレクサ52は電源切断保護回路のスイッチSを直接に駆動する。各スイッチSは2つの制御状態を有する。第1制御状態では、スイッチSがオンつまり閉じた状態である。第2制御状態では、スイッチSがオフつまり開いた状態である。各スイッチSは第1制御状態でそれぞれのレベルシフタ及び接地間の電流経路をつなぎ、第2制御状態で経路を遮断する。スイッチを一般的なものとして表示している。マルチプレクサ52からの高信号又は低信号どちらの信号を用いてスイッチSをある特定の制御状態に入れても構わない。スイッチSはMOSFETが好ましいが、望むところの任意の技術のスイッチで構わない。

【0030】

電力切断マルチプレクサ52は2入力、すなわちハードウェア制御用の入力54とソフトウェア制御用の入力56とを有する。マルチプレクサ52の入力は、ハードウェアイネーブルラッチ58の出力によって選択され、ハードウェアイネーブルラッチ58はホストインタフェース44の線33に出力されたハードウェア制御イネーブルビットによってセットされる。

【0031】

ハードウェア制御

ハードウェア制御イネーブルビットは電力切断保護回路のハードウェア制御とソフトウェア制御の間で選択する。表示している実施例において、ハードウェア制御イネーブルビットを"1"にするとハードウェア制御を選択する。ハードウェア制御モードで、ホストCPUはグラフィックスコントローラ32の端子49を介して電力切断保護回路を制御する。

【0032】

ハードウェア制御は、排他的論理和ゲート60を含んだ論理回路と端子49極性ラッチ62(pin 49 polarity latch 62)を有する回路50にインプリメントされるのが好ましい。この論理回路はグラフィックスコントローラの端子49から得る電力制御信号を用いる。上述のごとく、ホストは電力VPを周辺装置14に接続及び接続解除するのに電力制御信号36を用いる。VP及びスイッチの両方を制御するのに一つの信号36を用いるのは有益ではあるけれども、この論理回路は電力制御信号36を使用する必要がない。別の実施例において、この回路は、端子49からのスイッチSのハードウェア制御専用の信号を使用する。

【0033】

端子49極性ラッチ62は、ホストインタフェース44の線37に供給されるハードウェア構成極性ビットによって設定される。ハードウェア極性ビットは、出力VPが接続解除になると間違いなくスイッチSが第1制御状態(オンつまり閉じた状態)になるようにするのに必要な値("1"か"0")をとるためにホストによって構成される。電力制御信号36とラッチ62の出力は排他的論理和ゲート60に入力される。排他的論理和ゲート60の出力54は電力切断マルチプレクサ52の第1入力に接続される。

【0034】

例はハードウェア制御モードを説明するものである。周辺装置への電力出力VPは、電力制御信号36がローになると接続解除されると仮定する。また、スイッチSは、電力切断マルチプレクサ52への入力54がハイになると、第1制御状態(オン)になると仮定しよう。ハードウェア極性ビットをハイ(端子49極性ラッチ62に格納されている)に設定すると、電力制御信号36がローの場合、排他的論理和ゲート60がハイの出力を供給する。このハイの信号は、周辺装置への電力VPが接続解除されていると、スイッチSをオンにするためにマルチプレクサ52を通って送られる。

【0035】

ホスト16は、周辺装置に電力VPを供給して周辺装置を再びオンにする。ホスト16は、スイッチ34を再びオンにして電力VPを供給する。ホストは電力制御信号36をハイに遷移させてこれを行なう。それが排他的論理和ゲート60をトグルさせる。例の説明を続けると、ホストが電力制御信号36をハイに遷移させると、排他的論理和60の出力がローになり、スイッチSをオフにする。したがって、周辺装置への電力VPが接続されると、スイッチSはオフになる。

【0036】

この例をまとめると、次のような一覧表になる。

【0037】

グラフィックスコントローラ32がリセットされた場合には、端子49極性ラッチ62に保持されているハードウェア極性ビットがリセットされる。

【0038】

線42に供給されたリセット信号がグラフィックスコントローラのリセットを示している。リセット信号はいろいろな異なる影響の結果アサートされることがあり、「累積」リセット信号と呼ばれる。例えば、累積リセット信号は、グラフィックスコントローラ32のハードウェアリセット端子46に供給されたハードウェア信号、ビット又はコードによるか、或いは、ホストインタフェース44を介してリセットラッチ38に対して出されたソフトウェア命令としてかのどちらかで、ホスト16の命令から生じることがある。もしくは、グラフィックスコントローラが自ら、内部リセット信号、ビット又はコードを生成しても構わない。当業者ならばすぐ分かるように、概して、信号、ビット、コード(例えば、バイト)などは同じように機能し、しかるべき修正変更によって互いに置き換えて使用可能なことを理解するべきである。そうした信号、ビット、コードなどを本書では総称的に「表示(indication)」と呼ぶ。

【0039】

別の論理回路はグラフィックスコントローラをリセットするために上記のルートのどれかを選択する。具体的には、好適な回路50において、3入力論理和ゲート40は線42に累積リセット信号を生成する。論理和ゲート40への第1入力はリセットラッチ38に接続される。第2入力はハードウェアリセット端子46に接続される。そして第3入力は内部リセット信号に接続される。論理和ゲート40の出力は線42に接続される。線42はラッチ58、62、a及びbに接続される。

【0040】

端子49極性ラッチ62に格納されている内容は、累積リセット信号が線42上でアサートされると、"0"にリセットされる。したがって、ラッチ62に格納されているハードウェア極性ビットがスイッチSを第1制御状態(オン)にするために"1"だった場合には、電力VPが周辺装置から接続解除されている間に累積リセット信号が線42上でアサートされることにより、スイッチSがオフになる。この結果は好ましくない。

【0041】

こうした好ましくない結果にならないように、リセット時にメモリ損失になりやすいグラフィックスコントローラレジスタの使用に依存しないハードウェア制御を設けることができる。例えば、グラフィックスコントローラの端子49をスイッチSに直接に接続することができる。しかしながら、この手法では、ホストが供給した電力制御信号36の極性がスイッチSの要件にマッチしていなければならない。グラフィックスコントローラがある特定のシステムで使用可能などんな極性の信号でも使用する能力をもっていると自由度が高まるし好ましいから、電力制御信号36が事前に定義された極性を必要とするのは欠点である。任意のホスト16がスイッチ"S"を作動させるための2つの状態のうちのいずれかを必要とするグラフィックスコントローラチップ32を作動させられるように、必要な極性を端子49極性ラッチ62を介してソフトウェアで構成できるのは本発明の傑出した利点である。

【0042】

電力VPが周辺装置から接続解除されると、端子49極性ラッチ62に格納されている内容は"1"になり、スイッチ"S"をオンにする。しかしながら、累積リセット信号が線42上でアサートされると、ラッチ62の内容は"0"にリセットされる。そのために、ハードウェア制御モードで動作していて電力VPが周辺装置から接続解除されると、グラフィックスコントローラのリセット時にスイッチSの状態が変わる。この好ましくない状態変化を回避するために、回路50は線42上の累積リセット信号をハードウェアイネーブルラッチ58に接続する。ラッチ58をリセットすることで電力切断マルチプレクサ52をソフトウェア制御を選択するよう制御する。以下に述べるように、VPがオフの状態で且つハードウェア制御下で動作しているとき、このソフトウェア制御の選択によってスイッチSの状態の好ましくない変化を防ぐことができる。リセット後、ホストは、いつでも、ハードウェアイネーブルラッチ58に"1"を書き込んでハードウェア制御を再び選択することができる。

【0043】

ソフトウェア制御

好適な実施例50ではハードウェアイネーブルラッチ58に"0"を書き込むことによってソフトウェア制御をインプリメントする。このゼロを、「通常」の場合には、ソフトウェアインタフェースを介してか、又はグラフィックスコントローラ32をリセットすることによってかいずれかのやり方で書き込むので構わない。ラッチ58の出力により、第2マルチプレクサ64の出力56がスイッチSを駆動するための電力切断マルチプレクサ52への入力56として選択される。

【0044】

通常の場合、ソフトウェア制御は、周辺装置への電力VPが接続又は接続解除のどちらかになると、スイッチSの状態を必要に応じて変えるようになっている。

【0045】

第2マルチプレクサ64は、グラフィックスコントローラ32の端子48で使用可能になるソフトウェア構成極性信号の制御下で、メモリ記憶素子のペア66、具体的にはR-Sラッチ"a"と"b"間で選択する。各ラッチはデータ記憶入力"D"(Da、Db)とデータ記憶入力からラッチされたデータを出力するための対応するデータ記憶出力"Q"(Qa、Qb)とを有する。ラッチの一つ"a"はリセット入力"R"を有し、他方のラッチ"b"はセット入力"S"を有する。好適な実施例において、入力R及びSは結び合わされて極性選択入力69を形成し、極性選択入力69はラッチ"a"と"b"のリセット入力及びセット入力に接続されている。

【0046】

ソフトウェアパワーオンビットはラッチ"a"と"b"の両データ記憶入力Dへのホストインタフェース44の線67に供給される。したがって、ラッチ"a"と"b"は通常動作時に同じデータ記憶出力Qを生成する。ラッチペアの両方のラッチが同じデータ記憶出力を生成する場合には、端子48上のソフトウェア構成極性信号は第2マルチプレクサ64の出力56に影響を及ぼさない。

【0047】

線37に供給されたハードウェア極性ビットと同様に、線67に供給されたソフトウェア極性ビットは望むとおりにスイッチSを制御するのに適するようにホストによってセットされ、ハイかローかどちらかの信号によって第1制御状態になるスイッチとインタフェースをとる柔軟性を提供する。

【0048】

しかしながら、グラフィックスコントローラがリセットされた場合には、累積リセット信号が線42に供給される。これによりラッチペア66のラッチの片方"a"が"0"にリセットされ、他方"b"が"1"にリセットされる。ホスト16は、スイッチSの望ましい状態に適したラッチ"a"か"b"どちらかを選択するために、端子48上の望ましいソフトウェア構成極性信号をアサートする。

【0049】

ソフトウェア制御下で作動しているときの通常動作及びリセット動作の例を考慮してみよう。周辺装置への電力VPがオンになっている場合には、スイッチSは第2制御状態(オフつまり開いた状態)であるはずで、周辺装置への電力がオフの場合にはスイッチSは第1制御状態(オンつまり閉じた状態)になっているはずである。電力切断マルチプレクサ52からの信号出力がハイのときスイッチSは第1制御状態で、電力切断マルチプレクサ52からの信号出力がローのときスイッチSは第2制御状態になると仮定しよう。

【0050】

通常動作の例として、周辺装置への電力VPがオンの場合、線67上のソフトウェアパワーオンビットはスイッチをオフに維持するためにローのはずである。電力VPをオフにしようとすると、ホストが線67上のソフトウェアパワーオンビットをローからハイにトグルしてスイッチをオンにする。

【0051】

リセット動作の例として、線67上のソフトウェアパワーオンビットはハイで、第2マルチプレクサ64の出力も対応してハイであると仮定しよう。グラフィックスコントローラがリセットされると、ラッチペア69に格納されている内容はリセットの結果失われる。線42上のリセット信号はラッチ"a"を"0"にリセットし、ラッチ"b"を"1"にセットする。マルチプレクサ64の出力をハイに維持するために、ホストは端子48上のソフトウェア構成極性ビットをロー(この例では)にすることでラッチ"b"のデータ記憶出力を選択する。ラッチ"b"を選択することで、マルチプレクサ64の出力がハイに維持される。

【0052】

周辺装置への電力を回復すると、ホストは線67上のソフトウェアパワーオンビットを操作してスイッチSのコントロールを取り戻すことができる。ホスト16が回路要件を認識するようにしさえすれば、ソフトウェア構成極性ビットの使用により、図2に表示した回路の変形例のソフトウェア制御下で同じ程度のコントロールを提供できることが容易に明白になるはずである。

【0053】

ソフトウェア制御を説明してきたが、ハードウェア制御モードで動作していてリセットが発生すると、スイッチSの状態の変化がソフトウェア制御の選択によって防止される様子を次に例をあげて説明する。電力制御信号36がローのとき周辺装置電力出力VPは接続解除されると仮定しよう。また、マルチプレクサ52への入力54がハイのときスイッチSがオンになると仮定しよう。ホストが端子49極性ラッチ62に"1"を格納し、電力制御信号36をローにアサートして周辺装置への電力をオフにした場合、その結果として排他的論理和ゲート60がハイの出力を生成して、スイッチ"S"をオンにするので、望ましい。線42上のリセット信号をアサートすると端子49極性ラッチ62が"0"にリセットされる。しかしながら、電力制御信号36は依然としてローである。そのために、排他的論理和ゲート60がハイの出力を生成して、スイッチSをオフにする。述べたように、この結果は好ましくない。

【0054】

しかしながら、線42上のリセット信号をアサートすることにより、ハードウェアイネーブルラッチ58もゼロにリセットされて、グラフィックスコントローラをソフトウェアモードにし、排他的論理和ゲート60の出力を一時的に無意味にする。さらに、リセット信号をアサートすることによりラッチ"a"が"0"にリセットされ、ラッチ"b"は"1"にセットされる。ホストが端子48上のローのソフトウェア構成極性信号をアサートして、ラッチ"b"を選択する。ラッチ"b"に格納されている"1"がスイッチSをオン状態に復元するので、望ましい。

【0055】

本発明の電力切断回路及び方法は、当業者ならば容易に明白になるように、ハードウェアかソフトウェア、又はその両方でインプリメント可能で、機械が実行する一つ以上の命令プログラムを含んだ機械可読媒体を採用しても構わない。

【0056】

具体的な電力切断回路及び方法を好適な例として表示すると共に説明してきたが、すでに述べたものに加えて、発明の原理から逸脱せずに、他の構成及び方法を使用できることを認識するはずである。

【0057】

上記の明細書で用いた用語や表現は本書における説明のためであって限定のためではない。そうした用語や表現を使用したからといって、表示し説明した特徴の均等物又はその一部分を除外するつもりはない。発明の範囲は下記の請求項によってのみ定義及び限定されるものと認識している。

【図面の簡単な説明】

【0058】

【図1】グラフィックスコントローラ及び周辺装置を含んで構成されたシステムの電力切断保護回路を制御するための先行技術による回路の概略図。

【図2】本発明による、グラフィックスコントローラ及び周辺装置を含んで構成されたシステムの電力切断保護回路を制御するための好適な回路の概略図。

【符号の説明】

【0059】

12 グラフィックスコントローラ

14 周辺装置

16 ホストCPU

18 電源

20 ディスプレイ

24 ホストインタフェース

30 リセット

32 グラフィックスコントローラ

33 ハードウェア制御イネーブル

34 スイッチ

36 電力制御信号

37 ハードウェア構成極性ビット

38 リセットラッチ

42 累積リセット信号

44 ホストインタフェース

46 ハードウェアリセット端子

49 端子

52 電力切断マルチプレクサ

58 ハードウェアイネーブルラッチ

62 極性ラッチ

64 第2マルチプレクサ

66 ラッチペア

67 ソフトウェアパワーオンビット

【特許請求の範囲】

【請求項1】

周辺装置に接続され、ホストによって制御されるグラフィックスコントローラであって、前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、そのレベルシフタと接地との間の電流経路内のスイッチとを含み、そのスイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに電力切断制御回路を含んで構成されており、該電力切断制御回路は、

その第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納された前記当該データを前記第1及び第2記憶素子のそれぞれの記憶出力に供給するメモリペアであって、前記第1及び第2記憶素子のうちの一方の記憶データ出力をスイッチの第1制御状態に対応するようにさせ、前記第1及び第2記憶素子の他方の記憶データ出力をスイッチの第2制御状態に対応するようにさせる極性選択入力を有するメモリペアと、

前記メモリペアのそれぞれの記憶出力に接続された入力と、スイッチを制御するためのスイッチの制御線に接続された出力と、前記第1及び第2記憶素子の記憶出力のうちの一方又は他方を選択するために前記入力間で選択するための選択線とを有する第1選択回路を含む、グラフィックスコントローラ。

【請求項2】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項1に記載のグラフィックスコントローラ。

【請求項3】

前記メモリペアの前記極性選択入力はグラフィックスコントローラをリセットするためのグラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は周辺装置への電力がオフになるとスイッチの第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項1に記載のグラフィックスコントローラ。

【請求項4】

前記第1選択回路は、周辺装置への電力がオンになると、スイッチの第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項3に記載のグラフィックスコントローラ。

【請求項5】

前記累積リセット信号はグラフィックスコントローラによって内部的にアサートされる、請求項3に記載のグラフィックスコントローラ。

【請求項6】

グラフィックスコントローラはホストとインタフェースをとるためのホストインタフェースを含み、回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための論理回路とを備え、当該論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記論理回路によってアサートされる、請求項5に記載のグラフィックスコントローラ。

【請求項7】

グラフィックスコントローラの端子を介してホストに接続されたリセット線をさらに備え、当該リセット線はハードウェアリセット信号を送信するためのものであり、前記論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は、前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると前記論理回路によってアサートされる、請求項6に記載のグラフィックスコントローラ。

【請求項8】

グラフィックスコントローラは、前記ホストとインタフェースをとり、前記ホストからデータを受け取り、そのデータを前記ラッチペアに送るためのホストインタフェースを含んで構成されている、請求項1に記載のグラフィックスコントローラ。

【請求項9】

グラフィックスコントローラはホストインタフェースを含んで構成され、回路はさらに第2選択回路が前記第1選択回路の前記出力とスイッチとの間に挿入されており、当該第2選択回路は前記メモリペアにそれぞれ接続された入力とハードウェア制御回路と前記入力間で選択するための選択線とを有し、回路はさらに前記第2選択回路の選択線を制御するためのハードウェア制御ビットをラッチするためのハードウェア制御ラッチを備え、前記ハードウェア制御回路は周辺装置への電力がオンかオフかを示す表示(indication)を受け取るように構成されている、請求項1に記載のグラフィックスコントローラ。

【請求項10】

前記ハードウェア制御回路は、ハードウェア極性ビットをラッチするためのハードウェア極性ラッチを備えると共に、前記表示及びラッチされた前記ハードウェア極性ビットを受け取り、前記表示と前記ハードウェア極性ビットとの排他的論理和形成結果に従ってスイッチをその制御状態の一つに駆動するための出力を供給するための第1論理回路を備える、請求項9に記載のグラフィックスコントローラ。

【請求項11】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項10に記載のグラフィックスコントローラ。

【請求項12】

前記メモリペアの前記極性選択入力はグラフィックスコントローラをリセットするためのグラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は周辺装置への電力がオフになるとスイッチの第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項10に記載のグラフィックスコントローラ。

【請求項13】

前記第1選択回路は、周辺装置への電力がオンになるとスイッチの第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項12に記載のグラフィックスコントローラ。

【請求項14】

前記累積リセット信号はグラフィックスコントローラによって内部的にアサートされる、請求項13に記載のグラフィックスコントローラ。

【請求項15】

グラフィックスコントローラはホストとインタフェースをとるためのホストインタフェースを含み、回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための第2論理回路とを備え、当該第2論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記第2論理回路によってアサートされる、請求項15に記載のグラフィックスコントローラ。

【請求項16】

グラフィックスコントローラの端子を介してホストに接続されたリセット線をさらに備え、当該リセット線はハードウェアリセット信号を送るためのものであり、前記第2論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は、前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると前記第2論理回路によってアサートされる、請求項15に記載のグラフィックスコントローラ。

【請求項17】

グラフィックスコントローラは前記ラッチペアにデータを送るためにホストインタフェースを含んで構成されている、請求項16に記載のグラフィックスコントローラ。

【請求項18】

ホストと、周辺装置と、前記ホストによって制御され前記周辺装置に接続されたグラフィックスコントローラとを備えるシステムであって、

前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、そのレベルシフタと接地との間の電流経路内のスイッチとを含み、スイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに電力切断制御回路を含んで構成され、

該電力切断制御回路は、

第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納された前記当該データを第1及び第2記憶素子のそれぞれの記憶出力に供給するためのメモリペアであって、前記第1及び第2記憶素子のうちの一方の記憶データ出力をスイッチの第1制御状態に対応するようにさせ、前記第1及び第2記憶素子の他方の記憶データ出力をスイッチの第2制御状態に対応するようにさせる極性選択入力を有するメモリペアと、

前記メモリペアのそれぞれの記憶出力に接続された入力と、スイッチを制御するためのスイッチの制御線に接続された出力と、前記第1及び第2記憶素子の記憶出力のうちの一方又は他方を選択するために前記入力間で選択するための選択線とを有する第1選択回路を備える、システム。

【請求項19】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項18に記載のシステム。

【請求項20】

前記メモリペアの前記極性選択入力は前記グラフィックスコントローラをリセットするためのグラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は周辺装置への電力がオフになると前記スイッチの前記第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項18に記載のシステム。

【請求項21】

前記第1選択回路は、周辺装置への電力がオンになると前記スイッチの前記第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項20に記載のシステム。

【請求項22】

前記累積リセット信号は前記グラフィックスコントローラによって内部的にアサートされる、請求項20に記載のシステム。

【請求項23】

前記グラフィックスコントローラにはホストインタフェースがあり、前記電力切断保護制御回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための論理回路とを備え、当該論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記論理回路によってアサートされる、請求項22に記載のシステム。

【請求項24】

前記グラフィックスコントローラはその端子を介して前記ホストに接続されたリセット線をさらに備え、当該リセット線は前記ホストからハードウェアリセット信号を送るためのものであり、前記論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると前記論理回路によってアサートされる、請求項23に記載のシステム。

【請求項25】

前記グラフィックスコントローラは、前記ホストとインタフェースをとり、前記ホストからデータを受け取り、そしてデータを前記ラッチペアに送るためのホストインタフェースを含んで構成されている、請求項18に記載のシステム。

【請求項26】

前記グラフィックスコントローラは前記ホストとインタフェースをとるためのホストインタフェースを含んで構成され、前記電力切断保護制御回路はさらに前記第1選択回路の前記出力とスイッチとの間に挿入された第2選択回路を備えており、当該第2選択回路は前記メモリペアにそれぞれ接続された入力とハードウェア制御回路と前記入力間で選択するための選択線とを有し、前記電力切断保護制御回路はさらに前記第2選択回路の選択線を制御するためのハードウェア制御ビットをラッチするためのハードウェア制御ラッチを備え、前記ハードウェア制御回路は周辺装置への電力がオンかオフかを示す表示を受け取るように構成されている、請求項18に記載のシステム。

【請求項27】

前記ハードウェア制御回路は、ハードウェア極性ビットをラッチするためのハードウェア極性ラッチと、前記表示及びラッチされた前記ハードウェア極性ビットを受け取り、前記表示及び前記ハードウェア極性ビットの排他的論理和形成結果に従ってスイッチをその制御状態の一つに駆動するための出力を供給するための第1論理回路とを備える、請求項26に記載のシステム。

【請求項28】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項27に記載のシステム。

【請求項29】

前記メモリペアの前記極性選択入力は前記グラフィックスコントローラをリセットするための前記グラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は前記周辺装置への電力がオフになるとスイッチの第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項27に記載のシステム。

【請求項30】

前記第1選択回路は前記周辺装置への電力がオンになるとスイッチの第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項29に記載のシステム。

【請求項31】

前記累積リセット信号は前記グラフィックスコントローラによって内部的にアサートされる、請求項31に記載のシステム。

【請求項32】

前記グラフィックスコントローラは前記ホストとインタフェースをとるためのホストインタフェースを含み、前記電力切断保護制御回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための第2論理回路とを備え、当該第2論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記第2論理回路によってアサートされる、請求項31に記載のシステム。

【請求項33】

前記グラフィックスコントローラはさらにその端子を介して前記ホストに接続されたリセット線をさらに備え、当該リセット線はハードウェアリセット信号を送るためのものであり、前記第2論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は、前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると、前記第2論理回路によってアサートされる、請求項32に記載のシステム。

【請求項34】

前記グラフィックスコントローラは、前記ホストとインタフェースをとり、前記ホストからデータを受け取り、データを前記ラッチペアに送るためのホストインタフェースを含んで構成されている、請求項33に記載のシステム。

【請求項35】

周辺装置に接続され、ホストによって制御されるグラフィックスコントローラを含んで構成されたシステムにおける、周辺装置への電力の切断を制御するための方法であって、

前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、該レベルシフタと接地との間の電流経路内のスイッチとを含み、該スイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに第1及び第2メモリからなるメモリペアを含んで構成され、

周辺装置への電力の切断を制御するための方法は、

極性の表示を提供するステップと、

グラフィックスコントローラをリセットするステップと、

グラフィックスコントローラをリセットする前記ステップに応じてメモリペアの第1メモリに第1制御状態に対応する第1表示を格納するステップと、

グラフィックスコントローラをリセットする前記ステップに応じてメモリペアの第2メモリに第2制御状態に対応する第2表示を格納するステップと、

前記極性表示に従って第1及び第2メモリのうちの一つの出力を選択するステップと、

選択された前記出力に従ってスイッチを駆動するステップとを有する方法。

【請求項36】

周辺装置への電力をオフにし、グラフィックスコントローラをリセットする前記ステップよりも前にスイッチを閉じるステップをさらに有する、請求項35に記載の方法。

【請求項37】

前記メモリペアの前記第1メモリ並びに第2メモリに第3表示を格納することにより、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開くステップをさらに有する、請求項36に記載の方法。

【請求項38】

周辺装置への電力がオンであることを示すホストからの第1表示を受け取り、ある所定の極性を示す第2表示を受け取り、そして前記第1及び第2表示の排他的論理和を形成することにより、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開くステップをさらに有する、請求項36に記載の方法。

【請求項39】

周辺装置に接続され、ホストによって制御されるグラフィックスコントローラを含んで構成されたシステムにおける、周辺装置への電力の切断を制御するための方法を実行するべく機械で実行可能な命令プログラムを含んだ機械可読媒体であって、

前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、該レベルシフタと接地との間の電流経路内のスイッチとを含み、該スイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに第1及び第2メモリからなるメモリペアを含んで構成され、極性表示を提供し、前記グラフィックスコントローラをリセットし、前記スイッチを駆動してなる周辺装置への電力の切断を制御するための方法を実行するために、

前記グラフィックスコントローラをリセットする前記ステップに応じて第1制御状態に対応する第1表示をメモリペアの第1メモリに格納させるステップと、

前記グラフィックスコントローラをリセットする前記ステップに応じて第2制御状態に対応する第2表示をメモリペアの第1メモリに格納させるステップと、

前記極性表示に従って第1及び第2メモリのうちの一つの出力を選択するステップとをさらに有し、スイッチを駆動するステップは選択された前記出力に従って実行される、方法を実行するべく機械で実行可能な命令プログラムを含んだ機械可読媒体。

【請求項40】

方法はさらに、周辺装置への電力をオフにし、グラフィックスコントローラをリセットするステップよりも前にスイッチを閉じ、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開けるステップをさらに有し、方法の更なるステップは、前記メモリペアの前記第1メモリ並びに第2メモリに第3表示を格納させることからなり、スイッチを開く前記ステップは当該第3表示に従って実行される、請求項39に記載の媒体。

【請求項41】

方法はさらに、周辺装置への電力をオフにし、グラフィックスコントローラをリセットするステップよりも前にスイッチを閉じ、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開けるステップをさらに有し、方法の更なるステップは、周辺装置への電力がオンになっていることを示すホストからの第1表示を受け取り、ある所定の極性を示す第2表示を受け取り、前記第1及び第2表示の排他的論理和を形成することからなる、請求項39に記載の媒体。

【請求項1】

周辺装置に接続され、ホストによって制御されるグラフィックスコントローラであって、前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、そのレベルシフタと接地との間の電流経路内のスイッチとを含み、そのスイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに電力切断制御回路を含んで構成されており、該電力切断制御回路は、

その第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納された前記当該データを前記第1及び第2記憶素子のそれぞれの記憶出力に供給するメモリペアであって、前記第1及び第2記憶素子のうちの一方の記憶データ出力をスイッチの第1制御状態に対応するようにさせ、前記第1及び第2記憶素子の他方の記憶データ出力をスイッチの第2制御状態に対応するようにさせる極性選択入力を有するメモリペアと、

前記メモリペアのそれぞれの記憶出力に接続された入力と、スイッチを制御するためのスイッチの制御線に接続された出力と、前記第1及び第2記憶素子の記憶出力のうちの一方又は他方を選択するために前記入力間で選択するための選択線とを有する第1選択回路を含む、グラフィックスコントローラ。

【請求項2】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項1に記載のグラフィックスコントローラ。

【請求項3】

前記メモリペアの前記極性選択入力はグラフィックスコントローラをリセットするためのグラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は周辺装置への電力がオフになるとスイッチの第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項1に記載のグラフィックスコントローラ。

【請求項4】

前記第1選択回路は、周辺装置への電力がオンになると、スイッチの第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項3に記載のグラフィックスコントローラ。

【請求項5】

前記累積リセット信号はグラフィックスコントローラによって内部的にアサートされる、請求項3に記載のグラフィックスコントローラ。

【請求項6】

グラフィックスコントローラはホストとインタフェースをとるためのホストインタフェースを含み、回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための論理回路とを備え、当該論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記論理回路によってアサートされる、請求項5に記載のグラフィックスコントローラ。

【請求項7】

グラフィックスコントローラの端子を介してホストに接続されたリセット線をさらに備え、当該リセット線はハードウェアリセット信号を送信するためのものであり、前記論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は、前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると前記論理回路によってアサートされる、請求項6に記載のグラフィックスコントローラ。

【請求項8】

グラフィックスコントローラは、前記ホストとインタフェースをとり、前記ホストからデータを受け取り、そのデータを前記ラッチペアに送るためのホストインタフェースを含んで構成されている、請求項1に記載のグラフィックスコントローラ。

【請求項9】

グラフィックスコントローラはホストインタフェースを含んで構成され、回路はさらに第2選択回路が前記第1選択回路の前記出力とスイッチとの間に挿入されており、当該第2選択回路は前記メモリペアにそれぞれ接続された入力とハードウェア制御回路と前記入力間で選択するための選択線とを有し、回路はさらに前記第2選択回路の選択線を制御するためのハードウェア制御ビットをラッチするためのハードウェア制御ラッチを備え、前記ハードウェア制御回路は周辺装置への電力がオンかオフかを示す表示(indication)を受け取るように構成されている、請求項1に記載のグラフィックスコントローラ。

【請求項10】

前記ハードウェア制御回路は、ハードウェア極性ビットをラッチするためのハードウェア極性ラッチを備えると共に、前記表示及びラッチされた前記ハードウェア極性ビットを受け取り、前記表示と前記ハードウェア極性ビットとの排他的論理和形成結果に従ってスイッチをその制御状態の一つに駆動するための出力を供給するための第1論理回路を備える、請求項9に記載のグラフィックスコントローラ。

【請求項11】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項10に記載のグラフィックスコントローラ。

【請求項12】

前記メモリペアの前記極性選択入力はグラフィックスコントローラをリセットするためのグラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は周辺装置への電力がオフになるとスイッチの第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項10に記載のグラフィックスコントローラ。

【請求項13】

前記第1選択回路は、周辺装置への電力がオンになるとスイッチの第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項12に記載のグラフィックスコントローラ。

【請求項14】

前記累積リセット信号はグラフィックスコントローラによって内部的にアサートされる、請求項13に記載のグラフィックスコントローラ。

【請求項15】

グラフィックスコントローラはホストとインタフェースをとるためのホストインタフェースを含み、回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための第2論理回路とを備え、当該第2論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記第2論理回路によってアサートされる、請求項15に記載のグラフィックスコントローラ。

【請求項16】

グラフィックスコントローラの端子を介してホストに接続されたリセット線をさらに備え、当該リセット線はハードウェアリセット信号を送るためのものであり、前記第2論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は、前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると前記第2論理回路によってアサートされる、請求項15に記載のグラフィックスコントローラ。

【請求項17】

グラフィックスコントローラは前記ラッチペアにデータを送るためにホストインタフェースを含んで構成されている、請求項16に記載のグラフィックスコントローラ。

【請求項18】

ホストと、周辺装置と、前記ホストによって制御され前記周辺装置に接続されたグラフィックスコントローラとを備えるシステムであって、

前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、そのレベルシフタと接地との間の電流経路内のスイッチとを含み、スイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに電力切断制御回路を含んで構成され、

該電力切断制御回路は、

第1及び第2記憶素子のそれぞれの記憶入力で使用可能になるデータを格納し、その格納された前記当該データを第1及び第2記憶素子のそれぞれの記憶出力に供給するためのメモリペアであって、前記第1及び第2記憶素子のうちの一方の記憶データ出力をスイッチの第1制御状態に対応するようにさせ、前記第1及び第2記憶素子の他方の記憶データ出力をスイッチの第2制御状態に対応するようにさせる極性選択入力を有するメモリペアと、

前記メモリペアのそれぞれの記憶出力に接続された入力と、スイッチを制御するためのスイッチの制御線に接続された出力と、前記第1及び第2記憶素子の記憶出力のうちの一方又は他方を選択するために前記入力間で選択するための選択線とを有する第1選択回路を備える、システム。

【請求項19】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項18に記載のシステム。

【請求項20】

前記メモリペアの前記極性選択入力は前記グラフィックスコントローラをリセットするためのグラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は周辺装置への電力がオフになると前記スイッチの前記第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項18に記載のシステム。

【請求項21】

前記第1選択回路は、周辺装置への電力がオンになると前記スイッチの前記第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項20に記載のシステム。

【請求項22】

前記累積リセット信号は前記グラフィックスコントローラによって内部的にアサートされる、請求項20に記載のシステム。

【請求項23】

前記グラフィックスコントローラにはホストインタフェースがあり、前記電力切断保護制御回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための論理回路とを備え、当該論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記論理回路によってアサートされる、請求項22に記載のシステム。

【請求項24】

前記グラフィックスコントローラはその端子を介して前記ホストに接続されたリセット線をさらに備え、当該リセット線は前記ホストからハードウェアリセット信号を送るためのものであり、前記論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると前記論理回路によってアサートされる、請求項23に記載のシステム。

【請求項25】

前記グラフィックスコントローラは、前記ホストとインタフェースをとり、前記ホストからデータを受け取り、そしてデータを前記ラッチペアに送るためのホストインタフェースを含んで構成されている、請求項18に記載のシステム。

【請求項26】

前記グラフィックスコントローラは前記ホストとインタフェースをとるためのホストインタフェースを含んで構成され、前記電力切断保護制御回路はさらに前記第1選択回路の前記出力とスイッチとの間に挿入された第2選択回路を備えており、当該第2選択回路は前記メモリペアにそれぞれ接続された入力とハードウェア制御回路と前記入力間で選択するための選択線とを有し、前記電力切断保護制御回路はさらに前記第2選択回路の選択線を制御するためのハードウェア制御ビットをラッチするためのハードウェア制御ラッチを備え、前記ハードウェア制御回路は周辺装置への電力がオンかオフかを示す表示を受け取るように構成されている、請求項18に記載のシステム。

【請求項27】

前記ハードウェア制御回路は、ハードウェア極性ビットをラッチするためのハードウェア極性ラッチと、前記表示及びラッチされた前記ハードウェア極性ビットを受け取り、前記表示及び前記ハードウェア極性ビットの排他的論理和形成結果に従ってスイッチをその制御状態の一つに駆動するための出力を供給するための第1論理回路とを備える、請求項26に記載のシステム。

【請求項28】

前記第1及び第2記憶素子はそれぞれデータラッチからなる、請求項27に記載のシステム。

【請求項29】

前記メモリペアの前記極性選択入力は前記グラフィックスコントローラをリセットするための前記グラフィックスコントローラ内の累積リセット信号に応答し、前記第1選択回路は前記周辺装置への電力がオフになるとスイッチの第1制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項27に記載のシステム。

【請求項30】

前記第1選択回路は前記周辺装置への電力がオンになるとスイッチの第2制御状態に対応する前記記憶素子の記憶出力の一つを選択するように構成されている、請求項29に記載のシステム。

【請求項31】

前記累積リセット信号は前記グラフィックスコントローラによって内部的にアサートされる、請求項31に記載のシステム。

【請求項32】

前記グラフィックスコントローラは前記ホストとインタフェースをとるためのホストインタフェースを含み、前記電力切断保護制御回路はさらにリセットビットをラッチするためのリセットビットラッチと前記累積リセット信号を生成するための第2論理回路とを備え、当該第2論理回路は内部リセット信号を受け取るための入力と前記リセットビットを受け取るための入力とを有し、前記累積リセット信号は前記内部リセット信号及び前記リセットビットのうちのどちらかがアサートされると前記第2論理回路によってアサートされる、請求項31に記載のシステム。

【請求項33】

前記グラフィックスコントローラはさらにその端子を介して前記ホストに接続されたリセット線をさらに備え、当該リセット線はハードウェアリセット信号を送るためのものであり、前記第2論理回路は前記ハードウェアリセット信号を受け取るための入力を有し、前記累積リセット信号は、前記内部リセット信号、前記ソフトウェアリセットビット、及び前記ハードウェアリセット信号のうちのどれかがアサートされると、前記第2論理回路によってアサートされる、請求項32に記載のシステム。

【請求項34】

前記グラフィックスコントローラは、前記ホストとインタフェースをとり、前記ホストからデータを受け取り、データを前記ラッチペアに送るためのホストインタフェースを含んで構成されている、請求項33に記載のシステム。

【請求項35】

周辺装置に接続され、ホストによって制御されるグラフィックスコントローラを含んで構成されたシステムにおける、周辺装置への電力の切断を制御するための方法であって、

前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、該レベルシフタと接地との間の電流経路内のスイッチとを含み、該スイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに第1及び第2メモリからなるメモリペアを含んで構成され、

周辺装置への電力の切断を制御するための方法は、

極性の表示を提供するステップと、

グラフィックスコントローラをリセットするステップと、

グラフィックスコントローラをリセットする前記ステップに応じてメモリペアの第1メモリに第1制御状態に対応する第1表示を格納するステップと、

グラフィックスコントローラをリセットする前記ステップに応じてメモリペアの第2メモリに第2制御状態に対応する第2表示を格納するステップと、

前記極性表示に従って第1及び第2メモリのうちの一つの出力を選択するステップと、

選択された前記出力に従ってスイッチを駆動するステップとを有する方法。

【請求項36】

周辺装置への電力をオフにし、グラフィックスコントローラをリセットする前記ステップよりも前にスイッチを閉じるステップをさらに有する、請求項35に記載の方法。

【請求項37】

前記メモリペアの前記第1メモリ並びに第2メモリに第3表示を格納することにより、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開くステップをさらに有する、請求項36に記載の方法。

【請求項38】

周辺装置への電力がオンであることを示すホストからの第1表示を受け取り、ある所定の極性を示す第2表示を受け取り、そして前記第1及び第2表示の排他的論理和を形成することにより、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開くステップをさらに有する、請求項36に記載の方法。

【請求項39】

周辺装置に接続され、ホストによって制御されるグラフィックスコントローラを含んで構成されたシステムにおける、周辺装置への電力の切断を制御するための方法を実行するべく機械で実行可能な命令プログラムを含んだ機械可読媒体であって、

前記グラフィックスコントローラは、周辺装置から受け取った信号の電圧レベルをグラフィックスコントローラ内で信号を処理するのに適した別の電圧レベルにシフトさせるためのレベルシフタと、該レベルシフタと接地との間の電流経路内のスイッチとを含み、該スイッチはその第1制御状態でオンにそして第2制御状態でオフになり、前記グラフィックスコントローラはさらに第1及び第2メモリからなるメモリペアを含んで構成され、極性表示を提供し、前記グラフィックスコントローラをリセットし、前記スイッチを駆動してなる周辺装置への電力の切断を制御するための方法を実行するために、

前記グラフィックスコントローラをリセットする前記ステップに応じて第1制御状態に対応する第1表示をメモリペアの第1メモリに格納させるステップと、

前記グラフィックスコントローラをリセットする前記ステップに応じて第2制御状態に対応する第2表示をメモリペアの第1メモリに格納させるステップと、

前記極性表示に従って第1及び第2メモリのうちの一つの出力を選択するステップとをさらに有し、スイッチを駆動するステップは選択された前記出力に従って実行される、方法を実行するべく機械で実行可能な命令プログラムを含んだ機械可読媒体。

【請求項40】

方法はさらに、周辺装置への電力をオフにし、グラフィックスコントローラをリセットするステップよりも前にスイッチを閉じ、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開けるステップをさらに有し、方法の更なるステップは、前記メモリペアの前記第1メモリ並びに第2メモリに第3表示を格納させることからなり、スイッチを開く前記ステップは当該第3表示に従って実行される、請求項39に記載の媒体。

【請求項41】

方法はさらに、周辺装置への電力をオフにし、グラフィックスコントローラをリセットするステップよりも前にスイッチを閉じ、スイッチを閉じる前記ステップの後に周辺装置への電力をオンにし、その後スイッチを開けるステップをさらに有し、方法の更なるステップは、周辺装置への電力がオンになっていることを示すホストからの第1表示を受け取り、ある所定の極性を示す第2表示を受け取り、前記第1及び第2表示の排他的論理和を形成することからなる、請求項39に記載の媒体。

【図1】

【図2】

【図2】

【公開番号】特開2006−40294(P2006−40294A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2005−220467(P2005−220467)

【出願日】平成17年7月29日(2005.7.29)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成17年7月29日(2005.7.29)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]