ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施の形態は、電圧制御型スイッチング素子のゲート駆動回路およびパワー半導体モジュールに関する。

【背景技術】

【0002】

電気自動車や太陽光発電システムなどにはインバータに代表される電力変換装置が使用されており、システム全体の効率向上のために、電力変換装置の損失を小さくすることが要求される。

【0003】

電力変換装置の損失の約50%は半導体スイッチング素子の損失であり、半導体スイッチング素子の低損失化が重要な技術である。

【0004】

近年、電力変換装置には半導体スイッチング素子として、電圧制御型トランジスタであるのMOSFET(Metal Oxide Semiconductor Field Effect

Transistor)やIGBT(Insulated

Gate Bipolar Transistor)が広く用いられている。

【0005】

これらのスイッチング素子はゲート・ソース間(またはゲート・エミッタ間)にゲート駆動回路から+15V程度の電圧を印加することにより、ゲート・ソース間(またはゲート・エミッタ間)の電圧が閾値をこえて、ドレイン・ソース間(またはコレクタ・エミッタ間)が導通状態となりオン状態となる。

【0006】

また、スイッチング素子をオフさせるときはゲート駆動回路の出力電圧を0Vまたは−15V程度の電圧とすることにより、ゲート・ソース間(またはゲート・エミッタ間)の電圧を閾値以下にする。

【0007】

MOSFETおよびIGBTのゲート電極は酸化膜で覆われる構造となっており、ゲート電極とソース電極(またはエミッタ電極)の間にゲート・ソース間キャパシタンス(またはゲート・エミッタ間キャパシタンス)および、ゲート電極とドレイン電極(またはコレクタ電極)間のゲート・ドレイン間キャパシタンス(またはゲート・コレクタ間キャパシタンス)が形成される。

【0008】

したがって、スイッチング素子のゲート側の等価回路はゲート・ソース間キャパシタンス(またはゲート・エミッタ間キャパシタンス)とゲート・ドレイン間キャパシタス(またはゲート・コレクタ間キャパシタンス)の並列接続となる。

【0009】

通常、ゲート駆動回路とスイッチング素子のゲート電極間にゲート抵抗が接続される。したがって、スイッチング素子をオンさせるためにゲート駆動回路から+15V程度の電圧を印加するとゲート抵抗を介してゲート・ソース間キャパシタンス(またはゲート・エミッタ間キャパシタンス)とゲート・ドレイン間キャパシタス(またはゲート・コレクタ間キャパシタンス)を充電することになる。

【0010】

標準的なハードスイッチング回路ではゲート回路の値を変化させることにより、上記キャパシタンスの充電時間を変化させ、スイッチング素子のスイッチング時間を調整する。

【0011】

スイッチング損失はスイッチング時間を短くすることにより小さくできるので、スイッチング素子の低損失化のため、ゲート抵抗の値を小さくし、スイッチング時間を短縮させる方法がとられている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2009−290287号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

図1に示すインバータ回路では、スイッチング素子をハイサイドとローサイドに設置して上下アームを構成し、ハイサイドスイッチング素子がオン状態のとき、ローサイドスイッチング素子はオフ状態、また、ハイサイドスイッチング素子がオフ状態のとき、ローサイドスイッチング素子はオン状態となるように、どちらか一方がオンのときはもう片方はオフ状態になるように制御される。また、両方のスイッチング素子が同時にオンすると上下アームにスイッチング素子の定格電流以上の短絡電流が流れてしまい、スイッチング素子が破壊してしまう可能性がある。したがって、同時にオン状態にならないように、両方の素子が同時にオフ状態になる期間(デッドタイム)をもうける。

【0014】

ここで、図2に示すように、一方のスイッチング素子がオフ状態からオン状態になるともう片方のスイッチング素子のドレイン・ソース間(またはコレクタ・エミッタ間)電圧は、0Vから入力直流電圧に自動的に変化する。それにともない、ゲート・ドレイン間(またはゲート・コレクタ間)キャパシタンスがほぼ入力直流電圧と同じ値まで充電される。

【0015】

このとき、ゲート・ドレイン間(またはゲート・コレクタ間)キャパシタンスに変位電流が流れ、この電流がゲート・ソース間(またはゲート・エミッタ間)キャパシタンスを充電し、ゲート電圧が閾値をこえてしまい、スイッチング素子がオンしてしまうことがある。

【0016】

変位電流のピーク値はスイッチング素子のドレイン・ソース間(またはコレクタ・エミッタ間)電圧の時間変化の割合(dV/dt)に比例するので、スイッチング素子のスイッチング損失を小さくするためにスイッチング時間を短くすると変位電流のピーク値が大きくなり、先に説明した原理でスイッチング素子がオンしやすくなる。

【0017】

そこで、ゲート・ソース間(またはゲート・エミッタ間)を半導体スイッチング素子で短絡することにより、ゲート電圧が閾値をこえないようにするゲート駆動回路が検討されている。

【0018】

しかしながら、このような回路では、通常必要なゲート駆動回路を構成する部品の他に、ダイオードを2個、抵抗を1個、スイッチング素子を1個などの素子を少なくとも追加する必要がある。また、上記スイッチング素子は通常のゲート駆動回路の制御信号に同期して動作させる必要があり、同期信号を発生させるための制御装置が必要になることと、それらの回路全体の設計が複雑になる。

【0019】

本発明の実施の形態はこのような課題を解決するためのものであり、スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を、部品点数の少ない簡易な回路構成で実現することを目的とする。

【課題を解決するための手段】

【0020】

上記目的を達成するための第1の実施の形態であるゲート駆動回路は、ローサイドゲート駆動回路の出力端子にトランスの1次側を接続し、ハイサイドスイッチング素子のゲート・ソース間にトランスの1次側電圧と反対の極性の電圧が発生するようにトランスの2次側を接続する。これによって、ローサイドゲート駆動回路から正極性のゲート駆動電圧が出力されるとトランスを介してハイサイドスイッチング素子のゲート・ソース間に負極性の電圧パルスが印加され、ゲート・ソース間電圧は閾値以下の電圧となり、ローサイドスイッチング素子がターンオンするときに、ハイサイドスイッチング素子がオフ状態を保持するようにしたものである。

【0021】

上記目的を達成するための第2の実施の形態であるゲート駆動回路は、スイッチング素子のゲート・ソース間にNchノーマリーオン型スイッチング素子のドレイン・ソースを接続し、トランスの1次側をゲート駆動回路の出力に接続する。また、ゲート駆動回路から正極性のゲート駆動電圧が出力されるとNchノーマリーオン型スイッチング素子のゲート・ソース間に負極性の電圧パルスが印加されるようにトランスの2次側をNchノーマリーオン型スイッチング素子のゲート・ソース間に接続する。そして、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される。ローサイドゲート駆動回路から正極性の電圧が出力され、ローサイドスイッチング素子がターンオンしたときに、ハイサイドのNchノーマリーオン型スイッチング素子のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりハイサイドスイッチング素子のゲート・ソース間が短絡され、ハイサイドスイッチング素子がオフ状態を保持するようにしたものである。一方、ハイサイドゲート駆動回路から正極性の電圧が出力され、ハイサイドスイッチング素子がターンオンしたときに、ローサイドのNchノーマリーオン型スイッチング素子のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりローサイドスイッチング素子のゲート・ソース間が短絡され、ローサイドスイッチング素子がオフ状態を保持するようにしたものである。

【0022】

上記目的を達成するための第3の実施の形態であるゲート駆動回路は、スイッチング素子のゲート・ソース間にPchノーマリーオン型スイッチング素子のドレイン・ソースを接続する。また、前記Pchノーマリーオン型スイッチング素子のゲート駆動回路は前記スイッチング素子のゲート駆動回路と共通とする。ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される。ローサイドゲート駆動回路から正極性の電圧が出力され、ローサイドスイッチング素子がターンオンしたときに、ハイサイドPchノーマリーオン型スイッチング素子はオン状態となりハイサイドスイッチング素子のゲート・ソース間が短絡され、ハイサイドスイッチング素子がオフ状態を保持するようにしたものである。一方、ハイサイドスイッチング素子がターンオンしたときに、ローサイドPchノーマリーオン型スイッチング素子はオン状態となりローサイドスイッチング素子のゲート・ソース間が短絡され、ローサイドスイッチング素子がオフ状態を保持するようにしたものである。

【図面の簡単な説明】

【0023】

【図1】従来のインバータ回路の1レグ分を示す等価回路図である。

【図2】従来のインバータ回路におけるスイッチング素子のゲート・ソース間に発生するゲート電圧波形図である。

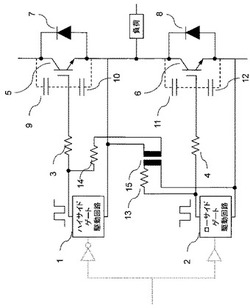

【図3】実施例1のゲート駆動回路の等価回路図である。

【図4】実施例1のシミュレーション波形図である。

【図5】実施例2のゲート駆動回路の等価回路図である。

【図6】実施例3のゲート駆動回路の等価回路図である。

【発明を実施するための形態】

【0024】

以下,本発明の実施形態について図面を用いて説明する。

【0025】

[第1の実施の形態]

まず、第1の実施の形態に係わるゲート駆動回路について説明する。

図3は、本発明の実施の形態に係わるゲート駆動回路の等価回路である。ローサイドゲート駆動回路2の出力端子にトランス15の1次側を接続し、ハイサイドスイッチング素子5のゲート・ソース間にトランスの1次側電圧と反対の極性の電圧が発生するようにトランス15の2次側が接続される。

【0026】

ローサイドゲート駆動回路2から正極性のゲート駆動電圧が出力されるとトランス15を介してハイサイドスイッチング素子5のゲート・ソース間に負極性の電圧パルスが印加され、ゲート・ソース間電圧は閾値以下の電圧となり、ローサイドスイッチング素子6がターンオンするときに、ハイサイドスイッチング素子5がオフ状態を保持する。

【0027】

図4は、実施例1のゲート駆動回路の回路シミュレーション結果である。ローサイドゲート・エミッタ電圧が0Vから+15Vの電圧に変化する期間において、ハイサイドゲート・エミッタ電圧には負極性のパルス電圧が印加されていることが確認できる。また、ハイサイドコレクタ電流も流れていないことから、ハイサイドスイッチング素子はオフ状態を維持していることが確認できる。

【0028】

この実施の形態によれば、ターンオンする側のスイッチング素子の各種電圧・電流の状態を検出して、その状態をゲート駆動側へフィードバックするための外部制御回路を追加することなく、自動的に、ターンオンしない側のスイッチング素子のオフ状態を保持できる点で好ましい効果が得られる。

【0029】

かかる第1の実施の形態におけるトランスとしては、空芯トランスを用いることが好ましい。これは、磁性体コアを有するトランスでは、ヒステリシス損失が発生し、損失低下に寄与しないからである。また空芯トランスを使用すると、比較的コスト面で有利である。

【0030】

また、この実施の形態で、ゲート駆動回路は、スイッチング素子がオフ状態は0V、オン状態は正極性の電圧を出力するものであることが好ましい。

その理由は、以下の通りである。すなわち、本実施の形態で解決しようとする課題は、変位電流によりゲート・ソース間キャパシタンスが充電され、ゲート・ソース間で電圧が閾値を越えてしまい誤動作するおそれがあることを解消するものである。この現象を防止する簡単な方法として、スイッチング素子がオフ状態の時に、ゲート・ソース間にマイナスバイアス(負極性の電圧を印加する)ことにより、充電電圧が閾値を越えないようにする方法がある。この場合、負極性の電源が別に必要なため、ゲート回路のコストが上昇するという欠点がある。本実施の形態によれば、負極性の電源が不要となるので、電力変換装置のコストを下げることが可能になる。

【0031】

[第2の実施の形態]

図5は、第2の実施の形態に係わるゲート駆動回路の等価回路である。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をハイサイドゲート駆動回路1の出力に接続し、ハイサイドゲート駆動回路1から正極性のゲート駆動電圧が出力されるとNchノーマリーオン型スイッチング素子13のゲート・ソース間に負極性の電圧パルスが印加されるようにトランス15の2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続する。なお、ローサイドもハイサイドと同様な構成・動作原理であるので、説明は省略する。

【0032】

ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるようにハイサイドゲート駆動回路1とローサイドゲート駆動回路2が制御する。

【0033】

ローサイドゲート駆動回路2から正極性の電圧が出力され、ローサイドスイッチング素子6がターンオンしたときに、Nchノーマリーオン型スイッチング素子13のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりハイサイドスイッチング素子5のゲート・ソース間が短絡され、ハイサイドスイッチング素子5がオフ状態を維持する。

【0034】

この実施の形態によれば、特にターンオンする側のスイッチング素子の各種電圧・電流の状態を検出して、その状態をゲート駆動側へフィードバックするための外部制御回路を追加することなく、自動的に、ターンオンしない側のスイッチング素子のオフ状態を保持できる点で好ましい効果が得られる。また、ローサイドスイッチング素子6のターンオン動作終了後もハイサイドスイッチング素子5のゲート・ソース間は短絡された状態であるので、外部から何らかのノイズが侵入した場合でもハイサイドスイッチング素子5はオフ状態を保持できる点で好ましい効果が得られる。

【0035】

かかる第1の実施の形態におけるトランスとしては、空芯トランスを用いることが好ましい。これは、磁性体コアを有するトランスでは、ヒステリシス損失が発生し、損失低下に寄与しないからである。

【0036】

また、この実施の形態においても、前述の第1の実施形態と同様にゲート駆動回路は、スイッチング素子がオフ状態は0V、オン状態は正極性の電圧を出力するものであることが好ましい。

【0037】

[第3の実施の形態]

図6は、本発明の第3の実施の形態に係わるゲート駆動回路の等価回路である。ハイサイドスイッチング素子5のゲート・ソース間にPchノーマリーオン型スイッチング素子14のドレイン・ソースを接続し、ハイサイドゲート駆動回路1で前記Pchノーマリーオン型スイッチング素子14のゲートを駆動する。なお、ローサイドもハイサイドと同様な構成・動作原理であるので、説明は省略する。

【0038】

ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるようにハイサイドゲート駆動回路1とローサイドゲート駆動回路2を制御する。

【0039】

ローサイドゲート駆動回路2から正極性の電圧が出力され、ローサイドスイッチンググ素子6がターンオンしたときに、Pchノーマリーオン型スイッチング素子14のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりハイサイドスイッチング素子5のゲート・ソース間が短絡され、ハイサイドスイッチング素子5がオフ状態を維持する。

【0040】

この実施の形態によれば、特にターンオンする側のスイッチング素子の各種電圧・電流の状態を検出して、その状態をゲート駆動側へフィードバックするための外部制御回路を追加することなく、自動的に、ターンオンしない側のスイッチング素子のオフ状態を保持できる点で好ましい効果が得られる。また、ローサイドスイッチング素子6のターンオン動作終了後もハイサイドスイッチング素子5のゲート・ソース間は短絡された状態であるので、外部から何らかのノイズが侵入した場合でもハイサイドスイッチング素子5はオフ状態を保持できる点で好ましい効果が得られる。

【0041】

かかる第1の実施の形態におけるトランスとしては、空芯トランスを用いることが好ましい。これは、磁性体コアを有するトランスでは、ヒステリシス損失が発生し、損失低下に寄与しないからである。

【0042】

また、この実施の形態においても、前述の第1の実施形態と同様にゲート駆動回路は、スイッチング素子がオフ状態は0V、オン状態は正極性の電圧を出力するものであることが好ましい。

【0043】

以上、3つの実施の形態について説明したが、これらの構成によれば、スイッチング素子のゲート・ソース間(またはゲート・エミッタ間)電圧を閾値以下に保持するための回路を付加したゲート駆動回路を部品点数の少ない簡易な回路構成で実現することができる。

【0044】

[半導体素子チップ、モジュール、パッケージ]

上記各実施の形態においては、この発明の実施の形態として駆動回路として説明したが、この実施の形態の駆動回路は、パルス出力の遅延、波形の鈍り、配線抵抗の増加などを防止するために、可能な限り配線長さが短い方が好ましい。同一の半導体チップ上に形成できる素子は、集合させて同一ICチップ上に形成することが好ましい。また、パッケージとしても同一パッケージに封入しモジュールとすることが好ましい。

【0045】

より具体的には、上述のゲート駆動回路において、トランスを、ローサイドゲート駆動回路、ハイサイドゲート駆動回路、Nch型ノーマリーオン型スイッチング素子、あるいはPchノーマリーオン型スイッチング素子と同一のパッケージに封入してゲート駆動ICとすることができる。また、Nch型ノーマリーオン型スイッチング素子、Pch型ノーマリーオン型スイッチング素子をメインスイッチング素子と同一の半導体チップに集積化してスイッチング素子とすることができる。

【0046】

さらに、ハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入してパワー半導体モジュールとすることができる。

あるいは、ハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、Nchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入してパワー半導体モジュールとすることができる。

また、ハイサイドゲート駆動回路、ローサイドゲート駆動回路、Pchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入してパワー半導体モジュールとすることができる。

【0047】

上記モジュール化、同一パッケージ化によって、以下の効果が期待される。すなわち、(1)回路技術者にとっては、空芯トランスの接続作業が不要化される。(2)各種パワー半導体(スイッチング素子)のパラメータに合わせて最適なパラメータの空芯トランスを組み合わせることにより、回路技術者は特性が最適化されたパワー半導体モジュールなどの部品を採用することができる。(3)パワー半導体チップと空芯トランスの特性が向上する。

【0048】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0049】

1…ハイサイドゲート駆動回路

2…ローサイドゲート駆動回路

3、4、14…抵抗

5…ハイサイドスイッチング素子

6…ローサイドスイッチング素子

7、8…ダイオード

9、10、11、12…キャパシタ

13…Nchノーマリーオン型スイッチング素子

14…Pchノーマリーオン型スイッチング素子

15…トランス

【技術分野】

【0001】

本発明の実施の形態は、電圧制御型スイッチング素子のゲート駆動回路およびパワー半導体モジュールに関する。

【背景技術】

【0002】

電気自動車や太陽光発電システムなどにはインバータに代表される電力変換装置が使用されており、システム全体の効率向上のために、電力変換装置の損失を小さくすることが要求される。

【0003】

電力変換装置の損失の約50%は半導体スイッチング素子の損失であり、半導体スイッチング素子の低損失化が重要な技術である。

【0004】

近年、電力変換装置には半導体スイッチング素子として、電圧制御型トランジスタであるのMOSFET(Metal Oxide Semiconductor Field Effect

Transistor)やIGBT(Insulated

Gate Bipolar Transistor)が広く用いられている。

【0005】

これらのスイッチング素子はゲート・ソース間(またはゲート・エミッタ間)にゲート駆動回路から+15V程度の電圧を印加することにより、ゲート・ソース間(またはゲート・エミッタ間)の電圧が閾値をこえて、ドレイン・ソース間(またはコレクタ・エミッタ間)が導通状態となりオン状態となる。

【0006】

また、スイッチング素子をオフさせるときはゲート駆動回路の出力電圧を0Vまたは−15V程度の電圧とすることにより、ゲート・ソース間(またはゲート・エミッタ間)の電圧を閾値以下にする。

【0007】

MOSFETおよびIGBTのゲート電極は酸化膜で覆われる構造となっており、ゲート電極とソース電極(またはエミッタ電極)の間にゲート・ソース間キャパシタンス(またはゲート・エミッタ間キャパシタンス)および、ゲート電極とドレイン電極(またはコレクタ電極)間のゲート・ドレイン間キャパシタンス(またはゲート・コレクタ間キャパシタンス)が形成される。

【0008】

したがって、スイッチング素子のゲート側の等価回路はゲート・ソース間キャパシタンス(またはゲート・エミッタ間キャパシタンス)とゲート・ドレイン間キャパシタス(またはゲート・コレクタ間キャパシタンス)の並列接続となる。

【0009】

通常、ゲート駆動回路とスイッチング素子のゲート電極間にゲート抵抗が接続される。したがって、スイッチング素子をオンさせるためにゲート駆動回路から+15V程度の電圧を印加するとゲート抵抗を介してゲート・ソース間キャパシタンス(またはゲート・エミッタ間キャパシタンス)とゲート・ドレイン間キャパシタス(またはゲート・コレクタ間キャパシタンス)を充電することになる。

【0010】

標準的なハードスイッチング回路ではゲート回路の値を変化させることにより、上記キャパシタンスの充電時間を変化させ、スイッチング素子のスイッチング時間を調整する。

【0011】

スイッチング損失はスイッチング時間を短くすることにより小さくできるので、スイッチング素子の低損失化のため、ゲート抵抗の値を小さくし、スイッチング時間を短縮させる方法がとられている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2009−290287号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

図1に示すインバータ回路では、スイッチング素子をハイサイドとローサイドに設置して上下アームを構成し、ハイサイドスイッチング素子がオン状態のとき、ローサイドスイッチング素子はオフ状態、また、ハイサイドスイッチング素子がオフ状態のとき、ローサイドスイッチング素子はオン状態となるように、どちらか一方がオンのときはもう片方はオフ状態になるように制御される。また、両方のスイッチング素子が同時にオンすると上下アームにスイッチング素子の定格電流以上の短絡電流が流れてしまい、スイッチング素子が破壊してしまう可能性がある。したがって、同時にオン状態にならないように、両方の素子が同時にオフ状態になる期間(デッドタイム)をもうける。

【0014】

ここで、図2に示すように、一方のスイッチング素子がオフ状態からオン状態になるともう片方のスイッチング素子のドレイン・ソース間(またはコレクタ・エミッタ間)電圧は、0Vから入力直流電圧に自動的に変化する。それにともない、ゲート・ドレイン間(またはゲート・コレクタ間)キャパシタンスがほぼ入力直流電圧と同じ値まで充電される。

【0015】

このとき、ゲート・ドレイン間(またはゲート・コレクタ間)キャパシタンスに変位電流が流れ、この電流がゲート・ソース間(またはゲート・エミッタ間)キャパシタンスを充電し、ゲート電圧が閾値をこえてしまい、スイッチング素子がオンしてしまうことがある。

【0016】

変位電流のピーク値はスイッチング素子のドレイン・ソース間(またはコレクタ・エミッタ間)電圧の時間変化の割合(dV/dt)に比例するので、スイッチング素子のスイッチング損失を小さくするためにスイッチング時間を短くすると変位電流のピーク値が大きくなり、先に説明した原理でスイッチング素子がオンしやすくなる。

【0017】

そこで、ゲート・ソース間(またはゲート・エミッタ間)を半導体スイッチング素子で短絡することにより、ゲート電圧が閾値をこえないようにするゲート駆動回路が検討されている。

【0018】

しかしながら、このような回路では、通常必要なゲート駆動回路を構成する部品の他に、ダイオードを2個、抵抗を1個、スイッチング素子を1個などの素子を少なくとも追加する必要がある。また、上記スイッチング素子は通常のゲート駆動回路の制御信号に同期して動作させる必要があり、同期信号を発生させるための制御装置が必要になることと、それらの回路全体の設計が複雑になる。

【0019】

本発明の実施の形態はこのような課題を解決するためのものであり、スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を、部品点数の少ない簡易な回路構成で実現することを目的とする。

【課題を解決するための手段】

【0020】

上記目的を達成するための第1の実施の形態であるゲート駆動回路は、ローサイドゲート駆動回路の出力端子にトランスの1次側を接続し、ハイサイドスイッチング素子のゲート・ソース間にトランスの1次側電圧と反対の極性の電圧が発生するようにトランスの2次側を接続する。これによって、ローサイドゲート駆動回路から正極性のゲート駆動電圧が出力されるとトランスを介してハイサイドスイッチング素子のゲート・ソース間に負極性の電圧パルスが印加され、ゲート・ソース間電圧は閾値以下の電圧となり、ローサイドスイッチング素子がターンオンするときに、ハイサイドスイッチング素子がオフ状態を保持するようにしたものである。

【0021】

上記目的を達成するための第2の実施の形態であるゲート駆動回路は、スイッチング素子のゲート・ソース間にNchノーマリーオン型スイッチング素子のドレイン・ソースを接続し、トランスの1次側をゲート駆動回路の出力に接続する。また、ゲート駆動回路から正極性のゲート駆動電圧が出力されるとNchノーマリーオン型スイッチング素子のゲート・ソース間に負極性の電圧パルスが印加されるようにトランスの2次側をNchノーマリーオン型スイッチング素子のゲート・ソース間に接続する。そして、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される。ローサイドゲート駆動回路から正極性の電圧が出力され、ローサイドスイッチング素子がターンオンしたときに、ハイサイドのNchノーマリーオン型スイッチング素子のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりハイサイドスイッチング素子のゲート・ソース間が短絡され、ハイサイドスイッチング素子がオフ状態を保持するようにしたものである。一方、ハイサイドゲート駆動回路から正極性の電圧が出力され、ハイサイドスイッチング素子がターンオンしたときに、ローサイドのNchノーマリーオン型スイッチング素子のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりローサイドスイッチング素子のゲート・ソース間が短絡され、ローサイドスイッチング素子がオフ状態を保持するようにしたものである。

【0022】

上記目的を達成するための第3の実施の形態であるゲート駆動回路は、スイッチング素子のゲート・ソース間にPchノーマリーオン型スイッチング素子のドレイン・ソースを接続する。また、前記Pchノーマリーオン型スイッチング素子のゲート駆動回路は前記スイッチング素子のゲート駆動回路と共通とする。ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される。ローサイドゲート駆動回路から正極性の電圧が出力され、ローサイドスイッチング素子がターンオンしたときに、ハイサイドPchノーマリーオン型スイッチング素子はオン状態となりハイサイドスイッチング素子のゲート・ソース間が短絡され、ハイサイドスイッチング素子がオフ状態を保持するようにしたものである。一方、ハイサイドスイッチング素子がターンオンしたときに、ローサイドPchノーマリーオン型スイッチング素子はオン状態となりローサイドスイッチング素子のゲート・ソース間が短絡され、ローサイドスイッチング素子がオフ状態を保持するようにしたものである。

【図面の簡単な説明】

【0023】

【図1】従来のインバータ回路の1レグ分を示す等価回路図である。

【図2】従来のインバータ回路におけるスイッチング素子のゲート・ソース間に発生するゲート電圧波形図である。

【図3】実施例1のゲート駆動回路の等価回路図である。

【図4】実施例1のシミュレーション波形図である。

【図5】実施例2のゲート駆動回路の等価回路図である。

【図6】実施例3のゲート駆動回路の等価回路図である。

【発明を実施するための形態】

【0024】

以下,本発明の実施形態について図面を用いて説明する。

【0025】

[第1の実施の形態]

まず、第1の実施の形態に係わるゲート駆動回路について説明する。

図3は、本発明の実施の形態に係わるゲート駆動回路の等価回路である。ローサイドゲート駆動回路2の出力端子にトランス15の1次側を接続し、ハイサイドスイッチング素子5のゲート・ソース間にトランスの1次側電圧と反対の極性の電圧が発生するようにトランス15の2次側が接続される。

【0026】

ローサイドゲート駆動回路2から正極性のゲート駆動電圧が出力されるとトランス15を介してハイサイドスイッチング素子5のゲート・ソース間に負極性の電圧パルスが印加され、ゲート・ソース間電圧は閾値以下の電圧となり、ローサイドスイッチング素子6がターンオンするときに、ハイサイドスイッチング素子5がオフ状態を保持する。

【0027】

図4は、実施例1のゲート駆動回路の回路シミュレーション結果である。ローサイドゲート・エミッタ電圧が0Vから+15Vの電圧に変化する期間において、ハイサイドゲート・エミッタ電圧には負極性のパルス電圧が印加されていることが確認できる。また、ハイサイドコレクタ電流も流れていないことから、ハイサイドスイッチング素子はオフ状態を維持していることが確認できる。

【0028】

この実施の形態によれば、ターンオンする側のスイッチング素子の各種電圧・電流の状態を検出して、その状態をゲート駆動側へフィードバックするための外部制御回路を追加することなく、自動的に、ターンオンしない側のスイッチング素子のオフ状態を保持できる点で好ましい効果が得られる。

【0029】

かかる第1の実施の形態におけるトランスとしては、空芯トランスを用いることが好ましい。これは、磁性体コアを有するトランスでは、ヒステリシス損失が発生し、損失低下に寄与しないからである。また空芯トランスを使用すると、比較的コスト面で有利である。

【0030】

また、この実施の形態で、ゲート駆動回路は、スイッチング素子がオフ状態は0V、オン状態は正極性の電圧を出力するものであることが好ましい。

その理由は、以下の通りである。すなわち、本実施の形態で解決しようとする課題は、変位電流によりゲート・ソース間キャパシタンスが充電され、ゲート・ソース間で電圧が閾値を越えてしまい誤動作するおそれがあることを解消するものである。この現象を防止する簡単な方法として、スイッチング素子がオフ状態の時に、ゲート・ソース間にマイナスバイアス(負極性の電圧を印加する)ことにより、充電電圧が閾値を越えないようにする方法がある。この場合、負極性の電源が別に必要なため、ゲート回路のコストが上昇するという欠点がある。本実施の形態によれば、負極性の電源が不要となるので、電力変換装置のコストを下げることが可能になる。

【0031】

[第2の実施の形態]

図5は、第2の実施の形態に係わるゲート駆動回路の等価回路である。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をハイサイドゲート駆動回路1の出力に接続し、ハイサイドゲート駆動回路1から正極性のゲート駆動電圧が出力されるとNchノーマリーオン型スイッチング素子13のゲート・ソース間に負極性の電圧パルスが印加されるようにトランス15の2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続する。なお、ローサイドもハイサイドと同様な構成・動作原理であるので、説明は省略する。

【0032】

ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるようにハイサイドゲート駆動回路1とローサイドゲート駆動回路2が制御する。

【0033】

ローサイドゲート駆動回路2から正極性の電圧が出力され、ローサイドスイッチング素子6がターンオンしたときに、Nchノーマリーオン型スイッチング素子13のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりハイサイドスイッチング素子5のゲート・ソース間が短絡され、ハイサイドスイッチング素子5がオフ状態を維持する。

【0034】

この実施の形態によれば、特にターンオンする側のスイッチング素子の各種電圧・電流の状態を検出して、その状態をゲート駆動側へフィードバックするための外部制御回路を追加することなく、自動的に、ターンオンしない側のスイッチング素子のオフ状態を保持できる点で好ましい効果が得られる。また、ローサイドスイッチング素子6のターンオン動作終了後もハイサイドスイッチング素子5のゲート・ソース間は短絡された状態であるので、外部から何らかのノイズが侵入した場合でもハイサイドスイッチング素子5はオフ状態を保持できる点で好ましい効果が得られる。

【0035】

かかる第1の実施の形態におけるトランスとしては、空芯トランスを用いることが好ましい。これは、磁性体コアを有するトランスでは、ヒステリシス損失が発生し、損失低下に寄与しないからである。

【0036】

また、この実施の形態においても、前述の第1の実施形態と同様にゲート駆動回路は、スイッチング素子がオフ状態は0V、オン状態は正極性の電圧を出力するものであることが好ましい。

【0037】

[第3の実施の形態]

図6は、本発明の第3の実施の形態に係わるゲート駆動回路の等価回路である。ハイサイドスイッチング素子5のゲート・ソース間にPchノーマリーオン型スイッチング素子14のドレイン・ソースを接続し、ハイサイドゲート駆動回路1で前記Pchノーマリーオン型スイッチング素子14のゲートを駆動する。なお、ローサイドもハイサイドと同様な構成・動作原理であるので、説明は省略する。

【0038】

ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるようにハイサイドゲート駆動回路1とローサイドゲート駆動回路2を制御する。

【0039】

ローサイドゲート駆動回路2から正極性の電圧が出力され、ローサイドスイッチンググ素子6がターンオンしたときに、Pchノーマリーオン型スイッチング素子14のゲート・ソース間電圧は0Vまたは正極性となりオン状態となりハイサイドスイッチング素子5のゲート・ソース間が短絡され、ハイサイドスイッチング素子5がオフ状態を維持する。

【0040】

この実施の形態によれば、特にターンオンする側のスイッチング素子の各種電圧・電流の状態を検出して、その状態をゲート駆動側へフィードバックするための外部制御回路を追加することなく、自動的に、ターンオンしない側のスイッチング素子のオフ状態を保持できる点で好ましい効果が得られる。また、ローサイドスイッチング素子6のターンオン動作終了後もハイサイドスイッチング素子5のゲート・ソース間は短絡された状態であるので、外部から何らかのノイズが侵入した場合でもハイサイドスイッチング素子5はオフ状態を保持できる点で好ましい効果が得られる。

【0041】

かかる第1の実施の形態におけるトランスとしては、空芯トランスを用いることが好ましい。これは、磁性体コアを有するトランスでは、ヒステリシス損失が発生し、損失低下に寄与しないからである。

【0042】

また、この実施の形態においても、前述の第1の実施形態と同様にゲート駆動回路は、スイッチング素子がオフ状態は0V、オン状態は正極性の電圧を出力するものであることが好ましい。

【0043】

以上、3つの実施の形態について説明したが、これらの構成によれば、スイッチング素子のゲート・ソース間(またはゲート・エミッタ間)電圧を閾値以下に保持するための回路を付加したゲート駆動回路を部品点数の少ない簡易な回路構成で実現することができる。

【0044】

[半導体素子チップ、モジュール、パッケージ]

上記各実施の形態においては、この発明の実施の形態として駆動回路として説明したが、この実施の形態の駆動回路は、パルス出力の遅延、波形の鈍り、配線抵抗の増加などを防止するために、可能な限り配線長さが短い方が好ましい。同一の半導体チップ上に形成できる素子は、集合させて同一ICチップ上に形成することが好ましい。また、パッケージとしても同一パッケージに封入しモジュールとすることが好ましい。

【0045】

より具体的には、上述のゲート駆動回路において、トランスを、ローサイドゲート駆動回路、ハイサイドゲート駆動回路、Nch型ノーマリーオン型スイッチング素子、あるいはPchノーマリーオン型スイッチング素子と同一のパッケージに封入してゲート駆動ICとすることができる。また、Nch型ノーマリーオン型スイッチング素子、Pch型ノーマリーオン型スイッチング素子をメインスイッチング素子と同一の半導体チップに集積化してスイッチング素子とすることができる。

【0046】

さらに、ハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入してパワー半導体モジュールとすることができる。

あるいは、ハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、Nchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入してパワー半導体モジュールとすることができる。

また、ハイサイドゲート駆動回路、ローサイドゲート駆動回路、Pchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入してパワー半導体モジュールとすることができる。

【0047】

上記モジュール化、同一パッケージ化によって、以下の効果が期待される。すなわち、(1)回路技術者にとっては、空芯トランスの接続作業が不要化される。(2)各種パワー半導体(スイッチング素子)のパラメータに合わせて最適なパラメータの空芯トランスを組み合わせることにより、回路技術者は特性が最適化されたパワー半導体モジュールなどの部品を採用することができる。(3)パワー半導体チップと空芯トランスの特性が向上する。

【0048】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0049】

1…ハイサイドゲート駆動回路

2…ローサイドゲート駆動回路

3、4、14…抵抗

5…ハイサイドスイッチング素子

6…ローサイドスイッチング素子

7、8…ダイオード

9、10、11、12…キャパシタ

13…Nchノーマリーオン型スイッチング素子

14…Pchノーマリーオン型スイッチング素子

15…トランス

【特許請求の範囲】

【請求項1】

2つのスイッチング素子を直列に接続し、接続点よりも高電位側をハイサイドスイッチング素子、低電位側をローサイドスイッチング素子として、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される電力変換回路において、ローサイドゲート駆動回路の出力端子にトランスの1次側を接続し、ハイサイドスイッチング素子のゲート・ソース間にトランスの1次側電圧と反対の極性の電圧が発生するようにトランスの2次側を接続することを特徴とするゲート駆動回路。

【請求項2】

2つのスイッチング素子を直列に接続し、接続点よりも高電位側をハイサイドスイッチング素子、低電位側をローサイドスイッチング素子として、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される電力変換回路において、ハイサイドおよび、ローサイドスイッチング素子のゲート・ソース間にNchノーマリーオン型補助スイッチング素子のドレイン・ソースを接続し、トランスの1次側をゲート駆動回路の出力に接続し、ゲート駆動回路から正極性のゲート駆動電圧が出力されるとNchノーマリーオン型スイッチング素子のゲート・ソース間に負極性の電圧パルスが印加されるようにトランスの2次側をNchノーマリーオン型スイッチング素子のゲート・ソース間に接続することを特徴とするゲート駆動回路。

【請求項3】

2つのスイッチング素子を直列に接続し、接続点よりも高電位側をハイサイドスイッチング素子、低電位側をローサイドスイッチング素子として、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される電力変換回路において、ハイサイドおよび、ローサイドスイッチング素子のゲート・ソース間にPchノーマリーオン型補助スイッチング素子のドレイン・ソースを接続し、ローサイドまたはハイサイドのどちらか一方のゲート駆動回路から正極性の電圧が出力されてメインのスイッチング素子がターンオンしたときに、もう一方のメインのスイッチング素子に接続されているPchノーマリーオン型補助スイッチング素子がオン状態となりメインのスイッチング素子のゲート・ソース間が短絡され、メインのスイッチング素子がオフ状態を保持することを特徴としたゲート駆動回路。

【請求項4】

前記トランスは空芯トランスであることを特徴とする請求項1ないし3のいずれかに記載のゲート駆動回路。

【請求項5】

ゲート駆動回路は0Vと正極性の電圧を出力することを特徴とする請求項1ないし3のいずれかに記載のゲート駆動回路。

【請求項6】

請求項1に記載のゲート駆動回路におけるハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入したことを特徴とするパワー半導体モジュール。

【請求項7】

請求項2に記載のゲート駆動回路におけるハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、Nchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入したことを特徴とするパワー半導体モジュール。

【請求項8】

請求項3に記載のゲート駆動回路におけるハイサイドゲート駆動回路、ローサイドゲート駆動回路、Pchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入したことを特徴とするパワー半導体モジュール。

【請求項1】

2つのスイッチング素子を直列に接続し、接続点よりも高電位側をハイサイドスイッチング素子、低電位側をローサイドスイッチング素子として、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される電力変換回路において、ローサイドゲート駆動回路の出力端子にトランスの1次側を接続し、ハイサイドスイッチング素子のゲート・ソース間にトランスの1次側電圧と反対の極性の電圧が発生するようにトランスの2次側を接続することを特徴とするゲート駆動回路。

【請求項2】

2つのスイッチング素子を直列に接続し、接続点よりも高電位側をハイサイドスイッチング素子、低電位側をローサイドスイッチング素子として、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される電力変換回路において、ハイサイドおよび、ローサイドスイッチング素子のゲート・ソース間にNchノーマリーオン型補助スイッチング素子のドレイン・ソースを接続し、トランスの1次側をゲート駆動回路の出力に接続し、ゲート駆動回路から正極性のゲート駆動電圧が出力されるとNchノーマリーオン型スイッチング素子のゲート・ソース間に負極性の電圧パルスが印加されるようにトランスの2次側をNchノーマリーオン型スイッチング素子のゲート・ソース間に接続することを特徴とするゲート駆動回路。

【請求項3】

2つのスイッチング素子を直列に接続し、接続点よりも高電位側をハイサイドスイッチング素子、低電位側をローサイドスイッチング素子として、ローサイドゲート駆動回路から正極性の電圧が出力されるとハイサイドゲート駆動回路は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路から正極性の電圧が出力されるようにハイサイドとローサイドゲート駆動回路が制御される電力変換回路において、ハイサイドおよび、ローサイドスイッチング素子のゲート・ソース間にPchノーマリーオン型補助スイッチング素子のドレイン・ソースを接続し、ローサイドまたはハイサイドのどちらか一方のゲート駆動回路から正極性の電圧が出力されてメインのスイッチング素子がターンオンしたときに、もう一方のメインのスイッチング素子に接続されているPchノーマリーオン型補助スイッチング素子がオン状態となりメインのスイッチング素子のゲート・ソース間が短絡され、メインのスイッチング素子がオフ状態を保持することを特徴としたゲート駆動回路。

【請求項4】

前記トランスは空芯トランスであることを特徴とする請求項1ないし3のいずれかに記載のゲート駆動回路。

【請求項5】

ゲート駆動回路は0Vと正極性の電圧を出力することを特徴とする請求項1ないし3のいずれかに記載のゲート駆動回路。

【請求項6】

請求項1に記載のゲート駆動回路におけるハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入したことを特徴とするパワー半導体モジュール。

【請求項7】

請求項2に記載のゲート駆動回路におけるハイサイドゲート駆動回路、ローサイドゲート駆動回路、トランス、Nchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入したことを特徴とするパワー半導体モジュール。

【請求項8】

請求項3に記載のゲート駆動回路におけるハイサイドゲート駆動回路、ローサイドゲート駆動回路、Pchノーマリーオン型スイッチング素子、ハイサイドメインスイッチング素子、ローサイドメインスイッチング素子を同一のパッケージに封入したことを特徴とするパワー半導体モジュール。

【図1】

【図3】

【図5】

【図6】

【図2】

【図4】

【図3】

【図5】

【図6】

【図2】

【図4】

【公開番号】特開2012−191408(P2012−191408A)

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願番号】特願2011−52784(P2011−52784)

【出願日】平成23年3月10日(2011.3.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願日】平成23年3月10日(2011.3.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]