ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ゲート駆動回路に関し、特に電力変換装置のスイッチング素子として機能するトランジスタのゲートを駆動するゲート駆動回路、これを備える電力変換装置、及びゲート駆動方法に関する。

【背景技術】

【0002】

従来の電力制御回路では、電力変換を制御するスイッチング素子として、パワーMOSFET(Metal−Oxide−Semiconductor Field−Effect Transistor)又は絶縁ゲートバイポーラトランジスタ(IGBT:Insulated Gate Bipolar Transistor)が用いられている。一方、近年スイッチング速度が高速なことから窒化ガリウム(GaN)を用いたパワーMOSFET(以下、GaNトランジスタと称す)が注目されている。GaNトランジスタは、閾値電圧Vthの大きさに応じてノーマリオン型とノーマリオフ型の2種類がある。詳細には、ノーマリオン型トランジスタの閾値電圧Vthは0より低く、ゲート電圧とソース電圧が同電位の場合にオン状態となる。ノーマリオフ型トランジスタの閾値電圧Vthは0より高く、ゲート電圧とソース電圧が同電位の場合にオフ状態になる。

【0003】

GaNの場合、ノーマリオン型トランジスタは、ノーマリオフ型トランジスタに比べてスイッチング性能に優れる。例えば、ノーマリオン型トランジスタは、ノーマリオフ型トランジスタよりも少ないゲート容量であるとともにオン抵抗を低くすることができ、高速スイッチング動作を実現できる。ただし、ノーマリオン型トランジスタをオフ状態にするためには、ゲートに接地電位(0V)よりも低い負電圧を供給する必要がある。このため、ノーマリオン型トランジスタを駆動する場合、チャージポンプなどを用いて負電圧を生成する回路(以下、負電圧源と称す)を用意する必要がある。

【0004】

ノーマリオン型トランジスタをスイッチング素子として利用した半導体装置の一例が、特開2011−101217に記載されている(特許文献1参照)。特許文献1には、負電圧源に応じてノーマリオン型GaNトランジスタのゲートを駆動するハイサイド駆動部を備える半導体装置が記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−101217

【発明の概要】

【発明が解決しようとする課題】

【0006】

ノーマリオン型トランジスタはスイッチング性能に優れるが、ゲートに供給される負電圧が不安定な場合、オン状態となることがある。

【0007】

図1は、発明者によって想定された電力変換回路の構成を示す図である。ここで発明者は、ハイサイドトランジスタ及びローサイドトランジスタとしてノーマリオン型のN型パワートランジスタを利用することを想定した。図1に示す電力変換回路は、ゲート駆動回路101、102、ハーフブリッジ回路のスイッチング素子として機能するハイサイドトランジスタ201及びローサイドトランジスタ202、負電圧源301、302を具備する。

【0008】

ゲート駆動回路101は、入力信号501(PWM信号:Pulse Width Modulation)の反転信号を反転した出力信号によりハイサイドトランジスタ201のゲートを駆動する。ゲート駆動回路101は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源301から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備え、例えばCMOS(Complementary Metal Oxide Semiconductor)インバータが好適である。ゲート駆動回路102は、入力信号502(PWM信号)の反転信号を反転した出力信号によりローサイドトランジスタ202のゲートを駆動する。ゲート駆動回路102は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備え、例えばCMOSインバータが好適である。

【0009】

ハイサイドトランジスタ201のドレインには、図示しない電源から第3電源電圧VHが供給され、ソースは出力端子を介してローサイドトランジスタ202のドレインに接続される。ローサイドトランジスタ202のソースは接地され、ドレインは出力端子を介してハイサイドトランジスタ201のソースに接続される。出力端子は、負荷500に接続される。

【0010】

以上のような構成から、ハイサイドトランジスタ201及びローサイドトランジスタ202は、ゲートに供給される電圧に応じたスイッチング動作により、第3電源電圧VHと接地電圧GNDに応じた出力を負荷500に出力する。

【0011】

図1に示す電力変換回路では、ノーマリオン型のハイサイドトランジスタ201を駆動するため、負電圧源301からゲート駆動回路101に対し接地電位よりも低い負電圧(第2電源電圧VNEG)が供給される。同様にノーマリオン型のローサイドトランジスタ202を駆動するため、負電圧源302からゲート駆動回路102に対し負電圧(第2電源電圧VNEG)が供給される。例えば、第2電源電圧VNEGは、負電圧源301、302において、第1電源電圧VDDに応じて生成されるため、第1電源電圧VDDが不安定な期間中、第2電源電圧VNEGも不安定な値を示す。例えば、電源を投入した直後や、制御回路の電源を遮断したとき等、第2電源電圧VNEGは安定して生成されない。

【0012】

図2は、図1に示す電力変換回路における電源投入時の第1電源電圧VDD、第2電源電圧VNEG、及びスイッチング素子(ハイサイドトランジスタ201及びローサイドトランジスタ202)に流れる貫通電流Iの関係を示すタイミングチャートである。図2を参照して、時刻T1に電源が投入されてから時刻T2までの間、第1電源電圧VDDは不安定な値を示しながら所定の値となるまで上昇する。この間、負電圧源301、302は、第1電源電圧VDDが所定のレベルに達していないため動作せず、第2電源電圧VNEGは0Vを示す。このため、ノーマリオン型のハイサイドトランジスタ201、ローサイドトランジスタ202はともにオン状態となる。時刻T1から時刻T2までの間、ハイサイドトランジスタ201に供給される第3電源電圧VHは、第1電源電圧VDDの上昇に伴い増加するため、第3電源電圧VHによる貫通電流Iが、ハイサイドトランジスタ201及びローサイドトランジスタ202を介して流れ始める。

【0013】

時刻T2において、第1電源電圧VDDが所定の値に安定すると、負電圧源301、302は動作を開始し、第2電源電圧VNEG(負電圧)は低下し始める。しかし、第2電源電圧VNEGが、所定の値に安定する時刻T3までの間、ノーマリオン型のハイサイドトランジスタ201及びローサイドトランジスタ202がともにオン状態となる場合がある。この場合、第3電源電圧VHによる貫通電流Iが、ハイサイドトランジスタ201及びローサイドトランジスタ202を介して流れてしまう。

【0014】

以上のように、図1に示す電力変換回路において、第2電源電圧VNEG(負電圧)が十分に生成されていないタイミングでは、ハイサイドトランジスタ201とローサイドトランジスタ202の両方がオン状態になってしまい、大きな貫通電流が流れる場合がある。この貫通電流によって、電力変換回路の出力電圧Voutは不定になるため、負荷500が破壊される恐れがある。又、N型パワートランジスタ201、202も巨大な貫通電流による発熱で破壊する恐れがある。

【課題を解決するための手段】

【0015】

上記の課題を解決するために、本発明は、以下に述べられる手段を採用する。その手段を構成する技術的事項の記述には、[特許請求の範囲]の記載と[発明を実施するための形態]の記載との対応関係を明らかにするために、[発明を実施するための形態]で使用される番号・符号が付加されている。ただし、付加された番号・符号は、[特許請求の範囲]に記載されている発明の技術的範囲を限定的に解釈するために用いてはならない。

【0016】

本発明によるゲート駆動回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ(21)及びローサイドトランジスタ(22)のゲートを相補に駆動する2つの駆動回路(11、12)と制御回路(40)とを具備する。ハイサイドトランジスタ(21)とローサイドトランジスタ(22)の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路(11、12)の少なくとも一方は、低電位側の電源電圧として供給される第2電源電圧(VNEG)に応じた駆動電圧を、ノーマリオン型のトランジスタのゲートに出力する。ここで第2電源電圧(VNEG)は接地電圧(GND)よりも低い。制御回路(40)は、第2電源電圧(VNEG)が予め設定された目標電圧よりも高い場合、ハイサイドトランジスタ(21)に流れるドレイン電流を遮断する。

【0017】

他の観点において、本発明によるゲート駆動方法は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ(21)及びローサイドトランジスタ(22)のゲートを相補に駆動する2つの駆動回路を具備するゲート駆動回路(11、12)のゲート駆動方法である。本発明によるゲート駆動方法は、2つの駆動回路(11、12)の少なくとも一方に対する低電位側の電源電圧として供給される、接地電位(GND)より低い電源電圧(VNEG)が目標電圧よりも高い場合、ハイサイドトランジスタ(21)に流れるドレイン電流を遮断するステップとを具備する。

【発明の効果】

【0018】

本発明によれば、電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制することができる。

【図面の簡単な説明】

【0019】

【図1】図1は、発明者が想定した電力変換回路の構成を示す図である。

【図2】図2は、図1に示す電力変換回路における電源投入時の電源電圧、負電圧、及びスイッチング素子に流れる貫通電流の関係を示すタイミングチャートである。

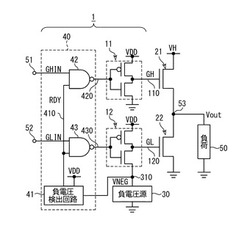

【図3】図3は、本発明によるゲート駆動回路の第1の実施の形態における構成を示す図である。

【図4A】図4Aは、本発明に係る負電圧源の構成の一例を示す図である。

【図4B】図4Bは、本発明に係る負電圧源の構成の一例を示す図である。

【図4C】図4Cは、本発明に係る負電圧源の構成の一例を示す図である。

【図5】図5は、本発明に係る負電圧源に利用されるダイオードの構造の一例を示す図である。

【図6】図6は、本発明に係る負電圧検出回路の構成の一例を示す図である。

【図7】図7は、本発明によるゲート駆動回路の第1の実施の形態における動作を示すタイミングチャートである。

【図8】図8は、第1の実施の形態におけるゲート駆動回路を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。

【図9】図9は、図8に示すマルチフェーズスイッチング電源に搭載されるフェーズICの構成の一例を示す図である。

【図10】図10は、第1の実施の形態におけるゲート駆動回路を利用した3相インバータの構成の一例を示す図である。

【図11】図11は、図10に示す3相インバータに搭載されるフェーズICの構成の一例を示す図である。

【図12】図12は、本発明によるゲート駆動回路の第2の実施の形態における構成を示す図である。

【図13】図13は、本発明によるゲート駆動回路の第2の実施の形態における動作を示すタイミングチャートである。

【図14】図14は、第2の実施の形態におけるゲート駆動回路を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。

【図15】図15は、図13に示すマルチフェーズスイッチング電源に搭載されるフェーズICの構成の一例を示す図である。

【図16】図16は、第2の実施の形態におけるゲート駆動回路を利用した3相インバータの構成の一例を示す図である。

【図17】図17は、第1の実施の形態における電力変換回路を搭載したSiPの構造の一例を示す図である。

【図18】図18は、本発明によるゲート駆動回路を適用したインバータの構成の一例を示す図である。

【発明を実施するための形態】

【0020】

以下、添付図面を参照しながら本発明の実施の形態を説明する。図面において同一、又は類似の参照符号は、同一、類似、又は等価な構成要素を示している。

【0021】

1.第1の実施の形態

図3から図11を参照して、第1の実施の形態におけるゲート駆動回路1を説明する。第1の実施の形態におけるゲート駆動回路1は、ノーマリオン型のローサイドトランジスタを駆動するための負電圧に応じて、ハイサイドトランジスタのゲート電圧を制御する。ゲート駆動回路1は、負電圧が所定の電圧に達するまで、ハイサイドトランジスタをオフ状態とすることでハイサイドトランジスタのドレイン電流を遮断する。これにより、負電圧が不安定な期間において、ハーフブリッジ回路を構成するスイッチング素子(ハイサイドトランジスタ及びローサイドトランジスタ)への貫通電流を抑制する。

(構成)

以下、図3から図6を参照して、第1の実施の形態におけるゲート駆動回路1の構成の詳細を説明する。図3は、本発明による電力変換回路の第1の実施の形態における構成を示す図である。図3を参照して、第1の実施の形態における電力変換回路は、ゲート駆動回路1と、ハーフブリッジ回路のスイッチング素子として機能し、負荷50に接続されるハイサイドトランジスタ21及びローサイドトランジスタ22を具備する。第1の実施の形態におけるゲート駆動回路1は、駆動回路11、12、負電圧源30、制御回路40を具備し、ハイサイドトランジスタ21及びローサイドトランジスタ22を駆動する。図3に示す一例では、負電圧(第2電源電圧VNEG)が目標電圧よりも高く、不安定な期間中、ゲート電圧を制御することにより強制的にオフ状態に制御可能であることから、ハイサイドトランジスタ21としてノーマリオフ型のNチャネル型GaNトランジスタが好適に利用される。又、スイッチング性能の観点からローサイドトランジスタ22としてノーマリオン型のNチャネル型GaNトランジスタが好適に利用される。

【0022】

ハイサイドトランジスタ21のドレインには、図示しない電源から第3電源電圧VHが供給され、ソースは出力ノード53を介してローサイドトランジスタ22のドレインに接続される。ローサイドトランジスタ22のソースは接地され、ドレインは出力ノード53を介してハイサイドトランジスタ21のソースに接続される。出力ノード53は、負荷50に接続される。

【0023】

駆動回路11は、制御回路40から入力ノード420に出力された信号に応じて、ハイサイドトランジスタ21のゲートを駆動する。駆動回路11の入力ノードは制御回路40に接続され、出力ノード110は、ハイサイドトランジスタ21のゲートに接続される。駆動回路11は、図示しない電源から供給される第1電源電圧VDDを高位側の電源電圧とし、接地電圧を低位側の電源電圧として動作するトーテムポール回路を備える。図3に示す一例では、駆動回路11はCMOS(Complementary Metal Oxide Semiconductor)インバータであり、入力される信号の反転信号を、ゲート駆動信号GHとしてハイサイドトランジスタ21のゲートに出力する。駆動回路12は、制御回路40から入力ノード420に出力された信号に応じて、ローサイドトランジスタ22のゲートを駆動する。駆動回路11の入力ノードは、制御回路40に接続され、出力ノード120は、ローサイドトランジスタ22のゲートに接続される。駆動回路12は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源30から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備える。図3に示す一例では、駆動回路12はCMOSインバータであり、入力される信号の反転信号を、ゲート駆動信号GLとしてローサイドトランジスタ22のゲートに出力する。尚、駆動回路12に供給される高電位側の電源電圧は第1電源電圧VDDに限らず、ノーマリオン型トランジスタをオン状態とできる電圧であれば任意に設定できる。

【0024】

負電圧源30は、接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)を生成する。図4A〜図4Dのそれぞれは、負電圧源30の構成の一例を示す図である。負電圧源30は、例えば、図4Aに示す降圧型チャージポンプによって構成される。図4Aに示す負電圧源には、クロックパルス信号φ1が入力される。図4Aを参照して、ハイレベルのクロックパルス信号φ1により、容量Cin及びダイオードD10を介してGNDに電流が流れ、容量Cinに電荷がチャージされる。続くローレベルのクロックパルス信号φ1により、GNDから容量Cout、ダイオードD20、容量Cinを介して入力側に電流が流れ、容量Cinにチャージされた電荷が容量Cinにチャージされる。これにより、容量CoutとダイオードD20との接続ノード(出力ノード310)の電圧が接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)となる。

【0025】

負電圧源30は、図4Bに示すディクソン型チャージポンプによっても実現できる。図4Bに示す負電圧源30には、相互に相補のクロックパルス信号φ10、φ20が入力される。クロックパルス信号φ10がローレベル、クロックパルス信号φ20がハイレベルの期間、ダイオードD2、D4が導通状態となり、ダイオードD1、D3が遮断状態となる(1)。これにより容量C1、C3に電荷がチャージされる。クロックパルス信号φ10がハイレベル、クロックパルスφ20がローレベルの期間、ダイオードD1、D3が導通状態となり、ダイオードD2、D4が遮断状態となる(2)。これにより、容量C2、C4に電荷がチャージされる。この際、容量C1、C3にチャージされた電荷が容量C2、C4にチャージされる。上記(1)、(2)を繰り返すことにより、容量Coutには、容量C4にチャージされた電荷がチャージされ、容量CoutとダイオードD5との接続ノード(出力ノード310)の電圧が、接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)となる。

【0026】

負電圧源30は、図4Cに示す降圧型チョッパ回路によっても実現できる。図4Cを参照して、負電圧源30に入力されるクロックパルス信号φ2に応じてスイッチS1がオンすると、第1電源(第1電源電圧VDD)からチョークコイルLを介して接地端子(GND)側へ電流が流れ、チョークコイルLにエネルギーが蓄えられる。続いてクロックパルス信号φ2に応じてスイッチS1がオフ状態となると、チョークコイルLに蓄えられたエネルギーにより出力ノード310から接地端子(GND)側に電流が流れ、出力ノード310は接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)に降圧する。

【0027】

図5は、本発明に係る負電圧源30に利用されるダイオードの構造の一例を示す図である。上述のように負電圧(第2電源電圧VNEG)を生成するためには、ダイオードが重要な構成部品となる。ダイオードを集積回路上で実現することが求められる。しかし、通常の基板では、P−sub基板がGNDに接続されているため、接地電圧GNDよりも低い電位のN−wellまたはN+拡散層をP−sub基板上に作ることができない。例えば、順方向のPN接合により、接地電圧GNDよりも低い電位のN−well又はN+拡散層には接地電圧GNDが供給される。このため、本発明では、ダブルウェル、トリプルウェル、ディープNウェル、SOI基板の何れかを使用可能なプロセスを利用することで、負電圧源30で用いられるダイオードを集積回路上で実現することが好ましい。

【0028】

例えば、図5に示すように、トリプルウェル構造により、第1電源電圧VDDが供給されたN−well N1によって逆バイアスされた寄生ダイオードD40が形成されることで、N+拡散層N2及びP−well P2によって形成されるダイオードD50と接地電圧GNDが供給されるP−sub P1との間が絶縁される。詳細には、GNDに接続されたP−sub P1上にN−wellN1、N−well N1上にP−well P2、P−well P2上にN+拡散層N2が形成され、N−well N1に第1電源電圧VDDが供給され、P−well P2にアノード端子、N+拡散層N2にカソード端子が接続される。このような構成により、N−well N1とP−well P2との間に逆バイアスされた寄生ダイオードD40が形成され、N+拡散層N2及びP−well P2によって形成されるダイオードD50と接地電圧GNDが供給されるP−sub P1との間が絶縁される。このような構造により、負電圧源に利用可能なダイオードD50を形成することが可能となる。

【0029】

ウェルの層数が図5に示す一例と同じ又は多い場合や、N−基板にダブルウェルが形成されたプロセスを用いる場合、すなわち多層ウェル構造を利用することで、N−wellとP+拡散層の間で負電圧源30に利用するダイオードを構成することも可能である。又、トランジスタのボディを基板から絶縁できるSOI基板を利用することで、トランジスタのボディとなるP−sub、N−subと、N+拡散層、P+拡散層の組み合わせによって負電圧源30に利用するダイオードを形成することが可能となる。尚、通常プロセスによるPN接合ダイオードや、ショットキーダイオード等を負電圧源30に利用しても構わない。

【0030】

負電圧源30は、図4A〜図4Cの様に構成できるが、安定的な第2電源電圧VNEGが供給できれば、その構成はこれに限らない。

【0031】

制御回路40は、負電圧検出回路41、選択演算回路42、43を具備する。負電圧検出回路41は、負電圧源30とローサイドトランジスタ22との接続ノード(出力ノード310)に接続される。負電圧検出回路41は、出力ノード310から供給される第2電源電圧VNEGが所望の値となっているかを監視し、監視結果に応じた信号レベル(論理値)の駆動制御信号RDYを、出力ノード410を介して選択演算回路42、43に出力する。詳細には、負電圧検出回路41は、第2電源電圧VNEGが予め設定された目標電圧よりも高いか否かを監視し、第2電源電圧VNEGが目標電圧より高い場合、ローレベル“0”の駆動制御信号RDYを出力し、第2電源電圧VNEGが目標電圧よりも低い場合、ハイレベル“1”の駆動制御信号RDYを出力する。

【0032】

図6は、本発明に係る負電圧検出回路41の構成の一例を示す図である。図6に示す負電圧検出回路41は、抵抗411、412、P型MOSトランジスタ413、414、コンパレータ415を具備する。抵抗411の一端には第1電源電圧VDDが供給され、他端はP型MOSトランジスタ413のドレイン及びコンパレータ415の反転入力端子に接続される。抵抗412の一端には第1電源電圧VDDが供給され、他端はP型MOSトランジスタ414のドレイン及びコンパレータ415の非反転入力端子に接続される。P型MOSトランジスタ413のゲートは接地され、ソースは負電圧源30の出力ノード310に接続される。P型MOSトランジスタ414のゲートは参照電圧生成回路440の出力ノード320に接続され、ソースは接地される。参照電圧生成回路440は参照電圧Vrefを出力ノード320に出力する。ここで参照電圧Vrefに−1を乗じた値“−Vref”は接地電圧GNDより低く、第2電源電圧VNEGに対して規定された所望の値(ここでは目標電圧)に設定される。

【0033】

図6に示す負電圧検出回路41では、接地電圧GNDから第2電源電圧VNEGを減じた値が、参照電圧Vrefから接地電圧GNDを減じた値よりも大きいとき、すなわち、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなると、抵抗411を流れる電流I1が抵抗412を流れる電流I2よりも大きくなる。この場合、反転入力端子の電圧V1が非反転入力端子の電圧V2よりも小さくなるため、コンパレータ415は出力ノード410にハイレベル“1”の駆動制御信号RDYを出力する。一方、接地電圧GNDから第2電源電圧VNEGを減じた値が、参照電圧Vrefから接地電圧GNDを減じた値よりも小さいとき、すなわち、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも高い場合、電流I1が電流I2よりも小さくなる。この場合、反転入力端子の電圧V1が非反転入力端子の電圧V2よりも大きくなるため、コンパレータ415は出力ノード410にローレベル“0”の駆動制御信号RDYを出力する。

【0034】

負電圧検出回路41は、図6の様に第2電源電圧VNEGと参照電圧Vrefとを比較する比較回路によって構成できるが、第2電源電圧VNEGが所定のレベル(目標電圧)に達したか否かを検出しその検出結果を駆動制御信号RDYとして出力できれば、その構成はこれに限らない。例えば、トランジスタの閾値電圧Vthやダイオードの順電圧VFを目標電圧として第2電源電圧VNEGの値を監視してもよい。又、上述の例では、参照電圧Vrefに−1を乗じた値“−Vref”を目標電圧としたがこれに限らない。例えば、第2電源電圧VNEGに基づいて生成された電圧(例えば分圧抵抗による分圧電圧)と参照電圧Vrefとを比較した結果に応じて、第2電源電圧VNEGが目標電圧以下となったか否かを検出する方法を負電圧検出回路41に採用しても構わない。

【0035】

選択演算回路42は、入力ノード51から入力されるPWM信号(入力信号GHIN)と、負電圧検出回路41から入力される駆動制御信号RDYとの論理演算結果を、駆動回路11の入力ノード420に出力する。ここでは、選択演算回路42はNANDゲートが好適に利用され、入力信号GHINと駆動制御信号RDY(のそれぞれが示す論理値)の否定論理積を入力ノード420に出力する。すなわち、選択演算回路42は、駆動制御信号RDYがローレベルレベル“0”のとき、入力信号GHINがいかなる値であってもハイレベル“1”の演算結果を入力ノード420(駆動回路11)に出力する。一方、選択演算回路42は、駆動制御信号RDYがハイレベルレベル“1”のとき、入力信号GHINが示す論理レベルに対応する論理レベルの演算結果を入力ノード420(駆動回路11)に出力する。ここでは入力信号GHINがハイレベル“1”のときローレベル“0”の演算結果が出力され、入力信号GHINがローレベル“0”のときハイレベル“1”の演算結果が出力される。同様に選択演算回路42は、入力ノード52から入力されるPWM信号(入力信号GLIN)と、負電圧検出回路41から入力される駆動制御信号RDYとの論理演算結果を、駆動回路12の入力ノード430に出力する。ここでは、選択演算回路42はNANDゲートが好適に利用され、入力信号GLINと駆動制御信号RDY(のそれぞれが示す論理値)の否定論理積を入力ノード430に出力する。すなわち、選択演算回路42は、駆動制御信号RDYがローレベルレベル“0”のとき、入力信号GLINがいかなる値であってもハイレベル“1”の演算結果を入力ノード430(駆動回路12)に出力する。一方、選択演算回路42は、駆動制御信号RDYがハイレベルレベル“1”のとき、入力信号GLINが示す論理レベルに対応する論理レベルの演算結果を入力ノード430(駆動回路12)に出力する。ここでは入力信号GLINがハイレベル“1”のときローレベル“0”の演算結果が出力され、入力信号GLINがローレベル“0”のときハイレベル“1”の演算結果が出力される。

【0036】

以上のような構成により、第1の実施の形態における制御回路40は、目標電圧よりも第2電源電圧VNEGが高い場合、入力信号GHIN、GLINに関わらずハイレベル“1”の出力信号を駆動回路11、12に出力し、目標電圧よりも第2電源電圧VNEGが低い場合、入力信号GHIN、GLINに応じた論理レベルの出力信号を駆動回路11、12に出力する。尚、入力ノード51、52に入力される入力信号GHINと入力信号GLINは互いに相補な信号であることが一般的に多い。

【0037】

駆動回路11は入力される信号を反転してハイサイドトランジスタ21に出力する。例えば、目標電圧よりも第2電源電圧VNEGが高い場合、制御回路40から入力されるハイレベルの信号を反転したローレベルのゲート駆動信号GHをハイサイドトランジスタ21に出力する。ハイサイドトランジスタ21は、Nチャネル型のノーマリオフ型トランジスタであるため、駆動回路11から出力されるローレベルのゲート駆動信号GHによって強制的にオフ状態となる。本実施の形態では、駆動回路12に供給される第2電源電圧VNEGが所定の値(目標電圧)に達するまでの間、ノーマリオフ型のハイサイドトランジスタ21を強制的にオフ状態としている。これにより、第3電源電圧VHに起因する貫通電流の発生を防止することができる。

【0038】

(動作)

次に図3及び図7を参照して、第1の実施の形態におけるゲート駆動回路1の動作を説明する。図7は、本発明によるゲート駆動回路の第1の実施の形態における動作を示すタイミングチャートである。

【0039】

図7を参照して、時刻T1に電力変換回路を含む半導体装置全体の電源(システム電源)が投入されてから時刻T2までの間、第1電源電圧VDDは不安定な値を示しながら所定の値となるまで上昇する。この間、負電圧源30は、第1電源電圧VDDが所定のレベルに達していないため動作せず、第2電源電圧VNEGは0Vを示す。負電圧検出回路41は、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも高い0Vであるため、ローレベル“0”の駆動制御信号RDYを出力ノード410に出力する。これにより、駆動回路11は、入力信号GHIN、GLINの値に関わらずローレベル“0”のゲート駆動信号GHを出力ノード110(ハイサイドトランジスタ21のゲート)に供給し、ハイサイドトランジスタ21を強制的にオフ状態とする。

【0040】

時刻T2において、第1電源電圧VDDが所定の値に安定すると、負電圧源30は動作を開始し、第2電源電圧VNEG(負電圧)は低下し始める。時刻T2から、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなる時刻T3までの間、負電圧検出回路41は、ローレベル“0”の駆動制御信号RDYを出力ノード410に出力する。これにより、駆動回路11は、入力信号GHINの値に関わらず、出力ノード110(ハイサイドトランジスタ21のゲート)にローレベル“0”のゲート駆動信号GHを供給し、ハイサイドトランジスタ21を強制的にオフ状態とする。一方、時刻T2から時刻T3の期間中、第2電源電圧VNEGは参照電圧に−1を乗じた値“−Vref”より高く不安定な値を示すため、駆動回路12から、出力ノード120(ローサイドトランジスタ22のゲート)に供給されるゲート駆動信号GLは不安定な値を示す。このため、ローサイドトランジスタ22のオン/オフの状態は不定となる場合がある。

【0041】

本実施の形態におけるゲート駆動回路1では、システム電源(第1電源電圧VDD)が投入される時刻T1から、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”を下回る時刻T3までの期間、制御回路40によってノーマリオフ型のハイサイドトランジスタ21を強制的にオフ状態としている。この結果、第3電源電圧VHを供給する電源と出力ノード53(負荷50)との電気的接続が遮断され、第3電源電圧VHに起因したハーフブリッジ回路におけるスイッチング素子(ハイサイドトランジスタ21、ローサイドトランジスタ22)への貫通電流が阻止される。

【0042】

時刻T3以降、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”より低くなるため、負電圧検出回路41は、ハイレベル“1”の駆動制御信号RDYを出力する。これにより、駆動回路11、12は、入力信号GHIN、GLINの信号レベルに応じた信号レベルのゲート駆動信号GH、GLを出力する通常動作モードに移行する。

【0043】

第1の実施の形態では、ローサイドトランジスタ22としてスイッチング性能が良好なノーマリオン型のGaNトランジスタを用いている。このため、ローサイドトランジスタ22のゲート駆動する駆動回路12には、システム電源投入時等にその値が不安定となる第2電源電圧VNEG(負電圧)が供給される。第2電源電圧VNEGが不安定である場合、特に、第2電源電圧VNEGが規定の電圧(目標電圧以下)まで低下していない場合、ローサイドトランジスタ22はオフ状態とならない。本実施の形態におけるゲート駆動回路は、第2電源電圧VNEGが規定の電圧(目標電圧、ここでは“−Vref”)に達するまでハイサイドトランジスタ21を強制的にオフ状態とする。このため、第2電源電圧VNEGが不安定な期間においても第3電源電圧VHに起因したスイッチング素子(ハイサイドトランジスタ21、ローサイドトランジスタ22)への貫通電流を防止することができる。又、第2電源電圧VNEGが規定の電圧(目標電圧、ここでは“−Vref”)に達した場合、ゲート駆動回路1は、入力信号GHIN、GLINに応じて、ハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御することが可能となる。この際、ゲート駆動回路は、ゲート駆動信号GH、GLがハイレベルになることを許可する。

【0044】

(ゲート駆動回路の適用例)

図8は、第1の実施の形態におけるゲート駆動回路1を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。図8に示すマルチフェーズスイッチング電源は、並列接続された複数のスイッチング電源60と、複数のハーフブリッジ60のそれぞれに搭載されたフェーズIC23を制御する制御IC70を具備する。複数のハーフブリッジ60のそれぞれは、負荷50とともにハーフブリッジ回路を構成するスイッチング素子として機能するハイサイドトランジスタ21及びローサイドトランジスタ22と、そのスイッチング動作を制御するフェーズIC23を備える。複数のハーフブリッジ60のそれぞれのハイサイドトランジスタ21及びローサイドトランジスタ22は、第3電源(第3電源電圧VH)とGND(接地電圧GND)との間に設けられ、それぞれの出力ノード53は共通接続される。

【0045】

フェーズIC23は、出力ノード110を介してハイサイドトランジスタ21のゲートに接続され、出力ノード120を介してローサイドトランジスタ22のゲートに接続される。又、フェーズIC23は入力ノード230、231を介して制御IC70に接続される。図9は、図8に示すマルチフェーズスイッチング電源に搭載されるフェーズIC23の構成の一例を示す図である。

【0046】

図9を参照して、フェーズIC23は、図3に示すゲート駆動回路1、デッドタイム回路31、32を備える。制御IC70は、入力ノード230を介してゲート駆動回路1にPWM信号を出力する。この際、PWM信号は、デッドタイム回路31、32を介して入力ノード51、52に入力される。これにより、入力ノード51、52に入力される入力信号GHIN、GLINは、デッドタイムを含むPWM信号となる。又、デッドタイム回路32に入力されるPWM信号は反転されるため、入力ノード51、52に入力される入力信号GHIN、GLINは相互に相補な関係となる。

【0047】

ゲート駆動回路1は、入力信号GHIN、GLINに応じたゲート駆動信号GH、GLを出力することで、ハーフブリッジ回路のスイッチング素子であるハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御する。ここで、負電圧源30から供給される第2電源電圧VNEGが目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”)よりも高い場合、ゲート駆動回路1は、ハイサイドトランジスタ21をオフ状態とするゲート駆動信号GHを出力する。これにより、複数のハーフブリッジ60のそれぞれにおいて、第2電源電圧VNEGが目標電圧より高いときに発生する貫通電流を防止することができる。

【0048】

制御IC70は、入力ノード231を介してフェーズIC23に異常検出信号を出力する。異常検出信号は、例えば選択演算回路42に入力され、駆動回路11(ハイサイドトランジスタ21)の動作を制御する。詳細には、制御IC70は、スイッチング電源の出力ノード53の電圧を監視し、異常を検出するとローレベル“0”の異常検出信号をフェーズIC23(入力ノード231)に出力する。選択演算回路42は、ローレベル“0”の異常検出信号に応じてハイレベル“1”の出力信号を駆動回路11に出力する。これにより、駆動回路11は、ローレベル“0”のゲート駆動信号GHを出力し、ハイサイドトランジスタ21をオフ状態とする。すなわち、スイッチング電源の出力異常(例えば出力信号Voutが所定の値を超える)に応じて、フェーズIC23は、ハイサイドトランジスタ21をオフ状態とし、スイッチング電源の動作を停止する。

【0049】

尚、図8に示すマルチフェーズスイッチング電源では、ハーフブリッジ60毎(フェーズIC23毎)に負電圧源30が搭載されているが、これに限らず、複数のハーフブリッジ60に共通の負電圧源が設けられても良い。この場合、目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC23のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC23に共通の負電圧検出回路(図示なし)によって行われても良い。

【0050】

図8のように、図3に示すゲート駆動回路1をマルチフェーズスイッチング電源に利用することで、第2電源電圧VNEGが不安定な期間に複数のハーフブリッジのいずれかにおいて発生する貫通電流を防止することができる。

【0051】

図10は、第1の実施の形態におけるゲート駆動回路1を利用した3相インバータの構成の一例を示す図である。図10に示す三相インバータは、並列接続された複数のハーフブリッジ61−1〜61−3と、複数のハーフブリッジ61−1〜61−3のそれぞれに搭載されたフェーズIC24を制御する制御IC80を具備する。複数のハーフブリッジ61−1〜61−3のそれぞれは、負荷50とともにハーフブリッジ回路のスイッチング素子として機能するハイサイドトランジスタ21及びローサイドトランジスタ22と、そのスイッチング動作を制御するフェーズIC24を備える。複数のハーフブリッジ61−1〜61−3のそれぞれのハイサイドトランジスタ21及びローサイドトランジスタ22は、第3電源(第3電源電圧VH)とGND(接地電圧GND)との間に設けられる。ハーフブリッジ61−1〜61−3の出力ノード53−1〜53−3は、図示しない3相モータ(負荷50に相当)のu端子、v端子、w端子に接続される。図10に示す一例では、ハーフブリッジ61−1の出力ノード53−1はu端子に接続され、ハーフブリッジ61−2の出力ノード53−2はv端子に接続され、ハーフブリッジ61−3の出力ノード53−3はw端子に接続される。

【0052】

フェーズIC24は、出力ノード110を介してハイサイドトランジスタ21のゲートに接続され、出力ノード120を介してローサイドトランジスタ22のゲートに接続される。又、フェーズIC24は入力ノード230を介して制御IC80に接続される。図11は、図10に示す3相インバータに搭載されるフェーズIC24の構成の一例を示す図である。

【0053】

図11を参照して、フェーズIC24は、図3に示すゲート駆動回路1を備える。制御IC80は、入力ノード230を介してゲート駆動回路1にPWM信号を出力する。この際、PWM信号は、デッドタイム回路31、32を介して入力ノード51、52に入力される。これにより、入力ノード51、52に入力される入力信号GHIN、GLINは、デッドタイムを含むPWM信号となる。又、デッドタイム回路32に入力されるPWM信号は反転されるため、入力ノード51、52に入力される入力信号GHIN、GLINは相互に相補な関係となる。尚、制御IC80は、周辺機器やコンソールに接続されるマイコンに例示され、駆動系の第1電源電圧VDDより低い電源電圧を高位側の電源とし、接地電圧GNDと異なる電源電圧を低位側の電源として動作する。この場合、PWM信号はレベルシフタ(図示なし)を介してフェーズICに入力される。

【0054】

ゲート駆動回路1は、入力信号GHIN、GLINに応じたゲート駆動信号GH、GLを出力することで、ハーフブリッジ回路のスイッチング素子であるハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御する。ここで、負電圧源30から供給される第2電源電圧VNEGが目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”)よりも高い場合、ゲート駆動回路1は、ハイサイドトランジスタ21をオフ状態とするゲート駆動信号GHを出力する。これにより、複数のハーフブリッジ61−1〜61−3のいずれかにおいて、第2電源電圧VNEGが目標電圧より高い値となるときに発生する貫通電流や、これによるモータの破壊を防止することができる。

【0055】

尚、図10に示す3相インバータでは、ハーフブリッジ61毎(フェーズIC24毎)に負電圧源30が搭載されているが、これに限らず、複数のハーフブリッジ61−1、61−2、61−3に共通の負電圧源が設けられても良い。この場合、目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC24のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC24に共通の負電圧検出回路(図示なし)によって行われても良い。

【0056】

又、ハイサイドトランジスタ21を駆動する駆動回路11は、低位側電源電圧として接地電圧GNDが供給される接地端子ではなく、出力ノード53−1〜53−3のうち、対応する出力ノード53に接続されても構わない。この場合、出力ノード53の電圧に所定の電圧を加算した電圧が高位側電源電圧(第1電源電圧VDD)として駆動回路11に供給される。同様に、ローサイドトランジスタ22を駆動する駆動回路12には、第1電源電圧VDDが供給されるのではなく、接地電圧GNDよりも高い任意の大きさの電圧が高位側電源電圧として供給されても良い。

【0057】

例えば、電気自動車に利用されるモータに図10に示す3相インバータを適用する場合、ハイサイドの駆動回路11の低位側電源として出力ノード53−1が接続され、高電位側の第1電源電圧VDDとして“出力ノード53−1の電圧+15V”が供給される。又、ローサイドの駆動回路12の高位側電源電圧として“第2電源電圧VNEG+15V”が供給され、低位側電源電圧として第2電源電圧VNEGが供給される。更に電気自動車に利用されるモータを駆動するための第3電源電圧VHとして、例えば“接地電圧GND+600V”といった高電圧が供給される。

【0058】

図10のように、図3に示すゲート駆動回路1を3相インバータに利用することで、第2電源電圧VNEGが目標電圧よりも高く不安定な期間に複数のインバータのいずれかにおいて発生する貫通電流を防止することができる。特に、第3電源電圧VHが高電圧となるモータを駆動する場合、第3電源電圧VHに起因する貫通電流を防止することは、モータの破壊を防止する上で有効である。

【0059】

本実施の形態では、ハイサイドトランジスタ21として、ゲート電圧が0Vにおいてオフ状態となるノーマリオフ型のパワートランジスタを利用している。この場合、ハイサイドトランジスタ21のゲートを駆動するとき第2電源電圧VNEG(負電圧)を利用していないため、第2電源電圧VNEGが規定の電圧まで低下することを待たずにハイサイドトランジスタ21をオフ状態とすることができる。このため、本実施の形態におけるゲート駆動回路は、図2のように第1電源電圧VDD(例えばシステム制御系電源)と同時的に第3電源電圧VH(例えばパワー系の電源)が上昇するようなシステムにおいても利用でき、第3電源電圧VHの上昇にともなって発生するスイッチング素子への貫通電流を防止することができる。

【0060】

又、システム電源断により第1電源電圧VDDが遮断された場合、ハイサイドトランジスタ21のゲート電圧はゼロとなる。この場合、ハイサイドトランジスタ21がノーマリオフ型トランジスタであれば、ハイサイド側がオフ状態になる。このときローサイドトランジスタ22がオン状態であっても、負荷50に印加される電圧はゼロになるので、装置の破壊などが引き起こされることはない。

【0061】

2.第2の実施の形態

第1の実施の形態における電力変換回路では、ハイサイドトランジスタ21としてノーマリオフ型のトランジスタを用いている。この構成を用いることで、システム電源(第1電源電圧VDD)の投入時や遮断時の貫通電流の問題を解決することができるが、ノーマリオン型のトランジスタに比べてスイッチング性能(例えばゲート容量に対するオン抵抗の低さ)は、若干悪化する。

【0062】

第2の実施の形態における電力変換回路では、スイッチング性能を向上させるため、ハイサイドトランジスタ21としてノーマリオン型のトランジスタが用いられる。

(構成)

以下、図12から図16を参照して、第2の実施の形態におけるゲート駆動回路1の構成の詳細を説明する。図12は、本発明による電力変換回路の第2の実施の形態における構成を示す図である。図12を参照して、第2の実施の形態における電力変換回路は、ゲート駆動回路1と、ハーフブリッジ回路のスイッチング素子として機能し、負荷50に接続されるハイサイドトランジスタ21及びローサイドトランジスタ22を具備する。第2の実施の形態におけるゲート駆動回路1は、駆動回路11、12、負電圧源30−1、30−2、制御回路40を具備し、ハイサイドトランジスタ21及びローサイドトランジスタ22を駆動する。図12に示す一例では、スイッチング性能が良好であるノーマリオン型のNチャネル型GaNトランジスタがハイサイドトランジスタ21及びローサイドトランジスタ22として好適に利用される。

【0063】

ハイサイドトランジスタ21のドレインには、図示しない電源から第3電源電圧VHが供給され、ソースは出力ノード53を介してローサイドトランジスタ22のドレインに接続される。ローサイドトランジスタ22のソースは接地され、ドレインは出力ノード53を介してハイサイドトランジスタ21のソースに接続される。出力ノード53は、負荷50に接続される。

【0064】

第2の実施の形態における駆動回路11は、入力ノード51から入力されるPWM信号(入力信号GHIN)に応じて、ノーマリオン型のハイサイドトランジスタ21のゲートを駆動する。駆駆動回路11は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備える。図12に示す一例では、駆動回路11はCMOSインバータであり、入力信号GHINを反転させた信号を、ゲート駆動信号GHとしてハイサイドトランジスタ21のゲートに出力する。第2の実施の形態における駆動回路12は、入力ノード52から入力されるPWM信号(入力信号GLIN)に応じて、ノーマリオン型のローサイドトランジスタ22のゲートを駆動する。駆動回路12は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源30から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備える。図12に示す一例では、駆動回路12はCMOSインバータであり、入力信号GLINを反転させた信号を、ゲート駆動信号GLとしてローサイドトランジスタ22のゲートに出力する。尚、駆動回路11、12に供給される高電位側の電源電圧は第1電源電圧VDDに限らず、ノーマリオン型トランジスタをオン状態とできる電圧であれば任意に設定できる。

【0065】

負電圧源30−1、30−2は、接地電圧GNDよりも低い負電圧(第2電源電圧VNEG1、VNEG2)を生成する。負電圧源30−1、30−2は、第1の実施の形態と同様な構成であり、例えば図4A〜図4Cに示す構成が好適である。

【0066】

第2の実施の形態における制御回路40は、負電圧検出回路41−1、41−2、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46を具備する。負電圧検出回路41−1、41−2は、第1の実施の形態における負電圧検出回路41と同様な構成により、第2電源電圧VNEG1、VNEG2と、参照電圧Vref(図12に図示なし)との比較結果に応じた信号レベル(論理値)の駆動制御信号RDYを出力する。

【0067】

詳細には、負電圧検出回路41−1は、負電圧源30−1とローサイドトランジスタ22との接続ノード(出力ノード310−1)に接続される。負電圧検出回路41−1は、出力ノード310−1から供給される第2電源電圧VNEG1と、目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”(図12に図示なし))との比較結果に応じた信号レベル(論理値)の駆動制御信号RDY1を、出力ノード410−1を介して選択演算回路44に出力する。負電圧検出回路41−2は、負電圧源30−2とハイサイドトランジスタ21との接続ノード(出力ノード310−2)に接続される。負電圧検出回路41−2は、出力ノード310−2から供給される第2電源電圧VNEG2と、目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”(図12に図示なし))との比較結果に応じた信号レベル(論理値)の駆動制御信号RDY2を、出力ノード410−2を介して選択演算回路44に出力する。例えば、負電圧検出回路41−1、41−2は、第2電源電圧VNEG1、VNEG2が目標電圧よりも高い場合、ローレベル“0”の駆動制御信号RDY1、RDY2を選択演算回路44に出力し、第2電源電圧VNEGが目標電圧よりも低い場合、ハイレベル“1”の駆動制御信号RDY1、RDY2を選択演算回路44に出力する。第2の実施の形態における負電圧検出回路41−1、41−2の構成は、図6に示す負電圧検出回路41の構成と同様である。

【0068】

選択演算回路44は、負電圧検出回路41−1、41−2から入力される駆動制御信号RDY1、RDY2との論理演算結果を、スイッチ制御回路45に出力する。ここでは、選択演算回路44はNANDゲートが好適に利用され、駆動制御信号RDY1と駆動制御信号RDY2(のそれぞれが示す論理値)の否定論理積をスイッチ制御回路45に出力する。すなわち、選択演算回路44は、駆動制御信号RDY1、RDY2の少なくとも一方がローレベルレベル“0”のとき、ハイレベル“1”の演算結果をスイッチ制御回路45に出力する。又、選択演算回路44は、駆動制御信号RDY1、RDY2が両者ともハイレベルレベル“1”のとき、ローレベル“0”の演算結果をスイッチ制御回路45に出力する。

【0069】

スイッチ制御回路45は、選択演算回路44から出力された演算結果に応じて、電源制御スイッチ46のスイッチング動作(オン又はオフ)を制御する。詳細には、スイッチ制御回路45は、図示しない電源から供給される第1電源電圧VDDと接地電圧GNDに応じて動作するトーテムポール回路を備える。例えば、駆動回路11はCMOSインバータであり、入力信号の反転信号をスイッチ制御信号SCとして出力ノード130を介して電源制御スイッチ46のスイッチング制御端子。例えば、選択演算回路44から出力された演算結果がローレベル“0”の場合、ハイレベル“1”のスイッチ制御信号SCを出力し、選択演算回路44から出力された演算結果がハイレベル“1”の場合、ローレベル“0”のスイッチ制御信号SCを出力する。

【0070】

電源制御スイッチ46は、第3電源電圧VHが供給される電源とハイサイドトランジスタ21のドレインとの間に設けられる。電源制御スイッチ46は、出力ノード130から供給されるスイッチ制御信号SCに応じて、第3電源電圧VHが供給される電源とハイサイドトランジスタ21のドレインとの接続/切断を制御する。電源制御スイッチ46は、電源(第3電源電圧VH)とハイサイドトランジスタ21との間の接続/切断が制御できれば、FET、IGBT、バイポーラトランジスタ、サイリスタ、あるいは機械的スイッチ(例えばリレースイッチ)等に例示されるスイッチ素子が好適である。又、電源制御スイッチ46は低抵抗、低コストであれば良くスイッチング速度が高速である必要はないため、例えばIGBTのような低速スイッチも電源制御スイッチ46として利用できる。ただし、負電圧に依存せずに電源とハイサイドトランジスタ21との接続を確実に切断するため、電源制御スイッチ46は、ノーマリオフ型(エンハンスメント型)のトランジスタが好適に利用される。例えば、電源制御スイッチ46として、コレクタが電源(第3電源電圧VH)に接続され、エミッタがハイサイドトランジスタ21のドレインに接続され、ゲートが出力ノード130に接続されたNチャネル型のIGBTが設けられる。

【0071】

スイッチング素子として利用されるハイサイドトランジスタ21及びローサイドトランジスタ22は、高速動作が求められることからNチャネル型トランジスタが好適に用いられる。一方、電源制御スイッチ46は、第2電源電圧VNEGが不安定なときに負荷50に供給される電力を遮断するためのスイッチ素子であれば良い。すなわち、電源制御スイッチ46は、PWM信号などによる頻繁なスイッチングは行わないため、単純に低抵抗であれば良く、高速スイッチング性能は要求されない。このため、電源制御スイッチ46がトランジスタによって構成される場合、電源制御スイッチ46は、電源とハイサイドトランジスタ21との間の導通を制御できればPチャネル型トランジスタでも、Nチャネル型トランジスタでもどちらでも構わない。

【0072】

以上のような構成により、第2の実施の形態における制御回路40では、目標電圧よりも第2電源電圧VNEGが高い場合、電源制御スイッチ46がオフとなり、ハイサイドトランジスタ21への第3電源電圧VHの供給が遮断され、ハイサイドトランジスタ21のドレイン電流が遮断される。これにより、第2電源電圧VNEGが目標電圧よりも高く不安定な期間において、第3電源電圧VHに起因するハイサイドトランジスタ21への貫通電流の発生を防止することができる。一方、目標電圧よりも第2電源電圧VNEGが低い場合、電源制御スイッチ46がオン状態となり、ハイサイドトランジスタ21へ第3電源電圧VHが供給される。第2電源電圧VNEGが参照電圧Vrefより低い規定の値で安定すると、ハイサイドトランジスタ21及びローサイドトランジスタ22は、入力信号GHIN、GLINに応じた通常のスイッチング動作を行うことが可能となる。

【0073】

(動作)

次に図12及び図13を参照して、第2の実施の形態におけるゲート駆動回路1の動作を説明する。図13は、本発明によるゲート駆動回路の第2の実施の形態における動作を示すタイミングチャートである。

【0074】

図13を参照して、時刻T1に電力変換回路を含む半導体装置全体の電源(システム電源)が投入されてから時刻T2までの間、第1電源電圧VDDは不安定な値を示しながら所定の値となるまで上昇する。この間、負電圧源30は、第1電源電圧VDDが所定のレベルに達していないため動作せず、第2電源電圧VNEGxは0Vを示す(xは、1又は2)。負電圧検出回路41−xは、第2電源電圧VNEGxが参照電圧Vrefに−1を乗じた値“−Vref”よりも高い0Vであるため、ローレベル“0”の駆動制御信号RDYxを出力ノード410−xに出力する。これにより、スイッチ制御回路45はローレベル“0”のスイッチ制御信号SCを出力ノード130(電源制御スイッチ46の制御端子)に供給し、電源制御スイッチ46を強制的にオフ状態とする。

【0075】

時刻T2において、第1電源電圧VDDが所定の値に安定すると、負電圧源30は動作を開始し、第2電源電圧VNEGx(負電圧)は低下し始める。時刻T2から、第2電源電圧VNEGxが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなる時刻T3までの間、負電圧検出回路41−xは、ローレベル“0”の駆動制御信号RDYxを出力ノード410−xに出力する。これにより、スイッチ制御回路45はローレベル“0”のスイッチ制御信号SCを出力ノード130(電源制御スイッチ46の制御端子)に供給し、電源制御スイッチ46を強制的にオフ状態とする。

【0076】

本実施の形態におけるゲート駆動回路1では、システム電源が投入される時刻T1から、第2電源電圧VNEGが参照電圧Vrefを下回る時刻T3までの期間、制御回路40におけるノーマリオフ型の電源制御スイッチ46を強制的にオフ状態としている。この結果、第3電源電圧VHを供給する電源とハイサイドトランジスタ21との電気的接続が遮断され、第3電源電圧VHに起因したハイサイドトランジスタ21への貫通電流が阻止される。

【0077】

時刻T3以降、第2電源電圧VNEGxが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなると、負電圧検出回路41−xは、ハイレベル“1”の駆動制御信号RDYxを出力する。これにより、スイッチ制御回路45はハイレベル“1”のスイッチ制御信号SCを出力ノード130(電源制御スイッチ46の制御端子)に供給し、電源制御スイッチ46をオン状態とする。これにより、ハイサイドトランジスタ21に第3電源電圧VHが供給され、ハイサイドトランジスタ21及びローサイドトランジスタ22は、入力信号GHIN、GLINの信号レベルに応じたスイッチング動作を行う通常動作モードに移行する。

【0078】

第2の実施の形態では、ノーマリオフ型の電源制御スイッチ46によって、第2電源電圧VNEGに応じた第3電源電圧VHの供給制御を行っている。このため、ローサイドトランジスタ22のみならずハイサイドトランジスタ21にも高速スイッチング可能で低抵抗なノーマリオン型のGaNトランジスタを用いることが可能となる。従って、第2の実施の形態における電力変換回路によれば、ハーフブリッジ回路のスイッチング素子におけるオン抵抗による損失と、スイッチング損失の両方を小さくしながら、負電圧が不安定なときに発生する貫通電流を防止することができる。

【0079】

(ゲート駆動回路の適用例)

図14は、第2の実施の形態におけるゲート駆動回路1を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。図14に示すマルチフェーズスイッチング電源は、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46、並列接続された複数のハーフブリッジ62、複数のハーフブリッジ62のそれぞれに搭載されたフェーズIC25を制御する制御IC90を具備する。図12に示すゲート駆動回路1のうち、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46は、複数のハーフブリッジ62に共通して設けられ、これら以外の構成は、複数のハーフブリッジ62のそれぞれのフェーズIC25に搭載される。以下では、電源制御スイッチ46として、コレクタが電源(第3電源電圧VH)に接続され、エミッタが複数のハイサイドトランジスタ21のドレインに共通接続され、ゲートが出力ノード130に接続されたNチャネル型のIGBTが設けられているものとして説明する。

【0080】

複数のハーフブリッジ62のそれぞれは、負荷50とともにハーフブリッジ回路のスイッチング素子を構成するハイサイドトランジスタ21及びローサイドトランジスタ22と、そのスイッチング動作を制御するフェーズIC25を備える。複数のハーフブリッジ62のそれぞれにおけるハイサイドトランジスタ21は共通の電源制御スイッチ46を介して第3電源(第3電源電圧VH)に接続され、ローサイドトランジスタ22はGND(接地電圧GND)に接続される。又、複数のハーフブリッジ62の出力ノード53は共通接続される。ここで、ハイサイドトランジスタ21及びローサイドトランジスタ22はノーマリオン型のトランジスタが好適に利用される。

【0081】

選択演算回路44は、複数のハーフブリッジ62のそれぞれに搭載されたフェーズIC25から出力される駆動制御信号RDYxを入力とし、その否定論理積をスイッチ制御回路45に出力する。スイッチ制御回路45は、選択演算回路44からの演算結果の反転信号をスイッチ制御信号SCとして電源制御スイッチ46のゲートに出力する。電源制御スイッチ46は、スイッチ制御信号SCに応じて第3電源(第3電源電圧VH)と、複数のハーフブリッジ62のハイサイドトランジスタ21との接続/切断を制御する。

【0082】

フェーズIC25は、出力ノード110を介してハイサイドトランジスタ21のゲートに接続され、出力ノード120を介してローサイドトランジスタ22のゲートに接続される。又、フェーズIC25は入力ノード230を介して制御IC90に接続される。図15は、図14に示すマルチフェーズスイッチング電源に搭載されるフェーズIC25の構成の一例を示す図である。

【0083】

図15を参照して、フェーズIC25は、図12に示すゲート駆動回路1のうち、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46を除く、駆動回路11、12、負電圧源30−1、30−2、負電圧検出回路41−1、41−2と、デッドタイム回路31、32を備える。制御IC70は、入力ノード230を介してゲート駆動回路1にPWM信号を出力する。この際、PWM信号は、デッドタイム回路31、32を介して入力ノード51、52に入力される。これにより、入力ノード51、52に入力される入力信号GHIN、GLINは、デッドタイムを含むPWM信号となる。又、デッドタイム回路32に入力されるPWM信号は反転されるため、入力ノード51、52に入力される入力信号GHIN、GLINは相互に相補な関係となる。

【0084】

駆動回路11、12は、入力信号GHIN、GLINに応じたゲート駆動信号GH、GLを出力することで、ハーフブリッジ回路のスイッチング素子であるハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御する。負電圧検出回路41−1、41−2から出力される駆動制御信号RDY1、RDY2は、複数のハーフブリッジ62に共通の選択演算回路44に入力される。ここで、複数のフェーズIC25のそれぞれの負電圧源30−1、30−2から供給される第2電源電圧VNEG1、VNEG2の少なくとも一方が目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”)よりも高い場合、スイッチ制御回路45は、電源制御スイッチ46をオフ状態とするスイッチ制御信号SCを出力する。これにより、複数のハーフブリッジ62のいずれかにおいて、第2電源電圧VNEG1、VNEG2が規定の値より高いときに発生する貫通電流を防止することができる。

【0085】

制御IC90は、スイッチング電源の出力ノード53の電圧を監視し、異常を検出するとローレベル“0”の異常検出信号を選択演算回路44に出力してもよい。この場合、スイッチ制御回路45は、ローレベル“0”のスイッチ制御信号SCを出力し、電源制御スイッチ46をオフ状態とする。すなわち、スイッチング電源の出力異常(例えば出力信号Voutが所定の値を超える場合)に応じて、スイッチ制御回路45は、電源制御スイッチ46をオフ状態とし、スイッチング電源の動作を停止する。

【0086】

尚、図14に示すマルチフェーズスイッチング電源では、ハーフブリッジ62毎(フェーズIC25毎)に負電圧源30−1、30−2が搭載されているが、これに限らず、複数のハーフブリッジ62、あるいは駆動回路11、12に共通の負電圧源が設けられても良い。この場合、目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC25のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC23に共通の負電圧検出回路(図示なし)によって行われても良い。

【0087】

図14のように、図12に示すゲート駆動回路1をマルチフェーズスイッチング電源に利用することで、第2電源電圧VNEG1、VNEG2が目標電圧よりも高く不安定な期間に複数のハーフブリッジ62のいずれかにおいて発生する貫通電流を防止することができる。又、複数のハーフブリッジ62に共通の電源制御スイッチ46によって、複数のハーフブリッジ62への電源供給を制御しているため、面積の増大を抑制しながら負電圧異常に起因する貫通電流を防止することが可能となる。

【0088】

図16は、第2の実施の形態におけるゲート駆動回路1を利用した3相インバータの構成の一例を示す図である。図16に示す3相インバータは、選択演算回路47、48、スイッチ制御回路45、電源制御スイッチ46、並列接続された複数のハーフブリッジ63−1〜63−3、複数のハーフブリッジ63−1〜63−3のそれぞれに搭載されたフェーズIC25を制御する制御IC80を具備する。図12に示すゲート駆動回路1のうち、スイッチ制御回路45及び電源制御スイッチ46が、複数のハーフブリッジ63−1〜63−3に共通して設けられるとともに、選択演算回路44に替えて、複数のハーフブリッジ63−1〜63−3に共通する選択演算回路47、48が設けられ、これら以外の構成は、複数のハーフブリッジ63−1〜63−3のそれぞれのフェーズIC25に搭載される。以下では、電源制御スイッチ46として、コレクタが電源(第3電源電圧VH)に接続され、エミッタが複数のハイサイドトランジスタ21のドレインに共通接続され、ゲートが出力ノード130に接続されたNチャネル型のIGBTが設けられているものとして説明する。

【0089】

複数のハーフブリッジ63−1〜63−3のそれぞれは、図14に示すハーフブリッジ62と同様に、負荷50とともにハーフブリッジ回路のスイッチング素子を構成するハイサイドトランジスタ21及びローサイドトランジスタ22と、ハーフブリッジ回路のスイッチング動作を制御するフェーズIC25を備える。複数のハーフブリッジ63−1〜63−3のそれぞれにおけるハイサイドトランジスタ21は共通の電源制御スイッチ46を介して第3電源(第3電源電圧VH)に接続され、ローサイドトランジスタ22はGND(接地電圧GND)に接続される。又、複数のハーフブリッジ63−1〜63−3の出力ノード53の出力ノード53−1〜53−3は、図示しない3相モータ(負荷50に相当)のu端子、v端子、w端子に接続される。ここでu端子とは3相誘導モータのステータコイルのうち、u相コイルの入力端子であり、v端子とはv相コイルの入力端子であり、w端子とはw相コイルの入力端子である。図16に示す一例では、ハーフブリッジ63−1の出力ノード53−1はu端子に接続され、ハーフブリッジ63−2の出力ノード53−2はv端子に接続され、ハーフブリッジ63−3の出力ノード53−3はw端子に接続される。

【0090】

ハーフブリッジ63−1〜63−3の構成は、出力ノード53−1〜53−3の接続先以外、図14に示すハーフブリッジ62と同様であるため、その説明は省略する。又、フェーズIC25の構成は、駆動制御信号RDY1、RDY2の出力先が、選択演算回路47である以外図15に示す構成と同様である。

【0091】

選択演算回路47は、複数のハーフブリッジ63−1〜63−3のそれぞれにおけるフェーズIC25から出力される駆動制御信号RDY1、RDY2の論理演算結果を、選択演算回路48に出力する。ここでは、選択演算回路47はNANDゲートが好適に利用され、駆動制御信号RDY1と駆動制御信号RDY2(のそれぞれが示す論理値)の否定論理積を選択演算回路48に出力する。選択演算回路48は、ORゲートが好適に利用され、選択演算回路47の出力と異常検出信号との論理和をスイッチ制御回路45に出力する。u端子、v端子、w端子のいずれかに対する出力信号や、図示しないモータに異常が生じた場合、ハイレベル“1”の異常検出信号が入力され、異常がない場合、ローレベル“0”の異常検出信号が入力される。選択演算回路48は、選択演算回路47の演算結果と異常検出信号のすくなくとも一方が、ハイレベル“1”の場合、すなわちモータ等に異常がある場合や第2電源電圧VNEG1、VNEG2の少なくとも一方が目標電圧に達していない場合、ハイレベル“1”の信号をスイッチ制御回路45に出力する。この場合、スイッチ制御回路45はローレベル“0”のスイッチ制御信号SCを電源制御スイッチ46のゲート)に供給し、電源制御スイッチ46を強制的にオフ状態とする。これにより、モータ出力に異常のあるときに第3電源電圧VHの供給を遮断できるとともに、複数のハーフブリッジ63−1〜63−3のいずれかにおいて、第2電源電圧VNEG1、VNEG2が目標電圧より高いときに発生する貫通電流や、これによるモータの破壊を防止することができる。

【0092】

一方、選択演算回路47の演算結果と異常検出信号の両者ともローレベル“0”の場合、すなわちモータ等に異常がない場合や第2電源電圧VNEG1、VNEG2の両者が規定のレベルに達している場合、選択演算回路48はローレベル“0”の信号をスイッチ制御回路45に出力する。この場合、スイッチ制御回路45はハイレベル“1”のスイッチ制御信号SCを電源制御スイッチ46のゲートに供給し、電源制御スイッチ46を強制的にオン状態とする。これにより、複数のハーフブリッジ63−1〜63−3には第3電源電圧VHが供給され、複数のハーフブリッジ63−1〜63−3は入力信号GHIN、GLINに応じた駆動電圧を出力端子53−1〜53−3に出力して図示しない3相モータを駆動する。

【0093】

尚、図16に示す3相インバータでは、ハーフブリッジ63毎(フェーズIC25毎)に負電圧源30が搭載されているが、これに限らず、複数のハーフブリッジ63−1、63−2、63−3に共通の負電圧源が設けられても良い。この場合目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC25のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC25に共通の負電圧検出回路(図示なし)によって行われても良い。

【0094】

又、ハイサイドトランジスタ21は、接地電圧GNDが供給される接地端子ではなく、出力ノード53−1〜53−3のうち、対応する出力ノード53に接続されても構わない。電気自動車に利用されるモータに図10に示す3相インバータを適用する場合、ハイサイドトランジスタ21の低位電源として、接地端子に替えて出力ノード53−1に接続されることで、第1電源電圧VDDとして“出力ノード53−1の電圧+15V”が供給され、第3電源電圧として“接地電圧GND+600V”が供給される。

【0095】

図16のように、図12に示すゲート駆動回路1を3相インバータに利用することで、第2電源電圧VNEG1、VNEG2が不安定な期間に複数のインバータ63−1〜63−3のいずれかにおいて発生する貫通電流を防止することができる。又、複数のハーフブリッジ63−1〜63−3に共通の電源制御スイッチ46によって、複数のハーフブリッジ63−1〜63−3への電源供給を制御しているため、面積の増大を抑制しながら負電圧異常に起因する貫通電流を防止することが可能となる。特に、第3電源電圧VHが高電圧となるモータを駆動する場合、第3電源電圧VHに起因する貫通電流を防止することは、モータの破壊を防止する上で有効である。

【0096】

本実施の形態では、ハイサイド、ローサイドともにノーマリオン型トランジスタを用いているため、第1の実施の形態に比べてパワートランジスタによる損失を減らすことが可能である。又、ハイサイドトランジスタ21と電源の間に挿入するノーマリオフ型の電源制御スイッチ46は、複数のフェーズICで共有することができるため、貫通電流防止のための構成による面積増大を抑制することができる。

【0097】

(パッケージ例)

図17は、第1の実施の形態における電力変換回路を1つのパッケージに実装した場合の構成例を示す図である。図17を参照して、本発明に係るパッケージ(SiP:System in Package)は、図3に示すゲート駆動回路1を含む制御チップ91、ハイサイドトランジスタ21を含むハイサイド部92、ローサイドトランジスタ22を含むローサイド部を具備し、制御チップ91、ハイサイド部92、ローサイド部93は樹脂によりモールドパッケージされる。制御チップ91、ハイサイド部92、ローサイド部93は、基板上に設けられ、それぞれボンディングワイヤや基板上の配線によって接続される。詳細には、制御チップ91は、出力ノード110として機能するボンディングワイヤを介してハイサイド部92に接続され、出力ノード120として機能するボンディングワイヤを介してローサイド部93に接続される。又、制御チップ91は、第1電源電圧VDDや接地電圧GNDが供給される外部端子や、入力ノード230として機能する外部端子に接続される。ハイサイド部92は、第3電源電圧VHが供給される外部端子や、出力ノード53として機能する外部端子に接続される。ローサイド部93は、接地電圧GNDが供給される外部端子や、出力ノード53として機能する外部端子に接続される。ハイサイドトランジスタ21の方がローサイドトランジスタ22に比べオン状態となるデューティ比(オンデューティ)が低いため、ローサイドトランジスタ22に比べると相対的にオン抵抗による損失が小さく、スイッチング損失の割合が高くなる。このため、ハイサイドトランジスタ21のオン抵抗を低減するよりもスイッチング時間を短くする方が電力損失の削減に有効である。従って、ハイサイド部92は、ゲート入力容量を小さくするためにローサイド部93よりも小さいチップを用いることが望ましい。

【0098】

図18は、第2の実施の形態における電力変換回路を1つのパッケージに実装した場合の構成例を示す図である。図18を参照して、本発明に係るパッケージ(SiP)は、図12に示すゲート駆動回路1を含む制御チップ91、ハイサイドトランジスタ21を含むハイサイド部92、ローサイドトランジスタ22を含むローサイド部を具備し、制御チップ91、ハイサイド部92、ローサイド部93は樹脂によりモールドパッケージされる。制御チップ91、ハイサイド部92、ローサイド部93は、基板上に設けられ、それぞれボンディングワイヤや基板上の配線によって接続される。詳細には、制御チップ91は、出力ノード110として機能するボンディングワイヤを介してハイサイド部92に接続され、出力ノード120として機能するボンディングワイヤを介してローサイド部93に接続される。又、制御チップ91は、第1電源電圧VDDや接地電圧GNDが供給される外部端子や、入力ノード230として機能する外部端子に接続される。更に、制御チップ91は、第3電源電圧VHが供給される外部端子とハイサイド部92との間を、ボンディングワイヤを介して接続される。ハイサイド部92は、制御チップ91を介して第3電源電圧VHが供給される外部端子に接続されるとともに、出力ノード53として機能する外部端子に接続される。ローサイド部93は、接地電圧GNDが供給される外部端子や、出力ノード53として機能する外部端子に接続される。又、図17と同様に、ハイサイド部92は、ゲート入力容量を小さくするためにローサイド部93よりも小さいチップを用いることが望ましい。

【0099】

本発明による電力変換回路は、SiPのようにパッケージ化しても実現できるが、SOI構造により1チップ化しても構わない。この場合、ゲート駆動回路1、ハイサイドトランジスタ21、ローサイドトランジスタ22は、STIにより絶縁分離される。

【0100】

以上のように本発明によるゲート駆動回路1は、負電圧(第2電源電圧VNEG)が規定のレベルに達していなければ、電源投入時に限らずシステム電源の遮断時や、負電圧源の故障等によっても、ハイサイドトランジスタ21への第3電源電圧VHの供給を遮断する。これにより、第3電源電圧VHに起因する貫通電流を防止し、負荷50やハイサイドトランジスタ21及びローサイドトランジスタ22の破壊を防ぐことが可能となる。本発明によれば、負電圧(第2電源電圧VNEG)が不安定なときでも貫通電流を防止できるため、電力変換回路として機能するブリッジ回路のスイッチ素子として、ノーマリオン型のパワートランジスタ、特にFigure Of Merit(FOM)の優れたノーマリオン型のGaNトランジスタを利用することが可能となる。

【0101】

特に、第2の実施の形態におけるゲート駆動回路1では、ブリッジ回路のスイッチング素子とは別に設けられた電源制御スイッチ46により、ハイサイドトランジスタ21への第3電源電圧VHの供給を制御している。このため、PWM信号によるスイッチング動作を行うハイサイドトランジスタ21とローサイドトランジスタ22の両方に、FOMの優れたノーマリオン型のGaNトランジスタを使用できる。この結果、電力変換回路におけるスイッチング素子は低抵抗かつ高速スイッチングが可能となり、オン抵抗による損失とスイッチング損失の両方を小さくすることが可能となる。

【0102】

以上、本発明の実施の形態を詳述してきたが、具体的な構成は上記実施の形態に限られるものではなく、本発明の要旨を逸脱しない範囲の変更があっても本発明に含まれる。

【0103】

第1及び第2の実施の形態では、キャリアの移動度が高く低抵抗で電力損失が小さいことから、ハイサイドトランジスタ21及びローサイドトランジスタ22としてNチャネル型トランジスタを好適に利用している。しかし、ハイサイドトランジスタ21及びローサイドトランジスタ22の少なくとも一方にPチャネル型トランジスタを利用しても構わない。ハイサイドトランジスタ21にPチャネル型トランジスタを利用する場合、貫通電流を遮断するために出力される駆動制御信号GHの信号レベルは、上述の実施の形態に対し反転することは言うまでもない。又、電源制御スイッチ46もNチャネル型トランジスタ、Pチャネル型トランジスタ、あるいはPNPバイポーラトランジスタのいずれを利用しても構わない。

【0104】

第1の実施の形態において、第2電源電圧VNEGに応じてオフ状態とする対象は、ノーマリオフ型トランジスタとは限らずノーマリオン型トランジスタでも良い。すなわち、図3に示すハイサイドトランジスタ21としてノーマリオン型トランジスタ(例えばノーマリオン型GaNトランジスタ)が利用されても良い。この場合、駆動回路11は、駆動回路12と同様に、第1電源電圧VDDと負電圧源30から供給される第2電源電圧VNEG(負電圧)とに応じて動作する。負電圧検出回路41は、ハイサイドの駆動回路11に供給される第2電源電圧VNEGと参照電圧Vrefとの比較結果に応じた駆動制御信号RDYをハイサイドの選択演算回路42に出力する。これにより、ハイサイドの駆動回路11に供給される負電圧が規定のレベルに達しない場合、ハイサイドトランジスタ21を強制的にオフ状態にすることができる。ここで、負電圧源30や負電圧検出回路41として、ハイサイド、ローサイドに共通な負電圧源や負電圧検出回路が設けられても良いし、ハイサイド、ローサイドのそれぞれに個別の負電圧源や負電圧検出回路が設けられても良い。又、ハイサイドのみに負電圧源30、負電圧検出回路41及び選択演算回路42が設けられても良い。

【0105】

上述の実施の形態では、駆動回路11、12、46は反転出力しているがこれに限らず、正論理のゲートドライバが用いられても良い。この場合、駆動回路11、12、46を制御する論理ゲートは、実施の形態で示した論理の反転出力を駆動回路11、12、46に入力する論理ゲートに置換されることは言うまでもない。

【符号の説明】

【0106】

1 :ゲート駆動回路

11、12:駆動回路

21:ハイサイドトランジスタ

22:ローサイドトランジスタ

30、30−1、30−2:負電圧源

31、32:デッドタイム回路

40:制御回路

41、41−1、41−2:負電圧検出回路

42、44、47、48:選択演算回路

45:スイッチ制御回路

46:電源制御スイッチ

50:負荷

51、52:入力ノード

53、53−1〜53−3:の出力ノード

60、62:ハーフブリッジ

61−1〜61−3、63−1〜63−3:ハーフブリッジ

91:制御チップ

92:ハイサイド部

93:ローサイド部

110、120、310、 310−1、310−2、320:出力ノード

230、231、420、430:入力ノード

410、410−1、410−2:出力ノード

411、412:抵抗

413、414:P型MOSトランジスタ

415:コンパレータ

440:参照電圧生成回路

【技術分野】

【0001】

本発明は、ゲート駆動回路に関し、特に電力変換装置のスイッチング素子として機能するトランジスタのゲートを駆動するゲート駆動回路、これを備える電力変換装置、及びゲート駆動方法に関する。

【背景技術】

【0002】

従来の電力制御回路では、電力変換を制御するスイッチング素子として、パワーMOSFET(Metal−Oxide−Semiconductor Field−Effect Transistor)又は絶縁ゲートバイポーラトランジスタ(IGBT:Insulated Gate Bipolar Transistor)が用いられている。一方、近年スイッチング速度が高速なことから窒化ガリウム(GaN)を用いたパワーMOSFET(以下、GaNトランジスタと称す)が注目されている。GaNトランジスタは、閾値電圧Vthの大きさに応じてノーマリオン型とノーマリオフ型の2種類がある。詳細には、ノーマリオン型トランジスタの閾値電圧Vthは0より低く、ゲート電圧とソース電圧が同電位の場合にオン状態となる。ノーマリオフ型トランジスタの閾値電圧Vthは0より高く、ゲート電圧とソース電圧が同電位の場合にオフ状態になる。

【0003】

GaNの場合、ノーマリオン型トランジスタは、ノーマリオフ型トランジスタに比べてスイッチング性能に優れる。例えば、ノーマリオン型トランジスタは、ノーマリオフ型トランジスタよりも少ないゲート容量であるとともにオン抵抗を低くすることができ、高速スイッチング動作を実現できる。ただし、ノーマリオン型トランジスタをオフ状態にするためには、ゲートに接地電位(0V)よりも低い負電圧を供給する必要がある。このため、ノーマリオン型トランジスタを駆動する場合、チャージポンプなどを用いて負電圧を生成する回路(以下、負電圧源と称す)を用意する必要がある。

【0004】

ノーマリオン型トランジスタをスイッチング素子として利用した半導体装置の一例が、特開2011−101217に記載されている(特許文献1参照)。特許文献1には、負電圧源に応じてノーマリオン型GaNトランジスタのゲートを駆動するハイサイド駆動部を備える半導体装置が記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−101217

【発明の概要】

【発明が解決しようとする課題】

【0006】

ノーマリオン型トランジスタはスイッチング性能に優れるが、ゲートに供給される負電圧が不安定な場合、オン状態となることがある。

【0007】

図1は、発明者によって想定された電力変換回路の構成を示す図である。ここで発明者は、ハイサイドトランジスタ及びローサイドトランジスタとしてノーマリオン型のN型パワートランジスタを利用することを想定した。図1に示す電力変換回路は、ゲート駆動回路101、102、ハーフブリッジ回路のスイッチング素子として機能するハイサイドトランジスタ201及びローサイドトランジスタ202、負電圧源301、302を具備する。

【0008】

ゲート駆動回路101は、入力信号501(PWM信号:Pulse Width Modulation)の反転信号を反転した出力信号によりハイサイドトランジスタ201のゲートを駆動する。ゲート駆動回路101は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源301から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備え、例えばCMOS(Complementary Metal Oxide Semiconductor)インバータが好適である。ゲート駆動回路102は、入力信号502(PWM信号)の反転信号を反転した出力信号によりローサイドトランジスタ202のゲートを駆動する。ゲート駆動回路102は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備え、例えばCMOSインバータが好適である。

【0009】

ハイサイドトランジスタ201のドレインには、図示しない電源から第3電源電圧VHが供給され、ソースは出力端子を介してローサイドトランジスタ202のドレインに接続される。ローサイドトランジスタ202のソースは接地され、ドレインは出力端子を介してハイサイドトランジスタ201のソースに接続される。出力端子は、負荷500に接続される。

【0010】

以上のような構成から、ハイサイドトランジスタ201及びローサイドトランジスタ202は、ゲートに供給される電圧に応じたスイッチング動作により、第3電源電圧VHと接地電圧GNDに応じた出力を負荷500に出力する。

【0011】

図1に示す電力変換回路では、ノーマリオン型のハイサイドトランジスタ201を駆動するため、負電圧源301からゲート駆動回路101に対し接地電位よりも低い負電圧(第2電源電圧VNEG)が供給される。同様にノーマリオン型のローサイドトランジスタ202を駆動するため、負電圧源302からゲート駆動回路102に対し負電圧(第2電源電圧VNEG)が供給される。例えば、第2電源電圧VNEGは、負電圧源301、302において、第1電源電圧VDDに応じて生成されるため、第1電源電圧VDDが不安定な期間中、第2電源電圧VNEGも不安定な値を示す。例えば、電源を投入した直後や、制御回路の電源を遮断したとき等、第2電源電圧VNEGは安定して生成されない。

【0012】

図2は、図1に示す電力変換回路における電源投入時の第1電源電圧VDD、第2電源電圧VNEG、及びスイッチング素子(ハイサイドトランジスタ201及びローサイドトランジスタ202)に流れる貫通電流Iの関係を示すタイミングチャートである。図2を参照して、時刻T1に電源が投入されてから時刻T2までの間、第1電源電圧VDDは不安定な値を示しながら所定の値となるまで上昇する。この間、負電圧源301、302は、第1電源電圧VDDが所定のレベルに達していないため動作せず、第2電源電圧VNEGは0Vを示す。このため、ノーマリオン型のハイサイドトランジスタ201、ローサイドトランジスタ202はともにオン状態となる。時刻T1から時刻T2までの間、ハイサイドトランジスタ201に供給される第3電源電圧VHは、第1電源電圧VDDの上昇に伴い増加するため、第3電源電圧VHによる貫通電流Iが、ハイサイドトランジスタ201及びローサイドトランジスタ202を介して流れ始める。

【0013】

時刻T2において、第1電源電圧VDDが所定の値に安定すると、負電圧源301、302は動作を開始し、第2電源電圧VNEG(負電圧)は低下し始める。しかし、第2電源電圧VNEGが、所定の値に安定する時刻T3までの間、ノーマリオン型のハイサイドトランジスタ201及びローサイドトランジスタ202がともにオン状態となる場合がある。この場合、第3電源電圧VHによる貫通電流Iが、ハイサイドトランジスタ201及びローサイドトランジスタ202を介して流れてしまう。

【0014】

以上のように、図1に示す電力変換回路において、第2電源電圧VNEG(負電圧)が十分に生成されていないタイミングでは、ハイサイドトランジスタ201とローサイドトランジスタ202の両方がオン状態になってしまい、大きな貫通電流が流れる場合がある。この貫通電流によって、電力変換回路の出力電圧Voutは不定になるため、負荷500が破壊される恐れがある。又、N型パワートランジスタ201、202も巨大な貫通電流による発熱で破壊する恐れがある。

【課題を解決するための手段】

【0015】

上記の課題を解決するために、本発明は、以下に述べられる手段を採用する。その手段を構成する技術的事項の記述には、[特許請求の範囲]の記載と[発明を実施するための形態]の記載との対応関係を明らかにするために、[発明を実施するための形態]で使用される番号・符号が付加されている。ただし、付加された番号・符号は、[特許請求の範囲]に記載されている発明の技術的範囲を限定的に解釈するために用いてはならない。

【0016】

本発明によるゲート駆動回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ(21)及びローサイドトランジスタ(22)のゲートを相補に駆動する2つの駆動回路(11、12)と制御回路(40)とを具備する。ハイサイドトランジスタ(21)とローサイドトランジスタ(22)の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路(11、12)の少なくとも一方は、低電位側の電源電圧として供給される第2電源電圧(VNEG)に応じた駆動電圧を、ノーマリオン型のトランジスタのゲートに出力する。ここで第2電源電圧(VNEG)は接地電圧(GND)よりも低い。制御回路(40)は、第2電源電圧(VNEG)が予め設定された目標電圧よりも高い場合、ハイサイドトランジスタ(21)に流れるドレイン電流を遮断する。

【0017】

他の観点において、本発明によるゲート駆動方法は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ(21)及びローサイドトランジスタ(22)のゲートを相補に駆動する2つの駆動回路を具備するゲート駆動回路(11、12)のゲート駆動方法である。本発明によるゲート駆動方法は、2つの駆動回路(11、12)の少なくとも一方に対する低電位側の電源電圧として供給される、接地電位(GND)より低い電源電圧(VNEG)が目標電圧よりも高い場合、ハイサイドトランジスタ(21)に流れるドレイン電流を遮断するステップとを具備する。

【発明の効果】

【0018】

本発明によれば、電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制することができる。

【図面の簡単な説明】

【0019】

【図1】図1は、発明者が想定した電力変換回路の構成を示す図である。

【図2】図2は、図1に示す電力変換回路における電源投入時の電源電圧、負電圧、及びスイッチング素子に流れる貫通電流の関係を示すタイミングチャートである。

【図3】図3は、本発明によるゲート駆動回路の第1の実施の形態における構成を示す図である。

【図4A】図4Aは、本発明に係る負電圧源の構成の一例を示す図である。

【図4B】図4Bは、本発明に係る負電圧源の構成の一例を示す図である。

【図4C】図4Cは、本発明に係る負電圧源の構成の一例を示す図である。

【図5】図5は、本発明に係る負電圧源に利用されるダイオードの構造の一例を示す図である。

【図6】図6は、本発明に係る負電圧検出回路の構成の一例を示す図である。

【図7】図7は、本発明によるゲート駆動回路の第1の実施の形態における動作を示すタイミングチャートである。

【図8】図8は、第1の実施の形態におけるゲート駆動回路を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。

【図9】図9は、図8に示すマルチフェーズスイッチング電源に搭載されるフェーズICの構成の一例を示す図である。

【図10】図10は、第1の実施の形態におけるゲート駆動回路を利用した3相インバータの構成の一例を示す図である。

【図11】図11は、図10に示す3相インバータに搭載されるフェーズICの構成の一例を示す図である。

【図12】図12は、本発明によるゲート駆動回路の第2の実施の形態における構成を示す図である。

【図13】図13は、本発明によるゲート駆動回路の第2の実施の形態における動作を示すタイミングチャートである。

【図14】図14は、第2の実施の形態におけるゲート駆動回路を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。

【図15】図15は、図13に示すマルチフェーズスイッチング電源に搭載されるフェーズICの構成の一例を示す図である。

【図16】図16は、第2の実施の形態におけるゲート駆動回路を利用した3相インバータの構成の一例を示す図である。

【図17】図17は、第1の実施の形態における電力変換回路を搭載したSiPの構造の一例を示す図である。

【図18】図18は、本発明によるゲート駆動回路を適用したインバータの構成の一例を示す図である。

【発明を実施するための形態】

【0020】

以下、添付図面を参照しながら本発明の実施の形態を説明する。図面において同一、又は類似の参照符号は、同一、類似、又は等価な構成要素を示している。

【0021】

1.第1の実施の形態

図3から図11を参照して、第1の実施の形態におけるゲート駆動回路1を説明する。第1の実施の形態におけるゲート駆動回路1は、ノーマリオン型のローサイドトランジスタを駆動するための負電圧に応じて、ハイサイドトランジスタのゲート電圧を制御する。ゲート駆動回路1は、負電圧が所定の電圧に達するまで、ハイサイドトランジスタをオフ状態とすることでハイサイドトランジスタのドレイン電流を遮断する。これにより、負電圧が不安定な期間において、ハーフブリッジ回路を構成するスイッチング素子(ハイサイドトランジスタ及びローサイドトランジスタ)への貫通電流を抑制する。

(構成)

以下、図3から図6を参照して、第1の実施の形態におけるゲート駆動回路1の構成の詳細を説明する。図3は、本発明による電力変換回路の第1の実施の形態における構成を示す図である。図3を参照して、第1の実施の形態における電力変換回路は、ゲート駆動回路1と、ハーフブリッジ回路のスイッチング素子として機能し、負荷50に接続されるハイサイドトランジスタ21及びローサイドトランジスタ22を具備する。第1の実施の形態におけるゲート駆動回路1は、駆動回路11、12、負電圧源30、制御回路40を具備し、ハイサイドトランジスタ21及びローサイドトランジスタ22を駆動する。図3に示す一例では、負電圧(第2電源電圧VNEG)が目標電圧よりも高く、不安定な期間中、ゲート電圧を制御することにより強制的にオフ状態に制御可能であることから、ハイサイドトランジスタ21としてノーマリオフ型のNチャネル型GaNトランジスタが好適に利用される。又、スイッチング性能の観点からローサイドトランジスタ22としてノーマリオン型のNチャネル型GaNトランジスタが好適に利用される。

【0022】

ハイサイドトランジスタ21のドレインには、図示しない電源から第3電源電圧VHが供給され、ソースは出力ノード53を介してローサイドトランジスタ22のドレインに接続される。ローサイドトランジスタ22のソースは接地され、ドレインは出力ノード53を介してハイサイドトランジスタ21のソースに接続される。出力ノード53は、負荷50に接続される。

【0023】

駆動回路11は、制御回路40から入力ノード420に出力された信号に応じて、ハイサイドトランジスタ21のゲートを駆動する。駆動回路11の入力ノードは制御回路40に接続され、出力ノード110は、ハイサイドトランジスタ21のゲートに接続される。駆動回路11は、図示しない電源から供給される第1電源電圧VDDを高位側の電源電圧とし、接地電圧を低位側の電源電圧として動作するトーテムポール回路を備える。図3に示す一例では、駆動回路11はCMOS(Complementary Metal Oxide Semiconductor)インバータであり、入力される信号の反転信号を、ゲート駆動信号GHとしてハイサイドトランジスタ21のゲートに出力する。駆動回路12は、制御回路40から入力ノード420に出力された信号に応じて、ローサイドトランジスタ22のゲートを駆動する。駆動回路11の入力ノードは、制御回路40に接続され、出力ノード120は、ローサイドトランジスタ22のゲートに接続される。駆動回路12は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源30から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備える。図3に示す一例では、駆動回路12はCMOSインバータであり、入力される信号の反転信号を、ゲート駆動信号GLとしてローサイドトランジスタ22のゲートに出力する。尚、駆動回路12に供給される高電位側の電源電圧は第1電源電圧VDDに限らず、ノーマリオン型トランジスタをオン状態とできる電圧であれば任意に設定できる。

【0024】

負電圧源30は、接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)を生成する。図4A〜図4Dのそれぞれは、負電圧源30の構成の一例を示す図である。負電圧源30は、例えば、図4Aに示す降圧型チャージポンプによって構成される。図4Aに示す負電圧源には、クロックパルス信号φ1が入力される。図4Aを参照して、ハイレベルのクロックパルス信号φ1により、容量Cin及びダイオードD10を介してGNDに電流が流れ、容量Cinに電荷がチャージされる。続くローレベルのクロックパルス信号φ1により、GNDから容量Cout、ダイオードD20、容量Cinを介して入力側に電流が流れ、容量Cinにチャージされた電荷が容量Cinにチャージされる。これにより、容量CoutとダイオードD20との接続ノード(出力ノード310)の電圧が接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)となる。

【0025】

負電圧源30は、図4Bに示すディクソン型チャージポンプによっても実現できる。図4Bに示す負電圧源30には、相互に相補のクロックパルス信号φ10、φ20が入力される。クロックパルス信号φ10がローレベル、クロックパルス信号φ20がハイレベルの期間、ダイオードD2、D4が導通状態となり、ダイオードD1、D3が遮断状態となる(1)。これにより容量C1、C3に電荷がチャージされる。クロックパルス信号φ10がハイレベル、クロックパルスφ20がローレベルの期間、ダイオードD1、D3が導通状態となり、ダイオードD2、D4が遮断状態となる(2)。これにより、容量C2、C4に電荷がチャージされる。この際、容量C1、C3にチャージされた電荷が容量C2、C4にチャージされる。上記(1)、(2)を繰り返すことにより、容量Coutには、容量C4にチャージされた電荷がチャージされ、容量CoutとダイオードD5との接続ノード(出力ノード310)の電圧が、接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)となる。

【0026】

負電圧源30は、図4Cに示す降圧型チョッパ回路によっても実現できる。図4Cを参照して、負電圧源30に入力されるクロックパルス信号φ2に応じてスイッチS1がオンすると、第1電源(第1電源電圧VDD)からチョークコイルLを介して接地端子(GND)側へ電流が流れ、チョークコイルLにエネルギーが蓄えられる。続いてクロックパルス信号φ2に応じてスイッチS1がオフ状態となると、チョークコイルLに蓄えられたエネルギーにより出力ノード310から接地端子(GND)側に電流が流れ、出力ノード310は接地電圧GNDよりも低い負電圧(第2電源電圧VNEG)に降圧する。

【0027】

図5は、本発明に係る負電圧源30に利用されるダイオードの構造の一例を示す図である。上述のように負電圧(第2電源電圧VNEG)を生成するためには、ダイオードが重要な構成部品となる。ダイオードを集積回路上で実現することが求められる。しかし、通常の基板では、P−sub基板がGNDに接続されているため、接地電圧GNDよりも低い電位のN−wellまたはN+拡散層をP−sub基板上に作ることができない。例えば、順方向のPN接合により、接地電圧GNDよりも低い電位のN−well又はN+拡散層には接地電圧GNDが供給される。このため、本発明では、ダブルウェル、トリプルウェル、ディープNウェル、SOI基板の何れかを使用可能なプロセスを利用することで、負電圧源30で用いられるダイオードを集積回路上で実現することが好ましい。

【0028】

例えば、図5に示すように、トリプルウェル構造により、第1電源電圧VDDが供給されたN−well N1によって逆バイアスされた寄生ダイオードD40が形成されることで、N+拡散層N2及びP−well P2によって形成されるダイオードD50と接地電圧GNDが供給されるP−sub P1との間が絶縁される。詳細には、GNDに接続されたP−sub P1上にN−wellN1、N−well N1上にP−well P2、P−well P2上にN+拡散層N2が形成され、N−well N1に第1電源電圧VDDが供給され、P−well P2にアノード端子、N+拡散層N2にカソード端子が接続される。このような構成により、N−well N1とP−well P2との間に逆バイアスされた寄生ダイオードD40が形成され、N+拡散層N2及びP−well P2によって形成されるダイオードD50と接地電圧GNDが供給されるP−sub P1との間が絶縁される。このような構造により、負電圧源に利用可能なダイオードD50を形成することが可能となる。

【0029】

ウェルの層数が図5に示す一例と同じ又は多い場合や、N−基板にダブルウェルが形成されたプロセスを用いる場合、すなわち多層ウェル構造を利用することで、N−wellとP+拡散層の間で負電圧源30に利用するダイオードを構成することも可能である。又、トランジスタのボディを基板から絶縁できるSOI基板を利用することで、トランジスタのボディとなるP−sub、N−subと、N+拡散層、P+拡散層の組み合わせによって負電圧源30に利用するダイオードを形成することが可能となる。尚、通常プロセスによるPN接合ダイオードや、ショットキーダイオード等を負電圧源30に利用しても構わない。

【0030】

負電圧源30は、図4A〜図4Cの様に構成できるが、安定的な第2電源電圧VNEGが供給できれば、その構成はこれに限らない。

【0031】

制御回路40は、負電圧検出回路41、選択演算回路42、43を具備する。負電圧検出回路41は、負電圧源30とローサイドトランジスタ22との接続ノード(出力ノード310)に接続される。負電圧検出回路41は、出力ノード310から供給される第2電源電圧VNEGが所望の値となっているかを監視し、監視結果に応じた信号レベル(論理値)の駆動制御信号RDYを、出力ノード410を介して選択演算回路42、43に出力する。詳細には、負電圧検出回路41は、第2電源電圧VNEGが予め設定された目標電圧よりも高いか否かを監視し、第2電源電圧VNEGが目標電圧より高い場合、ローレベル“0”の駆動制御信号RDYを出力し、第2電源電圧VNEGが目標電圧よりも低い場合、ハイレベル“1”の駆動制御信号RDYを出力する。

【0032】

図6は、本発明に係る負電圧検出回路41の構成の一例を示す図である。図6に示す負電圧検出回路41は、抵抗411、412、P型MOSトランジスタ413、414、コンパレータ415を具備する。抵抗411の一端には第1電源電圧VDDが供給され、他端はP型MOSトランジスタ413のドレイン及びコンパレータ415の反転入力端子に接続される。抵抗412の一端には第1電源電圧VDDが供給され、他端はP型MOSトランジスタ414のドレイン及びコンパレータ415の非反転入力端子に接続される。P型MOSトランジスタ413のゲートは接地され、ソースは負電圧源30の出力ノード310に接続される。P型MOSトランジスタ414のゲートは参照電圧生成回路440の出力ノード320に接続され、ソースは接地される。参照電圧生成回路440は参照電圧Vrefを出力ノード320に出力する。ここで参照電圧Vrefに−1を乗じた値“−Vref”は接地電圧GNDより低く、第2電源電圧VNEGに対して規定された所望の値(ここでは目標電圧)に設定される。

【0033】

図6に示す負電圧検出回路41では、接地電圧GNDから第2電源電圧VNEGを減じた値が、参照電圧Vrefから接地電圧GNDを減じた値よりも大きいとき、すなわち、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなると、抵抗411を流れる電流I1が抵抗412を流れる電流I2よりも大きくなる。この場合、反転入力端子の電圧V1が非反転入力端子の電圧V2よりも小さくなるため、コンパレータ415は出力ノード410にハイレベル“1”の駆動制御信号RDYを出力する。一方、接地電圧GNDから第2電源電圧VNEGを減じた値が、参照電圧Vrefから接地電圧GNDを減じた値よりも小さいとき、すなわち、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも高い場合、電流I1が電流I2よりも小さくなる。この場合、反転入力端子の電圧V1が非反転入力端子の電圧V2よりも大きくなるため、コンパレータ415は出力ノード410にローレベル“0”の駆動制御信号RDYを出力する。

【0034】

負電圧検出回路41は、図6の様に第2電源電圧VNEGと参照電圧Vrefとを比較する比較回路によって構成できるが、第2電源電圧VNEGが所定のレベル(目標電圧)に達したか否かを検出しその検出結果を駆動制御信号RDYとして出力できれば、その構成はこれに限らない。例えば、トランジスタの閾値電圧Vthやダイオードの順電圧VFを目標電圧として第2電源電圧VNEGの値を監視してもよい。又、上述の例では、参照電圧Vrefに−1を乗じた値“−Vref”を目標電圧としたがこれに限らない。例えば、第2電源電圧VNEGに基づいて生成された電圧(例えば分圧抵抗による分圧電圧)と参照電圧Vrefとを比較した結果に応じて、第2電源電圧VNEGが目標電圧以下となったか否かを検出する方法を負電圧検出回路41に採用しても構わない。

【0035】

選択演算回路42は、入力ノード51から入力されるPWM信号(入力信号GHIN)と、負電圧検出回路41から入力される駆動制御信号RDYとの論理演算結果を、駆動回路11の入力ノード420に出力する。ここでは、選択演算回路42はNANDゲートが好適に利用され、入力信号GHINと駆動制御信号RDY(のそれぞれが示す論理値)の否定論理積を入力ノード420に出力する。すなわち、選択演算回路42は、駆動制御信号RDYがローレベルレベル“0”のとき、入力信号GHINがいかなる値であってもハイレベル“1”の演算結果を入力ノード420(駆動回路11)に出力する。一方、選択演算回路42は、駆動制御信号RDYがハイレベルレベル“1”のとき、入力信号GHINが示す論理レベルに対応する論理レベルの演算結果を入力ノード420(駆動回路11)に出力する。ここでは入力信号GHINがハイレベル“1”のときローレベル“0”の演算結果が出力され、入力信号GHINがローレベル“0”のときハイレベル“1”の演算結果が出力される。同様に選択演算回路42は、入力ノード52から入力されるPWM信号(入力信号GLIN)と、負電圧検出回路41から入力される駆動制御信号RDYとの論理演算結果を、駆動回路12の入力ノード430に出力する。ここでは、選択演算回路42はNANDゲートが好適に利用され、入力信号GLINと駆動制御信号RDY(のそれぞれが示す論理値)の否定論理積を入力ノード430に出力する。すなわち、選択演算回路42は、駆動制御信号RDYがローレベルレベル“0”のとき、入力信号GLINがいかなる値であってもハイレベル“1”の演算結果を入力ノード430(駆動回路12)に出力する。一方、選択演算回路42は、駆動制御信号RDYがハイレベルレベル“1”のとき、入力信号GLINが示す論理レベルに対応する論理レベルの演算結果を入力ノード430(駆動回路12)に出力する。ここでは入力信号GLINがハイレベル“1”のときローレベル“0”の演算結果が出力され、入力信号GLINがローレベル“0”のときハイレベル“1”の演算結果が出力される。

【0036】

以上のような構成により、第1の実施の形態における制御回路40は、目標電圧よりも第2電源電圧VNEGが高い場合、入力信号GHIN、GLINに関わらずハイレベル“1”の出力信号を駆動回路11、12に出力し、目標電圧よりも第2電源電圧VNEGが低い場合、入力信号GHIN、GLINに応じた論理レベルの出力信号を駆動回路11、12に出力する。尚、入力ノード51、52に入力される入力信号GHINと入力信号GLINは互いに相補な信号であることが一般的に多い。

【0037】

駆動回路11は入力される信号を反転してハイサイドトランジスタ21に出力する。例えば、目標電圧よりも第2電源電圧VNEGが高い場合、制御回路40から入力されるハイレベルの信号を反転したローレベルのゲート駆動信号GHをハイサイドトランジスタ21に出力する。ハイサイドトランジスタ21は、Nチャネル型のノーマリオフ型トランジスタであるため、駆動回路11から出力されるローレベルのゲート駆動信号GHによって強制的にオフ状態となる。本実施の形態では、駆動回路12に供給される第2電源電圧VNEGが所定の値(目標電圧)に達するまでの間、ノーマリオフ型のハイサイドトランジスタ21を強制的にオフ状態としている。これにより、第3電源電圧VHに起因する貫通電流の発生を防止することができる。

【0038】

(動作)

次に図3及び図7を参照して、第1の実施の形態におけるゲート駆動回路1の動作を説明する。図7は、本発明によるゲート駆動回路の第1の実施の形態における動作を示すタイミングチャートである。

【0039】

図7を参照して、時刻T1に電力変換回路を含む半導体装置全体の電源(システム電源)が投入されてから時刻T2までの間、第1電源電圧VDDは不安定な値を示しながら所定の値となるまで上昇する。この間、負電圧源30は、第1電源電圧VDDが所定のレベルに達していないため動作せず、第2電源電圧VNEGは0Vを示す。負電圧検出回路41は、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも高い0Vであるため、ローレベル“0”の駆動制御信号RDYを出力ノード410に出力する。これにより、駆動回路11は、入力信号GHIN、GLINの値に関わらずローレベル“0”のゲート駆動信号GHを出力ノード110(ハイサイドトランジスタ21のゲート)に供給し、ハイサイドトランジスタ21を強制的にオフ状態とする。

【0040】

時刻T2において、第1電源電圧VDDが所定の値に安定すると、負電圧源30は動作を開始し、第2電源電圧VNEG(負電圧)は低下し始める。時刻T2から、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなる時刻T3までの間、負電圧検出回路41は、ローレベル“0”の駆動制御信号RDYを出力ノード410に出力する。これにより、駆動回路11は、入力信号GHINの値に関わらず、出力ノード110(ハイサイドトランジスタ21のゲート)にローレベル“0”のゲート駆動信号GHを供給し、ハイサイドトランジスタ21を強制的にオフ状態とする。一方、時刻T2から時刻T3の期間中、第2電源電圧VNEGは参照電圧に−1を乗じた値“−Vref”より高く不安定な値を示すため、駆動回路12から、出力ノード120(ローサイドトランジスタ22のゲート)に供給されるゲート駆動信号GLは不安定な値を示す。このため、ローサイドトランジスタ22のオン/オフの状態は不定となる場合がある。

【0041】

本実施の形態におけるゲート駆動回路1では、システム電源(第1電源電圧VDD)が投入される時刻T1から、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”を下回る時刻T3までの期間、制御回路40によってノーマリオフ型のハイサイドトランジスタ21を強制的にオフ状態としている。この結果、第3電源電圧VHを供給する電源と出力ノード53(負荷50)との電気的接続が遮断され、第3電源電圧VHに起因したハーフブリッジ回路におけるスイッチング素子(ハイサイドトランジスタ21、ローサイドトランジスタ22)への貫通電流が阻止される。

【0042】

時刻T3以降、第2電源電圧VNEGが参照電圧Vrefに−1を乗じた値“−Vref”より低くなるため、負電圧検出回路41は、ハイレベル“1”の駆動制御信号RDYを出力する。これにより、駆動回路11、12は、入力信号GHIN、GLINの信号レベルに応じた信号レベルのゲート駆動信号GH、GLを出力する通常動作モードに移行する。

【0043】

第1の実施の形態では、ローサイドトランジスタ22としてスイッチング性能が良好なノーマリオン型のGaNトランジスタを用いている。このため、ローサイドトランジスタ22のゲート駆動する駆動回路12には、システム電源投入時等にその値が不安定となる第2電源電圧VNEG(負電圧)が供給される。第2電源電圧VNEGが不安定である場合、特に、第2電源電圧VNEGが規定の電圧(目標電圧以下)まで低下していない場合、ローサイドトランジスタ22はオフ状態とならない。本実施の形態におけるゲート駆動回路は、第2電源電圧VNEGが規定の電圧(目標電圧、ここでは“−Vref”)に達するまでハイサイドトランジスタ21を強制的にオフ状態とする。このため、第2電源電圧VNEGが不安定な期間においても第3電源電圧VHに起因したスイッチング素子(ハイサイドトランジスタ21、ローサイドトランジスタ22)への貫通電流を防止することができる。又、第2電源電圧VNEGが規定の電圧(目標電圧、ここでは“−Vref”)に達した場合、ゲート駆動回路1は、入力信号GHIN、GLINに応じて、ハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御することが可能となる。この際、ゲート駆動回路は、ゲート駆動信号GH、GLがハイレベルになることを許可する。

【0044】

(ゲート駆動回路の適用例)

図8は、第1の実施の形態におけるゲート駆動回路1を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。図8に示すマルチフェーズスイッチング電源は、並列接続された複数のスイッチング電源60と、複数のハーフブリッジ60のそれぞれに搭載されたフェーズIC23を制御する制御IC70を具備する。複数のハーフブリッジ60のそれぞれは、負荷50とともにハーフブリッジ回路を構成するスイッチング素子として機能するハイサイドトランジスタ21及びローサイドトランジスタ22と、そのスイッチング動作を制御するフェーズIC23を備える。複数のハーフブリッジ60のそれぞれのハイサイドトランジスタ21及びローサイドトランジスタ22は、第3電源(第3電源電圧VH)とGND(接地電圧GND)との間に設けられ、それぞれの出力ノード53は共通接続される。

【0045】

フェーズIC23は、出力ノード110を介してハイサイドトランジスタ21のゲートに接続され、出力ノード120を介してローサイドトランジスタ22のゲートに接続される。又、フェーズIC23は入力ノード230、231を介して制御IC70に接続される。図9は、図8に示すマルチフェーズスイッチング電源に搭載されるフェーズIC23の構成の一例を示す図である。

【0046】

図9を参照して、フェーズIC23は、図3に示すゲート駆動回路1、デッドタイム回路31、32を備える。制御IC70は、入力ノード230を介してゲート駆動回路1にPWM信号を出力する。この際、PWM信号は、デッドタイム回路31、32を介して入力ノード51、52に入力される。これにより、入力ノード51、52に入力される入力信号GHIN、GLINは、デッドタイムを含むPWM信号となる。又、デッドタイム回路32に入力されるPWM信号は反転されるため、入力ノード51、52に入力される入力信号GHIN、GLINは相互に相補な関係となる。

【0047】

ゲート駆動回路1は、入力信号GHIN、GLINに応じたゲート駆動信号GH、GLを出力することで、ハーフブリッジ回路のスイッチング素子であるハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御する。ここで、負電圧源30から供給される第2電源電圧VNEGが目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”)よりも高い場合、ゲート駆動回路1は、ハイサイドトランジスタ21をオフ状態とするゲート駆動信号GHを出力する。これにより、複数のハーフブリッジ60のそれぞれにおいて、第2電源電圧VNEGが目標電圧より高いときに発生する貫通電流を防止することができる。

【0048】

制御IC70は、入力ノード231を介してフェーズIC23に異常検出信号を出力する。異常検出信号は、例えば選択演算回路42に入力され、駆動回路11(ハイサイドトランジスタ21)の動作を制御する。詳細には、制御IC70は、スイッチング電源の出力ノード53の電圧を監視し、異常を検出するとローレベル“0”の異常検出信号をフェーズIC23(入力ノード231)に出力する。選択演算回路42は、ローレベル“0”の異常検出信号に応じてハイレベル“1”の出力信号を駆動回路11に出力する。これにより、駆動回路11は、ローレベル“0”のゲート駆動信号GHを出力し、ハイサイドトランジスタ21をオフ状態とする。すなわち、スイッチング電源の出力異常(例えば出力信号Voutが所定の値を超える)に応じて、フェーズIC23は、ハイサイドトランジスタ21をオフ状態とし、スイッチング電源の動作を停止する。

【0049】

尚、図8に示すマルチフェーズスイッチング電源では、ハーフブリッジ60毎(フェーズIC23毎)に負電圧源30が搭載されているが、これに限らず、複数のハーフブリッジ60に共通の負電圧源が設けられても良い。この場合、目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC23のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC23に共通の負電圧検出回路(図示なし)によって行われても良い。

【0050】

図8のように、図3に示すゲート駆動回路1をマルチフェーズスイッチング電源に利用することで、第2電源電圧VNEGが不安定な期間に複数のハーフブリッジのいずれかにおいて発生する貫通電流を防止することができる。

【0051】

図10は、第1の実施の形態におけるゲート駆動回路1を利用した3相インバータの構成の一例を示す図である。図10に示す三相インバータは、並列接続された複数のハーフブリッジ61−1〜61−3と、複数のハーフブリッジ61−1〜61−3のそれぞれに搭載されたフェーズIC24を制御する制御IC80を具備する。複数のハーフブリッジ61−1〜61−3のそれぞれは、負荷50とともにハーフブリッジ回路のスイッチング素子として機能するハイサイドトランジスタ21及びローサイドトランジスタ22と、そのスイッチング動作を制御するフェーズIC24を備える。複数のハーフブリッジ61−1〜61−3のそれぞれのハイサイドトランジスタ21及びローサイドトランジスタ22は、第3電源(第3電源電圧VH)とGND(接地電圧GND)との間に設けられる。ハーフブリッジ61−1〜61−3の出力ノード53−1〜53−3は、図示しない3相モータ(負荷50に相当)のu端子、v端子、w端子に接続される。図10に示す一例では、ハーフブリッジ61−1の出力ノード53−1はu端子に接続され、ハーフブリッジ61−2の出力ノード53−2はv端子に接続され、ハーフブリッジ61−3の出力ノード53−3はw端子に接続される。

【0052】

フェーズIC24は、出力ノード110を介してハイサイドトランジスタ21のゲートに接続され、出力ノード120を介してローサイドトランジスタ22のゲートに接続される。又、フェーズIC24は入力ノード230を介して制御IC80に接続される。図11は、図10に示す3相インバータに搭載されるフェーズIC24の構成の一例を示す図である。

【0053】

図11を参照して、フェーズIC24は、図3に示すゲート駆動回路1を備える。制御IC80は、入力ノード230を介してゲート駆動回路1にPWM信号を出力する。この際、PWM信号は、デッドタイム回路31、32を介して入力ノード51、52に入力される。これにより、入力ノード51、52に入力される入力信号GHIN、GLINは、デッドタイムを含むPWM信号となる。又、デッドタイム回路32に入力されるPWM信号は反転されるため、入力ノード51、52に入力される入力信号GHIN、GLINは相互に相補な関係となる。尚、制御IC80は、周辺機器やコンソールに接続されるマイコンに例示され、駆動系の第1電源電圧VDDより低い電源電圧を高位側の電源とし、接地電圧GNDと異なる電源電圧を低位側の電源として動作する。この場合、PWM信号はレベルシフタ(図示なし)を介してフェーズICに入力される。

【0054】

ゲート駆動回路1は、入力信号GHIN、GLINに応じたゲート駆動信号GH、GLを出力することで、ハーフブリッジ回路のスイッチング素子であるハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御する。ここで、負電圧源30から供給される第2電源電圧VNEGが目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”)よりも高い場合、ゲート駆動回路1は、ハイサイドトランジスタ21をオフ状態とするゲート駆動信号GHを出力する。これにより、複数のハーフブリッジ61−1〜61−3のいずれかにおいて、第2電源電圧VNEGが目標電圧より高い値となるときに発生する貫通電流や、これによるモータの破壊を防止することができる。

【0055】

尚、図10に示す3相インバータでは、ハーフブリッジ61毎(フェーズIC24毎)に負電圧源30が搭載されているが、これに限らず、複数のハーフブリッジ61−1、61−2、61−3に共通の負電圧源が設けられても良い。この場合、目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC24のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC24に共通の負電圧検出回路(図示なし)によって行われても良い。

【0056】

又、ハイサイドトランジスタ21を駆動する駆動回路11は、低位側電源電圧として接地電圧GNDが供給される接地端子ではなく、出力ノード53−1〜53−3のうち、対応する出力ノード53に接続されても構わない。この場合、出力ノード53の電圧に所定の電圧を加算した電圧が高位側電源電圧(第1電源電圧VDD)として駆動回路11に供給される。同様に、ローサイドトランジスタ22を駆動する駆動回路12には、第1電源電圧VDDが供給されるのではなく、接地電圧GNDよりも高い任意の大きさの電圧が高位側電源電圧として供給されても良い。

【0057】

例えば、電気自動車に利用されるモータに図10に示す3相インバータを適用する場合、ハイサイドの駆動回路11の低位側電源として出力ノード53−1が接続され、高電位側の第1電源電圧VDDとして“出力ノード53−1の電圧+15V”が供給される。又、ローサイドの駆動回路12の高位側電源電圧として“第2電源電圧VNEG+15V”が供給され、低位側電源電圧として第2電源電圧VNEGが供給される。更に電気自動車に利用されるモータを駆動するための第3電源電圧VHとして、例えば“接地電圧GND+600V”といった高電圧が供給される。

【0058】

図10のように、図3に示すゲート駆動回路1を3相インバータに利用することで、第2電源電圧VNEGが目標電圧よりも高く不安定な期間に複数のインバータのいずれかにおいて発生する貫通電流を防止することができる。特に、第3電源電圧VHが高電圧となるモータを駆動する場合、第3電源電圧VHに起因する貫通電流を防止することは、モータの破壊を防止する上で有効である。

【0059】

本実施の形態では、ハイサイドトランジスタ21として、ゲート電圧が0Vにおいてオフ状態となるノーマリオフ型のパワートランジスタを利用している。この場合、ハイサイドトランジスタ21のゲートを駆動するとき第2電源電圧VNEG(負電圧)を利用していないため、第2電源電圧VNEGが規定の電圧まで低下することを待たずにハイサイドトランジスタ21をオフ状態とすることができる。このため、本実施の形態におけるゲート駆動回路は、図2のように第1電源電圧VDD(例えばシステム制御系電源)と同時的に第3電源電圧VH(例えばパワー系の電源)が上昇するようなシステムにおいても利用でき、第3電源電圧VHの上昇にともなって発生するスイッチング素子への貫通電流を防止することができる。

【0060】

又、システム電源断により第1電源電圧VDDが遮断された場合、ハイサイドトランジスタ21のゲート電圧はゼロとなる。この場合、ハイサイドトランジスタ21がノーマリオフ型トランジスタであれば、ハイサイド側がオフ状態になる。このときローサイドトランジスタ22がオン状態であっても、負荷50に印加される電圧はゼロになるので、装置の破壊などが引き起こされることはない。

【0061】

2.第2の実施の形態

第1の実施の形態における電力変換回路では、ハイサイドトランジスタ21としてノーマリオフ型のトランジスタを用いている。この構成を用いることで、システム電源(第1電源電圧VDD)の投入時や遮断時の貫通電流の問題を解決することができるが、ノーマリオン型のトランジスタに比べてスイッチング性能(例えばゲート容量に対するオン抵抗の低さ)は、若干悪化する。

【0062】

第2の実施の形態における電力変換回路では、スイッチング性能を向上させるため、ハイサイドトランジスタ21としてノーマリオン型のトランジスタが用いられる。

(構成)

以下、図12から図16を参照して、第2の実施の形態におけるゲート駆動回路1の構成の詳細を説明する。図12は、本発明による電力変換回路の第2の実施の形態における構成を示す図である。図12を参照して、第2の実施の形態における電力変換回路は、ゲート駆動回路1と、ハーフブリッジ回路のスイッチング素子として機能し、負荷50に接続されるハイサイドトランジスタ21及びローサイドトランジスタ22を具備する。第2の実施の形態におけるゲート駆動回路1は、駆動回路11、12、負電圧源30−1、30−2、制御回路40を具備し、ハイサイドトランジスタ21及びローサイドトランジスタ22を駆動する。図12に示す一例では、スイッチング性能が良好であるノーマリオン型のNチャネル型GaNトランジスタがハイサイドトランジスタ21及びローサイドトランジスタ22として好適に利用される。

【0063】

ハイサイドトランジスタ21のドレインには、図示しない電源から第3電源電圧VHが供給され、ソースは出力ノード53を介してローサイドトランジスタ22のドレインに接続される。ローサイドトランジスタ22のソースは接地され、ドレインは出力ノード53を介してハイサイドトランジスタ21のソースに接続される。出力ノード53は、負荷50に接続される。

【0064】

第2の実施の形態における駆動回路11は、入力ノード51から入力されるPWM信号(入力信号GHIN)に応じて、ノーマリオン型のハイサイドトランジスタ21のゲートを駆動する。駆駆動回路11は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備える。図12に示す一例では、駆動回路11はCMOSインバータであり、入力信号GHINを反転させた信号を、ゲート駆動信号GHとしてハイサイドトランジスタ21のゲートに出力する。第2の実施の形態における駆動回路12は、入力ノード52から入力されるPWM信号(入力信号GLIN)に応じて、ノーマリオン型のローサイドトランジスタ22のゲートを駆動する。駆動回路12は、例えば第1電源電圧VDDを高電位側の電源電圧とし、負電圧源30から供給される第2電源電圧VNEGを低位側の電源電圧として動作するトーテムポール回路を備える。図12に示す一例では、駆動回路12はCMOSインバータであり、入力信号GLINを反転させた信号を、ゲート駆動信号GLとしてローサイドトランジスタ22のゲートに出力する。尚、駆動回路11、12に供給される高電位側の電源電圧は第1電源電圧VDDに限らず、ノーマリオン型トランジスタをオン状態とできる電圧であれば任意に設定できる。

【0065】

負電圧源30−1、30−2は、接地電圧GNDよりも低い負電圧(第2電源電圧VNEG1、VNEG2)を生成する。負電圧源30−1、30−2は、第1の実施の形態と同様な構成であり、例えば図4A〜図4Cに示す構成が好適である。

【0066】

第2の実施の形態における制御回路40は、負電圧検出回路41−1、41−2、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46を具備する。負電圧検出回路41−1、41−2は、第1の実施の形態における負電圧検出回路41と同様な構成により、第2電源電圧VNEG1、VNEG2と、参照電圧Vref(図12に図示なし)との比較結果に応じた信号レベル(論理値)の駆動制御信号RDYを出力する。

【0067】

詳細には、負電圧検出回路41−1は、負電圧源30−1とローサイドトランジスタ22との接続ノード(出力ノード310−1)に接続される。負電圧検出回路41−1は、出力ノード310−1から供給される第2電源電圧VNEG1と、目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”(図12に図示なし))との比較結果に応じた信号レベル(論理値)の駆動制御信号RDY1を、出力ノード410−1を介して選択演算回路44に出力する。負電圧検出回路41−2は、負電圧源30−2とハイサイドトランジスタ21との接続ノード(出力ノード310−2)に接続される。負電圧検出回路41−2は、出力ノード310−2から供給される第2電源電圧VNEG2と、目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”(図12に図示なし))との比較結果に応じた信号レベル(論理値)の駆動制御信号RDY2を、出力ノード410−2を介して選択演算回路44に出力する。例えば、負電圧検出回路41−1、41−2は、第2電源電圧VNEG1、VNEG2が目標電圧よりも高い場合、ローレベル“0”の駆動制御信号RDY1、RDY2を選択演算回路44に出力し、第2電源電圧VNEGが目標電圧よりも低い場合、ハイレベル“1”の駆動制御信号RDY1、RDY2を選択演算回路44に出力する。第2の実施の形態における負電圧検出回路41−1、41−2の構成は、図6に示す負電圧検出回路41の構成と同様である。

【0068】

選択演算回路44は、負電圧検出回路41−1、41−2から入力される駆動制御信号RDY1、RDY2との論理演算結果を、スイッチ制御回路45に出力する。ここでは、選択演算回路44はNANDゲートが好適に利用され、駆動制御信号RDY1と駆動制御信号RDY2(のそれぞれが示す論理値)の否定論理積をスイッチ制御回路45に出力する。すなわち、選択演算回路44は、駆動制御信号RDY1、RDY2の少なくとも一方がローレベルレベル“0”のとき、ハイレベル“1”の演算結果をスイッチ制御回路45に出力する。又、選択演算回路44は、駆動制御信号RDY1、RDY2が両者ともハイレベルレベル“1”のとき、ローレベル“0”の演算結果をスイッチ制御回路45に出力する。

【0069】

スイッチ制御回路45は、選択演算回路44から出力された演算結果に応じて、電源制御スイッチ46のスイッチング動作(オン又はオフ)を制御する。詳細には、スイッチ制御回路45は、図示しない電源から供給される第1電源電圧VDDと接地電圧GNDに応じて動作するトーテムポール回路を備える。例えば、駆動回路11はCMOSインバータであり、入力信号の反転信号をスイッチ制御信号SCとして出力ノード130を介して電源制御スイッチ46のスイッチング制御端子。例えば、選択演算回路44から出力された演算結果がローレベル“0”の場合、ハイレベル“1”のスイッチ制御信号SCを出力し、選択演算回路44から出力された演算結果がハイレベル“1”の場合、ローレベル“0”のスイッチ制御信号SCを出力する。

【0070】

電源制御スイッチ46は、第3電源電圧VHが供給される電源とハイサイドトランジスタ21のドレインとの間に設けられる。電源制御スイッチ46は、出力ノード130から供給されるスイッチ制御信号SCに応じて、第3電源電圧VHが供給される電源とハイサイドトランジスタ21のドレインとの接続/切断を制御する。電源制御スイッチ46は、電源(第3電源電圧VH)とハイサイドトランジスタ21との間の接続/切断が制御できれば、FET、IGBT、バイポーラトランジスタ、サイリスタ、あるいは機械的スイッチ(例えばリレースイッチ)等に例示されるスイッチ素子が好適である。又、電源制御スイッチ46は低抵抗、低コストであれば良くスイッチング速度が高速である必要はないため、例えばIGBTのような低速スイッチも電源制御スイッチ46として利用できる。ただし、負電圧に依存せずに電源とハイサイドトランジスタ21との接続を確実に切断するため、電源制御スイッチ46は、ノーマリオフ型(エンハンスメント型)のトランジスタが好適に利用される。例えば、電源制御スイッチ46として、コレクタが電源(第3電源電圧VH)に接続され、エミッタがハイサイドトランジスタ21のドレインに接続され、ゲートが出力ノード130に接続されたNチャネル型のIGBTが設けられる。

【0071】

スイッチング素子として利用されるハイサイドトランジスタ21及びローサイドトランジスタ22は、高速動作が求められることからNチャネル型トランジスタが好適に用いられる。一方、電源制御スイッチ46は、第2電源電圧VNEGが不安定なときに負荷50に供給される電力を遮断するためのスイッチ素子であれば良い。すなわち、電源制御スイッチ46は、PWM信号などによる頻繁なスイッチングは行わないため、単純に低抵抗であれば良く、高速スイッチング性能は要求されない。このため、電源制御スイッチ46がトランジスタによって構成される場合、電源制御スイッチ46は、電源とハイサイドトランジスタ21との間の導通を制御できればPチャネル型トランジスタでも、Nチャネル型トランジスタでもどちらでも構わない。

【0072】

以上のような構成により、第2の実施の形態における制御回路40では、目標電圧よりも第2電源電圧VNEGが高い場合、電源制御スイッチ46がオフとなり、ハイサイドトランジスタ21への第3電源電圧VHの供給が遮断され、ハイサイドトランジスタ21のドレイン電流が遮断される。これにより、第2電源電圧VNEGが目標電圧よりも高く不安定な期間において、第3電源電圧VHに起因するハイサイドトランジスタ21への貫通電流の発生を防止することができる。一方、目標電圧よりも第2電源電圧VNEGが低い場合、電源制御スイッチ46がオン状態となり、ハイサイドトランジスタ21へ第3電源電圧VHが供給される。第2電源電圧VNEGが参照電圧Vrefより低い規定の値で安定すると、ハイサイドトランジスタ21及びローサイドトランジスタ22は、入力信号GHIN、GLINに応じた通常のスイッチング動作を行うことが可能となる。

【0073】

(動作)

次に図12及び図13を参照して、第2の実施の形態におけるゲート駆動回路1の動作を説明する。図13は、本発明によるゲート駆動回路の第2の実施の形態における動作を示すタイミングチャートである。

【0074】

図13を参照して、時刻T1に電力変換回路を含む半導体装置全体の電源(システム電源)が投入されてから時刻T2までの間、第1電源電圧VDDは不安定な値を示しながら所定の値となるまで上昇する。この間、負電圧源30は、第1電源電圧VDDが所定のレベルに達していないため動作せず、第2電源電圧VNEGxは0Vを示す(xは、1又は2)。負電圧検出回路41−xは、第2電源電圧VNEGxが参照電圧Vrefに−1を乗じた値“−Vref”よりも高い0Vであるため、ローレベル“0”の駆動制御信号RDYxを出力ノード410−xに出力する。これにより、スイッチ制御回路45はローレベル“0”のスイッチ制御信号SCを出力ノード130(電源制御スイッチ46の制御端子)に供給し、電源制御スイッチ46を強制的にオフ状態とする。

【0075】

時刻T2において、第1電源電圧VDDが所定の値に安定すると、負電圧源30は動作を開始し、第2電源電圧VNEGx(負電圧)は低下し始める。時刻T2から、第2電源電圧VNEGxが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなる時刻T3までの間、負電圧検出回路41−xは、ローレベル“0”の駆動制御信号RDYxを出力ノード410−xに出力する。これにより、スイッチ制御回路45はローレベル“0”のスイッチ制御信号SCを出力ノード130(電源制御スイッチ46の制御端子)に供給し、電源制御スイッチ46を強制的にオフ状態とする。

【0076】

本実施の形態におけるゲート駆動回路1では、システム電源が投入される時刻T1から、第2電源電圧VNEGが参照電圧Vrefを下回る時刻T3までの期間、制御回路40におけるノーマリオフ型の電源制御スイッチ46を強制的にオフ状態としている。この結果、第3電源電圧VHを供給する電源とハイサイドトランジスタ21との電気的接続が遮断され、第3電源電圧VHに起因したハイサイドトランジスタ21への貫通電流が阻止される。

【0077】

時刻T3以降、第2電源電圧VNEGxが参照電圧Vrefに−1を乗じた値“−Vref”よりも低くなると、負電圧検出回路41−xは、ハイレベル“1”の駆動制御信号RDYxを出力する。これにより、スイッチ制御回路45はハイレベル“1”のスイッチ制御信号SCを出力ノード130(電源制御スイッチ46の制御端子)に供給し、電源制御スイッチ46をオン状態とする。これにより、ハイサイドトランジスタ21に第3電源電圧VHが供給され、ハイサイドトランジスタ21及びローサイドトランジスタ22は、入力信号GHIN、GLINの信号レベルに応じたスイッチング動作を行う通常動作モードに移行する。

【0078】

第2の実施の形態では、ノーマリオフ型の電源制御スイッチ46によって、第2電源電圧VNEGに応じた第3電源電圧VHの供給制御を行っている。このため、ローサイドトランジスタ22のみならずハイサイドトランジスタ21にも高速スイッチング可能で低抵抗なノーマリオン型のGaNトランジスタを用いることが可能となる。従って、第2の実施の形態における電力変換回路によれば、ハーフブリッジ回路のスイッチング素子におけるオン抵抗による損失と、スイッチング損失の両方を小さくしながら、負電圧が不安定なときに発生する貫通電流を防止することができる。

【0079】

(ゲート駆動回路の適用例)

図14は、第2の実施の形態におけるゲート駆動回路1を利用したマルチフェーズスイッチング電源の構成の一例を示す図である。図14に示すマルチフェーズスイッチング電源は、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46、並列接続された複数のハーフブリッジ62、複数のハーフブリッジ62のそれぞれに搭載されたフェーズIC25を制御する制御IC90を具備する。図12に示すゲート駆動回路1のうち、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46は、複数のハーフブリッジ62に共通して設けられ、これら以外の構成は、複数のハーフブリッジ62のそれぞれのフェーズIC25に搭載される。以下では、電源制御スイッチ46として、コレクタが電源(第3電源電圧VH)に接続され、エミッタが複数のハイサイドトランジスタ21のドレインに共通接続され、ゲートが出力ノード130に接続されたNチャネル型のIGBTが設けられているものとして説明する。

【0080】

複数のハーフブリッジ62のそれぞれは、負荷50とともにハーフブリッジ回路のスイッチング素子を構成するハイサイドトランジスタ21及びローサイドトランジスタ22と、そのスイッチング動作を制御するフェーズIC25を備える。複数のハーフブリッジ62のそれぞれにおけるハイサイドトランジスタ21は共通の電源制御スイッチ46を介して第3電源(第3電源電圧VH)に接続され、ローサイドトランジスタ22はGND(接地電圧GND)に接続される。又、複数のハーフブリッジ62の出力ノード53は共通接続される。ここで、ハイサイドトランジスタ21及びローサイドトランジスタ22はノーマリオン型のトランジスタが好適に利用される。

【0081】

選択演算回路44は、複数のハーフブリッジ62のそれぞれに搭載されたフェーズIC25から出力される駆動制御信号RDYxを入力とし、その否定論理積をスイッチ制御回路45に出力する。スイッチ制御回路45は、選択演算回路44からの演算結果の反転信号をスイッチ制御信号SCとして電源制御スイッチ46のゲートに出力する。電源制御スイッチ46は、スイッチ制御信号SCに応じて第3電源(第3電源電圧VH)と、複数のハーフブリッジ62のハイサイドトランジスタ21との接続/切断を制御する。

【0082】

フェーズIC25は、出力ノード110を介してハイサイドトランジスタ21のゲートに接続され、出力ノード120を介してローサイドトランジスタ22のゲートに接続される。又、フェーズIC25は入力ノード230を介して制御IC90に接続される。図15は、図14に示すマルチフェーズスイッチング電源に搭載されるフェーズIC25の構成の一例を示す図である。

【0083】

図15を参照して、フェーズIC25は、図12に示すゲート駆動回路1のうち、選択演算回路44、スイッチ制御回路45、電源制御スイッチ46を除く、駆動回路11、12、負電圧源30−1、30−2、負電圧検出回路41−1、41−2と、デッドタイム回路31、32を備える。制御IC70は、入力ノード230を介してゲート駆動回路1にPWM信号を出力する。この際、PWM信号は、デッドタイム回路31、32を介して入力ノード51、52に入力される。これにより、入力ノード51、52に入力される入力信号GHIN、GLINは、デッドタイムを含むPWM信号となる。又、デッドタイム回路32に入力されるPWM信号は反転されるため、入力ノード51、52に入力される入力信号GHIN、GLINは相互に相補な関係となる。

【0084】

駆動回路11、12は、入力信号GHIN、GLINに応じたゲート駆動信号GH、GLを出力することで、ハーフブリッジ回路のスイッチング素子であるハイサイドトランジスタ21及びローサイドトランジスタ22のスイッチング動作を制御する。負電圧検出回路41−1、41−2から出力される駆動制御信号RDY1、RDY2は、複数のハーフブリッジ62に共通の選択演算回路44に入力される。ここで、複数のフェーズIC25のそれぞれの負電圧源30−1、30−2から供給される第2電源電圧VNEG1、VNEG2の少なくとも一方が目標電圧(ここでは参照電圧Vrefに−1を乗じた値“−Vref”)よりも高い場合、スイッチ制御回路45は、電源制御スイッチ46をオフ状態とするスイッチ制御信号SCを出力する。これにより、複数のハーフブリッジ62のいずれかにおいて、第2電源電圧VNEG1、VNEG2が規定の値より高いときに発生する貫通電流を防止することができる。

【0085】

制御IC90は、スイッチング電源の出力ノード53の電圧を監視し、異常を検出するとローレベル“0”の異常検出信号を選択演算回路44に出力してもよい。この場合、スイッチ制御回路45は、ローレベル“0”のスイッチ制御信号SCを出力し、電源制御スイッチ46をオフ状態とする。すなわち、スイッチング電源の出力異常(例えば出力信号Voutが所定の値を超える場合)に応じて、スイッチ制御回路45は、電源制御スイッチ46をオフ状態とし、スイッチング電源の動作を停止する。

【0086】

尚、図14に示すマルチフェーズスイッチング電源では、ハーフブリッジ62毎(フェーズIC25毎)に負電圧源30−1、30−2が搭載されているが、これに限らず、複数のハーフブリッジ62、あるいは駆動回路11、12に共通の負電圧源が設けられても良い。この場合、目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC25のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC23に共通の負電圧検出回路(図示なし)によって行われても良い。

【0087】

図14のように、図12に示すゲート駆動回路1をマルチフェーズスイッチング電源に利用することで、第2電源電圧VNEG1、VNEG2が目標電圧よりも高く不安定な期間に複数のハーフブリッジ62のいずれかにおいて発生する貫通電流を防止することができる。又、複数のハーフブリッジ62に共通の電源制御スイッチ46によって、複数のハーフブリッジ62への電源供給を制御しているため、面積の増大を抑制しながら負電圧異常に起因する貫通電流を防止することが可能となる。

【0088】

図16は、第2の実施の形態におけるゲート駆動回路1を利用した3相インバータの構成の一例を示す図である。図16に示す3相インバータは、選択演算回路47、48、スイッチ制御回路45、電源制御スイッチ46、並列接続された複数のハーフブリッジ63−1〜63−3、複数のハーフブリッジ63−1〜63−3のそれぞれに搭載されたフェーズIC25を制御する制御IC80を具備する。図12に示すゲート駆動回路1のうち、スイッチ制御回路45及び電源制御スイッチ46が、複数のハーフブリッジ63−1〜63−3に共通して設けられるとともに、選択演算回路44に替えて、複数のハーフブリッジ63−1〜63−3に共通する選択演算回路47、48が設けられ、これら以外の構成は、複数のハーフブリッジ63−1〜63−3のそれぞれのフェーズIC25に搭載される。以下では、電源制御スイッチ46として、コレクタが電源(第3電源電圧VH)に接続され、エミッタが複数のハイサイドトランジスタ21のドレインに共通接続され、ゲートが出力ノード130に接続されたNチャネル型のIGBTが設けられているものとして説明する。

【0089】

複数のハーフブリッジ63−1〜63−3のそれぞれは、図14に示すハーフブリッジ62と同様に、負荷50とともにハーフブリッジ回路のスイッチング素子を構成するハイサイドトランジスタ21及びローサイドトランジスタ22と、ハーフブリッジ回路のスイッチング動作を制御するフェーズIC25を備える。複数のハーフブリッジ63−1〜63−3のそれぞれにおけるハイサイドトランジスタ21は共通の電源制御スイッチ46を介して第3電源(第3電源電圧VH)に接続され、ローサイドトランジスタ22はGND(接地電圧GND)に接続される。又、複数のハーフブリッジ63−1〜63−3の出力ノード53の出力ノード53−1〜53−3は、図示しない3相モータ(負荷50に相当)のu端子、v端子、w端子に接続される。ここでu端子とは3相誘導モータのステータコイルのうち、u相コイルの入力端子であり、v端子とはv相コイルの入力端子であり、w端子とはw相コイルの入力端子である。図16に示す一例では、ハーフブリッジ63−1の出力ノード53−1はu端子に接続され、ハーフブリッジ63−2の出力ノード53−2はv端子に接続され、ハーフブリッジ63−3の出力ノード53−3はw端子に接続される。

【0090】

ハーフブリッジ63−1〜63−3の構成は、出力ノード53−1〜53−3の接続先以外、図14に示すハーフブリッジ62と同様であるため、その説明は省略する。又、フェーズIC25の構成は、駆動制御信号RDY1、RDY2の出力先が、選択演算回路47である以外図15に示す構成と同様である。

【0091】

選択演算回路47は、複数のハーフブリッジ63−1〜63−3のそれぞれにおけるフェーズIC25から出力される駆動制御信号RDY1、RDY2の論理演算結果を、選択演算回路48に出力する。ここでは、選択演算回路47はNANDゲートが好適に利用され、駆動制御信号RDY1と駆動制御信号RDY2(のそれぞれが示す論理値)の否定論理積を選択演算回路48に出力する。選択演算回路48は、ORゲートが好適に利用され、選択演算回路47の出力と異常検出信号との論理和をスイッチ制御回路45に出力する。u端子、v端子、w端子のいずれかに対する出力信号や、図示しないモータに異常が生じた場合、ハイレベル“1”の異常検出信号が入力され、異常がない場合、ローレベル“0”の異常検出信号が入力される。選択演算回路48は、選択演算回路47の演算結果と異常検出信号のすくなくとも一方が、ハイレベル“1”の場合、すなわちモータ等に異常がある場合や第2電源電圧VNEG1、VNEG2の少なくとも一方が目標電圧に達していない場合、ハイレベル“1”の信号をスイッチ制御回路45に出力する。この場合、スイッチ制御回路45はローレベル“0”のスイッチ制御信号SCを電源制御スイッチ46のゲート)に供給し、電源制御スイッチ46を強制的にオフ状態とする。これにより、モータ出力に異常のあるときに第3電源電圧VHの供給を遮断できるとともに、複数のハーフブリッジ63−1〜63−3のいずれかにおいて、第2電源電圧VNEG1、VNEG2が目標電圧より高いときに発生する貫通電流や、これによるモータの破壊を防止することができる。

【0092】

一方、選択演算回路47の演算結果と異常検出信号の両者ともローレベル“0”の場合、すなわちモータ等に異常がない場合や第2電源電圧VNEG1、VNEG2の両者が規定のレベルに達している場合、選択演算回路48はローレベル“0”の信号をスイッチ制御回路45に出力する。この場合、スイッチ制御回路45はハイレベル“1”のスイッチ制御信号SCを電源制御スイッチ46のゲートに供給し、電源制御スイッチ46を強制的にオン状態とする。これにより、複数のハーフブリッジ63−1〜63−3には第3電源電圧VHが供給され、複数のハーフブリッジ63−1〜63−3は入力信号GHIN、GLINに応じた駆動電圧を出力端子53−1〜53−3に出力して図示しない3相モータを駆動する。

【0093】

尚、図16に示す3相インバータでは、ハーフブリッジ63毎(フェーズIC25毎)に負電圧源30が搭載されているが、これに限らず、複数のハーフブリッジ63−1、63−2、63−3に共通の負電圧源が設けられても良い。この場合目標電圧に至らない第2電源電圧VNEGの検出は、複数のフェーズIC25のそれぞれに搭載された負電圧検出回路41によって行われても良いし、複数のフェーズIC25に共通の負電圧検出回路(図示なし)によって行われても良い。

【0094】

又、ハイサイドトランジスタ21は、接地電圧GNDが供給される接地端子ではなく、出力ノード53−1〜53−3のうち、対応する出力ノード53に接続されても構わない。電気自動車に利用されるモータに図10に示す3相インバータを適用する場合、ハイサイドトランジスタ21の低位電源として、接地端子に替えて出力ノード53−1に接続されることで、第1電源電圧VDDとして“出力ノード53−1の電圧+15V”が供給され、第3電源電圧として“接地電圧GND+600V”が供給される。

【0095】

図16のように、図12に示すゲート駆動回路1を3相インバータに利用することで、第2電源電圧VNEG1、VNEG2が不安定な期間に複数のインバータ63−1〜63−3のいずれかにおいて発生する貫通電流を防止することができる。又、複数のハーフブリッジ63−1〜63−3に共通の電源制御スイッチ46によって、複数のハーフブリッジ63−1〜63−3への電源供給を制御しているため、面積の増大を抑制しながら負電圧異常に起因する貫通電流を防止することが可能となる。特に、第3電源電圧VHが高電圧となるモータを駆動する場合、第3電源電圧VHに起因する貫通電流を防止することは、モータの破壊を防止する上で有効である。

【0096】

本実施の形態では、ハイサイド、ローサイドともにノーマリオン型トランジスタを用いているため、第1の実施の形態に比べてパワートランジスタによる損失を減らすことが可能である。又、ハイサイドトランジスタ21と電源の間に挿入するノーマリオフ型の電源制御スイッチ46は、複数のフェーズICで共有することができるため、貫通電流防止のための構成による面積増大を抑制することができる。

【0097】

(パッケージ例)

図17は、第1の実施の形態における電力変換回路を1つのパッケージに実装した場合の構成例を示す図である。図17を参照して、本発明に係るパッケージ(SiP:System in Package)は、図3に示すゲート駆動回路1を含む制御チップ91、ハイサイドトランジスタ21を含むハイサイド部92、ローサイドトランジスタ22を含むローサイド部を具備し、制御チップ91、ハイサイド部92、ローサイド部93は樹脂によりモールドパッケージされる。制御チップ91、ハイサイド部92、ローサイド部93は、基板上に設けられ、それぞれボンディングワイヤや基板上の配線によって接続される。詳細には、制御チップ91は、出力ノード110として機能するボンディングワイヤを介してハイサイド部92に接続され、出力ノード120として機能するボンディングワイヤを介してローサイド部93に接続される。又、制御チップ91は、第1電源電圧VDDや接地電圧GNDが供給される外部端子や、入力ノード230として機能する外部端子に接続される。ハイサイド部92は、第3電源電圧VHが供給される外部端子や、出力ノード53として機能する外部端子に接続される。ローサイド部93は、接地電圧GNDが供給される外部端子や、出力ノード53として機能する外部端子に接続される。ハイサイドトランジスタ21の方がローサイドトランジスタ22に比べオン状態となるデューティ比(オンデューティ)が低いため、ローサイドトランジスタ22に比べると相対的にオン抵抗による損失が小さく、スイッチング損失の割合が高くなる。このため、ハイサイドトランジスタ21のオン抵抗を低減するよりもスイッチング時間を短くする方が電力損失の削減に有効である。従って、ハイサイド部92は、ゲート入力容量を小さくするためにローサイド部93よりも小さいチップを用いることが望ましい。

【0098】

図18は、第2の実施の形態における電力変換回路を1つのパッケージに実装した場合の構成例を示す図である。図18を参照して、本発明に係るパッケージ(SiP)は、図12に示すゲート駆動回路1を含む制御チップ91、ハイサイドトランジスタ21を含むハイサイド部92、ローサイドトランジスタ22を含むローサイド部を具備し、制御チップ91、ハイサイド部92、ローサイド部93は樹脂によりモールドパッケージされる。制御チップ91、ハイサイド部92、ローサイド部93は、基板上に設けられ、それぞれボンディングワイヤや基板上の配線によって接続される。詳細には、制御チップ91は、出力ノード110として機能するボンディングワイヤを介してハイサイド部92に接続され、出力ノード120として機能するボンディングワイヤを介してローサイド部93に接続される。又、制御チップ91は、第1電源電圧VDDや接地電圧GNDが供給される外部端子や、入力ノード230として機能する外部端子に接続される。更に、制御チップ91は、第3電源電圧VHが供給される外部端子とハイサイド部92との間を、ボンディングワイヤを介して接続される。ハイサイド部92は、制御チップ91を介して第3電源電圧VHが供給される外部端子に接続されるとともに、出力ノード53として機能する外部端子に接続される。ローサイド部93は、接地電圧GNDが供給される外部端子や、出力ノード53として機能する外部端子に接続される。又、図17と同様に、ハイサイド部92は、ゲート入力容量を小さくするためにローサイド部93よりも小さいチップを用いることが望ましい。

【0099】

本発明による電力変換回路は、SiPのようにパッケージ化しても実現できるが、SOI構造により1チップ化しても構わない。この場合、ゲート駆動回路1、ハイサイドトランジスタ21、ローサイドトランジスタ22は、STIにより絶縁分離される。

【0100】

以上のように本発明によるゲート駆動回路1は、負電圧(第2電源電圧VNEG)が規定のレベルに達していなければ、電源投入時に限らずシステム電源の遮断時や、負電圧源の故障等によっても、ハイサイドトランジスタ21への第3電源電圧VHの供給を遮断する。これにより、第3電源電圧VHに起因する貫通電流を防止し、負荷50やハイサイドトランジスタ21及びローサイドトランジスタ22の破壊を防ぐことが可能となる。本発明によれば、負電圧(第2電源電圧VNEG)が不安定なときでも貫通電流を防止できるため、電力変換回路として機能するブリッジ回路のスイッチ素子として、ノーマリオン型のパワートランジスタ、特にFigure Of Merit(FOM)の優れたノーマリオン型のGaNトランジスタを利用することが可能となる。

【0101】

特に、第2の実施の形態におけるゲート駆動回路1では、ブリッジ回路のスイッチング素子とは別に設けられた電源制御スイッチ46により、ハイサイドトランジスタ21への第3電源電圧VHの供給を制御している。このため、PWM信号によるスイッチング動作を行うハイサイドトランジスタ21とローサイドトランジスタ22の両方に、FOMの優れたノーマリオン型のGaNトランジスタを使用できる。この結果、電力変換回路におけるスイッチング素子は低抵抗かつ高速スイッチングが可能となり、オン抵抗による損失とスイッチング損失の両方を小さくすることが可能となる。

【0102】

以上、本発明の実施の形態を詳述してきたが、具体的な構成は上記実施の形態に限られるものではなく、本発明の要旨を逸脱しない範囲の変更があっても本発明に含まれる。

【0103】

第1及び第2の実施の形態では、キャリアの移動度が高く低抵抗で電力損失が小さいことから、ハイサイドトランジスタ21及びローサイドトランジスタ22としてNチャネル型トランジスタを好適に利用している。しかし、ハイサイドトランジスタ21及びローサイドトランジスタ22の少なくとも一方にPチャネル型トランジスタを利用しても構わない。ハイサイドトランジスタ21にPチャネル型トランジスタを利用する場合、貫通電流を遮断するために出力される駆動制御信号GHの信号レベルは、上述の実施の形態に対し反転することは言うまでもない。又、電源制御スイッチ46もNチャネル型トランジスタ、Pチャネル型トランジスタ、あるいはPNPバイポーラトランジスタのいずれを利用しても構わない。

【0104】

第1の実施の形態において、第2電源電圧VNEGに応じてオフ状態とする対象は、ノーマリオフ型トランジスタとは限らずノーマリオン型トランジスタでも良い。すなわち、図3に示すハイサイドトランジスタ21としてノーマリオン型トランジスタ(例えばノーマリオン型GaNトランジスタ)が利用されても良い。この場合、駆動回路11は、駆動回路12と同様に、第1電源電圧VDDと負電圧源30から供給される第2電源電圧VNEG(負電圧)とに応じて動作する。負電圧検出回路41は、ハイサイドの駆動回路11に供給される第2電源電圧VNEGと参照電圧Vrefとの比較結果に応じた駆動制御信号RDYをハイサイドの選択演算回路42に出力する。これにより、ハイサイドの駆動回路11に供給される負電圧が規定のレベルに達しない場合、ハイサイドトランジスタ21を強制的にオフ状態にすることができる。ここで、負電圧源30や負電圧検出回路41として、ハイサイド、ローサイドに共通な負電圧源や負電圧検出回路が設けられても良いし、ハイサイド、ローサイドのそれぞれに個別の負電圧源や負電圧検出回路が設けられても良い。又、ハイサイドのみに負電圧源30、負電圧検出回路41及び選択演算回路42が設けられても良い。

【0105】

上述の実施の形態では、駆動回路11、12、46は反転出力しているがこれに限らず、正論理のゲートドライバが用いられても良い。この場合、駆動回路11、12、46を制御する論理ゲートは、実施の形態で示した論理の反転出力を駆動回路11、12、46に入力する論理ゲートに置換されることは言うまでもない。

【符号の説明】

【0106】

1 :ゲート駆動回路

11、12:駆動回路

21:ハイサイドトランジスタ

22:ローサイドトランジスタ

30、30−1、30−2:負電圧源

31、32:デッドタイム回路

40:制御回路

41、41−1、41−2:負電圧検出回路

42、44、47、48:選択演算回路

45:スイッチ制御回路

46:電源制御スイッチ

50:負荷

51、52:入力ノード

53、53−1〜53−3:の出力ノード

60、62:ハーフブリッジ

61−1〜61−3、63−1〜63−3:ハーフブリッジ

91:制御チップ

92:ハイサイド部

93:ローサイド部

110、120、310、 310−1、310−2、320:出力ノード

230、231、420、430:入力ノード

410、410−1、410−2:出力ノード

411、412:抵抗

413、414:P型MOSトランジスタ

415:コンパレータ

440:参照電圧生成回路

【特許請求の範囲】

【請求項1】

相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ及びローサイドトランジスタのゲートを相補に駆動する2つの駆動回路と、

制御回路と

を具備し、

前記ハイサイドトランジスタと前記ローサイドトランジスタの少なくとも一方は、ノーマリオン型トランジスタであり、

2つの前記ゲート駆動回路の少なくとも一方は、低電位側の電源電圧として供給される第2電源電圧に応じた駆動電圧を、前記ノーマリオン型のトランジスタのゲートに出力し、

前記第2電源電圧は、接地電圧よりも低く、

前記制御回路は、前記第2電源電圧が目標電圧よりも高い場合、前記ハイサイドトランジスタに流れるドレイン電流を遮断する

ゲート駆動回路。

【請求項2】

請求項1に記載のゲート駆動回路において、

前記制御回路は、前記第2電源電圧が前記目標電圧よりも高い場合、前記ハイサイドトランジスタのゲート電圧を制御し、前記ハイサイドトランジスタのドレイン電流を遮断する

ゲート駆動回路。

【請求項3】

請求項2に記載のゲート駆動回路において、

前記制御回路は、前記第2電源電圧が前記目標電圧よりも低い場合、第1論理レベルの信号を出力し、前記第2電源電圧が前記目標電圧よりも高い場合、第2論理レベルの信号を出力し、

前記第2駆動回路は、前記第2論理レベルの前記信号に応じた駆動電圧を前記ハイサイドトランジスタのゲートに供給し、前記ハイサイドトランジスタにおけるドレイン電流を遮断する

ゲート駆動回路。

【請求項4】

請求項1又は2に記載のゲート駆動回路において、

前記制御回路は、正電源と前記ハイサイドトランジスタとの間の接続を制御する電源制御スイッチと、前記第2電源電圧が前記目標電圧よりも高い場合、前記電源制御スイッチの制御端子の電圧を制御することで、前記ハイサイドトランジスタと前記正電源との接続を切断するスイッチ制御回路を備える

ゲート駆動回路。

【請求項5】

請求項2に記載のゲート駆動回路において、

前記スイッチ制御回路は、前記第2電源電圧が前記目標電圧よりも低い場合、第1論理レベルのスイッチ制御信号を出力し、前記第2電源電圧が前記目標電圧よりも高い場合、第2論理レベルのスイッチ制御信号を出力し、

前記電源制御スイッチは、前記第1論理レベルの前記スイッチ制御信号に応じて前記ハイサイドトランジスタと前記正電源とを電気的に接続し、前記第2論理レベルの前記スイッチ制御信号に応じて前記ハイサイドトランジスタと前記正電源との接続を切断する

ゲート駆動回路。

【請求項6】

請求項4又は5に記載のゲート駆動回路において、

前記電源制御スイッチは、複数のハーフブリッジ回路に接続され、

前記複数のハーフブリッジ回路のそれぞれは、前記ハイサイドトランジスタと前記ローサイドトランジスタを備え、

前記電源制御スイッチは、前記複数のトランジスタ対のそれぞれの前記ハイサイドトランジスタと前記正電源との接続を制御する

ゲート駆動回路。

【請求項7】

請求項1から6のいずれか1項に記載のゲート駆動回路において、

前記ローサイドトランジスタは、ノーマリオン型トランジスタである

ゲート駆動回路。

【請求項8】

請求項4から6のいずれか1項に記載のゲート駆動回路において、

前記ハイサイドトランジスタ及び前記ローサイドトランジスタは、ノーマリオン型トランジスタである

ゲート駆動回路。

【請求項9】

請求項1から8のいずれか1項に記載のゲート駆動回路において、

前記ノーマリオン型トランジスタは、Nチャネル型のGaNパワートランジスタである

ゲート駆動回路。

【請求項10】

請求項1から9のいずれか1項に記載のゲート駆動回路において、

前記第2電源電圧を、2つの前記ゲート駆動回路の少なくとも一方に供給する負電圧源を更に具備し、

前記負電圧源は、降圧型チャージポンプである

ゲート駆動回路。

【請求項11】

請求項1から9のいずれか1項に記載のゲート駆動回路において、

前記第2電源電圧を、2つの前記ゲート駆動回路の少なくとも一方に供給する負電圧源を更に具備し、

前記負電圧源は、降圧型チョッパ回路である

ゲート駆動回路。

【請求項12】

請求項10又は11に記載のゲート駆動回路において、

前記負電圧源は、多層ウェル構造又はディープNウェル構造によって形成されたダイオードを備える

ゲート駆動回路。

【請求項13】

請求項1から9のいずれか1項に記載のゲート駆動回路と、

相互に直列接続され、ハーフブリッジ回路を構成するハイサイドトランジスタ及びローサイドトランジスタと

を具備し、

前記ゲート駆動回路は、PWM信号に応じて前記ハイサイドトランジスタ及びローサイドトランジスタを駆動する

電力変換回路。

【請求項14】

請求項13に記載の電力変換回路が複数設けられ、

前記複数の電力変換回路のそれぞれのハーフブリッジ回路は、モータにおける複数のステータコイルの入力端子に接続される

3相インバータ。

【請求項15】

相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ及びローサイドトランジスタのゲートを相補に駆動する2つの駆動回路を具備するゲート駆動回路のゲート駆動方法において、

2つの前記駆動回路の少なくとも一方に対する低電位側の電源電圧として供給される、接地電位より低い電源電圧が目標電圧よりも高いか否かを監視するステップと、

前記電源電圧が目標電圧よりも高い場合、前記ハイサイドトランジスタに流れるドレイン電流を遮断するステップと

を具備する

ゲート駆動方法。

【請求項1】

相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ及びローサイドトランジスタのゲートを相補に駆動する2つの駆動回路と、

制御回路と

を具備し、

前記ハイサイドトランジスタと前記ローサイドトランジスタの少なくとも一方は、ノーマリオン型トランジスタであり、

2つの前記ゲート駆動回路の少なくとも一方は、低電位側の電源電圧として供給される第2電源電圧に応じた駆動電圧を、前記ノーマリオン型のトランジスタのゲートに出力し、

前記第2電源電圧は、接地電圧よりも低く、

前記制御回路は、前記第2電源電圧が目標電圧よりも高い場合、前記ハイサイドトランジスタに流れるドレイン電流を遮断する

ゲート駆動回路。

【請求項2】

請求項1に記載のゲート駆動回路において、

前記制御回路は、前記第2電源電圧が前記目標電圧よりも高い場合、前記ハイサイドトランジスタのゲート電圧を制御し、前記ハイサイドトランジスタのドレイン電流を遮断する

ゲート駆動回路。

【請求項3】

請求項2に記載のゲート駆動回路において、

前記制御回路は、前記第2電源電圧が前記目標電圧よりも低い場合、第1論理レベルの信号を出力し、前記第2電源電圧が前記目標電圧よりも高い場合、第2論理レベルの信号を出力し、

前記第2駆動回路は、前記第2論理レベルの前記信号に応じた駆動電圧を前記ハイサイドトランジスタのゲートに供給し、前記ハイサイドトランジスタにおけるドレイン電流を遮断する

ゲート駆動回路。

【請求項4】

請求項1又は2に記載のゲート駆動回路において、

前記制御回路は、正電源と前記ハイサイドトランジスタとの間の接続を制御する電源制御スイッチと、前記第2電源電圧が前記目標電圧よりも高い場合、前記電源制御スイッチの制御端子の電圧を制御することで、前記ハイサイドトランジスタと前記正電源との接続を切断するスイッチ制御回路を備える

ゲート駆動回路。

【請求項5】

請求項2に記載のゲート駆動回路において、

前記スイッチ制御回路は、前記第2電源電圧が前記目標電圧よりも低い場合、第1論理レベルのスイッチ制御信号を出力し、前記第2電源電圧が前記目標電圧よりも高い場合、第2論理レベルのスイッチ制御信号を出力し、

前記電源制御スイッチは、前記第1論理レベルの前記スイッチ制御信号に応じて前記ハイサイドトランジスタと前記正電源とを電気的に接続し、前記第2論理レベルの前記スイッチ制御信号に応じて前記ハイサイドトランジスタと前記正電源との接続を切断する

ゲート駆動回路。

【請求項6】

請求項4又は5に記載のゲート駆動回路において、

前記電源制御スイッチは、複数のハーフブリッジ回路に接続され、

前記複数のハーフブリッジ回路のそれぞれは、前記ハイサイドトランジスタと前記ローサイドトランジスタを備え、

前記電源制御スイッチは、前記複数のトランジスタ対のそれぞれの前記ハイサイドトランジスタと前記正電源との接続を制御する

ゲート駆動回路。

【請求項7】

請求項1から6のいずれか1項に記載のゲート駆動回路において、

前記ローサイドトランジスタは、ノーマリオン型トランジスタである

ゲート駆動回路。

【請求項8】

請求項4から6のいずれか1項に記載のゲート駆動回路において、

前記ハイサイドトランジスタ及び前記ローサイドトランジスタは、ノーマリオン型トランジスタである

ゲート駆動回路。

【請求項9】

請求項1から8のいずれか1項に記載のゲート駆動回路において、

前記ノーマリオン型トランジスタは、Nチャネル型のGaNパワートランジスタである

ゲート駆動回路。

【請求項10】

請求項1から9のいずれか1項に記載のゲート駆動回路において、

前記第2電源電圧を、2つの前記ゲート駆動回路の少なくとも一方に供給する負電圧源を更に具備し、

前記負電圧源は、降圧型チャージポンプである

ゲート駆動回路。

【請求項11】

請求項1から9のいずれか1項に記載のゲート駆動回路において、

前記第2電源電圧を、2つの前記ゲート駆動回路の少なくとも一方に供給する負電圧源を更に具備し、

前記負電圧源は、降圧型チョッパ回路である

ゲート駆動回路。

【請求項12】

請求項10又は11に記載のゲート駆動回路において、

前記負電圧源は、多層ウェル構造又はディープNウェル構造によって形成されたダイオードを備える

ゲート駆動回路。

【請求項13】

請求項1から9のいずれか1項に記載のゲート駆動回路と、

相互に直列接続され、ハーフブリッジ回路を構成するハイサイドトランジスタ及びローサイドトランジスタと

を具備し、

前記ゲート駆動回路は、PWM信号に応じて前記ハイサイドトランジスタ及びローサイドトランジスタを駆動する

電力変換回路。

【請求項14】

請求項13に記載の電力変換回路が複数設けられ、

前記複数の電力変換回路のそれぞれのハーフブリッジ回路は、モータにおける複数のステータコイルの入力端子に接続される

3相インバータ。

【請求項15】

相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ及びローサイドトランジスタのゲートを相補に駆動する2つの駆動回路を具備するゲート駆動回路のゲート駆動方法において、

2つの前記駆動回路の少なくとも一方に対する低電位側の電源電圧として供給される、接地電位より低い電源電圧が目標電圧よりも高いか否かを監視するステップと、

前記電源電圧が目標電圧よりも高い場合、前記ハイサイドトランジスタに流れるドレイン電流を遮断するステップと

を具備する

ゲート駆動方法。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−70530(P2013−70530A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−207784(P2011−207784)

【出願日】平成23年9月22日(2011.9.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月22日(2011.9.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]