ゲート駆動回路

【課題】MOS−FETを確実にオフさせることができ、かつ、複雑な構成を追加することのない、ゲート駆動回路を提供する。

【解決手段】パワーMOS−FETを駆動するためのゲート駆動回路において、前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧を印加する第1のスイッチング素子と、前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されているものである。

【解決手段】パワーMOS−FETを駆動するためのゲート駆動回路において、前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧を印加する第1のスイッチング素子と、前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されているものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パワーMOS−FETを駆動するゲート駆動回路に関するものである。

【背景技術】

【0002】

モータ等の電気負荷を駆動するための駆動回路として、Nチャネル型MOS−FETを直列に接続し、その接続点に電気負荷を接続する、いわゆるトーテムポール型のものが一般的に知られており、このような電気負荷駆動回路は、ハーフブリッジ、Hブリッジ、多相ブリッジ等、様々な態様で用いられ、その用途も様々である。

【0003】

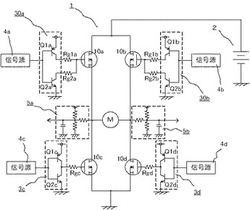

例えば、車両用の電動パワーステアリング装置においては、図4に示すような、4つのNチャネル型MOS−FETを用いたHブリッジ回路にてモータを駆動するものが一般的に知られている。

【0004】

図4において、Nチャネル型MOS−FET10a〜10dからなるHブリッジ回路1の出力端子間を橋絡すべくモータMが接続されており、また、Hブリッジ回路1の入力端子間にはバッテリ2が接続されている。4つのNチャネル型MOS−FET10a〜10dのゲート端子には、それぞれゲート抵抗Rga〜Rgdを介して、ゲート駆動回路3a〜3dが接続されており、そのゲート駆動回路3a〜3dには、該ゲート駆動回路3a〜3dをそれぞれ動作させるべく信号源4a〜4dが接続されている。この信号源4a〜4は、図示しないが、ステアリング系に設けられ、運転者の操舵力を検出する操舵トルクセンサや車両の速度を検出する車速センサ等の各種センサの検出結果に基づき、マイクロコンピュータ等により構成された制御ユニットにて演算された所望の目標トルクをモータMが生ずるよう4つのNチャネル型MOS−FET10a〜10dを駆動するための信号を出力するものである。また、Hブリッジ回路1の各出力端子には、その端子電圧、即ちモータ端子電圧を検出すべく、モータ端子電圧検出回路5a,5bが設けられている。

【0005】

また、前記ゲート駆動回路3aは、PNPトランジスタQ1aとNPNトランジスタQ2aが直列接続された構成となっており、該PNPトランジスタQ1aとNPNトランジスタQ2aの接続点が、ゲート抵抗Rgaを介してNチャネル型MOS−FET10aのゲート端子に接続されている。このPNPトランジスタQ1aとNPNトランジスタQ2aは信号源4aの信号に応じて相補的にオン、オフ駆動されるもので、PNPトランジスタQ1aがオンされることで、Nチャネル型MOS−FET10aのゲート端子に、該Nチャネル型MOS−FET10aがオンするための電圧が印加され、NPNトランジスタQ2aがオンされることでNチャネル型MOS−FET10aのゲート端子に、該Nチャネル型MOS−FET10aがオフするための電圧が印加される。なお、ゲート駆動回路3b〜3dの構成、動作も同様であるため、詳細な説明は省略するが、例えば、モータMを右回転させる場合は、Nチャネル型MOS−FET10aとNチャネル型MOS−FET10dをオンさせ、左回転させる場合は、Nチャネル型MOS−FET10bとNチャネル型MOS−FET10cをオンさせるものとする。

【0006】

このようなトーテムポール接続されたNチャネル型MOS−FETを駆動するものにおいて、特に高電位側のNチャネル型MOS−FET10aをオフする際の動作を詳細に検討する。

【0007】

高電位側Nチャネル型MOS−FET10aをオフすべく、NPNトランジスタQ2aをオンすると、高電位側Nチャネル型MOS−FET10aのゲート電位が接地電位に向かって低下していき、高電位側Nチャネル型MOS−FET10aのゲート−ソース間電圧が低下することになり、該高電位側Nチャネル型MOS−FET10aがオフしていく。この際、モータに流れていた電流は、モータのインダクタンス成分により流れ続けようとするため、高電位側Nチャネル型MOS−FET10aと直列に接続された低電位側Nチャネル型MOS−FET10cの寄生ダイオードを通って電流が流れ始める(いわゆる回生電流)。この回生電流によって、低電位側Nチャネル型MOS−FET10cの寄生ダイオードには電圧降下が生じるため、高電位側Nチャネル型MOS−FET10aと低電位側Nチャネル型MOS−FET10cの接続点の電位は、接地レベルよりも寄生ダイオードの電圧降下分(一般的には0.7V程度)低い負電位となってしまう。これにより、高電位側Nチャネル型MOS−FET10aのゲート−ソース間電圧が大きくなってしまい、高電位側Nチャネル型MOS−FET10aが完全にオフできず、続く動作によって、低電位側Nチャネル型MOS−FET10cがオンされ、高電位側Nチャネル型MOS−FET10a、低電位側Nチャネル型MOS−FET10cともにオンされ、短絡電流が流れてしまうという問題が生じる場合があった。

【0008】

また、ここでNチャネル型MOS−FETには図5に示すように、その構造上、入力容量と呼ばれる容量成分が存在することが知られており、Nチャネル型MOS−FETのゲート端子に接続されるゲート抵抗Rgとこの入力容量Cが、いわゆる積分回路を構成することとなるため、矩形波状のゲート信号を印加した場合に、ゲート−ソース間の電位差が、Nチャネル型MOS−FETをオンする電位差になるまでの時間、および、Nチャネル型MOS−FETをオフする電位差になるまでの時間、(すなわち、スイッチング速度)は、ゲート抵抗Rgの大きさによって決まる。上述の短絡電流を防止するためには、オフする電位差になるまでの時間を短くするようにゲート抵抗小さくすることが重要である。ところが、ゲート抵抗を小さくすると、スイッチング速度が速くなるものの、Nチャネル型MOS−FETをオンする際に電磁ノイズが生じる。

【0009】

すなわち、Nチャネル型MOS−FETをオフする際に、該Nチャネル型MOS−FETのゲート端子を、ゲート抵抗およびNPNトランジスタを介して接地電位に接続するわけであるが、上述のノイズを防止するためにはゲート抵抗を比較的大きめの抵抗値に設定する必要があり、上述の短絡電流を防止するためにはゲート抵抗を小さくする必要があり、両立が難しいという問題が生じる場合があった。

【0010】

このように高電位側Nチャネル型MOS−FETが完全にオフできなくなってしまうという問題を解決するために、特許文献1に示されるような方法が知られている。

【0011】

以下、特許文献1のゲート駆動回路の動作について説明するが、特許文献1(特に第3図)の関係部分のみを模式的に示した図7を用いる。この図6において、前記図4と同一符号は同一箇所を示し、詳細な説明は省略する。この図6では、前記図4と比べ、ゲート駆動回路3aおよび3bに設けられたNPNトランジスタQ2aおよびQ2bのエミッタに、負電源が接続されている点が異なる。

【0012】

図6に示すゲート駆動回路においては、特に高電位側Nチャネル型MOS−FET10aをオフする際は、NPNトランジスタQ2aをオンすることで、高電位側Nチャネル型MOS−FET10aのゲート端子をゲート抵抗Rgaを介して負電源6aに接続し、高電位側Nチャネル型MOS−FET10aのゲート電位を低下させて、高電位側Nチャネル型MOS−FET10aをオフさせるものである。このようなゲート駆動回路によれば、転流電流が流れて、トーテムポール接続された高電位側Nチャネル型MOS−FET10aと低電位側Nチャネル型MOS−FET10cの接続点の電位が、低電位側Nチャネル型MOS−FET10cの寄生ダイオードの電圧降下分だけ低い負電位となっても、高電位側Nチャネル型MOS−FET10aのゲート−ソース間電圧を充分低下させることができ、該高電位側Nチャネル型MOS−FET10aを完全にオフさせることができる。

【0013】

次に、特許文献2のゲート駆動回路の動作について説明するが、特許文献1(特に図1)の関係部分のみを模式的に示した図7を用いる。この図7において、前記図4または図6と同一符号は同一箇所を示し、詳細な説明は省略する。この図7では、前記図4と比べ、ゲート駆動回路3aおよび3bに設けられたNPNトランジスタQ2aおよびQ2bのエミッタが高電位側Nチャネル型MOS−FET10aあるいは10bのソースが接続されている点が異なる。

【0014】

図7に示すゲート駆動回路においては、特に高電位側Nチャネル型MOS−FET10aをオフする際は、PNPトランジスタQ2aをオンすることで、高電位側Nチャネル型MOS−FET10aのゲート端子をゲート抵抗Rgaを介して高電位側Nチャネル型MOS−FET10aのソース端子と接続するため、回生電流が流れて、トーテムポール接続された高電位側Nチャネル型MOS−FET10aと低電位側Nチャネル型MOS−FET10cの接続点の電位が、低電位側Nチャネル型MOS−FET10cの寄生ダイオードの電圧降下分だけ低い負電位となっても、高電位側Nチャネル型MOS−FET10aのゲート端子とソース端子は同電位となり、ゲート−ソース間電圧は充分低下させることができ、該高電位側Nチャネル型MOS−FET10aを完全にオフさせることができる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平2−87963号公報

【特許文献2】特開2004−328413号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

以上説明したように、特許文献1および特許文献2に示されたゲート駆動回路によれば、図4に示すような一般的なゲート駆動回路における課題は解決できるものの、別な課題が生じるものである。

【0017】

まず、特許文献1(模式的には図6)に示されたゲート駆動回路によれば、負電源6a,6bが必要となる。この負電源6a,6bは、上述した車両用の電動パワーステアリング装置のように、単一の電源(電動パワーステアリング装置においては、車載バッテリ)を用いるものにおいては、負電源を作り出すために複雑な回路を追加する必要があるため、部品点数が増加してしまい、装置の大型化、コストアップを招くという課題がある。

【0018】

一方、特許文献2(模式的には図7)に示されたゲート駆動回路によれば、特許文献1のように負電源6a,6bが必要となることはなく、ゲート駆動回路を構成するNPNトランジスタのエミッタ端子とNチャネル型MOS−FETのソース端子を接続するだけでよく、非常に簡単な構成にて実現することができるものである。

【0019】

ここで、電動パワーステアリング装置には上述したように、モータ端子電圧を検出するためのモータ端子電圧検出回路5a,5bが設けられている。このモータ端子電圧検出回路5a,5bにて検出したモータ端子電圧は、図示しないマイクロコンピュータ等に入力され、モータ制御や、装置の異常判定に用いられるものである。

【0020】

図7に戻り、ゲート駆動回路3aのNPNトランジスタQ2aのエミッタ端子が、Nチャネル型MOS−FET10aのソース端子に接続されている。このNチャネル型MOS−FET10aのソース端子は、Hブリッジ回路1の出力端子でもあり、即ちモータ端子でもあることが図7から見てとれる。上述したモータ端子電圧検出回路5aは、このモータ端子の端子電圧を検出するものであるが、ゲート駆動回路3aが動作し、NPNトランジスタQ2aがオンされた場合には、そのゲート電流がこのモータ端子電圧検出回路5aに流れ込むこととなってしまい、モータ端子電圧検出回路5aによるモータ端子電圧の検出に誤差を生じることとなってしまう。

【0021】

この検出されたモータ端子電圧は、装置の異常判定や、モータ制御に用いられるものであるため、その検出に誤差を生じてしまうと、モータ制御が正確に行われず、また、装置の異常を誤判定してしまうという課題があり、このようなゲート駆動回路を電動パワーステアリング装置に用いた場合には、電動パワーステアリング装置の操舵フィーリングの悪化や商品性の劣化を招くこととなってしまう。

【0022】

本発明は、上記の課題を解決するためになされたもので、トーテムポール型に接続されたNチャネル型MOS−FETの特に高電位側のNチャネル型MOS−FETを確実にオフさせることができ、かつ、複雑な構成を追加することなく、また、モータ端子電圧の検出誤差を生じさせることのない、ゲート駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0023】

本発明に係るゲート駆動回路は、パワーMOS−FETを駆動するためのゲート駆動回路において、前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧を印加する第1のスイッチング素子と、前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されているものである。

【0024】

また、前記第2の抵抗は、前記MOS−FETのゲート端子と前記第2のスイッチング素子の間の配線抵抗としてもよく、また、複数のゲート駆動回路を含むICとして構成してもよい。

【発明の効果】

【0025】

本発明によれば、パワーMOS−FETのを確実にオフさせることができ、かつ、複雑な構成を追加することなく、また、モータ端子電圧の検出誤差を生じさせることのない、ゲート駆動回路を提供することができるという効果を奏する。

【図面の簡単な説明】

【0026】

【図1】この発明の実施の形態1のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【図2】この発明の実施の形態1のゲート駆動回路を備えるモータ駆動回路の変形例を示す回路図である。

【図3】この発明の実施の形態1のゲート駆動回路を備えるモータ駆動回路の変形例を示す回路図である。

【図4】従来のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【図5】Nチャネル型MOS−FETのスイッチング動作を説明する図である。

【図6】従来のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【図7】従来のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【発明を実施するための形態】

【0027】

実施の形態1.

図1は、この発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路の構成を示すブロック図である。前述した図4の構成との差異は、ゲート駆動回路30a、30bおよび、そのゲート駆動回路30a、30bから高電位側Nチャネル型MOS−FET10a、10bの間に、それぞれ2つのゲート抵抗Rg1a、Rg1b、Rg2a、Rg2bが接続されている点である。また、ここで、これらのゲート抵抗の抵抗値はRg1a=Rg1b>Rg2a=Rg2bとなるように設定されている。

【0028】

図1に示すゲート駆動回路を備えるモータの駆動回路において、高電位側Nチャネル型MOS−FET10a、10bのゲート端子に信号を与えるためのゲート駆動回路30a,30bは、駆動電源に接続されたPNPトランジスタQ1a(請求項の第1のスイッチング素子に相当)をオンし、ゲート抵抗Rg1a(請求項の第1の抵抗に相当)を介して、高電位側Nチャネル型MOS−FET10aに信号を印加することで、高電位側Nチャネル型MOS−FET10aをオンし、また、NPNトランジスタQ2a(請求項の第2のスイッチング素子に相当)をオンし、ゲート抵抗Rg2a(請求項の第2の抵抗に相当)を介してゲート端子を接地電位に接続することでゲート−ソース間の電位差を無くし、高電位側Nチャネル型MOS−FETをオフする。

【0029】

このような高電位側Nチャネル型MOS−FETのオン、オフ動作においては、上述のとおり、ゲート抵抗値がRg1a>Rg2aとなるように設定されているため、Nチャネル型MOS−FETの入力容量Cとゲート抵抗Rg1aあるいはRg2aで形成される積分回路の時定数が異なり、オン動作時よりもオフ動作時の方が速いスイッチング速度となる。

【0030】

従って、Nチャネル型MOS−FET10aのオフ動作時に、Nチャネル型MOS−FET10aのゲート端子を、ゲート抵抗Rg2a、NPNトランジスタQ2aを介して接地電位に接続するわけであるが、ゲート抵抗Rg2aは、上述のとおり、ゲート抵抗Rg1aより小さい値に設定されているため、スイッチング速度が速く、速やかにNチャネル型MOS−FET10aを完全にオフすることができ、続く動作によって、低電位側Nチャネル型MOS−FET10cがオンされても、高電位側Nチャネル型MOS−FET10a、低電位側Nチャネル型MOS−FET10cともにオンされ、短絡電流が流れてしまうことはない。

【0031】

このようなゲート駆動回路によれば、ゲート抵抗Rg1a、Rg2aの抵抗値をこのように設定して、オン動作時とオフ動作時のスイッチング速度を、オン動作時よりもオフ動作時の方が速くすることによって、トーテムポール型に接続されたNチャネル型MOS−FETをオンする際に生じる電磁ノイズを抑制することができる。

【0032】

また、図6に示した従来の装置のように負電源6a、6bを設ける必要がないため、車両用の電動パワーステアリング装置のように、単一の電源(電動パワーステアリング装置においては、車載バッテリ)を用いるものにおいても、負電源を作り出すために複雑な回路を追加する必要がなく、部品点数の増加、装置の大型化、コストアップを招くことはない。

【0033】

さらに、図7に示した従来の装置のように、ゲート駆動回路のNPNトランジスタのエミッタ端子と高電位側Nチャネル型MOS-FETのソース端子を接続するものではなく、モータ端子電圧検出回路にゲート電流が流れ込まず、モータ端子電圧の検出に誤差が生じることがなく、電動パワーステアリング装置等に使用した際にも、その誤差の影響で、装置の操舵フィーリングの悪化や商品性の劣化を招くことがない。

【0034】

以上説明したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、このようなゲート駆動回路をディスクリート構成としてもよいが、図2(a)に示すように、信号源を含めて単一のIC300として構成してもよい。すなわち、1つのNチャネル型MOS−FETに対して、2つのポートを持つICとして構成してもよい。これにより、ICのチップサイズは増大させることなく、ゲート抵抗を変更するだけで最適なスイッチング速度が得られ、装置全体が小型化でき、かつ、設計自由度が向上する。

【0035】

なお、図2(a)では、単一のパワーMOS−FETを駆動するための信号源およびゲート駆動回路のみをIC300として構成するものを示したが、図2(b)に示すように、Hブリッジ回路を構成する全てのパワーMOS−FET10a,10b,10c,10dを駆動するための信号源4a,4b,4c,4dおよびゲート駆動回路30a,30b,30c、30d全てを単一のICとして構成しても何ら差し支えない。

【0036】

また、この図2(b)では、Hブリッジ回路構成のモータ駆動回路を例にとったため、信号源およびゲート駆動回路はそれぞれ4つとしたが、3相ブリッジ回路であれば、それぞれ6つとなるのは自明であり、要は、駆動されるパワーMOS−FETの個数と同数の信号源およびゲート駆動回路を単一のICとして構成すればよい。これによれば、一般的によく用いられる、Hブリッジ回路や三相ブリッジ回路等に対して、各1種のICを準備すれば、ゲート抵抗を変更するのみで、スイッチング速度を任意に変更でき、標準化や部品点数の低減を実現することができる。さらに、トーテムポール型に接続された2つのパワーMOS−FETを駆動するために、信号源およびゲート駆動回路それぞれ2つずつを単一のICとして構成してもよく、この場合、モータ駆動回路の相数が異なっても、同じICを使用できるため、幾分、部品点数は増えるものの、より進んだ標準化を実現できる。

【0037】

また、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、オン側およびオフ側のいずれにもゲート抵抗を備えるものについて説明したが、図3に示すようにオフ側のゲート抵抗を備えず、Nチャネル型MOS−FETのゲート端子とゲート駆動回路のNPNトランジスタのコレクタ端子を直接接続して(すなわち、オフ側のゲート回路Rg2aは、Nチャネル型MOS−FETのゲート端子とNPNトランジスタのコレクタ端子間の配線抵抗のみとする構成にして)も良い。このように構成すれば、部品点数をさらに低減でき、オフ動作時のスイッチング速度をさらに速めることができ、オフ動作時のスイッチング損失をより低減できる。

【0038】

また、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、ゲート駆動回路として、PNPトランジスタとNPNトランジスタを備えるものについて説明したが、これに限られるものではなく、同種のトランジスタ2つを用い、その一方の入力段に反転回路(インバータ)を備えるようにしてもよく、またFET等他のスイッチング素子で構成してもよい。

【0039】

なお、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、高電位側Nチャネル型MOS−FETを駆動するためのゲート駆動回路のみを、オン側およびオフ側のゲート抵抗を介して接続するものとしたが、低電位側Nチャネル型MOS−FETを駆動するゲート駆動回路も同様の構成としても何ら差し支えない。さらに、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、電気負荷駆動回路として、Hブリッジ回路を用いたものについて説明したが、これ以外のもの、例えばハーフブリッジ回路、多相ブリッジ回路等、いわゆるトーテムポール型に接続された電気負荷駆動回路であれば、いずれの形のものでも同様に適用できるものである。

【符号の説明】

【0040】

1:Hブリッジ回路、10a〜10d:Nチャネル型MOS−FET、2:バッテリ、30a〜30d:ゲート駆動回路、300:IC、4a〜4d:信号源、5a,5b:モータ端子電圧検出回路、M:モータ、Q1a:PNPトランジスタ(第1のスイッチング素子)、Q2a:NPNトランジスタ(第2のスイッチング素子)、Rg1a:ゲート抵抗(第1の抵抗)、Rg2a:ゲート抵抗(第2の抵抗)

【技術分野】

【0001】

本発明は、パワーMOS−FETを駆動するゲート駆動回路に関するものである。

【背景技術】

【0002】

モータ等の電気負荷を駆動するための駆動回路として、Nチャネル型MOS−FETを直列に接続し、その接続点に電気負荷を接続する、いわゆるトーテムポール型のものが一般的に知られており、このような電気負荷駆動回路は、ハーフブリッジ、Hブリッジ、多相ブリッジ等、様々な態様で用いられ、その用途も様々である。

【0003】

例えば、車両用の電動パワーステアリング装置においては、図4に示すような、4つのNチャネル型MOS−FETを用いたHブリッジ回路にてモータを駆動するものが一般的に知られている。

【0004】

図4において、Nチャネル型MOS−FET10a〜10dからなるHブリッジ回路1の出力端子間を橋絡すべくモータMが接続されており、また、Hブリッジ回路1の入力端子間にはバッテリ2が接続されている。4つのNチャネル型MOS−FET10a〜10dのゲート端子には、それぞれゲート抵抗Rga〜Rgdを介して、ゲート駆動回路3a〜3dが接続されており、そのゲート駆動回路3a〜3dには、該ゲート駆動回路3a〜3dをそれぞれ動作させるべく信号源4a〜4dが接続されている。この信号源4a〜4は、図示しないが、ステアリング系に設けられ、運転者の操舵力を検出する操舵トルクセンサや車両の速度を検出する車速センサ等の各種センサの検出結果に基づき、マイクロコンピュータ等により構成された制御ユニットにて演算された所望の目標トルクをモータMが生ずるよう4つのNチャネル型MOS−FET10a〜10dを駆動するための信号を出力するものである。また、Hブリッジ回路1の各出力端子には、その端子電圧、即ちモータ端子電圧を検出すべく、モータ端子電圧検出回路5a,5bが設けられている。

【0005】

また、前記ゲート駆動回路3aは、PNPトランジスタQ1aとNPNトランジスタQ2aが直列接続された構成となっており、該PNPトランジスタQ1aとNPNトランジスタQ2aの接続点が、ゲート抵抗Rgaを介してNチャネル型MOS−FET10aのゲート端子に接続されている。このPNPトランジスタQ1aとNPNトランジスタQ2aは信号源4aの信号に応じて相補的にオン、オフ駆動されるもので、PNPトランジスタQ1aがオンされることで、Nチャネル型MOS−FET10aのゲート端子に、該Nチャネル型MOS−FET10aがオンするための電圧が印加され、NPNトランジスタQ2aがオンされることでNチャネル型MOS−FET10aのゲート端子に、該Nチャネル型MOS−FET10aがオフするための電圧が印加される。なお、ゲート駆動回路3b〜3dの構成、動作も同様であるため、詳細な説明は省略するが、例えば、モータMを右回転させる場合は、Nチャネル型MOS−FET10aとNチャネル型MOS−FET10dをオンさせ、左回転させる場合は、Nチャネル型MOS−FET10bとNチャネル型MOS−FET10cをオンさせるものとする。

【0006】

このようなトーテムポール接続されたNチャネル型MOS−FETを駆動するものにおいて、特に高電位側のNチャネル型MOS−FET10aをオフする際の動作を詳細に検討する。

【0007】

高電位側Nチャネル型MOS−FET10aをオフすべく、NPNトランジスタQ2aをオンすると、高電位側Nチャネル型MOS−FET10aのゲート電位が接地電位に向かって低下していき、高電位側Nチャネル型MOS−FET10aのゲート−ソース間電圧が低下することになり、該高電位側Nチャネル型MOS−FET10aがオフしていく。この際、モータに流れていた電流は、モータのインダクタンス成分により流れ続けようとするため、高電位側Nチャネル型MOS−FET10aと直列に接続された低電位側Nチャネル型MOS−FET10cの寄生ダイオードを通って電流が流れ始める(いわゆる回生電流)。この回生電流によって、低電位側Nチャネル型MOS−FET10cの寄生ダイオードには電圧降下が生じるため、高電位側Nチャネル型MOS−FET10aと低電位側Nチャネル型MOS−FET10cの接続点の電位は、接地レベルよりも寄生ダイオードの電圧降下分(一般的には0.7V程度)低い負電位となってしまう。これにより、高電位側Nチャネル型MOS−FET10aのゲート−ソース間電圧が大きくなってしまい、高電位側Nチャネル型MOS−FET10aが完全にオフできず、続く動作によって、低電位側Nチャネル型MOS−FET10cがオンされ、高電位側Nチャネル型MOS−FET10a、低電位側Nチャネル型MOS−FET10cともにオンされ、短絡電流が流れてしまうという問題が生じる場合があった。

【0008】

また、ここでNチャネル型MOS−FETには図5に示すように、その構造上、入力容量と呼ばれる容量成分が存在することが知られており、Nチャネル型MOS−FETのゲート端子に接続されるゲート抵抗Rgとこの入力容量Cが、いわゆる積分回路を構成することとなるため、矩形波状のゲート信号を印加した場合に、ゲート−ソース間の電位差が、Nチャネル型MOS−FETをオンする電位差になるまでの時間、および、Nチャネル型MOS−FETをオフする電位差になるまでの時間、(すなわち、スイッチング速度)は、ゲート抵抗Rgの大きさによって決まる。上述の短絡電流を防止するためには、オフする電位差になるまでの時間を短くするようにゲート抵抗小さくすることが重要である。ところが、ゲート抵抗を小さくすると、スイッチング速度が速くなるものの、Nチャネル型MOS−FETをオンする際に電磁ノイズが生じる。

【0009】

すなわち、Nチャネル型MOS−FETをオフする際に、該Nチャネル型MOS−FETのゲート端子を、ゲート抵抗およびNPNトランジスタを介して接地電位に接続するわけであるが、上述のノイズを防止するためにはゲート抵抗を比較的大きめの抵抗値に設定する必要があり、上述の短絡電流を防止するためにはゲート抵抗を小さくする必要があり、両立が難しいという問題が生じる場合があった。

【0010】

このように高電位側Nチャネル型MOS−FETが完全にオフできなくなってしまうという問題を解決するために、特許文献1に示されるような方法が知られている。

【0011】

以下、特許文献1のゲート駆動回路の動作について説明するが、特許文献1(特に第3図)の関係部分のみを模式的に示した図7を用いる。この図6において、前記図4と同一符号は同一箇所を示し、詳細な説明は省略する。この図6では、前記図4と比べ、ゲート駆動回路3aおよび3bに設けられたNPNトランジスタQ2aおよびQ2bのエミッタに、負電源が接続されている点が異なる。

【0012】

図6に示すゲート駆動回路においては、特に高電位側Nチャネル型MOS−FET10aをオフする際は、NPNトランジスタQ2aをオンすることで、高電位側Nチャネル型MOS−FET10aのゲート端子をゲート抵抗Rgaを介して負電源6aに接続し、高電位側Nチャネル型MOS−FET10aのゲート電位を低下させて、高電位側Nチャネル型MOS−FET10aをオフさせるものである。このようなゲート駆動回路によれば、転流電流が流れて、トーテムポール接続された高電位側Nチャネル型MOS−FET10aと低電位側Nチャネル型MOS−FET10cの接続点の電位が、低電位側Nチャネル型MOS−FET10cの寄生ダイオードの電圧降下分だけ低い負電位となっても、高電位側Nチャネル型MOS−FET10aのゲート−ソース間電圧を充分低下させることができ、該高電位側Nチャネル型MOS−FET10aを完全にオフさせることができる。

【0013】

次に、特許文献2のゲート駆動回路の動作について説明するが、特許文献1(特に図1)の関係部分のみを模式的に示した図7を用いる。この図7において、前記図4または図6と同一符号は同一箇所を示し、詳細な説明は省略する。この図7では、前記図4と比べ、ゲート駆動回路3aおよび3bに設けられたNPNトランジスタQ2aおよびQ2bのエミッタが高電位側Nチャネル型MOS−FET10aあるいは10bのソースが接続されている点が異なる。

【0014】

図7に示すゲート駆動回路においては、特に高電位側Nチャネル型MOS−FET10aをオフする際は、PNPトランジスタQ2aをオンすることで、高電位側Nチャネル型MOS−FET10aのゲート端子をゲート抵抗Rgaを介して高電位側Nチャネル型MOS−FET10aのソース端子と接続するため、回生電流が流れて、トーテムポール接続された高電位側Nチャネル型MOS−FET10aと低電位側Nチャネル型MOS−FET10cの接続点の電位が、低電位側Nチャネル型MOS−FET10cの寄生ダイオードの電圧降下分だけ低い負電位となっても、高電位側Nチャネル型MOS−FET10aのゲート端子とソース端子は同電位となり、ゲート−ソース間電圧は充分低下させることができ、該高電位側Nチャネル型MOS−FET10aを完全にオフさせることができる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平2−87963号公報

【特許文献2】特開2004−328413号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

以上説明したように、特許文献1および特許文献2に示されたゲート駆動回路によれば、図4に示すような一般的なゲート駆動回路における課題は解決できるものの、別な課題が生じるものである。

【0017】

まず、特許文献1(模式的には図6)に示されたゲート駆動回路によれば、負電源6a,6bが必要となる。この負電源6a,6bは、上述した車両用の電動パワーステアリング装置のように、単一の電源(電動パワーステアリング装置においては、車載バッテリ)を用いるものにおいては、負電源を作り出すために複雑な回路を追加する必要があるため、部品点数が増加してしまい、装置の大型化、コストアップを招くという課題がある。

【0018】

一方、特許文献2(模式的には図7)に示されたゲート駆動回路によれば、特許文献1のように負電源6a,6bが必要となることはなく、ゲート駆動回路を構成するNPNトランジスタのエミッタ端子とNチャネル型MOS−FETのソース端子を接続するだけでよく、非常に簡単な構成にて実現することができるものである。

【0019】

ここで、電動パワーステアリング装置には上述したように、モータ端子電圧を検出するためのモータ端子電圧検出回路5a,5bが設けられている。このモータ端子電圧検出回路5a,5bにて検出したモータ端子電圧は、図示しないマイクロコンピュータ等に入力され、モータ制御や、装置の異常判定に用いられるものである。

【0020】

図7に戻り、ゲート駆動回路3aのNPNトランジスタQ2aのエミッタ端子が、Nチャネル型MOS−FET10aのソース端子に接続されている。このNチャネル型MOS−FET10aのソース端子は、Hブリッジ回路1の出力端子でもあり、即ちモータ端子でもあることが図7から見てとれる。上述したモータ端子電圧検出回路5aは、このモータ端子の端子電圧を検出するものであるが、ゲート駆動回路3aが動作し、NPNトランジスタQ2aがオンされた場合には、そのゲート電流がこのモータ端子電圧検出回路5aに流れ込むこととなってしまい、モータ端子電圧検出回路5aによるモータ端子電圧の検出に誤差を生じることとなってしまう。

【0021】

この検出されたモータ端子電圧は、装置の異常判定や、モータ制御に用いられるものであるため、その検出に誤差を生じてしまうと、モータ制御が正確に行われず、また、装置の異常を誤判定してしまうという課題があり、このようなゲート駆動回路を電動パワーステアリング装置に用いた場合には、電動パワーステアリング装置の操舵フィーリングの悪化や商品性の劣化を招くこととなってしまう。

【0022】

本発明は、上記の課題を解決するためになされたもので、トーテムポール型に接続されたNチャネル型MOS−FETの特に高電位側のNチャネル型MOS−FETを確実にオフさせることができ、かつ、複雑な構成を追加することなく、また、モータ端子電圧の検出誤差を生じさせることのない、ゲート駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0023】

本発明に係るゲート駆動回路は、パワーMOS−FETを駆動するためのゲート駆動回路において、前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧を印加する第1のスイッチング素子と、前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されているものである。

【0024】

また、前記第2の抵抗は、前記MOS−FETのゲート端子と前記第2のスイッチング素子の間の配線抵抗としてもよく、また、複数のゲート駆動回路を含むICとして構成してもよい。

【発明の効果】

【0025】

本発明によれば、パワーMOS−FETのを確実にオフさせることができ、かつ、複雑な構成を追加することなく、また、モータ端子電圧の検出誤差を生じさせることのない、ゲート駆動回路を提供することができるという効果を奏する。

【図面の簡単な説明】

【0026】

【図1】この発明の実施の形態1のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【図2】この発明の実施の形態1のゲート駆動回路を備えるモータ駆動回路の変形例を示す回路図である。

【図3】この発明の実施の形態1のゲート駆動回路を備えるモータ駆動回路の変形例を示す回路図である。

【図4】従来のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【図5】Nチャネル型MOS−FETのスイッチング動作を説明する図である。

【図6】従来のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【図7】従来のゲート駆動回路を備えるモータ駆動回路の構成を示す回路図である。

【発明を実施するための形態】

【0027】

実施の形態1.

図1は、この発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路の構成を示すブロック図である。前述した図4の構成との差異は、ゲート駆動回路30a、30bおよび、そのゲート駆動回路30a、30bから高電位側Nチャネル型MOS−FET10a、10bの間に、それぞれ2つのゲート抵抗Rg1a、Rg1b、Rg2a、Rg2bが接続されている点である。また、ここで、これらのゲート抵抗の抵抗値はRg1a=Rg1b>Rg2a=Rg2bとなるように設定されている。

【0028】

図1に示すゲート駆動回路を備えるモータの駆動回路において、高電位側Nチャネル型MOS−FET10a、10bのゲート端子に信号を与えるためのゲート駆動回路30a,30bは、駆動電源に接続されたPNPトランジスタQ1a(請求項の第1のスイッチング素子に相当)をオンし、ゲート抵抗Rg1a(請求項の第1の抵抗に相当)を介して、高電位側Nチャネル型MOS−FET10aに信号を印加することで、高電位側Nチャネル型MOS−FET10aをオンし、また、NPNトランジスタQ2a(請求項の第2のスイッチング素子に相当)をオンし、ゲート抵抗Rg2a(請求項の第2の抵抗に相当)を介してゲート端子を接地電位に接続することでゲート−ソース間の電位差を無くし、高電位側Nチャネル型MOS−FETをオフする。

【0029】

このような高電位側Nチャネル型MOS−FETのオン、オフ動作においては、上述のとおり、ゲート抵抗値がRg1a>Rg2aとなるように設定されているため、Nチャネル型MOS−FETの入力容量Cとゲート抵抗Rg1aあるいはRg2aで形成される積分回路の時定数が異なり、オン動作時よりもオフ動作時の方が速いスイッチング速度となる。

【0030】

従って、Nチャネル型MOS−FET10aのオフ動作時に、Nチャネル型MOS−FET10aのゲート端子を、ゲート抵抗Rg2a、NPNトランジスタQ2aを介して接地電位に接続するわけであるが、ゲート抵抗Rg2aは、上述のとおり、ゲート抵抗Rg1aより小さい値に設定されているため、スイッチング速度が速く、速やかにNチャネル型MOS−FET10aを完全にオフすることができ、続く動作によって、低電位側Nチャネル型MOS−FET10cがオンされても、高電位側Nチャネル型MOS−FET10a、低電位側Nチャネル型MOS−FET10cともにオンされ、短絡電流が流れてしまうことはない。

【0031】

このようなゲート駆動回路によれば、ゲート抵抗Rg1a、Rg2aの抵抗値をこのように設定して、オン動作時とオフ動作時のスイッチング速度を、オン動作時よりもオフ動作時の方が速くすることによって、トーテムポール型に接続されたNチャネル型MOS−FETをオンする際に生じる電磁ノイズを抑制することができる。

【0032】

また、図6に示した従来の装置のように負電源6a、6bを設ける必要がないため、車両用の電動パワーステアリング装置のように、単一の電源(電動パワーステアリング装置においては、車載バッテリ)を用いるものにおいても、負電源を作り出すために複雑な回路を追加する必要がなく、部品点数の増加、装置の大型化、コストアップを招くことはない。

【0033】

さらに、図7に示した従来の装置のように、ゲート駆動回路のNPNトランジスタのエミッタ端子と高電位側Nチャネル型MOS-FETのソース端子を接続するものではなく、モータ端子電圧検出回路にゲート電流が流れ込まず、モータ端子電圧の検出に誤差が生じることがなく、電動パワーステアリング装置等に使用した際にも、その誤差の影響で、装置の操舵フィーリングの悪化や商品性の劣化を招くことがない。

【0034】

以上説明したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、このようなゲート駆動回路をディスクリート構成としてもよいが、図2(a)に示すように、信号源を含めて単一のIC300として構成してもよい。すなわち、1つのNチャネル型MOS−FETに対して、2つのポートを持つICとして構成してもよい。これにより、ICのチップサイズは増大させることなく、ゲート抵抗を変更するだけで最適なスイッチング速度が得られ、装置全体が小型化でき、かつ、設計自由度が向上する。

【0035】

なお、図2(a)では、単一のパワーMOS−FETを駆動するための信号源およびゲート駆動回路のみをIC300として構成するものを示したが、図2(b)に示すように、Hブリッジ回路を構成する全てのパワーMOS−FET10a,10b,10c,10dを駆動するための信号源4a,4b,4c,4dおよびゲート駆動回路30a,30b,30c、30d全てを単一のICとして構成しても何ら差し支えない。

【0036】

また、この図2(b)では、Hブリッジ回路構成のモータ駆動回路を例にとったため、信号源およびゲート駆動回路はそれぞれ4つとしたが、3相ブリッジ回路であれば、それぞれ6つとなるのは自明であり、要は、駆動されるパワーMOS−FETの個数と同数の信号源およびゲート駆動回路を単一のICとして構成すればよい。これによれば、一般的によく用いられる、Hブリッジ回路や三相ブリッジ回路等に対して、各1種のICを準備すれば、ゲート抵抗を変更するのみで、スイッチング速度を任意に変更でき、標準化や部品点数の低減を実現することができる。さらに、トーテムポール型に接続された2つのパワーMOS−FETを駆動するために、信号源およびゲート駆動回路それぞれ2つずつを単一のICとして構成してもよく、この場合、モータ駆動回路の相数が異なっても、同じICを使用できるため、幾分、部品点数は増えるものの、より進んだ標準化を実現できる。

【0037】

また、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、オン側およびオフ側のいずれにもゲート抵抗を備えるものについて説明したが、図3に示すようにオフ側のゲート抵抗を備えず、Nチャネル型MOS−FETのゲート端子とゲート駆動回路のNPNトランジスタのコレクタ端子を直接接続して(すなわち、オフ側のゲート回路Rg2aは、Nチャネル型MOS−FETのゲート端子とNPNトランジスタのコレクタ端子間の配線抵抗のみとする構成にして)も良い。このように構成すれば、部品点数をさらに低減でき、オフ動作時のスイッチング速度をさらに速めることができ、オフ動作時のスイッチング損失をより低減できる。

【0038】

また、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、ゲート駆動回路として、PNPトランジスタとNPNトランジスタを備えるものについて説明したが、これに限られるものではなく、同種のトランジスタ2つを用い、その一方の入力段に反転回路(インバータ)を備えるようにしてもよく、またFET等他のスイッチング素子で構成してもよい。

【0039】

なお、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、高電位側Nチャネル型MOS−FETを駆動するためのゲート駆動回路のみを、オン側およびオフ側のゲート抵抗を介して接続するものとしたが、低電位側Nチャネル型MOS−FETを駆動するゲート駆動回路も同様の構成としても何ら差し支えない。さらに、上述したこの発明の実施の形態1に係るゲート駆動回路を備えるモータの駆動回路では、電気負荷駆動回路として、Hブリッジ回路を用いたものについて説明したが、これ以外のもの、例えばハーフブリッジ回路、多相ブリッジ回路等、いわゆるトーテムポール型に接続された電気負荷駆動回路であれば、いずれの形のものでも同様に適用できるものである。

【符号の説明】

【0040】

1:Hブリッジ回路、10a〜10d:Nチャネル型MOS−FET、2:バッテリ、30a〜30d:ゲート駆動回路、300:IC、4a〜4d:信号源、5a,5b:モータ端子電圧検出回路、M:モータ、Q1a:PNPトランジスタ(第1のスイッチング素子)、Q2a:NPNトランジスタ(第2のスイッチング素子)、Rg1a:ゲート抵抗(第1の抵抗)、Rg2a:ゲート抵抗(第2の抵抗)

【特許請求の範囲】

【請求項1】

パワーMOS−FETを駆動するためのゲート駆動回路において、

前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧に接続させる第1のスイッチング素子と、

前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、

前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されていることを特徴とするゲート駆動回路。

【請求項2】

前記第2の抵抗は、前記MOS−FETのゲート端子と前記第2のスイッチング素子の間の配線抵抗であることを特徴とする請求項1記載のゲート駆動回路。

【請求項3】

複数の前記ゲート駆動回路をICとして構成し、第1の抵抗を接続するための第1のスイッチング素子と、第2の抵抗を接続するための第2のスイッチング素子を、異なるピンに出力することを特徴とする請求項1または2いずれか記載のゲート駆動回路。

【請求項4】

前記ICは、前記第1スイッチング素子と前記第2スイッチング素子を2組ずつ備えることを特徴とする請求項3記載のゲート駆動回路。

【請求項5】

前記ICは、前記第1スイッチング素子と前記第2スイッチング素子をそれぞれ、前記駆動されるパワーMOS−FETの個数と同数備えることを特徴とする請求項3記載のゲート駆動回路。

【請求項1】

パワーMOS−FETを駆動するためのゲート駆動回路において、

前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧に接続させる第1のスイッチング素子と、

前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、

前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されていることを特徴とするゲート駆動回路。

【請求項2】

前記第2の抵抗は、前記MOS−FETのゲート端子と前記第2のスイッチング素子の間の配線抵抗であることを特徴とする請求項1記載のゲート駆動回路。

【請求項3】

複数の前記ゲート駆動回路をICとして構成し、第1の抵抗を接続するための第1のスイッチング素子と、第2の抵抗を接続するための第2のスイッチング素子を、異なるピンに出力することを特徴とする請求項1または2いずれか記載のゲート駆動回路。

【請求項4】

前記ICは、前記第1スイッチング素子と前記第2スイッチング素子を2組ずつ備えることを特徴とする請求項3記載のゲート駆動回路。

【請求項5】

前記ICは、前記第1スイッチング素子と前記第2スイッチング素子をそれぞれ、前記駆動されるパワーMOS−FETの個数と同数備えることを特徴とする請求項3記載のゲート駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−188271(P2011−188271A)

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願番号】特願2010−51813(P2010−51813)

【出願日】平成22年3月9日(2010.3.9)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願日】平成22年3月9日(2010.3.9)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]