ゲート駆動回路

【課題】スイッチング損失低減のためにゲート抵抗を小さくすると、ゲート・ソース間電圧が振動しスイッチング素子が誤動作すること、ゲート駆動回路用電源が大型になることなどが問題となる。

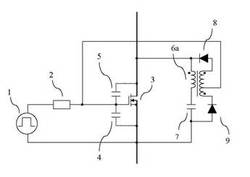

【解決手段】トランス6aとコンデンサ7の直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した第1の巻線を第1のダイオード8を介して前記スイッチング素子の正極端子とゲート端子との間に、前記トランスと磁気結合した第2の巻線を第2のダイオード9を介して前記スイッチング素子の負側端子とゲート端子との間に、各々接続する。

【解決手段】トランス6aとコンデンサ7の直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した第1の巻線を第1のダイオード8を介して前記スイッチング素子の正極端子とゲート端子との間に、前記トランスと磁気結合した第2の巻線を第2のダイオード9を介して前記スイッチング素子の負側端子とゲート端子との間に、各々接続する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、IGBTやMOSFETなどのスイッチング素子に適用するゲート駆動回路に関する。

【背景技術】

【0002】

図5に従来のゲート駆動方式、図6にその動作波形を示す。スイッチング素子としてMOSFETを用いた時の構成である。ゲート信号生成部1で生成されるゲート信号V1はゲート抵抗2を介してMOSFET3のゲート・ソース間に入力される。ターンオン時におけるt2の期間では、MOSFET 3に寄生する入力容量4が充電されてゲート電圧VGSが上昇し、ゲート閾値電圧を超えるとMOSFET3がオンし、ドレイン電流IDが流れ始める。

【0003】

期間t3では、ゲート信号生成部1→ゲート抵抗2→入力容量4→ゲート信号生成部1の経路で入力容量4に流れていた電流がゲート信号生成部1→ゲート抵抗2→帰還容量5→MOSFET3→ゲート信号生成部1の経路で帰還容量5を放電させる経路に転流し、ゲート・ソース間電圧VGSの上昇が停止する。帰還容量5に蓄えられていた電荷が放電されてドレイン・ゲート間電圧が低下するのと同時にドレイン・ソース間電圧VDSも低下する。この期間では入力容量4を充電する電流は流れないので、ゲート・ソース間電圧VGSは一定となる。帰還容量5の電荷が放出され、ドレイン・ソース間電圧VDSが零になると、期間t4において再び入力容量4を充電する電流が流れ始め、ゲート・ソース間電圧VGSは上昇する。

【0004】

一方、ターンオフ時においては次の動作となる。ゲート信号生成部1から出力されるゲート信号V1がオフに変化した後の期間t5では、入力容量4に蓄えられている電荷がゲート抵抗2を介して放電するため、ゲート・ソース間電圧VGSが閾値電圧まで低下する。期間t6ではドレイン・ソース間電圧VDSが上昇し、同時に帰還容量5が充電される。その充電電流はMOSFET3のドレイン→帰還容量5→入力容量4→MOSFET3のソースの経路で流れる。この時、入力容量4からゲート信号生成部1に放電する電流は入力容量4→ゲート抵抗2→ゲート信号生成部1→入力容量4の経路で逆方向に流れるので、入力容量4の電流は帰還容量5からの充電電流とゲート信号生成部1への放電電流とで相殺され、零となる。よって、この期間ではゲート電圧は一定となる。

【0005】

期間t6においてドレイン・ソース間電圧VDSが定常電圧になると帰還容量5の充電も終了し、MOSFET3のドレイン→帰還容量5→入力容量4→MOSFET3のソースで流れていた帰還容量5の充電電流も無くなるので、再びゲート・ソース間電圧VGSが低下する。この期間で、ゲート・ソース間電圧VGSが閾値電圧を下回るとドレイン電流IDも減少する。

上述のような動作において、帰還容量5が放電される期間t3と充電される期間t6において、ドレイン電流IDが大きな値を保ちながらドレイン・ソース間電圧VDSが変化する。スイッチング損失はスイッチング期間におけるドレイン・ソース間電圧VDSとドレイン電流IDの積を積分した値となるので、期間t3とt6が長くなるほどスイッチング損失が増加する。

【0006】

一般に、期間t3とt6を短くするためにゲート抵抗2を小さく設定して、大きな電流で入力容量4を急速に充放電する手法が用いられる。これにより、帰還容量5の充放電も高速になる。しかし、ゲート信号生成部1にも内部抵抗が存在し、外部で調整可能なゲート抵抗2を小さくしても限界がある。また、ゲート抵抗2を小さく設定すると、電源容量が増大すると共に、配線インダクタンスと帰還容量5や入力容量4の容量性成分で共振してゲート・ソース間電圧VGSが変動したり、僅かなノイズによりゲート・ソース間電圧VGSが変動してしまい、所望の制御とは異なるタイミングでMOSFET3がオン・オフしてしまういわゆる誤動作の恐れがある。

【0007】

図7に、特許文献1に示された高速化によりスイッチング損失を減らすゲート駆動回路例を示す。MOSFET3のドレインと直列にトランスを接続し、このトランスの二次巻線をゲート信号生成部1とMOSFET3のゲート端子との間に抵抗2を介して接続する構成である。ターンオン時にドレイン電流が増加し始めると、ゲート信号生成部1からオン電圧信号にトランスの二次巻線電圧の誘起電圧が加算され、ターンオンスピードが高速化される。また、ターンオフ時も同様にドレイン電流が減少を始めると、ゲート信号生成部からオフ電圧信号にトランスの二次巻線電圧の誘起電圧が減算され、ターンオフスピードが高速化される。ゲート駆動回路の容量を大きくする必要がないこと、ゲート抵抗を小さくする必要がないことなどの特長がある。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−235997号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上述のように、スイッチング損失低減のためにゲート抵抗を小さくすると、ゲート・ソース間電圧が振動しスイッチング素子が誤動作すること、ゲート駆動回路用電源が大型になることなどが問題となる。また、図7に示した特許文献1の方式では、トランスの偏磁が問題となるため、磁気リセット回路が必要となり、装置が大型となる問題がある。

従って、本発明の課題は、装置の大型化やゲート駆動電源の容量増大が不要で、スイッチング損失を低減できるゲート駆動回路を提供することである。

【課題を解決するための手段】

【0010】

上述の課題を解決するために、第1の発明においては、トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線を介して前記スイッチング素子の帰還容量にエネルギーを供給する。

【0011】

第2の発明においては、トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した第1の巻線を第1のダイオードを介して前記スイッチング素子の正極端子とゲート端子との間に接続し、前記トランスと磁気結合した第2の巻線を第2のダイオードを介して前記スイッチング素子の負側端子とゲート端子との間に接続する。

【0012】

第3の発明においては、第1又は第2の発明において、前記トランスと磁気結合した第1の巻線と帰還容量間又は入力容量間に電流を制限する部品を挿入する。

【0013】

第4の発明においては、トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線をゲート信号生成部と前記スイッチング素子のゲート端子との間に抵抗を介して接続する。

【発明の効果】

【0014】

本発明では、スイッチング素子と並列にトランスとコンデンサの直列回路を接続し、前記トランスと磁気結合した別の巻線のエネルギーとゲート信号生成部のエネルギーとでドレイン・ゲート間容量を充放電しているため、ゲート駆動電源の容量を増加させたり、ゲート抵抗を小さくする必要がなく、高速のターンオン動作とターンオフ動作が可能で、スイッチング損失の低減が可能となる。

【0015】

この結果、ゲート抵抗を小さくする必要がないので、振動や誤動作が生じない。また、ゲート駆動電源の容量を大きくする必要もない。さらに、トランスの偏磁の問題もなくなるので磁気リセット回路が不要で、装置の小型化が可能となる。

【図面の簡単な説明】

【0016】

【図1】本発明の第1の実施例を示す回路図である。

【図2】図1の動作波形図である。

【図3】本発明の第2の実施例を示す回路図である。

【図4】本発明の第3の実施例を示す回路図である。

【図5】従来例1を説明するための図である。

【図6】図5の動作波形図である。

【図7】従来例2を示す回路図である。

【発明を実施するための形態】

【0017】

本発明の要点は、スイッチング素子と並列にトランスとコンデンサの直列回路を接続し、前記トランスと磁気結合した別の巻線のエネルギーとゲート信号生成部のエネルギーとでドレイン・ゲート間容量を充放電している点である。

【実施例1】

【0018】

図1に本発明の第1の実施例を、図2に図1の動作波形例を示す。スイッチング素子としてMOSFETを用いた構成である。まず、ターンオン時の動作について説明する。ここで、期間t1とt2では図5と図6に示した従来技術と同様な動作となる。期間t3では、コンデンサ7に蓄えられている電荷がコンデンサ7→トランス6a→MOSFET3→コンデンサ7の経路で零になるまで放電する。同時に、トランス6aにおける別巻線の中間タップからダイオード9を介して入力容量4を充電する電流が流れる。この期間に、入力容量4を充電することによって、帰還容量5の放電も早くなる。よって、入力容量4の充電と帰還容量5の放電が急速に行われ、t3の期間が短くなる。これにより、スイッチングスピードも増加し、ターンオン損失が低減される。

【0019】

ターンオフ動作においては、期間t5とt6で図5と図6に示す従来技術と同様な動作となる。しかし、本発明では期間t6において、MOSFET3のドレイン・ソース間電圧VDSの上昇とともにコンデンサ7が充電される。その充電電流がトランス6aにも流れるので、トランス6aの巻線→ダイオード8→帰還容量5→トランス6aの中間タップの経路で帰還容量5を充電する電流が流れる。よって、帰還容量5の電圧は急速に上昇するため、期間t6が短くなり、スイッチングスピードが増加し、ターンオフ時のスイッチング損失が低減される。

【0020】

従って、本発明ではターンオン時だけでなく、ターンオフ時においても高速スイッチングが可能となり、効果的にスイッチング損失を低減できる。なお、本発明はMOSFETだけでなく、IGBTなどのスイッチング素子にも同様に適用できる。

【実施例2】

【0021】

図3に、本発明の第2の実施例を示す。第1の実施例との違いは、電流を制限する部品として抵抗10がトランス6aの中間タップとMOSFET3のゲート端子との間に接続されている点である。ここで、トランス6aから帰還容量5または入力容量4を充電する電流は抵抗10で調整可能となり、ドレイン・ゲート間電圧やゲート・ソース間電圧の変化率も調整可能となる。よって、抵抗10の値によってスイッチングスピードを調整できる。これにより、スイッチング時の跳ね上り電圧やノイズも低減でき、装置の低ノイズ化や信頼性の向上につながる。

【実施例3】

【0022】

図4に、本発明の第3の実施例を示す。MOSFET3と並列にトランス6bとコンデンサ7の直列回路が接続されている。磁気結合されたトランス6bの別の巻線はゲート信号生成部1とMOSFET3のゲート端子との間に抵抗を介して接続される。このような構成において、ターンオン動作時はゲート信号生成部1からの信号により入力容量4が閾値電圧まで充電された後MOSFET3がオンし始めるとコンデンサ7の電荷はトランス6bを通ってMOSFET3で放電を始める。すると、トランス6bの磁気結合された別の巻線には電圧が誘起され、ゲート信号生成部1の電圧に加算された電圧がMOSFETのゲート端子に印加される。この結果、帰還容量5は急速に放電されることになり、MOSFET3は高速にターンオンする。

【0023】

また、ターンオフ動作時はゲート信号生成部1からの信号により入力容量4が閾値電圧まで放電された後MOSFET3がオフし始めるとコンデンサ7にはトランス6bを通って電流が流れ始める。すると、トランス6bの磁気結合された別巻線に電圧が誘起され、ゲート信号生成部の電圧を減少させ、MOSFET3のオフ動作を加速させる。

上述の動作により、ターンオン時及びターンオフ時のスイッチング損失を低減させることができる。この動作においては、トランス6bの励磁はコンデンサ7の短時間の充電時と短時間の放電時だけであり、偏磁に至ることはない。

尚、上記実施例にはスイッチング素子としてMOSFETを用いた例を示したが、IGBTなどの電圧駆動型素子でも実現可能である。

【符号の説明】

【0024】

1・・・ゲート信号生成部 2、10・・・抵抗

3・・・MOSFET 4・・・入力容量

5・・・帰還容量 6a、6b、6c・・・トランス

7・・・コンデンサ 8、9・・・ダイオード

【技術分野】

【0001】

本発明は、IGBTやMOSFETなどのスイッチング素子に適用するゲート駆動回路に関する。

【背景技術】

【0002】

図5に従来のゲート駆動方式、図6にその動作波形を示す。スイッチング素子としてMOSFETを用いた時の構成である。ゲート信号生成部1で生成されるゲート信号V1はゲート抵抗2を介してMOSFET3のゲート・ソース間に入力される。ターンオン時におけるt2の期間では、MOSFET 3に寄生する入力容量4が充電されてゲート電圧VGSが上昇し、ゲート閾値電圧を超えるとMOSFET3がオンし、ドレイン電流IDが流れ始める。

【0003】

期間t3では、ゲート信号生成部1→ゲート抵抗2→入力容量4→ゲート信号生成部1の経路で入力容量4に流れていた電流がゲート信号生成部1→ゲート抵抗2→帰還容量5→MOSFET3→ゲート信号生成部1の経路で帰還容量5を放電させる経路に転流し、ゲート・ソース間電圧VGSの上昇が停止する。帰還容量5に蓄えられていた電荷が放電されてドレイン・ゲート間電圧が低下するのと同時にドレイン・ソース間電圧VDSも低下する。この期間では入力容量4を充電する電流は流れないので、ゲート・ソース間電圧VGSは一定となる。帰還容量5の電荷が放出され、ドレイン・ソース間電圧VDSが零になると、期間t4において再び入力容量4を充電する電流が流れ始め、ゲート・ソース間電圧VGSは上昇する。

【0004】

一方、ターンオフ時においては次の動作となる。ゲート信号生成部1から出力されるゲート信号V1がオフに変化した後の期間t5では、入力容量4に蓄えられている電荷がゲート抵抗2を介して放電するため、ゲート・ソース間電圧VGSが閾値電圧まで低下する。期間t6ではドレイン・ソース間電圧VDSが上昇し、同時に帰還容量5が充電される。その充電電流はMOSFET3のドレイン→帰還容量5→入力容量4→MOSFET3のソースの経路で流れる。この時、入力容量4からゲート信号生成部1に放電する電流は入力容量4→ゲート抵抗2→ゲート信号生成部1→入力容量4の経路で逆方向に流れるので、入力容量4の電流は帰還容量5からの充電電流とゲート信号生成部1への放電電流とで相殺され、零となる。よって、この期間ではゲート電圧は一定となる。

【0005】

期間t6においてドレイン・ソース間電圧VDSが定常電圧になると帰還容量5の充電も終了し、MOSFET3のドレイン→帰還容量5→入力容量4→MOSFET3のソースで流れていた帰還容量5の充電電流も無くなるので、再びゲート・ソース間電圧VGSが低下する。この期間で、ゲート・ソース間電圧VGSが閾値電圧を下回るとドレイン電流IDも減少する。

上述のような動作において、帰還容量5が放電される期間t3と充電される期間t6において、ドレイン電流IDが大きな値を保ちながらドレイン・ソース間電圧VDSが変化する。スイッチング損失はスイッチング期間におけるドレイン・ソース間電圧VDSとドレイン電流IDの積を積分した値となるので、期間t3とt6が長くなるほどスイッチング損失が増加する。

【0006】

一般に、期間t3とt6を短くするためにゲート抵抗2を小さく設定して、大きな電流で入力容量4を急速に充放電する手法が用いられる。これにより、帰還容量5の充放電も高速になる。しかし、ゲート信号生成部1にも内部抵抗が存在し、外部で調整可能なゲート抵抗2を小さくしても限界がある。また、ゲート抵抗2を小さく設定すると、電源容量が増大すると共に、配線インダクタンスと帰還容量5や入力容量4の容量性成分で共振してゲート・ソース間電圧VGSが変動したり、僅かなノイズによりゲート・ソース間電圧VGSが変動してしまい、所望の制御とは異なるタイミングでMOSFET3がオン・オフしてしまういわゆる誤動作の恐れがある。

【0007】

図7に、特許文献1に示された高速化によりスイッチング損失を減らすゲート駆動回路例を示す。MOSFET3のドレインと直列にトランスを接続し、このトランスの二次巻線をゲート信号生成部1とMOSFET3のゲート端子との間に抵抗2を介して接続する構成である。ターンオン時にドレイン電流が増加し始めると、ゲート信号生成部1からオン電圧信号にトランスの二次巻線電圧の誘起電圧が加算され、ターンオンスピードが高速化される。また、ターンオフ時も同様にドレイン電流が減少を始めると、ゲート信号生成部からオフ電圧信号にトランスの二次巻線電圧の誘起電圧が減算され、ターンオフスピードが高速化される。ゲート駆動回路の容量を大きくする必要がないこと、ゲート抵抗を小さくする必要がないことなどの特長がある。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−235997号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上述のように、スイッチング損失低減のためにゲート抵抗を小さくすると、ゲート・ソース間電圧が振動しスイッチング素子が誤動作すること、ゲート駆動回路用電源が大型になることなどが問題となる。また、図7に示した特許文献1の方式では、トランスの偏磁が問題となるため、磁気リセット回路が必要となり、装置が大型となる問題がある。

従って、本発明の課題は、装置の大型化やゲート駆動電源の容量増大が不要で、スイッチング損失を低減できるゲート駆動回路を提供することである。

【課題を解決するための手段】

【0010】

上述の課題を解決するために、第1の発明においては、トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線を介して前記スイッチング素子の帰還容量にエネルギーを供給する。

【0011】

第2の発明においては、トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した第1の巻線を第1のダイオードを介して前記スイッチング素子の正極端子とゲート端子との間に接続し、前記トランスと磁気結合した第2の巻線を第2のダイオードを介して前記スイッチング素子の負側端子とゲート端子との間に接続する。

【0012】

第3の発明においては、第1又は第2の発明において、前記トランスと磁気結合した第1の巻線と帰還容量間又は入力容量間に電流を制限する部品を挿入する。

【0013】

第4の発明においては、トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線をゲート信号生成部と前記スイッチング素子のゲート端子との間に抵抗を介して接続する。

【発明の効果】

【0014】

本発明では、スイッチング素子と並列にトランスとコンデンサの直列回路を接続し、前記トランスと磁気結合した別の巻線のエネルギーとゲート信号生成部のエネルギーとでドレイン・ゲート間容量を充放電しているため、ゲート駆動電源の容量を増加させたり、ゲート抵抗を小さくする必要がなく、高速のターンオン動作とターンオフ動作が可能で、スイッチング損失の低減が可能となる。

【0015】

この結果、ゲート抵抗を小さくする必要がないので、振動や誤動作が生じない。また、ゲート駆動電源の容量を大きくする必要もない。さらに、トランスの偏磁の問題もなくなるので磁気リセット回路が不要で、装置の小型化が可能となる。

【図面の簡単な説明】

【0016】

【図1】本発明の第1の実施例を示す回路図である。

【図2】図1の動作波形図である。

【図3】本発明の第2の実施例を示す回路図である。

【図4】本発明の第3の実施例を示す回路図である。

【図5】従来例1を説明するための図である。

【図6】図5の動作波形図である。

【図7】従来例2を示す回路図である。

【発明を実施するための形態】

【0017】

本発明の要点は、スイッチング素子と並列にトランスとコンデンサの直列回路を接続し、前記トランスと磁気結合した別の巻線のエネルギーとゲート信号生成部のエネルギーとでドレイン・ゲート間容量を充放電している点である。

【実施例1】

【0018】

図1に本発明の第1の実施例を、図2に図1の動作波形例を示す。スイッチング素子としてMOSFETを用いた構成である。まず、ターンオン時の動作について説明する。ここで、期間t1とt2では図5と図6に示した従来技術と同様な動作となる。期間t3では、コンデンサ7に蓄えられている電荷がコンデンサ7→トランス6a→MOSFET3→コンデンサ7の経路で零になるまで放電する。同時に、トランス6aにおける別巻線の中間タップからダイオード9を介して入力容量4を充電する電流が流れる。この期間に、入力容量4を充電することによって、帰還容量5の放電も早くなる。よって、入力容量4の充電と帰還容量5の放電が急速に行われ、t3の期間が短くなる。これにより、スイッチングスピードも増加し、ターンオン損失が低減される。

【0019】

ターンオフ動作においては、期間t5とt6で図5と図6に示す従来技術と同様な動作となる。しかし、本発明では期間t6において、MOSFET3のドレイン・ソース間電圧VDSの上昇とともにコンデンサ7が充電される。その充電電流がトランス6aにも流れるので、トランス6aの巻線→ダイオード8→帰還容量5→トランス6aの中間タップの経路で帰還容量5を充電する電流が流れる。よって、帰還容量5の電圧は急速に上昇するため、期間t6が短くなり、スイッチングスピードが増加し、ターンオフ時のスイッチング損失が低減される。

【0020】

従って、本発明ではターンオン時だけでなく、ターンオフ時においても高速スイッチングが可能となり、効果的にスイッチング損失を低減できる。なお、本発明はMOSFETだけでなく、IGBTなどのスイッチング素子にも同様に適用できる。

【実施例2】

【0021】

図3に、本発明の第2の実施例を示す。第1の実施例との違いは、電流を制限する部品として抵抗10がトランス6aの中間タップとMOSFET3のゲート端子との間に接続されている点である。ここで、トランス6aから帰還容量5または入力容量4を充電する電流は抵抗10で調整可能となり、ドレイン・ゲート間電圧やゲート・ソース間電圧の変化率も調整可能となる。よって、抵抗10の値によってスイッチングスピードを調整できる。これにより、スイッチング時の跳ね上り電圧やノイズも低減でき、装置の低ノイズ化や信頼性の向上につながる。

【実施例3】

【0022】

図4に、本発明の第3の実施例を示す。MOSFET3と並列にトランス6bとコンデンサ7の直列回路が接続されている。磁気結合されたトランス6bの別の巻線はゲート信号生成部1とMOSFET3のゲート端子との間に抵抗を介して接続される。このような構成において、ターンオン動作時はゲート信号生成部1からの信号により入力容量4が閾値電圧まで充電された後MOSFET3がオンし始めるとコンデンサ7の電荷はトランス6bを通ってMOSFET3で放電を始める。すると、トランス6bの磁気結合された別の巻線には電圧が誘起され、ゲート信号生成部1の電圧に加算された電圧がMOSFETのゲート端子に印加される。この結果、帰還容量5は急速に放電されることになり、MOSFET3は高速にターンオンする。

【0023】

また、ターンオフ動作時はゲート信号生成部1からの信号により入力容量4が閾値電圧まで放電された後MOSFET3がオフし始めるとコンデンサ7にはトランス6bを通って電流が流れ始める。すると、トランス6bの磁気結合された別巻線に電圧が誘起され、ゲート信号生成部の電圧を減少させ、MOSFET3のオフ動作を加速させる。

上述の動作により、ターンオン時及びターンオフ時のスイッチング損失を低減させることができる。この動作においては、トランス6bの励磁はコンデンサ7の短時間の充電時と短時間の放電時だけであり、偏磁に至ることはない。

尚、上記実施例にはスイッチング素子としてMOSFETを用いた例を示したが、IGBTなどの電圧駆動型素子でも実現可能である。

【符号の説明】

【0024】

1・・・ゲート信号生成部 2、10・・・抵抗

3・・・MOSFET 4・・・入力容量

5・・・帰還容量 6a、6b、6c・・・トランス

7・・・コンデンサ 8、9・・・ダイオード

【特許請求の範囲】

【請求項1】

トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線を介して前記スイッチング素子の帰還容量にエネルギーを供給することを特徴としたゲート駆動回路

【請求項2】

トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した第1の巻線を第1のダイオードを介して前記スイッチング素子の正極端子とゲート端子との間に接続し、前記トランスと磁気結合した第2の巻線を第2のダイオードを介して前記スイッチング素子の負側端子とゲート端子との間に接続したことを特徴とするゲート駆動回路

【請求項3】

前記トランスと磁気結合した第1の巻線と帰還容量間又は入力容量間に電流を制限する部品を挿入することを特徴とした請求項1又は2に記載のゲート駆動回路。

【請求項4】

トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線をゲート信号生成部と前記スイッチング素子のゲート端子との間に抵抗を介して接続したことを特徴とするゲート駆動回路。

【請求項1】

トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線を介して前記スイッチング素子の帰還容量にエネルギーを供給することを特徴としたゲート駆動回路

【請求項2】

トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した第1の巻線を第1のダイオードを介して前記スイッチング素子の正極端子とゲート端子との間に接続し、前記トランスと磁気結合した第2の巻線を第2のダイオードを介して前記スイッチング素子の負側端子とゲート端子との間に接続したことを特徴とするゲート駆動回路

【請求項3】

前記トランスと磁気結合した第1の巻線と帰還容量間又は入力容量間に電流を制限する部品を挿入することを特徴とした請求項1又は2に記載のゲート駆動回路。

【請求項4】

トランスとコンデンサの直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した別巻線をゲート信号生成部と前記スイッチング素子のゲート端子との間に抵抗を介して接続したことを特徴とするゲート駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−41401(P2011−41401A)

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願番号】特願2009−186556(P2009−186556)

【出願日】平成21年8月11日(2009.8.11)

【出願人】(000005234)富士電機ホールディングス株式会社 (3,146)

【Fターム(参考)】

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願日】平成21年8月11日(2009.8.11)

【出願人】(000005234)富士電機ホールディングス株式会社 (3,146)

【Fターム(参考)】

[ Back to top ]