ゲート駆動回路

【課題】ワイドギャップ半導体のターンオフの速度を高速化できるゲート駆動回路。

【解決手段】負極が接地された正電源E1と、正極が接地された負電源E2と、正電源の正極と負電源の負極との間に設けられ、制御信号を生成する制御回路11と、正電源の正極と負電源の負極との間に設けられたトランジスタQ1とトランジスタQ2との直列回路と、ドレイン端子、接地されたソース端子及びQ1とQ2との接続点に接続されたゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子GaNFETと、制御信号のオフ時にQ1を所定時間だけオンさせQ1を介して負電源の電圧をスイッチング素子のゲート端子に印加するターンオフ制御回路13と、スイッチング素子のゲート端子と接地との間に設けられ、制御信号のオフ時にそのゲート端子とソース端子を短絡させるトランジスタQ3とトランジスタQ4との直列回路を備える。

【解決手段】負極が接地された正電源E1と、正極が接地された負電源E2と、正電源の正極と負電源の負極との間に設けられ、制御信号を生成する制御回路11と、正電源の正極と負電源の負極との間に設けられたトランジスタQ1とトランジスタQ2との直列回路と、ドレイン端子、接地されたソース端子及びQ1とQ2との接続点に接続されたゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子GaNFETと、制御信号のオフ時にQ1を所定時間だけオンさせQ1を介して負電源の電圧をスイッチング素子のゲート端子に印加するターンオフ制御回路13と、スイッチング素子のゲート端子と接地との間に設けられ、制御信号のオフ時にそのゲート端子とソース端子を短絡させるトランジスタQ3とトランジスタQ4との直列回路を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路に関する。

【背景技術】

【0002】

特許文献1には、還流ダイオードを省略したゲート駆動回路が開示されている。図8は、特許文献1に開示されたゲート駆動回路の回路図であり、図9は、図8に示すゲート駆動回路の動作を示すタイミングチャートである。このゲート駆動回路は、フォトカプラ41、駆動電源44、抵抗45、PNPトランジスタ46、NPNトランジスタ47及びダイオード48を備え、図示しないコンバータ回路のスイッチング素子T1及びT2をオンオフさせる。なお、図8では、スイッチング素子T2を制御するための回路は、スイッチング素子T1のそれらの回路と同一であるので、省略されている。

【0003】

このゲート駆動回路では、MOSFETからなるスイッチング素子T1,T2におけるドレイン電位がソース電位より低くなると、スイッチング素子T1,T2のゲートGにコレクタが接続されたPNPトランジスタ46のベースからスイッチング素子T1,T2のドレインへ電流を流すダイオード48が設けられている。これにより、PNPトランジスタ46のベース電位がゼロになり、スイッチング素子T1,T2のゲートGにオン電圧が印加されるので、回生(還流)ダイオードをスイッチング素子T1,T2で代用できる。

【0004】

ところで、例えば窒化ガリウム電界効果トランジスタ(GaNFET)はボディーダイオードを備えていないが、構造上、双方向に電流を流すことができる特性を有する。回生電流などのような逆方向の電流を流す場合、電流が流れ出す閾値電圧はゲート端子の電圧に依存する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−61413号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に開示された技術では、スイッチング素子のターンオフは、NPNトランジスタ47によるスイッチング素子T1,T2のゲート−ソース間の電圧をゼロにすることにより行われている。ところが、スイッチング素子のゲート−ソース間にはゲート容量が存在し、ゲート−ソース間を単にショートするだけではターンオフ時間を速めることができず、スイッチング損失を減らすことができない。

【0007】

したがって、GaNFETなどのワイドギャップ半導体のターンオフ時のスイッチング速度を高速化し、かつ、回生電流が流れる場合はワイドギャップ半導体を回生ダイオードとして機能させることができるゲート駆動回路が望まれている。

【0008】

本発明の課題は、ワイドギャップ半導体のターンオフ時のスイッチング速度を高速化し、かつ、回生電流が流れる場合はワイドギャップ半導体を回生ダイオードとして機能させることができるゲート駆動回路を提供することにある。

【課題を解決するための手段】

【0009】

上記の課題を解決するために、本発明に係るゲート駆動回路は、負極が接地された正電源と、正極が接地された負電源と、前記正電源の正極と前記負電源の負極との間に設けられ、制御信号を生成する制御回路と、前記正電源の正極と前記負電源の負極との間に設けられた第1トランジスタと第2トランジスタとの直列回路と、ドレイン、接地されたソース及び前記第1トランジスタと第2トランジスタとの接続点に接続されたゲートを備えたワイドバンドギャップ半導体からなるスイッチング素子と、前記制御回路からの制御信号がオフになった場合に、前記第1トランジスタを所定時間だけオンさせ前記第1トランジスタを介して前記負電源の電圧を前記スイッチング素子のゲート端子に印加するターンオフ制御回路と、前記スイッチング素子のゲートとソースとの間に設けられ、前記制御回路からの制御信号がオフになった場合に、前記スイッチング素子のゲートとソースとの間を短絡させる第3トランジスタと第4トランジスタとの直列回路とを備えることを特徴とする。

【発明の効果】

【0010】

本発明に係るゲート駆動回路によれば、ワイドギャップ半導体のターンオフ時のスイッチング速度を高速化し、かつ、回生電流が流れる場合はワイドギャップ半導体を回生ダイオードとして機能させることができる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施例1に係るゲート駆動回路の構成を示す図である。

【図2】本発明の実施例1に係るゲート駆動回路の動作を示すタイミングチャートである。

【図3】本発明の実施例1に係るゲート駆動回路で使用される双方向のスイッチング素子(GaNFET)の特性を示す図である。

【図4】本発明の実施例1に係るゲート駆動回路を電流共振型コンバータに応用した例を示す図である。

【図5】本発明の実施例2に係るゲート駆動回路の構成を示す図である。

【図6】本発明の実施例2に係るゲート駆動回路の動作を示すタイミングチャートである。

【図7】本発明の実施例2に係るゲート駆動回路を電流共振型コンバータに応用した例を示す図である。

【図8】従来のゲート駆動回路の構成を示す図である。

【図9】従来のゲート駆動回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態に係るゲート駆動回路について、図面を参照しながら詳細に説明する。

【実施例1】

【0013】

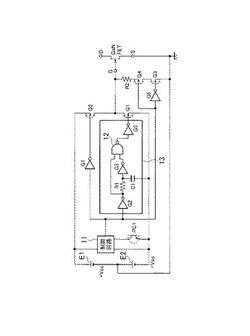

本発明の実施例1に係るゲート駆動回路は、2電源を備えている。図1は、本発明の実施例1に係るゲート駆動回路の構成を示す図である。このゲート駆動回路は、正電源E1、負電源E2、制御回路11、フォトカプラPC1、インバータG1、ターンオフ制御回路13、N型MOSFETからなるトランジスタQ1(第1トランジスタ)、P型MOSFETからなるトランジスタQ2(第2トランジスタ)、N型MOSFETからなるトランジスタQ3(第3トランジスタ)、P型MOSFETからなるトランジスタQ4(第4トランジスタ)、インバータG6、抵抗R2及びスイッチング素子GaNFETを備える。ターンオフ制御回路13は、インバータG2,G3,G5、NAND回路12、抵抗R1並びにコンデンサC1を備えている。

【0014】

スイッチング素子GaNFETは、ドレイン、ソース、ゲートを有しワイドバンドギャップ半導体からなる。なお、トランジスタQ3,Q4は、双方向スイッチを用いても良い。

【0015】

ゲート駆動回路は、インバータG1、ターンオフ制御回路13、トランジスタQ1〜Q4、インバータG6及び抵抗R2から構成されるが、ここでは、正電源E1、負電源E2、制御回路11、フォトカプラPC1及びスイッチング素子GaNFETを含めてゲート駆動回路と称する。

【0016】

正電源E1の正極は、制御回路11の正電源端子及びトランジスタQ2のソースに接続され、正電源E1の負極は、負電源E2の正極に接続されている。負電源E2の負極は、制御回路11の負電源端子、トランジスタQ1のソース、コンデンサC1及びフォトカプラPC1に接続されている。正電源E1の負極と負電源E2の正極との接続点は、接地されている。

【0017】

制御回路11は、正電源E1の正極と負電源E2の負極との間に設けられ、図示しない二次側回路からフィードバックされた信号を受信したフォトカプラPC1からの信号に応じて制御信号を生成し、インバータG1,G2,G6及びトランジスタQ4のゲートに出力する。

【0018】

インバータG1は、制御回路11からの制御信号を反転してトランジスタQ2のゲートに出力する。トランジスタQ2のソースは、正電源E1の正極に接続され、トランジスタQ2のドレインは、トランジスタQ1のドレインに接続されている。

【0019】

ターンオフ制御回路13内のインバータG2は、制御回路11からの制御信号を反転してナンド回路12の一方の入力端子に出力するとともに、抵抗R1を介してインバータG3に出力する。抵抗R1とインバータG3の入力端子との接続点には、コンデンサC1の一方の端子が接続され、コンデンサC1の他方の端子は、負電源E2の負極に接続されている。

【0020】

抵抗R1及びコンデンサC1は、CR積分による遅延回路を構成し、インバータG2からの信号を所定時間だけ遅延させてインバータG3に出力する。インバータG3は、遅延回路からの信号を反転してナンド回路12の他方の入力端子に出力する。

【0021】

ナンド回路12は、インバータG2からの信号とインバータG3からの信号との論理積をとった結果を反転し、インバータG5に出力する。インバータG5は、ナンド回路12からの信号を反転してトランジスタQ1のゲートに出力する。 このようなターンオフ制御回路13は、制御回路11からの制御信号の立ち下がりに応答して、即ち、制御信号がオフに変化したことに応答して、トランジスタQ1を所定時間だけオンさせる所定幅のHレベルのパルス信号を生成する。

【0022】

トランジスタQ1のドレインは、トランジスタQ2のドレインに接続され、ソースは、負電源E2の負極に接続されている。トランジスタQ1のドレインとトランジスタQ2のドレインとの接続点は、スイッチング素子GaNFETのゲートGに接続されている。スイッチング素子GaNFETのソースSは、接地されている。

【0023】

インバータG6は、制御回路11からの制御信号を反転してトランジスタQ3のゲートに出力する。トランジスタQ3のソースは、接地され、ドレインは、トランジスタQ4のドレインに接続されている。

【0024】

トランジスタQ4のソースは、抵抗R2を経由してスイッチング素子GaNFETのゲートGに接続され、ドレインは、トランジスタQ3のドレインに接続されている。トランジスタQ4のゲートには、制御回路11からの制御信号が入力される。

【0025】

次に、このように構成される実施例1に係るゲート駆動回路の動作を説明する。図2は、実施例1に係るゲート駆動回路の動作を示すタイミングチャートである。

【0026】

時刻t1において、図2(a)に示すように、制御回路11からHレベルの制御信号が出力されると、制御信号は、インバータG1でLレベルの信号に変換され、トランジスタQ2のゲートに印加される。これにより、図2(e)に示すように、トランジスタQ2がオンし、図2(h)に示すように、スイッチング素子GaNFETのゲートGに、正電源E1からの正電圧+Vccがゲート電圧Vgとして印加される。

【0027】

この時点でナンド回路12の出力はHレベルであるので、トランジスタQ1は、図2(f)に示すように、オフ状態である。コンデンサC1の電圧VC1は、インバータG2の出力がLレベルになることで、時刻t1aにおいて、放電によって充電電圧の1/2まで低下し、インバータG3の出力が反転する。しかし、ナンド回路12の一方の入力端子にはインバータG2から出力されるLレベルが入力され続けているので、ナンド回路12の出力はHレベルを維持して変化しない。

【0028】

時刻t2において、図2(a)に示すように、制御回路11からLレベルの制御信号が出力されると、制御信号は、インバータG1でHレベルの信号に変換され、トランジスタQ2のゲートに印加される。これにより、図2(e)に示すように、トランジスタQ2はオフする。また、図2(f)に示すように、ターンオフ制御回路13を介してトランジスタQ1がオンすると同時に、図2(g)に示すように、トランジスタQ4及びトランジスタQ3がオンする。

【0029】

したがって、時刻t2の時点では、スイッチング素子GaNFETのゲートGには負電源E2からの負電圧−Vccがゲート電圧Vgとして印加され、かつ、スイッチング素子GaNFETのゲートGとソースSとは、抵抗R2を介して短絡される。

【0030】

また、図2(b)に示すように、時刻t2においてインバータG2の出力がHレベルになるので、コンデンサC1には充電が開始され、図2(c)に示すように、時刻t3においてコンデンサC1は1/2まで充電される。これにより、インバータG3の出力が反転して、図2(f)に示すように、トランジスタQ1がオフされる。

【0031】

ここで、トランジスタQ3及びトランジスタQ4は、制御回路11から出力される制御信号がLレベルの期間はオン状態を保つので、時刻t6に至るまでスイッチング素子GaNFETのゲート−ソース間は抵抗R2を介して短絡されている。

【0032】

時刻t4において、スイッチング素子GaNFETのインダクタンスまたはLC(何れも図示しない)負荷などにより共振してスイッチング素子GaNFETのドレイン−ソース間電圧Vdsが振動を開始し、図2(i)に示すように、時刻t5でゼロボルトに達した後、時刻t5〜t6の期間で負電圧にまで低下する。スイッチング素子GaNFETのゲート−ソース間は抵抗R2で短絡されているので、図3に示す特性図の第3象限に示すゲート電圧Vgがゼロボルトのダイオード動作となり、ソースSからドレイン端子Dに回生電流を流すことができる。時刻t6以降は、時刻t1以降の動作と同じである。

【0033】

以上説明したように、本発明の実施例1に係るゲート駆動回路は、正電源と負電源、スイッチング素子GaNFETをオンさせるトランジスタQ2とオフさせるトランジスタQ1を備え、さらに、ターンオフ時にスイッチング素子GaNFETのゲートGの電圧を短時間だけ負電位に落とすターンオフ制御回路13と、ターンオフ直後にゲート−ソース間をダイオード接続させるトランジスタQ3,Q4から構成されている。

【0034】

実施例1に係るゲート駆動回路では、スイッチング素子GaNFETのターンオフ時、負電源E2を使用してゲート端子Gに印加されるゲート電圧Vgを負電圧−Vccまで落とし、スイッチング素子GaNFETのターンオフ速度を上げている。

【0035】

また、抵抗R1とコンデンサC1の時定数により決まる所定時間だけトランジスタQ1がオンすることによりゲート端子Gは負電圧−Vccまで落とされ、スイッチング素子GaNFETを急峻にオフさせることができる。また、オフ期間は、ゲートGとソースSは抵抗R2により短絡されているので、ダイオード接続される。この状態では、ドレイン端子Dの電圧がソース端子Sに対し負電位になると、逆方向に電流が流れるようになり、スイッチング素子GaNFETをダイオードの代わりとして使用することが可能になる。

【0036】

図4は、実施例1に係るゲート駆動回路を電流共振型コンバータに応用した例を示す。電流共振型コンバータは周知であるので、詳細な説明は省略するが、スイッチング素子QHを駆動するゲート駆動回路DRHと、スイッチング素子QLを駆動するゲート駆動回路DRLとの2つの実施例1に係るゲート駆動回路が使用されている。

【実施例2】

【0037】

本発明の実施例2に係るゲート駆動回路は、単電源で構成されている。図5は、本発明の実施例2に係るゲート駆動回路の構成を示す図である。このゲート駆動回路は、コンデンサCe、制御回路11、フォトカプラPC1、インバータG1,G2,G3、抵抗R1、コンデンサC1、ナンド回路12、N型MOSFETからなるトランジスタQ1,Q3、P型MOSFETからなるトランジスタQ2,Q4、スイッチング素子GaNFET、コンデンサCv、トランスT1、抵抗R、電源E、ダイオードDg、ダイオードD1及びD2、コンデンサCo並びに誤差増幅器ERRAMPを備えている。

【0038】

インバータG1,G2,G3、抵抗R1、コンデンサC1及びナンド回路12からなる回路は、本発明のゲート制御回路に対応する。

【0039】

トランスT1の一次巻線P1及びスイッチング素子GaNFETからなる直列回路は、電源Eの正負端子間に接続され、コンデンサCvは、スイッチング素子GaNFETのソース−ドレイン間に接続されている。電源Eの正負端子間には、抵抗R、コンデンサCe及びダイオードDgからなる直列回路が接続されている。

【0040】

トランスT1の補助巻線P2は、ダイオードD2を介してコンデンサCeの両端に接続されている。コンデンサCeは、実施例1に係るゲート駆動回路の正電源及び負電源に対応する電源として機能する。コンデンサCeの正極は、制御回路11の正電源端子、トランジスタQ2,Q4のソースに接続され、コンデンサCeの負極は、制御回路11の負電源端子、トランジスタQ1,Q3のソース、コンデンサC1及びフォトカプラPC1の受光部PC1−1に接続される。

【0041】

制御回路11は、コンデンサCeの両極間に設けられ、二次側回路のフォトカプラPC1の発光部PC1−2からフィードバックされた信号を受信したフォトカプラPC1の受光部PC1−1からの信号に応じて制御信号を生成し、インバータG1及びインバータG2に送る。インバータG1は、制御回路11からの制御信号を反転してトランジスタQ3,Q4のゲートに出力する。

【0042】

インバータG2は、制御回路11からの制御信号を反転してナンド回路12の一方の入力端子に出力するとともに、抵抗R1を介してインバータG3に出力する。抵抗R1とインバータG3の入力端子との接続点には、コンデンサC1の一方の端子が接続され、コンデンサC1の他方の端子は、制御回路11の負電源端子に接続されたグランドDriver_GNDに接続されている。グランドDriver_GNDは、スイッチング素子GaNFETのソースに対してフローティングされている。

【0043】

抵抗R1及びコンデンサC1は、CR積分による遅延回路を構成し、インバータG2からの信号を所定時間だけ遅延させてインバータG3に出力する。インバータG3は、遅延回路から送られてきた信号を反転してナンド回路12の他方の入力端子に出力する。

【0044】

ナンド回路12は、インバータG2からの信号とインバータG3からの信号との論理積をとった結果を反転し、トランジスタQ1,Q2のゲートに出力する。この構成により、ナンド回路12は、制御回路11から出力される制御信号の立ち下がりに応答して、即ち、制御信号がオフに変化したことに応答して、トランジスタQ1を所定時間だけオンさせるための所定幅のHレベルのパルス信号を生成する。

【0045】

トランジスタQ1のドレインは、トランジスタQ2のドレインに接続され、ソースは、グランドDriver_GNDに接続されている。トランジスタQ1のドレインとトランジスタQ2のドレインとの接続点は、スイッチング素子GaNFETのソースに接続されている。

【0046】

トランジスタQ3及びトランジスタQ4のゲートは、インバータG1の出力端子に接続され、トランジスタQ3のソースはグランドDriver_GNDに接続され、ドレインは、トランジスタQ4のドレインに接続されている。トランジスタQ4のソースは、コンデンサCeの正極に接続されている。また、トランジスタQ3のドレインとトランジスタQ4のドレインとの接続点は、スイッチング素子GaNFETのゲートに接続されている。

【0047】

また、トランスT1の二次巻線S1には、ダイオードD1とコンデンサCoとからなる整流回路が接続され、コンデンサCoの両端が出力端子に接続されている。また、出力端子間には誤差増幅器ERRAMPが設けら、誤差増幅器ERRAMPで検出された誤差信号に応じて、フォトカプラPC1の発光部PC1−2が駆動される。

【0048】

次に、このように構成される実施例2に係るゲート駆動回路の動作を説明する。図6は、実施例2に係るゲート駆動回路の動作を示すタイミングチャートである。

【0049】

時刻t11において、図6(a)に示すように、制御回路11からHレベルの信号が出力されると、制御信号は、インバータG1でLレベルの信号に変換され、トランジスタQ4及びトランジスタQ3のゲート端子に印加される。これにより、図6(b)に示すようにトランジスタQ4がオンするとともにトランジスタQ3がオフし、図6(e)に示すようにスイッチング素子GaNFETのゲート端子に、コンデンサCeの電圧がゲート電圧Vgとして印加される。

【0050】

この時点でナンド回路12の出力はHレベルであるので、トランジスタQ1はオン状態、トランジスタQ2はオフ状態となり、グランドDriver_GNDは、トランジスタQ1を介してスイッチング素子GaNFETのソースと接続される。

【0051】

時刻t12において、図6(a)に示すように、制御回路11からLレベルの制御信号が出力されると、制御信号は、インバータG1でHレベルの信号に変換され、トランジスタQ4及びトランジスタQ3のゲート端子に印加される。これにより、図6(b)に示すように、トランジスタQ4がオフし、トランジスタQ3がオンする。また、インバータG2、抵抗R1、コンデンサC1、インバータG3及びナンド回路12からなるゲート制御回路からの信号によりトランジスタQ1がオフすると同時にトランジスタQ2がオンする。

【0052】

したがって、時刻t12の時点では、トランジスタQ2を介してコンデンサCeの電圧(制御回路11の電源電圧)がスイッチング素子GaNFETのソースに印加されるので、スイッチング素子GaNFETのゲートには、図6(e)に示すように、相対的に負電圧が印加される。

【0053】

次に、時刻t12において、インバータG2の出力がHレベルになるのでコンデンサC1には充電が開始され、時刻t13において、コンデンサC1の電圧VC1は1/2まで充電される。これにより、インバータG3の出力が反転して、ナンド回路12を介してトランジスタQ2はオフ、トランジスタQ1はオンする。

【0054】

これにより、スイッチング素子GaNFETのゲートとソースとの間は、トランジスタQ1とトランジスタQ3により短絡され、次に制御回路11から出力される制御信号がHレベルになるまで、その状態が保たれる。

【0055】

時刻t10において、図6(g)に示すように、スイッチング素子GaNFETの負荷であるトランスT1及び共振コンデンサC1によりスイッチング素子GaNFETのドレイン−ソース間の電圧Vdsが振動を開始して、時刻t10でゼロボルト以下に達した後、時刻t10〜t11の期間で負電圧まで低下する。スイッチング素子GaNFETのゲート−ソース間は短絡されているので、図3に示す特性図の第3象限に示すゲート電圧Vgがゼロボルトのダイオード動作となり、ソースからドレインに回生電流を流すことができる。回生電流が流れている期間に制御回路11からHレベルの制御信号が出力されると、スイッチング素子GaNFETはオン状態になり、ドレイン−ソース間はより低下する。

【0056】

以上の動作により、回生ダイオードをスイッチング素子GaNFETのドレイン−ソース間に接続しなくとも低電圧で回生電流を流すことが可能となる。

【0057】

図7は、実施例2に係るゲート駆動回路を電流共振型コンバータに応用した例を示す。電流共振型コンバータは周知であるので、詳細な説明は省略するが、スイッチング素子QHを駆動するゲート駆動回路DHと、スイッチング素子QLを駆動するゲート駆動回路DLといった2つの実施例2に係るゲート駆動回路が使用されている。

【産業上の利用可能性】

【0058】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路として利用できる。

【符号の説明】

【0059】

11 制御回路

12 ナンド回路

13 ターンオフ制御回路

GaNFET スイッチング素子

G1,G2,G3,G5,G6 インバータ

R,R1,R2 抵抗

C1,Ce,Co コンデンサ

PC1 フォトカプラ

Q1〜Q4 トランジスタ

E 電源

E1 正電源

E2 負電源

Dg,D1,D2 ダイオード

T1 トランス

ERRAMP 誤差増幅器

【技術分野】

【0001】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路に関する。

【背景技術】

【0002】

特許文献1には、還流ダイオードを省略したゲート駆動回路が開示されている。図8は、特許文献1に開示されたゲート駆動回路の回路図であり、図9は、図8に示すゲート駆動回路の動作を示すタイミングチャートである。このゲート駆動回路は、フォトカプラ41、駆動電源44、抵抗45、PNPトランジスタ46、NPNトランジスタ47及びダイオード48を備え、図示しないコンバータ回路のスイッチング素子T1及びT2をオンオフさせる。なお、図8では、スイッチング素子T2を制御するための回路は、スイッチング素子T1のそれらの回路と同一であるので、省略されている。

【0003】

このゲート駆動回路では、MOSFETからなるスイッチング素子T1,T2におけるドレイン電位がソース電位より低くなると、スイッチング素子T1,T2のゲートGにコレクタが接続されたPNPトランジスタ46のベースからスイッチング素子T1,T2のドレインへ電流を流すダイオード48が設けられている。これにより、PNPトランジスタ46のベース電位がゼロになり、スイッチング素子T1,T2のゲートGにオン電圧が印加されるので、回生(還流)ダイオードをスイッチング素子T1,T2で代用できる。

【0004】

ところで、例えば窒化ガリウム電界効果トランジスタ(GaNFET)はボディーダイオードを備えていないが、構造上、双方向に電流を流すことができる特性を有する。回生電流などのような逆方向の電流を流す場合、電流が流れ出す閾値電圧はゲート端子の電圧に依存する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−61413号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に開示された技術では、スイッチング素子のターンオフは、NPNトランジスタ47によるスイッチング素子T1,T2のゲート−ソース間の電圧をゼロにすることにより行われている。ところが、スイッチング素子のゲート−ソース間にはゲート容量が存在し、ゲート−ソース間を単にショートするだけではターンオフ時間を速めることができず、スイッチング損失を減らすことができない。

【0007】

したがって、GaNFETなどのワイドギャップ半導体のターンオフ時のスイッチング速度を高速化し、かつ、回生電流が流れる場合はワイドギャップ半導体を回生ダイオードとして機能させることができるゲート駆動回路が望まれている。

【0008】

本発明の課題は、ワイドギャップ半導体のターンオフ時のスイッチング速度を高速化し、かつ、回生電流が流れる場合はワイドギャップ半導体を回生ダイオードとして機能させることができるゲート駆動回路を提供することにある。

【課題を解決するための手段】

【0009】

上記の課題を解決するために、本発明に係るゲート駆動回路は、負極が接地された正電源と、正極が接地された負電源と、前記正電源の正極と前記負電源の負極との間に設けられ、制御信号を生成する制御回路と、前記正電源の正極と前記負電源の負極との間に設けられた第1トランジスタと第2トランジスタとの直列回路と、ドレイン、接地されたソース及び前記第1トランジスタと第2トランジスタとの接続点に接続されたゲートを備えたワイドバンドギャップ半導体からなるスイッチング素子と、前記制御回路からの制御信号がオフになった場合に、前記第1トランジスタを所定時間だけオンさせ前記第1トランジスタを介して前記負電源の電圧を前記スイッチング素子のゲート端子に印加するターンオフ制御回路と、前記スイッチング素子のゲートとソースとの間に設けられ、前記制御回路からの制御信号がオフになった場合に、前記スイッチング素子のゲートとソースとの間を短絡させる第3トランジスタと第4トランジスタとの直列回路とを備えることを特徴とする。

【発明の効果】

【0010】

本発明に係るゲート駆動回路によれば、ワイドギャップ半導体のターンオフ時のスイッチング速度を高速化し、かつ、回生電流が流れる場合はワイドギャップ半導体を回生ダイオードとして機能させることができる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施例1に係るゲート駆動回路の構成を示す図である。

【図2】本発明の実施例1に係るゲート駆動回路の動作を示すタイミングチャートである。

【図3】本発明の実施例1に係るゲート駆動回路で使用される双方向のスイッチング素子(GaNFET)の特性を示す図である。

【図4】本発明の実施例1に係るゲート駆動回路を電流共振型コンバータに応用した例を示す図である。

【図5】本発明の実施例2に係るゲート駆動回路の構成を示す図である。

【図6】本発明の実施例2に係るゲート駆動回路の動作を示すタイミングチャートである。

【図7】本発明の実施例2に係るゲート駆動回路を電流共振型コンバータに応用した例を示す図である。

【図8】従来のゲート駆動回路の構成を示す図である。

【図9】従来のゲート駆動回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態に係るゲート駆動回路について、図面を参照しながら詳細に説明する。

【実施例1】

【0013】

本発明の実施例1に係るゲート駆動回路は、2電源を備えている。図1は、本発明の実施例1に係るゲート駆動回路の構成を示す図である。このゲート駆動回路は、正電源E1、負電源E2、制御回路11、フォトカプラPC1、インバータG1、ターンオフ制御回路13、N型MOSFETからなるトランジスタQ1(第1トランジスタ)、P型MOSFETからなるトランジスタQ2(第2トランジスタ)、N型MOSFETからなるトランジスタQ3(第3トランジスタ)、P型MOSFETからなるトランジスタQ4(第4トランジスタ)、インバータG6、抵抗R2及びスイッチング素子GaNFETを備える。ターンオフ制御回路13は、インバータG2,G3,G5、NAND回路12、抵抗R1並びにコンデンサC1を備えている。

【0014】

スイッチング素子GaNFETは、ドレイン、ソース、ゲートを有しワイドバンドギャップ半導体からなる。なお、トランジスタQ3,Q4は、双方向スイッチを用いても良い。

【0015】

ゲート駆動回路は、インバータG1、ターンオフ制御回路13、トランジスタQ1〜Q4、インバータG6及び抵抗R2から構成されるが、ここでは、正電源E1、負電源E2、制御回路11、フォトカプラPC1及びスイッチング素子GaNFETを含めてゲート駆動回路と称する。

【0016】

正電源E1の正極は、制御回路11の正電源端子及びトランジスタQ2のソースに接続され、正電源E1の負極は、負電源E2の正極に接続されている。負電源E2の負極は、制御回路11の負電源端子、トランジスタQ1のソース、コンデンサC1及びフォトカプラPC1に接続されている。正電源E1の負極と負電源E2の正極との接続点は、接地されている。

【0017】

制御回路11は、正電源E1の正極と負電源E2の負極との間に設けられ、図示しない二次側回路からフィードバックされた信号を受信したフォトカプラPC1からの信号に応じて制御信号を生成し、インバータG1,G2,G6及びトランジスタQ4のゲートに出力する。

【0018】

インバータG1は、制御回路11からの制御信号を反転してトランジスタQ2のゲートに出力する。トランジスタQ2のソースは、正電源E1の正極に接続され、トランジスタQ2のドレインは、トランジスタQ1のドレインに接続されている。

【0019】

ターンオフ制御回路13内のインバータG2は、制御回路11からの制御信号を反転してナンド回路12の一方の入力端子に出力するとともに、抵抗R1を介してインバータG3に出力する。抵抗R1とインバータG3の入力端子との接続点には、コンデンサC1の一方の端子が接続され、コンデンサC1の他方の端子は、負電源E2の負極に接続されている。

【0020】

抵抗R1及びコンデンサC1は、CR積分による遅延回路を構成し、インバータG2からの信号を所定時間だけ遅延させてインバータG3に出力する。インバータG3は、遅延回路からの信号を反転してナンド回路12の他方の入力端子に出力する。

【0021】

ナンド回路12は、インバータG2からの信号とインバータG3からの信号との論理積をとった結果を反転し、インバータG5に出力する。インバータG5は、ナンド回路12からの信号を反転してトランジスタQ1のゲートに出力する。 このようなターンオフ制御回路13は、制御回路11からの制御信号の立ち下がりに応答して、即ち、制御信号がオフに変化したことに応答して、トランジスタQ1を所定時間だけオンさせる所定幅のHレベルのパルス信号を生成する。

【0022】

トランジスタQ1のドレインは、トランジスタQ2のドレインに接続され、ソースは、負電源E2の負極に接続されている。トランジスタQ1のドレインとトランジスタQ2のドレインとの接続点は、スイッチング素子GaNFETのゲートGに接続されている。スイッチング素子GaNFETのソースSは、接地されている。

【0023】

インバータG6は、制御回路11からの制御信号を反転してトランジスタQ3のゲートに出力する。トランジスタQ3のソースは、接地され、ドレインは、トランジスタQ4のドレインに接続されている。

【0024】

トランジスタQ4のソースは、抵抗R2を経由してスイッチング素子GaNFETのゲートGに接続され、ドレインは、トランジスタQ3のドレインに接続されている。トランジスタQ4のゲートには、制御回路11からの制御信号が入力される。

【0025】

次に、このように構成される実施例1に係るゲート駆動回路の動作を説明する。図2は、実施例1に係るゲート駆動回路の動作を示すタイミングチャートである。

【0026】

時刻t1において、図2(a)に示すように、制御回路11からHレベルの制御信号が出力されると、制御信号は、インバータG1でLレベルの信号に変換され、トランジスタQ2のゲートに印加される。これにより、図2(e)に示すように、トランジスタQ2がオンし、図2(h)に示すように、スイッチング素子GaNFETのゲートGに、正電源E1からの正電圧+Vccがゲート電圧Vgとして印加される。

【0027】

この時点でナンド回路12の出力はHレベルであるので、トランジスタQ1は、図2(f)に示すように、オフ状態である。コンデンサC1の電圧VC1は、インバータG2の出力がLレベルになることで、時刻t1aにおいて、放電によって充電電圧の1/2まで低下し、インバータG3の出力が反転する。しかし、ナンド回路12の一方の入力端子にはインバータG2から出力されるLレベルが入力され続けているので、ナンド回路12の出力はHレベルを維持して変化しない。

【0028】

時刻t2において、図2(a)に示すように、制御回路11からLレベルの制御信号が出力されると、制御信号は、インバータG1でHレベルの信号に変換され、トランジスタQ2のゲートに印加される。これにより、図2(e)に示すように、トランジスタQ2はオフする。また、図2(f)に示すように、ターンオフ制御回路13を介してトランジスタQ1がオンすると同時に、図2(g)に示すように、トランジスタQ4及びトランジスタQ3がオンする。

【0029】

したがって、時刻t2の時点では、スイッチング素子GaNFETのゲートGには負電源E2からの負電圧−Vccがゲート電圧Vgとして印加され、かつ、スイッチング素子GaNFETのゲートGとソースSとは、抵抗R2を介して短絡される。

【0030】

また、図2(b)に示すように、時刻t2においてインバータG2の出力がHレベルになるので、コンデンサC1には充電が開始され、図2(c)に示すように、時刻t3においてコンデンサC1は1/2まで充電される。これにより、インバータG3の出力が反転して、図2(f)に示すように、トランジスタQ1がオフされる。

【0031】

ここで、トランジスタQ3及びトランジスタQ4は、制御回路11から出力される制御信号がLレベルの期間はオン状態を保つので、時刻t6に至るまでスイッチング素子GaNFETのゲート−ソース間は抵抗R2を介して短絡されている。

【0032】

時刻t4において、スイッチング素子GaNFETのインダクタンスまたはLC(何れも図示しない)負荷などにより共振してスイッチング素子GaNFETのドレイン−ソース間電圧Vdsが振動を開始し、図2(i)に示すように、時刻t5でゼロボルトに達した後、時刻t5〜t6の期間で負電圧にまで低下する。スイッチング素子GaNFETのゲート−ソース間は抵抗R2で短絡されているので、図3に示す特性図の第3象限に示すゲート電圧Vgがゼロボルトのダイオード動作となり、ソースSからドレイン端子Dに回生電流を流すことができる。時刻t6以降は、時刻t1以降の動作と同じである。

【0033】

以上説明したように、本発明の実施例1に係るゲート駆動回路は、正電源と負電源、スイッチング素子GaNFETをオンさせるトランジスタQ2とオフさせるトランジスタQ1を備え、さらに、ターンオフ時にスイッチング素子GaNFETのゲートGの電圧を短時間だけ負電位に落とすターンオフ制御回路13と、ターンオフ直後にゲート−ソース間をダイオード接続させるトランジスタQ3,Q4から構成されている。

【0034】

実施例1に係るゲート駆動回路では、スイッチング素子GaNFETのターンオフ時、負電源E2を使用してゲート端子Gに印加されるゲート電圧Vgを負電圧−Vccまで落とし、スイッチング素子GaNFETのターンオフ速度を上げている。

【0035】

また、抵抗R1とコンデンサC1の時定数により決まる所定時間だけトランジスタQ1がオンすることによりゲート端子Gは負電圧−Vccまで落とされ、スイッチング素子GaNFETを急峻にオフさせることができる。また、オフ期間は、ゲートGとソースSは抵抗R2により短絡されているので、ダイオード接続される。この状態では、ドレイン端子Dの電圧がソース端子Sに対し負電位になると、逆方向に電流が流れるようになり、スイッチング素子GaNFETをダイオードの代わりとして使用することが可能になる。

【0036】

図4は、実施例1に係るゲート駆動回路を電流共振型コンバータに応用した例を示す。電流共振型コンバータは周知であるので、詳細な説明は省略するが、スイッチング素子QHを駆動するゲート駆動回路DRHと、スイッチング素子QLを駆動するゲート駆動回路DRLとの2つの実施例1に係るゲート駆動回路が使用されている。

【実施例2】

【0037】

本発明の実施例2に係るゲート駆動回路は、単電源で構成されている。図5は、本発明の実施例2に係るゲート駆動回路の構成を示す図である。このゲート駆動回路は、コンデンサCe、制御回路11、フォトカプラPC1、インバータG1,G2,G3、抵抗R1、コンデンサC1、ナンド回路12、N型MOSFETからなるトランジスタQ1,Q3、P型MOSFETからなるトランジスタQ2,Q4、スイッチング素子GaNFET、コンデンサCv、トランスT1、抵抗R、電源E、ダイオードDg、ダイオードD1及びD2、コンデンサCo並びに誤差増幅器ERRAMPを備えている。

【0038】

インバータG1,G2,G3、抵抗R1、コンデンサC1及びナンド回路12からなる回路は、本発明のゲート制御回路に対応する。

【0039】

トランスT1の一次巻線P1及びスイッチング素子GaNFETからなる直列回路は、電源Eの正負端子間に接続され、コンデンサCvは、スイッチング素子GaNFETのソース−ドレイン間に接続されている。電源Eの正負端子間には、抵抗R、コンデンサCe及びダイオードDgからなる直列回路が接続されている。

【0040】

トランスT1の補助巻線P2は、ダイオードD2を介してコンデンサCeの両端に接続されている。コンデンサCeは、実施例1に係るゲート駆動回路の正電源及び負電源に対応する電源として機能する。コンデンサCeの正極は、制御回路11の正電源端子、トランジスタQ2,Q4のソースに接続され、コンデンサCeの負極は、制御回路11の負電源端子、トランジスタQ1,Q3のソース、コンデンサC1及びフォトカプラPC1の受光部PC1−1に接続される。

【0041】

制御回路11は、コンデンサCeの両極間に設けられ、二次側回路のフォトカプラPC1の発光部PC1−2からフィードバックされた信号を受信したフォトカプラPC1の受光部PC1−1からの信号に応じて制御信号を生成し、インバータG1及びインバータG2に送る。インバータG1は、制御回路11からの制御信号を反転してトランジスタQ3,Q4のゲートに出力する。

【0042】

インバータG2は、制御回路11からの制御信号を反転してナンド回路12の一方の入力端子に出力するとともに、抵抗R1を介してインバータG3に出力する。抵抗R1とインバータG3の入力端子との接続点には、コンデンサC1の一方の端子が接続され、コンデンサC1の他方の端子は、制御回路11の負電源端子に接続されたグランドDriver_GNDに接続されている。グランドDriver_GNDは、スイッチング素子GaNFETのソースに対してフローティングされている。

【0043】

抵抗R1及びコンデンサC1は、CR積分による遅延回路を構成し、インバータG2からの信号を所定時間だけ遅延させてインバータG3に出力する。インバータG3は、遅延回路から送られてきた信号を反転してナンド回路12の他方の入力端子に出力する。

【0044】

ナンド回路12は、インバータG2からの信号とインバータG3からの信号との論理積をとった結果を反転し、トランジスタQ1,Q2のゲートに出力する。この構成により、ナンド回路12は、制御回路11から出力される制御信号の立ち下がりに応答して、即ち、制御信号がオフに変化したことに応答して、トランジスタQ1を所定時間だけオンさせるための所定幅のHレベルのパルス信号を生成する。

【0045】

トランジスタQ1のドレインは、トランジスタQ2のドレインに接続され、ソースは、グランドDriver_GNDに接続されている。トランジスタQ1のドレインとトランジスタQ2のドレインとの接続点は、スイッチング素子GaNFETのソースに接続されている。

【0046】

トランジスタQ3及びトランジスタQ4のゲートは、インバータG1の出力端子に接続され、トランジスタQ3のソースはグランドDriver_GNDに接続され、ドレインは、トランジスタQ4のドレインに接続されている。トランジスタQ4のソースは、コンデンサCeの正極に接続されている。また、トランジスタQ3のドレインとトランジスタQ4のドレインとの接続点は、スイッチング素子GaNFETのゲートに接続されている。

【0047】

また、トランスT1の二次巻線S1には、ダイオードD1とコンデンサCoとからなる整流回路が接続され、コンデンサCoの両端が出力端子に接続されている。また、出力端子間には誤差増幅器ERRAMPが設けら、誤差増幅器ERRAMPで検出された誤差信号に応じて、フォトカプラPC1の発光部PC1−2が駆動される。

【0048】

次に、このように構成される実施例2に係るゲート駆動回路の動作を説明する。図6は、実施例2に係るゲート駆動回路の動作を示すタイミングチャートである。

【0049】

時刻t11において、図6(a)に示すように、制御回路11からHレベルの信号が出力されると、制御信号は、インバータG1でLレベルの信号に変換され、トランジスタQ4及びトランジスタQ3のゲート端子に印加される。これにより、図6(b)に示すようにトランジスタQ4がオンするとともにトランジスタQ3がオフし、図6(e)に示すようにスイッチング素子GaNFETのゲート端子に、コンデンサCeの電圧がゲート電圧Vgとして印加される。

【0050】

この時点でナンド回路12の出力はHレベルであるので、トランジスタQ1はオン状態、トランジスタQ2はオフ状態となり、グランドDriver_GNDは、トランジスタQ1を介してスイッチング素子GaNFETのソースと接続される。

【0051】

時刻t12において、図6(a)に示すように、制御回路11からLレベルの制御信号が出力されると、制御信号は、インバータG1でHレベルの信号に変換され、トランジスタQ4及びトランジスタQ3のゲート端子に印加される。これにより、図6(b)に示すように、トランジスタQ4がオフし、トランジスタQ3がオンする。また、インバータG2、抵抗R1、コンデンサC1、インバータG3及びナンド回路12からなるゲート制御回路からの信号によりトランジスタQ1がオフすると同時にトランジスタQ2がオンする。

【0052】

したがって、時刻t12の時点では、トランジスタQ2を介してコンデンサCeの電圧(制御回路11の電源電圧)がスイッチング素子GaNFETのソースに印加されるので、スイッチング素子GaNFETのゲートには、図6(e)に示すように、相対的に負電圧が印加される。

【0053】

次に、時刻t12において、インバータG2の出力がHレベルになるのでコンデンサC1には充電が開始され、時刻t13において、コンデンサC1の電圧VC1は1/2まで充電される。これにより、インバータG3の出力が反転して、ナンド回路12を介してトランジスタQ2はオフ、トランジスタQ1はオンする。

【0054】

これにより、スイッチング素子GaNFETのゲートとソースとの間は、トランジスタQ1とトランジスタQ3により短絡され、次に制御回路11から出力される制御信号がHレベルになるまで、その状態が保たれる。

【0055】

時刻t10において、図6(g)に示すように、スイッチング素子GaNFETの負荷であるトランスT1及び共振コンデンサC1によりスイッチング素子GaNFETのドレイン−ソース間の電圧Vdsが振動を開始して、時刻t10でゼロボルト以下に達した後、時刻t10〜t11の期間で負電圧まで低下する。スイッチング素子GaNFETのゲート−ソース間は短絡されているので、図3に示す特性図の第3象限に示すゲート電圧Vgがゼロボルトのダイオード動作となり、ソースからドレインに回生電流を流すことができる。回生電流が流れている期間に制御回路11からHレベルの制御信号が出力されると、スイッチング素子GaNFETはオン状態になり、ドレイン−ソース間はより低下する。

【0056】

以上の動作により、回生ダイオードをスイッチング素子GaNFETのドレイン−ソース間に接続しなくとも低電圧で回生電流を流すことが可能となる。

【0057】

図7は、実施例2に係るゲート駆動回路を電流共振型コンバータに応用した例を示す。電流共振型コンバータは周知であるので、詳細な説明は省略するが、スイッチング素子QHを駆動するゲート駆動回路DHと、スイッチング素子QLを駆動するゲート駆動回路DLといった2つの実施例2に係るゲート駆動回路が使用されている。

【産業上の利用可能性】

【0058】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路として利用できる。

【符号の説明】

【0059】

11 制御回路

12 ナンド回路

13 ターンオフ制御回路

GaNFET スイッチング素子

G1,G2,G3,G5,G6 インバータ

R,R1,R2 抵抗

C1,Ce,Co コンデンサ

PC1 フォトカプラ

Q1〜Q4 トランジスタ

E 電源

E1 正電源

E2 負電源

Dg,D1,D2 ダイオード

T1 トランス

ERRAMP 誤差増幅器

【特許請求の範囲】

【請求項1】

負極が接地された正電源と、

正極が接地された負電源と、

前記正電源の正極と前記負電源の負極との間に設けられ、制御信号を生成する制御回路と、

前記正電源の正極と前記負電源の負極との間に設けられた第1トランジスタと第2トランジスタとの直列回路と、

ドレイン、接地されたソース及び前記第1トランジスタと第2トランジスタとの接続点に接続されたゲートを備えたワイドバンドギャップ半導体からなるスイッチング素子と、

前記制御回路からの制御信号がオフになった場合に、前記第1トランジスタを所定時間だけオンさせ前記第1トランジスタを介して前記負電源の電圧を前記スイッチング素子のゲート端子に印加するターンオフ制御回路と、

前記スイッチング素子のゲートとソースとの間に設けられ、前記制御回路からの制御信号がオフになった場合に、前記スイッチング素子のゲートとソースとの間を短絡させる第3トランジスタと第4トランジスタとの直列回路と、

を備えることを特徴とするゲート駆動回路。

【請求項2】

前記第3トランジスタ及び第4トランジスタは、双方向スイッチからなることを特徴とする請求項1記載のゲート駆動回路。

【請求項3】

ドレイン端子、ソース端子及びゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子と、

前記スイッチング素子のオンオフを制御するための制御信号を生成する制御回路であって、自己のグランドが前記スイッチング素子のソースに対してフローティングされている制御回路と、

前記制御回路の電源端子間に設けられた第1トランジスタと第2トランジスタとの直列回路であって、第1トランジスタと第2トランジスタとの接続点が前記スイッチング素子のゲートに接続された直列回路と、

前記制御回路の電源端子間に設けられた第3トランジスタと第4トランジスタとの直列回路と、

前記制御回路からの制御信号がオンになった場合に、前記第1トランジスタと第4トランジスタをオンするとともに前記第2トランジスタと第3トランジスタをオフし、前記制御信号がオフになった場合に、前記第2トランジスタと第3トランジスタをオンするとともに前記第1トランジスタと第4トランジスタをオフし、且つ、前記制御信号がオフになった場合に、前記第2トランジスタを所定時間だけオンし、該所定時間が経過した後は、前記第1トランジスタをオンするとともに前記第2トランジスタをオフして、前記スイッチング素子のゲートとソースとの間を短絡させるゲート制御回路と、

を備えることを特徴とするゲート駆動回路。

【請求項4】

前記制御回路のグランドと前記スイッチング素子のソース端子とは、ダイオードを介して接続されていることを特徴とする請求項3記載のゲート駆動回路。

【請求項1】

負極が接地された正電源と、

正極が接地された負電源と、

前記正電源の正極と前記負電源の負極との間に設けられ、制御信号を生成する制御回路と、

前記正電源の正極と前記負電源の負極との間に設けられた第1トランジスタと第2トランジスタとの直列回路と、

ドレイン、接地されたソース及び前記第1トランジスタと第2トランジスタとの接続点に接続されたゲートを備えたワイドバンドギャップ半導体からなるスイッチング素子と、

前記制御回路からの制御信号がオフになった場合に、前記第1トランジスタを所定時間だけオンさせ前記第1トランジスタを介して前記負電源の電圧を前記スイッチング素子のゲート端子に印加するターンオフ制御回路と、

前記スイッチング素子のゲートとソースとの間に設けられ、前記制御回路からの制御信号がオフになった場合に、前記スイッチング素子のゲートとソースとの間を短絡させる第3トランジスタと第4トランジスタとの直列回路と、

を備えることを特徴とするゲート駆動回路。

【請求項2】

前記第3トランジスタ及び第4トランジスタは、双方向スイッチからなることを特徴とする請求項1記載のゲート駆動回路。

【請求項3】

ドレイン端子、ソース端子及びゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子と、

前記スイッチング素子のオンオフを制御するための制御信号を生成する制御回路であって、自己のグランドが前記スイッチング素子のソースに対してフローティングされている制御回路と、

前記制御回路の電源端子間に設けられた第1トランジスタと第2トランジスタとの直列回路であって、第1トランジスタと第2トランジスタとの接続点が前記スイッチング素子のゲートに接続された直列回路と、

前記制御回路の電源端子間に設けられた第3トランジスタと第4トランジスタとの直列回路と、

前記制御回路からの制御信号がオンになった場合に、前記第1トランジスタと第4トランジスタをオンするとともに前記第2トランジスタと第3トランジスタをオフし、前記制御信号がオフになった場合に、前記第2トランジスタと第3トランジスタをオンするとともに前記第1トランジスタと第4トランジスタをオフし、且つ、前記制御信号がオフになった場合に、前記第2トランジスタを所定時間だけオンし、該所定時間が経過した後は、前記第1トランジスタをオンするとともに前記第2トランジスタをオフして、前記スイッチング素子のゲートとソースとの間を短絡させるゲート制御回路と、

を備えることを特徴とするゲート駆動回路。

【請求項4】

前記制御回路のグランドと前記スイッチング素子のソース端子とは、ダイオードを介して接続されていることを特徴とする請求項3記載のゲート駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−42612(P2013−42612A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−178771(P2011−178771)

【出願日】平成23年8月18日(2011.8.18)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月18日(2011.8.18)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]