ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路に関する。

【背景技術】

【0002】

伝導度変調効果を有するゲート駆動型半導体素子のゲート駆動回路として、例えば、特許文献1は、半導体装置のゲート駆動回路を開示している。特許文献1の技術では、コンデンサと抵抗器とを並列に接続したゲート駆動回路を、ゲートとスイッチング出力回路との間に挿入し、半導体装置のゲート入力容量とコンデンサとの電圧分割により、半導体素子のオン閾値電圧以上の電圧をゲート端子に印加して高速のオン動作を行わせ、伝導度変調の維持に必要な電流をゲート駆動回路の抵抗器を介して供給する。

【0003】

これにより、半導体素子のゲート容量を積極的に利用し、少ない部品点数の簡易な回路構成によって高速で低損失な半導体装置のゲート駆動回路を提供することができる。

【0004】

ところで、ゲート駆動型半導体素子に還流電流が流れる回路では、主電極間(例えば、ソース−ドレイン間)に還流ダイオードを設けなければ還流時の損失が大きくなる。すなわち、ボディダイオードを有しないスイッチング素子でブリッジ回路を構成して誘導性の負荷を駆動する場合は、負荷に流れる電流が還流する場合がある。したがって、ボディダイオードを有しないスイッチング素子を用いる場合は、スイッチング素子に並列に還流ダイオードが付加される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−51165号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

双方向に導通可能なスイッチング素子は、図8に示すような特性を有する。つまり、逆方向の耐圧は、ゲートソース電圧Vgsに依存する。還流ダイオードを設けない場合は、ゲートソース電圧Vgsに依存したソースドレイン電圧Vdsで逆方向に逆電流が流れる。したがって、還流ダイオードを設けない場合は、「ソースドレイン電圧Vds×ソースドレイン電流Ids」という大きな損失が発生する。また、還流ダイオードにはリカバリ特性があり逆耐電圧印加時におけるリカバリ電流による損失及びノイズ発生により、高効率化および低ノイズ化、小型化の阻害要因となっている。

【0007】

本発明の課題は、双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路を提供することにある。

【課題を解決するための手段】

【0008】

上記の課題を解決するために、本発明に係るゲート駆動回路は、双方向に導通可能なスイッチング素子と、スイッチング素子のオンオフを制御する制御部と、スイッチング素子に流れる電流を検出する電流検出部と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立して、スイッチング素子をオン制御するゲート駆動部とを備えることを特徴とする。

【発明の効果】

【0009】

本発明に係るゲート駆動回路によれば、スイッチング素子に逆電流が流れるとスイッチング素子をオンさせて逆方向電圧降下を低減させるので、還流ダイオードを使用しなくても高効率化を図ることができる。また、還流ダイオードを設ける必要がないので、低ノイズ化および小型化を図ることができる。

【図面の簡単な説明】

【0010】

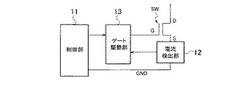

【図1】本発明の実施例1に係るゲート駆動回路の構成を概略的に示すブロック図である。

【図2】本発明の実施例1に係るゲート駆動回路の詳細な構成を示す回路図である。

【図3】本発明の実施例2に係るゲート駆動回路の詳細な構成を示す回路図である。

【図4】本発明の実施例3に係るゲート駆動回路が適用されたDC/DCコンバータの構成を示す回路図である。

【図5】本発明の実施例4に係るゲート駆動回路の構成を概略的に示すブロック図である。

【図6】本発明の実施例4に係るゲート駆動回路が適用されたDC/DCコンバータの他の構成を示す回路図である。

【図7】図6に示すゲート駆動回路の主要部の動作を示すタイミングチャートである。

【図8】従来のゲート駆動回路で駆動される、双方向に導通可能なスイッチング素子の特性を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態に係るゲート駆動回路を、図面を参照しながら詳細に説明する。

【実施例1】

【0012】

本発明の実施例1に係るゲート駆動回路は、電流検出素子としてカレントトランスを用いて逆方向に流れる電流を検出することを特徴とする。図1は、本発明の実施例1に係るゲート駆動回路の構成を概略的に示すブロック図である。ゲート駆動回路は、スイッチング素子SW、制御部11、電流検出部12及びゲート駆動部13を備えている。

【0013】

スイッチング素子SWは、双方向に導通可能なゲート駆動型半導体素子から構成されている。本明細書においては、スイッチング素子SWは、窒化ガリウム電界効果トランジスタ(GaNFET)によって構成されているものとして説明する。

【0014】

制御部11は、スイッチング素子SWのオンオフを制御するための制御信号を生成し、制御信号をゲート駆動部13に送る。電流検出部12は、スイッチング素子SWに流れる電流を検出し、その旨を表す信号をゲート駆動部13に送る。ゲート駆動部13は、スイッチング素子SWに逆方向の電流が流れた旨の信号が電流検出部12から送られてきた時に、制御部11からの信号による指示とは独立に、スイッチング素子SWをオンさせる。

【0015】

図2は、図1に示したゲート駆動回路の詳細な構成を示す回路図である。制御部11はパルス発生回路P1を備え、パルス発生回路P1は、スイッチング素子SWのオンオフを制御するためのパルス信号を生成し、生成されたパルス信号をゲート駆動部13に送る。

【0016】

電流検出部12では、電流検出素子としてカレントトランスCTが採用されている。カレントトランスCTの一次巻線Nsの一端はスイッチング素子SWのソースSに接続され、他端はグランドGNDに接続されている。カレントトランスCTの二次巻線Ndの一端はスイッチング素子SWのソースSに接続されるとともに、ゲート駆動部13に設けられた抵抗R3の一端に接続され、二次巻線Ndの他端はゲート駆動部13に設けられた抵抗R3の他端に接続されている。

【0017】

ゲート駆動部13は、抵抗R1、コンデンサC1、抵抗R2、抵抗R3及びダイオードD1を備えている。抵抗R1は、制御部11とスイッチング素子SWのゲートGとの間に設けられている。抵抗R1に並列に、コンデンサC1と抵抗R2とからなる直列回路が接続されている。抵抗R3は、電流検出部12のカレントトランスCTの二次巻線Ndの両端間に接続されている。

【0018】

ダイオードD1のアノードは、カレントトランスCTの二次巻線Ndの他端と抵抗R3との接続点に接続され、カソードがスイッチング素子SWのゲートGと抵抗R1の接続点に接続されている。

【0019】

このように構成される実施例1に係るゲート駆動回路は、図8に示すようなスイッチング素子SWの特性を生かして逆方向、つまりグランドGNDからスイッチング素子SWのソースSに向かって流れる電流を検出し、制御部11からの信号による指示とは独立に、スイッチング素子SWのゲートGを駆動してオンさせる。

【0020】

より詳しくは、逆方向に電流が流れると、カレントトランスCTの二次巻線Ndの他端(ドットが付されている端)からダイオードD1及びスイッチング素子SWのゲートGという経路で電流が流れてスイッチング素子SWをオンさせる。これにより、スイッチング素子SWに逆電流が流れた場合にスイッチング素子SWのゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低コストおよび小型化が可能になる。

【0021】

なお、上述した実施例1に係るゲート駆動回路では、電流検出素子としてのカレントトランスCTは、スイッチング素子SWのソース側に設けたが、ソースードレイン電流を検出するのが目的であるので、ドレイン側に設けるように構成することもできる。

【実施例2】

【0022】

本発明の実施例2に係るゲート駆動回路は、電流検出素子として抵抗を用いて逆方向に流れる電流を検出することを特徴とする。実施例2に係るゲート駆動回路は、実施例1に係るゲート駆動回路の電流検出部12a及びゲート駆動部13aを用いたことを特徴とする。以下、実施例1と異なる部分を説明する。

【0023】

図3は、実施例2に係るゲート駆動回路の詳細な構成を示す回路図である。電流検出部12aでは、電流検出素子として抵抗Rsが用いられている。抵抗Rsの一端はスイッチング素子SWのソースSに接続され、抵抗Rsの他端はグランドGNDに接続されている。スイッチング素子SWのソースSと抵抗Rsとの接続点は、ゲート駆動部13aのコンパレータCOMの反転入力端子(−)に接続されている。

【0024】

ゲート駆動部13aは、コンパレータCOM、オア回路31及びバッファ回路32を備えている。コンパレータCOMの非反転入力端子(+)は、グランドGNDに接続されている。コンパレータCOMは、電流検出部12aから反転入力端子(−)に入力される信号が、非反転入力端子(+)に入力されるグランドGNDの電圧より小さくなった場合に、即ち、逆電流が流れた場合に、Hレベルの信号を出力し、オア回路31の一方の入力端子に出力する。

【0025】

オア回路31の他方の入力端子には、制御部11からのパルス信号が入力される。オア回路31は、制御部11からの信号とコンパレータCOMからの信号の論理和をとって出力する。オア回路31からの信号は、バッファ回路32を介してスイッチング素子SWのゲートGに出力される。

【0026】

このように構成される実施例2に係るゲート駆動回路は、実施例1に係るゲート駆動回路と同様に、スイッチング素子SWを逆方向、つまりグランドGNDからスイッチング素子SWのソースSに向かって流れる電流を検出し、制御部11からの信号による指示とは独立に、スイッチング素子SWのゲートGを駆動してオンさせる。

【0027】

これにより、スイッチング素子SWに逆電流が流れた場合にスイッチング素子SWのゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低コストおよび小型化が可能になる。

【実施例3】

【0028】

本発明の実施例3に係るゲート駆動回路は、電流検出素子としてセンスMOSを用いて逆方向に流れる電流を検出することを特徴とする。図4は、実施例3に係るゲート駆動回路を電流共振型のDC/DCコンバータに適用した例を示す図である。なお、電流共振型のDC/DCコンバータの構成及び動作は周知であるので、ここでは、その説明は省略し、以下においては、本発明に関係するゲート駆動回路のみを説明する。

【0029】

制御部11bは、制御回路21及びフォトカプラの受光部PC1−1を備えている。制御回路21は、フォトカプラの受光部PC1−1からの信号に基づきスイッチング素子SWのオンオフを制御するためのパルス信号を生成してゲート駆動部13bに出力する。

【0030】

電流検出部12bでは、電流検出素子としてトランジスタQ2の電流センス素子であるトランジスタQ3が採用されている。電流検出部12bは、トランジスタQ3、電流検出用の抵抗Rs、コンダクタンスアンプOTA1及び直流電源Vcrを備えている。

【0031】

スイッチング素子Q2のソース−ドレイン間には、トランジスタQ3と抵抗Rsとの直列回路が接続されている。コンダクタンスアンプOTA1の非反転入力端子(+)はトランジスタQ3と抵抗Rsとの接続点に接続され、反転入力端子(−)は、スイッチング素子Q2のドレインの電位を負極とする直流電源Vcrに接続されている。コンダクタンスアンプOTA1は、逆電流によって非反転入力端子(+)の電圧が、直流電源Vcrの電圧より高くなった場合に逆電流が流れた旨を検出し、トランジスタQ3のドレイン電流に比例した電流信号をゲート駆動部13bに出力する。

【0032】

ゲート駆動部13bは、抵抗R1、コンパレータCP1、直流電源Vr、オア回路31及びバッファ回路32を備えている。抵抗R1は、コンダクタンスアンプOTA1の出力端子とグランドGNDとの間に設けられている。コンパレータCP1の非反転入力端子(+)はコンダクタンスアンプOTA1の出力端子と抵抗R1の接続点に接続され、反転入力端子(−)は、グランドGNDの電位を負極とする直流電源Vrの正極に接続されている。コンパレータCP1は、逆電流によって非反転入力端子(+)の電圧が、直流電源Vrの電圧より高くなった場合に逆電流が流れた旨を検出してHレベルの信号を生成し、オア回路31の一方の入力端子に出力する。オア回路31の他方の入力端子には、制御回路21からのパルス信号が入力される。オア回路31は、制御回路21からの信号とコンパレータCP1からの信号の論理和をとって出力する。オア回路31からの信号は、バッファ回路32を介してセンスMOSのトランジスタQ3及びスイッチング素子Q2のゲートに出力される。

【0033】

このように構成される実施例3に係るゲート駆動回路は、実施例2に係るゲート駆動回路と同様に、スイッチング素子Q2を逆方向、つまりグランドGNDからスイッチング素子Q2に向かって流れる電流を検出し、制御部11からの信号による指示とは独立に、スイッチング素子Q2のゲートを駆動してオンさせる。これにより、スイッチング素子Q2に逆電流が流れた場合にゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低ノイズおよび小型化が可能になる。

【実施例4】

【0034】

本発明の実施例4に係るゲート駆動回路は、実施例2に係るゲート駆動回路の制御部11とゲート駆動部13を一体化して新たな制御部11cを構成し、さらに集積回路(IC)化したことを特徴とする。以下、実施例2と異なる部分のみを説明する。

【0035】

図5は、本発明の実施例4に係るゲート駆動回路の構成を概略的に示すブロック図である。このゲート駆動回路は、スイッチング素子SW、制御部11c及び電流検出部12cを備えている。

【0036】

スイッチング素子SWは、実施例1〜実施例3で用いたスイッチング素子と同じものである。制御部11cは、スイッチング素子SWに逆方向の電流が流れた旨の信号が電流検出部12cから送られてきた時に、スイッチング素子SWをオンさせる信号を生成し、スイッチング素子SWのゲートGに出力する。

【0037】

図6は、実施例4に係るゲート駆動回路がDC/DCコンバータに適用された例を示す図であり、図7は、実施例4に係るゲート駆動回路の主要部の動作を示すタイミングチチャートである。なお、DC/DCコンバータの構成及び動作は周知であるので、ここでは、その説明は省略し、以下においては、本発明に関係するゲート駆動回路のみを説明する。

【0038】

集積回路IC41は、実施例2に係るゲート駆動回路の制御部11b及びゲート駆動部13bに相当する。電流検出部12は、IC41に外付けされる抵抗Rsによって構成されている。

【0039】

集積回路IC41は、内部電源Vcc、制御回路21、フォトカプラの受光部PC1−1、コンパレータCP1、基準電源Vref、オア回路31、インバータG1〜G3、トランジスタQ1〜Q4を備えている。

【0040】

制御回路21は、フォトカプラの受光部PC1−1からの信号及び外付けの起動抵抗Rcからの信号に応じて、スイッチング素子SWのオンオフを制御するためのパルス信号を生成し、オア回路31の一方の入力端子に出力する。

【0041】

コンパレータCP1の反転入力端子(−)は、スイッチング素子SWのソースと抵抗Rsとの接続点に接続され、非反転入力端子(+)は、グランドGNDを正極とする基準電源Vrefの負極に接続されている。コンパレータCP1は、反転入力端子(−)に入力される抵抗Rsで検出された電流を示す電圧値が、非反転入力端子(+)に入力される基準電源Vrefの負極の電位より小さくなった場合に逆電流が流れた旨を検出してHレベルの信号を生成し、オア回路31の他方の入力端子に出力する。

【0042】

オア回路31は、制御回路21から送られてくる信号とコンパレータCP1からの信号の論理和をとって出力する。オア回路31からの信号は、インバータG2及びG3を経由して、NチャンネルMOSFETから構成されたトランジスタQ1のゲート及びPチャンネルMOSFETから構成されたトランジスタQ2のゲートに送られる。トランジスタQ1のソースは内部電源Vccの負極に接続され、ドレインはトランジスタQ2のドレインに接続されている。

【0043】

トランジスタQ2のソースは内部電源Vccの正極に接続されている。トランジスタQ1のドレインとトランジスタQ2のドレインとの接続点は、外部の電源Veの負極に接続されている。

【0044】

また、オア回路31から出力された信号は、インバータG1を経由して、N型のMOSFETからなるトランジスタQ3のゲート及びP型のMOSFETからなるトランジスタQ4のゲートに出力される。トランジスタQ3のソースは外部の電源Veの負極に接続され、ドレインはトランジスタQ4のドレインに接続されている。トランジスタQ4のソースは内部電源Vccの正極に接続されている。トランジスタQ3のドレインとトランジスタQ4のドレインとの接続点は、IC41に外付けされたスイッチング素子SWのゲートに接続されている。

【0045】

このように構成される実施例4に係るゲート駆動回路は、実施例2に係るゲート駆動回路と同様に、スイッチング素子SWを逆方向、つまりグランドGNDからスイッチング素子SWに向かって流れる電流を検出し、制御回路21からの信号による指示とは独立に、スイッチング素子SWのゲートを駆動してオンさせる。これにより、スイッチング素子SWに逆電流が流れた場合にゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低コストおよび小型化が可能になる。

【0046】

なお、上述した各実施例では、スイッチング素子として、窒化ガリウム(GaN)といった窒化物半導体を用いたが、スイッチング素子としては、炭化ケイ素、ダイヤモンドなどといったワイドギャップ半導体を用いることができる。

【産業上の利用可能性】

【0047】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路として利用できる。

【符号の説明】

【0048】

11,11b,11c 制御部

12,12a,12b,12c 電流検出部

13,13a,13b ゲート駆動部

21 制御回路

31 オア回路

32 バッファ回路

SW,Q2 スイッチング素子

Q1〜Q4 トランジスタ

G1〜G3 インバータ

T1,T2 トランス

IC41 集積回路

OTA1 コンダクタンスアンプ

CT カレントトランス

Rs 電流検出用の抵抗

R1〜R3 抵抗

C1 コンデンサ

D1 ダイオード

COM、CP1 コンパレータ

PC1−1 フォトカプラの受光部

【技術分野】

【0001】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路に関する。

【背景技術】

【0002】

伝導度変調効果を有するゲート駆動型半導体素子のゲート駆動回路として、例えば、特許文献1は、半導体装置のゲート駆動回路を開示している。特許文献1の技術では、コンデンサと抵抗器とを並列に接続したゲート駆動回路を、ゲートとスイッチング出力回路との間に挿入し、半導体装置のゲート入力容量とコンデンサとの電圧分割により、半導体素子のオン閾値電圧以上の電圧をゲート端子に印加して高速のオン動作を行わせ、伝導度変調の維持に必要な電流をゲート駆動回路の抵抗器を介して供給する。

【0003】

これにより、半導体素子のゲート容量を積極的に利用し、少ない部品点数の簡易な回路構成によって高速で低損失な半導体装置のゲート駆動回路を提供することができる。

【0004】

ところで、ゲート駆動型半導体素子に還流電流が流れる回路では、主電極間(例えば、ソース−ドレイン間)に還流ダイオードを設けなければ還流時の損失が大きくなる。すなわち、ボディダイオードを有しないスイッチング素子でブリッジ回路を構成して誘導性の負荷を駆動する場合は、負荷に流れる電流が還流する場合がある。したがって、ボディダイオードを有しないスイッチング素子を用いる場合は、スイッチング素子に並列に還流ダイオードが付加される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−51165号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

双方向に導通可能なスイッチング素子は、図8に示すような特性を有する。つまり、逆方向の耐圧は、ゲートソース電圧Vgsに依存する。還流ダイオードを設けない場合は、ゲートソース電圧Vgsに依存したソースドレイン電圧Vdsで逆方向に逆電流が流れる。したがって、還流ダイオードを設けない場合は、「ソースドレイン電圧Vds×ソースドレイン電流Ids」という大きな損失が発生する。また、還流ダイオードにはリカバリ特性があり逆耐電圧印加時におけるリカバリ電流による損失及びノイズ発生により、高効率化および低ノイズ化、小型化の阻害要因となっている。

【0007】

本発明の課題は、双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路を提供することにある。

【課題を解決するための手段】

【0008】

上記の課題を解決するために、本発明に係るゲート駆動回路は、双方向に導通可能なスイッチング素子と、スイッチング素子のオンオフを制御する制御部と、スイッチング素子に流れる電流を検出する電流検出部と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立して、スイッチング素子をオン制御するゲート駆動部とを備えることを特徴とする。

【発明の効果】

【0009】

本発明に係るゲート駆動回路によれば、スイッチング素子に逆電流が流れるとスイッチング素子をオンさせて逆方向電圧降下を低減させるので、還流ダイオードを使用しなくても高効率化を図ることができる。また、還流ダイオードを設ける必要がないので、低ノイズ化および小型化を図ることができる。

【図面の簡単な説明】

【0010】

【図1】本発明の実施例1に係るゲート駆動回路の構成を概略的に示すブロック図である。

【図2】本発明の実施例1に係るゲート駆動回路の詳細な構成を示す回路図である。

【図3】本発明の実施例2に係るゲート駆動回路の詳細な構成を示す回路図である。

【図4】本発明の実施例3に係るゲート駆動回路が適用されたDC/DCコンバータの構成を示す回路図である。

【図5】本発明の実施例4に係るゲート駆動回路の構成を概略的に示すブロック図である。

【図6】本発明の実施例4に係るゲート駆動回路が適用されたDC/DCコンバータの他の構成を示す回路図である。

【図7】図6に示すゲート駆動回路の主要部の動作を示すタイミングチャートである。

【図8】従来のゲート駆動回路で駆動される、双方向に導通可能なスイッチング素子の特性を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態に係るゲート駆動回路を、図面を参照しながら詳細に説明する。

【実施例1】

【0012】

本発明の実施例1に係るゲート駆動回路は、電流検出素子としてカレントトランスを用いて逆方向に流れる電流を検出することを特徴とする。図1は、本発明の実施例1に係るゲート駆動回路の構成を概略的に示すブロック図である。ゲート駆動回路は、スイッチング素子SW、制御部11、電流検出部12及びゲート駆動部13を備えている。

【0013】

スイッチング素子SWは、双方向に導通可能なゲート駆動型半導体素子から構成されている。本明細書においては、スイッチング素子SWは、窒化ガリウム電界効果トランジスタ(GaNFET)によって構成されているものとして説明する。

【0014】

制御部11は、スイッチング素子SWのオンオフを制御するための制御信号を生成し、制御信号をゲート駆動部13に送る。電流検出部12は、スイッチング素子SWに流れる電流を検出し、その旨を表す信号をゲート駆動部13に送る。ゲート駆動部13は、スイッチング素子SWに逆方向の電流が流れた旨の信号が電流検出部12から送られてきた時に、制御部11からの信号による指示とは独立に、スイッチング素子SWをオンさせる。

【0015】

図2は、図1に示したゲート駆動回路の詳細な構成を示す回路図である。制御部11はパルス発生回路P1を備え、パルス発生回路P1は、スイッチング素子SWのオンオフを制御するためのパルス信号を生成し、生成されたパルス信号をゲート駆動部13に送る。

【0016】

電流検出部12では、電流検出素子としてカレントトランスCTが採用されている。カレントトランスCTの一次巻線Nsの一端はスイッチング素子SWのソースSに接続され、他端はグランドGNDに接続されている。カレントトランスCTの二次巻線Ndの一端はスイッチング素子SWのソースSに接続されるとともに、ゲート駆動部13に設けられた抵抗R3の一端に接続され、二次巻線Ndの他端はゲート駆動部13に設けられた抵抗R3の他端に接続されている。

【0017】

ゲート駆動部13は、抵抗R1、コンデンサC1、抵抗R2、抵抗R3及びダイオードD1を備えている。抵抗R1は、制御部11とスイッチング素子SWのゲートGとの間に設けられている。抵抗R1に並列に、コンデンサC1と抵抗R2とからなる直列回路が接続されている。抵抗R3は、電流検出部12のカレントトランスCTの二次巻線Ndの両端間に接続されている。

【0018】

ダイオードD1のアノードは、カレントトランスCTの二次巻線Ndの他端と抵抗R3との接続点に接続され、カソードがスイッチング素子SWのゲートGと抵抗R1の接続点に接続されている。

【0019】

このように構成される実施例1に係るゲート駆動回路は、図8に示すようなスイッチング素子SWの特性を生かして逆方向、つまりグランドGNDからスイッチング素子SWのソースSに向かって流れる電流を検出し、制御部11からの信号による指示とは独立に、スイッチング素子SWのゲートGを駆動してオンさせる。

【0020】

より詳しくは、逆方向に電流が流れると、カレントトランスCTの二次巻線Ndの他端(ドットが付されている端)からダイオードD1及びスイッチング素子SWのゲートGという経路で電流が流れてスイッチング素子SWをオンさせる。これにより、スイッチング素子SWに逆電流が流れた場合にスイッチング素子SWのゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低コストおよび小型化が可能になる。

【0021】

なお、上述した実施例1に係るゲート駆動回路では、電流検出素子としてのカレントトランスCTは、スイッチング素子SWのソース側に設けたが、ソースードレイン電流を検出するのが目的であるので、ドレイン側に設けるように構成することもできる。

【実施例2】

【0022】

本発明の実施例2に係るゲート駆動回路は、電流検出素子として抵抗を用いて逆方向に流れる電流を検出することを特徴とする。実施例2に係るゲート駆動回路は、実施例1に係るゲート駆動回路の電流検出部12a及びゲート駆動部13aを用いたことを特徴とする。以下、実施例1と異なる部分を説明する。

【0023】

図3は、実施例2に係るゲート駆動回路の詳細な構成を示す回路図である。電流検出部12aでは、電流検出素子として抵抗Rsが用いられている。抵抗Rsの一端はスイッチング素子SWのソースSに接続され、抵抗Rsの他端はグランドGNDに接続されている。スイッチング素子SWのソースSと抵抗Rsとの接続点は、ゲート駆動部13aのコンパレータCOMの反転入力端子(−)に接続されている。

【0024】

ゲート駆動部13aは、コンパレータCOM、オア回路31及びバッファ回路32を備えている。コンパレータCOMの非反転入力端子(+)は、グランドGNDに接続されている。コンパレータCOMは、電流検出部12aから反転入力端子(−)に入力される信号が、非反転入力端子(+)に入力されるグランドGNDの電圧より小さくなった場合に、即ち、逆電流が流れた場合に、Hレベルの信号を出力し、オア回路31の一方の入力端子に出力する。

【0025】

オア回路31の他方の入力端子には、制御部11からのパルス信号が入力される。オア回路31は、制御部11からの信号とコンパレータCOMからの信号の論理和をとって出力する。オア回路31からの信号は、バッファ回路32を介してスイッチング素子SWのゲートGに出力される。

【0026】

このように構成される実施例2に係るゲート駆動回路は、実施例1に係るゲート駆動回路と同様に、スイッチング素子SWを逆方向、つまりグランドGNDからスイッチング素子SWのソースSに向かって流れる電流を検出し、制御部11からの信号による指示とは独立に、スイッチング素子SWのゲートGを駆動してオンさせる。

【0027】

これにより、スイッチング素子SWに逆電流が流れた場合にスイッチング素子SWのゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低コストおよび小型化が可能になる。

【実施例3】

【0028】

本発明の実施例3に係るゲート駆動回路は、電流検出素子としてセンスMOSを用いて逆方向に流れる電流を検出することを特徴とする。図4は、実施例3に係るゲート駆動回路を電流共振型のDC/DCコンバータに適用した例を示す図である。なお、電流共振型のDC/DCコンバータの構成及び動作は周知であるので、ここでは、その説明は省略し、以下においては、本発明に関係するゲート駆動回路のみを説明する。

【0029】

制御部11bは、制御回路21及びフォトカプラの受光部PC1−1を備えている。制御回路21は、フォトカプラの受光部PC1−1からの信号に基づきスイッチング素子SWのオンオフを制御するためのパルス信号を生成してゲート駆動部13bに出力する。

【0030】

電流検出部12bでは、電流検出素子としてトランジスタQ2の電流センス素子であるトランジスタQ3が採用されている。電流検出部12bは、トランジスタQ3、電流検出用の抵抗Rs、コンダクタンスアンプOTA1及び直流電源Vcrを備えている。

【0031】

スイッチング素子Q2のソース−ドレイン間には、トランジスタQ3と抵抗Rsとの直列回路が接続されている。コンダクタンスアンプOTA1の非反転入力端子(+)はトランジスタQ3と抵抗Rsとの接続点に接続され、反転入力端子(−)は、スイッチング素子Q2のドレインの電位を負極とする直流電源Vcrに接続されている。コンダクタンスアンプOTA1は、逆電流によって非反転入力端子(+)の電圧が、直流電源Vcrの電圧より高くなった場合に逆電流が流れた旨を検出し、トランジスタQ3のドレイン電流に比例した電流信号をゲート駆動部13bに出力する。

【0032】

ゲート駆動部13bは、抵抗R1、コンパレータCP1、直流電源Vr、オア回路31及びバッファ回路32を備えている。抵抗R1は、コンダクタンスアンプOTA1の出力端子とグランドGNDとの間に設けられている。コンパレータCP1の非反転入力端子(+)はコンダクタンスアンプOTA1の出力端子と抵抗R1の接続点に接続され、反転入力端子(−)は、グランドGNDの電位を負極とする直流電源Vrの正極に接続されている。コンパレータCP1は、逆電流によって非反転入力端子(+)の電圧が、直流電源Vrの電圧より高くなった場合に逆電流が流れた旨を検出してHレベルの信号を生成し、オア回路31の一方の入力端子に出力する。オア回路31の他方の入力端子には、制御回路21からのパルス信号が入力される。オア回路31は、制御回路21からの信号とコンパレータCP1からの信号の論理和をとって出力する。オア回路31からの信号は、バッファ回路32を介してセンスMOSのトランジスタQ3及びスイッチング素子Q2のゲートに出力される。

【0033】

このように構成される実施例3に係るゲート駆動回路は、実施例2に係るゲート駆動回路と同様に、スイッチング素子Q2を逆方向、つまりグランドGNDからスイッチング素子Q2に向かって流れる電流を検出し、制御部11からの信号による指示とは独立に、スイッチング素子Q2のゲートを駆動してオンさせる。これにより、スイッチング素子Q2に逆電流が流れた場合にゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低ノイズおよび小型化が可能になる。

【実施例4】

【0034】

本発明の実施例4に係るゲート駆動回路は、実施例2に係るゲート駆動回路の制御部11とゲート駆動部13を一体化して新たな制御部11cを構成し、さらに集積回路(IC)化したことを特徴とする。以下、実施例2と異なる部分のみを説明する。

【0035】

図5は、本発明の実施例4に係るゲート駆動回路の構成を概略的に示すブロック図である。このゲート駆動回路は、スイッチング素子SW、制御部11c及び電流検出部12cを備えている。

【0036】

スイッチング素子SWは、実施例1〜実施例3で用いたスイッチング素子と同じものである。制御部11cは、スイッチング素子SWに逆方向の電流が流れた旨の信号が電流検出部12cから送られてきた時に、スイッチング素子SWをオンさせる信号を生成し、スイッチング素子SWのゲートGに出力する。

【0037】

図6は、実施例4に係るゲート駆動回路がDC/DCコンバータに適用された例を示す図であり、図7は、実施例4に係るゲート駆動回路の主要部の動作を示すタイミングチチャートである。なお、DC/DCコンバータの構成及び動作は周知であるので、ここでは、その説明は省略し、以下においては、本発明に関係するゲート駆動回路のみを説明する。

【0038】

集積回路IC41は、実施例2に係るゲート駆動回路の制御部11b及びゲート駆動部13bに相当する。電流検出部12は、IC41に外付けされる抵抗Rsによって構成されている。

【0039】

集積回路IC41は、内部電源Vcc、制御回路21、フォトカプラの受光部PC1−1、コンパレータCP1、基準電源Vref、オア回路31、インバータG1〜G3、トランジスタQ1〜Q4を備えている。

【0040】

制御回路21は、フォトカプラの受光部PC1−1からの信号及び外付けの起動抵抗Rcからの信号に応じて、スイッチング素子SWのオンオフを制御するためのパルス信号を生成し、オア回路31の一方の入力端子に出力する。

【0041】

コンパレータCP1の反転入力端子(−)は、スイッチング素子SWのソースと抵抗Rsとの接続点に接続され、非反転入力端子(+)は、グランドGNDを正極とする基準電源Vrefの負極に接続されている。コンパレータCP1は、反転入力端子(−)に入力される抵抗Rsで検出された電流を示す電圧値が、非反転入力端子(+)に入力される基準電源Vrefの負極の電位より小さくなった場合に逆電流が流れた旨を検出してHレベルの信号を生成し、オア回路31の他方の入力端子に出力する。

【0042】

オア回路31は、制御回路21から送られてくる信号とコンパレータCP1からの信号の論理和をとって出力する。オア回路31からの信号は、インバータG2及びG3を経由して、NチャンネルMOSFETから構成されたトランジスタQ1のゲート及びPチャンネルMOSFETから構成されたトランジスタQ2のゲートに送られる。トランジスタQ1のソースは内部電源Vccの負極に接続され、ドレインはトランジスタQ2のドレインに接続されている。

【0043】

トランジスタQ2のソースは内部電源Vccの正極に接続されている。トランジスタQ1のドレインとトランジスタQ2のドレインとの接続点は、外部の電源Veの負極に接続されている。

【0044】

また、オア回路31から出力された信号は、インバータG1を経由して、N型のMOSFETからなるトランジスタQ3のゲート及びP型のMOSFETからなるトランジスタQ4のゲートに出力される。トランジスタQ3のソースは外部の電源Veの負極に接続され、ドレインはトランジスタQ4のドレインに接続されている。トランジスタQ4のソースは内部電源Vccの正極に接続されている。トランジスタQ3のドレインとトランジスタQ4のドレインとの接続点は、IC41に外付けされたスイッチング素子SWのゲートに接続されている。

【0045】

このように構成される実施例4に係るゲート駆動回路は、実施例2に係るゲート駆動回路と同様に、スイッチング素子SWを逆方向、つまりグランドGNDからスイッチング素子SWに向かって流れる電流を検出し、制御回路21からの信号による指示とは独立に、スイッチング素子SWのゲートを駆動してオンさせる。これにより、スイッチング素子SWに逆電流が流れた場合にゲートをオン制御できるので、還流ダイオードを付加しなくても損失を低減させた高効率なゲート駆動回路を実現できる。また、還流ダイオードが不要であるので、低コストおよび小型化が可能になる。

【0046】

なお、上述した各実施例では、スイッチング素子として、窒化ガリウム(GaN)といった窒化物半導体を用いたが、スイッチング素子としては、炭化ケイ素、ダイヤモンドなどといったワイドギャップ半導体を用いることができる。

【産業上の利用可能性】

【0047】

本発明は、双方向に導通可能なスイッチング素子のゲート駆動を行うゲート駆動回路として利用できる。

【符号の説明】

【0048】

11,11b,11c 制御部

12,12a,12b,12c 電流検出部

13,13a,13b ゲート駆動部

21 制御回路

31 オア回路

32 バッファ回路

SW,Q2 スイッチング素子

Q1〜Q4 トランジスタ

G1〜G3 インバータ

T1,T2 トランス

IC41 集積回路

OTA1 コンダクタンスアンプ

CT カレントトランス

Rs 電流検出用の抵抗

R1〜R3 抵抗

C1 コンデンサ

D1 ダイオード

COM、CP1 コンパレータ

PC1−1 フォトカプラの受光部

【特許請求の範囲】

【請求項1】

双方向に導通可能なスイッチング素子と、

前記スイッチング素子のオンオフを制御する制御部と、

前記スイッチング素子に流れる電流を検出する電流検出部と、

前記電流検出部によって前記スイッチング素子に逆方向の電流が流れたことが検出された時に、前記制御部によるオンオフの制御とは独立に、前記スイッチング素子をオン制御するゲート駆動部と、

を備えることを特徴とするゲート駆動回路。

【請求項2】

ソース−ドレイン間を双方向に導通可能なスイッチング素子と、

前記スイッチング素子に流れる電流を検出する電流検出部と、

前記電流検出部によって前記スイッチング素子のソースからドレインに流れる電流が検出された場合に、前記スイッチング素子をオンさせる制御部と、

を備えることを特徴とするゲート駆動回路。

【請求項3】

前記電流検出部は、カレントトランスで構成されていることを特徴とする請求項1または請求項2記載のゲート駆動回路。

【請求項4】

前記電流検出部は、抵抗で構成されていることを特徴とする請求項1または請求項2記載のゲート駆動回路。

【請求項5】

前記電流検出部は、電流センス素子で構成されていることを特徴とする請求項1または請求項2記載のゲート駆動回路。

【請求項6】

前記スイッチング素子は、還流ダイオードを有しないことを特徴とする請求項1乃至請求項5のいずれか1項記載のゲート駆動回路。

【請求項7】

前記スイッチング素子は、ワイドバンドギャップ半導体からなることを特徴とする請求項1乃至請求項6のいずれか1項記載のゲート駆動回路。

【請求項1】

双方向に導通可能なスイッチング素子と、

前記スイッチング素子のオンオフを制御する制御部と、

前記スイッチング素子に流れる電流を検出する電流検出部と、

前記電流検出部によって前記スイッチング素子に逆方向の電流が流れたことが検出された時に、前記制御部によるオンオフの制御とは独立に、前記スイッチング素子をオン制御するゲート駆動部と、

を備えることを特徴とするゲート駆動回路。

【請求項2】

ソース−ドレイン間を双方向に導通可能なスイッチング素子と、

前記スイッチング素子に流れる電流を検出する電流検出部と、

前記電流検出部によって前記スイッチング素子のソースからドレインに流れる電流が検出された場合に、前記スイッチング素子をオンさせる制御部と、

を備えることを特徴とするゲート駆動回路。

【請求項3】

前記電流検出部は、カレントトランスで構成されていることを特徴とする請求項1または請求項2記載のゲート駆動回路。

【請求項4】

前記電流検出部は、抵抗で構成されていることを特徴とする請求項1または請求項2記載のゲート駆動回路。

【請求項5】

前記電流検出部は、電流センス素子で構成されていることを特徴とする請求項1または請求項2記載のゲート駆動回路。

【請求項6】

前記スイッチング素子は、還流ダイオードを有しないことを特徴とする請求項1乃至請求項5のいずれか1項記載のゲート駆動回路。

【請求項7】

前記スイッチング素子は、ワイドバンドギャップ半導体からなることを特徴とする請求項1乃至請求項6のいずれか1項記載のゲート駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−42613(P2013−42613A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−178772(P2011−178772)

【出願日】平成23年8月18日(2011.8.18)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月18日(2011.8.18)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]