コイル内蔵基板およびそれを備えたDC−DCコンバータモジュール

【課題】不要な磁束の発生を抑制して、インダクタとしての電気的特性に優れたコイルを内蔵したコイル内蔵基板を構成する。

【解決手段】第1磁性体層61と第2磁性体層62の一部および中間非磁性体層60のうち所定のフェライトシートにはコイル導体9が形成されている。コイル導体9は、径の大きな外コイル導体9Lと外コイル導体より径の小さな内コイル導体9Sとが磁性体層または中間非磁性体層を介して交互に積み重ねられている。コイル導体9が積み重ねられる順に直列接続されることによりコイルが形成されている。外コイル導体9Lと内コイル導体9Sとが交互に並んでいる。積み重ねられる方向に互いに隣接するコイル導体9L同士の層間とコイル導体9S同士の層間とにはそれぞれ低透磁率領域80が設けられている。この構造により、隣接するコイル導体9間を通過する無効な磁束φsが生じ難く、本来必要な有効な磁束φmが増大する。

【解決手段】第1磁性体層61と第2磁性体層62の一部および中間非磁性体層60のうち所定のフェライトシートにはコイル導体9が形成されている。コイル導体9は、径の大きな外コイル導体9Lと外コイル導体より径の小さな内コイル導体9Sとが磁性体層または中間非磁性体層を介して交互に積み重ねられている。コイル導体9が積み重ねられる順に直列接続されることによりコイルが形成されている。外コイル導体9Lと内コイル導体9Sとが交互に並んでいる。積み重ねられる方向に互いに隣接するコイル導体9L同士の層間とコイル導体9S同士の層間とにはそれぞれ低透磁率領域80が設けられている。この構造により、隣接するコイル導体9間を通過する無効な磁束φsが生じ難く、本来必要な有効な磁束φmが増大する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、内部にコイルを備え、DC−DCコンバータモジュール等に適用されるコイル内蔵基板およびそれを備えたDC−DCコンバータモジュールに関する。

【背景技術】

【0002】

磁性体基板の内部にコイルが構成されたインダクタが特許文献1に開示されている。図1は特許文献1に示されているインダクタ21の断面図である。この例では、導電体ペーストによりコイル導体3a〜3dが印刷された各磁性体グリーンシートと、低誘電率材料ペーストによる誘電体層22a〜22cが印刷された磁性体グリーンシートとが交互に積層されている。ここで、誘電体層22a〜22cは、コイル導体3a〜3dとほぼ同様なパターンに形成されている。これらの積層体が焼成されて、コイル11を内部に備えた磁性体チップ10が構成される。

特許文献1のインダクタは、積み重ねられる方向に隣接するコイル導体同士で生じる浮遊容量を低減させて高周波域まで使用できるとされている。

【0003】

一方、フェライト基板中に径の大きな外コイル導体と径の小さな内コイル導体とを交互に積み重ねてコイルを形成し、コイルの断面のパターンが千鳥状になるようにした積層型電子部品モジュールが特許文献2に開示されている。

【0004】

特許文献2の積層型電子部品モジュールは、表面の凹凸が抑制されて、搭載電子部品の接続不良および実装先の基板への実装不良が防止できるとされている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平5−6823号公報

【特許文献2】国際公開2009/081865号

【発明の概要】

【発明が解決しようとする課題】

【0006】

磁性体基板の内部の異なる高さに形成された複数のコイル導体が直列に接続されたコイルがインダクタとして機能するためには、コイル導体全体の内外を通過する大きなループ状の磁束が形成される事が望ましい。しかし、各コイル導体が磁性体層内の異なる高さに配置されているため、各コイル導体を個別に巻く不要な磁束が発生する。この不要な磁束はコイル導体全体によるインダクタのインダクタンスに寄与しないので、必要なインダクタンスを得るために多くの巻回数を必要とし、巻回数を多くするためにコイル導体の線幅を細くすると、直流抵抗が増大し、Q値が低下する問題がある。

【0007】

特許文献1、2のいずれでも、前記不要な磁束の発生を抑制して効率よくインダクタンス値を確保することはできない。

本発明は、不要な磁束の発生を抑制して、インダクタとしての電気的特性に優れたコイルを内蔵したコイル内蔵基板を提供することを目的としている。

【課題を解決するための手段】

【0008】

(1)本発明のコイル内蔵基板は、磁性体内に複数のコイル導体が配置され、

前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域が設けられたことを特徴とする。

【0009】

この構造により、隣接するコイル導体間を通過する不要な磁束の発生が抑制される。したがって、コイル導体を個別に周回する、または少ない層数のコイル導体を小領域で周回する磁束が抑制され、その分、コイル導体形成層の全体を周回する磁束が増加するので、効率よくインダクタンスが確保できる。

【0010】

(2)複数の前記コイル導体は、径の大きな外コイル導体と前記外コイル導体より径の小さな内コイル導体とが磁性体層を介して交互に積み重ねられ、

前記積み重ねられる方向において隣接するコイル導体同士の層間が、外コイル導体同士の層間または内コイル導体同士の層間の少なくとも一方であることが好ましい。その構造により、基板表面の平坦度を向上することができる。

【0011】

(3)前記低透磁率領域は外コイル導体同士の層間または内コイル導体同士の層間の一方にのみ設けられていることが好ましい。その構造により、強度劣化が抑えられるとともに形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。外コイル導体と内コイル導体のいずれの側に層間接続空洞を形成するかはL値やコイルの効率の高い側を選択すればよい。

【0012】

(4)前記低透磁率領域は前記コイル導体が設けられた前記磁性体層内のうち、前記中間非磁性体層から離れた側または前記中間非磁性体層寄りの位置に設けられていることが好ましい。その構造により、強度劣化が抑えられるとともに形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。

【0013】

(5)前記磁性体層は磁性体フェライトシートの焼成による層であることが好ましい。

【0014】

(6)前記低透磁率領域は、層間に設けられた孔に充填された熱消失性ペーストの焼成時に消失した層間空洞であることが好ましい。

【0015】

(7)前記低透磁率領域は前記磁性体層の積み重ねられる方向に延びる前記磁性体層による桟で複数の区画に区分されていることが好ましい。この構造により、コイル導体の低透磁率領域への落ち込みを抑制することができる。

【0016】

(8)前記低透磁率領域は、層間に設けられた孔に充填された非磁性体セラミックペーストの焼成により構成された層間非磁性体柱であってもよい。この構造により、基板内に低透磁率領域を設けることによる強度劣化が防止できる。

【0017】

(9)前記低透磁率領域は、層間に設けられた孔に充填された低透磁率の磁性体セラミックペーストの焼成により構成され前記磁性体層より透磁率の低い層間磁性体柱であってもよい。この構造によっても、基板内に低透磁率領域を設けることによる強度劣化が防止できる。

【0018】

(10)前記低透磁率領域の前記コイル導体の幅方向寸法は前記コイル導体の線幅より小さいことが好ましい。この構造により、コイル導体の内外周を磁性体層で確実に支えることができる。

【0019】

(11)本発明のDC−DCコンバータモジュールは、磁性体内に複数のコイル導体が配置されたコイル内蔵基板を備え、このコイル内蔵基板に内蔵されるコイルをコンバータ回路に含むDC−DCコンバータにおいて、

前記コイル内蔵基板は、前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域が設けられていることを特徴とする。

【発明の効果】

【0020】

本発明によれば、不要な磁束の発生が抑制されて、インダクタとしての電気的特性に優れたコイルを内蔵したコイル内蔵基板が構成できる。また、変換効率の高いDC−DCコンバータモジュールを得ることができる。

【図面の簡単な説明】

【0021】

【図1】図1は特許文献1に示されているインダクタ21の断面図である。

【図2】図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図3】図3はコイル内蔵基板101の各層に形成されている導体パターンを順に示す図である。

【図4】図4は第1の実施形態に係るDC−DCコンバータモジュールの回路図である。

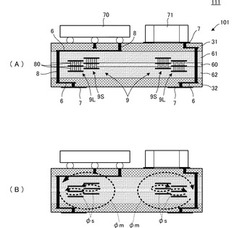

【図5】図5(A)、図5(B)は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図6】図6(A)、図6(B)は第3の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図7】図7(A)、図7(B)はコイル導体9と低透磁率領域80の大きさおよび位置の関係を示す部分拡大平面図である。

【図8】図8は第5の実施形態に係るDC−DCコンバータモジュールの回路図である。

【発明を実施するための形態】

【0022】

《第1の実施形態》

第1の実施形態のコイル内蔵基板およびそれを備えたDC−DCコンバータモジュールの構成を図2〜図4を参照して説明する。

図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このDC−DCコンバータモジュール111は、コイル内蔵基板101と、このコイル内蔵基板101の上面に搭載された電子部品70,71とで構成されている。

【0023】

コイル内蔵基板101は、中間非磁性体層60、第1磁性体層61、第2磁性体層62、および非磁性体層31,32を備えている。中間非磁性体層60および非磁性体層31,32は非磁性体フェライトシートが積層された層、第1磁性体層61および第2磁性体層62は磁性体フェライトシートが積層された層である。

【0024】

第1磁性体層61と第2磁性体層62の一部および中間非磁性体層60のうち所定のフェライトシートにはコイル導体9が形成されている。

【0025】

非磁性体層31は電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む。非磁性体層32は実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む。

【0026】

磁性体層61,62、および非磁性体層31,32には面内配線導体6、層間接続導体8を必要に応じて備えている。

コイル導体9は、径の大きな外コイル導体9Lと外コイル導体より径の小さな内コイル導体9Sとが磁性体または非磁性体の層を介して交互に積み重ねられている。コイル導体9が積み重ねられる順に直列接続されることによりコイルが形成されている。外コイル導体9Lと内コイル導体9Sとが交互に並んでいる。

【0027】

積み重ねられる方向に隣接する外コイル導体9L同士の層間と内コイル導体9S同士の層間にはそれぞれ低透磁率領域80が設けられている。この例では低透磁率領域80は、充填された熱消失性ペーストの焼成時に消失した層間空洞である。具体的には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートにレーザ加工法により孔を開け、その孔内にカーボンペーストや樹脂ペーストなどの熱消失性ペーストを充填し、積層体の焼成時に消失させ空洞にしたものである。

【0028】

前記低透磁率領域80は、孔に充填された非磁性体セラミックペーストの焼成により構成してもよい。その場合には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートに孔を開け、その孔内に非磁性体セラミックペーストを充填すればよい。積層体の焼成により前記非磁性体セラミックペーストは非磁性体セラミックとなる。そして低透磁率領域80は非磁性体セラミックの層間非磁性体柱として構成される。

【0029】

前記低透磁率領域80は、孔に充填された低透磁率の磁性体セラミックペーストの焼成により構成してもよい。その場合には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートに孔を開け、その孔内に低透磁率の磁性体セラミックペーストを充填すればよい。積層体の焼成により前記低透磁率の磁性体セラミックペーストは磁性体層61,62より低い透磁率を有する磁性体セラミックとなる。そして低透磁率領域80は低透磁率磁性体セラミックの層間非磁性体柱として構成される。

【0030】

このように、複数層に形成されているコイル導体9のうち積み重ねられる方向に隣接するコイル導体9同士の層間に低透磁率領域80を設けたことにより、隣接するコイル導体9間を通過する不要な磁束の発生が抑制される。そのため、コイル導体9を個別に周回する、または少ない層数のコイル導体を小領域で周回する磁束が抑制され、その分、コイル導体形成層の全体を周回する磁束が増加するので、効率よくインダクタンスが確保できる。

【0031】

図2(B)は比較例としてのコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このコイル内蔵基板には、図2(A)に示したような低透磁率領域80を設けていない。このように、複数層に形成されているコイル導体9のうち積み重ねられる方向に隣接するコイル導体9同士の層間に低透磁率領域80を設けない構造では、隣接するコイル導体9間を通過する無効な磁束φsが生じやすい。そのため、本来必要な有効な磁束φmが減少する。

【0032】

図2(A)に示した第1の実施形態によれば、図2(B)に示した無効な磁束φsが抑えられ、有効な磁束φmが増大する。

第1の実施形態によれば、コイル導体9の形成層内に中間非磁性体層60を備えているので、磁気ギャップを備えたインダクタとして作用する。

【0033】

なお、低透磁率領域80のコイル導体幅方向寸法はコイル導体9の線幅より小さい。そのため、コイル導体9の内外周を磁性体層で確実に支えることができる。

【0034】

図3は前記コイル内蔵基板101の各層に形成されている導体パターンを順に示す図である。図3において(1)は最下層の導体パターン、(14)は最上層の導体パターンである。(2)〜(13)は最下層と最上層との間の各層の導体パターンである。(1)に示す最下層の導体パターンのうちGNDはグランド電極、Vinは電源入力電極、Voutは電源出力電極、ENはイネーブル信号入力電極である。これらの電極は実装先の基板のランドに接続される。(4)〜(11)層にはコイル導体9a〜9hが形成されている。これらのコイル導体のうち、9a,9c,9e,9gが外コイル導体、9b,9d,9f,9hが内コイル導体である。これらのコイル導体は層間接続導体(ビア導体)を介して直列に接続されている。また、(5)〜(10)層には低透磁率領域80が形成されている。(14)層には制御IC搭載用電極GND,Vin,EN,FB,Loが形成されている。また、チップコンデンサ搭載用電極Ca,Cbが形成されている。

【0035】

このようにして、内コイル導体と外コイル導体とが交互に重なる構造であり、内コイル導体同士が対応する位置および外コイル導体同士が対向する位置に低透磁率領域80を配置したので、層数を増すことなく低透磁率領域80を配置することができる。

【0036】

図4は第1の実施形態に係るDC−DCコンバータモジュールの回路図である。図4においてコンデンサC1は図3中のチップコンデンサ搭載用電極Ca,Cbに接続されたコンデンサであり、図2に示した電子部品71に相当する。インダクタL1は図3中のコイル導体9a〜9hおよび磁性体層による構成されたインダクタである。電子部品70は制御ICである。この制御ICの各端子GND,Vin,EN,FB,Loが図3中の制御IC搭載用電極GND,Vin,EN,FB,Loにそれぞれ接続される。なお、電源出力電極Voutとグランドとの間には平滑コンデンサC2が接続される。制御ICやコンデンサは、コイル内蔵基板101上に搭載しても、親基板上にコイル内蔵基板101と並べて、結線してもよい。コイル内蔵基板101上に搭載した場合、親基板における占有面積を低減できる。親基板上にコイル内蔵基板101と並べた場合には、より低背化できる。

【0037】

電子部品70(制御IC)は電源出力電極Voutの電圧をフィードバック端子FBで受けて、出力電圧が一定となるようにインダクタL1に流れる電流のデューティ比を制御する。

【0038】

なお、前述のとおり、この実施形態のコイル内蔵基板のコイルは磁気ギャップを備えたインダクタとして作用するので、高い直流重畳特性が得られる。

【0039】

《第2の実施形態》

図5(A)、図5(B)は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。図5(A)に示すDC−DCコンバータモジュール112Aは、コイル内蔵基板102Aと、このコイル内蔵基板102Aの上面に搭載された電子部品70,71とで構成されている。図5(B)に示すDC−DCコンバータモジュール112Bは、コイル内蔵基板102Bと、このコイル内蔵基板102Bの上面に搭載された電子部品70,71とで構成されている。

【0040】

図5(A)の例では、内コイル導体9S同士の層間に低透磁率領域80が設けられていて、外コイル導体9L同士の層間には低透磁率領域80は設けられていない。

図5(B)の例では、外コイル導体9L同士の層間に低透磁率領域80が設けられていて、内コイル導体9S同士の層間には低透磁率領域80は設けられていない。図5(A)、図5(B)のいずれについてもその他の構成は第1の実施形態と同様である。

【0041】

このように、内コイル導体9S側または外コイル導体9L側のいずれかにのみ低透磁率領域80を設けてもよい。第1の実施形態に比べて低透磁率領域80の総合体積が少ないので、積み重ねられる方向に隣接するコイル導体9間を通過する無効な磁束の抑制効果は少ないが、コイル内蔵基板の強度劣化が抑えられるとともにモジュール基板表面の凹凸が少なくなる。すなわち形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。外コイル導体と内コイル導体のいずれの側に層間接続空洞を形成するかはインダクタンス値やコイルの効率の高い側を選択すればよい。

【0042】

《第3の実施形態》

図6(A)、図6(B)は第3の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。図6(A)に示すDC−DCコンバータモジュール113Aは、コイル内蔵基板103Aと、このコイル内蔵基板103Aの上面に搭載された電子部品70,71とで構成されている。図6(B)に示すDC−DCコンバータモジュール113Bは、コイル内蔵基板103Bと、このコイル内蔵基板103Bの上面に搭載された電子部品70,71とで構成されている。

【0043】

図6(A)の例では、中間非磁性体層60寄りの位置に低透磁率領域80が設けられている。図6(B)の例では、中間非磁性体層60から離れた位置に低透磁率領域80が設けられている。

【0044】

このように、中間非磁性層60寄りの位置と中間非磁性層60から離れた位置とのいずれかにのみ低透磁率領域80を設けてもよい。第1の実施形態に比べて低透磁率領域80の総合体積が少ないので、積み重ねられる方向に隣接するコイル導体9間を通過する無効な磁束の抑制効果は少ないが、コイル内蔵基板の強度劣化が抑えられるとともにモジュール基板表面の凹凸が少なくなる。すなわち形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。中間非磁性層60寄りの位置と中間非磁性層60から離れた位置とのいずれの側に層間接続空洞を形成するかはインダクタンス値やコイルの効率の高い側を選択すればよい。

【0045】

《第4の実施形態》

第4の実施形態では、低透磁率領域の平面形状の例を示す。

図7(A)、図7(B)はコイル導体9と低透磁率領域80の大きさおよび位置の関係を示す部分拡大平面図である。いずれの例でも、低透磁率領域80のコイル導体幅方向寸法はコイル導体9の線幅より小さい。

【0046】

低透磁率領域80の個々の平面形状は図7(A)のように円形であってもよいし、図7(B)のように概略矩形またはそれをコイル導体9の形状に沿って曲げた形状であってもよい。このような非円形の孔はレーザビームのスキャンによる穴開け加工で形成できる。図7(B)の例では、低透磁率領域80は磁性体層の積み重ねられる方向に延びる磁性体層または中間非磁性体層による桟GRで複数の区画に区分されている。この構造により、コイル導体9の低透磁率領域80への落ち込みを抑制することができる。

【0047】

《第5の実施形態》

第5の実施形態のコイル内蔵基板およびそれを備えたDC−DCコンバータモジュール115の構成を図8を参照して説明する。

図8は第5の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュール115の構成を示す断面図である。このDC−DCコンバータモジュール115は、コイル内蔵基板105と、このコイル内蔵基板105の上面に搭載された電子部品70,71とで構成されている。

【0048】

第1の実施形態では、コイルは、径の大きな外コイル導体9Lと外コイル導体より径の小さな内コイル導体9Sとが磁性体または非磁性体の層を介して交互に積み重ねられ、直列接続されていた。第5の実施形態では、コイルは、複数のコイル導体9が磁性体層を介して積み重ねられている。複数のコイル導体は、いずれも同一の径を有する。積み重ねられる順に直列接続されることによりコイルが形成されている。積み重ねられる方向において隣接するコイル導体9同士の層間に低透磁率領域80が設けられている。低透磁率領域80は、充填された熱消失性ペーストの焼成時に消失した層間空洞である。具体的には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートにレーザ加工法により孔を開け、その孔内にカーボンペーストや樹脂ペーストなどの熱消失性ペーストを充填し、積層体の焼成時に消失させ空洞にしたものである。

第5の実施形態のその他の構成は、第1の実施形態と同様に構成する。

【0049】

第5の実施形態においても、第1の実施形態と同様に、複数層に形成されているコイル導体9のうち積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域80を設けたことにより、隣接するコイル導体9間を通過する不要な磁束の発生が抑制される。そのため、コイル導体9を個別に周回する、または少ない層数のコイル導体を小領域で周回する磁束が抑制され、その分、コイル導体形成層の全体を周回する磁束が増加するので、効率よくインダクタンスが確保できる。

【0050】

また、コイル内蔵基板105のコイルは磁気ギャップを備えたインダクタとして作用するので、高い直流重畳特性が得られる。

【符号の説明】

【0051】

Ca,Cb…チップコンデンサ搭載用電極

GR…桟

6…面内配線導体

7…表面導体膜

8…層間接続導体

9…コイル導体

9a〜9h…コイル導体

9L…外コイル導体

9S…内コイル導体

31,32…非磁性体層

60…中間非磁性体層

61…第1磁性体層

62…第2磁性体層

70,71…電子部品

80…低透磁率領域

101…コイル内蔵基板

102A,102B…コイル内蔵基板

103A,103B…コイル内蔵基板

105…コイル内蔵基板

111…DC−DCコンバータモジュール

112A,112B…DC−DCコンバータモジュール

113A,113B…DC−DCコンバータモジュール

115…DC−DCコンバータモジュール

【技術分野】

【0001】

本発明は、内部にコイルを備え、DC−DCコンバータモジュール等に適用されるコイル内蔵基板およびそれを備えたDC−DCコンバータモジュールに関する。

【背景技術】

【0002】

磁性体基板の内部にコイルが構成されたインダクタが特許文献1に開示されている。図1は特許文献1に示されているインダクタ21の断面図である。この例では、導電体ペーストによりコイル導体3a〜3dが印刷された各磁性体グリーンシートと、低誘電率材料ペーストによる誘電体層22a〜22cが印刷された磁性体グリーンシートとが交互に積層されている。ここで、誘電体層22a〜22cは、コイル導体3a〜3dとほぼ同様なパターンに形成されている。これらの積層体が焼成されて、コイル11を内部に備えた磁性体チップ10が構成される。

特許文献1のインダクタは、積み重ねられる方向に隣接するコイル導体同士で生じる浮遊容量を低減させて高周波域まで使用できるとされている。

【0003】

一方、フェライト基板中に径の大きな外コイル導体と径の小さな内コイル導体とを交互に積み重ねてコイルを形成し、コイルの断面のパターンが千鳥状になるようにした積層型電子部品モジュールが特許文献2に開示されている。

【0004】

特許文献2の積層型電子部品モジュールは、表面の凹凸が抑制されて、搭載電子部品の接続不良および実装先の基板への実装不良が防止できるとされている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平5−6823号公報

【特許文献2】国際公開2009/081865号

【発明の概要】

【発明が解決しようとする課題】

【0006】

磁性体基板の内部の異なる高さに形成された複数のコイル導体が直列に接続されたコイルがインダクタとして機能するためには、コイル導体全体の内外を通過する大きなループ状の磁束が形成される事が望ましい。しかし、各コイル導体が磁性体層内の異なる高さに配置されているため、各コイル導体を個別に巻く不要な磁束が発生する。この不要な磁束はコイル導体全体によるインダクタのインダクタンスに寄与しないので、必要なインダクタンスを得るために多くの巻回数を必要とし、巻回数を多くするためにコイル導体の線幅を細くすると、直流抵抗が増大し、Q値が低下する問題がある。

【0007】

特許文献1、2のいずれでも、前記不要な磁束の発生を抑制して効率よくインダクタンス値を確保することはできない。

本発明は、不要な磁束の発生を抑制して、インダクタとしての電気的特性に優れたコイルを内蔵したコイル内蔵基板を提供することを目的としている。

【課題を解決するための手段】

【0008】

(1)本発明のコイル内蔵基板は、磁性体内に複数のコイル導体が配置され、

前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域が設けられたことを特徴とする。

【0009】

この構造により、隣接するコイル導体間を通過する不要な磁束の発生が抑制される。したがって、コイル導体を個別に周回する、または少ない層数のコイル導体を小領域で周回する磁束が抑制され、その分、コイル導体形成層の全体を周回する磁束が増加するので、効率よくインダクタンスが確保できる。

【0010】

(2)複数の前記コイル導体は、径の大きな外コイル導体と前記外コイル導体より径の小さな内コイル導体とが磁性体層を介して交互に積み重ねられ、

前記積み重ねられる方向において隣接するコイル導体同士の層間が、外コイル導体同士の層間または内コイル導体同士の層間の少なくとも一方であることが好ましい。その構造により、基板表面の平坦度を向上することができる。

【0011】

(3)前記低透磁率領域は外コイル導体同士の層間または内コイル導体同士の層間の一方にのみ設けられていることが好ましい。その構造により、強度劣化が抑えられるとともに形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。外コイル導体と内コイル導体のいずれの側に層間接続空洞を形成するかはL値やコイルの効率の高い側を選択すればよい。

【0012】

(4)前記低透磁率領域は前記コイル導体が設けられた前記磁性体層内のうち、前記中間非磁性体層から離れた側または前記中間非磁性体層寄りの位置に設けられていることが好ましい。その構造により、強度劣化が抑えられるとともに形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。

【0013】

(5)前記磁性体層は磁性体フェライトシートの焼成による層であることが好ましい。

【0014】

(6)前記低透磁率領域は、層間に設けられた孔に充填された熱消失性ペーストの焼成時に消失した層間空洞であることが好ましい。

【0015】

(7)前記低透磁率領域は前記磁性体層の積み重ねられる方向に延びる前記磁性体層による桟で複数の区画に区分されていることが好ましい。この構造により、コイル導体の低透磁率領域への落ち込みを抑制することができる。

【0016】

(8)前記低透磁率領域は、層間に設けられた孔に充填された非磁性体セラミックペーストの焼成により構成された層間非磁性体柱であってもよい。この構造により、基板内に低透磁率領域を設けることによる強度劣化が防止できる。

【0017】

(9)前記低透磁率領域は、層間に設けられた孔に充填された低透磁率の磁性体セラミックペーストの焼成により構成され前記磁性体層より透磁率の低い層間磁性体柱であってもよい。この構造によっても、基板内に低透磁率領域を設けることによる強度劣化が防止できる。

【0018】

(10)前記低透磁率領域の前記コイル導体の幅方向寸法は前記コイル導体の線幅より小さいことが好ましい。この構造により、コイル導体の内外周を磁性体層で確実に支えることができる。

【0019】

(11)本発明のDC−DCコンバータモジュールは、磁性体内に複数のコイル導体が配置されたコイル内蔵基板を備え、このコイル内蔵基板に内蔵されるコイルをコンバータ回路に含むDC−DCコンバータにおいて、

前記コイル内蔵基板は、前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域が設けられていることを特徴とする。

【発明の効果】

【0020】

本発明によれば、不要な磁束の発生が抑制されて、インダクタとしての電気的特性に優れたコイルを内蔵したコイル内蔵基板が構成できる。また、変換効率の高いDC−DCコンバータモジュールを得ることができる。

【図面の簡単な説明】

【0021】

【図1】図1は特許文献1に示されているインダクタ21の断面図である。

【図2】図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図3】図3はコイル内蔵基板101の各層に形成されている導体パターンを順に示す図である。

【図4】図4は第1の実施形態に係るDC−DCコンバータモジュールの回路図である。

【図5】図5(A)、図5(B)は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図6】図6(A)、図6(B)は第3の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図7】図7(A)、図7(B)はコイル導体9と低透磁率領域80の大きさおよび位置の関係を示す部分拡大平面図である。

【図8】図8は第5の実施形態に係るDC−DCコンバータモジュールの回路図である。

【発明を実施するための形態】

【0022】

《第1の実施形態》

第1の実施形態のコイル内蔵基板およびそれを備えたDC−DCコンバータモジュールの構成を図2〜図4を参照して説明する。

図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このDC−DCコンバータモジュール111は、コイル内蔵基板101と、このコイル内蔵基板101の上面に搭載された電子部品70,71とで構成されている。

【0023】

コイル内蔵基板101は、中間非磁性体層60、第1磁性体層61、第2磁性体層62、および非磁性体層31,32を備えている。中間非磁性体層60および非磁性体層31,32は非磁性体フェライトシートが積層された層、第1磁性体層61および第2磁性体層62は磁性体フェライトシートが積層された層である。

【0024】

第1磁性体層61と第2磁性体層62の一部および中間非磁性体層60のうち所定のフェライトシートにはコイル導体9が形成されている。

【0025】

非磁性体層31は電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む。非磁性体層32は実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む。

【0026】

磁性体層61,62、および非磁性体層31,32には面内配線導体6、層間接続導体8を必要に応じて備えている。

コイル導体9は、径の大きな外コイル導体9Lと外コイル導体より径の小さな内コイル導体9Sとが磁性体または非磁性体の層を介して交互に積み重ねられている。コイル導体9が積み重ねられる順に直列接続されることによりコイルが形成されている。外コイル導体9Lと内コイル導体9Sとが交互に並んでいる。

【0027】

積み重ねられる方向に隣接する外コイル導体9L同士の層間と内コイル導体9S同士の層間にはそれぞれ低透磁率領域80が設けられている。この例では低透磁率領域80は、充填された熱消失性ペーストの焼成時に消失した層間空洞である。具体的には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートにレーザ加工法により孔を開け、その孔内にカーボンペーストや樹脂ペーストなどの熱消失性ペーストを充填し、積層体の焼成時に消失させ空洞にしたものである。

【0028】

前記低透磁率領域80は、孔に充填された非磁性体セラミックペーストの焼成により構成してもよい。その場合には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートに孔を開け、その孔内に非磁性体セラミックペーストを充填すればよい。積層体の焼成により前記非磁性体セラミックペーストは非磁性体セラミックとなる。そして低透磁率領域80は非磁性体セラミックの層間非磁性体柱として構成される。

【0029】

前記低透磁率領域80は、孔に充填された低透磁率の磁性体セラミックペーストの焼成により構成してもよい。その場合には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートに孔を開け、その孔内に低透磁率の磁性体セラミックペーストを充填すればよい。積層体の焼成により前記低透磁率の磁性体セラミックペーストは磁性体層61,62より低い透磁率を有する磁性体セラミックとなる。そして低透磁率領域80は低透磁率磁性体セラミックの層間非磁性体柱として構成される。

【0030】

このように、複数層に形成されているコイル導体9のうち積み重ねられる方向に隣接するコイル導体9同士の層間に低透磁率領域80を設けたことにより、隣接するコイル導体9間を通過する不要な磁束の発生が抑制される。そのため、コイル導体9を個別に周回する、または少ない層数のコイル導体を小領域で周回する磁束が抑制され、その分、コイル導体形成層の全体を周回する磁束が増加するので、効率よくインダクタンスが確保できる。

【0031】

図2(B)は比較例としてのコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このコイル内蔵基板には、図2(A)に示したような低透磁率領域80を設けていない。このように、複数層に形成されているコイル導体9のうち積み重ねられる方向に隣接するコイル導体9同士の層間に低透磁率領域80を設けない構造では、隣接するコイル導体9間を通過する無効な磁束φsが生じやすい。そのため、本来必要な有効な磁束φmが減少する。

【0032】

図2(A)に示した第1の実施形態によれば、図2(B)に示した無効な磁束φsが抑えられ、有効な磁束φmが増大する。

第1の実施形態によれば、コイル導体9の形成層内に中間非磁性体層60を備えているので、磁気ギャップを備えたインダクタとして作用する。

【0033】

なお、低透磁率領域80のコイル導体幅方向寸法はコイル導体9の線幅より小さい。そのため、コイル導体9の内外周を磁性体層で確実に支えることができる。

【0034】

図3は前記コイル内蔵基板101の各層に形成されている導体パターンを順に示す図である。図3において(1)は最下層の導体パターン、(14)は最上層の導体パターンである。(2)〜(13)は最下層と最上層との間の各層の導体パターンである。(1)に示す最下層の導体パターンのうちGNDはグランド電極、Vinは電源入力電極、Voutは電源出力電極、ENはイネーブル信号入力電極である。これらの電極は実装先の基板のランドに接続される。(4)〜(11)層にはコイル導体9a〜9hが形成されている。これらのコイル導体のうち、9a,9c,9e,9gが外コイル導体、9b,9d,9f,9hが内コイル導体である。これらのコイル導体は層間接続導体(ビア導体)を介して直列に接続されている。また、(5)〜(10)層には低透磁率領域80が形成されている。(14)層には制御IC搭載用電極GND,Vin,EN,FB,Loが形成されている。また、チップコンデンサ搭載用電極Ca,Cbが形成されている。

【0035】

このようにして、内コイル導体と外コイル導体とが交互に重なる構造であり、内コイル導体同士が対応する位置および外コイル導体同士が対向する位置に低透磁率領域80を配置したので、層数を増すことなく低透磁率領域80を配置することができる。

【0036】

図4は第1の実施形態に係るDC−DCコンバータモジュールの回路図である。図4においてコンデンサC1は図3中のチップコンデンサ搭載用電極Ca,Cbに接続されたコンデンサであり、図2に示した電子部品71に相当する。インダクタL1は図3中のコイル導体9a〜9hおよび磁性体層による構成されたインダクタである。電子部品70は制御ICである。この制御ICの各端子GND,Vin,EN,FB,Loが図3中の制御IC搭載用電極GND,Vin,EN,FB,Loにそれぞれ接続される。なお、電源出力電極Voutとグランドとの間には平滑コンデンサC2が接続される。制御ICやコンデンサは、コイル内蔵基板101上に搭載しても、親基板上にコイル内蔵基板101と並べて、結線してもよい。コイル内蔵基板101上に搭載した場合、親基板における占有面積を低減できる。親基板上にコイル内蔵基板101と並べた場合には、より低背化できる。

【0037】

電子部品70(制御IC)は電源出力電極Voutの電圧をフィードバック端子FBで受けて、出力電圧が一定となるようにインダクタL1に流れる電流のデューティ比を制御する。

【0038】

なお、前述のとおり、この実施形態のコイル内蔵基板のコイルは磁気ギャップを備えたインダクタとして作用するので、高い直流重畳特性が得られる。

【0039】

《第2の実施形態》

図5(A)、図5(B)は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。図5(A)に示すDC−DCコンバータモジュール112Aは、コイル内蔵基板102Aと、このコイル内蔵基板102Aの上面に搭載された電子部品70,71とで構成されている。図5(B)に示すDC−DCコンバータモジュール112Bは、コイル内蔵基板102Bと、このコイル内蔵基板102Bの上面に搭載された電子部品70,71とで構成されている。

【0040】

図5(A)の例では、内コイル導体9S同士の層間に低透磁率領域80が設けられていて、外コイル導体9L同士の層間には低透磁率領域80は設けられていない。

図5(B)の例では、外コイル導体9L同士の層間に低透磁率領域80が設けられていて、内コイル導体9S同士の層間には低透磁率領域80は設けられていない。図5(A)、図5(B)のいずれについてもその他の構成は第1の実施形態と同様である。

【0041】

このように、内コイル導体9S側または外コイル導体9L側のいずれかにのみ低透磁率領域80を設けてもよい。第1の実施形態に比べて低透磁率領域80の総合体積が少ないので、積み重ねられる方向に隣接するコイル導体9間を通過する無効な磁束の抑制効果は少ないが、コイル内蔵基板の強度劣化が抑えられるとともにモジュール基板表面の凹凸が少なくなる。すなわち形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。外コイル導体と内コイル導体のいずれの側に層間接続空洞を形成するかはインダクタンス値やコイルの効率の高い側を選択すればよい。

【0042】

《第3の実施形態》

図6(A)、図6(B)は第3の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。図6(A)に示すDC−DCコンバータモジュール113Aは、コイル内蔵基板103Aと、このコイル内蔵基板103Aの上面に搭載された電子部品70,71とで構成されている。図6(B)に示すDC−DCコンバータモジュール113Bは、コイル内蔵基板103Bと、このコイル内蔵基板103Bの上面に搭載された電子部品70,71とで構成されている。

【0043】

図6(A)の例では、中間非磁性体層60寄りの位置に低透磁率領域80が設けられている。図6(B)の例では、中間非磁性体層60から離れた位置に低透磁率領域80が設けられている。

【0044】

このように、中間非磁性層60寄りの位置と中間非磁性層60から離れた位置とのいずれかにのみ低透磁率領域80を設けてもよい。第1の実施形態に比べて低透磁率領域80の総合体積が少ないので、積み重ねられる方向に隣接するコイル導体9間を通過する無効な磁束の抑制効果は少ないが、コイル内蔵基板の強度劣化が抑えられるとともにモジュール基板表面の凹凸が少なくなる。すなわち形状劣化も抑制される。そのため、親基板から子基板(個片)に分割する際のブレイク不良やクラックの発生を防止できる。中間非磁性層60寄りの位置と中間非磁性層60から離れた位置とのいずれの側に層間接続空洞を形成するかはインダクタンス値やコイルの効率の高い側を選択すればよい。

【0045】

《第4の実施形態》

第4の実施形態では、低透磁率領域の平面形状の例を示す。

図7(A)、図7(B)はコイル導体9と低透磁率領域80の大きさおよび位置の関係を示す部分拡大平面図である。いずれの例でも、低透磁率領域80のコイル導体幅方向寸法はコイル導体9の線幅より小さい。

【0046】

低透磁率領域80の個々の平面形状は図7(A)のように円形であってもよいし、図7(B)のように概略矩形またはそれをコイル導体9の形状に沿って曲げた形状であってもよい。このような非円形の孔はレーザビームのスキャンによる穴開け加工で形成できる。図7(B)の例では、低透磁率領域80は磁性体層の積み重ねられる方向に延びる磁性体層または中間非磁性体層による桟GRで複数の区画に区分されている。この構造により、コイル導体9の低透磁率領域80への落ち込みを抑制することができる。

【0047】

《第5の実施形態》

第5の実施形態のコイル内蔵基板およびそれを備えたDC−DCコンバータモジュール115の構成を図8を参照して説明する。

図8は第5の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュール115の構成を示す断面図である。このDC−DCコンバータモジュール115は、コイル内蔵基板105と、このコイル内蔵基板105の上面に搭載された電子部品70,71とで構成されている。

【0048】

第1の実施形態では、コイルは、径の大きな外コイル導体9Lと外コイル導体より径の小さな内コイル導体9Sとが磁性体または非磁性体の層を介して交互に積み重ねられ、直列接続されていた。第5の実施形態では、コイルは、複数のコイル導体9が磁性体層を介して積み重ねられている。複数のコイル導体は、いずれも同一の径を有する。積み重ねられる順に直列接続されることによりコイルが形成されている。積み重ねられる方向において隣接するコイル導体9同士の層間に低透磁率領域80が設けられている。低透磁率領域80は、充填された熱消失性ペーストの焼成時に消失した層間空洞である。具体的には、磁性体フェライトのグリーンシートおよび非磁性体フェライトのグリーンシートにレーザ加工法により孔を開け、その孔内にカーボンペーストや樹脂ペーストなどの熱消失性ペーストを充填し、積層体の焼成時に消失させ空洞にしたものである。

第5の実施形態のその他の構成は、第1の実施形態と同様に構成する。

【0049】

第5の実施形態においても、第1の実施形態と同様に、複数層に形成されているコイル導体9のうち積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域80を設けたことにより、隣接するコイル導体9間を通過する不要な磁束の発生が抑制される。そのため、コイル導体9を個別に周回する、または少ない層数のコイル導体を小領域で周回する磁束が抑制され、その分、コイル導体形成層の全体を周回する磁束が増加するので、効率よくインダクタンスが確保できる。

【0050】

また、コイル内蔵基板105のコイルは磁気ギャップを備えたインダクタとして作用するので、高い直流重畳特性が得られる。

【符号の説明】

【0051】

Ca,Cb…チップコンデンサ搭載用電極

GR…桟

6…面内配線導体

7…表面導体膜

8…層間接続導体

9…コイル導体

9a〜9h…コイル導体

9L…外コイル導体

9S…内コイル導体

31,32…非磁性体層

60…中間非磁性体層

61…第1磁性体層

62…第2磁性体層

70,71…電子部品

80…低透磁率領域

101…コイル内蔵基板

102A,102B…コイル内蔵基板

103A,103B…コイル内蔵基板

105…コイル内蔵基板

111…DC−DCコンバータモジュール

112A,112B…DC−DCコンバータモジュール

113A,113B…DC−DCコンバータモジュール

115…DC−DCコンバータモジュール

【特許請求の範囲】

【請求項1】

磁性体内に複数のコイル導体が配置されたコイル内蔵基板において、

前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接する前記コイル導体同士の層間に低透磁率領域が設けられたことを特徴とするコイル内蔵基板。

【請求項2】

複数の前記コイル導体は、径の大きな外コイル導体と前記外コイル導体より径の小さな内コイル導体とが磁性体層を介して交互に積み重ねられ、

前記積み重ねられる方向に隣接するコイル導体同士の層間が、外コイル導体同士の層間または内コイル導体同士の層間の少なくとも一方である、請求項1に記載のコイル内蔵基板。

【請求項3】

前記外コイル導体同士の層間または前記内コイル導体同士の層間の一方にのみ前記低透磁率領域が設けられたことを特徴とする請求項2に記載のコイル内蔵基板。

【請求項4】

前記コイル導体が形成された層範囲内のうち外層寄りまたは中間層寄りの位置に前記低透磁率領域が設けられた、請求項2または3に記載のコイル内蔵基板。

【請求項5】

前記磁性体層は磁性体フェライトシートの焼成による磁性体層である、請求項1〜4のいずれかに記載のコイル内蔵基板。

【請求項6】

前記低透磁率領域は、層間に設けられた孔に充填された熱消失性ペーストの焼成時に消失した層間空洞である、請求項1〜5のいずれかに記載のコイル内蔵基板。

【請求項7】

前記低透磁率領域は前記磁性体層の積み重ねられる方向に延びる前記磁性体層による桟で複数の区画に区分されている、請求項6に記載のコイル内蔵基板。

【請求項8】

前記低透磁率領域は、層間に設けられた孔に充填された非磁性体セラミックペーストの焼成により構成された層間非磁性体柱である、請求項1〜5のいずれかに記載のコイル内蔵基板。

【請求項9】

前記低透磁率領域は、層間に設けられた孔に充填された低透磁率の磁性体セラミックペーストの焼成により構成され、前記磁性体層より透磁率の低い層間磁性体柱である、請求項1〜5のいずれかに記載のコイル内蔵基板。

【請求項10】

前記低透磁率領域の前記コイル導体の幅方向寸法は前記コイル導体の線幅より小さい、請求項1〜9のいずれかに記載のコイル内蔵基板。

【請求項11】

磁性体内に複数のコイル導体が配置されたコイル内蔵基板を備え、このコイル内蔵基板に内蔵されるコイルをコンバータ回路に含むDC−DCコンバータにおいて、

前記コイル内蔵基板は、前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域が設けられていることを特徴とするDC−DCコンバータモジュール。

【請求項1】

磁性体内に複数のコイル導体が配置されたコイル内蔵基板において、

前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接する前記コイル導体同士の層間に低透磁率領域が設けられたことを特徴とするコイル内蔵基板。

【請求項2】

複数の前記コイル導体は、径の大きな外コイル導体と前記外コイル導体より径の小さな内コイル導体とが磁性体層を介して交互に積み重ねられ、

前記積み重ねられる方向に隣接するコイル導体同士の層間が、外コイル導体同士の層間または内コイル導体同士の層間の少なくとも一方である、請求項1に記載のコイル内蔵基板。

【請求項3】

前記外コイル導体同士の層間または前記内コイル導体同士の層間の一方にのみ前記低透磁率領域が設けられたことを特徴とする請求項2に記載のコイル内蔵基板。

【請求項4】

前記コイル導体が形成された層範囲内のうち外層寄りまたは中間層寄りの位置に前記低透磁率領域が設けられた、請求項2または3に記載のコイル内蔵基板。

【請求項5】

前記磁性体層は磁性体フェライトシートの焼成による磁性体層である、請求項1〜4のいずれかに記載のコイル内蔵基板。

【請求項6】

前記低透磁率領域は、層間に設けられた孔に充填された熱消失性ペーストの焼成時に消失した層間空洞である、請求項1〜5のいずれかに記載のコイル内蔵基板。

【請求項7】

前記低透磁率領域は前記磁性体層の積み重ねられる方向に延びる前記磁性体層による桟で複数の区画に区分されている、請求項6に記載のコイル内蔵基板。

【請求項8】

前記低透磁率領域は、層間に設けられた孔に充填された非磁性体セラミックペーストの焼成により構成された層間非磁性体柱である、請求項1〜5のいずれかに記載のコイル内蔵基板。

【請求項9】

前記低透磁率領域は、層間に設けられた孔に充填された低透磁率の磁性体セラミックペーストの焼成により構成され、前記磁性体層より透磁率の低い層間磁性体柱である、請求項1〜5のいずれかに記載のコイル内蔵基板。

【請求項10】

前記低透磁率領域の前記コイル導体の幅方向寸法は前記コイル導体の線幅より小さい、請求項1〜9のいずれかに記載のコイル内蔵基板。

【請求項11】

磁性体内に複数のコイル導体が配置されたコイル内蔵基板を備え、このコイル内蔵基板に内蔵されるコイルをコンバータ回路に含むDC−DCコンバータにおいて、

前記コイル内蔵基板は、前記複数のコイル導体が磁性体層を介して積み重ねられ、前記積み重ねられる方向に隣接するコイル導体同士の層間に低透磁率領域が設けられていることを特徴とするDC−DCコンバータモジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−164770(P2012−164770A)

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願番号】特願2011−23042(P2011−23042)

【出願日】平成23年2月4日(2011.2.4)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願日】平成23年2月4日(2011.2.4)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]