コイル内蔵基板

【課題】コイル導体9の形成層を中央高さよりずれた位置に配置するとともに、コイル導体によるインダクタとしての電気特性の劣化を抑えたコイル内蔵基板を構成する。

【解決手段】コイル内蔵基板101は、コイル導体9と磁性体とが積層された第1の磁性体層21と、電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む第1表面層31と、実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む第2表面層32と、を備えている。コイル導体9を含む層であるコイル導体形成層21Cと第1表面層31との間に第2の磁性体層22を備えている。コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2で表すと、A<B、μ1<μ2の関係にある。

【解決手段】コイル内蔵基板101は、コイル導体9と磁性体とが積層された第1の磁性体層21と、電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む第1表面層31と、実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む第2表面層32と、を備えている。コイル導体9を含む層であるコイル導体形成層21Cと第1表面層31との間に第2の磁性体層22を備えている。コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2で表すと、A<B、μ1<μ2の関係にある。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、内部にコイルを備え、例えばDC−DCコンバータモジュールに適用されるコイル内蔵基板に関する。

【背景技術】

【0002】

基板の内部にコイルが構成されたDC−DCコンバータモジュールが特許文献1に開示されている。図1は特許文献1に示されている積層型セラミック電子部品(DC−DCコンバータモジュール)1の断面図である。積層型セラミック電子部品1は、フェライトセラミックからなる基材層2と、基材層2の上下主面上にそれぞれ配置されかつフェライトセラミックからなる表面層3,4とを含む積層構造を有するセラミック積層体5を備えている。また、積層型セラミック電子部品1は、セラミック積層体5の内部および外部に設けられる導体パターンを備えている。導体パターンには大別して面内配線導体6と表面導体膜7と層間接続導体8とがある。面内配線導体6および表面導体膜7は、この積層型セラミック電子部品1を製造する過程において、基材層2または表面層3,4を形成するために積層されるセラミックグリーンシートの主面上に形成されていて、層間接続導体8は上記セラミックグリーンシートを厚み方向に貫通するように設けられている。面内配線導体6はセラミック積層体5の内部に形成されている。

【0003】

特定の面内配線導体6および特定の層間接続導体8によって、コイル導体9が基材層2の内部に形成されている。この積層型セラミック電子部品1は、たとえばDC−DCコンバータを構成するもので、表面層3の外方に向く主面上には、表面実装型電子部品10および11が搭載される。電子部品10はたとえばICチップであり、表面層3の外方に向く主面上に形成された表面導体膜7にはんだバンプ12を介して電気的に接続される。他方の電子部品11はたとえばチップコンデンサであり、表面層3の外方に向く主面上に形成された表面導体膜7にはんだ13を介して電気的に接続されている。下方の表面層4の外方に向く主面上に形成された表面導体膜7は、図示しないマザー基板上に、この積層型セラミック電子部品1を実装する際の端子電極として用いられている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開2007/148556号

【発明の概要】

【発明が解決しようとする課題】

【0005】

コイル導体の周囲に各種配線やシールド導体等がある場合、これらの各種配線やシールド導体とコイル導体との距離が不均一であると、コイル導体による磁界が周囲の各種配線やシールド導体に妨げられるなどして、理想的な磁界分布が実現できない。その結果、インダクタの電気特性が劣化する。すなわち、得られるインダクタンス値が小さくなり、必要なインダクタンス値を得るためにコイル導体の線幅を細くして巻回数を増すと、Q値および直流抵抗値が劣化する。

【0006】

図1に示したDC−DCコンバータモジュールに用いられる従来のコイル内蔵基板においては、コイル導体9を基材層2の中央高さ位置に配置しているので、このコイル導体9の形成層から表面層3,4までの厚みが等しく、コイル導体9の周囲の磁束密度の集中(偏り)が少ない。

【0007】

しかし、このコイル内蔵基板を備えるモジュールの小型低背化に伴い、図1に示した基材層2が薄くなると、コイル導体9の形成層は基材層2の中央高さ位置に必ずしも配置できない。例えば、基材層2内の配線導体(層間接続導体8など)の影響を加味してコイル導体9の形成層を中央高さ位置より上または下に配置することも必要になる。

【0008】

そこで、本発明は、コイル導体9の形成層を中央高さよりずれた位置に配置するとともに、コイル導体のインダクタとしての電気特性の劣化を抑えたコイル内蔵基板を提供することを目的としている。

【課題を解決するための手段】

【0009】

(1)本発明は、コイル導体と磁性体とが積層された第1の磁性体層と、第1主面側に形成され、表面導体膜を含む第1表面層と、第2主面側に形成され、表面導体膜を含む第2表面層と、を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に第2の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2で表すと、A<B、μ1<μ2の関係であることを特徴とする。

【0010】

(2)本発明は、コイル導体と磁性体とが積層された第1の磁性体層と、第1主面側に形成され、表面導体膜を含む第1表面層と、第2主面側に形成され、表面導体膜を含む第2表面層と、を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1の関係であることを特徴とする。

【0011】

(3)本発明は、コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、第2主面側に形成され、表面導体膜を含む第2表面層と、を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に第2の磁性体層を備え、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1<μ2の関係であることを特徴とする。

【0012】

(4)(1)または(3)において、前記コイル導体形成層と前記第2磁性体層との間、または前記第1表面層と前記第2磁性体層との間に第4の磁性体層を備え、第4の磁性体層の透磁率をμ4で表すと、μ1<μ2<μ4の関係であることが好ましい。

【0013】

(5)(2)または(3)において、前記コイル導体形成層と前記第3磁性体層との間、または前記第2表面層と前記第3磁性体層との間に第5の磁性体層を備え、第5の磁性体層の透磁率をμ5で表すと、μ5<μ3<μ1の関係であることが好ましい。

【発明の効果】

【0014】

本発明によれば、基板内の配線設計によるコイル導体周囲の配線導体に合わせて、コイル導体による磁束をコントロールし、より均一な磁界を発生するコイルが形成でき、直流抵抗が低く、Q値が高いコイル内蔵基板を構成できる。

【図面の簡単な説明】

【0015】

【図1】図1は特許文献1に示されている積層型セラミック電子部品の断面図である。

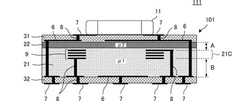

【図2】図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図3】図3は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図4】図4(A)、図4(B)、図4(C)は第3の実施形態の三種のコイル内蔵基板103A,103B,103C、およびそれらを備えたDC−DCコンバータモジュール113A,113B,113Cの構成を示す断面図である。

【図5】図5(A)、図5(B)、図5(C)は第4の実施形態の三種のコイル内蔵基板104A,104B,104C、およびそれらを備えたDC−DCコンバータモジュール114A,114B,114Cの構成を示す断面図である。

【図6】図6(A)、図6(B)、図6(C)は第5の実施形態の三種のコイル内蔵基板105A,105B,105C、およびそれらを備えたDC−DCコンバータモジュール115A,115B,115Cの構成を示す断面図である。

【図7】図7(A)、図7(B)は第6の実施形態の二種のコイル内蔵基板106A,106B、およびそれらを備えたDC−DCコンバータモジュール116A,116Bの構成を示す断面図である。

【図8】図8(A)、図8(B)は第7の実施形態の二種のコイル内蔵基板107A,107B、およびそれらを備えたDC−DCコンバータモジュール117A,117Bの構成を示す断面図である。

【図9】図9は第8の実施形態のコイル内蔵基板108、およびそれらを備えたDC−DCコンバータモジュール118の構成を示す断面図である。

【発明を実施するための形態】

【0016】

《第1の実施形態》

図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このDC−DCコンバータモジュール111は、コイル内蔵基板101と、このコイル内蔵基板101の上面に搭載された電子部品(11等)とで構成されている。通常、コイル内蔵基板101の上面には複数の電子部品が搭載されるが、図2ではそれらの電子部品のうち一つ(電子部品11)のみを図示している。

【0017】

コイル内蔵基板101は、コイル導体9と磁性体とが積層された第1の磁性体層21と、電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む第1表面層31と、実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む第2表面層32と、を備えている。

【0018】

第1の磁性体層21、第1表面層31および第2表面層32には面内配線導体6、層間接続導体8を必要に応じて備えている。

コイル導体9を含む層であるコイル導体形成層21Cと第1表面層31との間に第2の磁性体層22を備えている。

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2で表すと、A<B、μ1<μ2の関係にある。

【0019】

このように、コイル導体形成層21Cが電子部品搭載面側(第1主面側)に寄っている場合には、コイル導体形成層21Cと第1表面層31との間に第1の磁性体層21より透磁率の高い第2の磁性体層22を配置することにより、コイル導体形成層21Cと第1表面層31との間隔が狭いことによる磁界分布の不均一性が抑制される。具体的には、第2の磁性体層22はコイル導体9による磁束を層方向に導き、第1表面層31への(垂直方向への)磁束の拡がりが抑制される。そのため、第1表面層31に形成されている面内配線導体6、表面導体膜7および層間接続導体8等に渦電流が流れにくくなる。すなわち、第1表面層31に形成されている面内配線導体6、表面導体膜7および層間接続導体8等の影響を受けにくくなり、コイル導体9のインダクタとしての電気的特性の劣化が抑制される。

【0020】

これにより、より均一な磁界を発生するコイルが形成でき、直流抵抗が低く、Q値が高いコイル内蔵基板を構成できる。

【0021】

前記コイル内蔵基板101はグリーンシートプロセスにより製造される。前記第1の磁性体層21および第2の磁性体層22は、例えばFe-Ni-Zn-Cu系の酸化物を主成分とする磁性フェライトである。焼成前は、これらのセラミックグリーンシートの積層体である。また、前記第1表面層31および第2表面層32は、Fe-Zn-Cu系の酸化物を主成分とする非磁性フェライトである。焼成前はこのセラミックグリーンシートの積層体である。

【0022】

前記層間接続導体8は導電性ペーストの焼結体である。焼成前は所定のセラミックグリーンシートに形成された貫通孔に充填された導電性ペースト(未焼結の層間接続導体)である。また、コイル導体9、面内配線導体6、表面導体膜7、層間接続導体8は導電性ペーストの焼結体である。焼成前は所定のセラミックグリーンシート上に印刷された導電性ペーストである。これらの導電性ペーストに含まれる導電性金属は銀または銀/パラジウムを主成分としているものであることが好ましい。

【0023】

《第2の実施形態》

図3は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このDC−DCコンバータモジュール112は、コイル内蔵基板102と、このコイル内蔵基板102の上面に搭載された電子部品(11等)とで構成されている。

【0024】

コイル内蔵基板102は、コイル導体9と磁性体とが積層された第1の磁性体層21と、電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む第1表面層31と、実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む第2表面層32と、を備えている。

コイル導体9を含む層であるコイル導体形成層21Cと第2表面層32との間に第3の磁性体層23を備えている。

【0025】

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第3の磁性体層23の透磁率をμ3で表すと、A<B、μ3<μ1の関係にある。

【0026】

このように、コイル導体形成層21Cが電子部品搭載面側(第1主面側)に寄っている場合には、コイル導体形成層21Cと第2表面層32との間に第1の磁性体層21より透磁率の低い第3の磁性体層23を配置することにより、コイル導体形成層21Cと第2表面層32との間隔が広いことによる磁界分布の不均一性が抑制される。具体的には、第3の磁性体層23はコイル導体9による磁束の透過が抑制され、コイル導体形成層21Cの上下にほぼ均等に磁界が集中する。そのため、第2表面層32に形成されている面内配線導体6、表面導体膜7および層間接続導体8等に渦電流が流れにくくなる。すなわち、第2表面層32に形成されている面内配線導体6、表面導体膜7および層間接続導体8等の影響を受けにくくなり、コイル導体9のインダクタとしての電気的特性の劣化が抑制される。

【0027】

また、透磁率の小さなフェライトは一般に誘電正接(tanδ)が相対的に小さいので、透磁率の小さな第3の磁性体層23を配置することにより、誘電体損失が低減されて、そのことによってもQ値を高めることができる。

【0028】

これにより、より均一な磁界を発生するインダクタが形成でき、直流抵抗が低く、Q値が高いコイル内蔵基板を構成できる。

【0029】

《第3の実施形態》

図4(A)、図4(B)、図4(C)は第3の実施形態の三種のコイル内蔵基板103A,103B,103C、およびそれらを備えたDC−DCコンバータモジュール113A,113B,113Cの構成を示す断面図である。これらのDC−DCコンバータモジュール113A,113B,113Cは、コイル内蔵基板103A,103B,103Cと、これらのコイル内蔵基板103A,103B,103Cの上面に搭載された電子部品(11等)とで構成されている。

【0030】

前記コイル内蔵基板103A,103B,103Cと第1の実施形態で図2に示したコイル内蔵基板101と異なるのは第2の磁性体層22の配置である。第1の実施形態ではコイル導体形成層21Cと第1表面層31との間に第2の磁性体層22を単に配置された例を示したが、図4(A)のコイル内蔵基板103Aでは、第2の磁性体層22が第1表面層31寄りの位置または第1表面層31に接する位置に配置されている。図4(B)のコイル内蔵基板103Bでは、第2の磁性体層22がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。さらに、図4(C)のコイル内蔵基板103Cでは、第2の磁性体層22をコイル導体形成層21Cと第1表面層31との間の全体にわたって第2の磁性体層22が配置されている。

【0031】

このように、第2の磁性体層22の厚みと位置を適宜定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0032】

《第4の実施形態》

図5(A)、図5(B)、図5(C)は第4の実施形態の三種のコイル内蔵基板104A,104B,104C、およびそれらを備えたDC−DCコンバータモジュール114A,114B,114Cの構成を示す断面図である。これらのDC−DCコンバータモジュール114A,114B,114Cは、コイル内蔵基板104A,104B,104Cと、これらのコイル内蔵基板104A,104B,104Cの上面に搭載された電子部品(11等)とで構成されている。

【0033】

前記コイル内蔵基板104A,104B,104Cと第2の実施形態で図3に示したコイル内蔵基板102と異なるのは第3の磁性体層23の配置である。第2の実施形態ではコイル導体形成層21Cと第2表面層32との間に第3の磁性体層23が単に配置された例を示したが、図5(A)のコイル内蔵基板104Aでは、第3の磁性体層23が第2表面層32寄りの位置または第2表面層32に接する位置に配置されている。図5(B)のコイル内蔵基板104Bでは、第3の磁性体層23がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。さらに、図5(C)のコイル内蔵基板104Cでは、第3の磁性体層23がコイル導体形成層21Cと第2表面層32との間の全体にわたって第3の磁性体層23が配置されている。

【0034】

このように、第3の磁性体層23の厚みと位置を適宜定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0035】

《第5の実施形態》

図6(A)、図6(B)、図6(C)は第5の実施形態の三種のコイル内蔵基板105A,105B,105C、およびそれらを備えたDC−DCコンバータモジュール115A,115B,115Cの構成を示す断面図である。これらのDC−DCコンバータモジュール115A,115B,115Cは、コイル内蔵基板105A,105B,105Cと、これらのコイル内蔵基板105A,105B,105Cの上面に搭載された電子部品(11等)とで構成されている。

【0036】

第5の実施形態のコイル内蔵基板105A,105B,105Cは、コイル導体形成層21Cと第1表面層31との間に第2の磁性体層22が配置されていて、コイル導体形成層21Cと第2表面層32との間に第3の磁性体層23が配置されている。

【0037】

図6(A)のコイル内蔵基板105Aでは、第2の磁性体層22が第1表面層31寄りの位置または第1表面層31に接する位置に配置されている。また第3の磁性体層23が第2表面層32寄りの位置または第2表面層32に接する位置に配置されている。

【0038】

図6(B)のコイル内蔵基板105Bでは、第2の磁性体層22がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。また第3の磁性体層23がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。

【0039】

図6(C)のコイル内蔵基板105Cでは、第2の磁性体層22がコイル導体形成層21Cと第1表面層31との間の全体にわたって配置されている。また第3の磁性体層23がコイル導体形成層21Cと第2表面層32との間の全体にわたって配置されている。

【0040】

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2、第3の磁性体層23の透磁率をμ3で表すと、A<B、μ3<μ1<μ2の関係にある。

【0041】

このように、コイル導体形成層21Cと第1表面層31との間に第2の磁性体層22、コイル導体形成層21Cと第2表面層32との間に第3の磁性体層23をそれぞれ設けることにより、コイル導体形成層21Cに近い導体(第1表面層31に形成されている面内配線導体6、表面導体膜7および層間接続導体8等)と遠い導体(第2表面層32に形成されている面内配線導体6、表面導体膜7および層間接続導体8等)の両方について渦電流損による悪影響をより効果的に抑制できる。

【0042】

また、第2の磁性体層22および第3の磁性体層23の厚みと位置を適宜定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0043】

《第6の実施形態》

図7(A)、図7(B)は第6の実施形態の二種のコイル内蔵基板106A,106B、およびそれらを備えたDC−DCコンバータモジュール116A,116Bの構成を示す断面図である。これらのDC−DCコンバータモジュール116A,116Bは、コイル内蔵基板106A,106Bと、これらのコイル内蔵基板106A,106Bの上面に搭載された電子部品(11等)とで構成されている。

【0044】

図7(A)の例では、コイル導体形成層21Cと第2の磁性体層22との間に第4の磁性体層24を備えている。図7(B)の例では、第1表面層31と第2の磁性体層22との間に第4の磁性体層24を備えている。図7(A)、図7(B)のいずれについても、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2、第4の磁性体層24の透磁率をμ4で表すと、A<B、μ1<μ2<μ4の関係にある。

【0045】

このように、コイル導体形成層21Cと第1表面層31との間に、互いに透磁率の異なる二層の磁性体層を配置し、それらの厚み、透磁率および位置関係を定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0046】

《第7の実施形態》

図8(A)、図8(B)は第7の実施形態の二種のコイル内蔵基板107A,107B、およびそれらを備えたDC−DCコンバータモジュール117A,117Bの構成を示す断面図である。これらのDC−DCコンバータモジュール117A,117Bは、コイル内蔵基板107A,107Bと、これらのコイル内蔵基板107A,107Bの上面に搭載された電子部品(11等)とで構成されている。

【0047】

図8(A)の例では、コイル導体形成層21Cと第3の磁性体層23との間に第5の磁性体層25を備えている。図8(B)の例では、第2表面層32と第3の磁性体層23との間に第5の磁性体層25を備えている。図8(A)、図8(B)のいずれについても、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第3の磁性体層23の透磁率をμ3、第5の磁性体層25の透磁率をμ5で表すと、A<B、μ5<μ3<μ1の関係にある。

【0048】

このように、コイル導体形成層21Cと第2表面層32との間に、互いに透磁率の異なる二層の磁性体層を配置し、それらの厚み、透磁率および位置関係を定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0049】

《第8の実施形態》

図9は第8の実施形態のコイル内蔵基板108、およびそれらを備えたDC−DCコンバータモジュール118の構成を示す断面図である。このDC−DCコンバータモジュール118は、コイル内蔵基板108と、このコイル内蔵基板108の上面に搭載された電子部品(11等)とで構成されている。

【0050】

図9の例では、コイル導体形成層21Cと第1表面層31との間に第2の磁性体層22が設けられ、この第2の磁性体層22と第1表面層31との間に第4の磁性体層24が設けられている。また、コイル導体形成層21Cと第2表面層32との間に第3の磁性体層23が設けられ、この第3の磁性体層23と第2表面層32との間に第5の磁性体層25が設けられている。

【0051】

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2、第3の磁性体層23の透磁率をμ3、第4の磁性体層24の透磁率をμ4、第5の磁性体層25の透磁率をμ5で表すと、A<B、

μ5<μ3<μ1<μ2<μ4または、

μ3<μ5<μ1<μ2<μ4または、

μ5<μ3<μ1<μ4<μ2または、

μ3<μ5<μ1<μ4<μ2

の関係にある。

【0052】

このように、コイル導体形成層21Cと第1表面層31との間および第2表面層32との間に、互いに透磁率の異なる二層の磁性体層をそれぞれ配置し、それらの厚み、透磁率および位置関係を定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0053】

《他の実施形態》

以上に示した各実施形態では、電子部品搭載面を第1表面層31とし、実装面を第2表面層32側としたが、逆に、実装面が第1表面層31、電子部品搭載面が第2表面層32であってもよい。その場合でも、コイル導体形成層21Cと第1表面層との間隔をA、コイル導体形成層21Cと第2表面層との間隔をBで表したとき、A<Bの関係であれば、各実施形態で示した記述がそのまま当てはまる。

【符号の説明】

【0054】

6…面内配線導体

7…表面導体膜

8…層間接続導体

9…コイル導体

11…電子部品

21…第1の磁性体層

21C…コイル導体形成層

22…第2の磁性体層

23…第3の磁性体層

24…第4の磁性体層

25…第5の磁性体層

31…第1表面層

32…第2表面層

101,102,108…コイル内蔵基板

103A,103B,103C…コイル内蔵基板

104A,104B,104C…コイル内蔵基板

105A,105B,105C…コイル内蔵基板

106A,106B…コイル内蔵基板

107A,107B…コイル内蔵基板

111,112,118…DC−DCコンバータモジュール

113A,113B,113C…DC−DCコンバータモジュール

114A,114B,114C…DC−DCコンバータモジュール

115A,115B,115C…DC−DCコンバータモジュール

116A,116B…DC−DCコンバータモジュール

117A,117B…DC−DCコンバータモジュール

【技術分野】

【0001】

本発明は、内部にコイルを備え、例えばDC−DCコンバータモジュールに適用されるコイル内蔵基板に関する。

【背景技術】

【0002】

基板の内部にコイルが構成されたDC−DCコンバータモジュールが特許文献1に開示されている。図1は特許文献1に示されている積層型セラミック電子部品(DC−DCコンバータモジュール)1の断面図である。積層型セラミック電子部品1は、フェライトセラミックからなる基材層2と、基材層2の上下主面上にそれぞれ配置されかつフェライトセラミックからなる表面層3,4とを含む積層構造を有するセラミック積層体5を備えている。また、積層型セラミック電子部品1は、セラミック積層体5の内部および外部に設けられる導体パターンを備えている。導体パターンには大別して面内配線導体6と表面導体膜7と層間接続導体8とがある。面内配線導体6および表面導体膜7は、この積層型セラミック電子部品1を製造する過程において、基材層2または表面層3,4を形成するために積層されるセラミックグリーンシートの主面上に形成されていて、層間接続導体8は上記セラミックグリーンシートを厚み方向に貫通するように設けられている。面内配線導体6はセラミック積層体5の内部に形成されている。

【0003】

特定の面内配線導体6および特定の層間接続導体8によって、コイル導体9が基材層2の内部に形成されている。この積層型セラミック電子部品1は、たとえばDC−DCコンバータを構成するもので、表面層3の外方に向く主面上には、表面実装型電子部品10および11が搭載される。電子部品10はたとえばICチップであり、表面層3の外方に向く主面上に形成された表面導体膜7にはんだバンプ12を介して電気的に接続される。他方の電子部品11はたとえばチップコンデンサであり、表面層3の外方に向く主面上に形成された表面導体膜7にはんだ13を介して電気的に接続されている。下方の表面層4の外方に向く主面上に形成された表面導体膜7は、図示しないマザー基板上に、この積層型セラミック電子部品1を実装する際の端子電極として用いられている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開2007/148556号

【発明の概要】

【発明が解決しようとする課題】

【0005】

コイル導体の周囲に各種配線やシールド導体等がある場合、これらの各種配線やシールド導体とコイル導体との距離が不均一であると、コイル導体による磁界が周囲の各種配線やシールド導体に妨げられるなどして、理想的な磁界分布が実現できない。その結果、インダクタの電気特性が劣化する。すなわち、得られるインダクタンス値が小さくなり、必要なインダクタンス値を得るためにコイル導体の線幅を細くして巻回数を増すと、Q値および直流抵抗値が劣化する。

【0006】

図1に示したDC−DCコンバータモジュールに用いられる従来のコイル内蔵基板においては、コイル導体9を基材層2の中央高さ位置に配置しているので、このコイル導体9の形成層から表面層3,4までの厚みが等しく、コイル導体9の周囲の磁束密度の集中(偏り)が少ない。

【0007】

しかし、このコイル内蔵基板を備えるモジュールの小型低背化に伴い、図1に示した基材層2が薄くなると、コイル導体9の形成層は基材層2の中央高さ位置に必ずしも配置できない。例えば、基材層2内の配線導体(層間接続導体8など)の影響を加味してコイル導体9の形成層を中央高さ位置より上または下に配置することも必要になる。

【0008】

そこで、本発明は、コイル導体9の形成層を中央高さよりずれた位置に配置するとともに、コイル導体のインダクタとしての電気特性の劣化を抑えたコイル内蔵基板を提供することを目的としている。

【課題を解決するための手段】

【0009】

(1)本発明は、コイル導体と磁性体とが積層された第1の磁性体層と、第1主面側に形成され、表面導体膜を含む第1表面層と、第2主面側に形成され、表面導体膜を含む第2表面層と、を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に第2の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2で表すと、A<B、μ1<μ2の関係であることを特徴とする。

【0010】

(2)本発明は、コイル導体と磁性体とが積層された第1の磁性体層と、第1主面側に形成され、表面導体膜を含む第1表面層と、第2主面側に形成され、表面導体膜を含む第2表面層と、を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1の関係であることを特徴とする。

【0011】

(3)本発明は、コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、第2主面側に形成され、表面導体膜を含む第2表面層と、を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に第2の磁性体層を備え、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1<μ2の関係であることを特徴とする。

【0012】

(4)(1)または(3)において、前記コイル導体形成層と前記第2磁性体層との間、または前記第1表面層と前記第2磁性体層との間に第4の磁性体層を備え、第4の磁性体層の透磁率をμ4で表すと、μ1<μ2<μ4の関係であることが好ましい。

【0013】

(5)(2)または(3)において、前記コイル導体形成層と前記第3磁性体層との間、または前記第2表面層と前記第3磁性体層との間に第5の磁性体層を備え、第5の磁性体層の透磁率をμ5で表すと、μ5<μ3<μ1の関係であることが好ましい。

【発明の効果】

【0014】

本発明によれば、基板内の配線設計によるコイル導体周囲の配線導体に合わせて、コイル導体による磁束をコントロールし、より均一な磁界を発生するコイルが形成でき、直流抵抗が低く、Q値が高いコイル内蔵基板を構成できる。

【図面の簡単な説明】

【0015】

【図1】図1は特許文献1に示されている積層型セラミック電子部品の断面図である。

【図2】図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図3】図3は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。

【図4】図4(A)、図4(B)、図4(C)は第3の実施形態の三種のコイル内蔵基板103A,103B,103C、およびそれらを備えたDC−DCコンバータモジュール113A,113B,113Cの構成を示す断面図である。

【図5】図5(A)、図5(B)、図5(C)は第4の実施形態の三種のコイル内蔵基板104A,104B,104C、およびそれらを備えたDC−DCコンバータモジュール114A,114B,114Cの構成を示す断面図である。

【図6】図6(A)、図6(B)、図6(C)は第5の実施形態の三種のコイル内蔵基板105A,105B,105C、およびそれらを備えたDC−DCコンバータモジュール115A,115B,115Cの構成を示す断面図である。

【図7】図7(A)、図7(B)は第6の実施形態の二種のコイル内蔵基板106A,106B、およびそれらを備えたDC−DCコンバータモジュール116A,116Bの構成を示す断面図である。

【図8】図8(A)、図8(B)は第7の実施形態の二種のコイル内蔵基板107A,107B、およびそれらを備えたDC−DCコンバータモジュール117A,117Bの構成を示す断面図である。

【図9】図9は第8の実施形態のコイル内蔵基板108、およびそれらを備えたDC−DCコンバータモジュール118の構成を示す断面図である。

【発明を実施するための形態】

【0016】

《第1の実施形態》

図2は第1の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このDC−DCコンバータモジュール111は、コイル内蔵基板101と、このコイル内蔵基板101の上面に搭載された電子部品(11等)とで構成されている。通常、コイル内蔵基板101の上面には複数の電子部品が搭載されるが、図2ではそれらの電子部品のうち一つ(電子部品11)のみを図示している。

【0017】

コイル内蔵基板101は、コイル導体9と磁性体とが積層された第1の磁性体層21と、電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む第1表面層31と、実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む第2表面層32と、を備えている。

【0018】

第1の磁性体層21、第1表面層31および第2表面層32には面内配線導体6、層間接続導体8を必要に応じて備えている。

コイル導体9を含む層であるコイル導体形成層21Cと第1表面層31との間に第2の磁性体層22を備えている。

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2で表すと、A<B、μ1<μ2の関係にある。

【0019】

このように、コイル導体形成層21Cが電子部品搭載面側(第1主面側)に寄っている場合には、コイル導体形成層21Cと第1表面層31との間に第1の磁性体層21より透磁率の高い第2の磁性体層22を配置することにより、コイル導体形成層21Cと第1表面層31との間隔が狭いことによる磁界分布の不均一性が抑制される。具体的には、第2の磁性体層22はコイル導体9による磁束を層方向に導き、第1表面層31への(垂直方向への)磁束の拡がりが抑制される。そのため、第1表面層31に形成されている面内配線導体6、表面導体膜7および層間接続導体8等に渦電流が流れにくくなる。すなわち、第1表面層31に形成されている面内配線導体6、表面導体膜7および層間接続導体8等の影響を受けにくくなり、コイル導体9のインダクタとしての電気的特性の劣化が抑制される。

【0020】

これにより、より均一な磁界を発生するコイルが形成でき、直流抵抗が低く、Q値が高いコイル内蔵基板を構成できる。

【0021】

前記コイル内蔵基板101はグリーンシートプロセスにより製造される。前記第1の磁性体層21および第2の磁性体層22は、例えばFe-Ni-Zn-Cu系の酸化物を主成分とする磁性フェライトである。焼成前は、これらのセラミックグリーンシートの積層体である。また、前記第1表面層31および第2表面層32は、Fe-Zn-Cu系の酸化物を主成分とする非磁性フェライトである。焼成前はこのセラミックグリーンシートの積層体である。

【0022】

前記層間接続導体8は導電性ペーストの焼結体である。焼成前は所定のセラミックグリーンシートに形成された貫通孔に充填された導電性ペースト(未焼結の層間接続導体)である。また、コイル導体9、面内配線導体6、表面導体膜7、層間接続導体8は導電性ペーストの焼結体である。焼成前は所定のセラミックグリーンシート上に印刷された導電性ペーストである。これらの導電性ペーストに含まれる導電性金属は銀または銀/パラジウムを主成分としているものであることが好ましい。

【0023】

《第2の実施形態》

図3は第2の実施形態のコイル内蔵基板、およびそれを備えたDC−DCコンバータモジュールの構成を示す断面図である。このDC−DCコンバータモジュール112は、コイル内蔵基板102と、このコイル内蔵基板102の上面に搭載された電子部品(11等)とで構成されている。

【0024】

コイル内蔵基板102は、コイル導体9と磁性体とが積層された第1の磁性体層21と、電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む第1表面層31と、実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む第2表面層32と、を備えている。

コイル導体9を含む層であるコイル導体形成層21Cと第2表面層32との間に第3の磁性体層23を備えている。

【0025】

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第3の磁性体層23の透磁率をμ3で表すと、A<B、μ3<μ1の関係にある。

【0026】

このように、コイル導体形成層21Cが電子部品搭載面側(第1主面側)に寄っている場合には、コイル導体形成層21Cと第2表面層32との間に第1の磁性体層21より透磁率の低い第3の磁性体層23を配置することにより、コイル導体形成層21Cと第2表面層32との間隔が広いことによる磁界分布の不均一性が抑制される。具体的には、第3の磁性体層23はコイル導体9による磁束の透過が抑制され、コイル導体形成層21Cの上下にほぼ均等に磁界が集中する。そのため、第2表面層32に形成されている面内配線導体6、表面導体膜7および層間接続導体8等に渦電流が流れにくくなる。すなわち、第2表面層32に形成されている面内配線導体6、表面導体膜7および層間接続導体8等の影響を受けにくくなり、コイル導体9のインダクタとしての電気的特性の劣化が抑制される。

【0027】

また、透磁率の小さなフェライトは一般に誘電正接(tanδ)が相対的に小さいので、透磁率の小さな第3の磁性体層23を配置することにより、誘電体損失が低減されて、そのことによってもQ値を高めることができる。

【0028】

これにより、より均一な磁界を発生するインダクタが形成でき、直流抵抗が低く、Q値が高いコイル内蔵基板を構成できる。

【0029】

《第3の実施形態》

図4(A)、図4(B)、図4(C)は第3の実施形態の三種のコイル内蔵基板103A,103B,103C、およびそれらを備えたDC−DCコンバータモジュール113A,113B,113Cの構成を示す断面図である。これらのDC−DCコンバータモジュール113A,113B,113Cは、コイル内蔵基板103A,103B,103Cと、これらのコイル内蔵基板103A,103B,103Cの上面に搭載された電子部品(11等)とで構成されている。

【0030】

前記コイル内蔵基板103A,103B,103Cと第1の実施形態で図2に示したコイル内蔵基板101と異なるのは第2の磁性体層22の配置である。第1の実施形態ではコイル導体形成層21Cと第1表面層31との間に第2の磁性体層22を単に配置された例を示したが、図4(A)のコイル内蔵基板103Aでは、第2の磁性体層22が第1表面層31寄りの位置または第1表面層31に接する位置に配置されている。図4(B)のコイル内蔵基板103Bでは、第2の磁性体層22がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。さらに、図4(C)のコイル内蔵基板103Cでは、第2の磁性体層22をコイル導体形成層21Cと第1表面層31との間の全体にわたって第2の磁性体層22が配置されている。

【0031】

このように、第2の磁性体層22の厚みと位置を適宜定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0032】

《第4の実施形態》

図5(A)、図5(B)、図5(C)は第4の実施形態の三種のコイル内蔵基板104A,104B,104C、およびそれらを備えたDC−DCコンバータモジュール114A,114B,114Cの構成を示す断面図である。これらのDC−DCコンバータモジュール114A,114B,114Cは、コイル内蔵基板104A,104B,104Cと、これらのコイル内蔵基板104A,104B,104Cの上面に搭載された電子部品(11等)とで構成されている。

【0033】

前記コイル内蔵基板104A,104B,104Cと第2の実施形態で図3に示したコイル内蔵基板102と異なるのは第3の磁性体層23の配置である。第2の実施形態ではコイル導体形成層21Cと第2表面層32との間に第3の磁性体層23が単に配置された例を示したが、図5(A)のコイル内蔵基板104Aでは、第3の磁性体層23が第2表面層32寄りの位置または第2表面層32に接する位置に配置されている。図5(B)のコイル内蔵基板104Bでは、第3の磁性体層23がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。さらに、図5(C)のコイル内蔵基板104Cでは、第3の磁性体層23がコイル導体形成層21Cと第2表面層32との間の全体にわたって第3の磁性体層23が配置されている。

【0034】

このように、第3の磁性体層23の厚みと位置を適宜定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0035】

《第5の実施形態》

図6(A)、図6(B)、図6(C)は第5の実施形態の三種のコイル内蔵基板105A,105B,105C、およびそれらを備えたDC−DCコンバータモジュール115A,115B,115Cの構成を示す断面図である。これらのDC−DCコンバータモジュール115A,115B,115Cは、コイル内蔵基板105A,105B,105Cと、これらのコイル内蔵基板105A,105B,105Cの上面に搭載された電子部品(11等)とで構成されている。

【0036】

第5の実施形態のコイル内蔵基板105A,105B,105Cは、コイル導体形成層21Cと第1表面層31との間に第2の磁性体層22が配置されていて、コイル導体形成層21Cと第2表面層32との間に第3の磁性体層23が配置されている。

【0037】

図6(A)のコイル内蔵基板105Aでは、第2の磁性体層22が第1表面層31寄りの位置または第1表面層31に接する位置に配置されている。また第3の磁性体層23が第2表面層32寄りの位置または第2表面層32に接する位置に配置されている。

【0038】

図6(B)のコイル内蔵基板105Bでは、第2の磁性体層22がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。また第3の磁性体層23がコイル導体形成層21C寄りの位置またはコイル導体形成層21Cに接する位置に配置されている。

【0039】

図6(C)のコイル内蔵基板105Cでは、第2の磁性体層22がコイル導体形成層21Cと第1表面層31との間の全体にわたって配置されている。また第3の磁性体層23がコイル導体形成層21Cと第2表面層32との間の全体にわたって配置されている。

【0040】

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2、第3の磁性体層23の透磁率をμ3で表すと、A<B、μ3<μ1<μ2の関係にある。

【0041】

このように、コイル導体形成層21Cと第1表面層31との間に第2の磁性体層22、コイル導体形成層21Cと第2表面層32との間に第3の磁性体層23をそれぞれ設けることにより、コイル導体形成層21Cに近い導体(第1表面層31に形成されている面内配線導体6、表面導体膜7および層間接続導体8等)と遠い導体(第2表面層32に形成されている面内配線導体6、表面導体膜7および層間接続導体8等)の両方について渦電流損による悪影響をより効果的に抑制できる。

【0042】

また、第2の磁性体層22および第3の磁性体層23の厚みと位置を適宜定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0043】

《第6の実施形態》

図7(A)、図7(B)は第6の実施形態の二種のコイル内蔵基板106A,106B、およびそれらを備えたDC−DCコンバータモジュール116A,116Bの構成を示す断面図である。これらのDC−DCコンバータモジュール116A,116Bは、コイル内蔵基板106A,106Bと、これらのコイル内蔵基板106A,106Bの上面に搭載された電子部品(11等)とで構成されている。

【0044】

図7(A)の例では、コイル導体形成層21Cと第2の磁性体層22との間に第4の磁性体層24を備えている。図7(B)の例では、第1表面層31と第2の磁性体層22との間に第4の磁性体層24を備えている。図7(A)、図7(B)のいずれについても、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2、第4の磁性体層24の透磁率をμ4で表すと、A<B、μ1<μ2<μ4の関係にある。

【0045】

このように、コイル導体形成層21Cと第1表面層31との間に、互いに透磁率の異なる二層の磁性体層を配置し、それらの厚み、透磁率および位置関係を定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0046】

《第7の実施形態》

図8(A)、図8(B)は第7の実施形態の二種のコイル内蔵基板107A,107B、およびそれらを備えたDC−DCコンバータモジュール117A,117Bの構成を示す断面図である。これらのDC−DCコンバータモジュール117A,117Bは、コイル内蔵基板107A,107Bと、これらのコイル内蔵基板107A,107Bの上面に搭載された電子部品(11等)とで構成されている。

【0047】

図8(A)の例では、コイル導体形成層21Cと第3の磁性体層23との間に第5の磁性体層25を備えている。図8(B)の例では、第2表面層32と第3の磁性体層23との間に第5の磁性体層25を備えている。図8(A)、図8(B)のいずれについても、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第3の磁性体層23の透磁率をμ3、第5の磁性体層25の透磁率をμ5で表すと、A<B、μ5<μ3<μ1の関係にある。

【0048】

このように、コイル導体形成層21Cと第2表面層32との間に、互いに透磁率の異なる二層の磁性体層を配置し、それらの厚み、透磁率および位置関係を定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0049】

《第8の実施形態》

図9は第8の実施形態のコイル内蔵基板108、およびそれらを備えたDC−DCコンバータモジュール118の構成を示す断面図である。このDC−DCコンバータモジュール118は、コイル内蔵基板108と、このコイル内蔵基板108の上面に搭載された電子部品(11等)とで構成されている。

【0050】

図9の例では、コイル導体形成層21Cと第1表面層31との間に第2の磁性体層22が設けられ、この第2の磁性体層22と第1表面層31との間に第4の磁性体層24が設けられている。また、コイル導体形成層21Cと第2表面層32との間に第3の磁性体層23が設けられ、この第3の磁性体層23と第2表面層32との間に第5の磁性体層25が設けられている。

【0051】

ここで、コイル導体形成層21Cと第1表面層31との間隔をA、コイル導体形成層21Cと第2表面層32との間隔をB、第1の磁性体層21の透磁率をμ1、第2の磁性体層22の透磁率をμ2、第3の磁性体層23の透磁率をμ3、第4の磁性体層24の透磁率をμ4、第5の磁性体層25の透磁率をμ5で表すと、A<B、

μ5<μ3<μ1<μ2<μ4または、

μ3<μ5<μ1<μ2<μ4または、

μ5<μ3<μ1<μ4<μ2または、

μ3<μ5<μ1<μ4<μ2

の関係にある。

【0052】

このように、コイル導体形成層21Cと第1表面層31との間および第2表面層32との間に、互いに透磁率の異なる二層の磁性体層をそれぞれ配置し、それらの厚み、透磁率および位置関係を定めることによってコイル導体9による磁束がコントロールされて、磁界分布の均一性をより高めることができる。

【0053】

《他の実施形態》

以上に示した各実施形態では、電子部品搭載面を第1表面層31とし、実装面を第2表面層32側としたが、逆に、実装面が第1表面層31、電子部品搭載面が第2表面層32であってもよい。その場合でも、コイル導体形成層21Cと第1表面層との間隔をA、コイル導体形成層21Cと第2表面層との間隔をBで表したとき、A<Bの関係であれば、各実施形態で示した記述がそのまま当てはまる。

【符号の説明】

【0054】

6…面内配線導体

7…表面導体膜

8…層間接続導体

9…コイル導体

11…電子部品

21…第1の磁性体層

21C…コイル導体形成層

22…第2の磁性体層

23…第3の磁性体層

24…第4の磁性体層

25…第5の磁性体層

31…第1表面層

32…第2表面層

101,102,108…コイル内蔵基板

103A,103B,103C…コイル内蔵基板

104A,104B,104C…コイル内蔵基板

105A,105B,105C…コイル内蔵基板

106A,106B…コイル内蔵基板

107A,107B…コイル内蔵基板

111,112,118…DC−DCコンバータモジュール

113A,113B,113C…DC−DCコンバータモジュール

114A,114B,114C…DC−DCコンバータモジュール

115A,115B,115C…DC−DCコンバータモジュール

116A,116B…DC−DCコンバータモジュール

117A,117B…DC−DCコンバータモジュール

【特許請求の範囲】

【請求項1】

コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、

第2主面側に形成され、表面導体膜を含む第2表面層と、

を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に磁性体からなる第2の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2で表すと、A<B、μ1<μ2の関係であることを特徴とするコイル内蔵基板。

【請求項2】

コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、

第2主面側に形成され、表面導体膜を含む第2表面層と、

を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1の関係であることを特徴とするコイル内蔵基板。

【請求項3】

コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、

第2主面側に形成され、表面導体膜を含む第2表面層と、

を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に第2の磁性体層を備え、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1<μ2の関係であることを特徴とするコイル内蔵基板。

【請求項4】

前記コイル導体形成層と前記第2の磁性体層との間、または前記第1表面層と前記第2の磁性体層との間に第4の磁性体層を備え、

第4の磁性体層の透磁率をμ4で表すと、μ1<μ2<μ4の関係であることを特徴とする、請求項1または3に記載のコイル内蔵基板。

【請求項5】

前記コイル導体形成層と前記第3の磁性体層との間、または前記第2表面層と前記第3の磁性体層との間に第5の磁性体層を備え、

第5の磁性体層の透磁率をμ5で表すと、μ5<μ3<μ1の関係であることを特徴とする、請求項2または3に記載のコイル内蔵基板。

【請求項1】

コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、

第2主面側に形成され、表面導体膜を含む第2表面層と、

を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に磁性体からなる第2の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2で表すと、A<B、μ1<μ2の関係であることを特徴とするコイル内蔵基板。

【請求項2】

コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、

第2主面側に形成され、表面導体膜を含む第2表面層と、

を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1の関係であることを特徴とするコイル内蔵基板。

【請求項3】

コイル導体と磁性体とが積層された第1の磁性体層と、

第1主面側に形成され、表面導体膜を含む第1表面層と、

第2主面側に形成され、表面導体膜を含む第2表面層と、

を備えたコイル内蔵基板において、

前記コイル導体を含む層であるコイル導体形成層と前記第1表面層との間に第2の磁性体層を備え、

前記コイル導体を含む層であるコイル導体形成層と前記第2表面層との間に第3の磁性体層を備え、

前記コイル導体形成層と前記第1表面層との間隔をA、前記コイル導体形成層と前記第2表面層との間隔をB、第1の磁性体層の透磁率をμ1、第2の磁性体層の透磁率をμ2、第3の磁性体層の透磁率をμ3で表すと、A<B、μ3<μ1<μ2の関係であることを特徴とするコイル内蔵基板。

【請求項4】

前記コイル導体形成層と前記第2の磁性体層との間、または前記第1表面層と前記第2の磁性体層との間に第4の磁性体層を備え、

第4の磁性体層の透磁率をμ4で表すと、μ1<μ2<μ4の関係であることを特徴とする、請求項1または3に記載のコイル内蔵基板。

【請求項5】

前記コイル導体形成層と前記第3の磁性体層との間、または前記第2表面層と前記第3の磁性体層との間に第5の磁性体層を備え、

第5の磁性体層の透磁率をμ5で表すと、μ5<μ3<μ1の関係であることを特徴とする、請求項2または3に記載のコイル内蔵基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−138495(P2012−138495A)

【公開日】平成24年7月19日(2012.7.19)

【国際特許分類】

【出願番号】特願2010−290502(P2010−290502)

【出願日】平成22年12月27日(2010.12.27)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成24年7月19日(2012.7.19)

【国際特許分類】

【出願日】平成22年12月27日(2010.12.27)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]