コンタクト構造

【課題】液晶パネルなどにおいて、取り出し端子とFPCを接続するための異方性導電膜のコンタクトの信頼性を向上する。

【解決手段】アクティブマトリクス基板101上の接続配線183は端子部182において異方性導電膜195によって、FPC191に電気的に接続される。接続配線183はアクティブマトリクス基板101上のTFTのソース/ドレイン配線と同じ工程で作製され、金属膜と透明導電膜の積層膜でなる。異方性導電膜195との接続部分において、接続配線183の金属膜の側面は保護膜で覆われているためこの部分において、金属膜は透明導電膜、下地の絶縁膜109、保護膜に接して囲まれ外気に触れることがない。

【解決手段】アクティブマトリクス基板101上の接続配線183は端子部182において異方性導電膜195によって、FPC191に電気的に接続される。接続配線183はアクティブマトリクス基板101上のTFTのソース/ドレイン配線と同じ工程で作製され、金属膜と透明導電膜の積層膜でなる。異方性導電膜195との接続部分において、接続配線183の金属膜の側面は保護膜で覆われているためこの部分において、金属膜は透明導電膜、下地の絶縁膜109、保護膜に接して囲まれ外気に触れることがない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は絶縁表面を有する基板上に薄膜トランジスタ(以下、TFTと記す)

で構成された回路を有する半導体装置に関する。TFTで構成された回路を他の基板上の

回路と接続するための端子の構造に関する。特に本発明は、画素部とその周辺に設けられ

る駆動回路を同一基板上に設けた液晶表示装置やエレクトロルミネッセンス(EL)表示

装置や、これら表示装置を搭載した電気光学装置を搭載した電子機器に好適に利用できる

技術を提供する。尚、本明細書において半導体装置とは、半導体の特性を利用することで

機能する装置全般を指し、上記液晶表示装置だけでなく、表示装置を搭載した電子機器を

その範疇に含んでいる。

【背景技術】

【0002】

アクティブマトリクス型の液晶表示装置に代表される電気光学装置において、スイッチ

ング素子や能動回路を構成するためにTFTを用いる技術が開発されている。TFTはガ

ラスなどの基板上に気相成長法により半導体膜を形成し、その半導体膜を活性層として形

成する。半導体膜にはシリコン又はシリコン・ゲルマニウムなどシリコンを主成分とする

材料が好適に用いられている。さらに、シリコン半導体膜はその作製法により、非晶質シ

リコン膜や多結晶シリコンに代表される結晶質シリコン膜などを得ることができる。

【0003】

非晶質シリコン膜を活性層としたTFTは、非晶質構造などに起因する電子物性的要因

から、本質的に数cm2/Vsec以上の電界効果移動度を得ることができない。従って、アクテ

ィブマトリクス型の液晶表示装置において、画素部の各画素に設けられる液晶を駆動する

ためのスイッチング素子(画素TFT)として使用することはできても、画像表示を行う

ための駆動回路まで形成することは不可能であった。そのために、TAB(Tape Automat

ed Bonding)方式やCOG(Chip on Glass)方式を使ってドライバICなどを実装する

技術が用いられていた。

【0004】

一方、結晶質シリコン膜を活性層としたTFTでは、高い電界効果移動度が得られるこ

とから各種の機能回路を同一のガラス基板上に形成することが可能となり、画素TFTの

他に駆動回路においてnチャネル型TFTとpチャネル型TFTとから成るCMOS回路

を基本として形成されるシフトレジスタ回路、レベルシフタ回路、バッファ回路、サンプ

リング回路など同一基板上に作製することができる。低コスト化及び高品位化のため、ア

クティブマトリクス型液晶表示装置では、画素と画素を駆動するための駆動回路を同一基

板上に作製したアクティブマトリクス基板が用いられるようになった。

【0005】

上記のようなアクティブマトリクス基板では、駆動回路に電源や入力信号を供給するた

めに、アクティブマトリクス基板上に、駆動回路と接続した接続配線を作製し、接続配線

とFPC(Flexible Print Circuit)を実装する構造が採用されている。基板上の接続配線

とFPCの接続には異方性導電膜が用いられている。

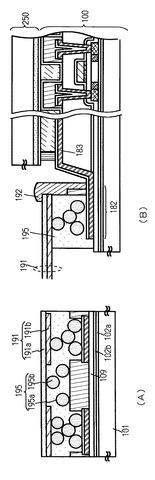

図30に異方性導電膜によってFPCに接続された接続配線の断面構造を示す。

【発明の概要】

【発明が解決しようとする課題】

【0006】

図30に示すように、アクティブマトリクス基板において、ガラス基板1の表面の絶縁

膜2上に接続配線3が形成されている。FPC4はポリイミドなどでなる可撓性の基板5

上に銅などからなる多数の配線6が形成されている。異方性導電膜7には、導電性スペー

サ8が、熱や光により硬化する接着剤9(樹脂)内に分散されている。接続配線3とFP

C4の上の配線6は導電性スペーサ8によって電気的に接続されている。

【0007】

接続配線3は、アルミニウムやチタンなどの金属膜3aとITO膜等の透明導電膜3b

の2多層構造となっている。透明導電膜3bとしてアルミニウムなどの金属膜を用いるこ

とで配線抵抗を低くできるが、金属膜3aが導電性スペーサ8に押されて変形するおそれ

がある。透明導電膜3bはインジウムやスズなどの金属の酸化物でなるため、金属膜3a

よりも硬度が高い。そこで、透明導電膜3bを表面に形成することで、金属膜3aの破損

や変形を防止している。

【0008】

しかしながら、金属膜3aの側面は異方性導電膜7が形成されるまでは剥き出しの状態

で、外気に曝されているため、腐食や酸化されやすい状態となっており、接続配線3とF

PC4との接続の信頼性を下げる原因となる。また、FPC4が実装された状態では、金

属膜3aの側面は樹脂と接しているため、水分に対する保護に問題がある。

【0009】

本発明は上述した問題点を解消して、FPCと配線の信頼性の高い接続を実現し、かつ

量産に適した接続配線を提供することを目的とする。

【課題を解決するための手段】

【0010】

上述の課題を課題を解決するために、本発明は基板上の接続配線を異方性導電膜によっ

て他の基板上の配線と電気的に接続するコンタクト構造であって、 前記引き出し配線は

金属膜と透明導電膜の積層膜でなり、前記異方性導電膜との接続部分において、前記金属

膜の側面は保護膜に覆われていることを特徴とする。

【0011】

また、他の構成は、基板上に、薄膜トランジスタが配置された回路と、前記薄膜トラン

ジスタでなる回路を他の回路と接続するための接続配線と、を有する半導体装置であって

、 前記接続配線金属膜と透明導電膜の積層膜でなり、前記他の回路との接続部分におい

て前記金属膜側面は保護膜に覆われていることを特徴とする。

【0012】

また、他の構成は薄膜トランジスタが配置された回路を有する第1の基板と、前記第1

の基板に対向する第2の基板とを有する半導体装置であって、 前記第1の基板上には、

前記薄膜トランジスタが配置された回路を他の回路と接続するための、金属膜と、該金属

膜表面に接する透明導電膜とでなる接続配線と、前記金属膜の側面に接する保護膜が形成

されていることを特徴とする。

【0013】

また、他の構成は薄膜トランジスタが配置された回路を有する第1の基板と、前記第1

の基板に対向する第2の基板とを有する半導体装置であって、 前記第1の基板上には、

前記薄膜トランジスタが配置された回路を他の回路と接続するための、金属膜と、該金属

膜表面に接する透明導電膜とでなる接続配線と、前記薄膜トランジスタ上に形成され、前

記第1の基板と前記第2の基板間隔を維持するための柱状スペーサと、前記金属膜の側面

に接する前記柱状スペーサと同じ材料でなる保護膜が形成されていることを特徴とする。

【発明の効果】

【0014】

本発明を用いることで、異方性導電膜によって他の回路と接続される接続配線において

、金属膜を保護膜及び透明導電膜で覆う構造となるため、製造過程や、異方性導電膜の接

着剤との接触によって生ずる金属膜の腐食、変質を防ぐことができるため、信頼性の高い

コンタクト構造とすることが可能になる。

【図面の簡単な説明】

【0015】

【図1】アクティブマトリクス基板の構成を説明する上面図。

【図2】液晶表示装置の回路構成を説明するブロック図。

【図3】アクティブマトリクス基板の作製工程を示す断面図。

【図4】アクティブマトリクス基板の作製工程を示す断面図。

【図5】アクティブマトリクス基板の作製工程を示す断面図。

【図6】アクティブマトリクス基板の作製工程を示す断面図。

【図7】アクティブマトリクス基板の作製工程を示す断面図。

【図8】液晶パネルの断面図。

【図9】接続配線の端子部の作製工程を示す断面図。

【図10】接続配線の端子部の作製工程を示す断面図。

【図11】接続配線の端子部の作製工程を示す断面図。

【図12】接続配線の端子部と異方性導電膜のコンタクト構造を示す断面図。

【図13】画素部の1画素の上面図。

【図14】柱状スペーサの形状を説明する図

【図15】接続配線の端子部の作製工程を示す断面図。

【図16】接続配線の端子部と異方性導電膜のコンタクト構造を示す断面図。

【図17】アクティブマトリクス基板の作製工程を示す断面図。

【図18】アクティブマトリクス基板の作製工程を示す断面図。

【図19】アクティブマトリクス基板の作製工程を示す断面図。

【図20】液晶パネルの断面図。

【図21】接続配線の端子部の作製工程を示す断面図。

【図22】半導体装置の一例を示す図。

【図23】半導体装置の一例を示す図。

【図24】投影型液晶表示装置の構成を示す図。

【図25】ICPエッチング装置のプラズマ生成機構を示す図。

【図26】マルチスパイラルコイル方式のICPエッチング装置を示す図。

【図27】テーパー角θのバイアスパワー依存性を示す図。

【図28】テーパー角θのCF4の流量比依存性を示す図。

【図29】テーパー角θの(W/レジスト)選択比依存性を示す図。

【図30】従来のアクティブマトリクス基板の端子部と異方性導電膜のコンタクト構造を示す図。

【発明を実施するための形態】

【0016】

[実施形態1]

本発明のコンタクト構造は、異方性導電膜によって回路を接続する実装方法を用いる半

導体装置、例えば、アクティブマトリクス型液晶表示装置や、EL表示装置に好適である

。本実施形態では、図12を用いて、本発明をアクティブマトリクス型の液晶表示装置に

適用した場合のコンタクト構造を説明する。

【0017】

アクティブマトリクス基板上の接続配線183は端子部182において異方性導電膜1

95によって、FPC191に電気的に接続される。接続配線183はアクティブマトリ

クス基板上のTFTのソース/ドレイン配線と同じ工程で作製される。即ち、ソース/ド

レイン配線と同じ材料で、同じ層に形成されている。

金属膜140と透明導電膜141の積層膜でなる。異方性導電膜195との接続部分にお

いて、接続配線183の側面は絶縁材料でなる保護膜173に覆われている。

【0018】

この構造により、接続配線183の金属膜140の側面は保護膜174で覆われる。従

って、接続部分において、金属膜140は透明導電膜141、絶縁膜109、保護膜17

4に接して囲まれ、外気に触れることがない。よって金属膜140の腐食を防止すること

ができる。

【0019】

保護膜174はソース/ドレイン配線の上層に形成される絶縁膜を用いて作製すること

ができる。本実施形態では、保護膜174はアクティブマトリクス基板と対向基板の間隔

を保持するために作製された柱状スペーサ172と同じ工程で作製されている。

【0020】

また、図16に示すように接続配線304をTFTのゲート配線配線と同じ工程で作製

することもできる。この場合には、接続配線304はゲート配線と同じ材料で同じ層に形

成されることになる。また、この場合には、保護膜303はゲート配線とソース/ドレイ

ン配線の間に形成された絶縁膜138、139で作製される。

【0021】

本発明において、接続配線は金属膜の表面を透明導電膜で覆った積層膜で形成される。

金属膜は単層膜に限定されない。金属膜の厚さは100nm〜1μmとする。金属膜として

は、アルミニウム(Al)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、

タングステン(W)から選ばれた元素を主成分とする金属膜や、金属元素を含む合金膜を

少なくとも1層含むが、これら金属層、合金層の単層膜または多層膜であってももちろん

よい。合金としては、Mo−W合金、Mo−Ta合金や、列記した元素と窒素の化合物で

ある窒化タンタル(TaN)、窒化タングステン(WN)、窒化チタン(TiN)膜、窒

化モリブデン(MoN)が挙げられる。またタングステンシリサイド、チタンシリサイド

、モリブデンシリサイドなどシリサイドを用いることもできる。

【0022】

透明導電膜の厚さは50nm〜0.5μmとする。透明導電膜の材料は、酸化インジウム

(In2O3)や酸化インジウム酸化スズ合金(In2O3―SnO2;ITO)などをスパ

ッタ法や真空蒸着法などを用いて形成して用いることができる。このような材料のエッチ

ング処理は塩酸系の溶液により行う。しかし、特にITOのエッチングは残渣が発生しや

すいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金(In2O3―

ZnO)を用いても良い。酸化インジウム酸化亜鉛合金は表面平滑性に優れ、ITOに対

して熱安定性にも優れているので、ドレイン配線169の端面で接触するAlとの腐蝕反

応を防止できる。

同様に、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高め

るためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)などを用いることができ

る。

【0023】

[実施形態2]

また、ゲート配線と同じ工程で接続配線を作製した場合、ゲート配線、接続配線の断面

形状をテーパー形状としてもよい。ゲート配線をテーパ状にすることにより、膜厚が中央

から側面に向かって減少することとなるので、後述する実施例で示すように、ゲート配線

をマスクにした半導体膜のドーピングにおいて、膜厚の変化を利用して半導体膜に添加さ

れる不純物濃度を変化させることができる。

【0024】

テーパ形状にするためには、高密度プラズマを用いたドライエッチング法を適用する。

高密度プラズマを得る手法にはマイクロ波や誘導結合プラズマ(Inductively Coupled Pl

asma:ICP)を用いたエッチング装置が適している。特に、ICPエッチング装置はプ

ラズマの制御が容易であり、処理基板の大面積化にも対応できる。

【0025】

ICPを用いたプラズマ処理装置では、プラズマ処理を高精度に行うための手段として

、高周波電力をインピーダンス整合器を介して4本の渦巻き状コイル部分が並列に接続さ

れてなるマルチスパイラルコイルに印加してプラズマを形成する方法を用いている。ここ

で、各コイル部分の1本当たりの長さは、高周波の波長の1/4倍としている。さらに、

被処理物を保持する下部電極にも、別途高周波電力を印加してバイアス電圧を付加する構

成としている。ICPを用いたプラズマ処理方法やプラズマ処理装置に関しては特開平9

−293600号公報等で開示されている。

【0026】

このようなICPを用いたプラズマ処理装置(例えば、エッチング装置)の構造概略図

を図25に示す。チャンバー上部の石英板11上にアンテナコイル12を配置し、マッチ

ングボックス13を介してRF電源14に接続されている。また、アンテナコイルに対向

して下部電極15が設けられ、下部電極15にプラズマ処理する基板10が配置される。

また下部電極15にもマッチングボックス16を介してRF電源17が接続されており、

基板上方のアンテナコイル12にRF電流が印加されると、アンテナコイル12にRF電

流Jがα方向に流れ、式1に従ってZ方向に磁界Bが発生する。

【0027】

s μ0 J=rotB(μ0 は透磁率) (式1)

【0028】

そして、ファラデーの電磁誘導の法則に従い、θ方向に誘導電界Eが生じる(式2)。

【0029】

−∂B/∂t=rotE (式2)

【0030】

誘導電界Eで電子がα方向に加速されてガス分子と衝突し、プラズマが生成される。誘

導電界の方向がα方向なので、荷電粒子がエッチングチャンバー壁や、基板に衝突して電

荷を消失する確率が低くなる。従って、1Pa程度の低圧力でも高密度のプラズマを発生

させることができる。また、下流へは、磁界Bがほとんどないので、シート状に広がった

高密度プラズマ領域となる。

ICPで高密度プラズマを得る為にはアンテナコイルに流れる高周波電流Jを低損失で

流す必要があり、そのインダクタンスを低下させなければならない。そのために、アンテ

ナコイルを分割した方式とすることが有効となる。

【0031】

アンテナコイル12(ICPパワーが印加される)と基板側の下部電極15(バイアス

パワーが印加される)のそれぞれに印加するRFパワーを調節することによってプラズマ

密度と自己バイアス電圧を独立に制御することが可能である。

また、被エッチング膜に応じて異なる周波数のRFパワーを印加できる。

【0032】

ICPエッチング装置で高密度プラズマを得るためには、アンテナコイル12に流れる

RF電流Jを低損失で流す必要があり、大面積化するためには、アンテナコイル12のイ

ンダクタンスを低下させなければならない。そのために図26に示したようにアンテナを

分割したマルチスパイラルコイル22のICPエッチング装置が開発された。図26中の

21は石英板、23、26はマッチングボックス、24、27はRF電源である。また、

チャンバーの底部には、基板28を保持する下部電極25が絶縁体29を介して設けられ

ている。

【0033】

このようなマルチスパイラルコイルを適用したICPを用いたエッチング装置を用いる

と、前記耐熱性導電性材料のエッチングを良好に行うことができまた所望のテーパー角θ

を有する配線を形成することができる。

【0034】

所望のテーパー角θを得るには、ICPエッチング装置のバイアスパワー密度を調節す

る。図27は、テーパー角θのバイアスパワー依存性を示した図である。図27に示した

ように、バイアスパワー密度に応じてテーパー角θを制御することができる。図27は、

ガラス基板上に所定のパターンに形成されたW(タングステン)膜について、そのパター

ン端部のテーパー形状(テーパー角)について調べた結果を示す。図27はテーパー角の

基板側にかけるバイアス電力(13.56MHz)依存性を示す。共通条件として放電電力

(コイルに印加する高周波電力、13.56MHz)を3.2W/cm2、圧力1.0Paとして

エッチングガスにCF4とCl2を用いた。エッチングガスの流量はCF4、Cl2共に30

SCCMとした。

【0035】

図27に示すようにテーパー角はバイアス電力が128〜384mW/cm2の範囲で70〜

20°まで変化させることが可能であることが明らかとなった。なお、CF4、Cl2の流

量は共に30SCCMとした。

【0036】

また、図28の実験からはテーパー角は60〜80°まで変化させることが可能であ流

ことが分かる。なお、図28の実験条件では、テーパー角のエッチングガス流量比依存性

について調べた結果を示す。なお、CF4とCl2の合計の流量を60SCCMとして、CF4

のみを20〜40SCCMの範囲で変化させた。このときバイアス電力は128mW/cm2とした

。

【0037】

更にテーパー角θはタングステンとレジストのエッチングの選択比に依存していると考

えられる。図29にタングステンとレジストの選択比とテーパー角θとの依存性を示した

。このようにICPエッチング装置を用いて、バイアスパワー密度や反応ガス流量比を適

宜決定することで、極めて容易に所望のテーパー角θが3°〜60°の配線を形成するこ

とが可能である。

【0038】

また、耐熱性導電性材料のICPエッチング装置における加工特性を考える。

ここでは、W(タングステン)膜とTa(タンタル)膜の他に、ゲート電極用の材料とし

てしばしば用いられるモリブデンータングステン(Mo−W)合金(組成比はMo:W=

48:50wt%)について、エッチング速度、適用するエッチングガス、およびゲート電

極の下地となるゲート絶縁膜との選択比の代表的な値を示す。ゲート絶縁膜はプラズマC

VD法で作製する酸化シリコン膜または酸化窒化シリコン膜であり、ここで選択比はゲー

ト絶縁膜のエッチング速度に対するそれぞれの材料のエッチング速度の割合として定義す

る。

【0039】

【表1】

【0040】

Ta膜はエッチング速度が140〜160nm/minであり、ゲート絶縁膜とのエッチング

の選択比が6〜8である。この値はW膜のエッチング速度が70〜90nm/minの範囲でゲ

ート絶縁膜との選択比が2〜4というよりも優れた値となっている。従って、被加工性と

いう観点からはTa膜も適しているが、表中に示さない値として、Ta膜は抵抗率が20

〜30μΩcmであり、W膜の10〜16μΩcmに比べて若干高い点が難点となる。

一方、Mo−W合金はエッチング速度が40〜60nm/minと遅く、またゲート絶縁膜に

対するエッチングの選択比は0.1〜2となり、この材料は被加工性という観点から必ず

しも適していないことが覗われる。このように、表1からはTa膜が最も良い結果を示し

ていることがわかるが、前述のように抵抗率を考慮するとW膜が総合的には適していると

考えられる。

【0041】

また、ドライエッチングに用いるエッチングガスとしてフッ素を含むガスと、塩素を含

むガスの混合ガスを用いることができる。フッ素を含むガスとしてはCF4、C2F6、ま

たはC4F8から選ばれたガスを用いることができる。また塩素を含むガスとしてはCl2

Cl2、SiCl4ガス、BCl4から選ばれたガスを用いることができる。

【実施例1】

【0042】

本実施例は、アクティブマトリクス型液晶パネルに関するものである。図1(A)は本

実施例のアクティブマトリクス基板の上面図であり、画素部、画素部の薄膜トランジスタ

を駆動するための駆動回路部とが形成されている。アクティブマトリクス基板上に作製さ

れた柱状スペーサおよびシール剤の位置関係を示す上面図である。

【0043】

図1(A)に示すように、ガラス基板101上には、薄膜トランジスタが配置された画

素部188と、画素部188に配置された薄膜トランジスタを駆動するための駆動回路と

して、走査信号駆動回路185と映像信号制御回路184が設けられている。さらに、そ

の他CPUやメモリなどの信号処理回路187が設けられている。

【0044】

画素部188では走査信号駆動回路185から延在するゲート配線189と映像信号制

御回路184から延在するソース配線190がマトリクス状に交差して画素を形成し、各

画素にはそれぞれ画素TFT204と保持容量205が設けられている。

【0045】

柱状スペーサ172はアクティブマトリクス基板と、対向基板の間隔を保持するもので

あって、樹脂でなる円柱状の構造物である。画素部188において設けられる柱状スペー

サ172は、すべての画素に対して設けても良いが、マトリクス状に配列した画素の数個

から数十個おきに設けても良い。即ち、画素部を構成する画素の全数に対するスペーサの

数の割合は20〜100%とすると良い。また、各回路184、185、187には柱状

スペーサ172の代わりに、樹脂を回路全面を覆うように設けても良い。本実施例では、

TFTのソースおよびドレイン配線の位置にあわせて、円柱状のスペーサを設けている。

【0046】

シール剤186は、基板101上の画素部188および走査信号制御回路185、映像

信号制御回路184、その他の信号処理回路187の外側であって、外部入出力端子18

2よりも内側に形成されている。

【0047】

また、アクティブマトリクス基板100上の回路184、185、187は接続配線1

83によって、外部の電源や回路に電気的に接続されている。また接続配線183は回路

184、185、187のTFTのソース(ドレイン)配線と同時に形成されている。端

子部182は接続配線183と一体的に形成され、他の基板上の配線との接続部になる。

図1(B)に端子部182の部分拡大図を示す。

【0048】

図1(B)に示すように、端子部182の側面は保護膜174によって覆われており、

接続配線183は端子部182において、異方性導電膜によってFPC191の配線19

1bと電気的に接続されている。191aはFPC191が設けられている基板を指す。

【0049】

図2はアクティブマトリクス基板100の回路のブロック図である。映像信号制御回路

184は、シフトレジスタ回路501a、レベルシフタ回路502a、バッファ回路50

3a、サンプリング回路504を備えている。また、走査信号駆動回路185は、シフト

レジスタ回路501b、レベルシフタ回路502b、バッファ回路503bを備えている

。

【0050】

シフトレジスタ回路501a、501bは駆動電圧が5〜16V(代表的には10V)

であり、この回路を形成するCMOS回路はTFTは、図6に示すの第1のpチャネル型

TFT200と第1のnチャネル型TFT201で形成する。

また、レベルシフタ回路502a、502bやバッファ回路503a、503bは駆動電

圧が14〜16Vと高くなるがシフトレジスタ回路と同様なTFTを用いれば良い。また

、これらの回路において、ゲートをマルチゲート構造で形成すると耐圧が高まり、回路の

信頼性を向上させる上で有効である。

【0051】

サンプリング回路504はアナログスイッチから成り、駆動電圧が14〜16Vである

が、極性が交互に反転して駆動される上、オフ電流値を低減させる必要があるため、図6

で示す第2のpチャネル型TFT202と第2のnチャネル型TFT203で形成するこ

とが望ましい。この回路において、pチャネル型TFT202のオフ電流値が問題となる

ときは、実施例2で示す工程で作製した、オフセット領域を設けたシングルドレイン構造

のTFTで作製すると良い。

【0052】

また、画素部は駆動電圧が14〜16Vであり、低消費電力化の観点からサンプリング

回路よりもさらにオフ電流値を低減することが要求され、図6で示す画素TFT204の

ようにマルチゲート構造とし、さらにLDD領域を設けた構造とするのが望ましい。

【0053】

なお、画素部188と駆動回路185、186のブロック構成のみを示したが、後述す

るTFTの工程に従えば、その他にも信号分割回路、分周波回路、D/Aコンバータ、γ

補正回路、オペアンプ回路、さらにメモリ回路や演算処理回路などの信号処理回路187

、さらに論理回路を同一基板上に形成することが可能である。このように、本発明は同一

基板上に画素部とその駆動回路とを含む半導体装置、例えば信号制御回路および画素部を

具備した液晶表示装置を実現することができる。

【0054】

以下、アクティブマトリクス基板の作製工程を説明する。図3〜図7は画素部188、

駆動回路の作製工程を示す断面図であり、図9〜図11は接続配線183の端子部182

の作製工程を示す図である。これら図面において同じ符号は同じ構成要素を示している。

【0055】

基板101にはコーニング社の#7059ガラスや#1737ガラスなどに代表される

バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板の他に、ポリエ

チレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテル

サルフォン(PES)など光学的異方性を有しないプラスチック基板を用いることができ

る。ガラス基板を用いる場合には、ガラス歪み点よりも10〜20℃程度低い温度であら

かじめ熱処理しておいても良い。そして、基板101のTFTを形成する表面に、基板1

01からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シ

リコン膜などの下地膜102を形成する。例えば、プラズマCVD法でSiH4、NH3、

N2Oから作製される酸化窒化シリコン膜102aを10〜200nm(好ましくは50〜

100nm)、同様にSiH4、N2Oから作製される酸化窒化水素化シリコン膜102bを

50〜200nm(好ましくは100〜150nm)の厚さに積層形成する(図3(A))

。

【0056】

酸化窒化シリコン膜は従来の平行平板型のプラズマCVD法を用いて形成する。酸化窒

化シリコン膜102aは、SiH4を10SCCM、NH3を100SCCM、N2Oを20SCCMと

して反応室に導入し、基板温度325℃、反応圧力40Pa、放電電力密度0.41W/cm2

、放電周波数60MHzとした。一方、酸化窒化水素化シリコン膜102bは、SiH4を5

SCCM、N2Oを120SCCM、H2を125SCCMとして反応室に導入し、基板温度400℃、

反応圧力20Pa、放電電力密度0.41W/cm2、放電周波数60MHzとした。これらの膜は

、基板温度を変化させ、反応ガスの切替えのみで連続して形成することもできる。

【0057】

このようにして作製した酸化窒化シリコン膜102aは、密度が9.28×1022/cm3

であり、フッ化水素アンモニウム(NH4HF2)を7.13%とフッ化アンモニウム(N

H4F)を15.4%含む混合溶液(ステラケミファ社製、商品名LAL500)の20

℃におけるエッチング速度が約63nm/minと遅く、緻密で硬い膜である。このような膜を

下地膜に用いると、この上に形成する半導体膜にガラス基板からのアルカリ金属元素が拡

散するのを防ぐのに有効である。

【0058】

次に、25〜80nm(好ましくは30〜60nm)の厚さで非晶質構造を有する半導

体膜103aを、プラズマCVD法やスパッタ法などの公知の方法で形成する。例えば、

プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成する。非晶質構造を有する

半導体膜には、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜

などの非晶質構造を有する化合物半導体膜を適用しても良い。また、下地膜102と非晶

質半導体膜103aとは両者を連続形成することも可能である。例えば、前述のように酸

化窒化シリコン膜102aと酸化窒化水素化シリコン膜102bをプラズマCVD法で連

続して成膜後、反応ガスをSiH4、N2O、H2からSiH4とH2或いはSiH4のみに切

り替えれば、一旦大気雰囲気に晒すことなく連続形成できる。その結果、酸化窒化水素化

シリコン膜102bの表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツ

キやしきい値電圧の変動を低減させることができる。

【0059】

そして、結晶化の工程を行い非晶質半導体膜103aから結晶質半導体膜103bを作

製する。その方法としてレーザーアニール法や熱アニール法(固相成長法)、またはラピ

ットサーマルアニール法(RTA法)を適用することができる。前述のようなガラス基板

や耐熱性の劣るプラスチック基板を用いる場合には、特にレーザーアニール法を適用する

ことが好ましい。RTA法では、赤外線ランプ、ハロゲンランプ、メタルハライドランプ

、キセノンランプなどを光源に用いる。或いは特開平7−130652号公報で開示され

た技術に従って、触媒元素を用いる結晶化法で結晶質半導体膜103bを形成することも

できる。結晶化の工程ではまず、非晶質半導体膜が含有する水素を放出させておくことが

好ましく、400〜500℃で1時間程度の熱処理を行い含有する水素量を5atom%以下

にしてから結晶化させると膜表面の荒れを防ぐことができるので良い。

【0060】

結晶化をレーザーアニール法にて行う場合には、パルス発振型または連続発光型のエキ

シマレーザーやアルゴンレーザーをその光源とする。パルス発振型のエキシマレーザーを

用いる場合には、レーザー光を線状に加工してレーザーアニールを行う。レーザーアニー

ル条件は実施者が適宣選択するものであるが、例えば、レーザーパルス発振周波数30H

zとし、レーザーエネルギー密度を100〜500mJ/cm2(代表的には300〜400mJ/

cm2)とする。そして線状ビームを基板全面に渡って照射し、この時の線状ビームの重ね合

わせ率(オーバーラップ率)を80〜98%として行う。このようにして図3(B)に示

すように結晶質半導体膜103bを得ることができる。

【0061】

そして、結晶質半導体膜103b上にフォトリソグラフィーの技術によって、フォトマ

スクPM1を用いてレジストパターンを形成し、ドライエッチングによって結晶質半導体

膜を島状に分割し、島状半導体膜104〜108を形成しする。ドライエッチングにはC

F4とO2の混合ガスを用いる。

【0062】

島状半導体膜に対し、TFTのしきい値電圧(Vth)を制御する目的でp型を付与する

不純物元素を1×1016〜5×1017atoms/cm3程度の濃度で島状半導体膜の全面に添加

しても良い。半導体に対してp型を付与する不純物元素には、ホウ素(B)、アルミニウ

ム(Al)、ガリウム(Ga)など周期律表第13族の元素が知られている。その方法と

して、イオン注入法やイオンドープ法を用いることができるが、大面積基板を処理するに

はイオンドープ法が適している。イオンドープ法ではジボラン(B2H6)をソースガスと

して用いホウ素(B)を添加する。このような不純物元素の注入は必ずしも必要でなく省

略しても差し支えないが、特にnチャネル型TFTのしきい値電圧を所定の範囲内に収め

るために好適に用いる手法である。

【0063】

ゲート絶縁膜109はプラズマCVD法またはスパッタ法を用い、膜厚を40〜150

nmとしてシリコンを含む絶縁膜で形成する。例えば、120nmの厚さで酸化窒化シリ

コン膜から形成すると良い。また、SiH4とN2OにO2を添加させて作製された酸化窒

化シリコン膜は、膜中の固定電荷密度が低減されているのでこの用途に対して好ましい材

料となる。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく

、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い(図3(C))。

【0064】

図3(D)に示すように、ゲート絶縁膜109上にゲート配線を形成するための導電膜

を形成する。導電膜は単層で形成しても良いが、必要に応じて二層あるいは三層といった

複数の層から成る積層構造としても良い。例えば、2層の場合には、上層に、タンタル(

Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)等の元素を主成分と

する金属膜やこれら元素の合金膜(代表的にはMo−W合金膜、Mo−Ta合金膜)で形

成し、下層は窒化タンタル(TaN)、窒化タングステン(WN)、窒化チタン(TiN

)膜、窒化モリブデン(MoN)などで形成する。例えば、2層の場合、上層に下層の導

電膜の窒化物で形成すればよく、下層/上層としてWN膜/W膜や、TaN膜/Ta膜膜

等とすればよい。また、3層の場合は、TaN膜/Ta膜/TaN膜とすればよい。2層

目の(上層の)導電膜は抵抗率を10〜50μΩcmの範囲ですることが好ましい。低抵抗

化を図るために含有する不純物濃度を低減させることが好ましく、特に酸素濃度に関して

は30ppm以下とすると良かった。例えば、タングステン(W)は酸素濃度を30pp

m以下とすることで20μΩcm以下の比抵抗値を実現することができた。

【0065】

また、配線抵抗の低抵抗化には、アルミニウムを主成分とする膜を用いるのが好ましい

。この場合、アルミニウムにSiやSc等を微量添加して耐熱性を高めるとよい。例えば

、ゲート配線を構成する導電膜として、Ti膜/Scを添加したAl膜や、Ti膜/Ti

N膜/Scを添加したAl膜を形成すればよい。

【0066】

W膜を成膜する場合には、Wをターゲットとしたスパッタ法で、アルゴン(Ar)ガス

と窒素(N2)ガスを導入して導電膜111を窒化タングステン(WN)で50nmの厚さ

に形成し、導電膜110をWで250nmの厚さに形成する。その他の方法として、W膜は

6フッ化タングステン(WF6)を用いて熱CVD法で形成することもできる。いずれに

してもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は2

0μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図

ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵

抗化する。このことより、スパッタ法による場合、純度99.9999%のWターゲット

を用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成

することにより、抵抗率9〜20μΩcmを実現することができる。

【0067】

TaN膜、Ta膜は同様にスパッタ法で形成することが可能である。TaN膜はTaを

ターゲットとしてスパッタガスにArと窒素との混合ガスを用いて形成し、Ta膜はスパ

ッタガスにArを用いる。また、これらのスパッタガス中に適量のXeやKrを加えてお

くと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。α相のTa膜

の抵抗率は20μΩcm程度でありゲート電極に使用することができるが、β相のTa膜の

抵抗率は180μΩcm程度でありゲート電極とするには不向きであった。TaN膜はα相

に近い結晶構造を持つので、この上にTa膜を形成すればα相のTa膜が容易に得られた

。本実施例では、ゲート配線を構成する導電膜として、下層の導電膜110としてTaN

膜を上層の導電膜111としてTa膜を成膜する。

【0068】

またゲート配線を構成する導電膜とゲート絶縁膜109の間に2〜20nm程度の厚さ

でリン(P)をドープしたシリコン膜を形成しておくことは有効である。これにより、そ

の上に形成される導電膜の密着性向上と酸化防止を図ると同時に、導電膜が微量に含有す

るアルカリ金属元素がゲート絶縁膜109に拡散するのを防ぐことができる。

【0069】

次に、フォトリソグラフィーの技術によって、フォトマスクPM2を用いてレジストマ

スクRM1 〜RM6 を形成し、導電膜110と導電膜111とを一括でエッチングしてゲート

配線118〜122と容量配線123を形成する。ゲート配線118〜122と容量配線

123は導電膜から成る118a〜122aと、導電膜から成る118b〜122bとが

一体として形成されている(図4(A))。

【0070】

そして、nチャネル型TFTにLDD領域を形成するために、n型を付与する不純物元

素添加の工程(n-ドープ工程)を行った。ここではゲート配線118〜122をマスク

として自己整合的にn型を付与する不純物元素をイオンドープ法で添加した。n型を付与

する不純物元素として添加するリン(P)を1×1016〜5×1019atoms/cm3の濃度範

囲で添加する。このようにして、図4(B)

に示すように島状半導体膜に低濃度n型不純物領域124〜129を形成する。

【0071】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する高

濃度n型不純物領域の形成を行った(n+ドープ工程)。まず、フォトマスクPM3を用

い、レジストのマスクRM8 〜RM12を形成し、n型を付与する不純物元素を添加して高濃度

n型不純物領域130〜135を形成した。n型を付与する不純物元素にはリン(P)を

用い、その濃度が1×1020〜1×1021atoms/cm3の濃度範囲となるようにフォスフィ

ン(PH3)を用いたイオンドープ法で行った(図4(C))。

【0072】

そして、pチャネル型TFTを形成する島状半導体膜104、106にソース領域およ

びドレイン領域とする高濃度p型不純物領域136、137を形成する。ここでは、ゲー

ト配線118、120をマスクとしてp型を付与する不純物元素を添加し、自己整合的に

高濃度p型不純物領域を形成する。

【0073】

この工程では、nチャネル型TFTを形成する島状半導体膜105、107、108は

、フォトマスクPM4を用いてレジストマスクRM13〜RM15を形成し全面を被覆しておく。

高濃度p型不純物領域136、137はジボラン(B2H6)を用いたイオンドープ法で形

成する。この領域のボロン(B)濃度は3×1020〜3×1021atoms/cm3となるように

する(図4(D))。

【0074】

高濃度p型不純物領域136、137には、前工程においてリン(P)が添加されてい

て、高濃度p型不純物領域136a、137aには1×1020〜1×1021atoms/cm3の

濃度で、高濃度p型不純物領域136b、137bには1×1016〜5×1019atoms/c

m3の濃度で含有しているが、この工程で添加するボロン(B)の濃度を1.5から3倍と

なるようにすることにより、pチャネル型TFTのソース領域およびドレイン領域として

機能する上で何ら問題はなかった。

【0075】

その後、図5(A)に示すように、ゲート配線およびゲート絶縁膜109上から保護絶

縁膜138を形成する。保護絶縁膜138は酸化シリコン膜、酸化窒化シリコン膜、窒化

シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。いずれにしても保護

絶縁膜138は無機絶縁物材料から形成する。保護絶縁膜138の膜厚は100〜200

nmとする。ここで、酸化シリコン膜を用いる場合には、プラズマCVD法で、オルトケ

イ酸テトラエチル(Tetraethyl Orthosilicate:TEOS)とO2 とを混合し、反応圧力

40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0

.8W/cm2で放電させて形成することができる。

【0076】

酸化窒化シリコン膜を用いる場合には、プラズマCVD法でSiH4、N2 O、NH3

から作製される酸化窒化シリコン膜、またはSiH4、N2 Oから作製される酸化窒化シ

リコン膜で形成すれば良い。この場合の作製条件は反応圧力20〜200Pa、基板温度3

00〜400℃とし、高周波(60MHz)電力密度0.1〜1.0W/cm2で形成することが

できる。また、SiH4 、N2 O、H2から作製される酸化窒化水素化シリコン膜を適用

しても良い。窒化シリコン膜も同様にプラズマCVD法でSiH4、NH3から作製するこ

とが可能である。

【0077】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化す

る工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に

、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用すること

ができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒

素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施

例では550℃で4時間の熱処理を行った。また、基板101に耐熱温度が低いプラスチ

ック基板を用いる場合にはレーザーアニール法を適用することが好ましい(図5(B))

。

【0078】

活性化の工程の後、さらに、3〜100%の水素を含む雰囲気中で、300〜450℃

で1〜12時間の熱処理を行い、島状半導体膜を水素化する工程を行った。この工程は熱

的に励起された水素により島状半導体膜にある1016〜1018/cm3のダングリングボンド

を終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起

された水素を用いる)を行っても良い。

【0079】

活性化および水素化の工程が終了したら、有機絶縁物材料からなる層間絶縁膜139を

1.0〜2.0μmの平均厚を有して形成する。有機樹脂材料としては、ポリイミド、ア

クリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用するこ

とができる。例えば、基板に塗布後、熱重合するタイプのポリイミドを用いる場合には、

クリーンオーブンで300℃で焼成して形成する。また、アクリルを用いる場合には、2

液性のものを用い、主材と硬化剤を混合した後、スピナーを用いて基板全面に塗布した後

、ホットプレートで80℃で60秒の予備加熱を行い、さらにクリーンオーブンで250

℃で60分焼成して形成することができる。(図5(C))

【0080】

このように、層間絶縁膜139を有機絶縁物材料で形成することにより、表面を良好に

平坦化させることができる。また、有機樹脂材料は一般に誘電率が低いので、寄生容量を

低減するできる。しかし、吸湿性があり保護膜としては適さないので、本実施例のように

、保護絶縁膜138として形成した酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン

膜などと組み合わせて用いる必要がある。

【0081】

その後、フォトマスクPM5を用い、所定のパターンのレジストマスクを形成し、それ

ぞれの島状半導体膜に形成されたソース領域またはドレイン領域に達するコンタクトホー

ルを絶縁膜138、139に形成する。更に、端子部182の絶縁膜138、139を除

去する。コンタクトホールの形成はドライエッチング法により行う。この場合、エッチン

グガスにCF4、O2、Heの混合ガスを用い有機樹脂材料から成る層間絶縁膜139をま

ずエッチングし、その後、続いてエッチングガスをCF4、O2として保護絶縁膜138を

エッチングする。さらに、島状半導体膜との選択比を高めるために、エッチングガスをC

HF3に切り替えてゲート絶縁膜をエッチングすることにより、良好にコンタクトホール

を形成することができる。

【0082】

そして、ソース/ドレイン配線及び接続配線183を形成する金属膜140と透明導電

膜141の積層膜を形成する。ここでは、金属膜140としてTi膜を50〜150nmの

厚さで形成し、島状半導体膜のソースまたはドレイン領域を形成する半導体膜とコンタク

トを形成し、そのTi膜上に重ねてアルミニウム(Al)を300〜400nmの厚さでス

パッタ法で形成する。また、金属膜140として、Ti膜/TiN膜/Al膜でなる積層

膜を成膜してもよい。

【0083】

透明導電膜の材料は、酸化インジウム(In2O3)や酸化インジウム酸化スズ合金(I

n2O3―SnO2;ITO)などをスパッタ法や真空蒸着法などを用いて形成して用いる

ことができる。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特

にITOのエッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸

化インジウム酸化亜鉛合金(In2O3―ZnO)を用いても良い。酸化インジウム酸化亜

鉛合金は表面平滑性に優れ、ITOに対して熱安定性にも優れているので、ドレイン配線

169の端面で接触するAlとの腐蝕反応を防止できる。同様に、酸化亜鉛(ZnO)も

適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添

加した酸化亜鉛(ZnO:Ga)などを用いることができる。本実施例では透明導電膜1

41として酸化インジウム酸化亜鉛合金を形成する。(図6(A))

【0084】

図9に図6(A)に対応する接続配線183の端子部182部分の構造を示す。(A)

は配線の長尺方向に垂直な断面に対応し、(B)は長尺方向に沿った断面図に対応し、T

FTとの構造と積層関係が明らかになるようにした。(C)は上面図である。図10、図

11も同様である。

【0085】

フォトマスクPM6によりレジストマスクパターンを形成し、エッチングによってソー

ス配線148〜152とドレイン配線153〜158を形成する。及び、図10に示すよ

うに接続配線183を形成する。ここで、ドレイン配線157は画素電極として機能する

ものである。(図6(B)、図10)。

【0086】

この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られた。例

えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理

を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。また、この

ような熱処理により保護絶縁膜138や、下地膜102にに存在する水素を島状半導体膜

104〜108に拡散させ水素化をすることもできる。いずれにしても、島状半導体膜1

04〜108中の欠陥密度を1016/cm3以下とすることが望ましく、そのために水素を0

.01〜0.1atomic%程度付与すれば良かった。

【0087】

こうして6枚のフォトマスクにより、同一の基板上に、駆動回路のTFTと画素部の画

素TFTとを有した基板を完成させることができる。駆動回路には第1のpチャネル型T

FT200、第1のnチャネル型TFT201、第2のpチャネル型TFT202、第2

のnチャネル型TFT203、画素部には画素TFT204、保持容量205が形成され

ている。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0088】

駆動回路の第1のpチャネル型TFT200には、島状半導体膜104にチャネル形成

領域206、高濃度p型不純物領域から成るソース領域207a、207b、ドレイン領

域208a,208bを有したシングルドレインの構造を有している。

【0089】

第1のnチャネル型TFT201の島状半導体膜105には、チャネル形成領域209

、ゲート電極119と重ならないLDD領域210、ソース領域212、ドレイン領域2

11が形成されている。LDD領域210のチャネル長方向の長さは1.0〜4.0μm

、好ましくは2.0〜3.0μmとした。nチャネル型TFTにおけるLDD領域の長さ

をこのようにすることにより、ドレイン領域近傍に発生する高電界を緩和して、ホットキ

ャリアの発生を防ぎ、TFTの劣化を防止することができる。

【0090】

サンプリング回路の第2のpチャネル型TFT202の島状半導体膜106には、チャ

ネル形成領域213、高濃度p型不純物領域から成るソース領域214a、214b、ド

レイン領域215a、215bが形成され、シングルドレインの構造となっている。

【0091】

第2のnチャネル型TFT203には、島状半導体膜107にチャネル形成領域216

、LDD領域217、218、ソース領域220、ドレイン領域219が形成されている

。LDD領域217、218の長さは1.0〜4.0μmとする。

【0092】

画素TFT204には、島状半導体膜108にチャネル形成領域221、222、LD

D領域223〜225、ソースまたはドレイン領域226〜228を有している。LDD

領域のチャネル長方向の長さは0.5〜4.0μm、好ましくは1.5〜2.5μmであ

る。更に画素TFT204には保持容量が接続されている。保持容量205は、ゲート絶

縁膜209を誘電体にし、容量配線123と画素TFT204のドレイン領域228に接

続する半導体膜229を電極にするコンデンサーである。図6(B)では画素TFT20

4をダブルゲート構造としたが、シングルゲート構造でも良いし、複数のゲート電極を設

けたマルチゲート構造としても差し支えない。

【0093】

図13は画素部のほぼ一画素分を示す上面図である。図中に示すA−A'断面が図6(

B)に示す画素部の断面図に対応している。画素TFT204は、ゲート配線を兼ねるゲ

ート電極122は、図示されていないゲート絶縁膜を介してその下の島状半導体膜108

と交差している。図示はしていないが、島状半導体膜108には、ソース領域、ドレイン

領域、LDD領域が形成されている。また、256はソース配線152とソース領域22

6とのコンタクト部、257はドレイン配線157とドレイン領域228とのコンタクト

部である。保持容量205は、画素TFT204のドレイン領域228から延在する半導

体膜229とゲート絶縁膜を介して容量配線123が重なる領域で形成されている。この

構成において半導体膜229には、価電子制御を目的とした不純物元素は添加されていな

い。

【0094】

以上の様な構成は、画素TFTおよび駆動回路が要求する仕様に応じて各回路を構成す

るTFTの構造を最適化し、半導体装置の動作性能と信頼性を向上させることを可能とし

ている。さらにゲート電極を耐熱性を有する導電性材料で形成することによりLDD領域

やソース領域およびドレイン領域の活性化を容易としている。

【0095】

更に本実施例では、図7に示すように、上述した工程を経たアクティブマトリクス基板

からに柱状スペーサ172を形成する。同時に、柱状スペーサ172を作製すると共に、

接続配線183の端子部182の側面を保護する保護膜174を形成する。柱状スペーサ

172の材料に限定はないが、例えば、JSR社製のNN700を用い、スピナーで塗布

した後、露光と現像処理によって所定のパターンに形成する。さらにクリーンオーブンな

どで150〜200℃で加熱して硬化させる。

【0096】

このようにして作製されるスペーサは露光と現像処理の条件によって形状を異ならせる

ことができるが、好ましくは、図14で示すように、柱状スペーサ172の形状は柱状で

頂部が平坦な形状となるようにすると、対向側の基板を合わせたときに液晶表示パネルと

しての機械的な強度を確保することができる。形状は円錐状、角錐状など特別の限定はな

いが、例えば円錐状としたときに具体的には、高さHを1.2〜5μmとし、平均半径L

1を5〜7μm、平均半径L1と底部の半径L2との比を1対1.5とする。このとき側

面のテーパー角は±15°以下とする。

【0097】

スペーサの配置は任意に決定すれば良いが、好ましくは、図7に示すように、画素部1

88においてはドレイン配線157(画素電極)のコンタクト部251と重ねてその部分

を覆うように柱状スペーサ172を形成すると良い。コンタクト部251は平坦性が損な

われこの部分では液晶がうまく配向しなくなるので、このようにしてコンタクト部251

にスペーサ用の樹脂を充填する形で柱状スペーサ172を形成することで、ディスクリネ

ーションなどを防止することができる。

【0098】

図11に示すように、柱状スペーサ172の作製過程で、接続配線183の側面を保護

する保護膜174が形成される。保護膜174は端子部182において、透明導電膜14

1の表面だけを露出するように形成される。保護膜174の形状は露光と現像処理の条件

によって決定できる。この構成により、接続配線183の端子部182において、金属膜

140は保護膜174、ゲート絶縁膜109、及び透明導電膜141接して、覆われるた

め、外気に曝されることがない。

【0099】

その後、基板101の表面に配向膜173を形成する。端子部182には配向膜173

は形成されない。通常液晶表示素子の配向膜にはポリイミド樹脂が用いられる。配向膜1

73を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配

向するようにした。画素部に設けた柱状スペーサ172の端部からラビング方向に対して

ラビングされない領域が2μm以下となるようにした。また、ラビング処理では静電気の

発生がしばしば問題となるが、駆動回路のTFT上にもスペーサ172を形成しておくと

、スペーサとしての本来の役割と、静電気からTFTを保護する効果を得ることができる

。

【0100】

以上により、基板間隔を保持する柱状スペーサ172が基板101と一体化したアクテ

ィブマトリクス基板が完成する。なお、配向膜173を形成した後、柱状スペーサ172

を形成した構成とすることもできる。(図7、図11)

【0101】

アクティブマトリクス基板と対になる対向基板には、図8に示すように、基板251上

に遮光膜252、図示しないカラーフィルター、透明導電膜253および配向膜254が

形成されている。遮光膜252はTi、Cr、Alなどを150〜300nmの厚さで形成

する。

【0102】

そして、図8に示すように画素部と駆動回路が形成されたアクティブマトリクス基板と

対向基板とをシール剤179で貼り合わせる。シール剤179にはフィラーが混入されて

いて、このフィラーと柱状スペーサ172によって均一な間隔を持って2枚の基板が貼り

合わせられる。そして、基板の隙間に液晶材料260を注入し、封止剤(図示せず)によ

って完全に封止して、液晶パネルが完成する。

【0103】

更に、アクティブマトリクス基板100上の回路を映像信号を入力するための回路や、

電力を供給するための電源等に接続するため、図12に示すように、端子部182におい

て、接続配線183とFPC191を異方性導電膜195によって電気的に接続する。図

12(A)は端子部182の配線の長尺方向と垂直な面の断面図であり、図12(B)は

長尺方向に沿った断面である。

【0104】

図12に示すように異方性導電膜195は接着剤195a内に金やクロムなどでメッキ

された数十〜数百μm粒子195bにより構成され、この粒子195bが接続配線183

とFPCの配線191bとに接触することにより、アクティブマトリクス基板100とF

PC191電気的に接続することができる。FPC191は基板101との接着強度を高

めるために、外端子部182の外側にはみだしており、端部には樹脂層192が設けられ

、機械的強度を高めている。

【実施例2】

【0105】

実施例1では、接続配線183をTFTのソース/ドレイン配線と同じ作製工程で作製

したが、本実施例では、ゲート配線と同じ工程で接続配線183を作製するとする。図1

5を用いて、本実施例を説明する。TFTの作製工程は実施例1を用いる。図15におい

て、図3〜図8と同じ符号は同じ構成要素をさす。

【0106】

まず、実施例1の作製工程に従って、図9(C)の工程までを行う。次に、ゲート配線

を構成する導電膜301と透明導電膜302の積層膜を成膜する。導電膜301は実施例

1述べたゲート配線を構成する導電膜110や111の材料を用いればよい。また透明導

電膜302としては、TFTのソース/ドレイン配線の表面に形成された透明導電膜14

1と同じ材料を用いることができる。ここでは、導電膜301として、WN膜/W膜の積

層膜をスパッタ法で成膜し、透明導電膜としてITO膜を成膜する(図15(A))。

【0107】

そして、図4(A)に示すようにレジストマスクを形成し、導電膜301と透明導電膜

302をエッチングして、TFTのゲート配線及び図15(B)に示すように接続配線3

04を形成する。Wを主成分とする材料で形成されている場合には、高速でかつ精度良く

エッチングを実施するために高密度プラズマを用いたドライエッチング法を適用すること

が望ましい。

【0108】

高密度プラズマを得る手法の一つとして、誘導結合プラズマ(Inductively Coupled Pl

asma:ICP)エッチング装置を用いると良い。ICPエッチング装置を用いたWのエッ

チング法は、エッチングガスにCF4とCl2の2種のガスを反応室に導入し、圧力0.5

〜1.5Pa(好ましくは1Pa)とし、誘導結合部に200〜1000Wの高周波(1

3.56MHz)電力を印加する。この時、基板が置かれたステージには20Wの高周波

電力が印加され、自己バイアスで負電位に帯電することにより、正イオンが加速されて異

方性のエッチングを行うことができる。ICPエッチング装置を使用することにより、W

などの硬い金属膜も2〜5nm/秒のエッチング速度を得ることができる。また、残渣を残

すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増しオ

ーバーエッチングをすると良い。

【0109】

しかし、この時に下地とのエッチングの選択比に注意する必要がある。例えば、W膜に

対する酸化窒化シリコン膜(ゲート絶縁膜109)の選択比は2.5〜3であるので、こ

のようなオーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50

nm程度エッチングされて実質的に薄くなる。

【0110】

そして、実施例1で説明したようにTFTの半導体膜にリン、ボロンを添加し、図5(

A)に示すように保護絶縁膜138を形成し、半導体膜に添加したリン、ボロンを活性化

する(図15(C))。

【0111】

そして、図5(C)に示すように層間絶縁膜139を形成する。層間絶縁膜139の材

料は実施例1で説明したた材料を選択すればよく、シリコン系の無機絶縁膜でもよいし、

アクリル等の有機樹脂膜でもよい(図15(D))。

【0112】

次に、図6に示すように、保護絶縁膜138に層間絶縁膜139に島状半導体膜に形成

されたソース領域またはドレイン領域に達するコンタクトホールを形成すると同時に、接

続配線304の端子部において、端子部の側面を覆う保護膜304を形成する(図15(

E))。

【0113】

以降の工程は実施例1と同様に実施して、アクティブマトリクス基板100を完成する

。そして、アクティブマトリクス基板100と対向基板250をシール剤179によって

貼り合わせ液晶材料260を封入し、接続配線304とFPC191を異方性導電膜19

5によって電気的に接続する(図15(F))。

【0114】

本実施例では、保護膜304によって、接続配線304の導電膜301の側面を覆って

いるため、導電膜301は保護膜304、ゲート絶縁膜109、透明導電膜302でくる

まれた構造となり、外気に曝されることがない。

【実施例3】

【0115】

本実施例は実施例1の変形例であり、ゲート配線の断面形状がテーパ状になるようにし

たものであり、また、接続配線をゲート配線と同じ作製工程で作製するようにした例であ

る。図17〜図19を用いて本実施例のアクティブマトリクス基板の作製工程を説明する

。ここでは、画素部の画素TFTおよび保持容量と、画素部の周辺に設けられる駆動回路

のTFTを同時に作製する方法について工程に従って詳細に説明する。図21に接続配線

の作製工程を示す。

【0116】

図17(A)において、ガラス基板601表面に、酸化シリコン膜、窒化シリコン膜ま

たは酸化窒化シリコン膜などの絶縁膜から成る下地膜602を形成する。本実施例では、

プラズマCVD法でSiH4、NH3、N2Oから成膜される酸化窒化シリコン膜を10〜

200nmし、酸化窒化シリコン膜表面にSiH4、N2Oから成膜される酸化窒化水素化シ

リコン膜602を50〜200nm(好ましくは100〜150nm)の厚さに積層形成す

る。

【0117】

次に、プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成し、実施例1と同

様に結晶化して、結晶質シリコン膜を形成する。そしてフォトマスクPM11を用いて、

フォトリソグラフィーの技術により、結晶質シリコン膜上にレジストパターンを形成し、

ドライエッチングによって結晶質半導体膜を島状に分割し、島状半導体膜604〜608

を形成する。結晶質シリコン膜のドライエッチングにはCF4とO2の混合ガスを用いる。

次に、ゲート絶縁膜609はプラズマCVD法で120nmの厚さで酸化窒化シリコン膜

から形成する。

【0118】

そして、ゲート絶縁膜609上にゲート配線を形成するために金属膜611、612と

透明導電膜613の積層膜を耐熱性導電膜を形成する。金属膜611をWN膜で、金属膜

膜612をW膜で形成し、透明導電膜613に酸化インジウム酸化亜鉛合金(In2O3―

ZnO)を成膜する(図17(A)、図21(A))

。

【0119】

第2のフォトマスクPM12を用い、フォトリソグラフィーの技術を使用してレジスト

マスクRM21〜RM27を形成し、透明導電膜613をエッチングして、ゲート配線618〜6

22と容量配線623、接続配線683の最上層618a〜623a、683aを形成す

る。(図17(B)、図21(B))

【0120】

透明導電膜でなる最上層618a〜623a、683aの側面は図18(B)

、図21(B)に示すように、レジストマスクRM21〜RM27よりも後退するようにエッチン

グされる。次に、 金属膜611、613を一括でエッチングして、テーパー状の断面を

有するゲート配線618〜6、22、容量配線623及び接続配線683が完成する。(

図17(C)、図21(C))

【0121】

配線618〜623、683は、透明導電膜613でなる層618a〜623a、68

3aと、金属膜612でなる層618b〜623b、683bと、金属膜611でなる層

618c〜623c、683cが積層された構造となる。

【0122】

このとき少なくともゲート配線618〜622の端部にテーパー部が形成されるように

エッチングする。このエッチング加工はICPエッチング装置により行う。エッチングガ

スにCF4とCl2の混合ガスを用いその流量をそれぞれ30SCCMとして、放電電力3.2

mW/cm2(13.56MHz)、バイアス電力224mW/cm2(13.56MHz)、圧力1.0Paでエッチング

を行った。このようなエッチング条件によって、ゲート配線618〜622の端部におい

て、該端部から内側にむかって徐々に厚さが増加するテーパー部が形成され、その角度は

25〜35°、好ましくは30°となる。テーパー部の角度は、後にLDD領域を形成す

る低濃度n型不純物領域の濃度勾配に大きく影響する。尚、テーパー部の角度θ1は、テ

ーパー部の長さ(WG)とテーパー部の厚さ(HG)を用いてTan(θ1)=HG/W

Gで表される。

【0123】

また、残渣を残すことなくエッチングするためには、絶縁膜609の厚さの10〜20

%程度の割合でオーバーエッチングする。しかし、この時に下地とのエッチングの選択比

に注意する必要がある。例えば、W膜に対する酸化窒化シリコン膜(ゲート絶縁膜609

)の選択比は表1で示したように2〜4(代表的には3)であるので、このようなオーバ

ーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチン

グされて実質的に薄くなり、新たな形状のゲート絶縁膜610が形成された。

【0124】

そして、画素TFTおよび駆動回路のnチャネル型TFTのLDD領域を形成するため

に、n型を付与する不純物元素添加の工程(n-ドープ工程)を行う。

ゲート電極の形成に用いたレジストマスク112〜117をそのまま残し、端部にテーパ

ー部を有するゲート配線618〜622をマスクとして自己整合的にn型を付与する不純

物元素としてリンをイオンドープ法で添加する(図18(A)

)。

【0125】

ここでは、n型を付与する不純物元素を配線618〜623のテーパー部とゲート絶縁

膜610とを通して、その下に位置する半導体膜に達するように添加するために、加速電

圧を高く80〜160keVとし、LDD領域を形成するためにドーズ量を低く、1×1

013〜5×1014atoms/cm2とする。半導体膜に添加される不純物の濃度は1×1016〜

1×1019atoms/cm3の濃度範囲で添加する。このようにして、図18(A)に示すよう

に島状半導体膜に低濃度n型不純物領域624〜629を形成する。

【0126】

この工程において、低濃度n型不純物領域624〜628において、少なくともゲート

配線618〜622に重なった部分に含まれるリン(P)の濃度勾配は、ゲート配線61

8〜622のテーパー部の膜厚変化を反映する。即ち、低濃度n型不純物領域624〜6

28へ添加されるリン(P)の濃度は、ゲート配線に重なる領域において、ゲート配線の

側面に向かって徐々に濃度が高くなる。これはテーパー部の膜厚の差によって、半導体膜

に達するリン(P)の濃度が変化するためである。尚、図18(A)では低濃度n型不純

物領域624〜628を斜めに図示しているが、これはリン(P)が添加された領域を直

接的に示しているのではなく、上述のようにリンの濃度変化がゲート配線618〜622

のテーパー部の形状に沿って変化していることを表している。

【0127】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する高

濃度n型不純物領域の形成を行った(n+ドープ工程)。レジストマスクRM21〜RM26を残

し、今度はゲート配線618〜622がリン(P)を遮蔽するマスクとなるように、イオ

ンドープ法において10〜30keVの低加速電圧の条件で添加する。このようにして高

濃度n型不純物領域630〜635を形成する。これら領域630〜635を覆うゲート

絶縁膜610は、ゲート配線の形成工程においてオーバーエッチングされたため、当初の

膜厚である120nmから薄くなり、70〜100nmとなっている。そのためこのような低

加速電圧の条件でも良好にリン(P)を添加することができる。そして、これら領域63

0〜635のリン(P)の濃度は1×1020〜1×1021atoms/cm3の範囲となるように

する(図18(B))。

【0128】

そして、pチャネル型TFTを形成する島状半導体膜604、606にソース領域およ

びドレイン領域とする高濃度p型不純物領域636、637を形成する。ここでは、ゲー

ト配線618、120をマスクとしてp型を付与する不純物元素を添加し、自己整合的に

高濃度p型不純物領域636、637を形成する。このとき、nチャネル型TFTを形成

する島状半導体膜605、107、108は、第3のフォトマスクPM23を用いてレジスト

マスクRM29〜RM31を形成し全面を被覆しておく(図18(C))。

【0129】

ここで形成される不純物領域636、637はジボラン(B2H6)を用いたイオンドー

プ法で形成する。そして、ゲート配線と重ならない高濃度p型不純物領域のボロン(B)

濃度が3×1020〜3×1021atoms/cm3となるようにする。

また、ゲート配線と重なる不純物領域にもゲート絶縁膜とゲート電極のテーパー部を介し

て不純物元素が添加されるので、実質的に低濃度p型不純物領域として形成され、少なく

とも1.5×1019atoms/cm3以上の濃度とし、ボロン(B)

の濃度を図18(A)の工程で添加されたリン(P)濃度の1.5から3倍となるように

することにより、pチャネル型TFTのソース領域およびドレイン領域として機能するた

めに何ら問題は生じない。

【0130】

その後、図19(A)、図21(D)に示すように、酸化窒化シリコンでなる保護絶縁

膜638を形成する。酸化窒化シリコン膜はプラズマCVD法でSiH4、N2O、NH3

から成膜する。その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元

素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行

う。

活性化の工程に続いて、雰囲気ガスを変化させ、3〜100%の水素を含む雰囲気中で

、300〜450℃で1〜12時間の熱処理を行い、島状半導体膜を水素化する工程を行

う。この工程は熱的に励起された水素により島状半導体膜にある1016〜1018/cm3のダ

ングリングボンドを終端する工程である。

【0131】

活性化および水素化の工程が終了したら、有機絶縁物材料からなる層間絶縁膜639を

平均の厚さが1.0〜2.0μmとなるように形成する(図19(B)

、図21(E))。

【0132】

その後、第4のフォトマスクPM24を用い、所定のパターンのレジストマスクを形成し、

それぞれの島状半導体膜に形成されたソース領域またはドレイン領域に達するコンタクト

ホール及び、図21(E)に示すように接続配線683の側面を覆う保護膜673を形成

する。

【0133】

この工程はドライエッチング法により行う。この場合、エッチングガスにCF4、O2、

Heの混合ガスを用い有機樹脂材料から成る層間絶縁膜639をまずエッチングし、その

後、続いてエッチングガスをCF4、O2として保護絶縁膜638をエッチングする。さら

に、島状半導体膜との選択比を高めるために、エッチングガスをCHF3に切り替えてゲ

ート絶縁膜610をエッチングすることにより、良好にコンタクトホールを形成すること

ができる。

【0134】

図21(E)に示すように、保護膜673によって接続配線683の側面を覆うことに

より、接続配線683の金属膜でなる層683c、683bの表面は透明導電膜でなる層

683aとゲート絶縁膜610と保護膜673に接した状態で囲まれるため、外気に曝さ

れることがない。

【0135】

そして、Ti膜(50〜150nm)/Al膜(300〜400nm)を積層した金属膜と

、金属膜表面に透明導電膜を80〜120nmの厚さで形成し、形成図19(C)に示すよ

うに、金属膜をスパッタ法や真空蒸着法で形成し、第5のフォトマスクPM25によりレジス

トマスクパターンを形成し、金属膜と透明導電膜をエッチングして、ソース配線648〜

652とドレイン配線653〜657を形成する。ここで、ドレイン配線657は画素電

極として機能するものである。ドレイン配線658は隣の画素に属する画素電極を表して

いる。

【0136】

駆動回路の第1のpチャネル型TFT700には、島状半導体膜604にチャネル形成

領域706、高濃度p型不純物領域から成るソース領域707、ドレイン領域708が形

成されている。領域707、708において、ゲート電極と重なる領域はボロン濃度が低

いLDD領域となっている。

【0137】

第1のnチャネル型TFT701には、島状半導体膜605にチャネル形成領域709

、低濃度n型不純物領域で形成されゲート配線と重なるLDD領域、710、711、高

濃度n型不純物領域で形成するソース領域713、ドレイン領域712を有している。

【0138】

このLDD領域におけるリン(P)の濃度分布はチャネル形成領域709から遠ざかる

につれて増加する。この増加の割合は、イオンドープにおける加速電圧やドーズ量などの

条件、テーパーの角度θ1やゲート配線619の厚さによって異なってくる。このように

、ゲート電極の端部をテーパー形状として、そのテーパー部を通して不純物元素を添加す

ることにより、テーパー部の下に存在する半導体膜中に、徐々に前記不純物元素の濃度が

変化するような不純物領域を形成することができる。本発明はこのような不純物領域を積

極的に活用する。nチャネル型TFTにおいてこのようなLDD領域を形成することによ

り、ドレイン領域近傍に発生する高電界を緩和して、ホットキャリアの発生を防ぎ、TF

Tの劣化を防止することができる。

【0139】

駆動回路の第2のpチャネル型TFT702はTFT700と同様に、島状半導体膜6

06にチャネル形成領域714、高濃度p型不純物領域で形成されるソース領域715、

ドレイン領域716を有する。領域715、716においてゲート配線と重なった領域は

ボロン濃度が低いp型のLDD領域となっている。

【0140】

第2のnチャネル型TFT703には、島状半導体膜607にチャネル形成領域717

、ゲート電極621と重なるLDD領域718、719、高濃度n型不純物領域で形成す

るソース領域720、ドレイン領域721を有している。LDD領域718、719は、

LDD領域711、712と同じ構成とする。

【0141】

画素TFT704には、島状半導体膜608にチャネル形成領域723、724、低濃

度n型不純物領域で形成するLDD領域725〜728、高濃度n型不純物領域で形成す

るソースまたはドレイン領域729〜731を有している。LDD領域725〜728は

、LDD領域711、712と同じ構成とする。

【0142】

さらに、保持容量705においては、半導体膜608にチャネル形成領域732と、L

DD領域733、734、n型の高濃度不純物領域735が改正され、ゲート絶縁膜61

0を誘電体に、容量配線623と、半導体膜608を電極にする。

【0143】

そして、実施例1と同様に、第6のフォトマスクを用いて、基板間隔を保持する柱状ス

ペーサ672を形成し、配向膜674を形成しラビングする。そして、実施例1と同様に

、対向基板250とアクティブマトリクス基板700をシール剤686と貼り合わせ、基

板の隙間に液晶材料260を封入する。対向基板250の構成は図8と同様である。

【0144】

更に、図21(F)に示すように、接続配線683の端子部において、接着剤195a

に導電粒195bが分散された異方性導電膜195によって、FPC191を電気的に接

続する。FPC191において、191aはポリイミド等でなる基板であり、191bは

銅等でなる配線である。

【0145】

実施例1〜3ではトップゲート型TFTを示したが、ボトムゲート型TFTに置き換え

ることは当業者であれば容易である。また、これた実施例では、アクティブマトリクス基

板について説明したが、これら実施例の接続配線の構造は他の半導体装置にも適用できる

ことはいうまでもない。実施例2、3のように接続配線の保護膜をTFTの層間絶縁膜で

形成する場合には、アクティブマトリクス型のEL装置などTFTでなる回路を有する半

導体装置に適用可能である。

【実施例4】

【0146】

本発明を実施して作製されたアクティブマトリクス基板および液晶表示装置並びにEL

型表示装置は様々な電気光学装置に用いることができる。そして、そのような電気光学装

置を表示媒体として組み込んだ電子機器全てに本発明を適用することがでできる。電子機

器としては、パーソナルコンピュータ、デジタルカメラ、ビデオカメラ、携帯情報端末(

モバイルコンピュータ、携帯電話、電子書籍など)、ナビゲーションシステムなどが上げ

られる。それらの一例を図23に示す。

【0147】

図23(A)はパーソナルコンピュータであり、マイクロプロセッサやメモリーなどを

備えた本体2001、画像入力部2002、表示装置2003、キーボード2004で構

成される。本発明は表示装置2003やその他の信号処理回路を形成することができる。

【0148】

図23(B)はビデオカメラであり、本体2101、表示装置2102、音声入力部2

103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本

発明は表示装置2102やその他の信号制御回路に適用することができる。

【0149】

図23(C)は携帯情報端末であり、本体2201、画像入力部2202、受像部22

03、操作スイッチ2204、表示装置2205で構成される。本発明は表示装置220

5やその他の信号制御回路に適用することができる。

【0150】

このような携帯型情報端末は、屋内はもとより屋外で使用されることも多い。

長時間の使用を可能とするためにはバックライト使用せず、外光を利用する反射型の液晶

表示装置が低消費電力型として適しているが、周囲が暗い場合にはバックライトを設けた

透過型の液晶表示装置が適している。このような背景から反射型と透過型の両方の特徴を

兼ね備えたハイブリット型の液晶表示装置が開発されているが、本発明はこのようなハイ

ブリット型の液晶表示装置にも適用できる。

【0151】

図22に実施例1の液晶パネルを携帯型情報端末に適用した例を示す。表示装置220

5はタッチパネル3002、液晶表示装置3003、LEDバックライト3004により

構成されている。タッチパネル3002は携帯型情報端末の操作を簡便にするために設け

ている。タッチパネル3002の構成は、一端にLEDなどの発光素子3100を、他の

一端にフォトダイオードなどの受光素子3200が設けられ、その両者の間に光路が形成

されている。このタッチパネル3002を押して光路を遮ると受光素子3200の出力が

変化するので、この原理を用いて発光素子と受光素子を液晶表示装置上でマトリクス状に

配置させることにより、入力媒体として機能させることができる。

【0152】

図23(D)はテレビゲームまたはビデオゲームなどの電子遊技機器であり、CPU等

の電子回路2308、記録媒体2304などが搭載された本体2301、コントローラ2

305、表示装置2303、本体2301に組み込まれた表示装置2302で構成される

。表示装置2303と本体2301に組み込まれた表示装置2302とは、同じ情報を表

示しても良いし、前者を主表示装置とし、後者を副表示装置として記録媒体2304の情

報を表示したり、機器の動作状態を表示したり、或いはタッチセンサーの機能を付加して

操作盤とすることもできる。また、本体2301とコントローラ2305と表示装置23

03とは、相互に信号を伝達するために有線通信としても良いし、センサ部2306、2

307を設けて無線通信または光通信としても良い。本発明は、表示装置2302、23

03に適用することができる。表示装置2303は従来のCRTを用いることもできる。

【0153】

図23(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレ

ーヤーであり、本体2401、表示装置2402、スピーカー部2403、記録媒体24

04、操作スイッチ2405で構成される。尚、記録媒体にはDVD(Digital Versati

le Disc)やコンパクトディスク(CD)などを用い、音楽プログラムの再生や映像表示

、ビデオゲーム(またはテレビゲーム)やインターネットを介した情報表示などを行うこ

とができる。本発明は表示装置2402やその他の信号制御回路に好適に利用することが

できる。

【0154】

図23(F)はデジタルカメラであり、本体2501、表示装置2502、接眼部25

03、操作スイッチ2504、受像部(図示しない)で構成される。本発明は表示装置2

502やその他の信号制御回路に適用することができる。

【0155】

図24(A)はフロント型プロジェクターであり、光源光学系および表示装置2601

、スクリーン2602で構成される。本発明は表示装置やその他の信号制御回路に適用す

ることができる。図24(B)はリア型プロジェクターであり、本体2701、光源光学

系および表示装置2702、ミラー2703、スクリーン2704で構成される。本発明

は表示装置やその他の信号制御回路に適用することができる。

【0156】

なお、図24(C)に、図24(A)および図24(B)における光源光学系および表

示装置2601、2702の構造の一例を示す。光源光学系および表示装置2601、2

702は光源光学系2801、ミラー2802、2804〜2806、ダイクロイックミ

ラー2803、ビームスプリッター2807、液晶表示装置2808、位相差板2809

、投射光学系2810で構成される。投射光学系2810は複数の光学レンズで構成され

る。

【0157】

図24(C)では液晶表示装置2808を三つ使用する三板式の例を示したが、このよ

うな方式に限定されず、単板式の光学系で構成しても良い。また、図24(C)中で矢印

で示した光路には適宣光学レンズや偏光機能を有するフィルムや位相を調節するためのフ

ィルムや、IRフィルムなどを設けても良い。また、図24(D)は図24(C)におけ

る光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系280

1はリフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換

素子2815、集光レンズ2816で構成される。尚、図24(D)に示した光源光学系

は一例であって図示した構成に限定されるものではない。

【0158】

また、ここでは図示しなかったが、本発明はその他にも、ナビゲーションシステムやイ

メージセンサの読み取り回路などに適用することも可能である。このように本願発明の適

用範囲はきわめて広く、あらゆる分野の電子機器に適用することが可能である。

【符号の説明】

【0159】

101 基板

172 柱状スペーサ

173 保護膜

182 端子部

183 接続配線

186 シール剤

191 FPC

【技術分野】

【0001】

本発明は絶縁表面を有する基板上に薄膜トランジスタ(以下、TFTと記す)

で構成された回路を有する半導体装置に関する。TFTで構成された回路を他の基板上の

回路と接続するための端子の構造に関する。特に本発明は、画素部とその周辺に設けられ

る駆動回路を同一基板上に設けた液晶表示装置やエレクトロルミネッセンス(EL)表示

装置や、これら表示装置を搭載した電気光学装置を搭載した電子機器に好適に利用できる

技術を提供する。尚、本明細書において半導体装置とは、半導体の特性を利用することで

機能する装置全般を指し、上記液晶表示装置だけでなく、表示装置を搭載した電子機器を

その範疇に含んでいる。

【背景技術】

【0002】

アクティブマトリクス型の液晶表示装置に代表される電気光学装置において、スイッチ

ング素子や能動回路を構成するためにTFTを用いる技術が開発されている。TFTはガ

ラスなどの基板上に気相成長法により半導体膜を形成し、その半導体膜を活性層として形

成する。半導体膜にはシリコン又はシリコン・ゲルマニウムなどシリコンを主成分とする

材料が好適に用いられている。さらに、シリコン半導体膜はその作製法により、非晶質シ

リコン膜や多結晶シリコンに代表される結晶質シリコン膜などを得ることができる。

【0003】

非晶質シリコン膜を活性層としたTFTは、非晶質構造などに起因する電子物性的要因

から、本質的に数cm2/Vsec以上の電界効果移動度を得ることができない。従って、アクテ

ィブマトリクス型の液晶表示装置において、画素部の各画素に設けられる液晶を駆動する

ためのスイッチング素子(画素TFT)として使用することはできても、画像表示を行う

ための駆動回路まで形成することは不可能であった。そのために、TAB(Tape Automat

ed Bonding)方式やCOG(Chip on Glass)方式を使ってドライバICなどを実装する

技術が用いられていた。

【0004】

一方、結晶質シリコン膜を活性層としたTFTでは、高い電界効果移動度が得られるこ

とから各種の機能回路を同一のガラス基板上に形成することが可能となり、画素TFTの

他に駆動回路においてnチャネル型TFTとpチャネル型TFTとから成るCMOS回路

を基本として形成されるシフトレジスタ回路、レベルシフタ回路、バッファ回路、サンプ

リング回路など同一基板上に作製することができる。低コスト化及び高品位化のため、ア

クティブマトリクス型液晶表示装置では、画素と画素を駆動するための駆動回路を同一基

板上に作製したアクティブマトリクス基板が用いられるようになった。

【0005】

上記のようなアクティブマトリクス基板では、駆動回路に電源や入力信号を供給するた

めに、アクティブマトリクス基板上に、駆動回路と接続した接続配線を作製し、接続配線

とFPC(Flexible Print Circuit)を実装する構造が採用されている。基板上の接続配線

とFPCの接続には異方性導電膜が用いられている。

図30に異方性導電膜によってFPCに接続された接続配線の断面構造を示す。

【発明の概要】

【発明が解決しようとする課題】

【0006】

図30に示すように、アクティブマトリクス基板において、ガラス基板1の表面の絶縁

膜2上に接続配線3が形成されている。FPC4はポリイミドなどでなる可撓性の基板5

上に銅などからなる多数の配線6が形成されている。異方性導電膜7には、導電性スペー

サ8が、熱や光により硬化する接着剤9(樹脂)内に分散されている。接続配線3とFP

C4の上の配線6は導電性スペーサ8によって電気的に接続されている。

【0007】

接続配線3は、アルミニウムやチタンなどの金属膜3aとITO膜等の透明導電膜3b

の2多層構造となっている。透明導電膜3bとしてアルミニウムなどの金属膜を用いるこ

とで配線抵抗を低くできるが、金属膜3aが導電性スペーサ8に押されて変形するおそれ

がある。透明導電膜3bはインジウムやスズなどの金属の酸化物でなるため、金属膜3a

よりも硬度が高い。そこで、透明導電膜3bを表面に形成することで、金属膜3aの破損

や変形を防止している。

【0008】

しかしながら、金属膜3aの側面は異方性導電膜7が形成されるまでは剥き出しの状態

で、外気に曝されているため、腐食や酸化されやすい状態となっており、接続配線3とF

PC4との接続の信頼性を下げる原因となる。また、FPC4が実装された状態では、金

属膜3aの側面は樹脂と接しているため、水分に対する保護に問題がある。

【0009】

本発明は上述した問題点を解消して、FPCと配線の信頼性の高い接続を実現し、かつ

量産に適した接続配線を提供することを目的とする。

【課題を解決するための手段】

【0010】

上述の課題を課題を解決するために、本発明は基板上の接続配線を異方性導電膜によっ

て他の基板上の配線と電気的に接続するコンタクト構造であって、 前記引き出し配線は

金属膜と透明導電膜の積層膜でなり、前記異方性導電膜との接続部分において、前記金属

膜の側面は保護膜に覆われていることを特徴とする。

【0011】

また、他の構成は、基板上に、薄膜トランジスタが配置された回路と、前記薄膜トラン

ジスタでなる回路を他の回路と接続するための接続配線と、を有する半導体装置であって

、 前記接続配線金属膜と透明導電膜の積層膜でなり、前記他の回路との接続部分におい

て前記金属膜側面は保護膜に覆われていることを特徴とする。

【0012】

また、他の構成は薄膜トランジスタが配置された回路を有する第1の基板と、前記第1

の基板に対向する第2の基板とを有する半導体装置であって、 前記第1の基板上には、

前記薄膜トランジスタが配置された回路を他の回路と接続するための、金属膜と、該金属

膜表面に接する透明導電膜とでなる接続配線と、前記金属膜の側面に接する保護膜が形成

されていることを特徴とする。

【0013】

また、他の構成は薄膜トランジスタが配置された回路を有する第1の基板と、前記第1

の基板に対向する第2の基板とを有する半導体装置であって、 前記第1の基板上には、

前記薄膜トランジスタが配置された回路を他の回路と接続するための、金属膜と、該金属

膜表面に接する透明導電膜とでなる接続配線と、前記薄膜トランジスタ上に形成され、前

記第1の基板と前記第2の基板間隔を維持するための柱状スペーサと、前記金属膜の側面

に接する前記柱状スペーサと同じ材料でなる保護膜が形成されていることを特徴とする。

【発明の効果】

【0014】

本発明を用いることで、異方性導電膜によって他の回路と接続される接続配線において

、金属膜を保護膜及び透明導電膜で覆う構造となるため、製造過程や、異方性導電膜の接

着剤との接触によって生ずる金属膜の腐食、変質を防ぐことができるため、信頼性の高い

コンタクト構造とすることが可能になる。

【図面の簡単な説明】

【0015】

【図1】アクティブマトリクス基板の構成を説明する上面図。

【図2】液晶表示装置の回路構成を説明するブロック図。

【図3】アクティブマトリクス基板の作製工程を示す断面図。

【図4】アクティブマトリクス基板の作製工程を示す断面図。

【図5】アクティブマトリクス基板の作製工程を示す断面図。

【図6】アクティブマトリクス基板の作製工程を示す断面図。

【図7】アクティブマトリクス基板の作製工程を示す断面図。

【図8】液晶パネルの断面図。

【図9】接続配線の端子部の作製工程を示す断面図。

【図10】接続配線の端子部の作製工程を示す断面図。

【図11】接続配線の端子部の作製工程を示す断面図。

【図12】接続配線の端子部と異方性導電膜のコンタクト構造を示す断面図。

【図13】画素部の1画素の上面図。

【図14】柱状スペーサの形状を説明する図

【図15】接続配線の端子部の作製工程を示す断面図。

【図16】接続配線の端子部と異方性導電膜のコンタクト構造を示す断面図。

【図17】アクティブマトリクス基板の作製工程を示す断面図。

【図18】アクティブマトリクス基板の作製工程を示す断面図。

【図19】アクティブマトリクス基板の作製工程を示す断面図。

【図20】液晶パネルの断面図。

【図21】接続配線の端子部の作製工程を示す断面図。

【図22】半導体装置の一例を示す図。

【図23】半導体装置の一例を示す図。

【図24】投影型液晶表示装置の構成を示す図。

【図25】ICPエッチング装置のプラズマ生成機構を示す図。

【図26】マルチスパイラルコイル方式のICPエッチング装置を示す図。

【図27】テーパー角θのバイアスパワー依存性を示す図。

【図28】テーパー角θのCF4の流量比依存性を示す図。

【図29】テーパー角θの(W/レジスト)選択比依存性を示す図。

【図30】従来のアクティブマトリクス基板の端子部と異方性導電膜のコンタクト構造を示す図。

【発明を実施するための形態】

【0016】

[実施形態1]

本発明のコンタクト構造は、異方性導電膜によって回路を接続する実装方法を用いる半

導体装置、例えば、アクティブマトリクス型液晶表示装置や、EL表示装置に好適である

。本実施形態では、図12を用いて、本発明をアクティブマトリクス型の液晶表示装置に

適用した場合のコンタクト構造を説明する。

【0017】

アクティブマトリクス基板上の接続配線183は端子部182において異方性導電膜1

95によって、FPC191に電気的に接続される。接続配線183はアクティブマトリ

クス基板上のTFTのソース/ドレイン配線と同じ工程で作製される。即ち、ソース/ド

レイン配線と同じ材料で、同じ層に形成されている。

金属膜140と透明導電膜141の積層膜でなる。異方性導電膜195との接続部分にお

いて、接続配線183の側面は絶縁材料でなる保護膜173に覆われている。

【0018】

この構造により、接続配線183の金属膜140の側面は保護膜174で覆われる。従

って、接続部分において、金属膜140は透明導電膜141、絶縁膜109、保護膜17

4に接して囲まれ、外気に触れることがない。よって金属膜140の腐食を防止すること

ができる。

【0019】

保護膜174はソース/ドレイン配線の上層に形成される絶縁膜を用いて作製すること

ができる。本実施形態では、保護膜174はアクティブマトリクス基板と対向基板の間隔

を保持するために作製された柱状スペーサ172と同じ工程で作製されている。

【0020】

また、図16に示すように接続配線304をTFTのゲート配線配線と同じ工程で作製

することもできる。この場合には、接続配線304はゲート配線と同じ材料で同じ層に形

成されることになる。また、この場合には、保護膜303はゲート配線とソース/ドレイ

ン配線の間に形成された絶縁膜138、139で作製される。

【0021】

本発明において、接続配線は金属膜の表面を透明導電膜で覆った積層膜で形成される。

金属膜は単層膜に限定されない。金属膜の厚さは100nm〜1μmとする。金属膜として

は、アルミニウム(Al)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、

タングステン(W)から選ばれた元素を主成分とする金属膜や、金属元素を含む合金膜を

少なくとも1層含むが、これら金属層、合金層の単層膜または多層膜であってももちろん

よい。合金としては、Mo−W合金、Mo−Ta合金や、列記した元素と窒素の化合物で

ある窒化タンタル(TaN)、窒化タングステン(WN)、窒化チタン(TiN)膜、窒

化モリブデン(MoN)が挙げられる。またタングステンシリサイド、チタンシリサイド

、モリブデンシリサイドなどシリサイドを用いることもできる。

【0022】

透明導電膜の厚さは50nm〜0.5μmとする。透明導電膜の材料は、酸化インジウム

(In2O3)や酸化インジウム酸化スズ合金(In2O3―SnO2;ITO)などをスパ

ッタ法や真空蒸着法などを用いて形成して用いることができる。このような材料のエッチ

ング処理は塩酸系の溶液により行う。しかし、特にITOのエッチングは残渣が発生しや

すいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金(In2O3―

ZnO)を用いても良い。酸化インジウム酸化亜鉛合金は表面平滑性に優れ、ITOに対

して熱安定性にも優れているので、ドレイン配線169の端面で接触するAlとの腐蝕反

応を防止できる。

同様に、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高め

るためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)などを用いることができ

る。

【0023】

[実施形態2]

また、ゲート配線と同じ工程で接続配線を作製した場合、ゲート配線、接続配線の断面

形状をテーパー形状としてもよい。ゲート配線をテーパ状にすることにより、膜厚が中央

から側面に向かって減少することとなるので、後述する実施例で示すように、ゲート配線

をマスクにした半導体膜のドーピングにおいて、膜厚の変化を利用して半導体膜に添加さ

れる不純物濃度を変化させることができる。

【0024】

テーパ形状にするためには、高密度プラズマを用いたドライエッチング法を適用する。

高密度プラズマを得る手法にはマイクロ波や誘導結合プラズマ(Inductively Coupled Pl

asma:ICP)を用いたエッチング装置が適している。特に、ICPエッチング装置はプ

ラズマの制御が容易であり、処理基板の大面積化にも対応できる。

【0025】

ICPを用いたプラズマ処理装置では、プラズマ処理を高精度に行うための手段として

、高周波電力をインピーダンス整合器を介して4本の渦巻き状コイル部分が並列に接続さ

れてなるマルチスパイラルコイルに印加してプラズマを形成する方法を用いている。ここ

で、各コイル部分の1本当たりの長さは、高周波の波長の1/4倍としている。さらに、

被処理物を保持する下部電極にも、別途高周波電力を印加してバイアス電圧を付加する構

成としている。ICPを用いたプラズマ処理方法やプラズマ処理装置に関しては特開平9

−293600号公報等で開示されている。

【0026】

このようなICPを用いたプラズマ処理装置(例えば、エッチング装置)の構造概略図

を図25に示す。チャンバー上部の石英板11上にアンテナコイル12を配置し、マッチ

ングボックス13を介してRF電源14に接続されている。また、アンテナコイルに対向

して下部電極15が設けられ、下部電極15にプラズマ処理する基板10が配置される。

また下部電極15にもマッチングボックス16を介してRF電源17が接続されており、

基板上方のアンテナコイル12にRF電流が印加されると、アンテナコイル12にRF電

流Jがα方向に流れ、式1に従ってZ方向に磁界Bが発生する。

【0027】

s μ0 J=rotB(μ0 は透磁率) (式1)

【0028】

そして、ファラデーの電磁誘導の法則に従い、θ方向に誘導電界Eが生じる(式2)。

【0029】

−∂B/∂t=rotE (式2)

【0030】

誘導電界Eで電子がα方向に加速されてガス分子と衝突し、プラズマが生成される。誘

導電界の方向がα方向なので、荷電粒子がエッチングチャンバー壁や、基板に衝突して電

荷を消失する確率が低くなる。従って、1Pa程度の低圧力でも高密度のプラズマを発生

させることができる。また、下流へは、磁界Bがほとんどないので、シート状に広がった

高密度プラズマ領域となる。

ICPで高密度プラズマを得る為にはアンテナコイルに流れる高周波電流Jを低損失で

流す必要があり、そのインダクタンスを低下させなければならない。そのために、アンテ

ナコイルを分割した方式とすることが有効となる。

【0031】

アンテナコイル12(ICPパワーが印加される)と基板側の下部電極15(バイアス

パワーが印加される)のそれぞれに印加するRFパワーを調節することによってプラズマ

密度と自己バイアス電圧を独立に制御することが可能である。

また、被エッチング膜に応じて異なる周波数のRFパワーを印加できる。

【0032】

ICPエッチング装置で高密度プラズマを得るためには、アンテナコイル12に流れる

RF電流Jを低損失で流す必要があり、大面積化するためには、アンテナコイル12のイ

ンダクタンスを低下させなければならない。そのために図26に示したようにアンテナを

分割したマルチスパイラルコイル22のICPエッチング装置が開発された。図26中の

21は石英板、23、26はマッチングボックス、24、27はRF電源である。また、

チャンバーの底部には、基板28を保持する下部電極25が絶縁体29を介して設けられ

ている。

【0033】

このようなマルチスパイラルコイルを適用したICPを用いたエッチング装置を用いる

と、前記耐熱性導電性材料のエッチングを良好に行うことができまた所望のテーパー角θ

を有する配線を形成することができる。

【0034】

所望のテーパー角θを得るには、ICPエッチング装置のバイアスパワー密度を調節す

る。図27は、テーパー角θのバイアスパワー依存性を示した図である。図27に示した

ように、バイアスパワー密度に応じてテーパー角θを制御することができる。図27は、

ガラス基板上に所定のパターンに形成されたW(タングステン)膜について、そのパター

ン端部のテーパー形状(テーパー角)について調べた結果を示す。図27はテーパー角の

基板側にかけるバイアス電力(13.56MHz)依存性を示す。共通条件として放電電力

(コイルに印加する高周波電力、13.56MHz)を3.2W/cm2、圧力1.0Paとして

エッチングガスにCF4とCl2を用いた。エッチングガスの流量はCF4、Cl2共に30

SCCMとした。

【0035】

図27に示すようにテーパー角はバイアス電力が128〜384mW/cm2の範囲で70〜

20°まで変化させることが可能であることが明らかとなった。なお、CF4、Cl2の流

量は共に30SCCMとした。

【0036】

また、図28の実験からはテーパー角は60〜80°まで変化させることが可能であ流

ことが分かる。なお、図28の実験条件では、テーパー角のエッチングガス流量比依存性

について調べた結果を示す。なお、CF4とCl2の合計の流量を60SCCMとして、CF4

のみを20〜40SCCMの範囲で変化させた。このときバイアス電力は128mW/cm2とした

。

【0037】

更にテーパー角θはタングステンとレジストのエッチングの選択比に依存していると考

えられる。図29にタングステンとレジストの選択比とテーパー角θとの依存性を示した

。このようにICPエッチング装置を用いて、バイアスパワー密度や反応ガス流量比を適

宜決定することで、極めて容易に所望のテーパー角θが3°〜60°の配線を形成するこ

とが可能である。

【0038】

また、耐熱性導電性材料のICPエッチング装置における加工特性を考える。

ここでは、W(タングステン)膜とTa(タンタル)膜の他に、ゲート電極用の材料とし

てしばしば用いられるモリブデンータングステン(Mo−W)合金(組成比はMo:W=

48:50wt%)について、エッチング速度、適用するエッチングガス、およびゲート電

極の下地となるゲート絶縁膜との選択比の代表的な値を示す。ゲート絶縁膜はプラズマC

VD法で作製する酸化シリコン膜または酸化窒化シリコン膜であり、ここで選択比はゲー

ト絶縁膜のエッチング速度に対するそれぞれの材料のエッチング速度の割合として定義す

る。

【0039】

【表1】

【0040】

Ta膜はエッチング速度が140〜160nm/minであり、ゲート絶縁膜とのエッチング

の選択比が6〜8である。この値はW膜のエッチング速度が70〜90nm/minの範囲でゲ

ート絶縁膜との選択比が2〜4というよりも優れた値となっている。従って、被加工性と

いう観点からはTa膜も適しているが、表中に示さない値として、Ta膜は抵抗率が20

〜30μΩcmであり、W膜の10〜16μΩcmに比べて若干高い点が難点となる。

一方、Mo−W合金はエッチング速度が40〜60nm/minと遅く、またゲート絶縁膜に

対するエッチングの選択比は0.1〜2となり、この材料は被加工性という観点から必ず

しも適していないことが覗われる。このように、表1からはTa膜が最も良い結果を示し

ていることがわかるが、前述のように抵抗率を考慮するとW膜が総合的には適していると

考えられる。

【0041】

また、ドライエッチングに用いるエッチングガスとしてフッ素を含むガスと、塩素を含

むガスの混合ガスを用いることができる。フッ素を含むガスとしてはCF4、C2F6、ま

たはC4F8から選ばれたガスを用いることができる。また塩素を含むガスとしてはCl2

Cl2、SiCl4ガス、BCl4から選ばれたガスを用いることができる。

【実施例1】

【0042】

本実施例は、アクティブマトリクス型液晶パネルに関するものである。図1(A)は本

実施例のアクティブマトリクス基板の上面図であり、画素部、画素部の薄膜トランジスタ

を駆動するための駆動回路部とが形成されている。アクティブマトリクス基板上に作製さ

れた柱状スペーサおよびシール剤の位置関係を示す上面図である。

【0043】

図1(A)に示すように、ガラス基板101上には、薄膜トランジスタが配置された画

素部188と、画素部188に配置された薄膜トランジスタを駆動するための駆動回路と

して、走査信号駆動回路185と映像信号制御回路184が設けられている。さらに、そ

の他CPUやメモリなどの信号処理回路187が設けられている。

【0044】

画素部188では走査信号駆動回路185から延在するゲート配線189と映像信号制

御回路184から延在するソース配線190がマトリクス状に交差して画素を形成し、各

画素にはそれぞれ画素TFT204と保持容量205が設けられている。

【0045】

柱状スペーサ172はアクティブマトリクス基板と、対向基板の間隔を保持するもので

あって、樹脂でなる円柱状の構造物である。画素部188において設けられる柱状スペー

サ172は、すべての画素に対して設けても良いが、マトリクス状に配列した画素の数個

から数十個おきに設けても良い。即ち、画素部を構成する画素の全数に対するスペーサの

数の割合は20〜100%とすると良い。また、各回路184、185、187には柱状

スペーサ172の代わりに、樹脂を回路全面を覆うように設けても良い。本実施例では、

TFTのソースおよびドレイン配線の位置にあわせて、円柱状のスペーサを設けている。

【0046】

シール剤186は、基板101上の画素部188および走査信号制御回路185、映像

信号制御回路184、その他の信号処理回路187の外側であって、外部入出力端子18

2よりも内側に形成されている。

【0047】

また、アクティブマトリクス基板100上の回路184、185、187は接続配線1

83によって、外部の電源や回路に電気的に接続されている。また接続配線183は回路

184、185、187のTFTのソース(ドレイン)配線と同時に形成されている。端

子部182は接続配線183と一体的に形成され、他の基板上の配線との接続部になる。

図1(B)に端子部182の部分拡大図を示す。

【0048】

図1(B)に示すように、端子部182の側面は保護膜174によって覆われており、

接続配線183は端子部182において、異方性導電膜によってFPC191の配線19

1bと電気的に接続されている。191aはFPC191が設けられている基板を指す。

【0049】

図2はアクティブマトリクス基板100の回路のブロック図である。映像信号制御回路

184は、シフトレジスタ回路501a、レベルシフタ回路502a、バッファ回路50

3a、サンプリング回路504を備えている。また、走査信号駆動回路185は、シフト

レジスタ回路501b、レベルシフタ回路502b、バッファ回路503bを備えている

。

【0050】

シフトレジスタ回路501a、501bは駆動電圧が5〜16V(代表的には10V)

であり、この回路を形成するCMOS回路はTFTは、図6に示すの第1のpチャネル型

TFT200と第1のnチャネル型TFT201で形成する。

また、レベルシフタ回路502a、502bやバッファ回路503a、503bは駆動電

圧が14〜16Vと高くなるがシフトレジスタ回路と同様なTFTを用いれば良い。また

、これらの回路において、ゲートをマルチゲート構造で形成すると耐圧が高まり、回路の

信頼性を向上させる上で有効である。

【0051】

サンプリング回路504はアナログスイッチから成り、駆動電圧が14〜16Vである

が、極性が交互に反転して駆動される上、オフ電流値を低減させる必要があるため、図6

で示す第2のpチャネル型TFT202と第2のnチャネル型TFT203で形成するこ

とが望ましい。この回路において、pチャネル型TFT202のオフ電流値が問題となる

ときは、実施例2で示す工程で作製した、オフセット領域を設けたシングルドレイン構造

のTFTで作製すると良い。

【0052】

また、画素部は駆動電圧が14〜16Vであり、低消費電力化の観点からサンプリング

回路よりもさらにオフ電流値を低減することが要求され、図6で示す画素TFT204の

ようにマルチゲート構造とし、さらにLDD領域を設けた構造とするのが望ましい。

【0053】

なお、画素部188と駆動回路185、186のブロック構成のみを示したが、後述す

るTFTの工程に従えば、その他にも信号分割回路、分周波回路、D/Aコンバータ、γ

補正回路、オペアンプ回路、さらにメモリ回路や演算処理回路などの信号処理回路187

、さらに論理回路を同一基板上に形成することが可能である。このように、本発明は同一

基板上に画素部とその駆動回路とを含む半導体装置、例えば信号制御回路および画素部を

具備した液晶表示装置を実現することができる。

【0054】

以下、アクティブマトリクス基板の作製工程を説明する。図3〜図7は画素部188、

駆動回路の作製工程を示す断面図であり、図9〜図11は接続配線183の端子部182

の作製工程を示す図である。これら図面において同じ符号は同じ構成要素を示している。

【0055】

基板101にはコーニング社の#7059ガラスや#1737ガラスなどに代表される

バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板の他に、ポリエ

チレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテル

サルフォン(PES)など光学的異方性を有しないプラスチック基板を用いることができ

る。ガラス基板を用いる場合には、ガラス歪み点よりも10〜20℃程度低い温度であら

かじめ熱処理しておいても良い。そして、基板101のTFTを形成する表面に、基板1

01からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シ

リコン膜などの下地膜102を形成する。例えば、プラズマCVD法でSiH4、NH3、

N2Oから作製される酸化窒化シリコン膜102aを10〜200nm(好ましくは50〜

100nm)、同様にSiH4、N2Oから作製される酸化窒化水素化シリコン膜102bを

50〜200nm(好ましくは100〜150nm)の厚さに積層形成する(図3(A))

。

【0056】

酸化窒化シリコン膜は従来の平行平板型のプラズマCVD法を用いて形成する。酸化窒

化シリコン膜102aは、SiH4を10SCCM、NH3を100SCCM、N2Oを20SCCMと

して反応室に導入し、基板温度325℃、反応圧力40Pa、放電電力密度0.41W/cm2

、放電周波数60MHzとした。一方、酸化窒化水素化シリコン膜102bは、SiH4を5

SCCM、N2Oを120SCCM、H2を125SCCMとして反応室に導入し、基板温度400℃、

反応圧力20Pa、放電電力密度0.41W/cm2、放電周波数60MHzとした。これらの膜は

、基板温度を変化させ、反応ガスの切替えのみで連続して形成することもできる。

【0057】

このようにして作製した酸化窒化シリコン膜102aは、密度が9.28×1022/cm3

であり、フッ化水素アンモニウム(NH4HF2)を7.13%とフッ化アンモニウム(N

H4F)を15.4%含む混合溶液(ステラケミファ社製、商品名LAL500)の20

℃におけるエッチング速度が約63nm/minと遅く、緻密で硬い膜である。このような膜を

下地膜に用いると、この上に形成する半導体膜にガラス基板からのアルカリ金属元素が拡

散するのを防ぐのに有効である。

【0058】

次に、25〜80nm(好ましくは30〜60nm)の厚さで非晶質構造を有する半導

体膜103aを、プラズマCVD法やスパッタ法などの公知の方法で形成する。例えば、

プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成する。非晶質構造を有する

半導体膜には、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜

などの非晶質構造を有する化合物半導体膜を適用しても良い。また、下地膜102と非晶

質半導体膜103aとは両者を連続形成することも可能である。例えば、前述のように酸

化窒化シリコン膜102aと酸化窒化水素化シリコン膜102bをプラズマCVD法で連

続して成膜後、反応ガスをSiH4、N2O、H2からSiH4とH2或いはSiH4のみに切

り替えれば、一旦大気雰囲気に晒すことなく連続形成できる。その結果、酸化窒化水素化

シリコン膜102bの表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツ

キやしきい値電圧の変動を低減させることができる。

【0059】

そして、結晶化の工程を行い非晶質半導体膜103aから結晶質半導体膜103bを作

製する。その方法としてレーザーアニール法や熱アニール法(固相成長法)、またはラピ

ットサーマルアニール法(RTA法)を適用することができる。前述のようなガラス基板

や耐熱性の劣るプラスチック基板を用いる場合には、特にレーザーアニール法を適用する

ことが好ましい。RTA法では、赤外線ランプ、ハロゲンランプ、メタルハライドランプ

、キセノンランプなどを光源に用いる。或いは特開平7−130652号公報で開示され

た技術に従って、触媒元素を用いる結晶化法で結晶質半導体膜103bを形成することも

できる。結晶化の工程ではまず、非晶質半導体膜が含有する水素を放出させておくことが

好ましく、400〜500℃で1時間程度の熱処理を行い含有する水素量を5atom%以下

にしてから結晶化させると膜表面の荒れを防ぐことができるので良い。

【0060】

結晶化をレーザーアニール法にて行う場合には、パルス発振型または連続発光型のエキ

シマレーザーやアルゴンレーザーをその光源とする。パルス発振型のエキシマレーザーを

用いる場合には、レーザー光を線状に加工してレーザーアニールを行う。レーザーアニー

ル条件は実施者が適宣選択するものであるが、例えば、レーザーパルス発振周波数30H

zとし、レーザーエネルギー密度を100〜500mJ/cm2(代表的には300〜400mJ/

cm2)とする。そして線状ビームを基板全面に渡って照射し、この時の線状ビームの重ね合

わせ率(オーバーラップ率)を80〜98%として行う。このようにして図3(B)に示

すように結晶質半導体膜103bを得ることができる。

【0061】

そして、結晶質半導体膜103b上にフォトリソグラフィーの技術によって、フォトマ

スクPM1を用いてレジストパターンを形成し、ドライエッチングによって結晶質半導体

膜を島状に分割し、島状半導体膜104〜108を形成しする。ドライエッチングにはC

F4とO2の混合ガスを用いる。

【0062】

島状半導体膜に対し、TFTのしきい値電圧(Vth)を制御する目的でp型を付与する

不純物元素を1×1016〜5×1017atoms/cm3程度の濃度で島状半導体膜の全面に添加

しても良い。半導体に対してp型を付与する不純物元素には、ホウ素(B)、アルミニウ

ム(Al)、ガリウム(Ga)など周期律表第13族の元素が知られている。その方法と

して、イオン注入法やイオンドープ法を用いることができるが、大面積基板を処理するに

はイオンドープ法が適している。イオンドープ法ではジボラン(B2H6)をソースガスと

して用いホウ素(B)を添加する。このような不純物元素の注入は必ずしも必要でなく省

略しても差し支えないが、特にnチャネル型TFTのしきい値電圧を所定の範囲内に収め

るために好適に用いる手法である。

【0063】

ゲート絶縁膜109はプラズマCVD法またはスパッタ法を用い、膜厚を40〜150

nmとしてシリコンを含む絶縁膜で形成する。例えば、120nmの厚さで酸化窒化シリ

コン膜から形成すると良い。また、SiH4とN2OにO2を添加させて作製された酸化窒

化シリコン膜は、膜中の固定電荷密度が低減されているのでこの用途に対して好ましい材

料となる。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく

、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い(図3(C))。

【0064】

図3(D)に示すように、ゲート絶縁膜109上にゲート配線を形成するための導電膜

を形成する。導電膜は単層で形成しても良いが、必要に応じて二層あるいは三層といった

複数の層から成る積層構造としても良い。例えば、2層の場合には、上層に、タンタル(

Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)等の元素を主成分と

する金属膜やこれら元素の合金膜(代表的にはMo−W合金膜、Mo−Ta合金膜)で形

成し、下層は窒化タンタル(TaN)、窒化タングステン(WN)、窒化チタン(TiN

)膜、窒化モリブデン(MoN)などで形成する。例えば、2層の場合、上層に下層の導

電膜の窒化物で形成すればよく、下層/上層としてWN膜/W膜や、TaN膜/Ta膜膜

等とすればよい。また、3層の場合は、TaN膜/Ta膜/TaN膜とすればよい。2層

目の(上層の)導電膜は抵抗率を10〜50μΩcmの範囲ですることが好ましい。低抵抗

化を図るために含有する不純物濃度を低減させることが好ましく、特に酸素濃度に関して

は30ppm以下とすると良かった。例えば、タングステン(W)は酸素濃度を30pp

m以下とすることで20μΩcm以下の比抵抗値を実現することができた。

【0065】

また、配線抵抗の低抵抗化には、アルミニウムを主成分とする膜を用いるのが好ましい

。この場合、アルミニウムにSiやSc等を微量添加して耐熱性を高めるとよい。例えば

、ゲート配線を構成する導電膜として、Ti膜/Scを添加したAl膜や、Ti膜/Ti

N膜/Scを添加したAl膜を形成すればよい。

【0066】

W膜を成膜する場合には、Wをターゲットとしたスパッタ法で、アルゴン(Ar)ガス

と窒素(N2)ガスを導入して導電膜111を窒化タングステン(WN)で50nmの厚さ

に形成し、導電膜110をWで250nmの厚さに形成する。その他の方法として、W膜は

6フッ化タングステン(WF6)を用いて熱CVD法で形成することもできる。いずれに

してもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は2

0μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図

ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵

抗化する。このことより、スパッタ法による場合、純度99.9999%のWターゲット

を用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成

することにより、抵抗率9〜20μΩcmを実現することができる。

【0067】

TaN膜、Ta膜は同様にスパッタ法で形成することが可能である。TaN膜はTaを

ターゲットとしてスパッタガスにArと窒素との混合ガスを用いて形成し、Ta膜はスパ

ッタガスにArを用いる。また、これらのスパッタガス中に適量のXeやKrを加えてお

くと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。α相のTa膜

の抵抗率は20μΩcm程度でありゲート電極に使用することができるが、β相のTa膜の

抵抗率は180μΩcm程度でありゲート電極とするには不向きであった。TaN膜はα相

に近い結晶構造を持つので、この上にTa膜を形成すればα相のTa膜が容易に得られた

。本実施例では、ゲート配線を構成する導電膜として、下層の導電膜110としてTaN

膜を上層の導電膜111としてTa膜を成膜する。

【0068】

またゲート配線を構成する導電膜とゲート絶縁膜109の間に2〜20nm程度の厚さ

でリン(P)をドープしたシリコン膜を形成しておくことは有効である。これにより、そ

の上に形成される導電膜の密着性向上と酸化防止を図ると同時に、導電膜が微量に含有す

るアルカリ金属元素がゲート絶縁膜109に拡散するのを防ぐことができる。

【0069】

次に、フォトリソグラフィーの技術によって、フォトマスクPM2を用いてレジストマ

スクRM1 〜RM6 を形成し、導電膜110と導電膜111とを一括でエッチングしてゲート

配線118〜122と容量配線123を形成する。ゲート配線118〜122と容量配線

123は導電膜から成る118a〜122aと、導電膜から成る118b〜122bとが

一体として形成されている(図4(A))。

【0070】

そして、nチャネル型TFTにLDD領域を形成するために、n型を付与する不純物元

素添加の工程(n-ドープ工程)を行った。ここではゲート配線118〜122をマスク

として自己整合的にn型を付与する不純物元素をイオンドープ法で添加した。n型を付与

する不純物元素として添加するリン(P)を1×1016〜5×1019atoms/cm3の濃度範

囲で添加する。このようにして、図4(B)

に示すように島状半導体膜に低濃度n型不純物領域124〜129を形成する。

【0071】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する高

濃度n型不純物領域の形成を行った(n+ドープ工程)。まず、フォトマスクPM3を用

い、レジストのマスクRM8 〜RM12を形成し、n型を付与する不純物元素を添加して高濃度

n型不純物領域130〜135を形成した。n型を付与する不純物元素にはリン(P)を

用い、その濃度が1×1020〜1×1021atoms/cm3の濃度範囲となるようにフォスフィ

ン(PH3)を用いたイオンドープ法で行った(図4(C))。

【0072】

そして、pチャネル型TFTを形成する島状半導体膜104、106にソース領域およ

びドレイン領域とする高濃度p型不純物領域136、137を形成する。ここでは、ゲー

ト配線118、120をマスクとしてp型を付与する不純物元素を添加し、自己整合的に

高濃度p型不純物領域を形成する。

【0073】

この工程では、nチャネル型TFTを形成する島状半導体膜105、107、108は

、フォトマスクPM4を用いてレジストマスクRM13〜RM15を形成し全面を被覆しておく。

高濃度p型不純物領域136、137はジボラン(B2H6)を用いたイオンドープ法で形

成する。この領域のボロン(B)濃度は3×1020〜3×1021atoms/cm3となるように

する(図4(D))。

【0074】

高濃度p型不純物領域136、137には、前工程においてリン(P)が添加されてい

て、高濃度p型不純物領域136a、137aには1×1020〜1×1021atoms/cm3の

濃度で、高濃度p型不純物領域136b、137bには1×1016〜5×1019atoms/c

m3の濃度で含有しているが、この工程で添加するボロン(B)の濃度を1.5から3倍と

なるようにすることにより、pチャネル型TFTのソース領域およびドレイン領域として

機能する上で何ら問題はなかった。

【0075】

その後、図5(A)に示すように、ゲート配線およびゲート絶縁膜109上から保護絶

縁膜138を形成する。保護絶縁膜138は酸化シリコン膜、酸化窒化シリコン膜、窒化

シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。いずれにしても保護

絶縁膜138は無機絶縁物材料から形成する。保護絶縁膜138の膜厚は100〜200

nmとする。ここで、酸化シリコン膜を用いる場合には、プラズマCVD法で、オルトケ

イ酸テトラエチル(Tetraethyl Orthosilicate:TEOS)とO2 とを混合し、反応圧力

40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0

.8W/cm2で放電させて形成することができる。

【0076】

酸化窒化シリコン膜を用いる場合には、プラズマCVD法でSiH4、N2 O、NH3

から作製される酸化窒化シリコン膜、またはSiH4、N2 Oから作製される酸化窒化シ

リコン膜で形成すれば良い。この場合の作製条件は反応圧力20〜200Pa、基板温度3

00〜400℃とし、高周波(60MHz)電力密度0.1〜1.0W/cm2で形成することが

できる。また、SiH4 、N2 O、H2から作製される酸化窒化水素化シリコン膜を適用

しても良い。窒化シリコン膜も同様にプラズマCVD法でSiH4、NH3から作製するこ

とが可能である。

【0077】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化す

る工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に

、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用すること

ができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒

素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施

例では550℃で4時間の熱処理を行った。また、基板101に耐熱温度が低いプラスチ

ック基板を用いる場合にはレーザーアニール法を適用することが好ましい(図5(B))

。

【0078】

活性化の工程の後、さらに、3〜100%の水素を含む雰囲気中で、300〜450℃

で1〜12時間の熱処理を行い、島状半導体膜を水素化する工程を行った。この工程は熱

的に励起された水素により島状半導体膜にある1016〜1018/cm3のダングリングボンド

を終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起

された水素を用いる)を行っても良い。

【0079】

活性化および水素化の工程が終了したら、有機絶縁物材料からなる層間絶縁膜139を

1.0〜2.0μmの平均厚を有して形成する。有機樹脂材料としては、ポリイミド、ア

クリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用するこ

とができる。例えば、基板に塗布後、熱重合するタイプのポリイミドを用いる場合には、

クリーンオーブンで300℃で焼成して形成する。また、アクリルを用いる場合には、2

液性のものを用い、主材と硬化剤を混合した後、スピナーを用いて基板全面に塗布した後

、ホットプレートで80℃で60秒の予備加熱を行い、さらにクリーンオーブンで250

℃で60分焼成して形成することができる。(図5(C))

【0080】

このように、層間絶縁膜139を有機絶縁物材料で形成することにより、表面を良好に

平坦化させることができる。また、有機樹脂材料は一般に誘電率が低いので、寄生容量を

低減するできる。しかし、吸湿性があり保護膜としては適さないので、本実施例のように

、保護絶縁膜138として形成した酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン

膜などと組み合わせて用いる必要がある。

【0081】

その後、フォトマスクPM5を用い、所定のパターンのレジストマスクを形成し、それ

ぞれの島状半導体膜に形成されたソース領域またはドレイン領域に達するコンタクトホー

ルを絶縁膜138、139に形成する。更に、端子部182の絶縁膜138、139を除

去する。コンタクトホールの形成はドライエッチング法により行う。この場合、エッチン

グガスにCF4、O2、Heの混合ガスを用い有機樹脂材料から成る層間絶縁膜139をま

ずエッチングし、その後、続いてエッチングガスをCF4、O2として保護絶縁膜138を

エッチングする。さらに、島状半導体膜との選択比を高めるために、エッチングガスをC

HF3に切り替えてゲート絶縁膜をエッチングすることにより、良好にコンタクトホール

を形成することができる。

【0082】

そして、ソース/ドレイン配線及び接続配線183を形成する金属膜140と透明導電

膜141の積層膜を形成する。ここでは、金属膜140としてTi膜を50〜150nmの

厚さで形成し、島状半導体膜のソースまたはドレイン領域を形成する半導体膜とコンタク

トを形成し、そのTi膜上に重ねてアルミニウム(Al)を300〜400nmの厚さでス

パッタ法で形成する。また、金属膜140として、Ti膜/TiN膜/Al膜でなる積層

膜を成膜してもよい。

【0083】

透明導電膜の材料は、酸化インジウム(In2O3)や酸化インジウム酸化スズ合金(I

n2O3―SnO2;ITO)などをスパッタ法や真空蒸着法などを用いて形成して用いる

ことができる。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特

にITOのエッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸

化インジウム酸化亜鉛合金(In2O3―ZnO)を用いても良い。酸化インジウム酸化亜

鉛合金は表面平滑性に優れ、ITOに対して熱安定性にも優れているので、ドレイン配線

169の端面で接触するAlとの腐蝕反応を防止できる。同様に、酸化亜鉛(ZnO)も

適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添

加した酸化亜鉛(ZnO:Ga)などを用いることができる。本実施例では透明導電膜1

41として酸化インジウム酸化亜鉛合金を形成する。(図6(A))

【0084】

図9に図6(A)に対応する接続配線183の端子部182部分の構造を示す。(A)

は配線の長尺方向に垂直な断面に対応し、(B)は長尺方向に沿った断面図に対応し、T

FTとの構造と積層関係が明らかになるようにした。(C)は上面図である。図10、図

11も同様である。

【0085】

フォトマスクPM6によりレジストマスクパターンを形成し、エッチングによってソー

ス配線148〜152とドレイン配線153〜158を形成する。及び、図10に示すよ

うに接続配線183を形成する。ここで、ドレイン配線157は画素電極として機能する

ものである。(図6(B)、図10)。

【0086】

この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られた。例

えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理

を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。また、この

ような熱処理により保護絶縁膜138や、下地膜102にに存在する水素を島状半導体膜

104〜108に拡散させ水素化をすることもできる。いずれにしても、島状半導体膜1

04〜108中の欠陥密度を1016/cm3以下とすることが望ましく、そのために水素を0

.01〜0.1atomic%程度付与すれば良かった。

【0087】

こうして6枚のフォトマスクにより、同一の基板上に、駆動回路のTFTと画素部の画

素TFTとを有した基板を完成させることができる。駆動回路には第1のpチャネル型T

FT200、第1のnチャネル型TFT201、第2のpチャネル型TFT202、第2

のnチャネル型TFT203、画素部には画素TFT204、保持容量205が形成され

ている。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0088】

駆動回路の第1のpチャネル型TFT200には、島状半導体膜104にチャネル形成

領域206、高濃度p型不純物領域から成るソース領域207a、207b、ドレイン領

域208a,208bを有したシングルドレインの構造を有している。

【0089】

第1のnチャネル型TFT201の島状半導体膜105には、チャネル形成領域209

、ゲート電極119と重ならないLDD領域210、ソース領域212、ドレイン領域2

11が形成されている。LDD領域210のチャネル長方向の長さは1.0〜4.0μm

、好ましくは2.0〜3.0μmとした。nチャネル型TFTにおけるLDD領域の長さ

をこのようにすることにより、ドレイン領域近傍に発生する高電界を緩和して、ホットキ

ャリアの発生を防ぎ、TFTの劣化を防止することができる。

【0090】

サンプリング回路の第2のpチャネル型TFT202の島状半導体膜106には、チャ

ネル形成領域213、高濃度p型不純物領域から成るソース領域214a、214b、ド

レイン領域215a、215bが形成され、シングルドレインの構造となっている。

【0091】

第2のnチャネル型TFT203には、島状半導体膜107にチャネル形成領域216

、LDD領域217、218、ソース領域220、ドレイン領域219が形成されている

。LDD領域217、218の長さは1.0〜4.0μmとする。

【0092】

画素TFT204には、島状半導体膜108にチャネル形成領域221、222、LD

D領域223〜225、ソースまたはドレイン領域226〜228を有している。LDD

領域のチャネル長方向の長さは0.5〜4.0μm、好ましくは1.5〜2.5μmであ

る。更に画素TFT204には保持容量が接続されている。保持容量205は、ゲート絶

縁膜209を誘電体にし、容量配線123と画素TFT204のドレイン領域228に接

続する半導体膜229を電極にするコンデンサーである。図6(B)では画素TFT20

4をダブルゲート構造としたが、シングルゲート構造でも良いし、複数のゲート電極を設

けたマルチゲート構造としても差し支えない。

【0093】

図13は画素部のほぼ一画素分を示す上面図である。図中に示すA−A'断面が図6(

B)に示す画素部の断面図に対応している。画素TFT204は、ゲート配線を兼ねるゲ

ート電極122は、図示されていないゲート絶縁膜を介してその下の島状半導体膜108

と交差している。図示はしていないが、島状半導体膜108には、ソース領域、ドレイン

領域、LDD領域が形成されている。また、256はソース配線152とソース領域22

6とのコンタクト部、257はドレイン配線157とドレイン領域228とのコンタクト

部である。保持容量205は、画素TFT204のドレイン領域228から延在する半導

体膜229とゲート絶縁膜を介して容量配線123が重なる領域で形成されている。この

構成において半導体膜229には、価電子制御を目的とした不純物元素は添加されていな

い。

【0094】

以上の様な構成は、画素TFTおよび駆動回路が要求する仕様に応じて各回路を構成す

るTFTの構造を最適化し、半導体装置の動作性能と信頼性を向上させることを可能とし

ている。さらにゲート電極を耐熱性を有する導電性材料で形成することによりLDD領域

やソース領域およびドレイン領域の活性化を容易としている。

【0095】

更に本実施例では、図7に示すように、上述した工程を経たアクティブマトリクス基板

からに柱状スペーサ172を形成する。同時に、柱状スペーサ172を作製すると共に、

接続配線183の端子部182の側面を保護する保護膜174を形成する。柱状スペーサ

172の材料に限定はないが、例えば、JSR社製のNN700を用い、スピナーで塗布

した後、露光と現像処理によって所定のパターンに形成する。さらにクリーンオーブンな

どで150〜200℃で加熱して硬化させる。

【0096】

このようにして作製されるスペーサは露光と現像処理の条件によって形状を異ならせる

ことができるが、好ましくは、図14で示すように、柱状スペーサ172の形状は柱状で

頂部が平坦な形状となるようにすると、対向側の基板を合わせたときに液晶表示パネルと

しての機械的な強度を確保することができる。形状は円錐状、角錐状など特別の限定はな

いが、例えば円錐状としたときに具体的には、高さHを1.2〜5μmとし、平均半径L

1を5〜7μm、平均半径L1と底部の半径L2との比を1対1.5とする。このとき側

面のテーパー角は±15°以下とする。

【0097】

スペーサの配置は任意に決定すれば良いが、好ましくは、図7に示すように、画素部1

88においてはドレイン配線157(画素電極)のコンタクト部251と重ねてその部分

を覆うように柱状スペーサ172を形成すると良い。コンタクト部251は平坦性が損な

われこの部分では液晶がうまく配向しなくなるので、このようにしてコンタクト部251

にスペーサ用の樹脂を充填する形で柱状スペーサ172を形成することで、ディスクリネ

ーションなどを防止することができる。

【0098】

図11に示すように、柱状スペーサ172の作製過程で、接続配線183の側面を保護

する保護膜174が形成される。保護膜174は端子部182において、透明導電膜14

1の表面だけを露出するように形成される。保護膜174の形状は露光と現像処理の条件

によって決定できる。この構成により、接続配線183の端子部182において、金属膜

140は保護膜174、ゲート絶縁膜109、及び透明導電膜141接して、覆われるた

め、外気に曝されることがない。

【0099】

その後、基板101の表面に配向膜173を形成する。端子部182には配向膜173

は形成されない。通常液晶表示素子の配向膜にはポリイミド樹脂が用いられる。配向膜1

73を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配

向するようにした。画素部に設けた柱状スペーサ172の端部からラビング方向に対して

ラビングされない領域が2μm以下となるようにした。また、ラビング処理では静電気の

発生がしばしば問題となるが、駆動回路のTFT上にもスペーサ172を形成しておくと

、スペーサとしての本来の役割と、静電気からTFTを保護する効果を得ることができる

。

【0100】

以上により、基板間隔を保持する柱状スペーサ172が基板101と一体化したアクテ

ィブマトリクス基板が完成する。なお、配向膜173を形成した後、柱状スペーサ172

を形成した構成とすることもできる。(図7、図11)

【0101】

アクティブマトリクス基板と対になる対向基板には、図8に示すように、基板251上

に遮光膜252、図示しないカラーフィルター、透明導電膜253および配向膜254が

形成されている。遮光膜252はTi、Cr、Alなどを150〜300nmの厚さで形成

する。

【0102】

そして、図8に示すように画素部と駆動回路が形成されたアクティブマトリクス基板と

対向基板とをシール剤179で貼り合わせる。シール剤179にはフィラーが混入されて

いて、このフィラーと柱状スペーサ172によって均一な間隔を持って2枚の基板が貼り

合わせられる。そして、基板の隙間に液晶材料260を注入し、封止剤(図示せず)によ

って完全に封止して、液晶パネルが完成する。

【0103】

更に、アクティブマトリクス基板100上の回路を映像信号を入力するための回路や、

電力を供給するための電源等に接続するため、図12に示すように、端子部182におい

て、接続配線183とFPC191を異方性導電膜195によって電気的に接続する。図

12(A)は端子部182の配線の長尺方向と垂直な面の断面図であり、図12(B)は

長尺方向に沿った断面である。

【0104】

図12に示すように異方性導電膜195は接着剤195a内に金やクロムなどでメッキ

された数十〜数百μm粒子195bにより構成され、この粒子195bが接続配線183

とFPCの配線191bとに接触することにより、アクティブマトリクス基板100とF

PC191電気的に接続することができる。FPC191は基板101との接着強度を高

めるために、外端子部182の外側にはみだしており、端部には樹脂層192が設けられ

、機械的強度を高めている。

【実施例2】

【0105】

実施例1では、接続配線183をTFTのソース/ドレイン配線と同じ作製工程で作製

したが、本実施例では、ゲート配線と同じ工程で接続配線183を作製するとする。図1

5を用いて、本実施例を説明する。TFTの作製工程は実施例1を用いる。図15におい

て、図3〜図8と同じ符号は同じ構成要素をさす。

【0106】

まず、実施例1の作製工程に従って、図9(C)の工程までを行う。次に、ゲート配線

を構成する導電膜301と透明導電膜302の積層膜を成膜する。導電膜301は実施例

1述べたゲート配線を構成する導電膜110や111の材料を用いればよい。また透明導

電膜302としては、TFTのソース/ドレイン配線の表面に形成された透明導電膜14

1と同じ材料を用いることができる。ここでは、導電膜301として、WN膜/W膜の積

層膜をスパッタ法で成膜し、透明導電膜としてITO膜を成膜する(図15(A))。

【0107】

そして、図4(A)に示すようにレジストマスクを形成し、導電膜301と透明導電膜

302をエッチングして、TFTのゲート配線及び図15(B)に示すように接続配線3

04を形成する。Wを主成分とする材料で形成されている場合には、高速でかつ精度良く

エッチングを実施するために高密度プラズマを用いたドライエッチング法を適用すること

が望ましい。

【0108】

高密度プラズマを得る手法の一つとして、誘導結合プラズマ(Inductively Coupled Pl

asma:ICP)エッチング装置を用いると良い。ICPエッチング装置を用いたWのエッ

チング法は、エッチングガスにCF4とCl2の2種のガスを反応室に導入し、圧力0.5

〜1.5Pa(好ましくは1Pa)とし、誘導結合部に200〜1000Wの高周波(1

3.56MHz)電力を印加する。この時、基板が置かれたステージには20Wの高周波

電力が印加され、自己バイアスで負電位に帯電することにより、正イオンが加速されて異

方性のエッチングを行うことができる。ICPエッチング装置を使用することにより、W

などの硬い金属膜も2〜5nm/秒のエッチング速度を得ることができる。また、残渣を残

すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増しオ

ーバーエッチングをすると良い。

【0109】

しかし、この時に下地とのエッチングの選択比に注意する必要がある。例えば、W膜に

対する酸化窒化シリコン膜(ゲート絶縁膜109)の選択比は2.5〜3であるので、こ

のようなオーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50

nm程度エッチングされて実質的に薄くなる。

【0110】

そして、実施例1で説明したようにTFTの半導体膜にリン、ボロンを添加し、図5(

A)に示すように保護絶縁膜138を形成し、半導体膜に添加したリン、ボロンを活性化

する(図15(C))。

【0111】

そして、図5(C)に示すように層間絶縁膜139を形成する。層間絶縁膜139の材

料は実施例1で説明したた材料を選択すればよく、シリコン系の無機絶縁膜でもよいし、

アクリル等の有機樹脂膜でもよい(図15(D))。

【0112】

次に、図6に示すように、保護絶縁膜138に層間絶縁膜139に島状半導体膜に形成

されたソース領域またはドレイン領域に達するコンタクトホールを形成すると同時に、接

続配線304の端子部において、端子部の側面を覆う保護膜304を形成する(図15(

E))。

【0113】

以降の工程は実施例1と同様に実施して、アクティブマトリクス基板100を完成する

。そして、アクティブマトリクス基板100と対向基板250をシール剤179によって

貼り合わせ液晶材料260を封入し、接続配線304とFPC191を異方性導電膜19

5によって電気的に接続する(図15(F))。

【0114】

本実施例では、保護膜304によって、接続配線304の導電膜301の側面を覆って

いるため、導電膜301は保護膜304、ゲート絶縁膜109、透明導電膜302でくる

まれた構造となり、外気に曝されることがない。

【実施例3】

【0115】

本実施例は実施例1の変形例であり、ゲート配線の断面形状がテーパ状になるようにし

たものであり、また、接続配線をゲート配線と同じ作製工程で作製するようにした例であ

る。図17〜図19を用いて本実施例のアクティブマトリクス基板の作製工程を説明する

。ここでは、画素部の画素TFTおよび保持容量と、画素部の周辺に設けられる駆動回路

のTFTを同時に作製する方法について工程に従って詳細に説明する。図21に接続配線

の作製工程を示す。

【0116】

図17(A)において、ガラス基板601表面に、酸化シリコン膜、窒化シリコン膜ま

たは酸化窒化シリコン膜などの絶縁膜から成る下地膜602を形成する。本実施例では、

プラズマCVD法でSiH4、NH3、N2Oから成膜される酸化窒化シリコン膜を10〜

200nmし、酸化窒化シリコン膜表面にSiH4、N2Oから成膜される酸化窒化水素化シ

リコン膜602を50〜200nm(好ましくは100〜150nm)の厚さに積層形成す

る。

【0117】

次に、プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成し、実施例1と同

様に結晶化して、結晶質シリコン膜を形成する。そしてフォトマスクPM11を用いて、

フォトリソグラフィーの技術により、結晶質シリコン膜上にレジストパターンを形成し、

ドライエッチングによって結晶質半導体膜を島状に分割し、島状半導体膜604〜608

を形成する。結晶質シリコン膜のドライエッチングにはCF4とO2の混合ガスを用いる。

次に、ゲート絶縁膜609はプラズマCVD法で120nmの厚さで酸化窒化シリコン膜

から形成する。

【0118】

そして、ゲート絶縁膜609上にゲート配線を形成するために金属膜611、612と

透明導電膜613の積層膜を耐熱性導電膜を形成する。金属膜611をWN膜で、金属膜

膜612をW膜で形成し、透明導電膜613に酸化インジウム酸化亜鉛合金(In2O3―

ZnO)を成膜する(図17(A)、図21(A))

。

【0119】

第2のフォトマスクPM12を用い、フォトリソグラフィーの技術を使用してレジスト

マスクRM21〜RM27を形成し、透明導電膜613をエッチングして、ゲート配線618〜6

22と容量配線623、接続配線683の最上層618a〜623a、683aを形成す

る。(図17(B)、図21(B))

【0120】

透明導電膜でなる最上層618a〜623a、683aの側面は図18(B)

、図21(B)に示すように、レジストマスクRM21〜RM27よりも後退するようにエッチン

グされる。次に、 金属膜611、613を一括でエッチングして、テーパー状の断面を

有するゲート配線618〜6、22、容量配線623及び接続配線683が完成する。(

図17(C)、図21(C))

【0121】

配線618〜623、683は、透明導電膜613でなる層618a〜623a、68

3aと、金属膜612でなる層618b〜623b、683bと、金属膜611でなる層

618c〜623c、683cが積層された構造となる。

【0122】

このとき少なくともゲート配線618〜622の端部にテーパー部が形成されるように

エッチングする。このエッチング加工はICPエッチング装置により行う。エッチングガ

スにCF4とCl2の混合ガスを用いその流量をそれぞれ30SCCMとして、放電電力3.2

mW/cm2(13.56MHz)、バイアス電力224mW/cm2(13.56MHz)、圧力1.0Paでエッチング

を行った。このようなエッチング条件によって、ゲート配線618〜622の端部におい

て、該端部から内側にむかって徐々に厚さが増加するテーパー部が形成され、その角度は

25〜35°、好ましくは30°となる。テーパー部の角度は、後にLDD領域を形成す

る低濃度n型不純物領域の濃度勾配に大きく影響する。尚、テーパー部の角度θ1は、テ

ーパー部の長さ(WG)とテーパー部の厚さ(HG)を用いてTan(θ1)=HG/W

Gで表される。

【0123】

また、残渣を残すことなくエッチングするためには、絶縁膜609の厚さの10〜20

%程度の割合でオーバーエッチングする。しかし、この時に下地とのエッチングの選択比

に注意する必要がある。例えば、W膜に対する酸化窒化シリコン膜(ゲート絶縁膜609

)の選択比は表1で示したように2〜4(代表的には3)であるので、このようなオーバ

ーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチン

グされて実質的に薄くなり、新たな形状のゲート絶縁膜610が形成された。

【0124】

そして、画素TFTおよび駆動回路のnチャネル型TFTのLDD領域を形成するため

に、n型を付与する不純物元素添加の工程(n-ドープ工程)を行う。

ゲート電極の形成に用いたレジストマスク112〜117をそのまま残し、端部にテーパ

ー部を有するゲート配線618〜622をマスクとして自己整合的にn型を付与する不純

物元素としてリンをイオンドープ法で添加する(図18(A)

)。

【0125】

ここでは、n型を付与する不純物元素を配線618〜623のテーパー部とゲート絶縁

膜610とを通して、その下に位置する半導体膜に達するように添加するために、加速電

圧を高く80〜160keVとし、LDD領域を形成するためにドーズ量を低く、1×1

013〜5×1014atoms/cm2とする。半導体膜に添加される不純物の濃度は1×1016〜

1×1019atoms/cm3の濃度範囲で添加する。このようにして、図18(A)に示すよう

に島状半導体膜に低濃度n型不純物領域624〜629を形成する。

【0126】

この工程において、低濃度n型不純物領域624〜628において、少なくともゲート

配線618〜622に重なった部分に含まれるリン(P)の濃度勾配は、ゲート配線61

8〜622のテーパー部の膜厚変化を反映する。即ち、低濃度n型不純物領域624〜6

28へ添加されるリン(P)の濃度は、ゲート配線に重なる領域において、ゲート配線の

側面に向かって徐々に濃度が高くなる。これはテーパー部の膜厚の差によって、半導体膜

に達するリン(P)の濃度が変化するためである。尚、図18(A)では低濃度n型不純

物領域624〜628を斜めに図示しているが、これはリン(P)が添加された領域を直

接的に示しているのではなく、上述のようにリンの濃度変化がゲート配線618〜622

のテーパー部の形状に沿って変化していることを表している。

【0127】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する高

濃度n型不純物領域の形成を行った(n+ドープ工程)。レジストマスクRM21〜RM26を残

し、今度はゲート配線618〜622がリン(P)を遮蔽するマスクとなるように、イオ

ンドープ法において10〜30keVの低加速電圧の条件で添加する。このようにして高

濃度n型不純物領域630〜635を形成する。これら領域630〜635を覆うゲート

絶縁膜610は、ゲート配線の形成工程においてオーバーエッチングされたため、当初の

膜厚である120nmから薄くなり、70〜100nmとなっている。そのためこのような低

加速電圧の条件でも良好にリン(P)を添加することができる。そして、これら領域63

0〜635のリン(P)の濃度は1×1020〜1×1021atoms/cm3の範囲となるように

する(図18(B))。

【0128】

そして、pチャネル型TFTを形成する島状半導体膜604、606にソース領域およ

びドレイン領域とする高濃度p型不純物領域636、637を形成する。ここでは、ゲー

ト配線618、120をマスクとしてp型を付与する不純物元素を添加し、自己整合的に

高濃度p型不純物領域636、637を形成する。このとき、nチャネル型TFTを形成

する島状半導体膜605、107、108は、第3のフォトマスクPM23を用いてレジスト

マスクRM29〜RM31を形成し全面を被覆しておく(図18(C))。

【0129】

ここで形成される不純物領域636、637はジボラン(B2H6)を用いたイオンドー

プ法で形成する。そして、ゲート配線と重ならない高濃度p型不純物領域のボロン(B)

濃度が3×1020〜3×1021atoms/cm3となるようにする。

また、ゲート配線と重なる不純物領域にもゲート絶縁膜とゲート電極のテーパー部を介し

て不純物元素が添加されるので、実質的に低濃度p型不純物領域として形成され、少なく

とも1.5×1019atoms/cm3以上の濃度とし、ボロン(B)

の濃度を図18(A)の工程で添加されたリン(P)濃度の1.5から3倍となるように

することにより、pチャネル型TFTのソース領域およびドレイン領域として機能するた

めに何ら問題は生じない。

【0130】

その後、図19(A)、図21(D)に示すように、酸化窒化シリコンでなる保護絶縁

膜638を形成する。酸化窒化シリコン膜はプラズマCVD法でSiH4、N2O、NH3

から成膜する。その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元

素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行

う。

活性化の工程に続いて、雰囲気ガスを変化させ、3〜100%の水素を含む雰囲気中で

、300〜450℃で1〜12時間の熱処理を行い、島状半導体膜を水素化する工程を行

う。この工程は熱的に励起された水素により島状半導体膜にある1016〜1018/cm3のダ

ングリングボンドを終端する工程である。

【0131】

活性化および水素化の工程が終了したら、有機絶縁物材料からなる層間絶縁膜639を

平均の厚さが1.0〜2.0μmとなるように形成する(図19(B)

、図21(E))。

【0132】

その後、第4のフォトマスクPM24を用い、所定のパターンのレジストマスクを形成し、

それぞれの島状半導体膜に形成されたソース領域またはドレイン領域に達するコンタクト

ホール及び、図21(E)に示すように接続配線683の側面を覆う保護膜673を形成

する。

【0133】

この工程はドライエッチング法により行う。この場合、エッチングガスにCF4、O2、

Heの混合ガスを用い有機樹脂材料から成る層間絶縁膜639をまずエッチングし、その

後、続いてエッチングガスをCF4、O2として保護絶縁膜638をエッチングする。さら

に、島状半導体膜との選択比を高めるために、エッチングガスをCHF3に切り替えてゲ

ート絶縁膜610をエッチングすることにより、良好にコンタクトホールを形成すること

ができる。

【0134】

図21(E)に示すように、保護膜673によって接続配線683の側面を覆うことに

より、接続配線683の金属膜でなる層683c、683bの表面は透明導電膜でなる層

683aとゲート絶縁膜610と保護膜673に接した状態で囲まれるため、外気に曝さ

れることがない。

【0135】

そして、Ti膜(50〜150nm)/Al膜(300〜400nm)を積層した金属膜と

、金属膜表面に透明導電膜を80〜120nmの厚さで形成し、形成図19(C)に示すよ

うに、金属膜をスパッタ法や真空蒸着法で形成し、第5のフォトマスクPM25によりレジス

トマスクパターンを形成し、金属膜と透明導電膜をエッチングして、ソース配線648〜

652とドレイン配線653〜657を形成する。ここで、ドレイン配線657は画素電

極として機能するものである。ドレイン配線658は隣の画素に属する画素電極を表して

いる。

【0136】

駆動回路の第1のpチャネル型TFT700には、島状半導体膜604にチャネル形成

領域706、高濃度p型不純物領域から成るソース領域707、ドレイン領域708が形

成されている。領域707、708において、ゲート電極と重なる領域はボロン濃度が低

いLDD領域となっている。

【0137】

第1のnチャネル型TFT701には、島状半導体膜605にチャネル形成領域709

、低濃度n型不純物領域で形成されゲート配線と重なるLDD領域、710、711、高

濃度n型不純物領域で形成するソース領域713、ドレイン領域712を有している。

【0138】

このLDD領域におけるリン(P)の濃度分布はチャネル形成領域709から遠ざかる