コントローラ

【課題】2種類のレギュレータを使用しなくても、電圧の切り換え時にオーバシュートおよびアンダーシュートを発生しないようにすることができるコントローラを提供する。

【解決手段】レギュレータ30−1〜30−nは、CPU25に電源電圧を供給する。SVIDインタフェース14は、外部から複数の電圧レギュレータ30−1〜30−nのうち動作させる台数の変更指令を受ける。位相クロック生成部21は、現在の台数から指示された変更後の台数へ段階的に動作させる電圧レギュレータの台数を変更する。

【解決手段】レギュレータ30−1〜30−nは、CPU25に電源電圧を供給する。SVIDインタフェース14は、外部から複数の電圧レギュレータ30−1〜30−nのうち動作させる台数の変更指令を受ける。位相クロック生成部21は、現在の台数から指示された変更後の台数へ段階的に動作させる電圧レギュレータの台数を変更する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コントローラに関し、特に、CPU(Central Processing Unit)などの半導体装置の電源を制御するためのコントローラに関する。

【背景技術】

【0002】

電源電圧切り替え動作時に発生するオーバーシュート/アンダーシュートを低減し、かつ電圧切り替えスピードを高速化することができる電源装置が知られている。

【0003】

たとえば、特許文献1(特開2007−288974号公報)の電源装置は、出力電圧を上げる過渡状態には、スイッチングレギュレータ400用のレジスタであるDCDC用レジスタのDAC値DD1を、シリーズレギュレータ300用のレジスタであるLDO用レジスタ201のDAC値LD01に代えてLDO用DAC302に供給し、シリーズレギュレータ300のLDO用DAC302は、DCDC用レジスタ202のDAC値DD1を参照してDAC動作を行う。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−288974号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1の装置は、電圧変更時の応答性と効率を両立することを目的としており、電圧の切り換え時のオーバシュートおよびアンダーシュートを防ぐために、切り換え時に応答速度の速いLDOと、電力効率の高いDCDCとを両方動作させて、両者の設定電圧を工夫することで、電流駆動の割合の最適化を行なっている。

【0006】

しかしながら、特許文献1の装置では、LDOとDCDCの2種類のレギュレータが必要となる。

【0007】

それゆえに、本発明の目的は、2種類のレギュレータを使用しなくても、電圧の切り換え時にオーバシュートおよびアンダーシュートを発生しないようにすることができるコントローラを提供することである。

【課題を解決するための手段】

【0008】

本発明の一実施形態のコントローラは、第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、現在の台数から指示された変更後の台数へ段階的に動作させる電圧レギュレータの台数を変更する制御部とを備える。

【発明の効果】

【0009】

本発明の一実施形態によれば、2種類のレギュレータを使用しなくても、電圧の切り換え時にオーバシュートおよびアンダーシュートを発生しないようにすることができる。

【図面の簡単な説明】

【0010】

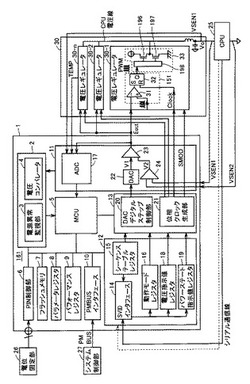

【図1】第1の実施形態の半導体システムの構成を表わす図である。

【図2】第1の実施形態の電圧制御動作の処理手順を表わすフローチャートである。

【図3】第1の実施形態のフェーズ数の制御手順を表わす図である。

【図4】第1の実施形態の段階的スケジュールテーブルの例を表わす図である。

【図5】現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化を説明するための図である。

【図6】第1の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【図7】第2の実施形態の半導体システムの構成を表わす図である。

【図8】第2の実施形態におけるフェーズ数の変更時の目標電圧の制御手順を表わす図である。

【図9】第2の実施形態の段階的スケジュールテーブルの例を表わす図である。

【図10】現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化および目標電圧を説明するための図である。

【図11】第2の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【図12】第2の実施形態の変形例における制御内容を説明するための図である。

【図13】第3の実施形態の半導体システムの構成を表わす図である。

【図14】第3の実施形態におけるフェーズ数の変更時の増幅率の変更手順を表わす図である。

【図15】第3の実施形態の段階的スケジュールテーブルの例を表わす図である。

【図16】現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合の増幅率の変化を説明するための図である。

【図17】第3の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態について図面を参照して説明する。

[第1の実施形態]

図1は、第1の実施形態の半導体システムの構成を表わす図である。

【0012】

図1を参照して、この半導体システムは、コントローラ1と、レギュレータ群30と、CPU25とを備える。

【0013】

レギュレータ群30は、コントローラ1と、CPU25の制御によって、電圧VoをCPU25へ供給する。レギュレータ群30は、電圧レギュレータ30−1〜30−nを備える。

【0014】

コントローラ1は、ここでは1チップ(1つの半導体チップ)で構成されている。

コントローラ1は、PIN制御部6と、フラッシュメモリ7と、パラメータレジスタ8と、パフォーマンスレジスタ9と、MCU5と、PMBUS(Power Management Bus)インタフェース10と、SVID(Serial VID)コマンド判定回路12と、ハードロジック電源制御回路13と、アナログ電源制御回路11と、電源異常監視回路2とを備える。

【0015】

コントローラ1の構成要素のうち、MCU5と、ハードロジック電源制御回路13と、アナログ電源制御回路11と、電源異常監視回路2とで、制御部161を構成する。

【0016】

SVIDコマンド判定回路12は、SVIDインタフェース14と、動作モードレジスタ16と、電圧指示値レジスタ18と、パワーステート指示値レジスタ19とを備える。

【0017】

CPU25は、ここでは、1チップで構成され、電圧レギュレータ30−1〜30−nから出力される電源電圧を受けて、様々な処理を行なう。また、CPU25は、SVIDインタフェース14を通じて、コントローラ1に指示を送る。たとえば、CPU25は、必要な電力量に応じて、動作させる電圧レギュレータの変更を指示する制御信号をSVIDインタフェース14を通じて、コントローラ1に送る。

【0018】

PIN制御部6は、外部の電位固定部26によって固定された端子の電位に従って、外部端子がどのように設定されたかを表わす設定情報をMCU5に出力する。

【0019】

フラッシュメモリ7は、MCU5が処理を行なうためのプログラムを格納する。プログラムを用いることによって、電源規格の変更があっても、デバイスを再開発する手間を省くことができる。また、フラッシュメモリ7は、最大許容電圧値、最大許容温度、および最大許容電流などの初期値を定めた複数のパラメータのテーブルを記憶する。

【0020】

パラメータレジスタ8は、SVIDインタフェース14を通じて、デジタルステップ制御でのステップごとの電圧値の変化量(刻み電圧)、および放電モードでの下げたい最終電圧である指示電圧と放電モードを指示電圧に達する前に放電モードを終了するときの目標電圧Vsとの差であるΔVの値などを記憶する。

【0021】

パフォーマンスレジスタ9は、フラッシュメモリ7に記録された最大許容電圧値、最大許容温度、および最大許容電流などのデータ受け取り、記憶する。

【0022】

ここで、最大許容電圧値は、CPUにかけることが可能な最大の電源電圧である。最大許容温度は、電圧レギュレータなどから測定される温度で動作上許される最高の温度である。最大許容電流は、電圧レギュレータが流すことができる最大の電流である。これらの値を超えた場合は、コントローラは値を下げるように電圧レギュレータなどに指示信号を出力する。

【0023】

MCU5は、プログラムに基づいて演算処理を行なう。

PMBUSインタフェース10は、PMBUSを通じて、外部のシステム制御部27から信号を受けるとともに、外部のシステム制御部27へ信号を出力する。

【0024】

SVIDインタフェース14は、シリアル通信線を通じて、CPU25からの信号を受けるとともに、CPU25へ信号を出力する。

【0025】

動作モードレジスタ16は、現在の動作モードを記憶する。たとえば、動作モードとして、通常モード、放電モードなどがある。

【0026】

電圧指示値レジスタ18は、電圧制御時の指示電圧の値を記憶する。

パワーステート指示値レジスタ19は、パワーステート制御時のパワーステートモードの指定値を記憶する。

【0027】

シーケンステーブルレジスタ15は、段階的スケジュールテーブルを記憶する。段階的スケジュールテーブルは、変更前のフェーズ数と、変更後のフェーズ数の組合せごとに、複数のステップの各々のフェーズ数、実行時間を定める。ここで、フェーズ数とは、動作させる電圧レギュレータの数である。

【0028】

ハードロジック電源制御回路13は、DACデジタルステップ制御部20と、位相クロック生成部21とを備える。

【0029】

DACデジタルステップ制御部20は、複数回のステップで指示された電圧に達するように、各ステップでの電圧変化値を決定し、決定した電圧変化値をデジタル電圧DVとして出力する。

【0030】

位相クロック生成部21は、動作させる電圧レギュレータへの制御信号SMODを活性化する。位相クロック生成部21は、動作させる電圧レギュレータへの位相クロックの位相を決定し、決定した位相の位相クロックを出力する。位相クロック生成部21は、内部のタイマに従って、PWM(Pulse Width Modulation)周期のタイミングで位相クロックを生成する。電圧レギュレータの位相クロックの周期は、すべて同一(PWM周期)であるが、電圧レギュレータの位相クロックの位相は、すべて異なる。位相クロック生成部21は、停止させる電圧レギュレータへの制御信号SMODを非活性化する。

【0031】

位相クロック生成部21は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けた場合に、シーケンステーブルレジスタ内の段階的スケジュールテーブルに従って、現在のフェーズ数からCPU25から指示された変更後のフェーズ数へ段階的にフェーズ数を変更する。位相クロック生成部25は、段階的スケジュールテーブルで定められる各ステップの実行時間に従って、ステップを切替える。

【0032】

アナログ電源制御回路11は、DAC(Digital Analog Converter)22と、差動アンプ24と、エラーアンプ23と、ADC(Analog Digital Converter)17とを備える。

【0033】

DAC22は、DACデジタルステップ制御部20から出力されたデジタル電圧DVをアナログ電圧V1に変換する。

【0034】

差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する。

【0035】

エラーアンプ23は、DAC22から出力される電圧V1と、差動アンプ24から出力される電圧V2との差を増幅して、増幅された電圧を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。

【0036】

ADC17は、電圧レギュレータ30−1〜30−nの出力電圧などをAD変換する。

電源異常監視回路2は、電圧コンパレータ4と、電源異常監視部3とを備える。

【0037】

電圧コンパレータ4は、電圧レギュレータにより生成された電圧を受け、所定の標準電圧とをアナログ処理で比較する。

【0038】

電源異常監視部3は、電圧コンパレータ4の出力に従って、CPU25の電源電圧が異常であるか否かを監視する。

【0039】

電圧レギュレータ30−1〜30−nは、CPU25に電源電圧を供給する。ここでは、各電圧レギュレータ30−1〜30−nはそれぞれ、1つのパッケージに収められている。さらにここでは、パッケージ内にハイサイドMOSトランジスタ196、ロウサイドMOSトランジスタ197、その他の部分(PWM部151とMOS制御部198)の3チップで構成されている。

【0040】

電圧レギュレータ30−1〜30−nは、PWM部151と、DC−DC変換器33とを備える。電圧レギュレータ30−1〜30−nは、制御信号SMODが活性化されると動作し、制御信号SMODが非活性化されると動作を停止する。

【0041】

PWM部151は、PWM比較器31と、ラッチ回路32とを備える。

PWM比較器31は、エラーアンプ23の出力である誤差信号をもとにPWM信号を出力する。

【0042】

ラッチ回路32のセット端子Sには、PWM比較器31の出力が入力される。ラッチ回路32のリセット端子Rには、位相クロック生成部21の出力であるクロックが入力される。

【0043】

DC−DC変換器33は、ラッチ回路32の出力と接続され、CPU25へ電源電圧を供給する。ここでは、ラッチ回路32から出力されるPWM信号によりDC−DC変換器33が制御される。

【0044】

図1に示すハイサイドMOSトランジスタ196がオンし、ロウサイドMOSトランジスタ197がオフすることで、CPU25の高電位側のCPU電圧線の電圧VSEN1が上昇する。他方、ハイサイドMOSトランジスタ196がオフし、ロウサイドMOSトランジスタ197がオンすることで、CPU電圧線の電圧VSEN1が降下する。

【0045】

通常モードでは、CPU電圧線の電圧VSEN1が一定の電圧になるように、ハイサイドMOSトランジスタ196とロウサイドMOSトランジスタ197のオン/オフが制御される。つまり、電圧が低い場合はハイサイドMOSトランジスタ196をオンさせて(このときロウサイドMOSトランジスタ197をオフ)電圧を上昇させたり、電圧が高い場合はロウサイドMOSトランジスタ197をオンさせて(このときハイサイドMOSトランジスタ196をオフ)電圧を降下させる。

【0046】

(電源制御動作)

図2は、第1の実施形態の電圧制御動作の処理手順を表わすフローチャートである。

【0047】

図2を参照して、CPU25は、電圧値Vtを指定した電圧制御コマンドをシリアル通信線へ出力する(ステップS801)。

【0048】

SVIDインタフェース14は、シリアル通信線から受信したコマンドを解釈し、電圧制御をDACデジタルステップ制御部20に指示する(ステップS802)。

【0049】

DACデジタルステップ制御部20は、指示された通常指示電圧Vtを目標値とし、この目標値に達するための、デジタル電圧DVを出力する(ステップS803)。

【0050】

DAC22は、デジタル電圧DVをアナログ電圧V1に変換する(ステップS804)。

【0051】

差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する(ステップS805)。

【0052】

エラーアンプ23は、DAC22から出力される電圧V1と、差動アンプ24から出力される電圧V2との差を増幅して、増幅された電圧(Eout)を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。電圧レギュレータは、エラーアンプ23から出力される電圧(Eout)に基づいて、出力する電圧を補正する。たとえば、指示電圧Vtより高電位側の電圧VSEN1が低い場合は、ハイサイドMOSトランジスタ196がオンすることで、高電位側の電圧VSEN1を上昇させる。また、指示電圧Vtより高電位側の電圧VSEN1が高い場合は、ロウサイドMOSトランジスタ197がオンすることで、高電位側の電圧VSEN1を降下させる(ステップS806)。

【0053】

その後、ステップS803に戻り、処理が繰返される。

これにより、高電位側の電圧VSEN1が指示電圧Vtになるように制御される。

【0054】

(フェーズ数の制御動作)

図3は、第1の実施形態のフェーズ数の制御手順を表わす図である。

【0055】

まず、CPU25は、複数の電圧レギュレータのうち動作させる台数(フェーズ数)の変更を指示する制御コマンドをシリアル通信線へ出力する(ステップS901)。

【0056】

SVIDインタフェース14は、シリアル通信線から受信した制御コマンドを解釈し、フェーズ数制御を位相クロック生成部21に指示する(ステップS902)。

【0057】

位相クロック生成部21は、シーケンステーブルレジスタから、指示されたフェーズ数と現在のフェーズ数に対応する段階的スケジュールテーブルを得る(ステップS903)。

【0058】

位相クロック生成部21は、段階的スケジュールテーブルに従って、フェーズ数を変化させる。位相クロック生成部21は、各段階でのフェーズ数に従って、電圧レギュレータ30−1〜30−nのうち動作させる電圧レギュレータと、停止させる電圧レギュレータとを決める。フェーズ数を変化させる場合には、可能な限り、位相クロックが均等となるように決定する。たとえば、8個の電圧レギュレータから8個の位相クロックが出力されているときには、フェーズ数を4個に変更する場合には、変更の結果、出力される4個の位相クロックの間隔が均等になるように、動作させる電圧レギュレータと停止させる電圧レギュレータとを決定する。位相クロック生成部21は、動作させる電圧レギュレータ対し制御信号SMODを活性化し、動作させる電圧レギュレータへ決定された位相のクロックを出力する。電圧レギュレータは、活性化された制御信号SMODを受けると、位相クロック生成部21から送られるクロックに基づいて、電圧を出力する。位相クロック生成部21は、停止させる電圧レギュレータに対し制御信号SMODを非活性化する。電圧レギュレータは、非活性化された制御信号SMODを受けると、電圧の出力を停止する(ステップS904)。

【0059】

図4は、第1の実施形態の段階的スケジュールテーブルの例を表わす図である。

図4の一例では、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合には、4段階でフェーズを変化させるように定められている。ステップ1において、実行時間ΔT(1)内にフェーズ数が+i(1)だけ増加するように定められている。ステップ2において、実行時間ΔT(2)内にフェーズ数が+i(2)だけ増加するように定められている。ステップ3において、実行時間ΔT(3)内にフェーズ数が+i(3)だけ増加するように定められている。ステップ4において、実行時間ΔT(4)内にフェーズ数が+i(4)だけ増加するように定められている。

【0060】

図4の別の例では、現在のフェーズ数Kが16であり、変更後のフェーズ数Mが2の場合には、6段階でフェーズを変化させるように定められている。ステップ1において、実行時間ΔT(1)内にフェーズ数が+i(1)だけ増加するように定められている。ステップ2において、実行時間ΔT(2)内にフェーズ数が+i(2)だけ増加するように定められている。ステップ3において、実行時間ΔT(3)内にフェーズ数が+i(3)だけ増加するように定められている。ステップ4において、実行時間ΔT(4)内にフェーズ数が+i(4)だけ増加するように定められている。ステップ5において、実行時間ΔT(5)内にフェーズ数が+i(5)だけ増加するように定められている。ステップ6において、実行時間ΔT(6)内にフェーズ数が+i(6)だけ増加するように定められている。

【0061】

図5は、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化を説明するための図である。ここでは、i(1)=0、i(2)=−4、i(3)=−2、i(4)=−1であるとして説明する。

【0062】

まず、ステップ1で、フェーズ数がK+i(1)(つまり8)となる。ステップ2で、フェーズ数がK+i(1)+i(2)(つまり4)となる。ステップ3で、フェーズ数がK+i(1)+i(2)+i(3)(つまり2)となる。ステップ4で、フェーズ数がK+i(1)+i(2)+i(3)+i(4)(つまり1)となる。

【0063】

図6は、第1の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【0064】

図6に示すように、従来のように、フェーズ数を8から1に急激に変化させた場合には、出力電圧(Vo)が急激に変化し、アンダーシュートが発生する。

【0065】

本実施の形態のように、フェーズ数を8→4→2→1と段階的に変化された場合には、出力電圧(Vo)が緩やかに変化し、アンダーシュートが発生しない。

【0066】

以上のように、本実施の形態によれば、フェーズ数を徐々に変化させることにより、アンダーシュートが発生するのを防止できる。

【0067】

また、本実施の形態によれば、フェーズ数を間引く場合に、レギュレータ群30から出力される複数個の位相クロックの間隔が均等になるように、動作させる電圧レギュレータと停止させる電圧レギュレータとを決定するので、電圧を安定化させることができる。

【0068】

また、段階的スケジュールの設定をレジスタとして持たせておくことにより、電圧安定を優先するか、短期間切替えを優先するか、状況に応じて設定を変更することもできる。たとえば、負荷状態の変更を直ちに行いたい場合、フェーズ数の切替えは速やかに行う必要があるので、フェーズ数を8から1へ直接変更することも可能である。

【0069】

また、本実施の形態によれば、ボード設計終了後に発見された電圧変動があった場合にでも、IC外部のフィルタ回路の再調整を必要とせずファームウエアの変更のみで対処が可能となる。

【0070】

なお、PWM周期の途中で、フェーズ数を間引いた場合、電圧レギュレータのスイッチングバランスが乱れ、電圧が安定しにくくなるような場合には、各ステップの実行時間(すなわち、ステップの切替タイミング)をPWM周期のタイミングに同期させることも可能である。また、複数のステップのうち、一部のステップの切替タイミングをPWM周期に同期させ、他のステップの切替タイミングは、段階的スケジュールテーブルに設定されたものを用いることとしてもよい。

【0071】

[第2の実施形態]

図7は、第2の実施形態の半導体システムの構成を表わす図である。

【0072】

図7を参照して、この半導体システムが、図1の第1の実施形態の半導体システムと相違する点は、以下のコントローラ1Aに関する点である。

【0073】

SVIDコマンド判定回路12Aにおけるシーケンステーブルレジスタ115は、段階的スケジュールテーブルを記憶する。段階的スケジュールテーブルは、変更前のフェーズ数と、変更後のフェーズ数の組合せごとに、複数のステップの各々のオフセット電圧、実行時間を定める。ここで、オフセット電圧とは、CPU25からの指示電圧から目標電圧を設定するために用いられる。

【0074】

ハードロジック電源制御回路13Aにおける位相クロック生成部121は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けた場合に、現在のフェーズ数からCPU25から指示された変更後のフェーズ数へ変更する。

【0075】

ハードロジック電源制御回路13AにおけるDACデジタルステップ制御部120は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けないときには、第1の実施形態で説明したように、指示電圧を目標電圧とし、CPU25に与えられる電圧が目標電圧となるように制御する。

【0076】

DACデジタルステップ制御部120は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、シーケンステーブルレジスタ115内の段階的スケジュールテーブルで定められるスケジュールに従って、指示電圧に段階的にオフセット電圧を加えることによって段階的に目標電圧を変更し、各段階でCPU25に与えられる電圧が目標電圧となるように制御する。DACデジタルステップ制御部120は、段階的スケジュールテーブルで定められる各ステップの実行時間に従って、ステップを切替える。

【0077】

(電源制御動作)

図8は、第2の実施形態におけるフェーズ数の変更時の目標電圧の制御手順を表わす図である。

【0078】

まず、CPU25は、フェーズ数を指定した制御コマンドをシリアル通信線へ出力する(ステップS301)。

【0079】

SVIDインタフェース14は、シリアル通信線から受信した制御コマンドを解釈し、フェーズ数制御をDACデジタルステップ制御部120に指示する(ステップS302)。

【0080】

DACデジタルステップ制御部120は、シーケンステーブルレジスタから、指示されたフェーズ数と現在のフェーズ数に対応する段階的変更スケジュールを得る(ステップS303)。

【0081】

DACデジタルステップ制御部120は、段階的変更スケジュールに従って、オフセット電圧を加えることによって目標値を変化させて(ステップS304)、デジタル電圧DVを出力する(ステップS305)。

【0082】

DAC22は、デジタル電圧DVをアナログ電圧V1に変換する(ステップS306)

。差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する(ステップS307)。

【0083】

エラーアンプ23は、DAC22から出力される電圧V1と、差動アンプ24から出力される電圧V2との差を増幅して、増幅された電圧(Eout)を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。電圧レギュレータは、エラーアンプ23から出力される電圧(Eout)に基づいて、出力する電圧を補正する。たとえば、指示電圧Vtより高電位側の電圧VSEN1が低い場合は、ハイサイドMOSトランジスタ196がオンすることで、高電位側の電圧VSEN1を上昇させる。また、指示電圧Vtより高電位側の電圧VSEN1が高い場合は、ロウサイドMOSトランジスタ197がオンすることで、高電位側の電圧VSEN1を降下させる(ステップS308)。

【0084】

その後、ステップS304に戻り、処理が繰返される。

図9は、第2の実施形態の段階的スケジュールテーブルの例を表わす図である。

【0085】

図9の一例では、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合には、6段階でフェーズを変化させるように定められている。実行時間ΔT(1)のステップ1において、フェーズ数がKを維持し、目標値が指示電圧Vtよりも+dv(1)だけ増加するように定められている。実行時間ΔT(2)のステップ2において、フェーズ数がKを維持し、目標値がさらに+dv(2)だけ増加するように定められている。実行時間ΔT(3)のステップ3において、フェーズ数がMに変化し、目標値がさらに+dv(3)だけ増加するように定められている。実行時間ΔT(4)のステップ4において、フェーズ数がMを維持し、目標値がさらに+dv(4)だけ増加するように定められている。実行時間ΔT(5)のステップ5において、フェーズ数がMを維持し、目標値がさらに+dv(5)だけ増加するように定められている。実行時間ΔT(6)のステップ6において、フェーズ数がMを維持し、目標値がさらに+dv(6)だけ増加するように定められている。

【0086】

図10は、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化および目標電圧を説明するための図である。ここでは、dv(1)=+20mv、dv(2)=+5mv、dv(3)=0mv、dv(4)=−5mv、dv(5)=−20mv、dv(6)=0mvであるとして説明する。

【0087】

まず、ステップ1で、フェーズ数がKを維持し、目標値がVt+dv(1)となる。

ステップ2で、フェーズ数がKを維持し、目標値がVt+dv(1)+dv(2)となる。ステップ3で、フェーズ数がMに変化し、目標値がVt+dv(1)+dv(2)+dv(3)となる。ステップ4で、フェーズ数がMを維持し、目標値がVt+dv(1)+dv(2)+dv(3)+dv(4)となる。ステップ5で、フェーズ数がMに変化し、目標値がVt+dv(1)+dv(2)+dv(3)+dv(4)+dv(5)となる。

ステップ6で、フェーズ数がMを維持し、目標値がVt+dv(1)+dv(2)+dv(3)+dv(4)+dv(5)+dv(6)となる。

【0088】

図11は、第2の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【0089】

図11に示すように、従来のように、フェーズ数を変化させるときに、指示電圧にオフセット電圧を加えない場合には、出力電圧(Vo)が急激に変化し、アンダーシュートが発生する。

【0090】

本実施の形態のように、フェーズ数を変化させるときに、指示電圧にオフセット電圧を段階的に加えた場合には、出力電圧(Vo)が緩やかに変化し、アンダーシュートが発生しない。

【0091】

以上のように、本実施の形態によれば、フェーズ切替え前に、目標電圧をオフセット(上昇)させ、フェーズ切替えが終了したのち、目標電圧のオフセットを解除(下降)することによって、アンダーシュートを相殺するができる。

【0092】

また、PWM周期の途中で、ステップを切替えた場合、電圧レギュレータのスイッチングバランスが乱れ、電圧が安定しにくくなるようなときには、各ステップの実行時間(すなわち、ステップの切替タイミング)をPWM周期のタイミングに同期させることも可能である。また、複数のステップのうち、一部のステップ(フェーズ数が切替るステップおよび/またはオフセット電圧が切替るステップ)の切替タイミングをPWM周期に同期させ、他のステップの切替タイミングは、段階的スケジュールテーブルに設定されたものを用いることとしてもよい。

【0093】

また、本実施の形態によれば、ボード設計終了後に発見された電圧変動があった場合にでも、IC外部のフィルタ回路の再調整を必要とせずファームウエアの変更のみで対処が可能となる。

【0094】

[第2の実施形態の変形例]

本変形例では、PWM周期ごとに発生するPWM周期割込み(位相クロック生成部内のタイマで生成する)のタイミングに基づいて、フェーズ数を切替る。

【0095】

図12は、第2の実施形態の変形例における制御内容を説明するための図である。

第2の実施形態で説明したように、フェーズ数を3から1に変更する際に、ステップ1〜ステップ6で段階的にオフセット電圧が変更される。

【0096】

まず、ステップ1で、フェーズ数が1を維持し、指示電圧Vtに20mvのオフセット電圧を加えた電圧が目標電圧となる。

【0097】

ステップ2で、フェーズ数が1を維持し、5mv増加したオフセット電圧を加えた電圧が目標電圧となる。

【0098】

ステップ3で、フェーズ数が3に変化し、オフセット電圧は増加されない。

ステップ4で、フェーズ数が3を維持し、5mv減少させたオフセット電圧を加えた電圧が目標電圧となる。

【0099】

ステップ5で、フェーズ数が3を維持し、20mv減少させたオフセット電圧を加えた電圧が目標電圧となる。

【0100】

ステップ6で、フェーズ数が3を維持し、オフセット電圧は増加されない。

フェーズ数の変更指令を受けたときに、内部ステータスがPS0からPS1へ変化し、PS1へ変化した時点から段階的スケジュールテーブルで定められた時間“8h05”が経過した時点でステップ1が開始する。

【0101】

ステップ1の開始から段階的スケジュールテーブルで定められた時間“8h30”が経過した時点でステップ1が終了し、ステップ2が開始する。

【0102】

PWM周期割込みが発生したときに、ステップ2が終了し、ステップ3が開始する。

ステップ3の開始から段階的スケジュールテーブルで定められた時間“8h40”が経過した時点でステップ3が終了し、ステップ4が開始する。

【0103】

ステップ4の開始から段階的スケジュールテーブルで定められた時間“8h10”が経過した時点でステップ4が終了し、ステップ5が開始する。

【0104】

ステップ5の開始から段階的スケジュールテーブルで定められた時間“8h16”が経過した時点でステップ5が終了し、ステップ6が開始する。

【0105】

[第3の実施形態]

図13は、第3の実施形態の半導体システムの構成を表わす図である。

【0106】

図13を参照して、この半導体システムが、図1の第1の実施形態の半導体システムと相違する点は、以下のコントローラ1Bに関する点である。

【0107】

SVIDコマンド判定回路12Bにおけるシーケンステーブルレジスタ215は、段階的スケジュールテーブルを記憶する。段階的スケジュールテーブルは、変更前のフェーズ数と、変更後のフェーズ数の組合せごとに、複数のステップの各々の増幅率、実行時間を定める。ここで、増幅率とは、差動アンプ24から出力される電圧V2を増幅する可変アンプ224の増幅率である。

【0108】

ハードロジック電源制御回路13Bにおける位相クロック生成部121は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けた場合に、現在のフェーズ数からCPU25から指示された変更後のフェーズ数へ変更する。

【0109】

ハードロジック電源制御回路13BにおけるDACデジタルステップ制御部220は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けないときには、DAC222を通じて、可変アンプ224の増幅率を「1」に設定させる(つまり、増幅しない)。これによって、CPU25に与えられている電圧と指示電圧との差に対応する電圧が電圧レギュレータに与えられる。

【0110】

DACデジタルステップ制御部220は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、シーケンステーブルレジスタ115内の段階的スケジュールテーブルで定められるスケジュールに従って、段階的に可変アンプ224の増幅率を変更する。これによって、各段階で、CPU25に与えられている電圧を各段階の増幅率で増幅した電圧と指示電圧との差に対応する電圧が電圧レギュレータに与えられる。

【0111】

DACデジタルステップ制御部220は、段階的スケジュールテーブルで定められる各ステップの実行時間に従って、ステップを切替える。

【0112】

DAC22は、DACデジタルステップ制御部20から出力されたデジタル電圧DVをアナログ電圧V1に変換する。差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する。可変アンプ224は、差動アンプ24から出力される電圧V2をDAC222で設定される増幅率で増幅して、電圧V3を出力する。

【0113】

エラーアンプ23は、DAC22から出力される電圧V1と、可変アンプ224から出力される電圧V3との差を増幅して、増幅された電圧を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。

【0114】

(電源制御動作)

図14は、第3の実施形態におけるフェーズ数の変更時の増幅率の変更手順を表わす図である。

【0115】

まず、CPU25は、フェーズ数を指定した制御コマンドをシリアル通信線へ出力する(ステップS101)。

【0116】

SVIDインタフェース14は、シリアル通信線から受信した制御コマンドを解釈し、フェーズ数制御を位相クロック生成部21に指示する(ステップS102)。

【0117】

DACデジタルステップ制御部220は、シーケンステーブルレジスタから、指示されたフェーズ数と現在のフェーズ数に対応する段階的変更スケジュールを得る(ステップS103)。

【0118】

DACデジタルステップ制御部220は、段階的変更スケジュールに従って、DAC22を介して、可変アンプ224の増幅率を変化させる(ステップS104)。

【0119】

DACデジタルステップ制御部20は、指示された通常指示電圧Vtを目標値とし、この目標値に達するための、デジタル電圧DVを出力する(ステップS105)。

【0120】

DAC22は、デジタル電圧DVをアナログ電圧V1に変換する(ステップS106)

。差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する(ステップS107)。

【0121】

可変アンプ224は、差動アンプ24の出力を設定された増幅率で増幅して電圧V3を出力する(ステップS108)。

【0122】

エラーアンプ23は、DAC22から出力される電圧V1と、可変アンプ224から出力される電圧V3との差を増幅して、増幅された電圧(Eout)を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。電圧レギュレータは、エラーアンプ23から出力される電圧(Eout)に基づいて、出力する電圧を補正する。たとえば、指示電圧Vtより高電位側の電圧VSEN1が低い場合は、ハイサイドMOSトランジスタ196がオンすることで、高電位側の電圧VSEN1を上昇させる。また、指示電圧Vtより高電位側の電圧VSEN1が高い場合は、ロウサイドMOSトランジスタ197がオンすることで、高電位側の電圧VSEN1を降下させる(ステップS109)。

【0123】

その後、ステップS104に戻り、処理が繰返される。

図15は、第3の実施形態の段階的スケジュールテーブルの例を表わす図である。

【0124】

図15の一例では、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合には、5段階でフェーズを変化させるように定められている。実行時間ΔT(1)のステップ1において、フェーズ数がKを維持し、増幅率がF(1)となるように定められている。実行時間ΔT(2)のステップ2において、フェーズ数がKを維持し、増幅率がF(2)となるように定められている。実行時間ΔT(3)のステップ3において、フェーズ数がMに変化し、増幅率がF(3)となるように定められている。実行時間ΔT(4)のステップ4において、フェーズ数がMを維持し、増幅率がF(4)となるように定められている。実行時間ΔT(4)のステップ5において、フェーズ数がMを維持し、増幅率がF(5)となるように定められている。

【0125】

図16は、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合の増幅率の変化を説明するための図である。ここでは、F(1)=8、F(2)=4、F(3)=4、F(4)=2、F(5)=1であるとして説明する。

【0126】

まず、ステップ1で、フェーズ数がKを維持し、増幅率がF(1)(=8)となる。

ステップ2で、フェーズ数がKを維持し、増幅率がF(2)(=4)となる。

【0127】

ステップ3で、フェーズ数がMに変化し、増幅率がF(3)(=4)となる。

ステップ4で、フェーズ数がMを維持し、増幅率がF(4)(=2)となる。

【0128】

ステップ5で、フェーズ数がMを維持し、増幅率がF(5)(=1)となる。

図17は、第3の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【0129】

図17に示すように、従来のように、フェーズ数を変化させるときに、増幅率を変更しない場合には、出力電圧(Vo)が急激に変化し、アンダーシュートが発生する。

【0130】

本実施の形態のように、フェーズ数を変化させるときに、増幅率を段階的に変更する場合は、出力電圧(Vo)が緩やかに変化し、アンダーシュートが発生しない。

【0131】

以上のように、本実施の形態によれば、フェーズ切替え前から、可変アンプの増幅率を段階的に切替えることによって、アンダーシュートを相殺することができる。

【0132】

また、PWM周期の途中で、ステップを切替えた場合、電圧レギュレータのスイッチングバランスが乱れ、電圧が安定しにくくなるようなときには、各ステップの実行時間(すなわち、ステップの切替タイミング)をPWM周期のタイミングに同期させることも可能である。また、複数のステップのうち、一部のステップ(フェーズ数が切替るステップおよび/または増幅率が切替るステップ)の切替タイミングをPWM周期に同期させ、他のステップの切替タイミングは、段階的スケジュールテーブルに設定されたものを用いることとしてもよい。

【0133】

また、本実施の形態によれば、ボード設計終了後に発見された電圧変動があった場合にでも、IC外部のフィルタ回路の再調整を必要とせずファームウエアの変更のみで対処が可能となる。

【0134】

(変形例)

本発明は、上記の実施形態に限定されるものではなく、たとえば以下のような変形例も含む。

【0135】

(1) 第1〜第3の実施形態の機能を組み合わせることとしてもよい。この場合、シーケンステーブルレジスタは、第1〜第3の実施形態で説明した段階的スケジュールテーブルを記憶することとなる。

【0136】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0137】

1,1A,1B コントローラ、2 電源異常監視回路、3 電源異常監視部、4 電圧コンパレータ、5 MCU、6 PIN制御部、7 フラッシュメモリ、8 パラメータレジスタ、9 パフォーマンスレジスタ、10 PMBUSインタフェース、11 アナログ電源制御回路、12,12A,12B SVIDコマンド判定回路、13,13A,13B ハードロジック電源制御回路、161,161A,161B 制御部、14 SVIDインタフェース、15,115,215 シーケンステーブルレジスタ、16 動作モードレジスタ、17,18 電圧指示値レジスタ、19 パワーステート指示値レジスタ、20,120,220 DACデジタルステップ制御部、21,121 位相クロック生成部、22 DAC、23 エラーアンプ、24 差動アンプ、25 CPU、26 電位固定部、27 システム制御部、30−1〜30−n 電圧レギュレータ、31 PWM比較器、32 ラッチ回路、33 DC−DCコンバータ、151 PWM部、196 ハイサイドMOSトランジスタ、197 ロウサイドMOSトランジスタ、198 MOS制御部。

【技術分野】

【0001】

本発明は、コントローラに関し、特に、CPU(Central Processing Unit)などの半導体装置の電源を制御するためのコントローラに関する。

【背景技術】

【0002】

電源電圧切り替え動作時に発生するオーバーシュート/アンダーシュートを低減し、かつ電圧切り替えスピードを高速化することができる電源装置が知られている。

【0003】

たとえば、特許文献1(特開2007−288974号公報)の電源装置は、出力電圧を上げる過渡状態には、スイッチングレギュレータ400用のレジスタであるDCDC用レジスタのDAC値DD1を、シリーズレギュレータ300用のレジスタであるLDO用レジスタ201のDAC値LD01に代えてLDO用DAC302に供給し、シリーズレギュレータ300のLDO用DAC302は、DCDC用レジスタ202のDAC値DD1を参照してDAC動作を行う。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−288974号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1の装置は、電圧変更時の応答性と効率を両立することを目的としており、電圧の切り換え時のオーバシュートおよびアンダーシュートを防ぐために、切り換え時に応答速度の速いLDOと、電力効率の高いDCDCとを両方動作させて、両者の設定電圧を工夫することで、電流駆動の割合の最適化を行なっている。

【0006】

しかしながら、特許文献1の装置では、LDOとDCDCの2種類のレギュレータが必要となる。

【0007】

それゆえに、本発明の目的は、2種類のレギュレータを使用しなくても、電圧の切り換え時にオーバシュートおよびアンダーシュートを発生しないようにすることができるコントローラを提供することである。

【課題を解決するための手段】

【0008】

本発明の一実施形態のコントローラは、第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、現在の台数から指示された変更後の台数へ段階的に動作させる電圧レギュレータの台数を変更する制御部とを備える。

【発明の効果】

【0009】

本発明の一実施形態によれば、2種類のレギュレータを使用しなくても、電圧の切り換え時にオーバシュートおよびアンダーシュートを発生しないようにすることができる。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態の半導体システムの構成を表わす図である。

【図2】第1の実施形態の電圧制御動作の処理手順を表わすフローチャートである。

【図3】第1の実施形態のフェーズ数の制御手順を表わす図である。

【図4】第1の実施形態の段階的スケジュールテーブルの例を表わす図である。

【図5】現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化を説明するための図である。

【図6】第1の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【図7】第2の実施形態の半導体システムの構成を表わす図である。

【図8】第2の実施形態におけるフェーズ数の変更時の目標電圧の制御手順を表わす図である。

【図9】第2の実施形態の段階的スケジュールテーブルの例を表わす図である。

【図10】現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化および目標電圧を説明するための図である。

【図11】第2の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【図12】第2の実施形態の変形例における制御内容を説明するための図である。

【図13】第3の実施形態の半導体システムの構成を表わす図である。

【図14】第3の実施形態におけるフェーズ数の変更時の増幅率の変更手順を表わす図である。

【図15】第3の実施形態の段階的スケジュールテーブルの例を表わす図である。

【図16】現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合の増幅率の変化を説明するための図である。

【図17】第3の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態について図面を参照して説明する。

[第1の実施形態]

図1は、第1の実施形態の半導体システムの構成を表わす図である。

【0012】

図1を参照して、この半導体システムは、コントローラ1と、レギュレータ群30と、CPU25とを備える。

【0013】

レギュレータ群30は、コントローラ1と、CPU25の制御によって、電圧VoをCPU25へ供給する。レギュレータ群30は、電圧レギュレータ30−1〜30−nを備える。

【0014】

コントローラ1は、ここでは1チップ(1つの半導体チップ)で構成されている。

コントローラ1は、PIN制御部6と、フラッシュメモリ7と、パラメータレジスタ8と、パフォーマンスレジスタ9と、MCU5と、PMBUS(Power Management Bus)インタフェース10と、SVID(Serial VID)コマンド判定回路12と、ハードロジック電源制御回路13と、アナログ電源制御回路11と、電源異常監視回路2とを備える。

【0015】

コントローラ1の構成要素のうち、MCU5と、ハードロジック電源制御回路13と、アナログ電源制御回路11と、電源異常監視回路2とで、制御部161を構成する。

【0016】

SVIDコマンド判定回路12は、SVIDインタフェース14と、動作モードレジスタ16と、電圧指示値レジスタ18と、パワーステート指示値レジスタ19とを備える。

【0017】

CPU25は、ここでは、1チップで構成され、電圧レギュレータ30−1〜30−nから出力される電源電圧を受けて、様々な処理を行なう。また、CPU25は、SVIDインタフェース14を通じて、コントローラ1に指示を送る。たとえば、CPU25は、必要な電力量に応じて、動作させる電圧レギュレータの変更を指示する制御信号をSVIDインタフェース14を通じて、コントローラ1に送る。

【0018】

PIN制御部6は、外部の電位固定部26によって固定された端子の電位に従って、外部端子がどのように設定されたかを表わす設定情報をMCU5に出力する。

【0019】

フラッシュメモリ7は、MCU5が処理を行なうためのプログラムを格納する。プログラムを用いることによって、電源規格の変更があっても、デバイスを再開発する手間を省くことができる。また、フラッシュメモリ7は、最大許容電圧値、最大許容温度、および最大許容電流などの初期値を定めた複数のパラメータのテーブルを記憶する。

【0020】

パラメータレジスタ8は、SVIDインタフェース14を通じて、デジタルステップ制御でのステップごとの電圧値の変化量(刻み電圧)、および放電モードでの下げたい最終電圧である指示電圧と放電モードを指示電圧に達する前に放電モードを終了するときの目標電圧Vsとの差であるΔVの値などを記憶する。

【0021】

パフォーマンスレジスタ9は、フラッシュメモリ7に記録された最大許容電圧値、最大許容温度、および最大許容電流などのデータ受け取り、記憶する。

【0022】

ここで、最大許容電圧値は、CPUにかけることが可能な最大の電源電圧である。最大許容温度は、電圧レギュレータなどから測定される温度で動作上許される最高の温度である。最大許容電流は、電圧レギュレータが流すことができる最大の電流である。これらの値を超えた場合は、コントローラは値を下げるように電圧レギュレータなどに指示信号を出力する。

【0023】

MCU5は、プログラムに基づいて演算処理を行なう。

PMBUSインタフェース10は、PMBUSを通じて、外部のシステム制御部27から信号を受けるとともに、外部のシステム制御部27へ信号を出力する。

【0024】

SVIDインタフェース14は、シリアル通信線を通じて、CPU25からの信号を受けるとともに、CPU25へ信号を出力する。

【0025】

動作モードレジスタ16は、現在の動作モードを記憶する。たとえば、動作モードとして、通常モード、放電モードなどがある。

【0026】

電圧指示値レジスタ18は、電圧制御時の指示電圧の値を記憶する。

パワーステート指示値レジスタ19は、パワーステート制御時のパワーステートモードの指定値を記憶する。

【0027】

シーケンステーブルレジスタ15は、段階的スケジュールテーブルを記憶する。段階的スケジュールテーブルは、変更前のフェーズ数と、変更後のフェーズ数の組合せごとに、複数のステップの各々のフェーズ数、実行時間を定める。ここで、フェーズ数とは、動作させる電圧レギュレータの数である。

【0028】

ハードロジック電源制御回路13は、DACデジタルステップ制御部20と、位相クロック生成部21とを備える。

【0029】

DACデジタルステップ制御部20は、複数回のステップで指示された電圧に達するように、各ステップでの電圧変化値を決定し、決定した電圧変化値をデジタル電圧DVとして出力する。

【0030】

位相クロック生成部21は、動作させる電圧レギュレータへの制御信号SMODを活性化する。位相クロック生成部21は、動作させる電圧レギュレータへの位相クロックの位相を決定し、決定した位相の位相クロックを出力する。位相クロック生成部21は、内部のタイマに従って、PWM(Pulse Width Modulation)周期のタイミングで位相クロックを生成する。電圧レギュレータの位相クロックの周期は、すべて同一(PWM周期)であるが、電圧レギュレータの位相クロックの位相は、すべて異なる。位相クロック生成部21は、停止させる電圧レギュレータへの制御信号SMODを非活性化する。

【0031】

位相クロック生成部21は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けた場合に、シーケンステーブルレジスタ内の段階的スケジュールテーブルに従って、現在のフェーズ数からCPU25から指示された変更後のフェーズ数へ段階的にフェーズ数を変更する。位相クロック生成部25は、段階的スケジュールテーブルで定められる各ステップの実行時間に従って、ステップを切替える。

【0032】

アナログ電源制御回路11は、DAC(Digital Analog Converter)22と、差動アンプ24と、エラーアンプ23と、ADC(Analog Digital Converter)17とを備える。

【0033】

DAC22は、DACデジタルステップ制御部20から出力されたデジタル電圧DVをアナログ電圧V1に変換する。

【0034】

差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する。

【0035】

エラーアンプ23は、DAC22から出力される電圧V1と、差動アンプ24から出力される電圧V2との差を増幅して、増幅された電圧を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。

【0036】

ADC17は、電圧レギュレータ30−1〜30−nの出力電圧などをAD変換する。

電源異常監視回路2は、電圧コンパレータ4と、電源異常監視部3とを備える。

【0037】

電圧コンパレータ4は、電圧レギュレータにより生成された電圧を受け、所定の標準電圧とをアナログ処理で比較する。

【0038】

電源異常監視部3は、電圧コンパレータ4の出力に従って、CPU25の電源電圧が異常であるか否かを監視する。

【0039】

電圧レギュレータ30−1〜30−nは、CPU25に電源電圧を供給する。ここでは、各電圧レギュレータ30−1〜30−nはそれぞれ、1つのパッケージに収められている。さらにここでは、パッケージ内にハイサイドMOSトランジスタ196、ロウサイドMOSトランジスタ197、その他の部分(PWM部151とMOS制御部198)の3チップで構成されている。

【0040】

電圧レギュレータ30−1〜30−nは、PWM部151と、DC−DC変換器33とを備える。電圧レギュレータ30−1〜30−nは、制御信号SMODが活性化されると動作し、制御信号SMODが非活性化されると動作を停止する。

【0041】

PWM部151は、PWM比較器31と、ラッチ回路32とを備える。

PWM比較器31は、エラーアンプ23の出力である誤差信号をもとにPWM信号を出力する。

【0042】

ラッチ回路32のセット端子Sには、PWM比較器31の出力が入力される。ラッチ回路32のリセット端子Rには、位相クロック生成部21の出力であるクロックが入力される。

【0043】

DC−DC変換器33は、ラッチ回路32の出力と接続され、CPU25へ電源電圧を供給する。ここでは、ラッチ回路32から出力されるPWM信号によりDC−DC変換器33が制御される。

【0044】

図1に示すハイサイドMOSトランジスタ196がオンし、ロウサイドMOSトランジスタ197がオフすることで、CPU25の高電位側のCPU電圧線の電圧VSEN1が上昇する。他方、ハイサイドMOSトランジスタ196がオフし、ロウサイドMOSトランジスタ197がオンすることで、CPU電圧線の電圧VSEN1が降下する。

【0045】

通常モードでは、CPU電圧線の電圧VSEN1が一定の電圧になるように、ハイサイドMOSトランジスタ196とロウサイドMOSトランジスタ197のオン/オフが制御される。つまり、電圧が低い場合はハイサイドMOSトランジスタ196をオンさせて(このときロウサイドMOSトランジスタ197をオフ)電圧を上昇させたり、電圧が高い場合はロウサイドMOSトランジスタ197をオンさせて(このときハイサイドMOSトランジスタ196をオフ)電圧を降下させる。

【0046】

(電源制御動作)

図2は、第1の実施形態の電圧制御動作の処理手順を表わすフローチャートである。

【0047】

図2を参照して、CPU25は、電圧値Vtを指定した電圧制御コマンドをシリアル通信線へ出力する(ステップS801)。

【0048】

SVIDインタフェース14は、シリアル通信線から受信したコマンドを解釈し、電圧制御をDACデジタルステップ制御部20に指示する(ステップS802)。

【0049】

DACデジタルステップ制御部20は、指示された通常指示電圧Vtを目標値とし、この目標値に達するための、デジタル電圧DVを出力する(ステップS803)。

【0050】

DAC22は、デジタル電圧DVをアナログ電圧V1に変換する(ステップS804)。

【0051】

差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する(ステップS805)。

【0052】

エラーアンプ23は、DAC22から出力される電圧V1と、差動アンプ24から出力される電圧V2との差を増幅して、増幅された電圧(Eout)を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。電圧レギュレータは、エラーアンプ23から出力される電圧(Eout)に基づいて、出力する電圧を補正する。たとえば、指示電圧Vtより高電位側の電圧VSEN1が低い場合は、ハイサイドMOSトランジスタ196がオンすることで、高電位側の電圧VSEN1を上昇させる。また、指示電圧Vtより高電位側の電圧VSEN1が高い場合は、ロウサイドMOSトランジスタ197がオンすることで、高電位側の電圧VSEN1を降下させる(ステップS806)。

【0053】

その後、ステップS803に戻り、処理が繰返される。

これにより、高電位側の電圧VSEN1が指示電圧Vtになるように制御される。

【0054】

(フェーズ数の制御動作)

図3は、第1の実施形態のフェーズ数の制御手順を表わす図である。

【0055】

まず、CPU25は、複数の電圧レギュレータのうち動作させる台数(フェーズ数)の変更を指示する制御コマンドをシリアル通信線へ出力する(ステップS901)。

【0056】

SVIDインタフェース14は、シリアル通信線から受信した制御コマンドを解釈し、フェーズ数制御を位相クロック生成部21に指示する(ステップS902)。

【0057】

位相クロック生成部21は、シーケンステーブルレジスタから、指示されたフェーズ数と現在のフェーズ数に対応する段階的スケジュールテーブルを得る(ステップS903)。

【0058】

位相クロック生成部21は、段階的スケジュールテーブルに従って、フェーズ数を変化させる。位相クロック生成部21は、各段階でのフェーズ数に従って、電圧レギュレータ30−1〜30−nのうち動作させる電圧レギュレータと、停止させる電圧レギュレータとを決める。フェーズ数を変化させる場合には、可能な限り、位相クロックが均等となるように決定する。たとえば、8個の電圧レギュレータから8個の位相クロックが出力されているときには、フェーズ数を4個に変更する場合には、変更の結果、出力される4個の位相クロックの間隔が均等になるように、動作させる電圧レギュレータと停止させる電圧レギュレータとを決定する。位相クロック生成部21は、動作させる電圧レギュレータ対し制御信号SMODを活性化し、動作させる電圧レギュレータへ決定された位相のクロックを出力する。電圧レギュレータは、活性化された制御信号SMODを受けると、位相クロック生成部21から送られるクロックに基づいて、電圧を出力する。位相クロック生成部21は、停止させる電圧レギュレータに対し制御信号SMODを非活性化する。電圧レギュレータは、非活性化された制御信号SMODを受けると、電圧の出力を停止する(ステップS904)。

【0059】

図4は、第1の実施形態の段階的スケジュールテーブルの例を表わす図である。

図4の一例では、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合には、4段階でフェーズを変化させるように定められている。ステップ1において、実行時間ΔT(1)内にフェーズ数が+i(1)だけ増加するように定められている。ステップ2において、実行時間ΔT(2)内にフェーズ数が+i(2)だけ増加するように定められている。ステップ3において、実行時間ΔT(3)内にフェーズ数が+i(3)だけ増加するように定められている。ステップ4において、実行時間ΔT(4)内にフェーズ数が+i(4)だけ増加するように定められている。

【0060】

図4の別の例では、現在のフェーズ数Kが16であり、変更後のフェーズ数Mが2の場合には、6段階でフェーズを変化させるように定められている。ステップ1において、実行時間ΔT(1)内にフェーズ数が+i(1)だけ増加するように定められている。ステップ2において、実行時間ΔT(2)内にフェーズ数が+i(2)だけ増加するように定められている。ステップ3において、実行時間ΔT(3)内にフェーズ数が+i(3)だけ増加するように定められている。ステップ4において、実行時間ΔT(4)内にフェーズ数が+i(4)だけ増加するように定められている。ステップ5において、実行時間ΔT(5)内にフェーズ数が+i(5)だけ増加するように定められている。ステップ6において、実行時間ΔT(6)内にフェーズ数が+i(6)だけ増加するように定められている。

【0061】

図5は、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化を説明するための図である。ここでは、i(1)=0、i(2)=−4、i(3)=−2、i(4)=−1であるとして説明する。

【0062】

まず、ステップ1で、フェーズ数がK+i(1)(つまり8)となる。ステップ2で、フェーズ数がK+i(1)+i(2)(つまり4)となる。ステップ3で、フェーズ数がK+i(1)+i(2)+i(3)(つまり2)となる。ステップ4で、フェーズ数がK+i(1)+i(2)+i(3)+i(4)(つまり1)となる。

【0063】

図6は、第1の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【0064】

図6に示すように、従来のように、フェーズ数を8から1に急激に変化させた場合には、出力電圧(Vo)が急激に変化し、アンダーシュートが発生する。

【0065】

本実施の形態のように、フェーズ数を8→4→2→1と段階的に変化された場合には、出力電圧(Vo)が緩やかに変化し、アンダーシュートが発生しない。

【0066】

以上のように、本実施の形態によれば、フェーズ数を徐々に変化させることにより、アンダーシュートが発生するのを防止できる。

【0067】

また、本実施の形態によれば、フェーズ数を間引く場合に、レギュレータ群30から出力される複数個の位相クロックの間隔が均等になるように、動作させる電圧レギュレータと停止させる電圧レギュレータとを決定するので、電圧を安定化させることができる。

【0068】

また、段階的スケジュールの設定をレジスタとして持たせておくことにより、電圧安定を優先するか、短期間切替えを優先するか、状況に応じて設定を変更することもできる。たとえば、負荷状態の変更を直ちに行いたい場合、フェーズ数の切替えは速やかに行う必要があるので、フェーズ数を8から1へ直接変更することも可能である。

【0069】

また、本実施の形態によれば、ボード設計終了後に発見された電圧変動があった場合にでも、IC外部のフィルタ回路の再調整を必要とせずファームウエアの変更のみで対処が可能となる。

【0070】

なお、PWM周期の途中で、フェーズ数を間引いた場合、電圧レギュレータのスイッチングバランスが乱れ、電圧が安定しにくくなるような場合には、各ステップの実行時間(すなわち、ステップの切替タイミング)をPWM周期のタイミングに同期させることも可能である。また、複数のステップのうち、一部のステップの切替タイミングをPWM周期に同期させ、他のステップの切替タイミングは、段階的スケジュールテーブルに設定されたものを用いることとしてもよい。

【0071】

[第2の実施形態]

図7は、第2の実施形態の半導体システムの構成を表わす図である。

【0072】

図7を参照して、この半導体システムが、図1の第1の実施形態の半導体システムと相違する点は、以下のコントローラ1Aに関する点である。

【0073】

SVIDコマンド判定回路12Aにおけるシーケンステーブルレジスタ115は、段階的スケジュールテーブルを記憶する。段階的スケジュールテーブルは、変更前のフェーズ数と、変更後のフェーズ数の組合せごとに、複数のステップの各々のオフセット電圧、実行時間を定める。ここで、オフセット電圧とは、CPU25からの指示電圧から目標電圧を設定するために用いられる。

【0074】

ハードロジック電源制御回路13Aにおける位相クロック生成部121は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けた場合に、現在のフェーズ数からCPU25から指示された変更後のフェーズ数へ変更する。

【0075】

ハードロジック電源制御回路13AにおけるDACデジタルステップ制御部120は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けないときには、第1の実施形態で説明したように、指示電圧を目標電圧とし、CPU25に与えられる電圧が目標電圧となるように制御する。

【0076】

DACデジタルステップ制御部120は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、シーケンステーブルレジスタ115内の段階的スケジュールテーブルで定められるスケジュールに従って、指示電圧に段階的にオフセット電圧を加えることによって段階的に目標電圧を変更し、各段階でCPU25に与えられる電圧が目標電圧となるように制御する。DACデジタルステップ制御部120は、段階的スケジュールテーブルで定められる各ステップの実行時間に従って、ステップを切替える。

【0077】

(電源制御動作)

図8は、第2の実施形態におけるフェーズ数の変更時の目標電圧の制御手順を表わす図である。

【0078】

まず、CPU25は、フェーズ数を指定した制御コマンドをシリアル通信線へ出力する(ステップS301)。

【0079】

SVIDインタフェース14は、シリアル通信線から受信した制御コマンドを解釈し、フェーズ数制御をDACデジタルステップ制御部120に指示する(ステップS302)。

【0080】

DACデジタルステップ制御部120は、シーケンステーブルレジスタから、指示されたフェーズ数と現在のフェーズ数に対応する段階的変更スケジュールを得る(ステップS303)。

【0081】

DACデジタルステップ制御部120は、段階的変更スケジュールに従って、オフセット電圧を加えることによって目標値を変化させて(ステップS304)、デジタル電圧DVを出力する(ステップS305)。

【0082】

DAC22は、デジタル電圧DVをアナログ電圧V1に変換する(ステップS306)

。差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する(ステップS307)。

【0083】

エラーアンプ23は、DAC22から出力される電圧V1と、差動アンプ24から出力される電圧V2との差を増幅して、増幅された電圧(Eout)を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。電圧レギュレータは、エラーアンプ23から出力される電圧(Eout)に基づいて、出力する電圧を補正する。たとえば、指示電圧Vtより高電位側の電圧VSEN1が低い場合は、ハイサイドMOSトランジスタ196がオンすることで、高電位側の電圧VSEN1を上昇させる。また、指示電圧Vtより高電位側の電圧VSEN1が高い場合は、ロウサイドMOSトランジスタ197がオンすることで、高電位側の電圧VSEN1を降下させる(ステップS308)。

【0084】

その後、ステップS304に戻り、処理が繰返される。

図9は、第2の実施形態の段階的スケジュールテーブルの例を表わす図である。

【0085】

図9の一例では、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合には、6段階でフェーズを変化させるように定められている。実行時間ΔT(1)のステップ1において、フェーズ数がKを維持し、目標値が指示電圧Vtよりも+dv(1)だけ増加するように定められている。実行時間ΔT(2)のステップ2において、フェーズ数がKを維持し、目標値がさらに+dv(2)だけ増加するように定められている。実行時間ΔT(3)のステップ3において、フェーズ数がMに変化し、目標値がさらに+dv(3)だけ増加するように定められている。実行時間ΔT(4)のステップ4において、フェーズ数がMを維持し、目標値がさらに+dv(4)だけ増加するように定められている。実行時間ΔT(5)のステップ5において、フェーズ数がMを維持し、目標値がさらに+dv(5)だけ増加するように定められている。実行時間ΔT(6)のステップ6において、フェーズ数がMを維持し、目標値がさらに+dv(6)だけ増加するように定められている。

【0086】

図10は、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合のフェーズ数の変化および目標電圧を説明するための図である。ここでは、dv(1)=+20mv、dv(2)=+5mv、dv(3)=0mv、dv(4)=−5mv、dv(5)=−20mv、dv(6)=0mvであるとして説明する。

【0087】

まず、ステップ1で、フェーズ数がKを維持し、目標値がVt+dv(1)となる。

ステップ2で、フェーズ数がKを維持し、目標値がVt+dv(1)+dv(2)となる。ステップ3で、フェーズ数がMに変化し、目標値がVt+dv(1)+dv(2)+dv(3)となる。ステップ4で、フェーズ数がMを維持し、目標値がVt+dv(1)+dv(2)+dv(3)+dv(4)となる。ステップ5で、フェーズ数がMに変化し、目標値がVt+dv(1)+dv(2)+dv(3)+dv(4)+dv(5)となる。

ステップ6で、フェーズ数がMを維持し、目標値がVt+dv(1)+dv(2)+dv(3)+dv(4)+dv(5)+dv(6)となる。

【0088】

図11は、第2の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【0089】

図11に示すように、従来のように、フェーズ数を変化させるときに、指示電圧にオフセット電圧を加えない場合には、出力電圧(Vo)が急激に変化し、アンダーシュートが発生する。

【0090】

本実施の形態のように、フェーズ数を変化させるときに、指示電圧にオフセット電圧を段階的に加えた場合には、出力電圧(Vo)が緩やかに変化し、アンダーシュートが発生しない。

【0091】

以上のように、本実施の形態によれば、フェーズ切替え前に、目標電圧をオフセット(上昇)させ、フェーズ切替えが終了したのち、目標電圧のオフセットを解除(下降)することによって、アンダーシュートを相殺するができる。

【0092】

また、PWM周期の途中で、ステップを切替えた場合、電圧レギュレータのスイッチングバランスが乱れ、電圧が安定しにくくなるようなときには、各ステップの実行時間(すなわち、ステップの切替タイミング)をPWM周期のタイミングに同期させることも可能である。また、複数のステップのうち、一部のステップ(フェーズ数が切替るステップおよび/またはオフセット電圧が切替るステップ)の切替タイミングをPWM周期に同期させ、他のステップの切替タイミングは、段階的スケジュールテーブルに設定されたものを用いることとしてもよい。

【0093】

また、本実施の形態によれば、ボード設計終了後に発見された電圧変動があった場合にでも、IC外部のフィルタ回路の再調整を必要とせずファームウエアの変更のみで対処が可能となる。

【0094】

[第2の実施形態の変形例]

本変形例では、PWM周期ごとに発生するPWM周期割込み(位相クロック生成部内のタイマで生成する)のタイミングに基づいて、フェーズ数を切替る。

【0095】

図12は、第2の実施形態の変形例における制御内容を説明するための図である。

第2の実施形態で説明したように、フェーズ数を3から1に変更する際に、ステップ1〜ステップ6で段階的にオフセット電圧が変更される。

【0096】

まず、ステップ1で、フェーズ数が1を維持し、指示電圧Vtに20mvのオフセット電圧を加えた電圧が目標電圧となる。

【0097】

ステップ2で、フェーズ数が1を維持し、5mv増加したオフセット電圧を加えた電圧が目標電圧となる。

【0098】

ステップ3で、フェーズ数が3に変化し、オフセット電圧は増加されない。

ステップ4で、フェーズ数が3を維持し、5mv減少させたオフセット電圧を加えた電圧が目標電圧となる。

【0099】

ステップ5で、フェーズ数が3を維持し、20mv減少させたオフセット電圧を加えた電圧が目標電圧となる。

【0100】

ステップ6で、フェーズ数が3を維持し、オフセット電圧は増加されない。

フェーズ数の変更指令を受けたときに、内部ステータスがPS0からPS1へ変化し、PS1へ変化した時点から段階的スケジュールテーブルで定められた時間“8h05”が経過した時点でステップ1が開始する。

【0101】

ステップ1の開始から段階的スケジュールテーブルで定められた時間“8h30”が経過した時点でステップ1が終了し、ステップ2が開始する。

【0102】

PWM周期割込みが発生したときに、ステップ2が終了し、ステップ3が開始する。

ステップ3の開始から段階的スケジュールテーブルで定められた時間“8h40”が経過した時点でステップ3が終了し、ステップ4が開始する。

【0103】

ステップ4の開始から段階的スケジュールテーブルで定められた時間“8h10”が経過した時点でステップ4が終了し、ステップ5が開始する。

【0104】

ステップ5の開始から段階的スケジュールテーブルで定められた時間“8h16”が経過した時点でステップ5が終了し、ステップ6が開始する。

【0105】

[第3の実施形態]

図13は、第3の実施形態の半導体システムの構成を表わす図である。

【0106】

図13を参照して、この半導体システムが、図1の第1の実施形態の半導体システムと相違する点は、以下のコントローラ1Bに関する点である。

【0107】

SVIDコマンド判定回路12Bにおけるシーケンステーブルレジスタ215は、段階的スケジュールテーブルを記憶する。段階的スケジュールテーブルは、変更前のフェーズ数と、変更後のフェーズ数の組合せごとに、複数のステップの各々の増幅率、実行時間を定める。ここで、増幅率とは、差動アンプ24から出力される電圧V2を増幅する可変アンプ224の増幅率である。

【0108】

ハードロジック電源制御回路13Bにおける位相クロック生成部121は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けた場合に、現在のフェーズ数からCPU25から指示された変更後のフェーズ数へ変更する。

【0109】

ハードロジック電源制御回路13BにおけるDACデジタルステップ制御部220は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けないときには、DAC222を通じて、可変アンプ224の増幅率を「1」に設定させる(つまり、増幅しない)。これによって、CPU25に与えられている電圧と指示電圧との差に対応する電圧が電圧レギュレータに与えられる。

【0110】

DACデジタルステップ制御部220は、CPU25から動作させる電圧レギュレータの台数(フェーズ数)の変更を指示する制御コマンドを受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、シーケンステーブルレジスタ115内の段階的スケジュールテーブルで定められるスケジュールに従って、段階的に可変アンプ224の増幅率を変更する。これによって、各段階で、CPU25に与えられている電圧を各段階の増幅率で増幅した電圧と指示電圧との差に対応する電圧が電圧レギュレータに与えられる。

【0111】

DACデジタルステップ制御部220は、段階的スケジュールテーブルで定められる各ステップの実行時間に従って、ステップを切替える。

【0112】

DAC22は、DACデジタルステップ制御部20から出力されたデジタル電圧DVをアナログ電圧V1に変換する。差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する。可変アンプ224は、差動アンプ24から出力される電圧V2をDAC222で設定される増幅率で増幅して、電圧V3を出力する。

【0113】

エラーアンプ23は、DAC22から出力される電圧V1と、可変アンプ224から出力される電圧V3との差を増幅して、増幅された電圧を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。

【0114】

(電源制御動作)

図14は、第3の実施形態におけるフェーズ数の変更時の増幅率の変更手順を表わす図である。

【0115】

まず、CPU25は、フェーズ数を指定した制御コマンドをシリアル通信線へ出力する(ステップS101)。

【0116】

SVIDインタフェース14は、シリアル通信線から受信した制御コマンドを解釈し、フェーズ数制御を位相クロック生成部21に指示する(ステップS102)。

【0117】

DACデジタルステップ制御部220は、シーケンステーブルレジスタから、指示されたフェーズ数と現在のフェーズ数に対応する段階的変更スケジュールを得る(ステップS103)。

【0118】

DACデジタルステップ制御部220は、段階的変更スケジュールに従って、DAC22を介して、可変アンプ224の増幅率を変化させる(ステップS104)。

【0119】

DACデジタルステップ制御部20は、指示された通常指示電圧Vtを目標値とし、この目標値に達するための、デジタル電圧DVを出力する(ステップS105)。

【0120】

DAC22は、デジタル電圧DVをアナログ電圧V1に変換する(ステップS106)

。差動アンプ24は、CPU25の高電位側の電圧VSEN1と低電位側の電圧VSEN2の差を増幅して電圧V2を出力する(ステップS107)。

【0121】

可変アンプ224は、差動アンプ24の出力を設定された増幅率で増幅して電圧V3を出力する(ステップS108)。

【0122】

エラーアンプ23は、DAC22から出力される電圧V1と、可変アンプ224から出力される電圧V3との差を増幅して、増幅された電圧(Eout)を指定された電圧と現在のCPU25の電圧との差を表わす電圧として電圧レギュレータへ出力する。電圧レギュレータは、エラーアンプ23から出力される電圧(Eout)に基づいて、出力する電圧を補正する。たとえば、指示電圧Vtより高電位側の電圧VSEN1が低い場合は、ハイサイドMOSトランジスタ196がオンすることで、高電位側の電圧VSEN1を上昇させる。また、指示電圧Vtより高電位側の電圧VSEN1が高い場合は、ロウサイドMOSトランジスタ197がオンすることで、高電位側の電圧VSEN1を降下させる(ステップS109)。

【0123】

その後、ステップS104に戻り、処理が繰返される。

図15は、第3の実施形態の段階的スケジュールテーブルの例を表わす図である。

【0124】

図15の一例では、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合には、5段階でフェーズを変化させるように定められている。実行時間ΔT(1)のステップ1において、フェーズ数がKを維持し、増幅率がF(1)となるように定められている。実行時間ΔT(2)のステップ2において、フェーズ数がKを維持し、増幅率がF(2)となるように定められている。実行時間ΔT(3)のステップ3において、フェーズ数がMに変化し、増幅率がF(3)となるように定められている。実行時間ΔT(4)のステップ4において、フェーズ数がMを維持し、増幅率がF(4)となるように定められている。実行時間ΔT(4)のステップ5において、フェーズ数がMを維持し、増幅率がF(5)となるように定められている。

【0125】

図16は、現在のフェーズ数Kが8であり、変更後のフェーズ数Mが1の場合の増幅率の変化を説明するための図である。ここでは、F(1)=8、F(2)=4、F(3)=4、F(4)=2、F(5)=1であるとして説明する。

【0126】

まず、ステップ1で、フェーズ数がKを維持し、増幅率がF(1)(=8)となる。

ステップ2で、フェーズ数がKを維持し、増幅率がF(2)(=4)となる。

【0127】

ステップ3で、フェーズ数がMに変化し、増幅率がF(3)(=4)となる。

ステップ4で、フェーズ数がMを維持し、増幅率がF(4)(=2)となる。

【0128】

ステップ5で、フェーズ数がMを維持し、増幅率がF(5)(=1)となる。

図17は、第3の実施形態におけるレギュレータ群30の出力電圧(Vo)の変化の例を表わす図である。

【0129】

図17に示すように、従来のように、フェーズ数を変化させるときに、増幅率を変更しない場合には、出力電圧(Vo)が急激に変化し、アンダーシュートが発生する。

【0130】

本実施の形態のように、フェーズ数を変化させるときに、増幅率を段階的に変更する場合は、出力電圧(Vo)が緩やかに変化し、アンダーシュートが発生しない。

【0131】

以上のように、本実施の形態によれば、フェーズ切替え前から、可変アンプの増幅率を段階的に切替えることによって、アンダーシュートを相殺することができる。

【0132】

また、PWM周期の途中で、ステップを切替えた場合、電圧レギュレータのスイッチングバランスが乱れ、電圧が安定しにくくなるようなときには、各ステップの実行時間(すなわち、ステップの切替タイミング)をPWM周期のタイミングに同期させることも可能である。また、複数のステップのうち、一部のステップ(フェーズ数が切替るステップおよび/または増幅率が切替るステップ)の切替タイミングをPWM周期に同期させ、他のステップの切替タイミングは、段階的スケジュールテーブルに設定されたものを用いることとしてもよい。

【0133】

また、本実施の形態によれば、ボード設計終了後に発見された電圧変動があった場合にでも、IC外部のフィルタ回路の再調整を必要とせずファームウエアの変更のみで対処が可能となる。

【0134】

(変形例)

本発明は、上記の実施形態に限定されるものではなく、たとえば以下のような変形例も含む。

【0135】

(1) 第1〜第3の実施形態の機能を組み合わせることとしてもよい。この場合、シーケンステーブルレジスタは、第1〜第3の実施形態で説明した段階的スケジュールテーブルを記憶することとなる。

【0136】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0137】

1,1A,1B コントローラ、2 電源異常監視回路、3 電源異常監視部、4 電圧コンパレータ、5 MCU、6 PIN制御部、7 フラッシュメモリ、8 パラメータレジスタ、9 パフォーマンスレジスタ、10 PMBUSインタフェース、11 アナログ電源制御回路、12,12A,12B SVIDコマンド判定回路、13,13A,13B ハードロジック電源制御回路、161,161A,161B 制御部、14 SVIDインタフェース、15,115,215 シーケンステーブルレジスタ、16 動作モードレジスタ、17,18 電圧指示値レジスタ、19 パワーステート指示値レジスタ、20,120,220 DACデジタルステップ制御部、21,121 位相クロック生成部、22 DAC、23 エラーアンプ、24 差動アンプ、25 CPU、26 電位固定部、27 システム制御部、30−1〜30−n 電圧レギュレータ、31 PWM比較器、32 ラッチ回路、33 DC−DCコンバータ、151 PWM部、196 ハイサイドMOSトランジスタ、197 ロウサイドMOSトランジスタ、198 MOS制御部。

【特許請求の範囲】

【請求項1】

第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、

外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、

現在の台数から指示された変更後の台数へ段階的に動作させる電圧レギュレータの台数を変更する制御部とを備えた、コントローラ。

【請求項2】

前記コントローラは、

変更前の電圧レギュレータの台数と変更後の電圧レギュレータの台数の組合せごとに、複数の段階の各々の台数を定めたスケジュールを記憶するレジスタを備え、

前記制御部は、前記レジスタ内のスケジュールに従って、段階的に動作させる電圧レギュレータの台数を変更する、請求項1記載のコントローラ。

【請求項3】

前記レジスタは、さらに、各段階の実行時間を保持し、

前記制御部は、前記レジスタ内のスケジュールで定められる各段階の実行時間に従って、段階的に動作させる電圧レギュレータの台数を変更する、請求項2記載のコントローラ。

【請求項4】

前記制御部は、動作させる電圧レギュレータへ位相クロックを出力し、各電圧レギュレータの位相は、それぞれ相違し、

前記制御部は、前記電圧レギュレータに与える位相クロックの周期を、前記スケジュールの少なくとも1つの段階の実行時間とする、請求項1記載のコントローラ。

【請求項5】

第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、

指示電圧と、外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、

前記変更指令を受けないときには、前記指示電圧を目標電圧とし、前記第1の半導体装置に与えられる電圧が目標電圧となるように制御する制御部とを備え、

前記制御部は、前記変更指令を受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、前記指示電圧に加えるオフセット電圧を段階的に変更するスケジュールに従って、段階的に前記目標電圧を変更し、各段階で前記前記第1の半導体装置に与えられる電圧が前記目標電圧となるように制御する、コントローラ。

【請求項6】

前記コントローラは、

変更前の電圧レギュレータの台数と変更後の電圧レギュレータの台数の組合せごとに、、複数の段階の各々の前記オフセット電圧を定めた前記スケジュールを記憶するレジスタを備え、

前記制御部は、前記レジスタ内のスケジュールに従って、段階的に前記オフセット電圧を変更する、請求項5記載のコントローラ。

【請求項7】

前記レジスタは、さらに、各段階の実行時間を保持し、

前記制御部は、前記レジスタ内のスケジュールで定められる各段階の実行時間に従って、段階的に前記オフセット電圧を変更する、請求項6記載のコントローラ。

【請求項8】

前記制御部は、動作させる電圧レギュレータへ位相クロックを出力し、各電圧レギュレータの位相は、それぞれ相違し、

前記制御部は、前記電圧レギュレータに与える位相クロックの周期を、前記スケジュールの少なくとも1つの段階の実行時間とする、請求項5記載のコントローラ。

【請求項9】

第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、

指示電圧と、外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、

前記変更指令を受けないときには、前記指示電圧と前記第1の半導体装置に与えられている第1の電圧との差に対応する電圧を前記電圧レギュレータに与える制御部とを備え、

前記制御部は、前記変更指令を受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、前記第1の電圧の増幅率を段階的に変更するスケジュールに従って、段階的に前記第1の電圧の増幅率を変更し、各段階で、前記指示電圧と第1の電圧を前記増幅率で増幅した電圧の差に対応する電圧を前記電圧レギュレータに与える、コントローラ。

【請求項10】

前記コントローラは、

変更前の電圧レギュレータの台数と変更後の電圧レギュレータの台数の組合せごとに、複数の段階の各々の前記増幅率を定めた前記スケジュールを記憶するレジスタを備え、

前記制御部は、前記レジスタ内のスケジュールに従って、段階的に前記増幅率を変更する、請求項9記載のコントローラ。

【請求項11】

前記レジスタは、さらに、各段階の実行時間を保持し、

前記制御部は、前記レジスタ内のスケジュールで定められる各段階の実行時間に従って、段階的に前記増幅率を変更する、請求項10記載のコントローラ。

【請求項12】

前記制御部は、動作させる電圧レギュレータへ位相クロックを出力し、各電圧レギュレータの位相は、それぞれ相違し、

前記制御部は、前記電圧レギュレータに与える位相クロックの周期を、前記スケジュールの少なくとも1つの段階の実行時間とする、請求項9記載のコントローラ。

【請求項1】

第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、

外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、

現在の台数から指示された変更後の台数へ段階的に動作させる電圧レギュレータの台数を変更する制御部とを備えた、コントローラ。

【請求項2】

前記コントローラは、

変更前の電圧レギュレータの台数と変更後の電圧レギュレータの台数の組合せごとに、複数の段階の各々の台数を定めたスケジュールを記憶するレジスタを備え、

前記制御部は、前記レジスタ内のスケジュールに従って、段階的に動作させる電圧レギュレータの台数を変更する、請求項1記載のコントローラ。

【請求項3】

前記レジスタは、さらに、各段階の実行時間を保持し、

前記制御部は、前記レジスタ内のスケジュールで定められる各段階の実行時間に従って、段階的に動作させる電圧レギュレータの台数を変更する、請求項2記載のコントローラ。

【請求項4】

前記制御部は、動作させる電圧レギュレータへ位相クロックを出力し、各電圧レギュレータの位相は、それぞれ相違し、

前記制御部は、前記電圧レギュレータに与える位相クロックの周期を、前記スケジュールの少なくとも1つの段階の実行時間とする、請求項1記載のコントローラ。

【請求項5】

第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、

指示電圧と、外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、

前記変更指令を受けないときには、前記指示電圧を目標電圧とし、前記第1の半導体装置に与えられる電圧が目標電圧となるように制御する制御部とを備え、

前記制御部は、前記変更指令を受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、前記指示電圧に加えるオフセット電圧を段階的に変更するスケジュールに従って、段階的に前記目標電圧を変更し、各段階で前記前記第1の半導体装置に与えられる電圧が前記目標電圧となるように制御する、コントローラ。

【請求項6】

前記コントローラは、

変更前の電圧レギュレータの台数と変更後の電圧レギュレータの台数の組合せごとに、、複数の段階の各々の前記オフセット電圧を定めた前記スケジュールを記憶するレジスタを備え、

前記制御部は、前記レジスタ内のスケジュールに従って、段階的に前記オフセット電圧を変更する、請求項5記載のコントローラ。

【請求項7】

前記レジスタは、さらに、各段階の実行時間を保持し、

前記制御部は、前記レジスタ内のスケジュールで定められる各段階の実行時間に従って、段階的に前記オフセット電圧を変更する、請求項6記載のコントローラ。

【請求項8】

前記制御部は、動作させる電圧レギュレータへ位相クロックを出力し、各電圧レギュレータの位相は、それぞれ相違し、

前記制御部は、前記電圧レギュレータに与える位相クロックの周期を、前記スケジュールの少なくとも1つの段階の実行時間とする、請求項5記載のコントローラ。

【請求項9】

第1の半導体装置に電源電圧を供給する複数の電圧レギュレータを制御するコントローラであって、

指示電圧と、外部から前記複数の電圧レギュレータのうち動作させる台数の変更指令を受けるインタフェースと、

前記変更指令を受けないときには、前記指示電圧と前記第1の半導体装置に与えられている第1の電圧との差に対応する電圧を前記電圧レギュレータに与える制御部とを備え、

前記制御部は、前記変更指令を受けたときには、現在の台数から指示された変更後台数への移行時および移行の前後において、前記第1の電圧の増幅率を段階的に変更するスケジュールに従って、段階的に前記第1の電圧の増幅率を変更し、各段階で、前記指示電圧と第1の電圧を前記増幅率で増幅した電圧の差に対応する電圧を前記電圧レギュレータに与える、コントローラ。

【請求項10】

前記コントローラは、

変更前の電圧レギュレータの台数と変更後の電圧レギュレータの台数の組合せごとに、複数の段階の各々の前記増幅率を定めた前記スケジュールを記憶するレジスタを備え、

前記制御部は、前記レジスタ内のスケジュールに従って、段階的に前記増幅率を変更する、請求項9記載のコントローラ。

【請求項11】

前記レジスタは、さらに、各段階の実行時間を保持し、

前記制御部は、前記レジスタ内のスケジュールで定められる各段階の実行時間に従って、段階的に前記増幅率を変更する、請求項10記載のコントローラ。

【請求項12】

前記制御部は、動作させる電圧レギュレータへ位相クロックを出力し、各電圧レギュレータの位相は、それぞれ相違し、

前記制御部は、前記電圧レギュレータに与える位相クロックの周期を、前記スケジュールの少なくとも1つの段階の実行時間とする、請求項9記載のコントローラ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−115977(P2013−115977A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−261656(P2011−261656)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]